## 中文摘要

本年度為此三年期計畫的第一年，首先研究碳離子佈植方式對於 NiSi 金屬矽化物熱穩定性的影響，以提升金屬矽化物奈米線源極/汲極的熱穩定性。當 NiSi 金屬矽化物形成溫度小於或等於 700 °C 時，雖然碳原子存在於 NiSi 金屬矽化物中，片電阻值增加的幅度很小，甚至小於  $1 \Omega/\square$ 。當有足夠多的碳原子存在於 NiSi 金屬矽化物中時，即碳離子植入的劑量高達  $5 \times 10^{15} \text{ cm}^{-2}$  時，能夠有效抑制 NiSi 金屬矽化物的結塊與晶相轉換現象，退火溫度高達 850 °C 時，甚至不會發生結塊與晶相轉換現象，故與對照組相比，能將 NiSi 金屬矽化物熱穩定性的溫度提升 150 °C。

在矽奈米線製作方面，目前能夠穩定地控制削減電子束微影的光阻線寬大小，得到非常均勻的光阻奈米線圖案。進一步的蝕刻製程以及氧化縮減製程正在開發中。

**關鍵詞：**鎳化矽、金屬矽化物、奈米線、電子束微影

## Abstract

This is the 1<sup>st</sup> year of the 3-year project. IN this year, we study the effect of carbon ion implantation on the thermal stability of NiSi in order to improve the thermal stability of the source/drain region of nano-wire devices. It is observed that C in NiSi only slightly increase the sheet resistance at temperatures lower than 600°C. With sufficiently high dosage, for example  $5 \times 10^{15} \text{ cm}^{-2}$ , the agglomeration and phase transformation of NiSi can be suppressed even at 850°C. The preparation technique of Si nano-wire is under development. Using the e-beam lithography and photo-resist trimming processes, PR pattern as narrow as 18nm has been obtained. The Si etching and oxidation processes need to be fine-tuned.

**Keywords:** NiSi, metal silicide, nano-wire, e-beam lithography.

## 一、前言

金氧半場效電晶體 (MOSFET) 微縮到 65nm 以下時，NiSi 已經廣泛被使用作為源極/汲極 (source/drain) 的金屬矽化物接觸技術，NiSi 金屬矽化物有許多優點，包括低

電阻率、低接觸阻抗、低溫製程、較低的矽消耗率、無線寬效應 (narrow line effect) 以及沒有橋接短路效應。然而，高溫熱穩定性成為 NiSi 金屬矽化物應用的最主要問題，一是 NiSi 薄膜在 700 °C 會發生結塊 (agglomeration) 現象，使得 NiSi 薄膜形成不連續薄膜，造成其片電阻值上升，二是 NiSi 晶相在 750 °C 會產生晶相轉換 (phase transformation)，變成較高電阻率的 NiSi<sub>2</sub> 晶相，故結塊和晶相轉換這兩種因素是造成高溫下，NiSi 金屬矽化物的片電阻值 (sheet resistance, R<sub>s</sub>) 上升的主要原因。這個問題在奈米線結構可能更為嚴重，因此在矽奈米線製程開發的同時，需要先設法提升 NiSi 的熱穩定性。

矽奈米線的製作是本計畫的首要條件，本年度採取電子束微影製程製作約 50-60nm 的圖案，再經過光阻削減步驟，將線寬縮小到 20nm 左右，最後再以氧化方式，將直徑微縮到 10nm 或更小。希望能有所突破，使第二、三年計畫可以順利進行。

## 二、研究目的與文獻探討

NiSi 金屬矽化物有許多優點，包括低電阻率、低接觸阻抗、低溫製程、較低的矽消耗率、無線寬效應 (narrow line effect) 以及沒有橋接短路效應 (bridging failure) [1]。然而，高溫熱穩定性成為 NiSi 金屬矽化物應用的最主要問題，一是 NiSi 薄膜在 700 °C 會發生結塊 (agglomeration) 現象，使得 NiSi 薄膜形成不連續薄膜，造成其片電阻值上升，二是 NiSi 晶相在 750 °C 會產生晶相轉換 (phase transformation)，變成較高電阻率的 NiSi<sub>2</sub> 晶相，故結塊和晶相轉換這兩種因素是造成高溫下，NiSi 金屬矽化物的片電阻值 (sheet resistance, R<sub>s</sub>) 上升的主要原因。

目前有許多提升 NiSi 金屬矽化物熱穩定性的方法已經被提出，一是在形成 NiSi 金屬矽化物之前，利用離子植入 (ion implantation) 的方式將 F 或是 N<sub>2</sub>離子植入矽基材 [2-3]，二是利用 Ti 或是 Pt 薄膜作為覆蓋層 (capping layer) 或是介入層 (interposing layer) 的方式 [4-5]，三是使用 Ni<sub>1-x</sub>Ti<sub>x</sub> 或是 Ni<sub>1-x</sub>Pt<sub>x</sub> 合金的方式來形成 NiSi 金屬矽化物 [6-7]。

最近根據文獻報導，S. Zaima 等人提出在矽基材上，先用低壓化學氣相沈積的方法

( low-pressure chemical vapor deposition, LPCVD ) 成長一層  $p^+ Si_{0.996}C_{0.004}$  後，再鍍 Ni 薄膜以及高溫熱退火形成 NiSi 金屬矽化物，其結果發現可以有效將 NiSi 金屬矽化物的結塊溫度提升到 750 °C，且晶相轉換的溫度也提升到 850°C [8]，故得知將碳 (carbon, C) 原子加到矽基材中，能有效提升 NiSi 金屬矽化物的高溫熱穩定性，主要原因是因為碳原子在矽與 NiSi 金屬矽化物的固態溶解度 (solid solubility) 都很低，所以碳原子會在 NiSi 金屬矽化物內的晶粒邊界 (grain boundary) 與 NiSi 金屬矽化物和矽的界面析出 (segregation)，修正晶界能 (grain boundary energy) 與界面能 (interface energy) 來提升 NiSi 金屬矽化物的熱穩定性。然而，N 型金氧半場效電晶體的應變矽 (strained Si) 技術，使用深埋式源極/汲極 (embedded source/drain) 的  $Si_{1-x}C_x$  來提升載子遷移率時，由於碳原子在矽中的固態溶解度很低，故很難用選擇性晶 (selective epitaxy) 的方式，成長取代碳 (substitutional carbon) 的比例超過 1% 的  $Si_{1-x}C_x$ ，故本計畫目的是採用碳離子植入的方式，能夠有效形成高濃度的取代碳，且採用離子佈植的方式能與傳統的 CMOS 製程技術相容，來達到提升 NiSi 金屬矽化物的熱穩定性的目標。

另一方面來說，當互補金氧半導體 (CMOS) 電晶體持續微縮下，所遭遇到的主要問題即是短通道效應 (Short Channel Effect, SCE) 所造成元件特性的劣化，為了克服短通道效應，許多的多閘極 (Multi-gate) 三微元件新型結構被提出，包含了鰭狀電晶體 (Fin FET) [9]、三閘極電晶體 (Tri-gate FET) [10]、Omega-gate 電晶體 [11]、Pi-gate 電晶體 [12] 等等，目的是縮減矽通道層的厚度以及增加電晶體閘極的數目，來增加閘極對於通道電位的控制能力，來降低短通道效應，目前最極致的結構是發展到全包覆式閘極 (Gate All Around, GAA) 電晶體，本計畫以全包覆式閘極電晶體為長遠目標 [13-15]，故必須先發展製作矽奈米線 (Si nano-wire) 的技術，將此矽奈米線作為後續製作全包覆式閘極電晶體的矽通道層。

在光學微影技術達到最小線寬極限時，如何精確製作出直徑 30 奈米以下的奈米線是一個重要的課題，本計畫是採用

Top-Down 的電漿乾式蝕刻方式製作奈米線，配合光阻削減 (PR ashing) 的技術來縮減微影製程後的光阻線寬，根據文獻報導 [16]，光阻削減技術能夠有效控制奈米線的線寬大小，並且使得電漿乾式蝕刻後的矽奈米線線寬非常均勻，故這是我們採用此技術的原因。

### 三、研究方法

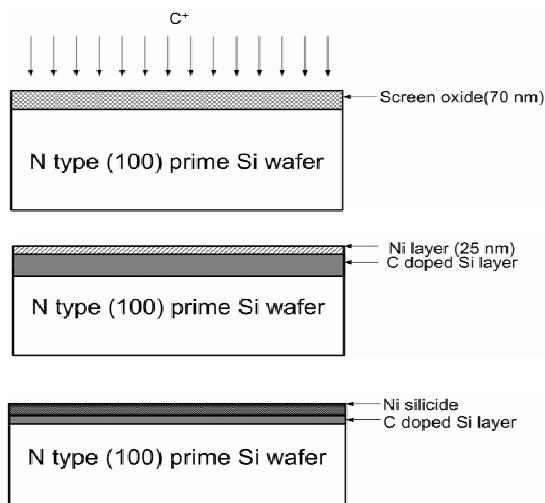

#### C-doped NiSi Technology

圖一為 C-doped NiSi 的金屬矽化物試片的製作流程圖。一開始使用 phosphorus-doped 的 (100) 六吋矽晶圓，其晶圓的電阻率為  $2\sim7 \Omega\text{-cm}$ ，接著成長 70 奈米的屏蔽氧化層 (screen oxide)，之後作碳離子植入，將碳離子打入矽晶圓中，碳離子植入的劑量條件範圍為  $1\times10^{15} \text{ cm}^{-2}$  與  $5\times10^{15} \text{ cm}^{-2}$ ，劑量大小主要是要研究關於碳含量的多寡對於 NiSi 金屬矽化物的熱穩定性影響，能量條件範圍為 30 keV 與 40 keV，能量大小主要是調整碳植入的  $R_p$  (projection range) 與 NiSi 金屬矽化物反應深度的相對位置，條件為 30 keV 的  $R_p$  較 NiSi 金屬矽化物反應深度來得淺，反之條件為 40 keV 的  $R_p$  較 NiSi 金屬矽化物反應深度來得深，並且也準備無作碳離子佈植的試片 (w/o carbon ion implantation samples) 作為本實驗的對照組。之後將作過碳離子植入的試片，一部份作 1050 °C 及 30 sec 的快速熱退火製程 (Rapid Thermal Annealing, RTA)，此部分的試片稱為 Carbon Implant Annealing samples (CIA samples)，作快速熱退火製程的目的是將植入的碳形成取代碳，另一部份未做快速熱退火製程的碳離子植入試片則稱為 w/o Carbon Implant Annealing samples (w/o CIA samples)。之後再利用稀釋的氟化氫 (DHF solution, HF:H<sub>2</sub>O = 1:50) 溶液將屏蔽氧化層給去除後，馬上使用物理氣相沈積機台 (Physical Vapor Deposition, PVD) 將 25 奈米的金屬 Ni 薄膜鍍在矽基材上，作 500~850 °C 及 30 sec 的一步驟快速熱退火 (one-step RTA) 來形成 NiSi 金屬矽化物，作後未反應的殘餘的 Ni 用硫酸及雙氧水混和比例為 3:1 的溶液去除，來完成試片的製作。在材料分析方面，用四點探針 (Four-point probe) 測量 NiSi 的金屬矽化物的片電阻，X 光繞射儀 (X-Ray Diffraction, XRD) 來分析 NiSi 晶相的金屬矽化物是否

有發生晶相轉換成  $\text{NiSi}_2$  晶相，而掃瞄式電子顯微鏡 (Scanning Electron Microscope, SEM) 用來觀察  $\text{NiSi}$  的金屬矽化物是否有結塊現象產生。

### **Si nano-wire Fabrication Technology**

一開始使用 boron-doped 的(100)六吋矽晶圓，其晶圓的電阻率為  $0.5\text{--}100 \Omega\text{-cm}$ ，用高溫濕式氧化爐管成長  $150$  奈米的二氧化矽層，接著用低壓化學氣相沈積爐管沈積非晶矽  $20$  奈米，最後在做作  $600^\circ\text{C}$  及  $24\text{ hr}$  的低溫長時間退火，即固相磊晶 (Solid Phase Epitaxy, SPE) 的再結晶方式，將非晶矽形成多晶矽，即完成 Poly-Si on Insulator (PSOI) 的晶片結構製作。接著用電子束微影 (E-Beam Lithography) 的方式曝出不同線寬大小的主動區域 (Active Region)，曝出的最小線寬約為  $60$  奈米，接著將晶片送入光阻蝕刻機台作低溫氧氣電漿的光阻削減製程，實驗時設定的溫度是  $60^\circ\text{C}$ 、RF power 的瓦數為  $900\text{ W}$ 、 $\text{O}_2$  的流量為  $2400\text{ sccm}$ ，我們改變不同的削減時間，來控制奈米線的線寬大小，並利用線上電子顯微鏡 (in-line SEM) 來觀察光阻削減前後的線寬大小，並計算出光阻的削減速率。

## **四、結果與討論**

### **C-doped $\text{NiSi}$ Technology**

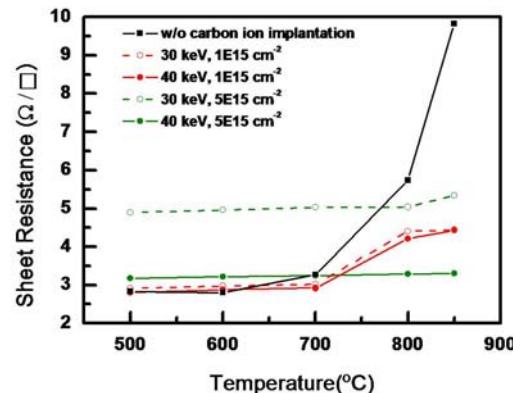

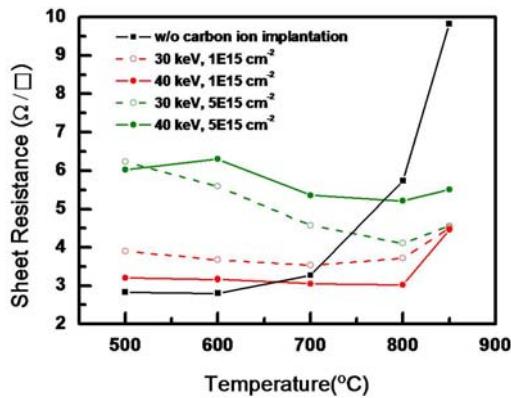

圖二為不同碳植入條件的 CIA samples 與 w/o carbon ion implantation samples (對照組) 的片電阻值跟退火溫度的關係圖。我們可以觀察到碳離子佈植的能量較低與劑量較高時，其片電阻值會較大一些，與對照組的片電阻值相比，可以發現低退火溫度下 ( $<700^\circ\text{C}$ )，由於碳原子存在於  $\text{NiSi}$  金屬矽化物的晶粒邊界，造成其片電阻值會較高。在屬  $\text{Ni}$  薄膜沈積後，直接量測  $\text{Ni}$  薄膜的片電阻，我們發現其中碳離子佈植的條件是  $5 \times 10^{15} \text{ cm}^{-2}$  以及  $30\text{ keV}$  的條件，其  $\text{Ni}$  薄膜的厚度較薄，故其  $\text{NiSi}$  金屬矽化物的片電阻值不管在任何溫度下都較其他條件來的高。

另外，我們可以看出對照組的片電阻值在退火溫度高於  $700^\circ\text{C}$  以上時，片電阻會持續增加，主要原因是因為  $\text{NiSi}$  金屬矽化物嚴重的結塊與發生晶相轉換形成高電阻率的  $\text{NiSi}_2$  晶相，然而對於碳離子植入的條件是  $1 \times 10^{15} \text{ cm}^{-2}$  的 CIA samples 來說，其片電阻值在  $700^\circ\text{C}$  時仍然非常穩定，到  $800^\circ\text{C}$

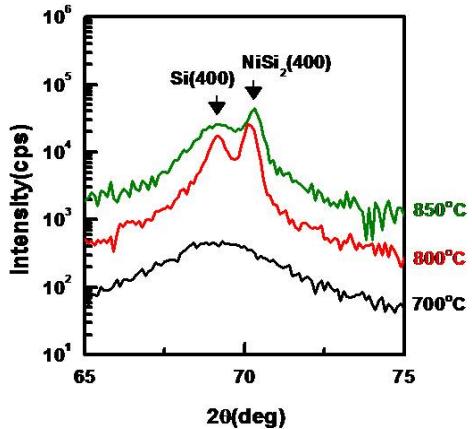

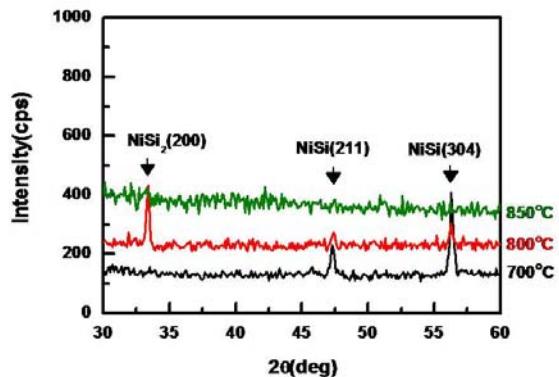

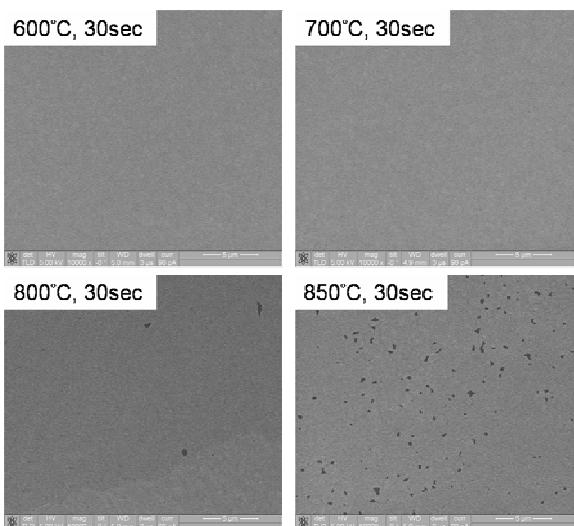

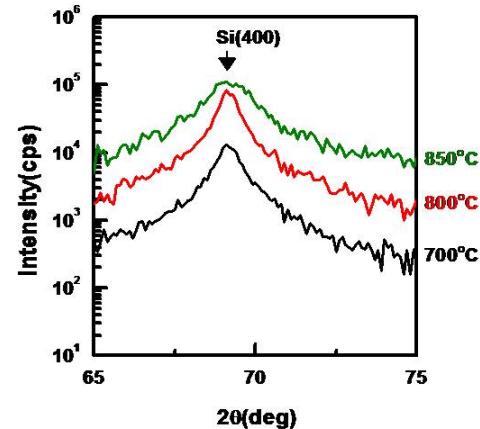

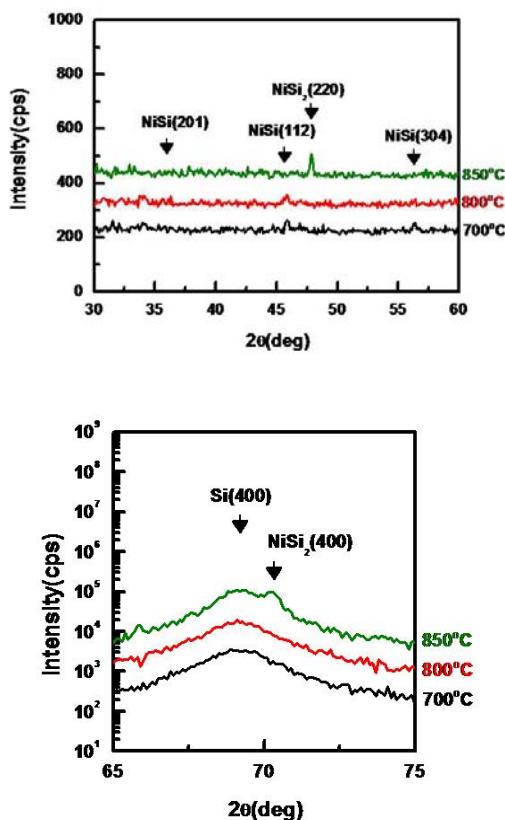

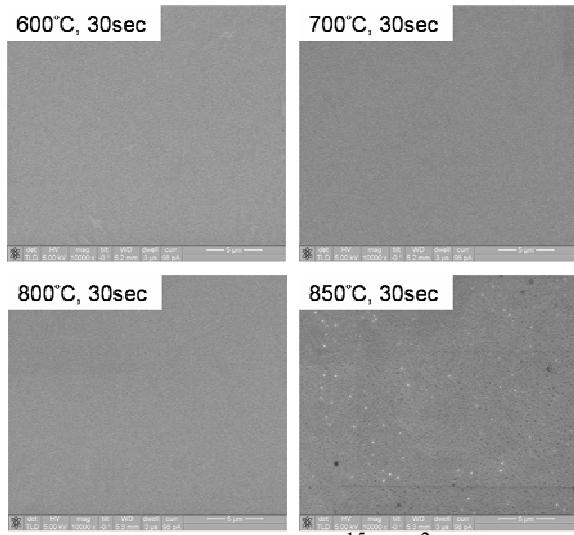

時，片電阻值才有明顯地增加，由圖三的 XRD 圖與圖四的 SEM 圖可以看出片阻值上升因素，主要是因為同時發生晶相轉換與些微的結塊現象。

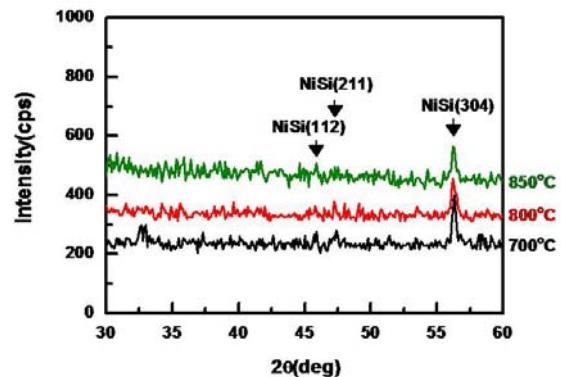

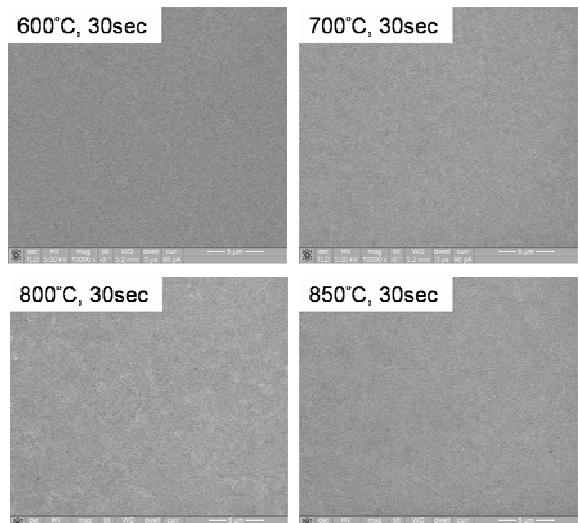

當碳植入的劑量達到  $5 \times 10^{15} \text{ cm}^{-2}$  時，可以看出其片電阻到  $800^\circ\text{C}$  時都非常穩定，片電阻與低退火溫度相比幾乎沒有增加，直到  $850^\circ\text{C}$  時，其片電阻才有些為增加，但是對於對照組而言，在  $850^\circ\text{C}$  時， $\text{NiSi}$  金屬矽化物有很嚴重的結塊現象，造成片電阻增加的很迅速。我們可以看到最佳的碳植入條件為  $5 \times 10^{15} \text{ cm}^{-2}$  與  $40\text{ keV}$ ，在退火溫度到達  $850^\circ\text{C}$  時，其片電阻值與低退火溫度相比，幾乎沒有增加，由圖五的 XRD 圖與圖六的 SEM 圖可以看出在  $850^\circ\text{C}$  時，並沒有發生晶相轉換與結塊的現象。

圖七為不同碳植入條件的 w/o CIA samples 與 w/o carbon ion implantation samples (對照組) 的片電阻值跟退火溫度的關係圖。對於碳植入條件為  $1 \times 10^{15} \text{ cm}^{-2}$  的 w/o CIA samples 來說，輕微的結塊與晶相轉換同時發生在  $800^\circ\text{C}$ ，造成片電阻值在  $800^\circ\text{C}$  會上升，此點結果與圖二的碳植入劑量為  $1 \times 10^{15} \text{ cm}^{-2}$  的 CIA samples 相同。對於 w/o CIA samples 來說，當碳植入的劑量高達  $5 \times 10^{15} \text{ cm}^{-2}$  時，將圖二與圖七相比，可以發現 w/o CIA samples 的片電阻值跟退火溫度的關係，比起 CIA samples 來得較大，我們推測此一結果的原因為晶粒大小變異的效應機制主導了此一現象，因為碳植入的量劑高達  $5 \times 10^{15} \text{ cm}^{-2}$  時，會將矽基材給非晶化，加上 w/o CIA samples 並未作  $1050^\circ\text{C}$  及  $30\text{ sec}$  的快速熱退火製程，故後續形成  $\text{NiSi}$  金屬矽化物的熱退火製程時，退火製程溫度越高，則形成的多晶  $\text{NiSi}$  金屬矽化物的晶粒會愈大，故其片電阻阻值愈低，對於碳植入條件為  $5 \times 10^{15} \text{ cm}^{-2}$  以及  $30\text{ keV}$  的條件來說，退火溫度小於或等於  $800^\circ\text{C}$  時，晶粒大小變異的效應主導了片電阻值的變化趨勢，然而當退火溫度到達  $850^\circ\text{C}$  時，由圖八的 XRD 與圖九的 SEM 圖可以看出晶相轉換與結塊的機制仍然主宰片電阻值，使其片電阻值在  $850^\circ\text{C}$  時會增加，而不是減少。

表一為各碳離子佈植條件的結塊溫度與晶相轉換溫度的總整理表格，可以歸納出當碳植入劑量為  $1 \times 10^{15} \text{ cm}^{-2}$  時，結塊溫度與晶相轉換溫度能夠達到  $800^\circ\text{C}$ ，當碳植入劑

量升高至  $5 \times 10^{15} \text{ cm}^{-2}$  時，可以更進一步將結塊溫度與晶相轉換溫度提升到 850 °C。

### Si nano-wire Fabrication Technology

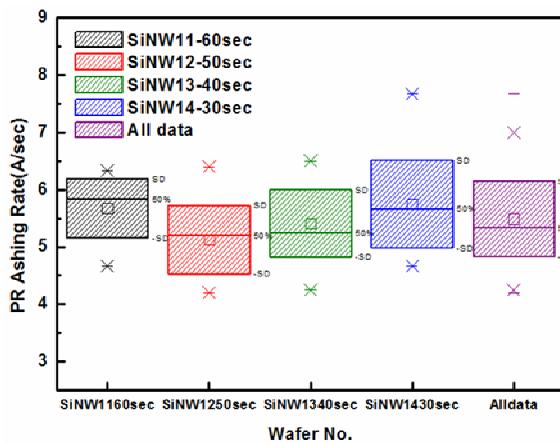

圖十為測試不同削減時間 (30 sec~60 sec) 下，其削減速率 (ashing rate) 的統計分佈圖，其削減速率皆介於 0.5 nm/sec 到 0.6 nm/sec，顯示此製程的穩定性，圖中並顯示所有削減速率 (All data) 的統計分佈結果，平均的削減速率為 0.549 nm/sec，且標準差為 0.065 nm/sec。

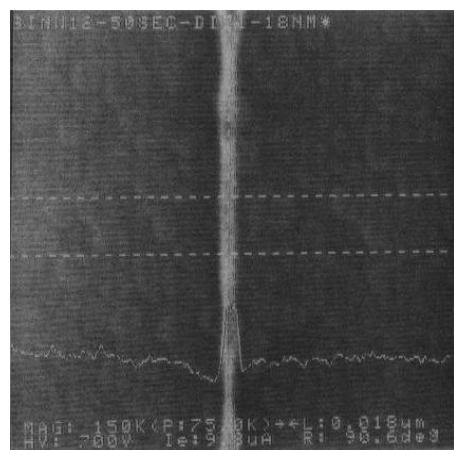

圖十一為原為 49 nm 的光阻線寬，經過削減時間為 50 sec 的條件，線上電子顯微鏡所拍出的削減過後的光阻線寬上視圖，其線寬為 18 nm 左右，且可以看出削減非常均勻。

### 五、結論

本計畫目前研究碳離子佈植方式對於 NiSi 金屬矽化物熱穩定性的影響，當 NiSi 金屬矽化物形成溫度小於或等於 700 °C 時，雖然碳原子存在於 NiSi 金屬矽化物中，會造成片電阻值上升，但其實片電阻值增加的幅度很小，對於 CIA samples 來說，片電阻值的增加幅度甚至小於  $1 \Omega/\square$ 。當有足夠多的碳原子存在於 NiSi 金屬矽化物中時，即碳離子植入的劑量高達  $5 \times 10^{15} \text{ cm}^{-2}$  時，能夠有效抑制 NiSi 金屬矽化物的結塊與晶相轉換現象，CIA samples 的碳植入條件為  $5 \times 10^{15} \text{ cm}^{-2}$  以及 40 keV 時，退火溫度高達 850 °C 時，甚至不會發生結塊與晶相轉換現象，故與對照組相比，能將 NiSi 金屬矽化物熱穩定性的溫度提升 150 °C。

在矽奈米線製作方面，目前能夠穩定地控制削減過後的光阻線寬大小，得到非常均勻的光阻奈米線圖案。

### 六、參考文獻

- [1]. Hiroshi Iwai, Tatsuya Ohguro, and Shun-ichiro Ohmi, “NiSi salicide technology for scaled CMOS,” Microelectronic Engineering., vol. 60, pp. 157-169, 2002.

- [2]. J. Kedzierski, P. Xuan, E. H. Anderson, J. Boker, T. J. King, and C. Hu, “F-enhanced morphological and thermal stability of NiSi films on  $\text{BF}_2^+$ -implanted Si(001),” Appl. Phys. Lett., vol. 81, pp. 5138-5140, 2002.

- [3]. P. S. Lee, K. L. Pey, D. Mangelinck, J. Ding, A. T. S. Wee, and L. Chan, “Improved NiSi Salicide Process Using Presilicide  $\text{N}_2^+$  Implant for MOSFETs,” IEEE Electron Device Letters, vol. 2, pp. 566-568, 2000.

- [4]. T. H. Hou, T. F. Lei, and T. S. Chao, “Improvement of junction leakage of nickel silicided junction by a Ti-capping layer,” IEEE Electron Device Letters, vol. 20, pp. 572-573, 1999.

- [5]. L. W. Cheng, S. L. Cheng, and L. J. Chena, “Formation of Ni silicides on (001) Si with a thin interposing Pt layer,” J. Vac. Sci. Technology, p.1176-1179, 2000.

- [6]. R. T. P. Lee, D. Z. Chi, M.Y. Lai, N. L. Yakovlev, and S. J. Chua, “Effects of Ti Incroporation in Ni on Silicidation Reaction and Structural/Electrical Properties of NiSi,” J. Electrochem. Soc, vol. 151, pp. 642-647, 2004.

- [7]. D. Mangelinck, J. Y. Dai, J. S. Pan, and S. K. Lahiri, “Enhancement of thermal stability of NiSi films on (100) Si and (111) Si by Pt addition ,” Appl. Phys. Lett., vol. 75, pp. 1736-1738, 1999.

- [8]. Shigeaki Zaima, Osamu Nakatsuka, Akira Sakai, Junichi Murota ,and Yukio Yasuda, “Interfacial reaction and electrical properties in Ni/Si and Ni/SiGe(C) contacts,” Applied Surface Science, vol. 224, pp. 215–221, 2004.

- [9]. B. Yu, L. Chang, S. Ahmed, H. Wang, S. Bell, C. Y. Yang, C. Tabery, C. Ho, Q. Xiang, T. J. King, J. Bokor, C. Hu, M. R. Lin, and D. Kyser, ”FinFET scaling to 10 nm gate length,” in IEDM Tech. Dig., pp.251-254, 2002.

- [10]. B. S. Doyle, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, A. Murthy, R. Rios, and R. Chau, “High Performance Fully-Depleted Tri-Gate CMOSTransistors,” IEEE Electron Device Lett., vol.24, No.4, pp.263-264, 2003.

- [11]. F. L. Yang, H. Y. Chen, F. C. Chen, C. C. Huang, C. Y. Chang, H. K. Chiu, C. C. Lee, C. C. Chen, H. T. Huang, C. J. Chen, H. J. Tao, Y. C. Yeo, M. S. Liang, and C. Hu, “25 nm CMOS Omega FETs,” in IEDM Tech. Dig., pp.255-258, 2002.

- [12]. J. T. Park, J. P. Colinge, and C. H. Diaz, “Pi-Gate SOI MOSFET,” IEEE Electron

Device Lett., vol.22, No.8, pp.405-408, 2001.

[13]. K. H. Yeo, S. D. Suk, M. Li, Y. Y. Yeoh, K. H. Cho, K. H. Hong, S. K. Yun, M. S. Lee, N. Cho, K. Lee, D. Hwang, B. Park, D. W. Kim, D. Park, and B. I. Ryu, "Gate-All-Around (GAA) Twin Silicon Nanowire MOSFET (TSNWFET) with 15nm Length Gate and 4 nm Radius Nanowires," in IEDM Tech. Dig., pp.539-542, 2006.

[14]. N. Singh, F. Y. Lim, W. W. Fang, S. C. Rustagi, L. K. Bera, A. Agarwal, C. H. Tung, K. M. Hoe, S. R. Omampuliyur, D. Tripathi1, A. O. Adeyeye1, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, "Ultra-Narrow Silicon Nanowire Gate-All-Around CMOS Devices: Impact of Diameter, Channel-Orientation and Low Temperature on Device Performance," in IEDM Tech. Dig., pp.547-550, 2006.

[15]. S. D. Suk, S. Y. Lee, S. M. Kim, E. J. Yoon, M. S. Kim, M. Li, C. W. Oh, K. H. Yeo, S. H. Kim, D. S. Shin, K. H. Lee, H. S. Park, J. N. Han, C. J. Park, J. B. Park, D. W. Kim, D. Park, and B.I. Ryu , "High performance 5 nm radius twin silicon nanowire MOSFET (TSNWFET): Fabrication on bulk Si wafer, characteristics, and reliability," in IEDM Tech. Dig., pp. 717, 2005.

[16]. Kazuya Asano, Yang-Kyu Choi, Tsu-Jae King, and Chen-ming Hu, "Patterning Sub-30-nm MOSFET Gate with I-Line Lithography," IEEE Transactions on Electron Devices, vol. 48, pp. 1004-1006, 2001.

表一 各碳離子佈植條件下，其 NiSi 金屬矽化物的結塊溫度與晶相轉換溫度的總整理。

| Spilt condition                 | Agglomeration | Phase transition |

|---------------------------------|---------------|------------------|

| 30keV,<br>1E15 cm <sup>-2</sup> | CIA           | 800 °C           |

|                                 | w/o CIA       | 800 °C           |

| 40keV,<br>1E15 cm <sup>-2</sup> | CIA           | 800 °C           |

|                                 | w/o CIA       | 800 °C           |

| 30keV,<br>5E15 cm <sup>-2</sup> | CIA           | 850 °C           |

|                                 | w/o CIA       | 850 °C           |

| 40keV,<br>5E15 cm <sup>-2</sup> | CIA           | >850 °C          |

|                                 | w/o CIA       | 850 °C           |

圖一 C-doped NiSi 的金屬矽化物試片的製作流程圖

圖二 不同碳植入條件的 CIA samples 與 w/o carbon ion implantation samples (對照組) 的片電阻值與退火溫度關係。

圖三 碳植入條件為  $1 \times 10^{15} \text{ cm}^{-2}$  以及 40 keV 的 CIA samples 的 XRD 圖。晶相轉換的溫度為 800 °C，可以從 XRD 圖看到  $\text{NiSi}_2$  晶相的繞射角。

圖四 碳植入條件為  $1 \times 10^{15} \text{ cm}^{-2}$  以及 40 keV 的 CIA samples 的 SEM 圖。 $\text{NiSi}$  金屬矽化物薄膜在 800 °C 的退火條件下有結塊現象產生。

圖五 碳植入條件為  $5 \times 10^{15} \text{ cm}^{-2}$  以及 40 keV 的 CIA samples 的 XRD 圖。即使退火溫度達到 850 °C，仍然沒有  $\text{NiSi}_2$  晶相產生。

圖六 碳植入條件為  $5 \times 10^{15} \text{ cm}^{-2}$  以及 40 keV 的 CIA samples 的 SEM 圖。即使退火溫度達到 850°C，仍然沒有 pin-holes 產生，代表  $\text{NiSi}$  金屬矽化物薄膜為連續，並沒有結塊情形發生。

圖七 不同碳植入條件的 w/o CIA samples 與 w/o carbon ion implantation samples (對照組) 的片電阻值與退火溫度關係。

圖八 碳植入條件為  $5 \times 10^{15} \text{ cm}^{-2}$  以及 30 keV 的 w/o CIA samples 的 XRD 圖。NiSi 金屬矽化物的晶相轉換的溫度發生在 850 °C。

圖九 碳植入條件為  $5 \times 10^{15} \text{ cm}^{-2}$  以及 30 keV 的 w/o CIA samples 的 SEM 圖。NiSi 金屬矽化物薄膜在 850 °C 有結塊情形產生。

圖十 不同削減時間 (30 sec~60 sec) 下，其削減速率 (ashing rate) 的統計分佈圖。

圖十一 原為 49 nm 的光阻線寬，經過削減時間為 50 sec 的條件，線上電子顯微鏡所拍出的削減過後的光阻線寬上視圖。