### 摘 要

本報告包含本三年期計畫之全部成果。內容分為兩個部分:碳摻雜技術與對 NiSi/Si 結構之影響、全包覆式多晶矽薄膜電晶體。

在碳掺雜技術方面,我們採用電漿浸潤技術、一般離子佈植技術、低能量/低溫離子佈植技術三種。過低的電漿浸潤能量會造成碳膜沈積,無法形成 NiSi,必須避免。三種技術的碳掺雜劑量達到 1x10<sup>15</sup> cm<sup>-2</sup>以上,都可以提高 NiSi 的熱穩定性達攝氏 50-100 度,但是如果同時有高劑量的 As, P, B 等掺雜,碳掺雜的作用則不明顯。低能量離子佈植技術可以形成品質最好的非晶矽層,搭配快速退火+雷射退火,可以得到最高的替代性碳濃度超過 1.1%,具實用價值。即使經過高溫退火,碳掺雜仍會增加矽基板的缺陷密度,Ni 可能藉由這些缺陷快速擴散,因此碳植入深度和接面深度必須適當搭配,以免接面漏電流增加。高劑量的碳掺雜可以微幅降低 NiSi/n-Si 的蕭基位障高度約 30meV,幅度不大,對於接觸電阻影響很小。

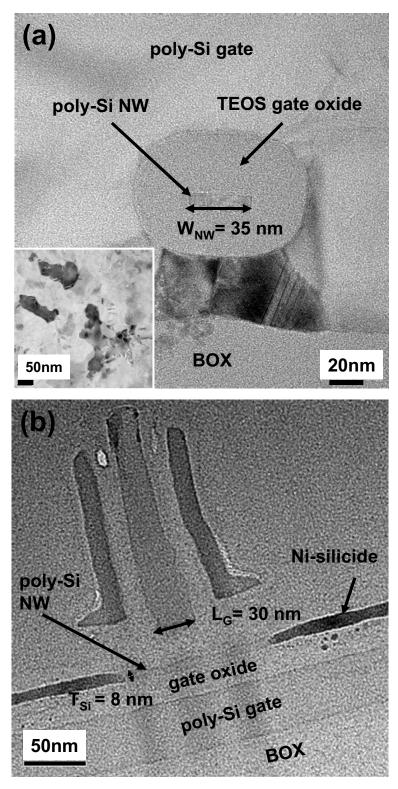

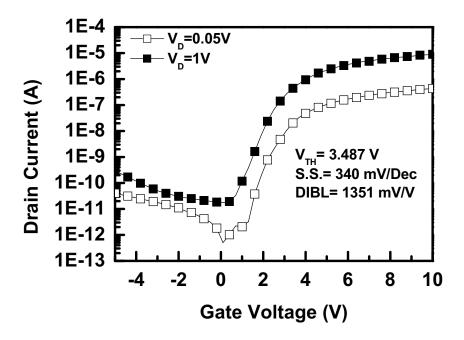

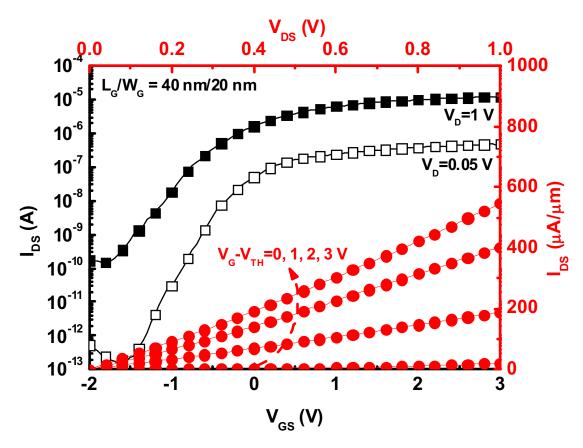

在全包覆式電晶體部分,以電子束微影、光阻消減、電漿蝕刻技術,製作通道 寬度、長度均小於 30nm 的電晶體,通道厚度減薄到 8nm,搭配全包覆式閘極結構,達 成全空乏型通道。再搭配修正蕭基位障接面技術,製作出通道長度 18nm 的世界最小的 薄膜電晶體。進一步搭配高介電常數介電質,將驅動電流推進到 500μA/μm 以上,接近 單晶矽電晶體,創下多晶矽薄膜電晶體的最大電流紀錄。

本計畫三年內有三名博士班研究生、六名碩士班研究生參與計畫執行。其中兩名博士生已經畢業,另一名預計一年內亦可獲得博士學位;六名碩士研究生中的四名已經獲得碩士學位。計畫成果已發表兩篇 SCI 期刊論文、五篇研討會論文,一篇期刊論文在審查中,另有一篇期刊論文、一篇研討會論文在撰寫中。以取得的數據,估計至少可以再發表 2-3 篇 SCI 期刊論文。

關鍵字:全包覆式電晶體、金屬矽化物、矽化鎳、碳摻雜、電漿浸潤。

#### **Abstract**

This final report summarizes all of the results of the 3-year project. This report is divided into two parts: effect of carbon incorporation techniques on the NiSi/Si structure and gate-all-around (GAA) poly-Si thin film transistor(TFT) technology.

In the part of carbon incorporation, plasma immersion ion implantation (PIII), conventional ion implantation, and low energy/low temperature ion implantation techniques were employed. Carbon film may be deposited on sample surface as the PIII energy is too low. In this case, the Ni/Si interaction will be blocked. All of the three techniques can raise the thermal stability of NiSi/Si by 50-100°C as the carbon dose is higher than  $1x10^{15}$  cm<sup>-2</sup>. However, with the high dose As, P, or B, this benefit disappears. The low energy ion implantation technique produces the highest quality surface amorphous layer among the three techniques. Low energy carbon ion implantation integrating with suitable rapid thermal annealing and laser annealing can obtain substitutional carbon concentration as high as 1.1%. This value is useful for strained Si application. Unfortunately, high dose carbon implantation produces many defects in Si substrate. These defects can not be fully removed after high temperature annealing. Ni atom may diffuse quickly via these defects and may results in higher p-n junction leakage current. The distribution of carbon and the junction depth should be designed carefully. High dose carbon incorporation may reduce the Schottky barrier height by 30meV on n-Si, which implies that the contact resistance will not be affected by carbon incorporation.

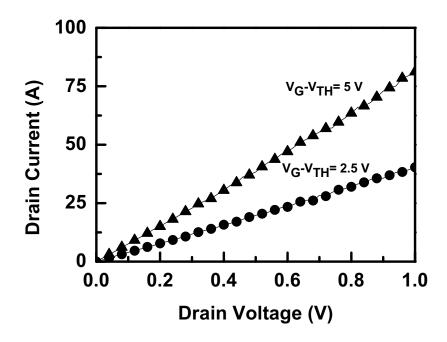

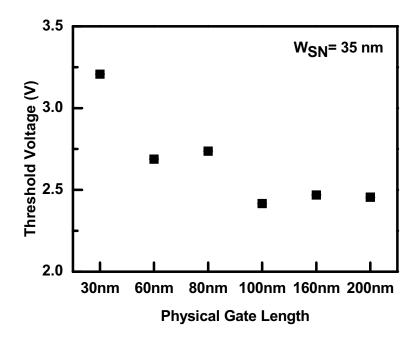

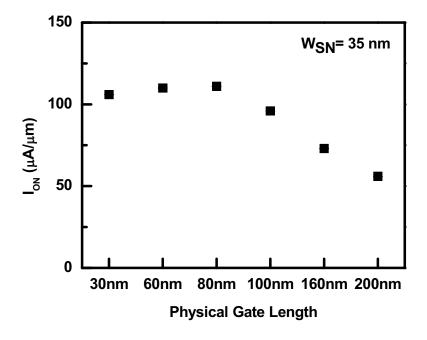

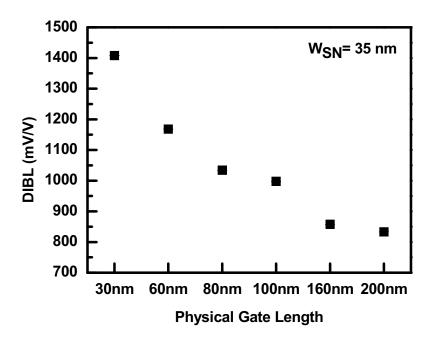

In the part of GAA TFT technology, e-beam lithography, photo-resist trimming, and plasma etching processes were developed to fabricate TFTs with channel length and channel with smaller than 30nm. Due to the 8-nm-thick ultra-thin active layer and the GAA gate structure, fully-depleted channel and good short channel effect is obtained. Integrating with the modified Schottky barrier source/drain junction, the record small TFT with 18-nm gate length is demonstrated. Using high dielectric constant dielectric to replace the  $SiO_2$  gate dielectric, the record high driving current of  $500 \,\mu\text{A}/\mu\text{m}$  is obtained. This driving capability is close to the conventional nMOSFET.

In the past three years, 3 Ph.D students and 6 graduate students involved this project. Among them, 2 of the 3 Ph.D student and 4 of the 6 graduate students have received their Ph.D and MS degrees, respectively. The other one Ph.D student is expected to receive his Ph. D degree in one year. Three undergraduate students have entered the MS program. Parts of the results have been published as 2 SCI journal papers and 5 conference papers. One SCI journal

is under revision. Recent results will be written as 2-3 SCI journal papers at least.

Key Words: gate-all-around transistor, metal silicide, NiSi, carbon incorporation, plasma immersion

## **Contents**

| Abstract – ( | ChineseI                                                       |

|--------------|----------------------------------------------------------------|

| Abstract – l | EnglishII                                                      |

| Contents     | IV                                                             |

| Part-I       |                                                                |

| Chapter 1.   | Effect of Carbon Plasma Immersion Ion Implantation on the      |

|              | Thermal Stability of Nickel Silicide Film1                     |

| Chapter 2.   | Effect of Carbon Ion Implantation on the Thermal Stability of  |

|              | Nickel Silicide Film                                           |

| Chapter 3.   | Impact of Carbon Ion Implantation on the Thermal Stability of  |

|              | Nickel Silicide Contacted Shallow Junction42                   |

| Chapter 4.   | Si-C Formation by Low Temperature Carbon Ion                   |

|              | Implantation63                                                 |

| Part-II      |                                                                |

| Chapter 5.   | Gate-All-Around Poly-Si Nano Wire Thin-Film                    |

|              | Transistor                                                     |

| Chapter 6.   | High Performance Poly-Si Nano Wire Thin Film Transistors using |

|              | the HfO <sub>2</sub> Gate Dielectric                           |

| Self-Evalua  | ntion110                                                       |

| Appendix     | Publications List in the Project111                            |

## Chapter 1

# Effect of Carbon Plasma Immersion Ion Implantation on the Thermal Stability of Nickel Silicide Film

#### 1.1 Introduction

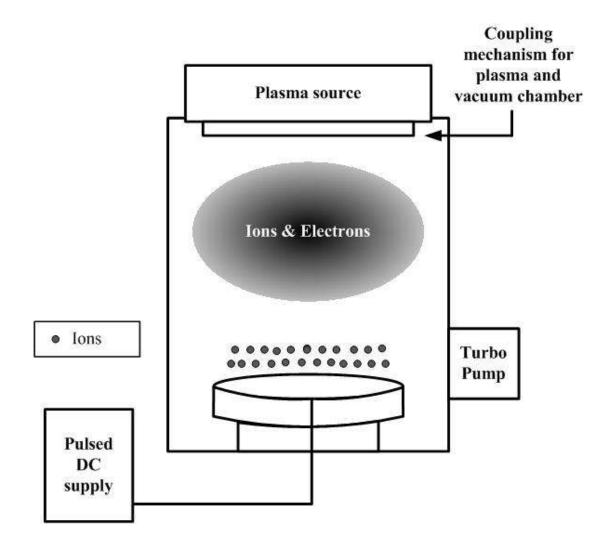

Plasma immersion ion implantation is a surface deposition technique, which applies high voltage pulsed DC or pure DC power to extract the accelerated ions from the plasma and targeting the ions into the wafer placed on the sample holder. Figure 1-1 is the schematic diagram of a PIII system, the holder is in a vacuum chamber which is connected to a high voltage power supply and insulated from the chamber wall. When the process begins, the substrate is applied with a negative bias, the electric field drives electrons away from the substrate and forms a Debye sheath layer. The Debye sheath layer contains only positive ion and no electrons in it. The biased substrate will accelerate the ions in the Debye sheath layer and implant the ions into the wafer on the holder.

The benefit of PIII process is that the implantation energy is controlled by the voltage of the pulsed DC signal, so the dopants can be implanted into the shallow region of the object surface by very low implantation energy. And because the object is totally immersed in the plasma, so PIII can implant high density of dopants into the wafer in a relatively short time compare to traditional ion implanter. In that way, the throughput of implantation process can be increase.

Several applications of PIII have been implemented by researchers. Using nitrogen PIII process to improve the surface property of stainless steel is one of the applications. By performing NPIII process, the surface hardness of stainless steel can be improved [1, 2]. Another important application is performing oxygen PIII on the metallic biomaterials which are used on medical purposes such as osteosynthesis plates used in jaw or skull surgery. After OPIII treatment, the biocompatibility of the biomaterials will be improved [3-7]. Diamond like carbon (DLC) film forming is another application of PIII [9-10]. The DLC film has a high hardness and Young's modulous, a good wear and abrasion resistance and a low friction coefficient. So it can be used in semi-conducting, biomedical, automotive and aerospace industries. And PIII is a promising way of efficiently forming DLC film on object's surface.

PIII has several applications on semiconductor device fabrication. First, because PIII can

do low energy ion implantation, it can be used on ultra-shallow junction fabrication. In the research of C.A. Pico et al., PMOS is successfully fabricated by using BPIII process [11]. PIII is also used on sidewall doping of trench structure [12]. Since PIII has immersion type doping characteristic, the sidewall doping of high aspect ratio trench structure is easier by using PIII. Nitrogen PIII can use on suppressing thermal hillock formation in aluminum metallization [13], or improve the electrical characteristics of high-k gated MOS devices [14].

In this chapter, we use PIII as carbon ion implantation source. First, we discuss the basic characteristic of the CPIII silicon substrate. Then the thermal stability improvement of CPIII on the NiSi/Si structure is discussed, both without As doping and with As doping samples are included.

#### 1.2 Experimental Procedure

#### A. Carbon Plasma Immersion Ion Implantation (CPIII)

The PIII system used in this project consists of process chamber, electrical power system, vacuum system, and gas providing system. Fig.1-2 shows the whole PIII equipment. The process chamber is a chamber with sample chuck at the bottom and an antenna to light the plasma on. A valve control panel is linked to the chamber to control all the valves linked to the process chamber. Fig.1-3 shows the control panel of the valves. Fig.1-4 and Fig.1-5 show the electrical power system, it includes a DC power supply and a DC pulse signal source. The vacuum system includes two pumps and one pressure meter. One pump is for the first step vacuum to make the pressure down from air pressure, the other pump is a turbo pump which can make the chamber pressure down to  $10^{-6}$  torr. The gas providing system includes CH<sub>4</sub> gas source and a gas flow meter.

At the beginning of the process, we put the wafer on the sample chuck. Then we use the vacuum system to make the chamber pressure down to  $10^{-5}$  torr. After the process pressure reached, CH<sub>4</sub> gas is pour into the process chamber with a flow rate of 50 sccm. DC power supply is turned on to light on the plasma with a value of 150V. In the final step, DC pulse signal is applied to the chuck and the carbon ions are implanted into the silicon substrate, the process pressure is about  $1.2 \times 10^{-3}$  torr.

#### B. Sample Preparation

Six-inch-diameter p-type (100) silicon wafers with nominal resistivity of 15 $\sim$ 25  $\Omega$ -cm were used as substrates. The PIII was performed at 3 keV and 5 keV, and the implantation

time is 1 min and 5 min. The samples are labeled in the form of xKyM, where the xK indicates the implantation energy is at x keV and the yM indicates the plasma immersion time is y min. After PIII, the 3K5M and 5K5M samples accepted additional arsenic ion implantation at 30 keV to a dose of  $5\times10^{15}$  cm<sup>-2</sup>. Then, all samples were dipped in diluted HF solution with (H<sub>2</sub>O: HF = 50:1) to remove the native oxide on sample surface. A 10-nm-thick Ni film was deposited by an E-gun system. The process pressure is  $6\times10^{-7}$  torr and the Ni deposition rate is 0.5A/sec. After Ni deposition, samples were cut into small pieces and were annealed in N<sub>2</sub> ambient by a rapid thermal annealing (RTA) system at temperatures ranging from 500 °C to 900 °C for 30seconds. The unreacted Ni was selectively etched by a mixture of  $H_2$ SO<sub>4</sub>:  $H_2$ O<sub>2</sub>=3:1.

#### C. Material Analysis

Several Material Analysis techniques include XRD \ SEM \ SIMS and TEM were used in our experiment. Electrical measurement of sheet resistance was performed, too.

XRD analysis is used to find out the nickel silicide phase transformation temperature. Scanning Electron Microscope (SEM) is used to inspect the surface morphology of the carbon implanted nickel silicide samples after annealing at different conditions. The surface continuity and the level of agglomeration can be observed by SEM inspection. Secondary Ion Mass Spectrometry (SIMS) is used to analysis the depth profiles of carbon and phosphorus atoms in samples after ion implantation and annealing. Transmission Electron Microscopy (TEM) is used to observe the microstructure of samples. It can help to figure out the thickness of amorphous layer and the level of amorphization.

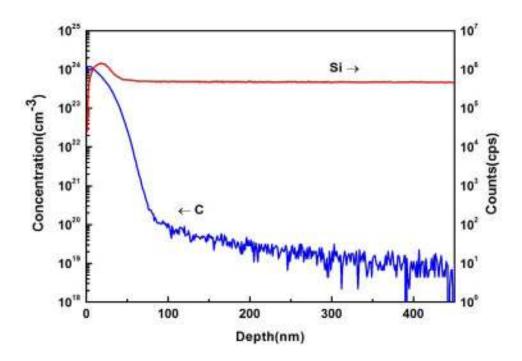

#### 1.3 Basic Material Analyses of CPIII on Si Substrate

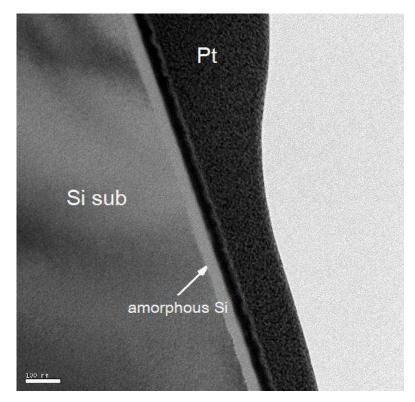

TEM was used to analyze the surface condition of the implanted silicon surface and SIMS was used to measure the depth profile of the carbon distribution after carbon plasma immersion ion implantation. Fig.1-6 and Fig.1-7 shows the SIMS result of the carbon implanted silicon substrate, we can find that if the implantation time is 15 minutes, the effective carbon dose could achieve  $1.52 \times 10^{18} \text{cm}^{-2}$  and most of the implanted carbons are located in the top 50 nm from the surface of the substrate. When the implantation time decreases to 5 minutes, the effective carbon dose is  $2.515 \times 10^{16} \text{cm}^{-2}$  and the implanted carbons are mostly located at the region which is near the surface. Fig.1-8 is the TEM result of 3K5M

CPIII sample, we can see that there is a 32nm thick amorphous layer on the surface of silicon substrate.

Since too many carbon implanted into silicon will deactivate other dopants and increase the interface contact resistance [15]. The suitable carbon dose in the silicon substrate should be between  $1\times10^{15}$  cm<sup>-2</sup> and  $1\times10^{16}$  cm<sup>-2</sup>. Base on all the experimental data, the carbon implantation time will be controlled less than 5 minutes in the following experiments, which is expected to produce better experimental results.

#### 1.4 Impact of CPIII on NiSi/Si Structure

In this section, thermal stability of the NiSi/Si structure after performing carbon PIII process is examined. First, the thermal stability of the pure NiSi/Si structure is discussed and used as reference, then the thermal stability of the carbon PIII NiSi/Si structure is discussed. Both NiSi/Si structure with N<sup>+</sup> doping and without N<sup>+</sup> doing are included.

#### A. Pure NiSi/Si Structure

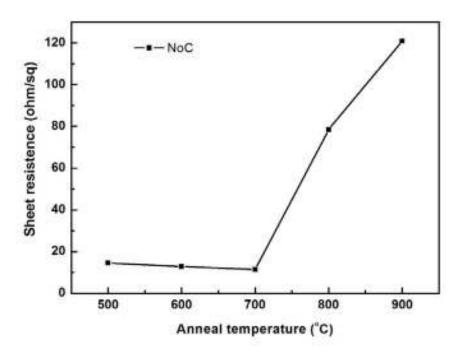

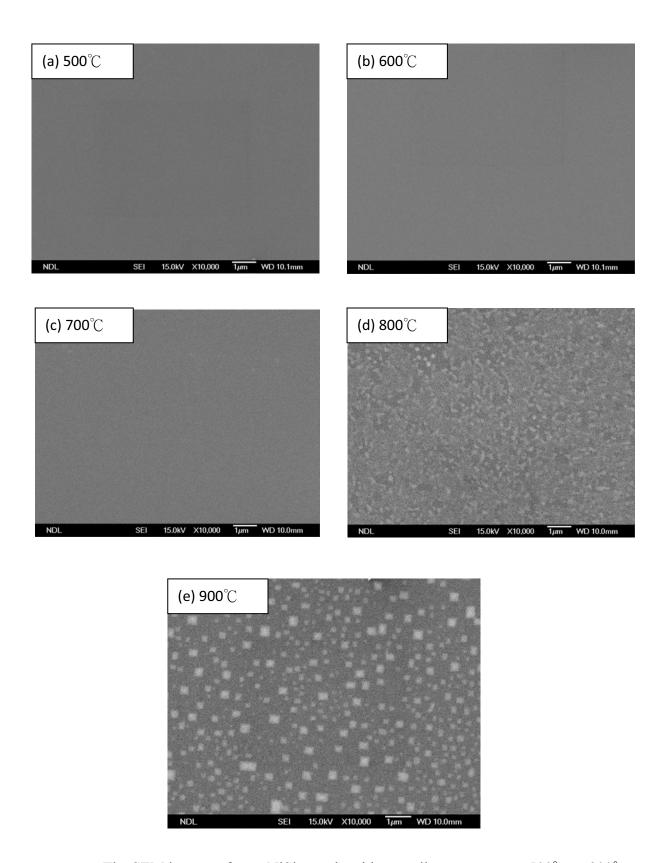

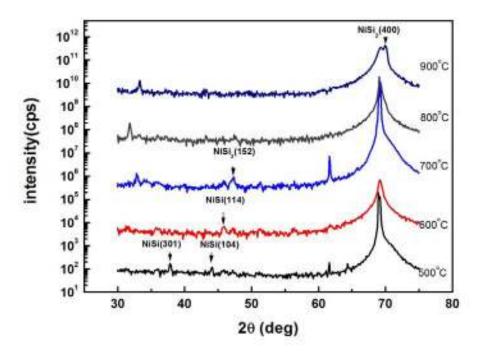

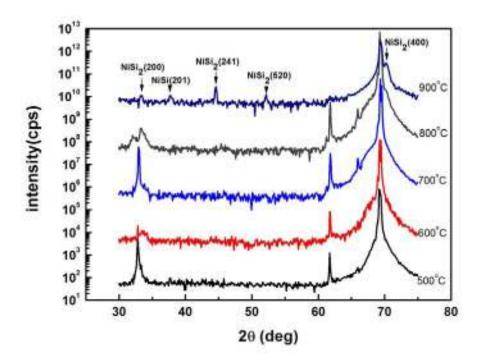

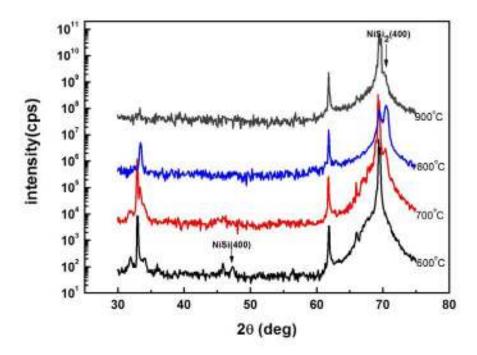

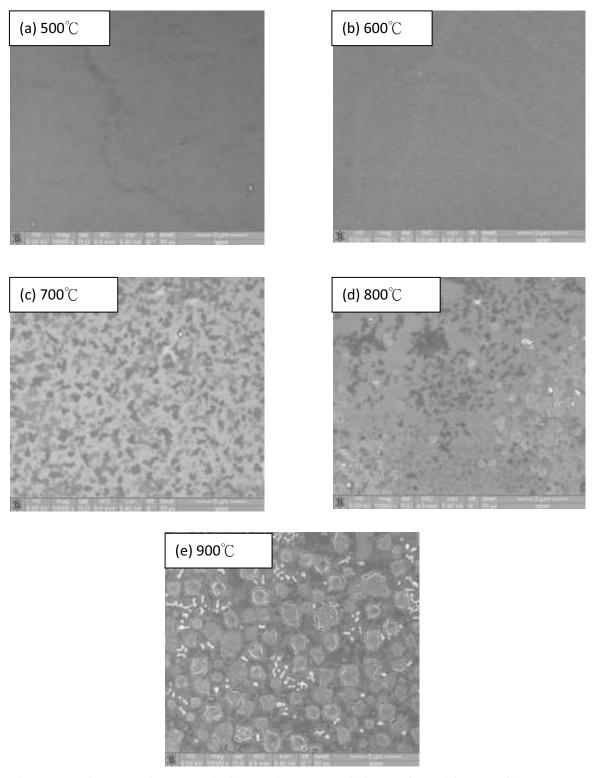

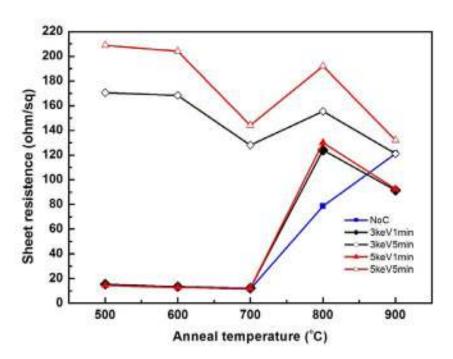

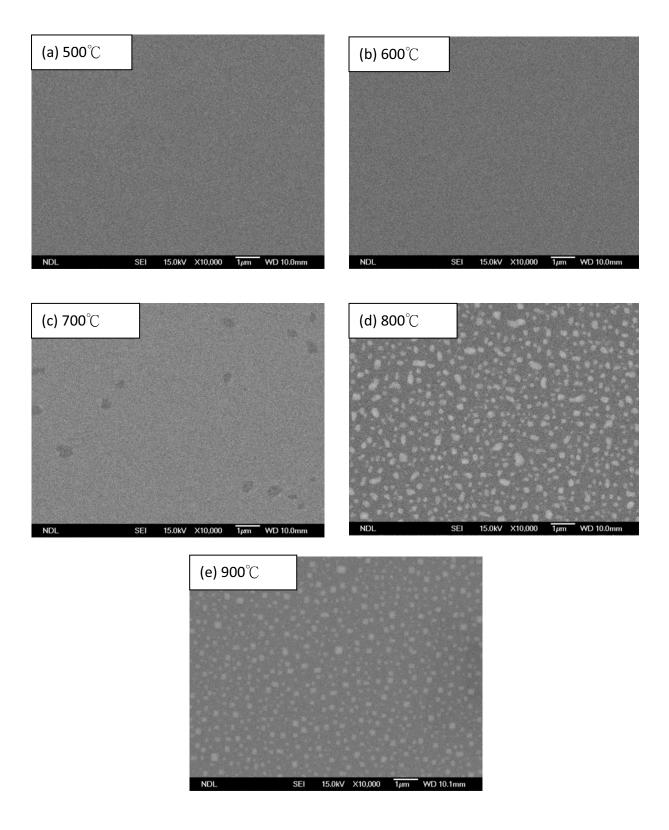

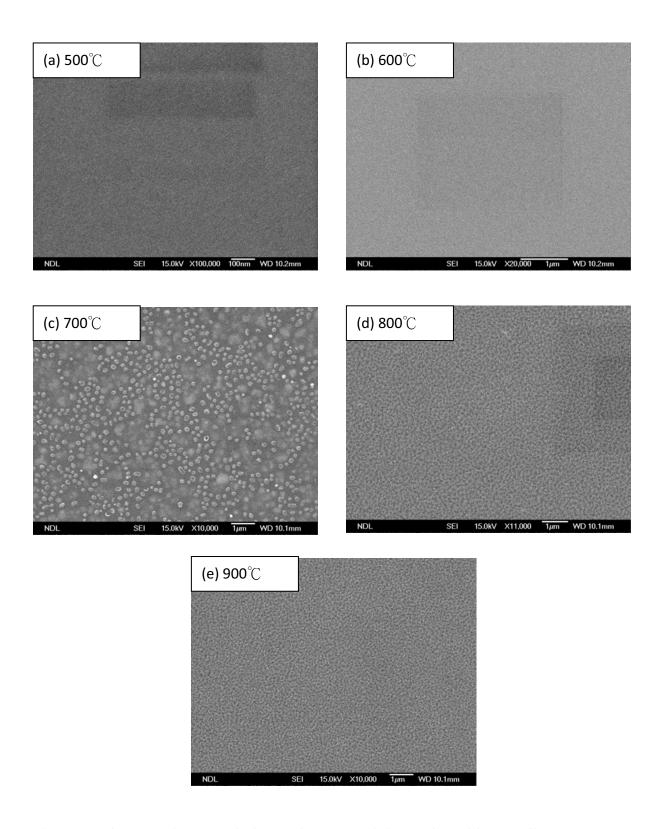

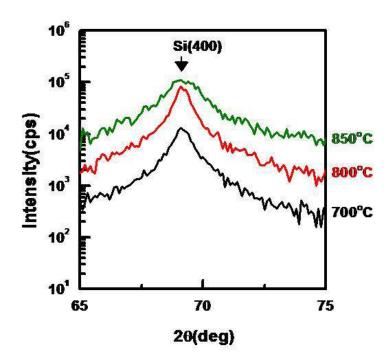

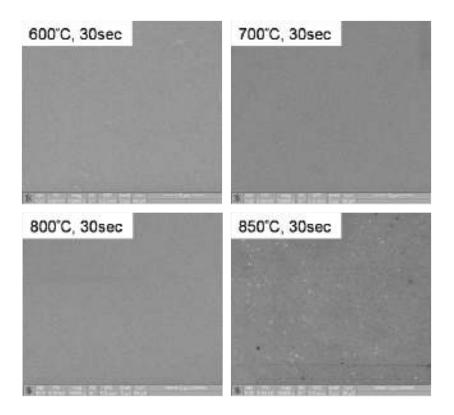

From the sheet resistance value of the samples shown in Fig.1-9, the resistance value of NiSi is very stable when the annealing temperature is lower than 700°C. This indicates that agglomeration and phase transformation do not occur when the annealing temperature is not higher than 700°C. From the SEM images in Fig.1-10(a) ~Fig.1-10(c), it is also found that the surface of the sample is smooth when the annealing temperature is not higher than 700°C. This indicates that agglomeration does not occur. As the annealing temperature increases to 800°C, the sheet resistance increases obviously. This result indicates that agglomeration and/or phase transformation occurs. From the SEM image shown in Fig.3-10(d), it is observed that the nickel silicide surface agglomerates and some holes appear. From the XRD spectra shown in Fig.3-11, it is observed that the phase of nickel silicide transforms from NiSi to NiSi<sub>2</sub> when the annealing temperature increases to 900°C. Fig.3-10(e) shows that the agglomeration is very sever, there is no continuous nickel silicide film on the surface.

In summary, pure NiSi can form stable nickel silicide thin film when the annealing temperature is not higher than 700°C. Agglomeration and phase transformation occur at temperatures higher than 800°C.

#### B. CPIII NiSi/Si Structure without Arsenic Doping

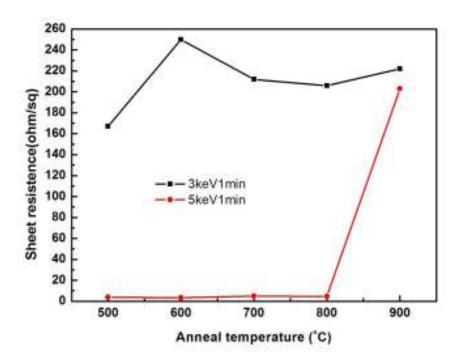

Fig.1-12 shows the sheet resistance values of the 3K1M and 5K1M CPIII samples after

annealing at various temperatures. It is surprised that the sheet resistance values of the 3K1M CPIII samples are all higher than  $160\Omega/\Box$  in the whole annealing temperature range from  $500^{\circ}$ C to  $900^{\circ}$ C. On the contrary, the 5K1M samples exhibits better thermal stability than the reference samples shown in the previous sub-section, i.e. the non-carbon implanted samples.

Fig.1-13 shows the XRD spectra of the 3K1M samples. There is no nickel silicide formed in the temperature range from 500°C to 700°C. As temperature increased to 800°C and 900°C, evident peaks with respect to NiSi<sub>2</sub> phase are observed. But, in Fig.1-14, SEM inspection observed that when the annealing temperature increases to 800°C and 900°C, the surface agglomerates severely. Since the NiSi<sub>2</sub> is totally not continuous, the sheet resistance value is very high.

Fig.1-15 shows the surface morphology of the 5K1M CPIII samples inspected by SEM. Even when the annealing temperature increases to 800°C, the surface agglomeration is very slight. Only a few pin holes occur on the surface and the nickel silicide film is continuous. The XRD spectra of the 5K1M samples are shown in Fig.1-16. The NiSi<sub>2</sub> phase observed on the 700°C annealed sample indicates that means phase transformation occurs. As annealing temperature increased to 900°C, the sheet resistance increased to a very high value. From the SEM micrograph, we can see the surface agglomeration is very severe which results in the high sheet resistance.

#### C. CPIII NiSi/Si Structure with Arsenic Doping

The effect of As doping on the thermal stability of the CPIII NiSi/Si structure is evaluated. After CPIII, all samples accepted additional  $\mathrm{As}^+$  ion implantation at 30keV to a dose of  $5\times10^{15}$  cm<sup>-2</sup>. Sheet resistance measurement  $\cdot$  XRD and SEM were done to analysis the thermal stability.

Fig.1-17 shows the sheet resistance results of the 3K1M, 3K5M, 5K1M, and 5K5M CPIII samples. It is found that the 3K1M CPIII sample has stably low sheet resistance around  $12\Omega/\Box$  to  $15\Omega/\Box$  when the annealing temperature is in the range of 500°C to 700°C. As the annealing temperature increases to  $800^{\circ}$ C, the sheet resistance increased to  $124 \Omega/\Box$ . This means that agglomeration occurs. When the annealing temperature further increases to  $900^{\circ}$ C, the sheet resistance is  $92.08\Omega/\Box$ , which is lower than the value of the  $800^{\circ}$ C annealed sample. The cause of this phenomenon may be explained as followed. The nickel silicide phase transformation speed is slower when annealing temperature is  $800^{\circ}$ C, the nickel silicide film

partly agglomerates before phase transformation, so the sheet resistance is high. When the annealing temperature increases to 900°C, the phase transformation speed is higher. NiSi phase can transform to NiSi<sub>2</sub> phase before severe agglomeration occurs, so the extent of agglomeration is slighter than that on the 800°C annealed sample, and the sheet resistance is lower. The SEM micrographs shown in Fig.1-18 proofs the agglomeration on the 800°C annealed sample is more severe than that on the 900°C annealed sample. This observation confirms previous hypothesis.

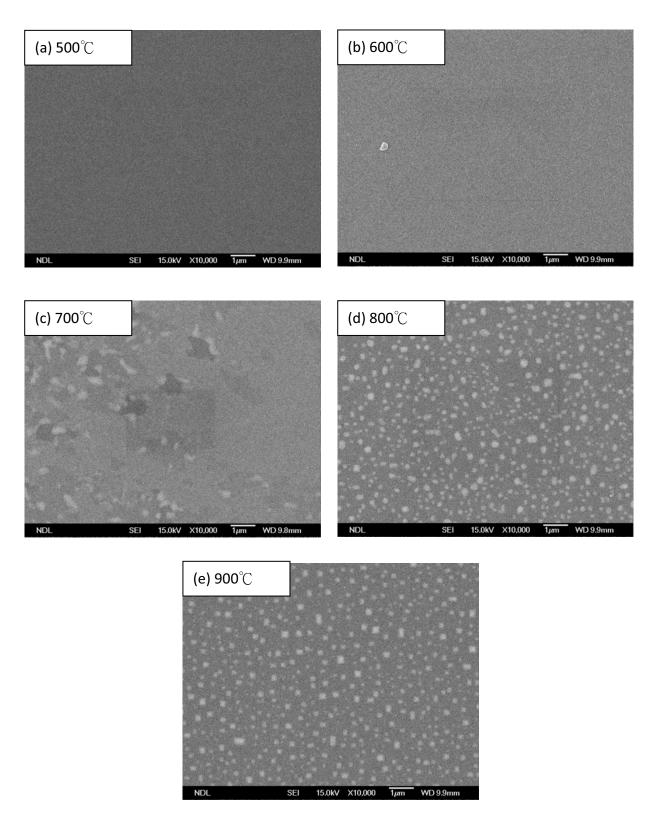

The sheet resistance results of the 5K1M CPIII sample are similar to the results of the 3K1M CPIII sample. That means the agglomeration and phase transform on the samples are similar. The surface morphology of the 3K1M and 5K1M CPIII samples inspected by SEM are shown in Fig.1-18 and Fig.1-19, respectively. It is observed that both 3K1M and 5K1M samples has very smooth surface without agglomeration when the annealing temperature is 500°C and 600°C. This observation matches with the sheet resistance results. As the annealing temperature increases to 700°C, both 3K1M and 5K1M samples reveal pin holes on part of the surface. Since most part of the surface is still continuous, the sheet resistance does not change significantly. From the SEM micrographs shown in Fig.1-18 and Fig.1-19, the surface morphologies of the 3K1M and 5K1M samples are very similar at every annealing temperatures, this result is consistent with the sheet resistance result.

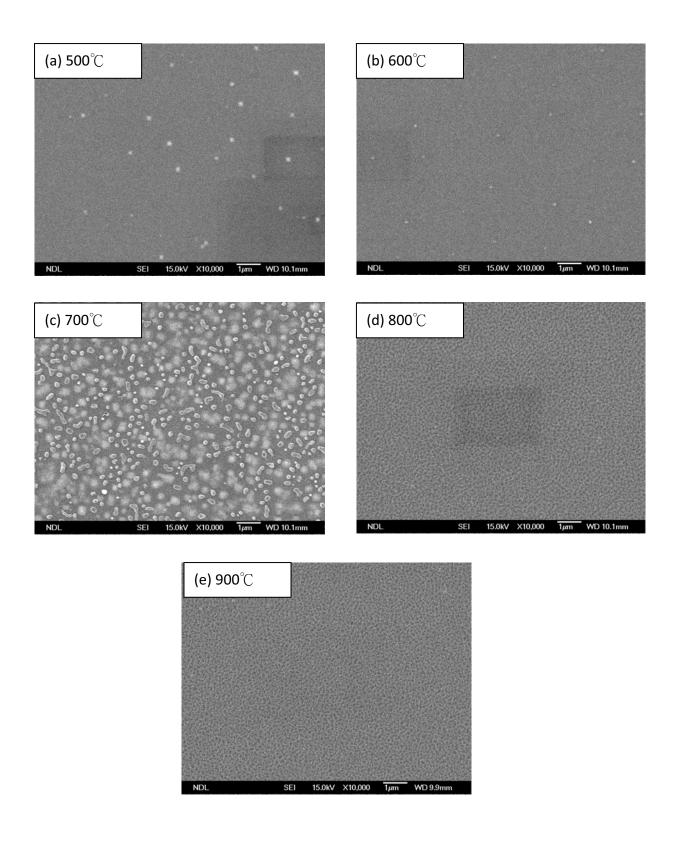

The sheet resistance values of the 3K5M and 5K5M PIII samples are very different from the 1 minute CPIII samples. When the annealing temperature is  $500^{\circ}$ C and  $600^{\circ}$ C, the sheet resistance values of both 3K5M and 5K5M samples are between  $160 \Omega/\square$  and  $200 \Omega/\square$ . The surface morphologies of both samples are shown in Fig.1-20 and Fig.1-21. It is observed that the surface of both samples were smooth, which implies that the high sheet resistance value is not due to agglomeration. The XRD analysis reveals that there's no nickel silicide formed on sample surface when the annealing temperature is  $500^{\circ}$ C and  $600^{\circ}$ C, as shown in Fig.1-22. As the annealing temperature increases to  $700^{\circ}$ C, NiSi<sub>2</sub> forms so the sheet resistance decreases. However, the SEM images shown in Fig.1-20 and Fig.1-21 show that the silicide film significantly agglomerates when the annealing temperature increases to  $700^{\circ}$ C, so the sheet resistance is still around  $130\Omega/\square$ . In the  $800^{\circ}$ C annealing case, the agglomeration is severer, so the sheet resistance further increases. When the annealing temperature increases to  $900^{\circ}$ C, because the phase transform speed increases as mentioned before, the agglomeration is slighter than the  $800^{\circ}$ C annealed sample, so the sheet resistance is lower.

The experimental results of the CPIII NiSi/Si structure are summarized as follows. In the

CPIII process, CH<sub>4</sub> plasma was used as implantation source. The CH<sub>4</sub> plasma contains some low energy (< 100eV) radicals, those radicals deposited on the surface and formed a carbon thin film. This carbon film will affect the forming of nickel silicide. In addition, the DC pulse signal was not a perfect square wave. In the rise time and fall time regions, the voltage changed with time and created some low energy ions. If the energy of ions is lower than 100eV, the ions might pile up on the surface and form a carbon film [16]. In the TEM micrograph shown in Fig.1-8, no carbon film is seen clearly because the carbon atom density on the surface is near the silicon atom density as the SIMS result shows (Fig.1-6 and Fig.1-7). The contrast between silicon substrate and carbon film is very close, so the carbon film could not be clearly identified. On the samples without arsenic doping, when the annealing temperature is between 500°C to 700°C, nickel silicide couldn't form on the 3K1M CPIII sample because of the existence of the carbon film. Until the annealing temperature increased to 800°C, the nickel silicide could form. The 5K1M CPIII samples have thinner carbon film on the surface because the carbon implantation energy was higher, and the nickel silicide formation was not affected. On the samples with arsenic doping, since the 3K1M and 5K1M CPIII samples has thinner carbon film, the high energy arsenic doping could remove or destroy the surface carbon film. In this case, NiSi could form on the surface when the annealing temperature is as low as 500°C. The 3K5M and 5K5M CPIII samples have thicker carbon film because the process time is longer. For that reason, arsenic doping could not remove all the carbon film and the nickel silicide could not form on the surface when the annealing temperature is between 500°C and 600°C. However, arsenic doping still reduce the carbon film thickness, and NiSi<sub>2</sub> could form when the annealing temperature is 700°C.

It is also observed that the thermal stability of the CPIII NiSi/Si structure is better than that of the pure NiSi/Si structure. The agglomeration temperature increased to 800°C and the phase transform temperature is between 700°C and 800°C. However, after arsenic doping, the thermal stability of the CPIII NiSi degrades. The agglomeration temperature reduces to 700°C and the phase transform temperature is lower than 800°C. The cause of this effect is the doped arsenic. Since arsenic atom is bigger than silicon, after implanted into silicon substrate, arsenic will change the interfacial energy between nickel silicide and silicon. High energy implanted arsenic will also interact with silicon and nickel in the nickel silicide, the nickel will diffuse to the substrate and the silicon may form SiO<sub>2</sub> with the residual oxygen in the annealing environment. All the effects will lower the nickel silicide thermal stability [17].

#### 1.5 Conclusions

Carbon plasma immersion ion implantation can implant large amount of carbon into silicon substrate in a short time. The SIMS depth profile indicates that the effective dose after 15minutes CPIII process can achieve  $1.52\times10^{18}$  cm<sup>-2</sup> and most of the implanted carbons are located in the top 50 nm from the surface of the substrate. From the TEM image we can find there's no evident amorphous layer on the surface. We perform CPIII on N<sup>+</sup>P junction structure at energy  $3\text{keV} \cdot 5\text{keV}$  for 1minute  $\cdot$  5minutes, and we find the CPIII process would not increase junction leakage because implanted carbon can repair the secondary defects caused by ion implantation by capturing Si interstitials, and further reduce the leakage current brought by secondary defects. As CPIII applied to NiSi/Si structure without arsenic doping, we find 5K1M CPIII process can improve the agglomeration temperature to  $800^{\circ}\text{C}$ . In the case of arsenic doped NiSi/Si structure, we find CPIII could not increase NiSi thermal stability because arsenic atom will change the interfacial energy between nickel silicide and silicon.

#### References

- [1] J. H. Liang, C. S. Wang, W. F. Tsai, C. F. Ai, "Parametric study of nitrided AISI 304 austenite stainless steel prepared by plasma immersion ion implantation," *Surface and Coatings Technol.*, Vol. 201, Issue. 15, pp. 6638-6642 23 April 2007.

- [2] X. B. Tian, Z. M. Zeng, T. Zhang, B. Y. Tang, P. K. Chu, "Medium -temperature plasma immersion-ion implantation of austenitic stainless steel," *Thin Solid Films*, Vol. 366, Issue 1-2, pp. 150-154, 1 May 2000.

- [3] P. K. Chu, B. Y. Tang, L. P. Wang, X. F. Wang, S. Y. Wang, and N. Huang, "Third-generation plasma immersion ion implanter for biomedical materials and research," *Review of Scientific Instruments*, Vol. 72, No. 3, pp. 1660-1665, March 2001.

- [4] S. Mändl, R. Sader, G. Thorwarth, D. Krause, H. -F. Zeilhofer, H. H. Horch, B. Rauschenbach, "Investigation on plasma immersion ion implantation treated medical implants," *Biomolecular Engineering*, Vol. 19, Issues 2-6, pp. 129-132, August 2002.

- [5] F. Berberich, W. Matz, U. Kreissig, E. Richter, N. Schell and W. Möller, "Structural characterisation of hardening of Ti–Al–V alloys after nitridation by plasma immersion ion implantation," *Applied Surface Science*, Vol. 179, Issues 1-4, pp. 13-19, 16 July 2001.

- [6] S. Mändl, D. Krause, G. Thorwarth, R. Sader, F. Zeilhofer, H. H. Horch, B. Rauschenbach, "Plasma immersion ion implantation treatment of medical implants," *Surface and Coatings Technol.*, Vol. 142-144, pp. 1046-1050, July 2001.

- [7] [34] N. Huang, P. Yang, Y.X. Leng, J. Wang, H. Sun, J. Y. Chen, G. J. Wan, "Surface modification of biomaterials by plasma immersion ion implantation," *Surface and Coatings Technol.*, Vol. 186, Issues 1-2, pp. 218-226, 2 August 2004.

- [8] Kuan-Wei Chen, Jen-Fin Lin, Wen-Fa Tsai, Chi-Fong Ai, "Plasma immersion ion implantation induced improvements of mechanical properties, wear resistance, and

- adhesion of diamond-like carbon films deposited on tool steel," *Surface and Coatings Technol.*, Vol. 204, Issue 3, pp. 229-236, 25 October 2009.

- [9] J. Y. Chen, L. P. Wang, K. Y. Fu, N. Huang, Y. Leng, Y. X. Leng, P. Yang, J. Wang, G. J. Wan, H. Sun, X. B. Tian, P. K. Chu, "Blood compatibility and sp<sup>3</sup>/sp<sup>2</sup> contents of diamond-like carbon (DLC) synthesized by plasma immersion ion implantation-deposition," *Surface and Coatings Technol.*, Vol. 156, Issues 1-3, pp. 289-294, 1 July 2002.

- [10] G. Thorwarth, C. Hammerl, M. Kuhn, W. Assmann, B. Schey, B. Stritzker, "Investigation of DLC synthesized by plasma immersion ion implantation and deposition," *Surface and Coatings Technology*, Vol. 193, Issues 1-3, pp. 206-212, 1 April 2005.

- [11] Carey. A. Pico, Michael. A. Lieberman and Nathan. W. Cheung, "PMOS integrated circuit fabrication using BF<sub>3</sub> plasma immersion ion implantation," *Journal of Electronic Materials*, Vol. 21, No. 1, pp. 75-79, January 1992.

- [12] X. Y. Qian, N.W. Cheung, M.A. Lieberman, R. Brennan, M.I. Current, and N. Jha, "Conformal implantation for trench doping with plasma immersion ion implantation," *Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms*, Vol. 55, Issues 1-4, pp. 898-901, 2 April 1991.

- [13] C.A. Pico, J. Tao, R.A. Stewart, M.A: Lieberman and N.W. Cheung, "The effects of plasma immersion ion implantation on thermal hillock formation," *Mater. Res. Soc. Proc.*, Vol. 225, 1991.

- [14] C. H. Fu, K. S. Chang-Liao, H. C. Chuang, T. K. Wang, S. F. Huang, W. F. Tsai, and C. F. Ai, "Effects of Nitrogen Incorporation by Plasma Immersion Ion Implantation on Electrical Characteristics of High-K Gated MOS Devices," *IEEE International Semiconductor Device Research Symp.*, 2007, pp. 1-2.

- [15] D. Christoph Mueller, and Wolfgang Fichtner, "Codoping as a measure against donor

- deactivation in Si: Ab initio calculations," Phys. Rev., Vol. 73, Issue 3, pp. 035210~1-035210~8, January 2006.

- [16] Zhenghua An, Ricky K.Y. Fu, Peng Chen, Weili Liu, Paul K. Chu, Chenglu Lin, "Fabrication of silicon carbide thin films by plasma immersion ion implantation with self-ignited glow discharge," Thin Solid Films, Vol. 447-448, pp. 153-157, 30 January 2004.

- [17] Jang-Gn Yun, Hee-Hwan Ji, Soon-Young Oh, Mi-Suk Bae, Hun-Jin Lee, Bin -Feng Huang, Yong-Goo Kim, Jin-Suk Wang, Nak-Gyun Sung, Sang-Bum Hu, Jeong-Gun Lee, Seong-Hyung Park, Hee-Seung Lee, Won-Joon Ho, Dae-Byung Kim, and Hi-Deok Lee, "Abnormal Oxidation of NiSi Formed on Arsenic-Doped Substrate," Electrochem. Solid-State Lett., Vol. 7, Issue 4, pp. G83-G85, 13 February 2004.

Fig.1-1. The schematic diagram of PIII system.

Fig.1-2. The process environment and equipment of PIII.

Fig.1-3. The control panel of process chamber valves

Fig.1-4. The DC power supply of electrical power system

Fig.1-5. The DC high voltage power supply of electrical power system

Fig.1-6. SIMS depth profile after CPIII process (10keV/15min)

Fig.1-7. SIMS depth profile after CPIII process (3keV/5min)

Fig.1-8. The TEM image of 3keV/5min CPIII sample

Fig.1-9. The sheet resistance value of pure NiSi sample with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs.

Fig.1-10. The SEM images of pure NiSi sample with annealing temperature  $500^{\circ}\text{C}$  to  $900^{\circ}\text{C}$ , annealing time 30secs.

Fig.1-11. The XRD patterns of pure NiSi sample with annealing temperature 500°C to 900°C, annealing time 30secs.

Fig.1-12. The sheet resistance value of 3keV1min and 5keV1min CPIII samples with annealing temperature 500°C to 900°C, annealing time 30secs. (No As)

Fig.1-13. The XRD patterns of 3keV1min CPIII NiSi samples with annealing temperature 500°C to 900°C, annealing time 30secs. (No As)

Fig.1-14. The XRD patterns of 5keV1min CPIII NiSi samples with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs. (No As)

Fig.1-15. The SEM images of 3keV1min CPIII NiSi samples with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs. (No As)

Fig.1-16. The SEM images of 3keV1min CPIII NiSi samples with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs. (No As)

Fig.1-17. The sheet resistance value of implant energy 3keV and 5keV implant time 1min and 5mins CPIII and pure NiSi samples with annealing temperature 500°C to 900°C, annealing time 30secs. (with As)

Fig.1-18. The SEM images of 3keV1min CPIII NiSi samples with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs. (With As)

Fig.1-19. The SEM images of 5keV1min CPIII NiSi samples with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs. (With As)

Fig.1-20. The SEM images of 3keV5min CPIII NiSi samples with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs. (With As)

Fig.1-21. The SEM images of 5keV5min CPIII NiSi samples with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs. (With As)

Fig.1-22. The XRD patterns of 5keV5min CPIII NiSi samples with annealing temperature  $500^{\circ}$ C to  $900^{\circ}$ C, annealing time 30secs. (With As)

## Chapter 2

## Effect of Carbon Ion Implantation on the Thermal Stability of Nickel Silicide Film

#### 2.1 Introduction

NiSi has been used as source/drain (S/D) contact material of sub-100 nm MOSFETs technology because of its several advantages including low resistivity, low contact resistivity, low temperature process, less Si consumption during silicide formation, and no narrow line effect and bridging failure [1]. For further scale-down, one of the main issues of NiSi is its poor thermal stability. It has been known that NiSi film agglomerates at 700 °C and transforms into NiSi<sub>2</sub> at 750 °C. These factors result in an increasing sheet resistance of nickel silicide and poor morphology, and then degrade device performance. Consequently, raising the thermal stability of NiSi is very important. Many different solutions have been proposed by several authors to improve the thermal stability of nickel silicide. These solutions involve the ion implantation utilizing F or N<sub>2</sub> ions before NiSi formation, Ti or Pt deposition as a capping layer or a interposing layer, and Ni<sub>1-x</sub>Ti<sub>x</sub> or Ni<sub>1-x</sub>Pt<sub>x</sub> alloy [2-7].

Recently, S. Zaima et al. reported that Ni film on  $p^+$  Si<sub>0.996</sub>C<sub>0.004</sub> epitaxial layer grown by low-pressure chemical vapor deposition (LPCVD) can suppress NiSi agglomeration effectively after annealing at 750 °C and retard its phase transformation until the annealing at 850 °C [8]. This result indicates that adding carbon (C) atoms in Si substrate is a feasible method to enhance the thermal stability of NiSi. Since the solid solubility of carbon in Si and NiSi is very low [9], carbon atoms segregate to the NiSi grain boundary and NiSi/Si interfaces and modify grain boundary and interfacial energy to suppress agglomeration and phase transformation [10]. However, when adopting selectively embedded S/D process of MOSFETs in order to produce strained Si channel, it is difficult to grow Si<sub>1-x</sub>C<sub>x</sub> with substitutional C concentration exceeding 1 % (x>1 %) due to extremely low solid solubility of C in Si.

In this chapter we introduce the ion implantation method with C ions into Si substrate so that high substitutional C concentration can be achieved, and this process is an easier than epitaxy process and can be integrated with conventional CMOS process flow. The correlation between the C dose of the ion implantation and the NiSi thermal stability is also discussed.

#### 2.2 Experiments

The starting material was phosphorus-doped (100) 6-in Si prime wafer with a resistivity of  $2\sim7~\Omega$ -cm. A 70-nm-thick screen SiO<sub>2</sub> was thermally grown. Then C ions were implanted into Si substrate through screen oxide with a dose range of  $1\times10^{15}$ ,  $5\times10^{15}$  cm<sup>-2</sup> to study the influence of C concentration on nickel silicide thermal stability. The ion energy is 30 and 40 keV. A sample without C<sup>+</sup> implantation is also prepared as reference. The C<sup>+</sup> implanted samples are named CIA samples. After C<sup>+</sup> implantation, some samples were annealed in a rapid thermal annealing (RTA) system in N<sub>2</sub> ambient at 1050 °C for 30 sec to make C atoms in the substitutional site of the Si lattice. These samples are called the CIA samples. The samples without post implantation annealing are called the w/o CIA samples. Samples without C<sup>+</sup> implantation were also prepared as reference.

After etching screen oxide by DHF dip, a 25 nm Ni layer was deposited in a physical vapor deposition (PVD) system. One step RTA process was performed to form nickel silicide at the temperature range of 500~850 °C for 30 sec. Finally, un-reacted Ni was removed by H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>SO<sub>4</sub> (1:3) mixture to finish sample preparation. Four-point probe technique was performed to measure the sheet resistance (R<sub>s</sub>) values of all samples. X-Ray Diffraction (XRD) was adopted to distinguish NiSi phase from NiSi<sub>2</sub> phase. The plan-view Scanning Electron Microscope (SEM) was used to inspect whether nickel silicide agglomerates.

#### 2.3 Results and Discussion

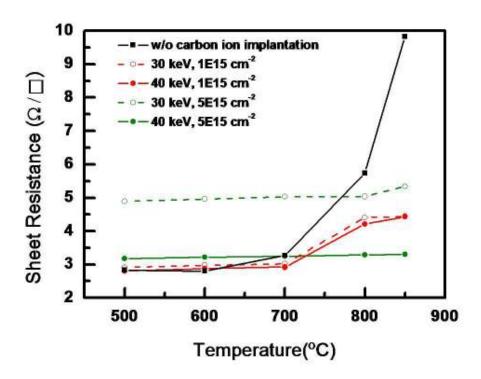

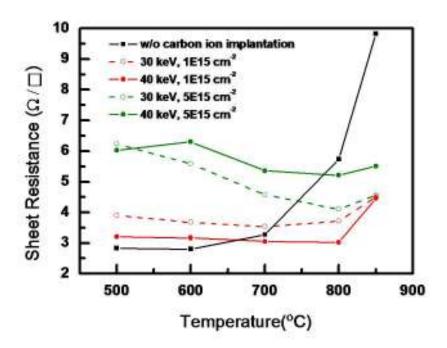

Fig.1 shows the measured  $R_s$  values of CIA samples and the reference samples as a function of annealing temperature for 30sec. Low energy or high dose  $C^+$  implantation result in slightly higher  $R_s$  value. As comparing with the reference sample, it is observed that the  $R_s$  values of CIA samples are slightly higher because of C atoms existence in nickel silicide. According to the  $R_s$  values measured after Ni film deposition, we found that the CIA samples with  $C^+$  implantation to a dose of  $5x10^{15}$  cm<sup>-2</sup> at 30 keV is deposited with thinner Ni film thickness, so these  $R_s$  values after nickel silicide formation are higher than the other samples.

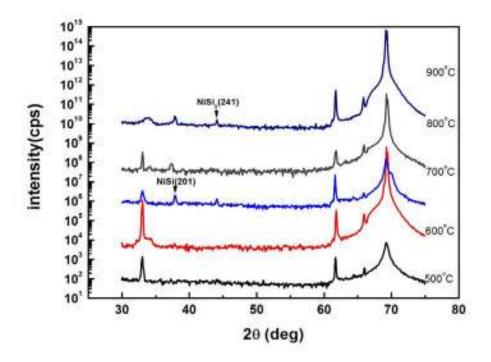

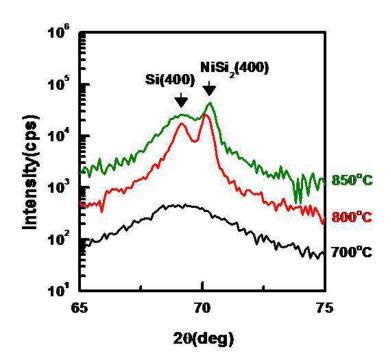

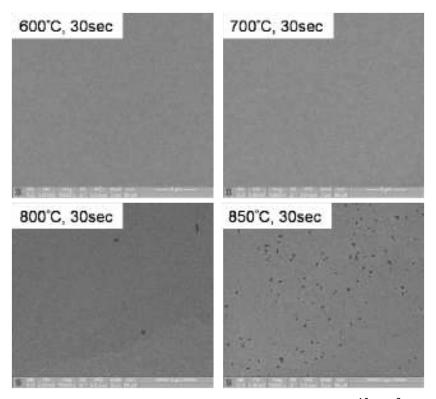

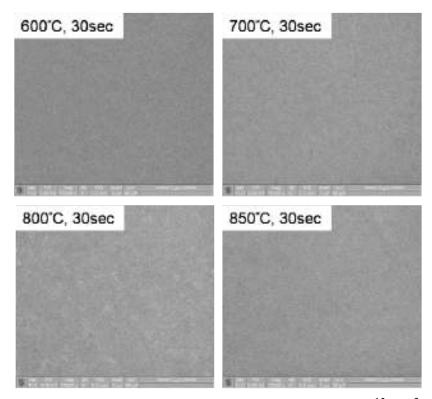

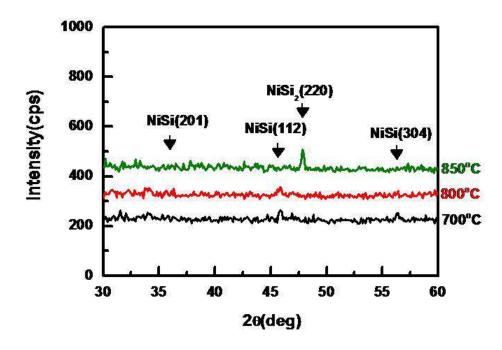

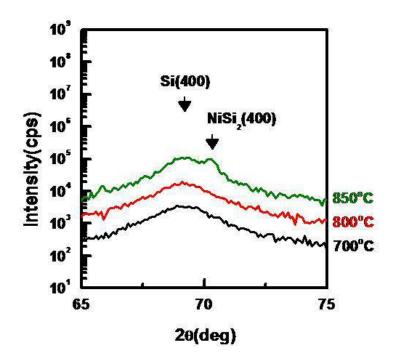

The  $R_s$  values of reference samples increases monotonically after 700°C because of serious agglomeration and phase transformation. At the same time, the  $R_s$  values of CIA samples with a dose of  $1x10^{15}$  cm<sup>-2</sup> is almost stable until 700 °C and become increase at 800 °C because phase transformation and lightly agglomeration occur simultaneously as shown in Fig.2 and 3, respectively.

As the  $C^+$  implantation dose increases up to  $5x10^{15}$  cm<sup>-2</sup>, the  $R_s$  values are stable without increasing until 850 °C. For the CIA samples with  $C^+$  implantation to  $5x10^{15}$  cm<sup>-2</sup> at 30 keV, the  $R_s$  values increase slightly at 850 °C, but for the reference samples, the  $R_s$  values increase greatly at 850 °C due to serious agglomeration. Hence the function of carbon atoms within nickel silicide is suppressing agglomeration. For the CIA samples with  $C^+$  implantation to  $5x10^{15}$  cm<sup>-2</sup> at 40 keV, the  $R_s$  values are unchanged even at 850 °C. According to the XRD result as shown in Fig.4, no phase transformation occurs, and the NiSi film is still continuous without agglomerating after 850 °C annealing as shown in the plane-view SEM micrographs of Fig.5.

Fig.6 shows the measured  $R_s$  values of w/o CIA samples and the reference sample as a function of annealing temperature for 30sec. For the w/o CIA samples with a dose of  $1x10^{15}$  cm<sup>-2</sup>, lightly agglomeration and phase transformation (not shown) take place at 800 °C as the same as the CIA samples with the same dose. When C+ implantation dose increases to  $5x10^{15}$  cm<sup>-2</sup>, as comparing between Fig.1 and Fig.6, the temperature dependence of the  $R_s$  value of the w/o CIA samples is more apparent than that of the CIA samples. We speculate that the grain size variation dominates this phenomenon. Because the Si surface was amorphorized by the high dose C<sup>+</sup> implantation, the poly-NiSi grain size of the w/o CIA samples is lager and the  $R_s$  value is lower with the increase of temperature during nickel silicide formation. For the w/o CIA samples with a dose of  $5x10^{15}$  cm<sup>-2</sup>, grain growth effect dominates  $R_s$  value at the temperature range of 500~800 °C as shown in Fig.6. On the contrary, phase transformation and agglomeration dominate  $R_s$  value at 850 °C as shown in Fig.7~8, so that the  $R_s$  values increase at 850 °C.

Table 2-1 summarize the phase transforming and agglomerating temperature of all samples. It is clear that carbon ion implantation with a dose of  $1x10^{15}$  cm<sup>-2</sup> can raise the agglomeration and phase transformation temperature of nickel silicide to 800 °C. Increasing carbon dose to  $5x10^{15}$  cm<sup>-2</sup>, it is able to further raise the agglomeration and phase transformation temperature of nickel silicide to 850 °C.

#### 2.4 Conclusions

We have investigated the impact of carbon ion implantation on the thermal stability of nickel silicide. Although carbon atoms exist within nickel silicide, may increase the sheet resistance at low silicide-formation temperature ( $\leq 700$  °C) due to C segregation at grain boundary, the increased sheet resistance value is only slightly larger than that of the reference

sample without  $C^+$  implantation. For the CIA samples, the increased of sheet resistance value is smaller than 1  $\Omega/\Box$ . Sufficient carbon atoms, a dose of  $5x10^{15}$  cm<sup>-2</sup>, can effectively suppress the agglomeration and phase transformation. For the CIA samples with a dose of  $5x10^{15}$  cm<sup>-2</sup> at 40 keV, agglomeration and phase transformation indeed can be suppressed completely even at 850 °C. Hence as the silicide-formation temperature exceeds 700 °C, samples with  $C^+$  implantation have lower  $R_s$  values than the reference samples. The thermal stability of nickel silicide can be improved by as high as 150 °C with the optimum  $C^+$  implantation condition of  $5x10^{15}$  cm<sup>-2</sup> at 40 keV.

#### References

- [1] Hiroshi Iwai, Tatsuya Ohguro, and Shun-ichiro Ohmi, "NiSi salicide technology for scaled CMOS," in Microelectronic Engineering., vol. 60, pp. 157-169, 2002.

- [2] J. Kedzierski, P. Xuan, E. H. Anderson, J. Boker, T. J. King, and C. Hu, "F-enhanced morphological and thermal stability of NiSi films on BF2+-implanted Si(001)," in Appl. Phys. Lett., vol. 81, pp. 5138-5140, 2002.

- [3] P. S. Lee, K. L. Pey, D. Mangelinck, J. Ding, A. T. S. Wee, and L. Chan, "Improved NiSi Salicide Process Using Presilicide N2+ Implant for MOSFETs," in IEEE Electron Device Letters, vol. 2, pp. 566-568, 2000.

- [4] T. H. Hou, T. F. Lei, and T. S. Chao, "Improvement of junction leakage of nickel silicided junction by a Ti-capping layer," IEEE Electron Device Letters, vol. 20, pp. 572-573, 1999.

- [5] L. W. Cheng, S. L. Cheng, and L. J. Chena, "Formation of Ni silicides on (001) Si with a thin interposing Pt layer," in J. Vac. Sci. Technology, p.1176-1179, 2000.

- [6] R. T. P. Lee, D. Z. Chi, M.Y. Lai, N. L. Yakovlev, and S. J. Chua, "Effects of Ti Incroporation in Ni on Silicidation Reaction and Structural/Electrical Propertives of NiSi," in J. Electrochem. Soc, vol. 151, pp. 642-647, 2004.

- [7] D. Mangelinck, J. Y. Dai, J. S. Pan, and S. K. Lahiri, "Enhancement of thermal stability of NiSi films on (100) Si and (111) Si by Pt addition," in Appl. Phys. Lett., vol. 75, pp. 1736-1738, 1999.

- [8] Shigeaki Zaima, Osamu Nakatsuka, Akira Sakai, Junichi Murota ,and Yukio Yasuda, "Interfacial reaction and electrical properties in Ni/Si and Ni/SiGe(C) contacts," in Applied Surface Science, vol. 224, pp. 215–221, 2004.

- [9] A. S. Edelstein, D. J. Gillespie, S. F. Cheng, J. H. Perepezko, and K. Landry, "Reactions at amorphous SiC/Ni interfaces," in J. Appl. Phys., vol. 85, pp. 2636-2641, 2002.

- [10] R. T. P. Lee, L.T. Yang, T.Y. Liow, K. M. Tan, A. E.J. Lim, K. W. Ang, D. M. Y. Lai, K. M. Hoe, G. Q. Lo, G. S. Samudra, D. Z. Chi, and Y. C. Yeo, "Nickel-Silicide:Carbon Contact Technology for N-Channel MOSFETs With Silicon-Carbon Source/Drain," in IEEE Electron Device Letters, vol. 29, pp. 89-92, 2008.

Table 2-1. Table I Summary of results of the agglomeration and phase transformation temperature of all samples.

| Spilt condition                    |         | Agglomeration | Phase transition |

|------------------------------------|---------|---------------|------------------|

| 30keV,                             | CIA     | 800 °C        | 800 °C           |

| $1 \times 10^{15} \text{ cm}^{-2}$ | w/o CIA | 800 °C        | 800 °C           |

| 40keV,                             | CIA     | 800 °C        | 800 °C           |

| $1 \times 10^{15} \text{ cm}^{-2}$ | w/o CIA | 800 °C        | 800 °C           |

| 30keV,                             | CIA     | 850 °C        | 850 °C           |

| $5 \times 10^{15} \text{ cm}^{-2}$ | w/o CIA | 850 °C        | 850 °C           |

| 40keV,                             | CIA     | >850 °C       | 850 °C           |

| $5x10^{15} \text{ cm}^{-2}$        | w/o CIA | 850 °C        | >850 °C          |

Fig.2-1. Sheet resistance of the CIA samples and the reference samples as a function of annealing temperature.

Fig.2-2. XRD spectra of the CIA samples with a dose of  $1x10^{15}$  cm<sup>-2</sup> at 40 keV. Phase transformation occurs at 800 °C and NiSi<sub>2</sub> XRD phase can be observed.

Fig.2-3. SEM micrographs of the CIA samples with a dose of  $1x10^{15}$  cm<sup>-2</sup> at 40 keV. Nickel silicide film agglomerates at 800 °C.

Fig.2-4. XRD spectra of the CIA samples with a dose of  $5x10^{15}$  cm<sup>-2</sup> at 40 keV. Phase transformation does not occur even at 850 °C.

Fig.2-5. SEM micrographs of the CIA samples with a dose of  $5x10^{15}$  cm<sup>-2</sup> at 40 keV. No pin-holes can be observed which indicates nickel silicide film is still continuous.

Fig.2-6. Sheet resistance of the w/o CIA samples and the reference samples as a function of annealing temperature.

Fig.2-7. XRD spectra of the w/o CIA samples with a dose of  $5x10^{15}$  cm<sup>-2</sup> at 30 keV. Phase transformation occurs at 850 °C.

Fig.2-8. SEM micrographs for w/o CIA samples with a dose of  $5x10^{15}$  cm<sup>-2</sup> at 30 keV. Nickel silicide film agglomerates at 850 °C.

# Chapter 3

# Impact of Carbon Ion Implantation on the Thermal Stability of Nickel Silicide Contacted Shallow Junction

#### 3.1 Introduction

Nickel monosilicide (NiSi) has been extensively investigated and used as a source/drain (S/D) contact material for a long time. NiSi has several advantages including low resistivity, low contact resistivity, a low-temperature process, less Si consumption during silicide formation, no narrow-line effect, and no bridging failure [1]. However, the main issue of NiSi film is its thermal stability at high temperatures. It is well known that NiSi film agglomerates to form small broken holes and then discontinuous islands at 700 °C, and the NiSi phase transforms into NiSi<sub>2</sub> phase at 700-750 °C. These two factors cause an increase in the sheet resistance ( $R_s$ ) of the Ni-silicide film. Moreover, with the continuous scaling down of complementary metal-oxide-semiconductor (CMOS) devices, ultra shallow S/D junctions are becoming increasingly important in order to suppress the short-channel effect (SCE). The decrease in junction depth requires a decrease in NiSi film thickness, which has a strong effect on its thermal stability. Consequently, several methods of raising the thermal stability of NiSi film have been published [2-7]. These methods involve ion implantation (I/I) utilizing F or  $N_2$  ions before NiSi formation, the deposition of Ti or Pt as a capping layer or an interposing layer, and the deposition of a Ni<sub>1-x</sub>Pt<sub>x</sub> or Ni<sub>1-x</sub>Pt<sub>x</sub> alloy.

Recently, Zaima *et al.* reported that a  $p^+$  Si<sub>0.996</sub>C<sub>0.004</sub> epitaxial layer grown by low-pressure chemical vapor deposition (LPCVD) can effectively raise the thermal stability of NiSi film [8], and similar results were also reported by Nakatsuka *et al.* [9]. The mechanism of suppressing the agglomeration and phase transformation of NiSi film is that C atoms segregate to the NiSi grain boundaries and NiSi/Si interface to modify the grain boundary and interfacial energy due to the low solid solubility of C atoms in NiSi [10]. Two common methods have been used to include C atoms within a Si substrate. One is Si<sub>1-x</sub>C<sub>x</sub> epitaxial growth directly on a Si substrate [8, 10], and the other is C I/I into a Si wafer surface followed by thermal annealing [9, 11-12]. As a result of the extremely low solid solubility of C atoms in Si, the Si<sub>1-x</sub>C<sub>x</sub> epitaxial process cannot easily achieve a higher substitutional C concentration than 1% (x>1%) [13]. In this chapter, we focus on C I/I technology. This

process is simpler than the epitaxy process and is compatible with the standard CMOS process flow. Moreover, it has been demonstrated that a  $Si_{1-x}C_x$  S/D can produce tensile strain in the channel region, increasing the electron mobility and drive current of n-type metal-oxide-semiconductor field-effect transistors (NMOSFETs) [14-15]. Thus, C I/I technology is feasible for integration with  $n^+/p$  shallow junctions in the future.

The impact of the C I/I process on n<sup>+</sup>/p shallow junction current-voltage (I-V) characteristics has not been studied in detail. In this chapter, we demonstrate and discuss the trade-off between the thermal stability of NiSi film and the n<sup>+</sup>/p shallow junction I-V characteristics. Some methods of fabricating NiSi-contact n<sup>+</sup>/p shallow junctions with both good thermal stability and excellent I-V characteristics are proposed.

#### 3.2 Experiments

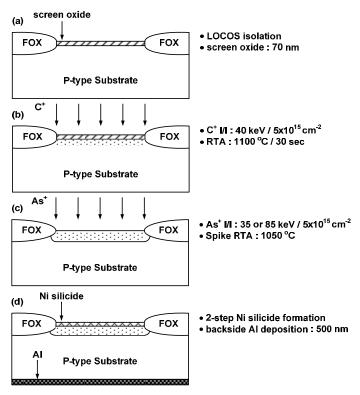

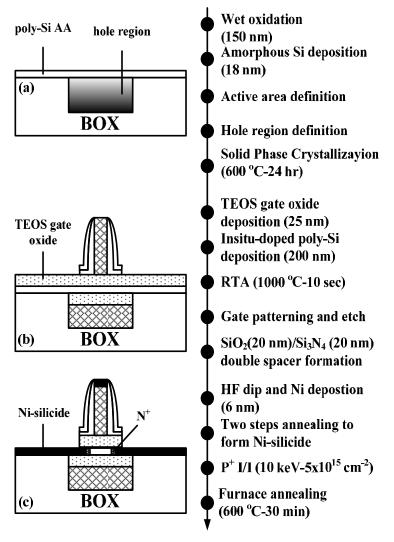

The starting material used in this study was boron-doped (100) 6-in.-diameter Si prime wafer with a resistivity of 2-7  $\Omega$  cm. After typical local-oxidation-of-silicon (LOCOS) isolation, a 70-nm-thick screen oxide layer was thermally grown. Next, C ions were implanted through the screen oxide at 40 keV to a dose of  $1 \times 10^{15}$  or  $5 \times 10^{15}$  cm<sup>-2</sup>. The projected range of C ions is 58 nm under the Si surface. Then C I/I defects were eliminated by rapid thermal annealing (RTA) at 1100 °C for 30 s. Samples without C I/I were also prepared as reference. After etching the screen oxide by diluted HF (DHF) solution, arsenic (As) ions were implanted to a dose of  $5x10^{15}$  cm<sup>-2</sup> at 35 or 85 keV followed by a 1050 °C spike annealing process. The lower As I/I energy of 35 keV results in more dopants within the Ni-silicide film and a shallower junction depth. After removing the native oxide by DHF solution, a 25-nm-thick Ni layer and a 5-nm-thick TiN capping layer were continuously deposited by a sputtering system followed by a two-step annealing process to form NiSi [16]. The first step was performed at 300 °C for 60 min. After that, the TiN capping layer and the unreacted Ni were selectively removed by a mixture of H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>SO<sub>4</sub>=1:3. The second annealing step was performed at a temperature of 500-800 °C for 30 s in order to study the NiSi thermal stability. Finally, a 500-nm-thick Al layer was deposited on the wafer backside surface by a sputtering system to complete the fabrication of the n<sup>+</sup>/p shallow junctions. Blanket samples without a LOCOS isolation structure were also fabricated for the purpose of material analysis. The main process flow of n<sup>+</sup>/p shallow junctions is illustrated in Fig. 1. The notation used to identify different samples along with their fabrication conditions are summarized in Table I.

The four-point probe technique was used to measure the sheet resistance (R<sub>s</sub>) of all

samples with blanket Ni-silicide films. X-ray diffraction (XRD) was adopted to distinguish the NiSi phase from the NiSi<sub>2</sub> phase. Scanning electron microscopy (SEM) was used to inspect the surface morphology of the Ni-silicide. The I-V characteristics of the n<sup>+</sup>/p shallow junctions were measured by an Agilent 4156C precision semiconductor parameter analyzer.

#### 3.3 Results and Discussion

#### A. Thermal stability

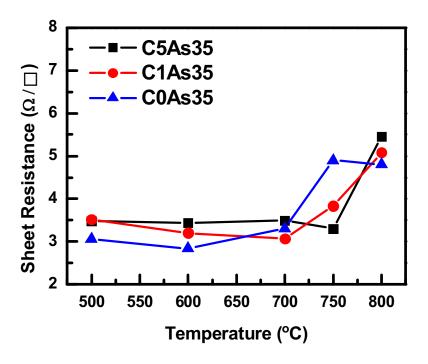

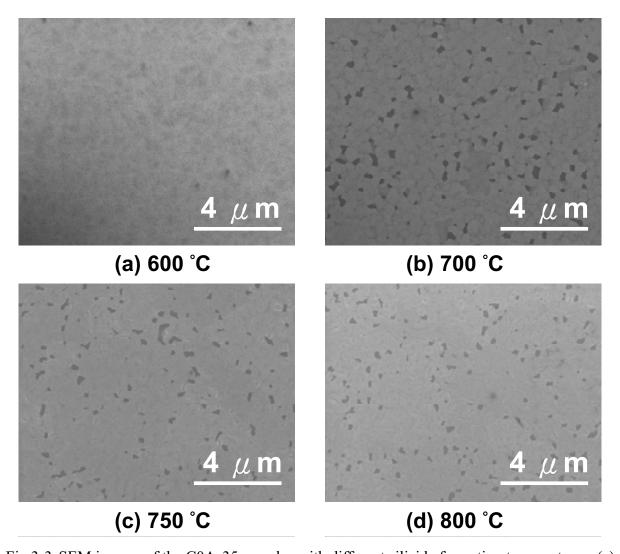

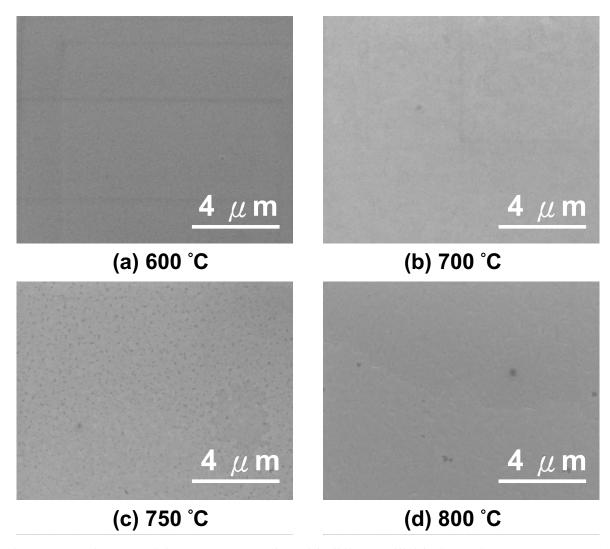

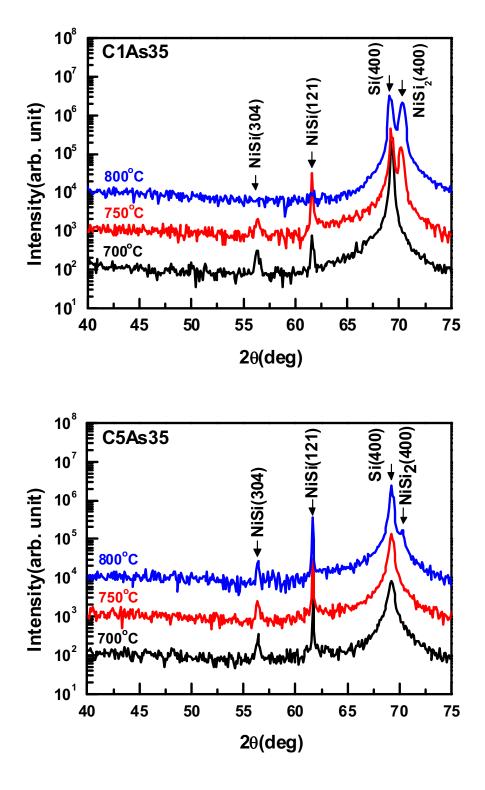

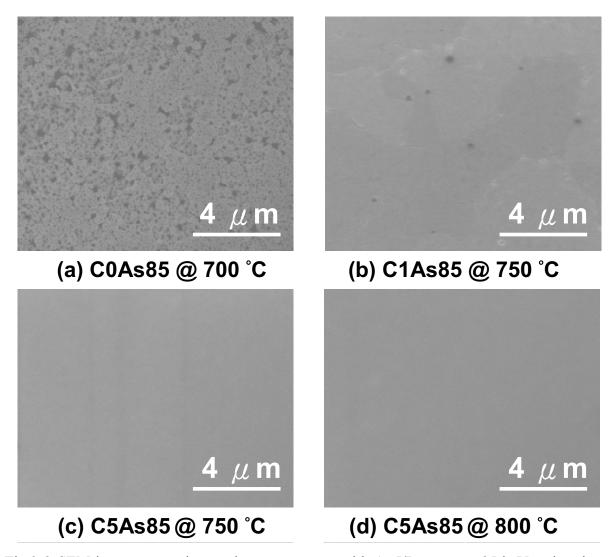

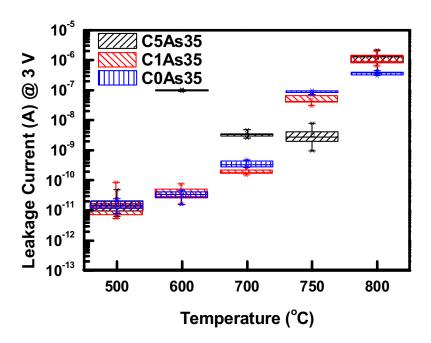

Figure 2 shows the measured  $R_s$  values as a function of silicide formation temperature with As I/I energy at 35 keV. The samples with the higher C I/I dose of  $5x10^{15}$  cm<sup>-2</sup> (C5As35) have slightly higher  $R_s$  values at a lower silicide formation temperature ( $\leq 700$  °C) due to the larger number of C atoms within the Ni-silicide film. Figures 3-5 display SEM images of the C0As35, C1As35, and C5As35 samples, respectively. The  $R_s$  values of the C0As35 samples increase from 700 °C because of NiSi film agglomeration. Many broken holes in the NiSi film can be seen in Fig. 3(b). On the other hand, few holes can be observed at 750 °C in the C1As35 samples, as shown in Fig. 4(c), and a continuous Ni-silicide film without any holes is obtained even at 800 °C in the C5As35 samples as shown in Fig. 5(d). Hence, it is confirmed that sufficient C atoms can effectively suppress the agglomeration of Ni-silicide film.

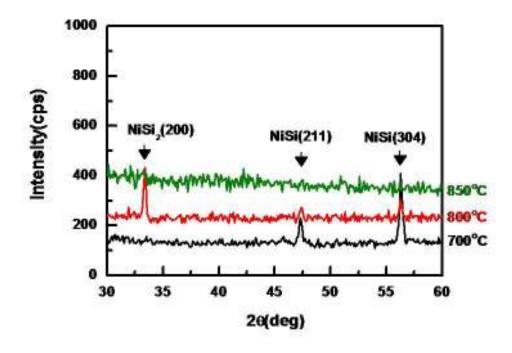

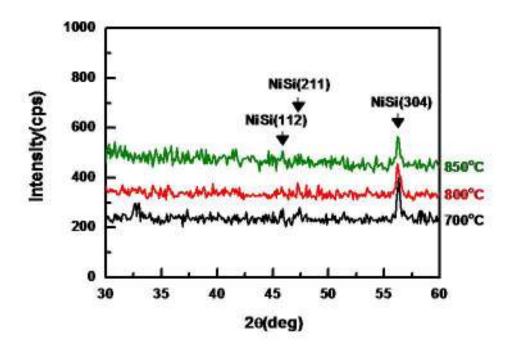

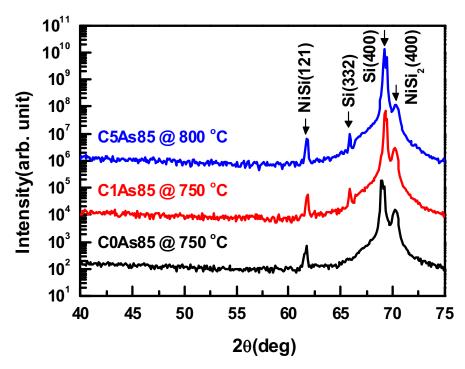

To understand the reason for the increased R<sub>s</sub> values of the C1As35 samples at 750 °C and the C5As35 samples at 800 °C, XRD analysis was used to identify the Ni-silicide phase. The XRD spectra of C1As35 and C5As35 samples are shown in Figs. 6(a) and 6(b), respectively. In Fig. 6(a), it is observed that the NiSi<sub>2</sub>(400) phase appears at 750 °C in the C1As35 samples, and the NiSi(121) phase coexists in the Ni-silicide film at the same time. Furthermore, the NiSi(121) phase disappears and only the NiSi<sub>2</sub>(400) phase can be detected at 800 °C. In the C5As35 samples, the NiSi<sub>2</sub>(400) phase does not occur until 800 °C as shown in Fig. 6(b). According to these observations, it is clear that increasing the C I/I dose to 5x10<sup>15</sup> cm<sup>-2</sup> can retard the phase transformation of NiSi film. In summary, performing the C I/I process with a higher C dose of 5x10<sup>15</sup> cm<sup>-2</sup> is a feasible method for enhancing the thermal stability of NiSi film even if As dopants exist.

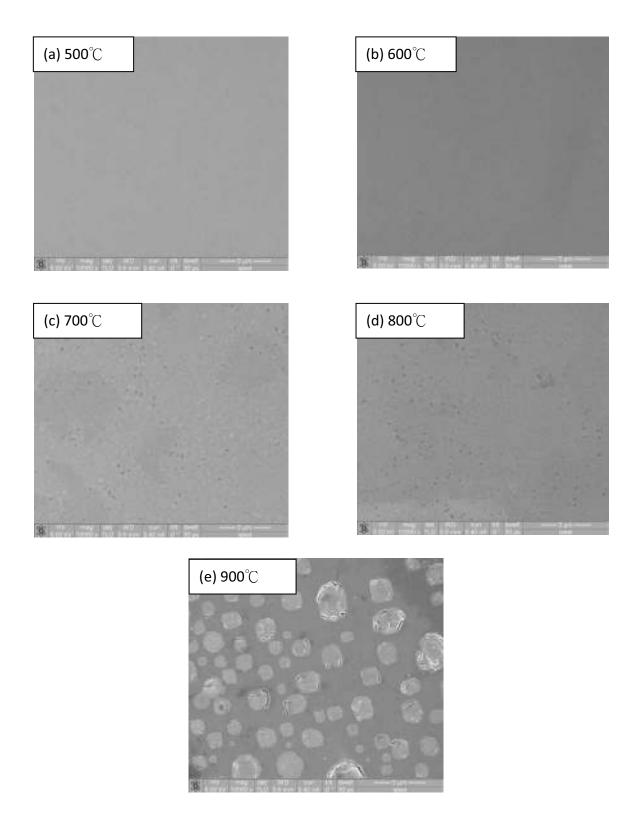

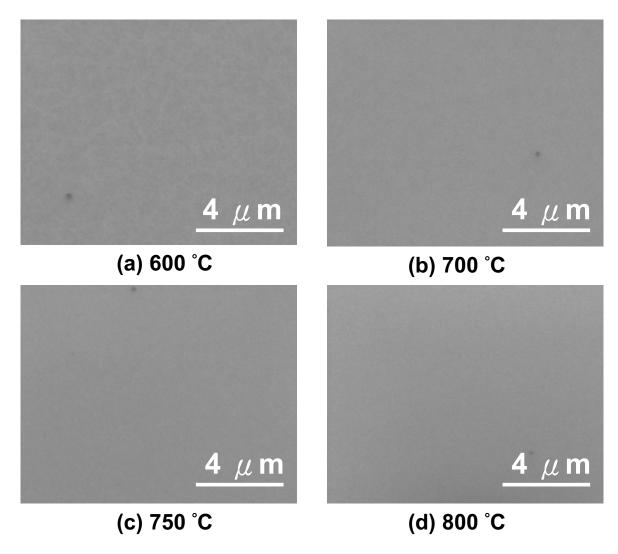

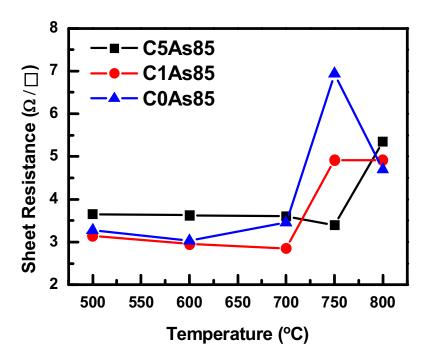

Figure 7 shows the measured  $R_s$  values as a function of silicide formation temperature with As I/I energy at 85 keV, and the corresponding SEM images and XRD spectra are shown in Figs. 8 and 9, respectively. The information revealed from these figures is similar to that discussed previously. Moreover, the phase transformation temperature of the C0As85 samples is 750 °C while that of the C0As35 samples is 700 °C. On the basis of the experimental

results of Ahmet *et al.* [17], we consider that the higher As I/I energy results in fewer As dopants within the NiSi film. Thus, the phase transformation temperature of the C0As85 samples is 50 °C higher than that of the C0As35 samples.

The agglomeration temperature and phase transformation temperature of all samples are summarized in Table II. It is clear that C I/I with a dose of  $1x10^{15}$  cm<sup>-2</sup> can raise the agglomeration and phase transformation temperatures of Ni-silicide film to 750 °C. By increasing the C I/I dose to  $5x10^{15}$  cm<sup>-2</sup>, the phase transformation temperature of Ni-silicide film can be further raised to 800 °C, and the agglomeration temperature becomes higher than 800 °C. The C I/I process successfully enhances the thermal stability of Ni-silicide film by at least 100 °C.

#### B. Junction characteristics

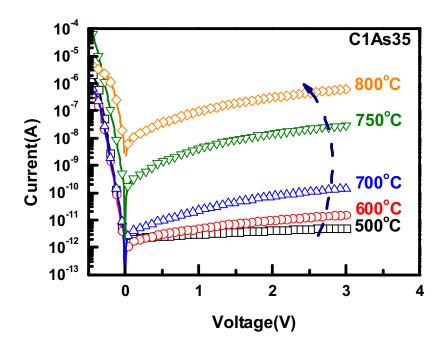

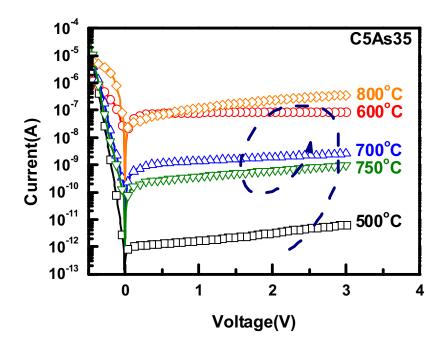

Figure 10 shows the I-V characteristics of the Ni-silicide-contact n<sup>+</sup>/p shallow junction with As I/I energy at 35 keV. The junction area is  $6.25 \times 10^{-4}$  cm<sup>2</sup>. Both the C1As35 and C5As35 samples exhibit the lowest leakage current at the silicide formation temperature of 500 °C. The lowest leakage value is approximately 10 nA/cm<sup>2</sup> at a reverse bias of 3 V, and this value is close to that of the junction without silicide. For the C0As35 and C1As35 samples, the leakage current increases with increasing silicide formation temperature. However, the samples with a C I/I dose of 5x10<sup>15</sup> cm<sup>-2</sup> exhibit very different reverse leakage current behavior. For the C5As35 samples, when the silicide formation temperature increases to 600 °C, the leakage current abruptly increases by 3 orders of magnitude. Then the leakage current decreases as the silicide formation temperature increases to 700 and 750 °C, but increases again as the silicide formation temperature increases to 800 °C. Figures 11 and 12 show statistics of the junction leakage current at a reverse bias of 3 V for the Ni-silicide-contact n<sup>+</sup>/p shallow junctions with As I/I at 35 and 85 keV, respectively. The silicide formation temperature dependences of the junction leakage current described above are confirmed to be universal behavior. The same leakage current dependence on the silicide formation temperature and C I/I dose can also be found at an As I/I energy of 85 keV as shown in Fig. 12.

Three mechanisms are considered to have an effect on the junction leakage current. The first one is the agglomeration of the Ni-silicide film. Agglomeration causes an increase in interface roughness at the Ni-silicide/Si contact, and the junction leakage current may increase owing to structural damage. The second is the diffusion of Ni atoms. The many defects

produced by the high-dose I/I process form the diffusion path. Ni atoms can rapidly diffuse via these defects during silicide formation. As Ni atoms diffuse toward the junction depletion region and form deep levels, the junction leakage current increases. The third is the phase transformation from the NiSi phase to the NiSi<sub>2</sub> phase. When the phase transformation occurs, the thickness of the silicide film becomes double that of the NiSi film. Thus, the Ni-silicide/Si interface becomes closer to the junction depletion region. Agglomeration can easily damage the junction depletion region, and more Ni atoms arrive at the junction depletion region to contribute to the junction leakage current. Agglomeration and the phase transformation occur at a high silicide formation temperature and depend on the silicide formation temperature and C I/I dose. In addition to the silicide formation temperature, the effect of the diffusion of Ni atoms is also related to the number of I/I defects, which depends on the C I/I dose.

For the reasons mentioned above, the deeper junction has fewer Ni atoms within the junction depletion region. Moreover, the agglomeration and phase transformation also have less impact on the deeper junction. Hence, by comparing Figs. 11 and 12, it can be seen that the leakage current at an As I/I energy of 85 keV is much lower than that of 35 keV at a high silicide formation temperature.

When the C I/I dose is zero or equal to  $1 \times 10^{15}$  cm<sup>-2</sup>, the number of defects is not large enough to form a long diffusion path for Ni atoms. Hence, the agglomeration and phase transformation dominate the junction leakage current mechanism, and the junction leakage current increases with silicide formation temperature. Because the C1As35 and C1As85 samples have better thermal stability of the Ni-silicide film, both samples exhibit a lower leakage current than the C0As35 and C0As85 samples with silicide formation temperatures of 700 and 750 °C .

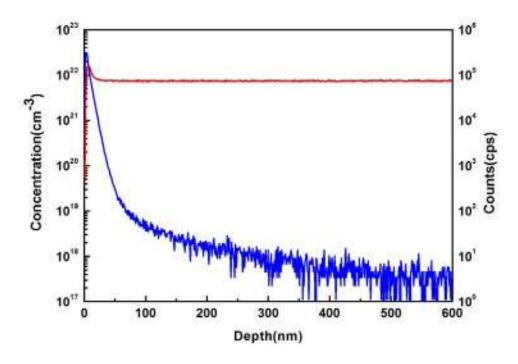

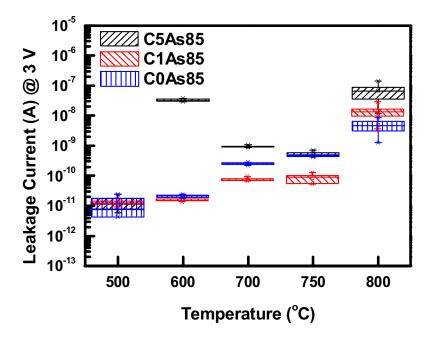

On the other hand, when the C I/I dose increases to 5x10<sup>15</sup> cm<sup>-2</sup>, it generates many remnant defects, and Ni atoms can diffuse very rapidly via these defects. Therefore, the diffusion of Ni atoms dominates the junction leakage current mechanism. The leakage currents of the C5As35 and C5As85 samples are similar to that of the C0As35 sample at 500 °C, as can be observed by comparing Figs. 11 and 12. This indicates that most of the defects generated by a high C I/I dose were annihilated by RTA at 1100 °C for 30 s. Figures 13(a) and 13(b) show the SIMS depth profiles of C, As, and Ni atoms of the C5As85 and C0As85 samples with the silicide formation temperature at 600 °C, respectively. The different surface NiSi thicknesses of these two samples is due to the thickness variation of the as-deposited Ni films. Hence, all of the depth profiles were measured from the NiSi/Si interface, which is

defined as the intersection of the Ni and As depth profiles. Rucker etal. reported that substitutional C atoms can enhance As dopants diffusion, but the diffusion enhancement effect ends when most of the C atoms precipitate [18]. In the case of our C5As85 samples, C atoms were incorporated by ion implantation, and this process produced a large number of Si interstitials. It is well known that C atoms can trap Si interstitials to eliminate secondary defects during high-temperature annealing [19]. Hence, C atoms combine with Si interstitials and precipitate to form immobile clusters during high-temperature annealing. Compared with the epitaxial Si:C layer in Rucker et al.'s experiment, most of the C atoms are not located at substitutional sites in our C5As85 samples. Therefore, no As diffusion enhancement is observed upon comparing Fig. 13(a) with Fig. 13(b). It is observed that the Ni depth profile of the C5As85 sample has an apparent hump whose position coincides with the peak of the C depth profile. The distance between As and Ni atom depth profiles measured at an As atom concentration of 1x10<sup>18</sup> cm<sup>-3</sup> is indicated in Figs. 13(a) and 13(b). The Ni distribution of the C5As85 sample is about 15 nm closer to the n<sup>+</sup>/p junction than that of the C0As85 sample. This implies that the C5As85 sample has more Ni atoms within the junction depletion region owing to the dissolution and diffusion of Ni atoms toward the junction depletion region along the many defects induced by C I/I with a dose of  $5x10^{15}$  cm<sup>-2</sup> during silicide formation. This explains why the C5As35 and C5As85 samples unexpectedly exhibit the highest leakage current at 600 °C. We consider that it can generate more and more vacancies injecting into Si substrate during Ni-silicide formation at a higher temperature [20]. These vacancies can combine and remove some residual defects, so that fewer Ni atoms can diffuse into the junction depletion region. Therefore, the junction leakage current decreases as the silicide formation temperature increases to 700 and 750 °C. Finally, the increase in the leakage current again at 800 °C is a result of the agglomeration and phase transformation of the Ni-silicide film.

To suppress the diffusion of nickel atoms, we propose two solutions. One method is to ensure that the carbon distribution is shallower than the junction depletion region by introducing a lower carbon ion implantation energy. Thus, a higher concentration of carbon atoms near the Si substrate surface can be obtained. We predict that this will further enhance the thermal stability of the nickel silicide film. Furthermore, defects are far away from the junction, thus reducing the leakage current. The other method is to eliminate the defects as completely as possible. Raising the thermal budget of RTA or developing other annealing processes to eliminate these defects will be researched in the future.

#### 3.4 Conclusions

We have investigated the impact of carbon ion implantation on the thermal stability of nickel silicide. Although carbon atoms exist within nickel silicide, may increase the sheet resistance at low silicide-formation temperature ( $\leq 700$  °C) due to C segregation at grain boundary, the increased sheet resistance value is only slightly larger than that of the reference sample without C<sup>+</sup> implantation. For the CIA samples, the increased of sheet resistance value is smaller than 1  $\Omega$ / $\square$ . Sufficient carbon atoms, a dose of  $5x10^{15}$  cm<sup>-2</sup>, can effectively suppress the agglomeration and phase transformation. For the CIA samples with a dose of  $5x10^{15}$  cm<sup>-2</sup> at 40 keV, agglomeration and phase transformation indeed can be suppressed completely even at 850 °C. Hence as the silicide-formation temperature exceeds 700 °C, samples with C<sup>+</sup> implantation have lower Rs values than the reference samples. The thermal stability of nickel silicide can be improved by as high as 150 °C with the optimum C<sup>+</sup> implantation condition of  $5x10^{15}$  cm<sup>-2</sup> at 40 keV.

#### References

- [1] H. Iwai, T. Ohguro, and S. I. Ohmi: Microelectron. Eng. **60** (2002) 157.

- [2] T. H. Hou, T. F. Lei, and T. S. Chao: IEEE Electron Device Lett. **20** (1999) 572.

- [3] D. Mangelinck, J. Y. Dai, J. S. Pan, and S. K. Lahiri: Appl. Phys. Lett. **75** (1999) 1736.

- [4] P. S. Lee, K. L. Pey, D. Mangelinck, J. Ding, A. T. S. Wee, and L. Chan: IEEE Electron Device Lett. 21 (2000) 566.

- [5] L. W. Cheng, S. L. Cheng, L. J. Chen, H. C. Chien, H. L. Lee, and F. M. Pan: J. Vac. Sci. Technol. A 18 (2000) 1176.

- [6] A. S. W. Wong, D. Z. Chi, M. Loomans, D. Ma, M. Y. Lai, W. C. Tjiu, S. J. Chua, C. W. Lim, and J. E. Greene: Appl. Phys. Lett. 81 (2002) 5138.

- [7] R. T. P. Lee, D. Z. Chi, M. Y. Lai, N. L. Yakovlev, and S. J. Chua: J. Electrochem. Soc. 151 (2004) 642.

- [8] S. Zaima, O. Nakatsuka, A. Sakai, J. Murota, and Y. Yasuda: Appl. Surf. Sci. **224** (2004) 215.

- [9] O. Nakatsuka, K. Okubo, A. Sakai, M. Ogawa, Y. Yasuda, and S. Zaima: Microelectron. Eng. 82 (2005) 479.

- [10] R. T. P. Lee, L. T. Yang, T. Y. Liow, K. M. Tan, A. E. J. Lim, K. W. Ang, D. M. Y. Lai, K. M. Hoe, G. Q. Lo, G. S. Samudra, D. Z. Chi, and Y. C. Yeo: IEEE Electron Device Lett. 29 (2008) 89.

- [11] Y. Liu, O. Gluschenkov, J. Li, A. Madan, A. Ozcan, B. Kim, T. Dyer, A. Chakravarti, K. Chan, C. Lavoie, I. Popova, T. Pinto, N. Rovedo, Z. Luo, R. Loesing, W. Henson, and K. Rim: Symp. VLSI Tech. Dig., 2007, p. 44.

- [12] S. M. Koh, K. Sekar, D. Lee, W. Krull, X. Wang, G. Samudra, and Y. C. Yeo: IEEE Electron Device Lett. **29** (2008) 1315.

- [13] A. C. Mocuca and D. W. Greve: J. Appl. Phys. **85** (1999) 1240.

- [14] K. W. Ang, K. J. Chui, V. Bliznetsov, A. Du, N. Balasubramanian, M. F. Li, G. Samudra, and Y. C. Yeo: IEDM Tech. Dig., 2004, p. 1069.

- [15] K. W. Ang, K. J. Chui, V. Bliznetsov, Y. Wang, L. Y. Wong, C. H. Tung, N. Balasubramanian, M. F. Li, G. Samudra, and Y. C. Yeo: IEDM Tech. Dig., 2005, p. 497.

- [16] B. Y. Tsui and C. P. Lin: IEEE Trans. Electron Devices **52** (2005) 2455.

- [17] P. Ahmet, T. Shiozawa, K. Nagahiro, T. Nagata, K. Kakushima, K. Tsutsui, T. Chikyow, and H. Iwai: Microelectron. Eng. **85** (2008) 1642.

- [18] H. Rucker, B. Heinemann, and R. Kurps: Phys. Rev. B 64 (2001) 073202.

- [19] S. Nishikawa and T. Yamaji: Appl. Phys. Lett. 62 (1993) 303.

- [20] L. J. Chen: Silicide Technology for Integrated Circuits (IEE, London, 2004) p. 27.

Table.3-1. Summary of results of the agglomeration and phase transformation temperature of all samples.

| Spilt condition       |         | Agglomeration | Phase transition |

|-----------------------|---------|---------------|------------------|

| 30keV,                | CIA     | 800 °C        | 800 °C           |

| 1E15 cm <sup>-2</sup> | w/o CIA | 800 °C        | 800 °C           |

| 40keV,                | CIA     | 800 °C        | 800 °C           |

| 1E15 cm <sup>-2</sup> | w/o CIA | 800 °C        | 800 °C           |

| 30keV,                | CIA     | 850 °C        | 850 °C           |

| 5E15 cm <sup>-2</sup> | w/o CIA | 850 °C        | 850 °C           |

| 40keV,                | CIA     | >850 °C       | 850 °C           |

| 5E15 cm <sup>-2</sup> | w/o CIA | 850 °C        | >850 °C          |

Table.3-2. Summary of results of agglomeration and phase transformation temperatures of all samples.

| Sample ID | Agglomeration temperature (°C) | Phase transition temperature (°C) |

|-----------|--------------------------------|-----------------------------------|

| C5As35    | > 800                          | 800                               |

| C1As35    | 750                            | 750                               |

| C0As35    | 700                            | 700                               |

| C5As85    | > 800                          | 800                               |

| C1As85    | 750                            | 750                               |

| C0As85    | 700                            | 750                               |

Fig.3-1 Main process flow of the n<sup>+</sup>/p shallow junction: (a) after LOCOS isolation and screen oxide growth, (b) after carbon ion implantation and annealing, (c) after arsenic ion implantation and activation, and (d) the final structure.

Fig.3-2 Sheet resistance values as a function of silicide formation temperature with As I/I energy at 35 keV and different C I/I doses.

Fig.3-3 SEM images of the C0As35 samples with different silicide formation temperatures: (a) 600 °C, (b) 700 °C, (c) 750 °C, and (d) 800 °C. Several holes are generated within the Ni-silicide film at 700 °C, causing an increase in sheet resistance.

Fig.3-4 SEM images of the C1As35 samples with different silicide formation temperatures: (a)  $600~^{\circ}$ C, (b)  $700~^{\circ}$ C, (c)  $750~^{\circ}$ C, and (d)  $800~^{\circ}$ C. Only a few small holes can be observed at  $750~^{\circ}$ C.

Fig.3-5 SEM images of the C5As35 samples with different silicide formation temperatures: (a) 600 °C, (b) 700 °C, (c) 750 °C, and (d) 800 °C. No holes can be observed, and the Ni-silicide film retains an intact structure.

Fig.3-6 XRD spectra of the (a) C1As35 samples and (b) C5As35 samples. The NiSi $_2$  phase appears to cause an increase in the sheet resistance at 750 °C in the C1As35 samples and at 800 °C in the C5As35 samples.

Fig.3-7 Sheet resistance values as a function of silicide formation temperature with As I/I energy at 85 keV and different C I/I doses.

Fig.3-8 SEM images at agglomeration temperature with As I/I energy at 85 keV and various C I/I doses: (a) C0As85 at 700 °C, (b) C1As85 at 750 °C, (c) C5As85 at 750 °C, and (d) C5As85 at 800 °C.

Fig.3-9 XRD spectra at phase transformation temperature with As I/I energy at 85 keV and various C I/I doses

Fig.3-10 Silicide formation temperature dependences of leakage current characteristics of Ni-silicide-contact n<sup>+</sup>/p shallow junction with As I/I energy at 35 keV: (a) C1As35 samples and (b) C5As35 samples.

Fig.3-11 Statistics of the reverse-bias junction leakage current at 3 V for the Ni-silicide-contact n<sup>+</sup>/p shallow junctions with As I/I at 35 keV.

Fig.3-12 Statistics of the reverse-bias junction leakage current at 3 V for the Ni-silicide-contact n<sup>+</sup>/p shallow junctions with As I/I at 85 keV.

Fig.3-13 SIMS depth profiles of C, Ni, and As of the (a) C5As85 and (b) C0As85 samples with silicide formation temperature at 600 °C.

# Chapter 4

# Si-C Formation by Low Temperature Carbon Ion Implantation

#### 4.1 Introduction

Low temperature ion implantation process is performed by putting wafer on a low temperature chuck to make the wafer temperature low. Low temperature wafer contains less thermal energy, thus the self annealing effect during implantation process can be reduced. In this way, the surface amorphous layer created by low temperature ion implantation will have better quality than that created by ion implantation at room temperature or higher temperature. High quality amorphous layer can improve the crystalline quality of substrate after annealing, and is beneficial for Si-C forming.

In this chapter, we use low temperature ion implantation to implant carbon ions. The basic characteristic of low temperature carbon ion implanted silicon substrate is examined. Different experimental conditions are investigated to find the best condition for Si-C forming.

## 4.2 Experiments

#### A. Low Temperature Ion Implantation

The low temperature ion implanter used in this chapter is model iPulsar produced by Advance Ion Beam Technology Co. (AIBT). The allowed implantation energy range is 100 eV - 40 keV and the dose range is  $1 \times 10^{13}$  to  $5 \times 10^{16}$  ions/cm<sup>2</sup>. Tilt angle is from 0° to 45° and the twist angle is from 0° to 360°. Since the implanter is designed for 12-inch wafer process, we use a 12-inch wafer as wafer holder, and attach 6-inch wafer on it, then put the holder on the chuck to perform ion implantation.

The iPulsar system contains one focused ion beam 2D mechanical scan system and one uniform strip shape ion beam 1D mechanical scan system, can provide various kind of implantation, especially low energy ion implantation. The cold wafer e-chuck in the iPulsar system is a special equipment, and is one of the major differences compare to conventional ion implanters. During the process, the chiller is flowed through the e-chuck and makes the chuck temperature low, the lowest temperature that e-chuck could achieve is -20 °C. The backside gas flow between the wafer backside and chuck is controlled to conduct the heat.

Low temperature e-chuck can lower the temperature of wafer, and can provide several process benefits.

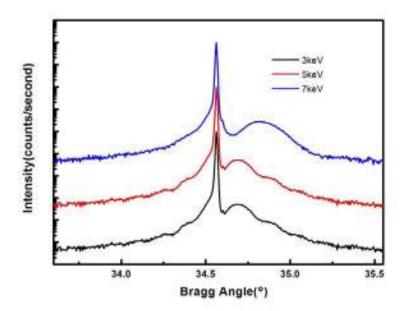

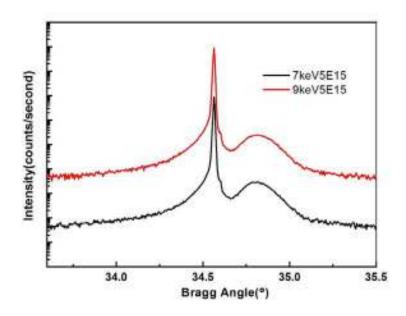

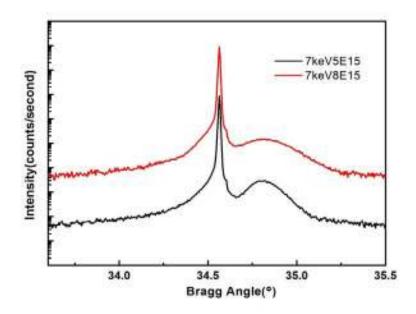

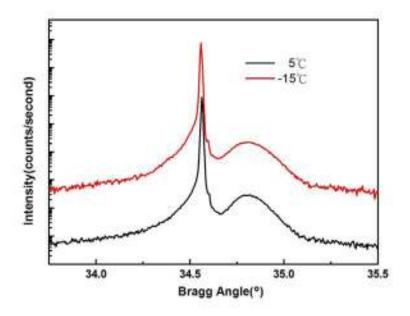

### B. Substitutional Carbon Density Sample

Six-inch-diameter p-type (100) silicon wafers with nominal resistivity of  $15\sim25~\Omega$ -cm were used as substrates. The low temperature ion implantation was performed at chuck temperature of 5°C or -15°C. The implant energy is at 3 keV, 5 keV, 7 keV, and 9 keV. The implantation dose is controlled to  $2\sim5\times10^{15}$  cm<sup>-2</sup>. The implantation conditions of samples are labeled in the form of energy/dose. For the samples implanted at 5°C chuck temperature the implantation conditions are 3 keV/5×10<sup>15</sup> cm<sup>-2</sup>  $\cdot$  5 keV/5×10<sup>15</sup> cm<sup>-2</sup> and 7 keV/5×10<sup>15</sup> cm<sup>-2</sup>. For the samples implanted at -15°C chuck temperature, the implantation conditions are 7  $keV/5\times10^{15}~cm^{-2}~,~7~keV/8\times10^{15}~cm^{-2}~,~9~keV/5\times10^{15}~cm^{-2}~and~3~keV/2\times10^{15}~cm^{-2}+~5$ keV/3×10<sup>15</sup> cm<sup>-2</sup>+ 7 keV/3×10<sup>15</sup> cm<sup>-2</sup>. Then all the samples accepted additional phosphorous ion implantation at 17 keV to a dose of 5×10<sup>15</sup> cm<sup>-2</sup>. After phosphorus ion implantation, the samples were cut into small pieces and two steps of annealing process were performed for SiC formation. In the first step, samples were annealed in N2 ambient by a rapid thermal annealing (RTA) system at temperatures ranging from 650 °C to 850 °C for 90 to 180 secs. In the second step, some of the samples were annealed in N2 ambient by a RTA system at temperature of 1000°C for 1sec second. Some samples were annealed by a pulse laser annealing (PLA) system. A 248nm KrF excimer laser was used as laser source, the laser energy is 350 mJ/cm<sup>2</sup>, the pulse duration is around 25 ns/shot and the number of shots ranges from 5 to 20.

The same process steps were also performed on the CPIII samples to evaluate the substitutional carbon density of the CPIII process. The carbon ion implant condition is 3K5M and the annealing temperature is 650°C and 750°C for 120 secs.

#### C. Material Analysis

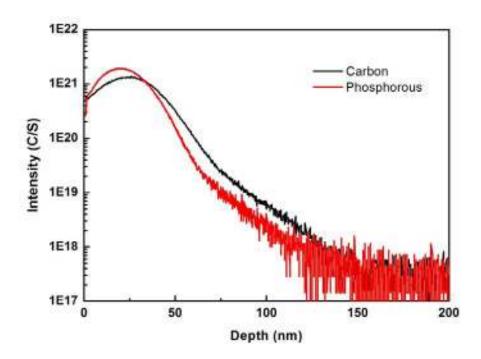

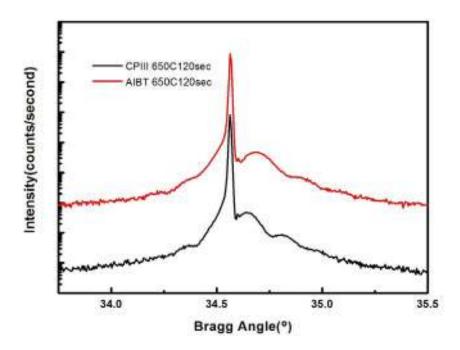

Several Material Analysis techniques include XRD \ SEM \ SIMS and TEM were used in our experiment. XRD analysis has two main purposes in this experiment. The first one is to find out the nickel silicide phase transformation temperature. The second purpose of XRD is to calculate the number of substitutional carbon by using the rocking curve method proposed by P. C. Kelires in 1997 [1]. This model can calculate the atomic percentage of the

substitutional carbon in Si matrix ( $C_{sub}$ ) by the lattice constant difference ( $\Delta d$ ) obtained from the XRD rocking curve. The detail is introduces in the next paragraph. First, the lattice constant difference  $\Delta d$  between Si and Si<sub>1-x</sub>C<sub>x</sub> could be obtained by the XRD rocking curve result. The lattice constant of Si<sub>1-x</sub>C<sub>x</sub> on the growth direction  $a_{\perp}$  can be calculated by

$$a_{\perp} = a_{Si} + \Delta d \ (a_{Si} = 5.431A)$$

After obtained the value of a<sub>1</sub>, the value of relaxed lattice parameter a<sub>rel</sub> can be calculated by

$$a_{\text{rel}} = \left[ (a_{\perp} - a_{\parallel}) \div \left( 1 + 2 \frac{C_{12}}{C_{11}} \right) \right] + a_{\parallel}$$

Finally the value x of Si<sub>1-x</sub>C<sub>x</sub> can be extracted by solving the following Equation

$$a_{\rm rel} = a_{\rm Si} - 2.439x + 0.5705x^2$$

Scanning Electron Microscope (SEM) is used to inspect the surface morphology of the carbon implanted nickel silicide samples after annealing at different conditions. The surface continuity and the level of agglomeration can be observed by SEM inspection. Secondary Ion Mass Spectrometry (SIMS) is used to analysis the depth profiles of carbon and phosphorus atoms in samples after ion implantation and annealing. Transmission Electron Microscopy (TEM) is used to observe the microstructure of samples. It can help to figure out the thickness of amorphous layer and the level of amorphization.

For electrical measurement, the sheet resistances of all blanket samples were measured by four point probe.

#### 4.3 Basic Material Analysis

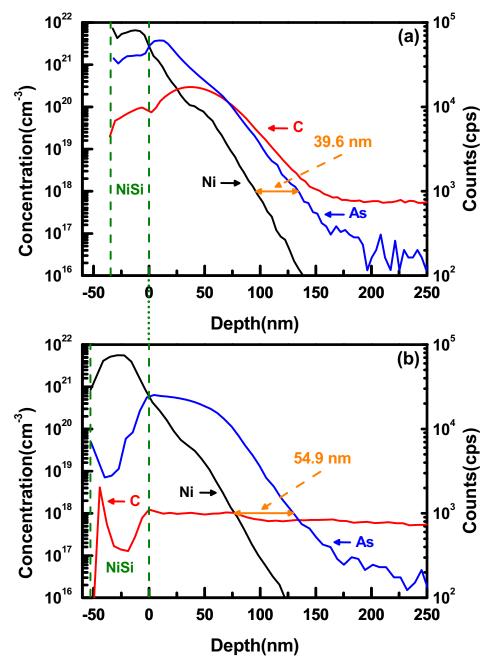

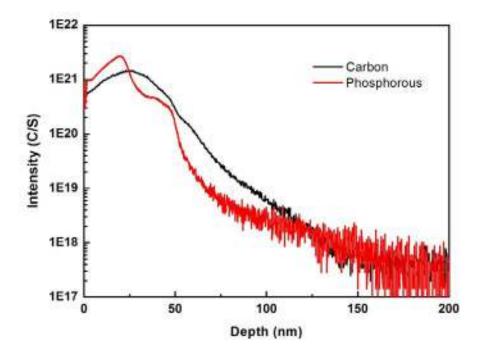

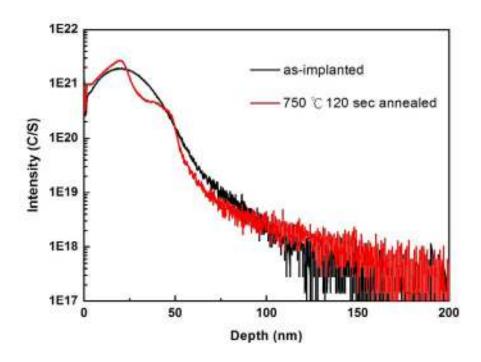

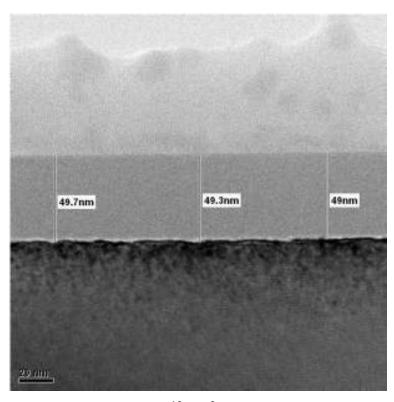

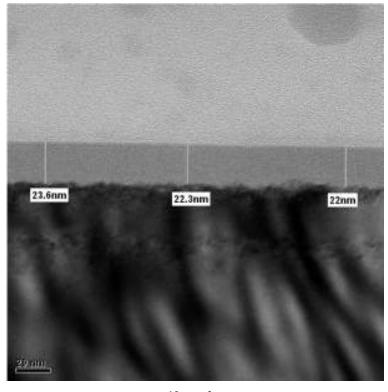

We performed SIMS and TEM on the sample with carbon implanted at 7 keV and a dose of 5×10<sup>15</sup> cm<sup>-2</sup>. The chuck temperature was -15°C during ion implantation. After carbon implantation, additional phosphorous ion implantation at 17 keV to a dose of 5×10<sup>15</sup> cm<sup>-2</sup> was performed. Both the as-implanted sample and the samples annealed at 750°C for 120 sec were analyzed. Fig.4-1 shows the SIMS depth profiles of carbon and phosphorus atoms of the as-implanted sample. It is observed that most of carbon atoms are located at the region between 25nm to 30nm from the surface. And the phosphorous atoms are located at the region between 18nm to 30nm from the surface. Fig.4-2 shows the SIMS depth profiles of carbon and phosphorus of the 750°C annealed sample. The carbon profile is nearly the same with that of the as-implanted sample. In Fig.4-3 we compare the phosphorous depth profiles of annealed sample to the as-implanted sample. After annealing, the concentrations of phosphorous in the region between 25nm to 43nm and between 49nm to 78nm significantly

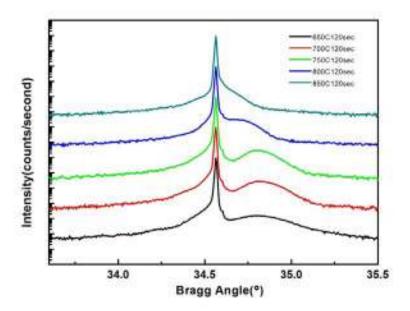

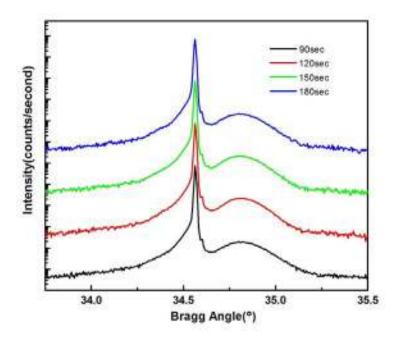

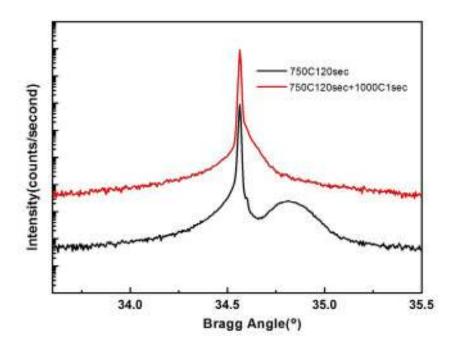

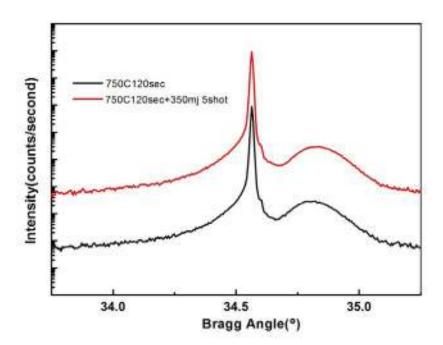

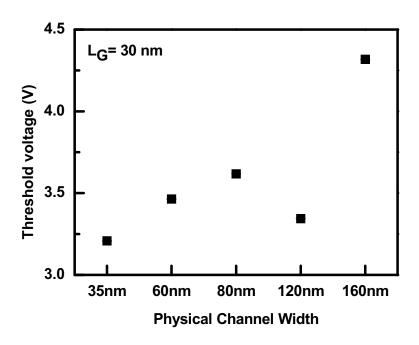

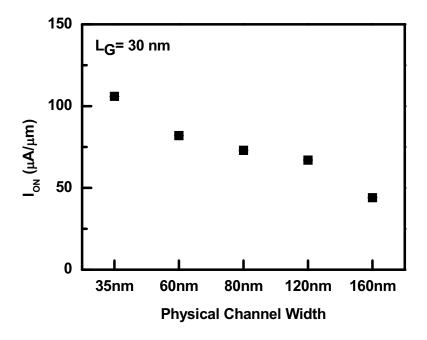

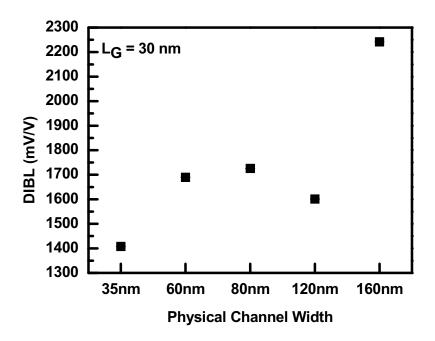

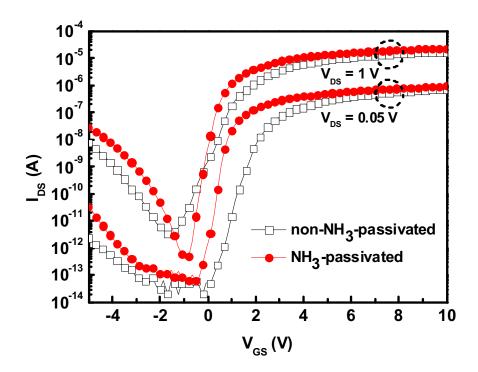

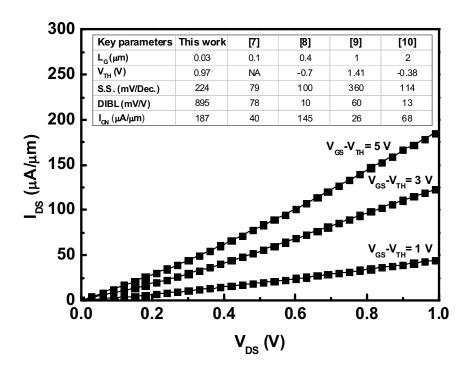

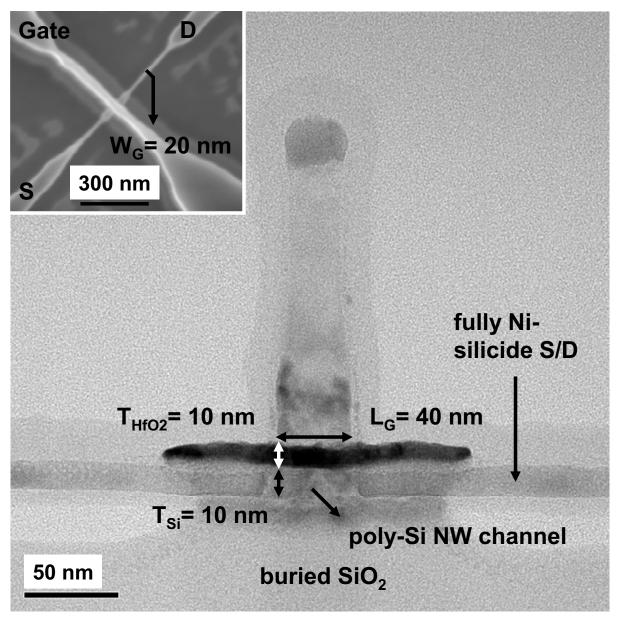

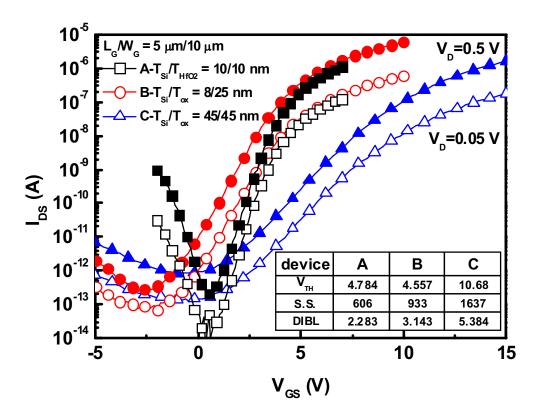

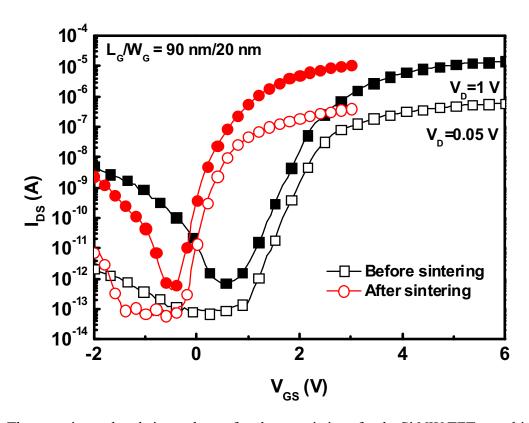

decreases and the concentrations of phosphorous in the region between 16nm to 24nm and between 44nm to 48nm increases evidently. In the deeper region of the silicon substrate, the number of phosphorous increased for less than one order.