# 行政院國家科學委員會補助專題研究計畫 □ 成 果 報 告 ■ 期中進度報告

# 以電流驅動錫晶鬚的成長之研究

| 計畫編       | 诵號:              | NSC    | 96-26        | -畫 □ 魯<br>28-E009-(<br>月 1日至                  | 010-MY3      | 引 31 日 |                    |

|-----------|------------------|--------|--------------|-----------------------------------------------|--------------|--------|--------------------|

| 共同主       | 持人               | :      | 智 教授 魏程昶     | <b>注</b><br>世、林宗寬、                            | 蕭翔耀,林        | 漢文     |                    |

| 成果報       | 2告類              | 型(依    | <b>交經費</b> 榜 | 定清單規定                                         | 繳交):■≒       | 精簡報告   | □完整報告              |

| □赴國□赴大□出席 | 1外出<br>、陸地<br>西際 | 差或品出學術 | 研習心 差或研 意議心  | 繳交之附件:<br>得報告一份<br>習心得報告-<br>得報告及發表<br>外研究報告書 | ー份<br>長之論文各・ | 一份     |                    |

| 處理方       | 7式:              | 列管     | 計畫及          | 下列情形者外                                        | 卜,得立即,       | 公開查詢   | 培育研究計畫、<br>F後可公開查詢 |

| 執行單       | 2位:              | 交通     | 大學材料         | 料系所                                           |              |        |                    |

| 中         | 華                | 民      | 國            | 98年                                           | 6 月          | 09 日   |                    |

#### 摘要

本實驗分為兩個部份,第一部份為覆晶銲錫(flip chip solder joints)通電之後形成晶鬚的結果,第二部分為製作 Blech 結構通電之後的結果。第一部份使用 Sn-0.7Cu 一對銲料通電之後,發現在 board side 為陽極時擠出 hillock,在 chip side 擠出 whisker,結果發現 hillock 成長比 whisker 還要嚴重,造成不等量的相被擠出原因為形成 Intermetallic Compound (IMC)量多寡的影響,IMC 生成的量與來自陰極端 Cu 原子的供應有關,IMC 的生成會阻礙 Sn 的擴散路徑,因此會擠出 Sn 原子的 hillock 或 whisker。

第二部份為 bleck 結構的結果,由於幾何結構使得電流產生集中,此種效應成為高輸出原件的可靠度議題。電流密度梯度能夠在電流集中區域產生驅動力,藉由通以直流電產生的電流密度梯度影響將有額外多餘的空孔從電流密度低的位置擴散至電流密度高的位置,經過交流電通電結果觀察到陰陽極表面變粗糙,我們發現到在陽極端有 Pb hillock 發生在經由直流電通電過後,因為此種通電條件下 Pb 原子為主要擴散載子, Pb hillock 產生在SnPb/(IMC)界面。

#### 實驗步驟

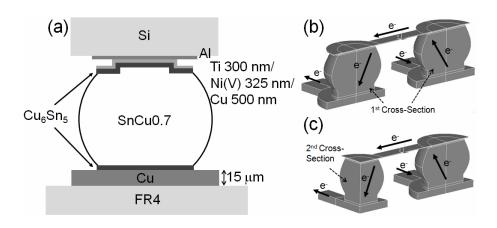

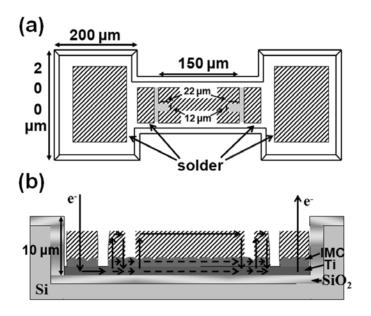

第一部分實驗過程,通電結構示意圖如圖 1(a),使用的尺寸為  $13\times 10\times 0.56$  mm³ chip 封裝結構,chip端為  $3.5\times 0.5\times 0.73$  mm³ Si chip,chip第一次reflow上Sn-0.7Cu,第二次reflow上機板,chip端under-bump-metallization(UBM)為  $0.3\mu$ m Ti/ $0.325\mu$ m Ni/ $0.5\mu$ m Cu,UBM開口與 passivation 開口分別為  $110\mu$ m與  $85\mu$ m,機板端為  $15\mu$ m Cu pad,Cu pad 經過 solder-on-pad(SOP)表面處理,Cu在結構中扮演黏著層,分別在chip端和機板端形成Cu<sub>6</sub>Sn<sub>5</sub> IMC。

圖 1(b)為研磨拋光至中間,通以一對銲錫 1.3×10<sup>4</sup> A/cm²電流密度在 100 度hotplate上,並且做同步觀察通電前與通電後結果,箭頭所指的為電子流方向,電子流從下端銅導線中央流入右側銲錫,經由上端AI導線流入左端銲錫,在經由下端銅導線離開,右邊銲錫電子流主要集中在左上角,左邊集中在右上端,電子流集中效應chip端遠高於機板端是由於機板端Cu為厚Cu UBM可以有效分散電流,圖 1(c)為切第二次橫截面示意圖,並用離子束與二次電子束觀察相分布與表面形貌。

圖 1、(a)Sn-0.7Cu 結構示意圖 (b)二分之一橫截面通電示意圖 (c)四分之一橫截面通電示意 圖

第二部份本研究主要是利用 Blech 結構,再加上通以較高的電流密度,在陽極端產生壓應力來探討在高電流驅動下銲錫晶鬚的生長情況與其結構。其中,於第一年中我們以 Sn-Pb 銲料合金為主要的探討對象。此通電所引發的錫鬚晶生長模式不同於傳統的錫鬚晶生長機制,主要為通電藉由電子撞擊原子而產生一驅動力,此驅動力會促使原子在線路中擴散。根據電遷移理論將會在錫條合金原子中生成應力,此一應力將會促使晶鬚的成長。因此,在實驗流程上主要包含:(1)微影製程的試片製備。(2)聚焦離子束(Focus ion beam, FIB)定義圖型。

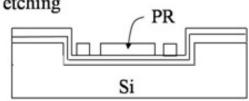

#### (1) 微影蝕刻的試片製備

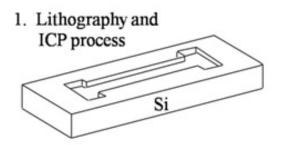

Blech 結構試片的製作流程如圖 3 所示。製作時,我們先將購得的 n-type Si 晶片經過丙酮、異丙醇與純水在超音波震盪器中清洗,以去除表面的有機物及污染物。然後將已經清洗完畢的 Si 晶片利用微影製程將所需的結構製作於基材上。

一開始將已經清洗完畢之 Si 試片塗佈 HMDS,以增加光阻與試片之黏著力,再利用 旋轉塗佈的方式將 AZ5214 光阻塗佈於上。之後將試片放置於 100℃下進行軟烤的動作, 此軟烤時間為六十秒鐘。而軟烤後的試片利用曝光機定義出所需的圖形,經過 UV 光照 射後,我們便可將試片置於 AZ4620MIF 顯影液中搖晃進行顯影。顯影完後的試片仍需 置於 120℃下一百二十秒鐘,以完成最後硬烤的動作。

顯影完後的光阻厚度經表面輪廓儀量測其厚度約為 2μm。最後為製作出 I shape 於 Si 基材上,我們使用清大貴儀中心的 inductively coupled plasma-reactive ion etching (ICP-RIE)於矽基材上製作出約 3μm 的 trench。最後進行 RCA 清洗步驟以利後續製程。

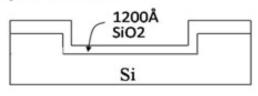

之後,我們利用交通大學奈米中心的 Oxidation and Diffusion furnaces 設備成長一層厚度為 1200Å 的 SiO2。此沉積層的目的為隔絕 Si 基材與之後將要製作於 SiO2 上的金

屬導線,以避免進行通電測試時,電子流藉由矽之半導體基材而導通,同時亦可避免金屬線與 Si 基材進行反應,產生矽化物(silicide)造成金屬導線的毀壞。為了將電流導入 SnPb 合金薄膜中,我們將試片放置於電子槍蒸鍍機中沉積 Ti(1500Å)/Cu(8000Å),製造

## 2. SiO<sub>2</sub> layer formation

# 3. E-gun evaporation processes

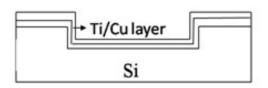

# Lithography for metal etching

#### 5. Polish down

## 6. FIB process

圖3、製作流程圖。

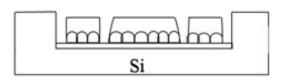

圖 4、拋光後之表面形貌圖。。

出金屬導線。之後再次利用微影蝕刻製程在Cu薄膜上定義出所需圖型,如 3.1 流程圖中的步驟 4 所示。爾後再利用 $FeCl_3$ 與D.I. water (1:200)調配之蝕刻液,蝕刻出所需之銅薄膜圖型。

爾後將共晶錫鉛焊錫置於已定義出之銅薄膜上,以210℃在加熱板上迴銲四秒。為 製作出平整的銲錫表面,我們使用拋光研磨方式製作出平整之銲錫表面如圖2所示。

#### (2) 聚焦離子束(FIB)定義圖型與分析方法

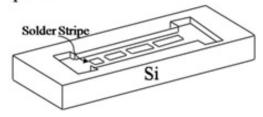

為了定義出不同的錫鉛合金長度,我們使用FIB之離子束蝕刻技術製作出  $150\mu m$ 長的 SnPb

銲錫,並在邊緣部份蝕刻出兩個  $22 \mu m \times 12 \mu m \times 12 \mu m$ 的坑洞,用以成長Pb晶鬚使用,如圖 5 所示。為了了解升溫後邊緣由於焦耳熱效應產生的溫升,使用infrared microscope (IR) 進行量測,接續為了更清楚電流密度的分布情形,此實驗中也導入模擬分析軟體。 Sn

與Cu

反應生成之Cu Cu Sn Sn

試片初步完成後,為評估所需通入的電流量,我們使用原子力顯微鏡(Atomic Force Microscope, AFM),利用因探針與試片表面原子間作用力造成懸臂彈簧片偏轉所得到之 3D表面形貌結果,來計算出試片之平均厚度。之後再依據不同層如 SnPb、Ti 與 IMC 各

圖 5、(a)試片以 FIB 離子束蝕刻後之示意圖。(b)試片經 FIB 離子束蝕刻後之剖面示意圖。

層之厚度利用並聯電路的方式求得通入之電流量與通入之電流密度,如圖 3(b)所示。

在通電過程中,我們將同時利用 SEM 與 BEI 影像來進行晶鬚生長情形觀測。為了深入了解複合晶鬚之成長方向與複合晶鬚成分,將使用 FIB 製作複合晶鬚之切片,利用 TEM 對切片進行觀察與分析。

#### 結果

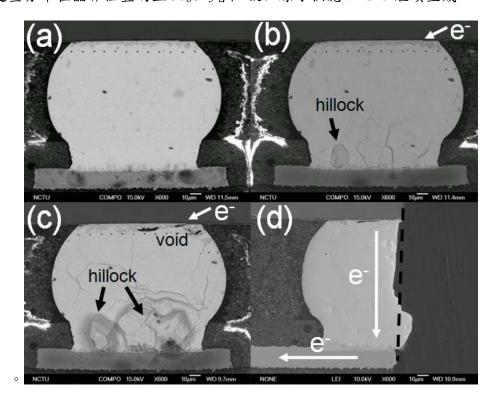

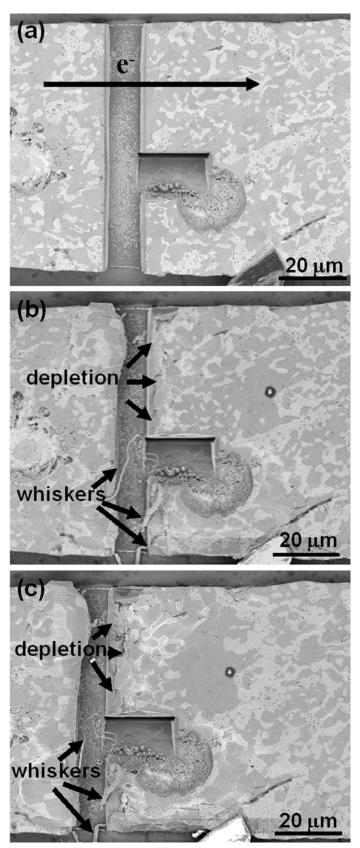

第一部分結果電子流向下圖 6(a)通電前,經過 150hrs 和 1632hrs 後,圖 6(b)(c)發現在板端產生 hillock,經過 1632hrs 在 chip 端產生 void,觀察圖 6(c)比較 void 體積與 hillock 體積似乎不符合質量守恆,因此研磨二次橫截面如圖 6(d)所示,solder 的中心的表面凹陷約5μm,長出的 hillock 厚度約 10μm 到 20μm,此結果消耗的體積約等於凸出的體積。

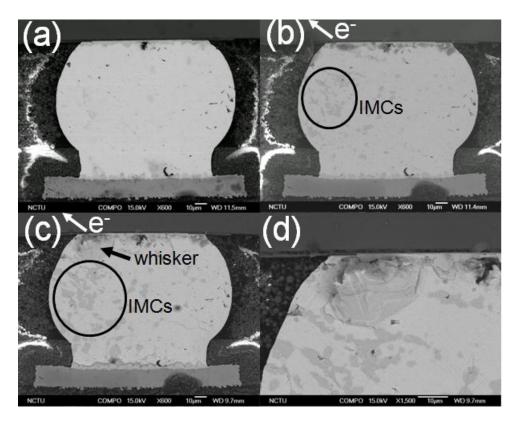

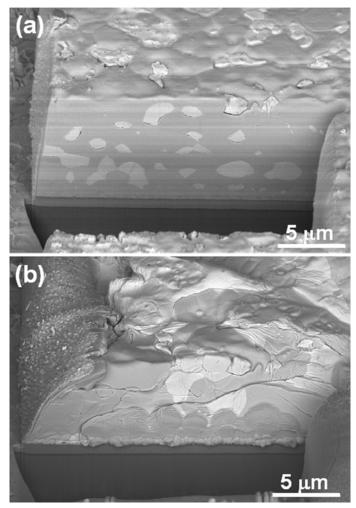

電子流向上的結果如圖 7(b)(c)會在chip端上看到whisker生成,比較電子流向上與向下的結果發現通電前相分布的情況大約相同,在電子流向上的結果中發現IMC大量生成在接近chip端附近,而沒有hillock生成只有少量的whisker生成,進一步使用離子影像觀察電子流向上與向下的結果,經過二次橫截面的結果如圖 8(a)(b)(c)(d),Sn相顏色在離子影像下比IMC還要暗,所以在電子流向下的結果中發現圖 8(b)在hillock底部有Cu<sub>6</sub>Sn<sub>5</sub>阻礙Sn原子前進,上端有兩個長條狀的Sn相供應hillock Sn原子,因此Cu<sub>6</sub>Sn<sub>5</sub>為阻礙Sn原子擴散至板端的阻礙層,在電子流向上的微結構中也可以發現有Sn原子被擠出表面,但是在電子流向上的情況中,不但有Sn原子因電子風力向上移動有更多的Cu原子向上移動,因此會再晶界的位置析出IMC,這些分布在晶界位置的上Cu<sub>6</sub>Sn<sub>5</sub>會阻礙Sn原子供應whisker繼續生成。

圖 6、在  $150^{\circ}$ C 通  $1.3 \times 10^4$  A/cm² (a)通電前 (b)通電 150hrs (c)通電 1632hrs (d)圖(c)二次横截面

圖 7、在  $150^{\circ}$ C 通  $1.3 \times 10^{4}$  A/cm² (a)通電前 (b)通電 150hrs (c)通電 1632hrs (d)圖(c)左上角 放大圖

圖 8、在  $150^{\circ}$ C 通  $1.3 \times 10^{4}$  A/cm² (a)電子流向下 (b)圖(a)板端放大 (c)電子流向上 (d)圖 (c)chip端放大

以下為第二部份的結果:

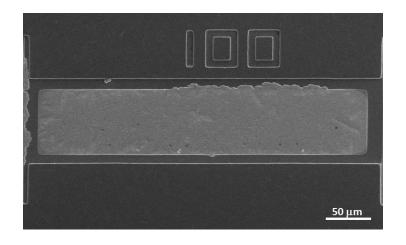

#### 電遷移效應之影響

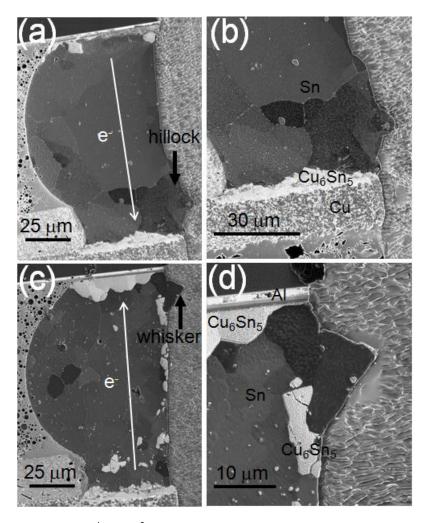

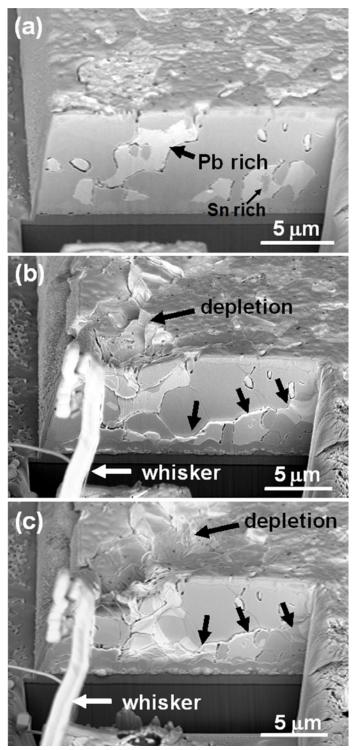

圖9(a)為試片剛完成之BEI圖,圖9(b)(c)於100°C下,經電流密度4.28×10<sup>4</sup> A/cm<sup>2</sup>、28hrs和50hrs後之表面形貌圖。亮區為富鉛相,暗區為富錫相,可以觀察到受到電流效應的影響,經過28hrs後陰極端富Sn區開始凹陷,經過50hrs後在富鉛區隨著通電時間增加生成更多的鉛鬚。

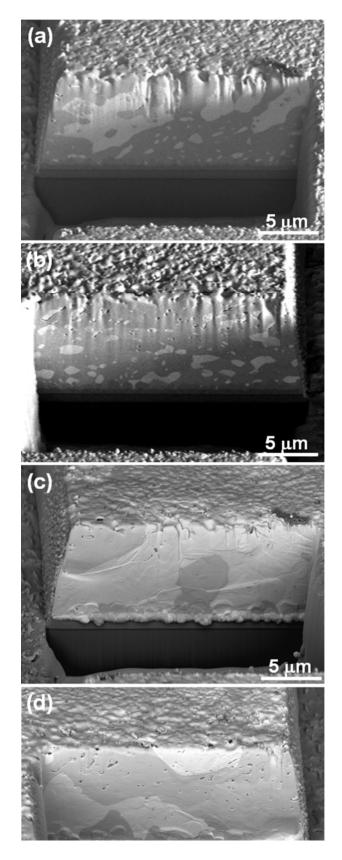

為了可以明顯看出電流集中效應造成在介金屬化合物與SnPb Solder之間的影響,傾斜觀察切面如圖10(a)-10(c),在此陰極端,可以觀察到通電後Cu層已經完全消耗完,對於solder stripe垂直方向微結構變化並沒有很明顯,隨著通電時間增加,富鉛相逐漸收縮,而錫相擴散往原本鉛相位置,鉛原子沿著側面移動,這是由於在此種條件通電情況下鉛原子是主要擴散載子。觀察陽極端微結構的變化,如圖11(a)-6(c),原本位在鉛相內的錫經由電子推力移動到陽極端邊緣位置。

由圖10(b)(c)可以發現到空孔從高電流密度區往低電流密度區移動,也就是移動到左上

角的位置,此種空孔形成的結果如同先前文獻Al的電遷移結果,基於電流密度梯度的力量, 高阻值的元素如鉛,會被電子力從電流密度高的位置推向電流密度低的位置,在圖5(b)(c) 與圖11(b)(c)明顯的觀察到亮區會集中在底部位置,也是鉛相集中的位置。

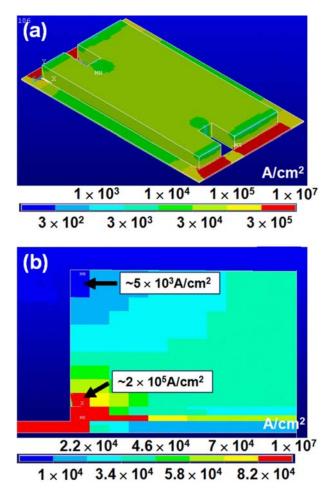

為了更進一步了解實際上電流密度的分布,我們使用有限元素分析法模擬出實際的電流密度值,如圖12(a)(b)所示,低電流密度區分布在兩端邊緣Solder Stripe表面,證實空孔聚集在低電流密度區,藉由模擬的結果,計算出電流梯度產生的驅動力。

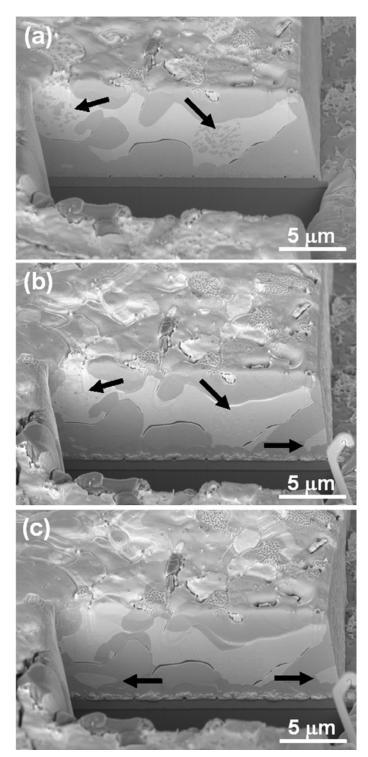

比較通以直流電與交流電微結構變化,如圖13、圖14所示,通以直流電之後陰極端觀察到消耗,鉛相也隨著高電流密度往右遷移,通以直流電則觀察到表面變粗糙,並無空孔聚集和鉛相移動,如果探討以往的結果,加入熱遷移的效應,鉛相是往溫度較低的地方移動,錫相是往熱端移動,可是在此實驗中並無觀察到此種現象,因為經由IR量測的結果整體的溫升只有1°C。

圖13是經由150°C以2×10<sup>4</sup> A/cm<sup>2</sup>電流密度通電後陽極端的結果,根據以往的文獻鉛在 此條件下是主要的擴散載子,累積的鉛相聚集在介金屬化合物與SnPb Solder的界面,進而 形成hillock,hillock形成的原因 (1)經由電子風力原子主要擴散至陽極端 (2)鉛累積在介金 屬化合物與SnPb Solder之間產生壓應力 (3)為了釋放壓應力hillock受到鉛相累積而形成。

圖 9、(a)通電前 (b) 於  $100\,^{\circ}$ C下,電流密度  $4.28\times10^4\,\text{A/cm}^2$ 經 28hr之BEI圖。(c) 50hrs後BEI 圖。

圖 10、陰極端 (a)通電前 (b) 於  $100\,^{\circ}$ C下,電流密度  $4.28\times10^{4}\,\text{A/cm}^{2}$ 經 28hr之傾斜BEI圖。 (c) 50hrs後傾斜BEI圖。

圖 11、陽極端 (a)通電前 (b) 於  $100\,^{\circ}$ C下,電流密度  $4.28\times10^{4}\,\text{A/cm}^{2}$ 經 28hr之傾斜BEI圖。 (c) 50hrs後傾斜BEI圖。

圖 12、(a)圖 4 傾斜後電流密度分佈圖 (b)垂直橫截面電流密度分佈

圖 13、傾斜垂直平面BEI影像 (a)通直流電前 (b)在  $150^{\circ}$ C 通以  $2 \times 10^{4} \, \text{A/cm}^{2}$  經過 26 hours之後

圖 14、傾斜垂直平面BEI影像 (a)(b)通交流電前 (b)在 150°C 通以 2 X 10<sup>4</sup> A/cm<sup>2</sup> 經過 852.5hours之後

# 討論

第一部分的結果顯示依照以往的文獻,生成hillock或whisker需要有足夠的壓應力,經

由電遷移產生的應力可以在陽極端發現有hillock或whisker生成,而因為電子風力會帶走大量的Cu原子,所以會在晶界的位置分部許多的IMCs,這些IMCs會阻礙Sn原子繼續供給hillock或whisker。

第二部份的結果主要驅動力來自電流密度梯度在通以直流電或交流電電流集中的區域,在直流電通電的結果,發現空孔聚集在電流密度低的位置,然而,通以交流電的結果代替空孔聚集的是表面粗糙,直流電的結果是在陽極端產生hillock,hillock形成的原因鉛相累積在介金屬化合物與SnPb Solder的界面,產生壓應力,進而為了釋放壓應力而產生hillock。

#### 參考文獻

<sup>1</sup>K. N. Tu, A. M. Gusak, and M. Li, J. Appl. Phys., 93, 1335 (2003).

<sup>2</sup>I. A. Blech, Appl. Phys. Lett., **29**, 131 (1976).

<sup>3</sup>H. B. Huntington and A. R. Grone, J. Phys. Chem. Solids, **20**, 76 (1961).

<sup>4</sup>Brook Chao, Seung-Hyun Chae, Xuefeng Zhang, Kuan-Hsun Lu, Jay Im, and P.S. Ho, Acta Materialia, **55**, 2805–2814 (2007).

<sup>5</sup>S. W. Chen and C. H. Wang, J. Mater. Res., **22**, 695-702 (2007).

<sup>6</sup>F. Y. Ouyang, Kai Chen, K. N. Tu, and Yi-Shao Lai, Appl. Phys. Lett., **91**, 231919 (2007).

<sup>7</sup>S. W. Liang, Y. W. Chang, T. L. Shao, Chih Chen, and K. N. Tu, Appl. Phys. Lett., **89**, 022117 (2006).

<sup>8</sup>W.J. Boettinger, C.E. Johnson, L.A. Bendersky, K.-W. Moon, M.E. Williams, and G.R. Stafford, Acta Materialia, **53**, 5033–5050 (2005).

<sup>9</sup>Minhua Lu, Da-Yuan Shih, Paul Lauro, Charles Goldsmith, and Donald W. Henderson, Appl. Phys. Lett., **92**, 211909 (2008).

<sup>10</sup>B. F. Dyson, T. R. Anthony, and D. Turnbull, J. Appl. Phys., **38**, 3408 (1967).

- <sup>11</sup>D. C. Yeh and H. B. Huntington, Phys. Rev. Letter., **53**, 1469 (1984).

- <sup>12</sup>J.S. Kang, R.A. Gagliano, G. Ghosh, and M.E. Fine, J. Electron. Mater., **31**, 1238-1243 (2002).

- <sup>13</sup>T. Kwok, T. Nguyen, P. Ho, and S. Yip, Proceedings of the 25th IEEE International Reliability Physics Symposium, San Diego, California, April 7–9, 130 (1987).

- <sup>14</sup>T. Kwok, T. Nguyen, S. Yip, and P. Ho, Proceedings of the 5th IEEE International VLSI Multilevel Interconnection Conference, Santa Clara, California, June 13–14, 252 (1988).

- <sup>15</sup>J. T. Trattles, A. G. O'Neill, and B. C. Mecrow, IEEE Trans. Electron Devices **40**, 1344 (1993).

- <sup>16</sup>W. J. Choi, E. C. C. Yeh and K. N. Tu, J. Appl. Phys. **94**, 5665 (2003).

- <sup>17</sup>J. W. Hah, K. W. Paik, J. O. Suh and K. N. Tu, J. Appl. Phys. **94**, 7560 (2003).

- <sup>18</sup>Y. H. Hsiao, Y. C. Chuang and C. Y. Liu, Scr. Mater. **54**, 661 (2006).

- <sup>19</sup>C. C. Wei and Chih Chen, Appl. Phys. Lett. **88**, 182105 (2006).

- <sup>20</sup>B. Y. Wu and Y. C. Chan, J. Alloys Compd. **392**, 237 (2005).

- <sup>21</sup>K. N. Tu, C. C. Yeh, C. Y. Liu, and Chih Chen, Appl. Phys. Lett. **76**, 988 (2000).

- <sup>22</sup>C. C. Wei, P. C. Liu, Chih Chen and K. N. Tu, J. Mater. Res. 23, 2017 (2008).

- <sup>23</sup>J. Choi, S. Lee, and Y. Joo, Jpn. J. Appl. Phys., Part 1 **41**, 7487 (2002).

- <sup>24</sup>I. A. Blech, J. Appl. Phys. **47**, 1203 (1976).

- <sup>25</sup>M. C. Gutzwiller, in *Atomic and Electronic Structure of Metals*, edited by J. J. Gilman and W. A. Tiller (American Society for Metals, Metals Park, OH, 1966), Chap. 12.

- <sup>26</sup> A. T. Huang, A. M. Gusak, and K. N. Tu, Appl. Phys. Lett. **88**, 141911 (2006).

- <sup>27</sup>T. Y. Lee, K. N. Tu, and D. R. Frear, J. Appl. Phys. **90**, 4502 (2001).

- <sup>28</sup>C. Y. Liu, C. Chen, C. N. Liao, and K. N. Tu, Appl. Phys. Lett. **75**, 58 (1999).