# 行政院國家科學委員會專題研究計畫 成果報告

奈米 CMOS 之高性能類比數位混合信號關鍵電路設計技術--

子計畫六：用於高密度高速連結系統之矽光電積體電路

研究成果報告(精簡版)

計畫類別：整合型

計畫編號：NSC 97-2221-E-009-176-

執行期間：97 年 08 月 01 日至 98 年 07 月 31 日

執行單位：國立交通大學電子工程學系及電子研究所

計畫主持人：陳巍仁

計畫參與人員：

碩士班研究生-兼任助理人員：張巧伶

碩士班研究生-兼任助理人員：楊松諭

碩士班研究生-兼任助理人員：黃世豪

碩士班研究生-兼任助理人員：黃文杰

碩士班研究生-兼任助理人員：黃健軒

碩士班研究生-兼任助理人員：賴炯為

碩士班研究生-兼任助理人員：陳曼毅

碩士班研究生-兼任助理人員：莊書瑾

碩士班研究生-兼任助理人員：楊川逸

博士班研究生-兼任助理人員：盧台祐

處理方式：本計畫可公開查詢

中華民國 99 年 01 月 06 日

行政院國家科學委員會補助專題研究計畫

■ 成果報告

□期中進度報告

奈米 CMOS 之高性能類比數位混合信號關鍵電路設計技術

子計畫六—用於高密度高速連結系統之矽光電積體電路

計畫類別： 個別型計畫      ■ 整合型計畫

計畫編號： NSC 98-2221-E-009-134-

執行期間： 97 年 08 月 01 日至 98 年 07 月 31 日

計畫主持人：陳巍仁 教授

共同主持人：

計畫參與人員：黃世豪、劉晟佑、吳宗恩、李彥緯、陳育祥、周順天、許世昕、

黃文杰

成果報告類型(依經費核定清單規定繳交)： 精簡報告     完整報告

本成果報告包括以下應繳交之附件：

- 赴國外出差或研習心得報告一份

- 赴大陸地區出差或研習心得報告一份

- 出席國際學術會議心得報告及發表之論文各一份

- 國際合作研究計畫國外研究報告書一份

處理方式：除產學合作研究計畫、提升產業技術及人才培育研究計畫、列管計畫及下列情形者外，得立即公開查詢

■ 涉及專利或其他智慧財產權， 一年 ■ 二年後可公開查詢

執行單位：國立交通大學電子研究所

中 華 民 國 98 年 10 月 20 日

## 可供推廣之研發成果資料表

可申請專利

可技術移轉

日期：98 年 10 月 20 日

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>國科會補助計畫</b><br><br><b>技術/創作名稱</b><br><br><b>發明人/創作人</b> | <p>計畫名稱：用於高密度高速連結系統之矽光電積體電路<br/>         計畫主持人：陳巍仁<br/>         計畫編號：NSC 98-2221-E-009-134-<br/>         學門領域：微電子</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>技術說明</b>                                                | <p>中文：本計劃完成一個 10 Gbps 且整合光感測器之光接收機。其中轉阻放大器結合巢狀回授及串聯共振技術，以達到高速操作之目的。光感測器採用二維對稱結構以提升頻率響應。本接收機提供 25 k 增益以推動外接 50 負載。其速度為傳統架構三倍。晶片面積為 0.95 mm x 0.8 mm。操作於 1.8 V 之下，接收機共消耗 118 mW。</p> <p>英文：A 10-Gbps optical receiver with monolithically integrated photo detector is implemented in generic 0.18- μm CMOS technology. A transimpedance amplifier with nested feedback and shunt-peaking is proposed for broad-band and high gain operations. Incorporating a 2-D meshed spatially-modulated light detector, the optical receiver is capable of delivering 25 k transimpedance gain when driving output loads of 50 . The operating speed is improved by 3X over the prior art with the same technology. The chip size is 0.95 mm x 0.8 mm. This receiver core drains 118 mW from 1.8 V supply.</p> |

| <b>可利用之產業<br/>及<br/>可開發之產品</b>                             | 光連結系統                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>技術特點</b>                                                | <ol style="list-style-type: none"> <li>1. 整合 CMOS 光感測器</li> <li>2. 為目前單晶片最高速度</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>推廣及運用的價值</b>                                            | 降低系統成本<br>提升速度                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

- ※ 1. 每項研發成果請填寫一式二份，一份隨成果報告送繳本會，一份送 貴單位研發成果推廣單位（如技術移轉中心）。

- ※ 2. 本項研發成果若尚未申請專利，請勿揭露可申請專利之主要內容。

- ※ 3. 本表若不敷使用，請自行影印使用。

# 奈米 CMOS 之高性能類比數位混合信號關鍵電路設計技術— 子計畫六：用於高密度高速連結系統之矽光電積體電路

## Multi-channel Optical Link Transceiver in Nanometer CMOS Technology

計畫編號：NSC 98-2221-E-009-134-

執行期限：97 年 08 月 01 日至 98 年 07 月 31 日

主持人：陳巍仁教授 國立交通大學電子研究所

### 一、中文摘要

本子計畫之重點為利用奈米標準 CMOS 技術設計一極高速之光電收發機積體電路，用於高密度光連結系統。透過多模式光纖 (multimode fiber) 與低電壓、低電流驅動之 VCSEL 雷射二極體，以符合未來的光連結系統之需求，並完成低成本、高速與高度整合之目標。為達此一高傳輸速率，主要需克服之設計挑戰包含：雷射二極體 (VCSEL) 之速度極限、多模式光纖之頻寬極限與色散所造成之符元干擾 (ISI) 效應、極高速、低電壓與低電流之混合信號積體電路之設計需求等。

本計畫初期之研究內容將包含高速雷射驅動電路、光接收機電路與高速混合信號前饋式 (FFE) 與迴授式 (DFE) 等化器技術。此整合型計畫之子計畫六已完整的執行完 3-Gbps 雷射驅動電路與 10-Gbps 光接收機電路，由實際晶片驗證並與模擬結果獲得相互的佐證並且獲得預期的研究結果，而且在等化器的部份也已經完成 10-Gbps 的電路模擬。

### Abstract

The goal of the first year project is to develop the ultra-high speed optical-electronics integration benches by using nano-meter standard CMOS technique. In order to comply with the bandwidth demands of hundreds Gbps computing system in the future, the target specifications are to develop transceiver ICs over multi-mode fibers, and through modulating a low voltage, and low current VCSEL. Low cost, ultra-high speed, and highly integrated solutions can be accomplished by

solving the major design issues such as speed limitation of VCSEL, bandwidth limitations of multi-mode fiber, dispersion induced inter symbol interference, and the challenges of ultra high speed, low voltage and low current mixed-signal IC designs, etc.

To achieve this goal, this project will aim at the design of VCSEL driver, optical receiver and high speed mixed-mode feed-forward (FFE) and decision feedback equalizer (DFE). In this project, a 3-Gbps VCSEL driver and 10-Gbps fully CMOS optical receiver have been proposed and implemented. Besides, the equalizers have been proposed to overcome the limitation of channel bandwidth and degradation of device bandwidth.

### 二、計畫的緣由與目的

在這個科技日新月異的時代，隨著時脈頻率與傳輸速率的需求不斷提高，傳統使用電性連接的方式將面臨系統同步、阻抗匹配、電感效應等問題；因此若使用光連接方式，將可改善晶片之間與電路板之間的傳輸速率。光通訊系統的優點包括：體積小、不易受到外界電磁干擾、且光纖頻寬大。

傳統使用昂貴的三五族材料，如砷化鎵 (GaAs) 等來製備，雖然擁有較佳的特性，但其在與 CMOS 積體電路整合時，將需要複合技術與額外的功率消耗；因此，本計畫在所有電路與感測器方面，完全使用 CMOS 技術，將可方便於系統整合，達到效能提升與低功率消耗，更因低價的標準 CMOS 製程達到低製程成本。

### 三、研究方法及成果

本計劃的內容包括了：雷射二極體驅動電路、矽光電接收機電路、可調增益放大器與等化器電路，以下將依序介紹每個電路架構。而本計畫的研究成果已經整理且發表了數篇論文，包括：國際期刊、國際研討會論文與國內研討會論文。

### (1) 雷射二極體驅動電路[1]-[3]

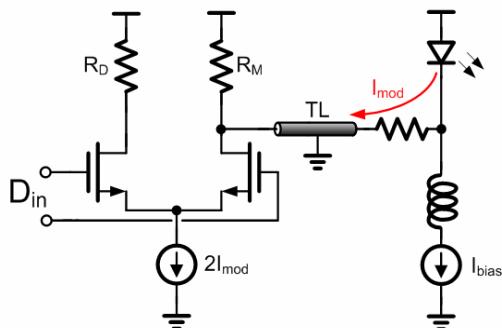

為解決雷射二極體驅動電路輸出級在高速操作下所面臨的阻抗匹配，傳統的方法是雷射二極體驅動電路輸出端採用被動性負載來匹配傳輸線特性阻抗，如圖一所示， $R_M$ 為匹配傳輸線阻抗之電阻，當傳輸線終端與負載阻抗不匹配產生反射返回驅動電路輸出級時，反射波會

圖一. 傳統的被動性負載之雷射二極體驅動電路。

被 $R_M$ 所吸收，但是輸出的調變電流會消耗一半於 $R_M$ 上，因此要達到同樣的光輸出功率，輸出級之調變電流源必須至少為兩倍 $I_{mod}$ ，以消耗功率的觀點來看是非常沒有效率的。因此，本計劃提出利用主動性元件作為負載，來取代被動性負載的雷射二極體驅動電路，除了有作為阻抗匹配的功能之外，相較於傳統採用被動性負載的雷射二極體驅動電路，它能減少驅動電路功率消耗。

雷射二極體其發光的功率大小，是由電流大小來決定，可將雷射二極體輸出光功率代表數位訊號一和數位訊號零，為了能於有限頻寬內傳送更多的資料，於此利用脈衝振幅調變(PAM)的方式，將欲傳送的資料先進行調變，將流過雷射二極體的電流振幅劃分成四種不同大小的振幅，其中每種振幅大小分別代表兩個位元的資料，如此可達到總資料傳送量為頻寬的兩倍。編碼上在此使用葛雷碼(Gray Code)，每一等份的振幅變化只改變一個位元，如此一來可降低誤碼率(BER)。

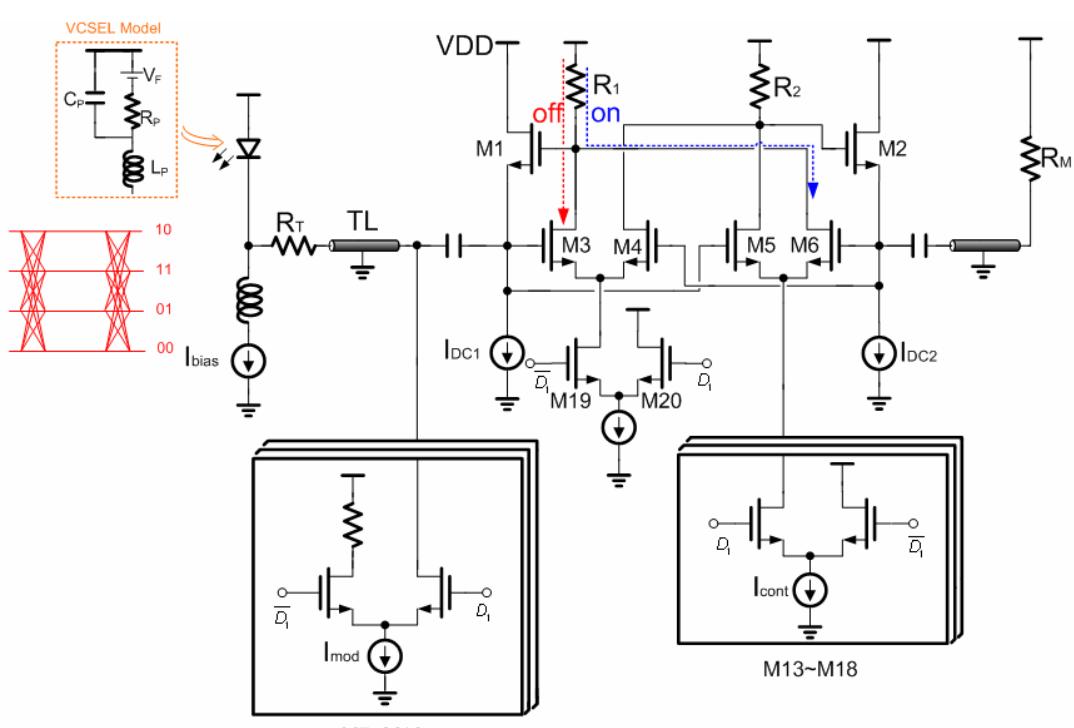

所提出之雷射驅動電路如圖二所示，由Ibias定義最低的光輸出功率，再加上額外的三組同樣大小電流源的輸出級(M7~M12)，來產生4 PAM的光輸出波形，使用M1及由M3~M6的Gilbert Cell組態達到主動式阻抗匹配的功能。當

圖二. 所提出之用於4-PAM主動負載雷射二極體驅動電路。

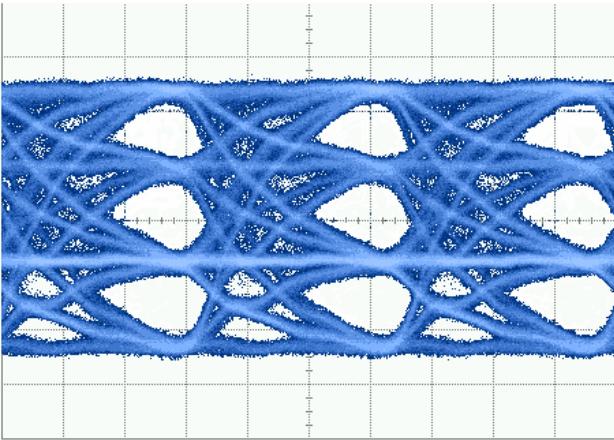

圖三. 光信號量測眼圖(4-PAM 3-Gbps)。

有調變電流輸出時，會在輸出端及M1的源極端有電壓變化，藉由M3~M6及M13~M18的控制電路在M1的閘極產生同樣大小、相同相位的電壓變化，如此輸出級的調變電流可完全傳送至負載的雷射二極體，當沒有調變電流輸出時，M1、M3及R<sub>1</sub>形成Regulated Cascode的架構可以作為阻抗匹配，在此設計中主動是阻抗匹配是由M1的輸出阻抗再除上一迴路增益，因此不須給予大直流偏壓即可完成較低特性阻抗的阻抗匹配。

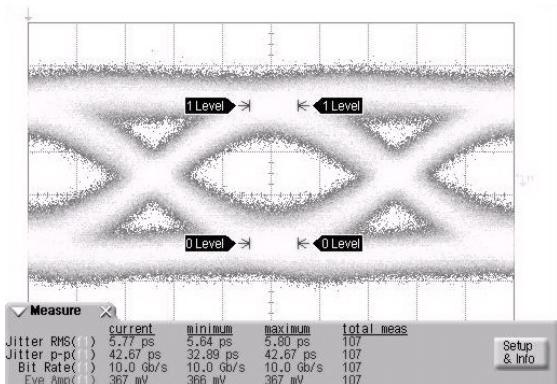

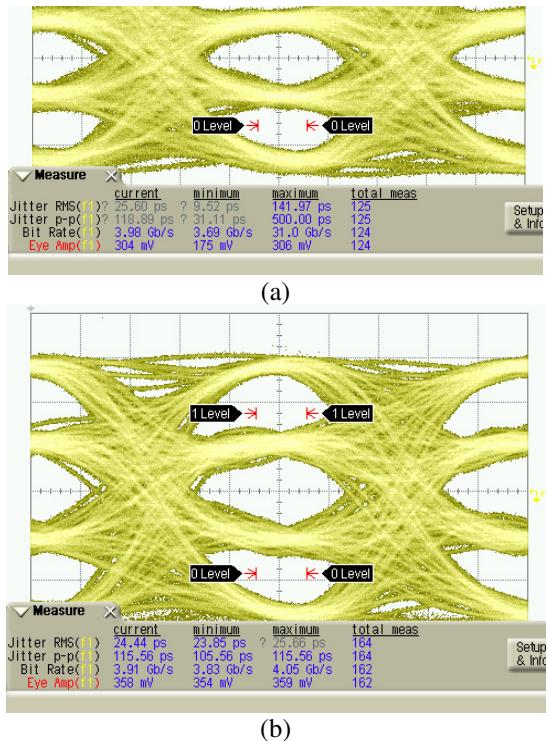

我們所實現的雷射二極體驅動電路以0.18  $\mu\text{m}$  CMOS的製程來完成設計，在1.8 V的操作電壓下，量測到的資料傳輸速率為4 Gbps；功率消耗約為200 mW；晶片大小為 $1600 \times 800 \mu\text{m}^2$ 。所設計的輸出級在調變電流為10mA的條件下只多消耗了9.72mW，相較於用電阻當阻抗匹配的輸出級，省下約23%的功率消耗。圖三為量測到操作於3-Gbps的速度下的4-PAM眼圖。

## (2) 砂光電接收機電路

低價高整合的CMOS製程下，高性能的光感測器已越來越受重視。在製程的條件下，無法對不同波長的入射光去做最佳化，因此會有較低的響應度及較慢的暫態響應。為了解決這些問題，很多方法被提出：有的使用SOI的基板[4]或是BiCMOS[5]去製作光感測元件，但是他們使用的是比較昂貴的製程；為了使用CMOS來減低費用，有利用N-well[6]或是DNW[7]來隔絕慢速的p-sub擴散電流，但是其光二極體因為用到高濃度的參雜，造成寄生電容大；因此

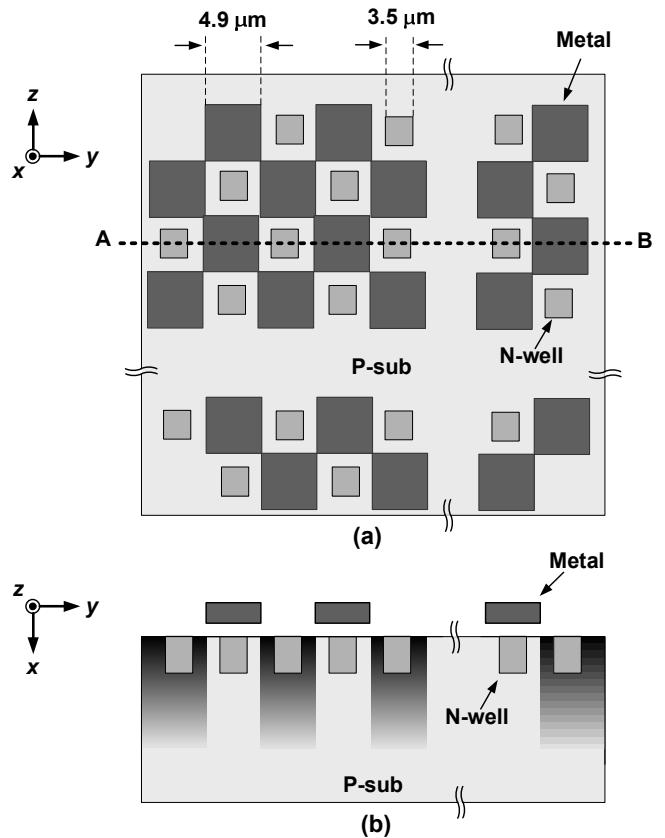

圖四. 所提出之 meshed SMPD (a)府視圖，(b)側視圖。

有利用SML[8]-[12]來製作感測元件，以求低寄生電容與高頻寬，然而傳統的條狀SMPD -3dB頻寬只有0.85 GHz而已，對於數Gbps的操作仍有難度。

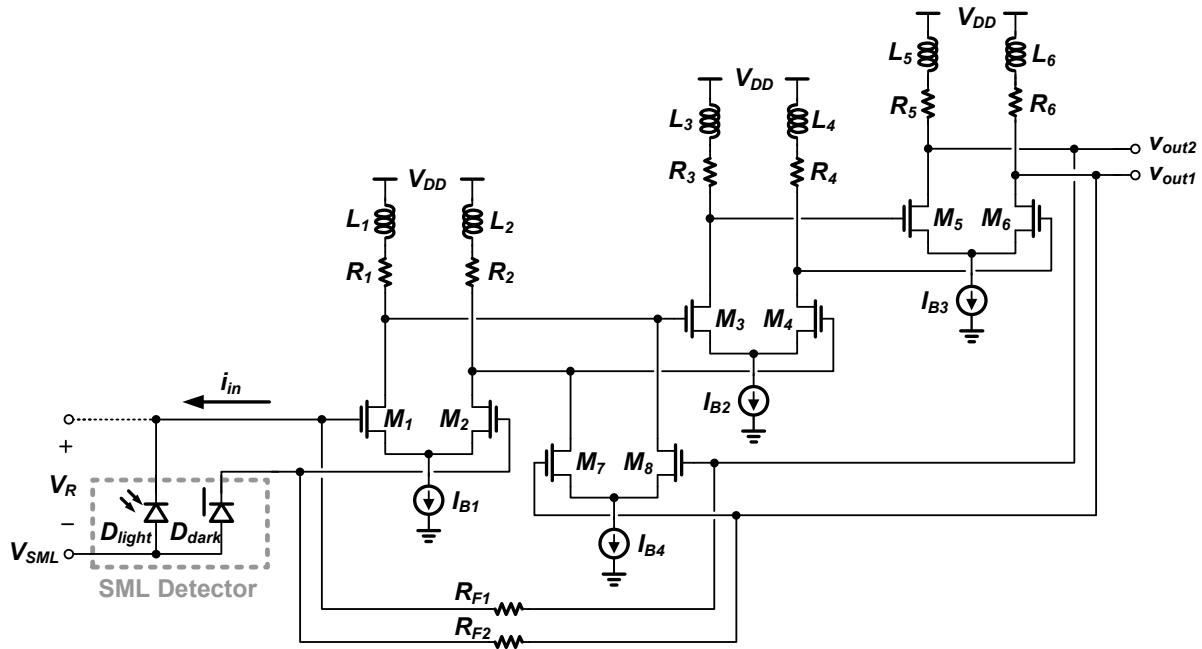

本計劃提出利用meshed SMPD的架構，如圖四所示。相較於傳統的stripe SMPD，所提出的光感測器因為慢速擴散電流較平均的吸收掉，留下更純的快速漂移電流，所以其擁有更高的頻寬。在逆偏壓-14.2V的情況下，可以量測到6.9 GHz的-3dB頻寬，用來操作於10 Gbps的資料速度。為了解決SMPD低響影度的問題，本計劃提出的一個巢狀回授的TIA電路，如圖五所示。該TIA搭配所設計的LA電路，其擁有極低的輸入等效電流雜訊：對於響應度是0.85A/W的商用光感測器而言，可以量測到輸入靈敏度有-19dBm；對於所提出的meshed SMPD靈敏度是0.03A/W，量測到的輸入靈敏度大約是-6dBm。圖六是本計劃之矽光電接收機所量測到的10-Gbps眼圖，其輸入的光功率為-6 dBm。

圖五. 本計劃所提出之轉阻放大器電路圖。

圖六. 所量測到OEIC之10-Gbps眼圖。

圖七. 自動增益控制電路。

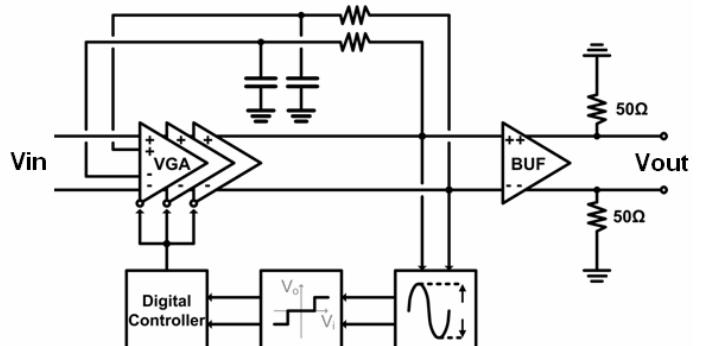

### (3) 用於4PAM之自動增益控制放大器[13]-[17]

本計劃提出一個無電感下資料傳輸速率達8Gbps，以數位方式控制增益的自動增益控制系統，系統如圖七所示。內含之可調增益放大器之部份，提出巢狀主動回授架構來增加傳輸頻寬，且使其轉移函式符合貝索濾波器響應，以減少群體延遲變異量。

若視核心 Cherry-Hooper 放大器為二階轉移函式，而輸入以及回授轉導級為單零點系統，則整體 VGA 系統轉移函式可堆導成為：

$$V_{out} \approx \frac{R_{sf}}{R_{si}} \cdot \frac{\frac{(1+\frac{s}{\omega_{zi}})}{(1+\frac{s}{\omega_{zf}})+\frac{1}{A'} \cdot (1+\frac{s}{\omega_{px}})(1+\frac{2\zeta}{\omega_n}s+\frac{s^2}{\omega_n^2})}} \quad (1)$$

其中  $R_{si}$ 、 $R_{sf}$ 、 $\omega_{zi}$ 、 $\omega_{zf}$  分別代表輸入以及回授級的源級退化阻值與其產生的零點， $\omega_{px}$  為回授節點形成的極點， $\delta$  與  $\omega_n$  為二階 Cherry-Hooper 放大器的 damping factor 與 natural frequency， $A'$  為這些因子所形成的變異量。

再利用數位電路實現具有【二分搜尋/線性搜尋】雙模式的增益控制電路達到快速鎖定、長時穩定的設計考量。電壓偵測器中利用數位電路設置了開關機制來減少重置時間以及趨穩時間；比較器亦使其具有遲滯效應，避免雜訊干

圖十二. 決策回饋等化器(DFE)。

圖九. 晶片量測 8-Gbps 之 4-PAM 眼圖。(a) VGA 的增益是 15dB 的狀況下；(b) VGA 的增益是 6dB 的狀況下，輸出電壓擺幅大約都是 400 mVpp。

擾以及增益調整解析度的有限造成電路不穩。

測試晶片使用標準  $0.18\mu\text{m}$  CMOS 製程來製造。在  $1.8\text{ V}$  的操作電壓之下，量測的資料傳輸速率可達  $8\text{ Gbps}$ ，輸入動態範圍為  $22\text{ dB}$ ，二分搜尋鎖定時間為  $170\text{ ns}$ ；在 24 位元溫度計碼的

圖十一. 前饋等化器(FFE)。

控制之下，增益控制解析度可達  $0.9\text{ dB/bit}$ ；電路晶片如圖八所示，面積大小為  $620 \times 620\mu\text{m}^2$ ，功率消耗為  $86.4\text{ mW}$ 。

圖九是量測到的 4-PAM 眼圖，速度為  $8\text{ Gbps}$  的情況下，在不同的輸入電壓下，輸出均是  $400\text{ mVpp}$ 。圖十是輸出電壓對於不同輸入電壓的量測圖，數位增益控制電路部份舉有雙模機制，利用二分搜尋法能在  $170\text{ ns}$  內調整到適當的輸出振幅準位，並且和增益大小無關。

#### (4) 等化器之技術

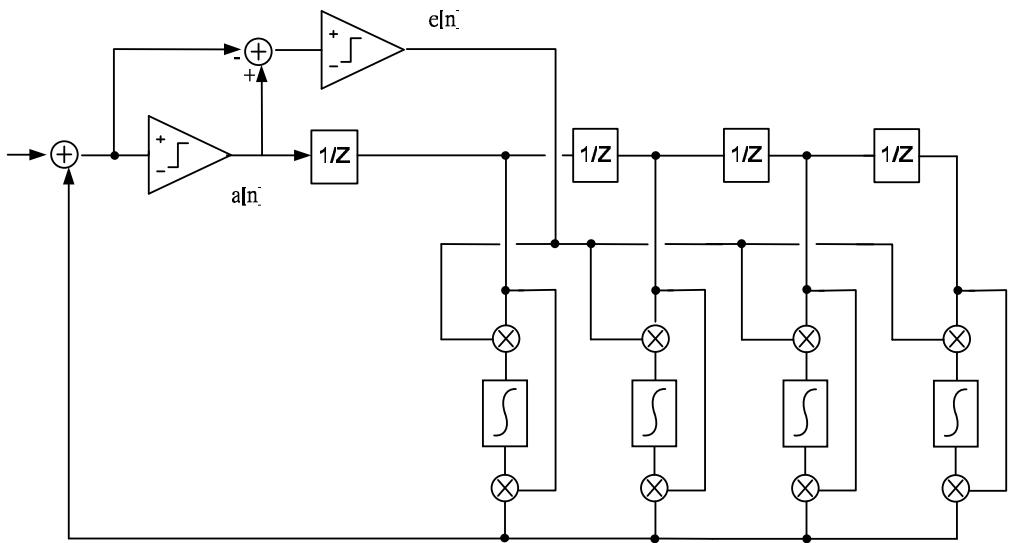

高速訊號經過通道之後會產生符元性干擾失真 ISI，使得前後 bit 互相影響導致眼圖張不開。其中 ISI 可細分為 pre-cursor 與 post-cursor 兩部分。本等化器架構包含了前饋等化器(FFE)與決策回饋等化器(DFE)，前饋等化器用來解決 pre-cursor 的問題，而決策回饋等化器則是用來解決 post-cursor 的問題。訊號先通過前饋等化器後再通過決策回饋等化器，可等化經由通道產生的符元性干擾，使眼圖打開。

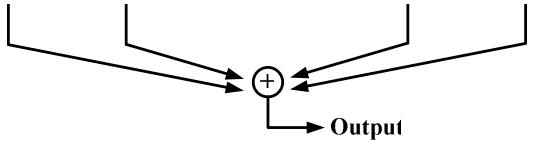

前饋等化器架構如圖十一所示可視為一可

調增益的濾波器，使用被動元件來實現架構中的 delay，將輸入經過 delay 乘上權重後相加可得輸出，適當的調整權重後可消去訊號 pre-cursor 的效應。

決策回饋等化器使用 sign-sign LMS 演算法實現，以解決 post-cursor 的問題。sign-sign LMS 演算法如下式所示，輸出是經由權重乘上各個 tap 的決策值之後相加所得：

$$y[n] = \sum_{i=0}^{N-1} W_i[n] \cdot a[n-i]$$

而更新權重的式子如下：

$$W_i[n+1] = W_i[n] + \mu \cdot e[n] \cdot a[n-i]$$

其中  $W_i[n]$  為第  $i$  個 tap 的權重。 $\mu$  為 step size。

依上述演算法，實做架構如圖十二所示，將接收到的訊號經過比較器量化出二位元訊號  $a[n]$  為決策值，此決策值經過 delay 可得到  $a[n-i]$ 。將之與積分器內存值  $W_i[n]$  相乘後 feedback 回來相加，此值即是前幾個 bit 對現在需決策的 bit 所造成影響，將之與 input 相加可消去 post-cursor 所帶來的影響。此外為了更新  $W_i[n]$  需要誤差值，此值可由取量化前後的結果輸入另一個比較器得到，輸入比較器的目的為將誤差量化為另一個二位元訊號  $e[n]$ ，即可由上式 2 更新  $W_i[n]$ 。

#### 四、結論與討論

此整合型計畫之子計畫六已完整的執行完畢，由實際晶片驗證並與模擬結果獲得相互的佐證並且獲得預期的研究結果。更詳細的研究成果內容，敬請參閱本研究群所發表之論文。

本計劃的主持人與其執行團隊對於國科會在研究計畫經費支持，表示非常感謝。

#### 五、計劃成果

[1] Song-Yu Yang, Wei-Zen Chen, and Tai-You Lu, "A 7.1mW, 10GHz All Digital Frequency Synthesizer with Dynamically Reconfigured Digital Loop Filter in 90nm CMOS Technology", IEEE Journal of Solid-State Circuits, accepted for publication.

[2] Wei-Zen Chen, Ruei-Ming Gan, and Shih-Hao Huang, "A Single Chip 2.5 Gbps CMOS Burst Mode Optical Receiver", IEEE Transactions on Circuits and Systems-(I), vol. 56, NO. 10, pp. 2325-2331, Oct., 2009.

[3] Song-Yu Yang and Wei-Zen Chen, " A 7.1 mW, 10-GHz All Digital Frequency Synthesizer with Dynamically Reconfigured Digital Loop Filter in 90 nm CMOS Technology", 2009 IEEE International Solid-State Circuits Conference Dig. of Tech. Papers, pp. 90-91.

[4] Wei-Zen Chen and Shih-Hao Huang, " A 10-Gbps CMOS Single Chip Optical Receiver with 2-D Meshed Spatially-Modulated Light Detector", 2009 IEEE Custom Integrated Circuit Conference, September, 2009.

[5] Guo-Wei Wu, Wei-Zen Chen, and Shih-Hao Huang, " An 8 Gbps Fast-Locked Automatic Gain Control for PAM Receiver,", 2008 IEEE Asian Solid-State Circuits Conference, Nov. 2009.

[6] 2009 中國工程師學會青年論文獎（黃世豪）

[7] 2009 Electronic Technology Symposium 最佳論文獎（黃世豪）

[8] 國科會晶片設計製作中心 (CIC) 2009 特別設計獎（楊松諭）

#### 六、參考文獻

- [1] H. Ransijn, G. Salvador, D. D. Daugherty, and K. D Gaynor, "A 10-Gb/s Laser/Modulator Driver IC with a Dual-Mode Actively Matched Output Buffer," *IEEE J. Solid-State Circuits*, vol. 36, no. 9, pp. 1314-1320, Sept. 2001.

- [2] R. Farjad-Rad, C.-K Ken Yang, M. Horowitz, and T. Lee. "A 0.4μm CMOS 10 Gb/s 4-PAM Pre-Emphasis Serial Link Transmitter," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 580-585, May 1999.

- [3] C.-H. Lin and S.-J. Jou "A 4/2 PAM Pre-emphasis Transmitter with Combined," ASSCC, pp. 189-192, Nov. 2005.

- [4] S.M. Csutak, et al., "High-speed monolithically integrated silicon photoreceivers fabricated in 130-nm CMOS technology," *IEEE Photonics Technology Letters*, pp. 516-518, Apr. 2002.

- [5] R. Swoboda, et al., "11Gb/s Monolithically Integrated Silicon Optical Receiver for 850nm Wavelength," *IEEE ISSCC Dig. Tech. Paper*, pp. 904-911, Feb. 2006.

- [6] T. Woodward, et al., "1-Gb/s integrated optical detectoprs and receivers in commercial CMOS technologies," *IEEE Journal of Selected Topics in Quantum Electronics*, pp.146-156, Mar./Apr. 1999.

- [7] W.-Z. Chen, et al., " A 2.5 Gbps CMOS Fully Integrated Optical Receiver with Lateral PIN Detector," *IEEE CICC*, pp. 293-296, Sep. 2007.

- [8] C. Rooman, et al, "Asynchronous 250 Mb/s Optical Receivers with Integrated Detector in Standard CMOS Technology," *IEEE JSSC*, pp. 953-958, Jul. 2000.

- [9] M. Jutzi, et al., "2-Gb/s CMOS Optical Integrated Receiver with a Spatially Modulated Photodetector," *IEEE Photonics Technology Letters*, pp. 1268-1270, Jun. 2005.

- [10] C. Hermans, et al., "A High-Speed 850-nm Optical Receiver Front-end in 0.18- $\mu$ m CMOS," *IEEE JSSC*, pp. 1606-1614, Jul. 2007.

- [11] W.-Z. Chen, et al., " A 3.125 Gbps CMOS Fully Integrated Optical Receiver with Adaptive Analog Equalizer," *IEEE A-SSCC*, pp. 396-399, Nov. 2007.

- [12] F. Tavernier, et al., "Power Effeciency 4.5Gbit/s Optical Receiver in 130nm CMOS with Integrated Photodiode," *IEEE ESSCIRC*, pp. 162-165, Sep. 2008.

- [13] S. Radovanović, A.J. Annema, and B. Nauta, "A 3-Gb/s Optical Receiver Front-end in 0.18 $\mu$ m CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 8, pp. 1706-1717, Aug. 2005.

- [14] T. Ridder, P. Ossieur, B. Baekelandt, C. Mélange, J. Bauwelinck, C. Ford, X. Z. Qiu, and J. Vandewege, "A 2.7V 9.8Gb/s Burst-Mode TIA with Fast Automatic Gain Locking and Coarse Threshold Extraction," *IEEE ISSCC Dig. Tech. Papers*, pp. 220-221, Feb. 2008.

- [15] J. M. Khouri, "On the design of constant settling time AGC circuits," *IEEE Transactions on Circuits and Systems (II)*, vol. 45, pp. 283 – 294, Mar. 1998.

- [16] W.-Z. Chen, R.-M. Gan, and S.-H. Huang, "A Single Chip 2.5 Gbps CMOS Burst Mode Optical Receiver", *IEEE Transactions on Circuits and Systems (I)*, Oct. 2009.

- [17] C.-F. Liao and S.-I. Liu, "A 10Gb/s CMOS AGC Amplifier with 35dB Dynamic Range for 10Gb Ethernet," *IEEE ISSCC Dig. Tech. Papers*, pp. 2092–2101, Feb. 2006.