Dual-metal-gate-integration complementary metal oxide semiconductor process scheme using Ru positive-channel metal oxide semiconductor and TaC negative-channel metal oxide semiconductor gate electrodes

Wen-Tung Chang, Tsung-Eong Hsieh, and Chung-Ju Lee

Citation: Journal of Vacuum Science & Technology B 25, 1265 (2007); doi: 10.1116/1.2752516

View online: http://dx.doi.org/10.1116/1.2752516

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvstb/25/4?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

# Articles you may be interested in

Fabrication of complementary metal-oxide-semiconductor integrated nanomechanical devices by ion beam patterning

J. Vac. Sci. Technol. B 27, 2691 (2009); 10.1116/1.3253550

Etching of TiN-based gates for advanced complementary metal-oxide-semiconductor devices

J. Vac. Sci. Technol. B 26, 1440 (2008); 10.1116/1.2953732

Dry etching of amorphous-Si gates for deep sub-100 nm silicon-on-insulator complementary metal—oxide semiconductor

J. Vac. Sci. Technol. B 20, 191 (2002); 10.1116/1.1431953

Application of 4-methyl-1-acetoxycalix[6]arene resist to complementary metal-oxide-semiconductor gate processing

J. Vac. Sci. Technol. B 17, 3394 (1999); 10.1116/1.591017

Germanium etching in high density plasmas for 0.18 m complementary metal–oxide–semiconductor gate patterning applications

J. Vac. Sci. Technol. B 16, 1833 (1998); 10.1116/1.590094

# Re-register for Table of Content Alerts

Create a profile.

Sign up today!

# Dual-metal-gate-integration complementary metal oxide semiconductor process scheme using Ru positive-channel metal oxide semiconductor and TaC negative-channel metal oxide semiconductor gate electrodes

Wen-Tung Chang and Tsung-Eong Hsieh<sup>a)</sup>

Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu, Taiwan 30010, Republic of China

Chung-Ju Lee

United Microelectronics Corporation (UMC), Hsinchu, Taiwan 30010, Republic of China

(Received 21 November 2006; accepted 30 May 2007; published 6 July 2007)

This article presents the development of a wet removal process on the integration of complementary metal oxide semiconductor (CMOS) dual metals with Ru for positive-channel metal oxide semiconductor and TaC for negative-channel metal oxide semiconductor on high-k HfO $_2$  gate dielectric. The integration scheme focused on the wet etching capability for the first metal and the selectivity control on the high-k dielectrics under the metal gate. Using the developed chemical, ceric ammonium nitrate and nitric acid mixture used for Ru metal removal and HfO $_2$  treated with Ar/O $_2$  plasma by selective diluted hydrofluoric wet etching, a CMOS dual-metal-gate structure was achieved with satisfactory device fabrication.

© 2007 American Vacuum Society. [DOI: 10.1116/1.2752516]

### I. INTRODUCTION

The complementary metal oxide semiconductor (CMOS) dual-metal-gate process on bulk Si with two metal gate materials using a gate-first approach is the main stream of present integration methodology. The candidate metals for both positive-channel metal oxide semiconductor (PMOS) and negative-channel metal oxide semiconductor (NMOS) rely on a proper integration scheme to implement on the Si wafer. According to the International Roadmap for Semiconductors, the introduction of high dielectric constant (high-k) gate materials and dual-metal-gate electrodes with appropriate work functions is demanded in the near future to reduce the gate direct tunneling leakage current<sup>2-6</sup> and to eliminate boron (B) penetration and polydepletion effect when the device scaling down is below 65 nm. In order to optimize the threshold voltage  $(V_t)$  in high performance devices, a metal gate with tunable work function, about 4.1-4.6 eV for NMOS and about 4.8-5.1 eV for PMOS devices, is required for advanced transistor structures such as fin field effect transistors or ultrathin-body metal oxide semiconductor field effect transistors. 7-9 Several approaches have been proposed, including a full silicided (FUSI) metal gate, 10-13 a midgap metal gate, and dual metal gates in CMOS integration. 14-21 FUSI is an extension of self-aligned silicide technology that has been widely used in CMOS devices. In a FUSI process, the poly-Si gate is totally silicided with the metal. The major advantage of the FUSI method is a CMOS compatible process integration. Among common silicides reported, NiSi FUSI has been demonstrated to have the best work function tunability and stable silicide/gate oxide interface. However, NiSi has the poorest thermal stability

and thermal treatment prior to silicidation process results in the incomplete elimination of boron penetration in *p*-channel device. Since the work function of the metal salicide cannot be modulated, a straightforward dual metal gate on the high-*k* dielectric CMOS process is hence proposed for N+-and P+-like gates in the 90 nm node or below. A versatile integration scheme has been developed which employs a wet etch process to remove the first metal selectively before depositing the second metal. Zhang *et al.* reported TaSiN (NMOS) and Ru (PMOS) on HfO<sub>2</sub>, utilizing a TaSiN wet etch then following a dual-metal-gate dry etching process to fabricate the 85 nm devices. Lu *et al.* and Samavedam *et al.* demonstrated Ti (NMOS), Mo (PMOS), TaSiN (NMOS), TiN (PMOS) dual-metal-gate integration on Si<sub>3</sub>N<sub>4</sub>, and HfO<sub>2</sub> gate dielectrics via the wet etching process, respectively. 18,19

The semiconductor industry is feverishly investigating high-*k* materials with a low equivalent oxide thickness (EOT) for the gate stack to replace SiO<sub>2</sub> or SiON due to unacceptable leakage current when EOT is further scaled down. At present, the dielectric films based on hafnium oxides such as HfO<sub>2</sub>, HfAlO, HfSiO, HfON, and HfSiON are the leading contenders. There are also integration issues as depositing thin stoichiometric layers with acceptable electrical properties and then removing the high-*k* gate oxide without damaging the source and drain areas. Recently, plasma etching on HfO<sub>2</sub> gate dielectric was investigated<sup>23,24</sup> and ion implantation was found to enhance wet chemical etching of HfO<sub>2</sub>. However, further study is required on the etch selectivity of HfO<sub>2</sub> over Si substrate for the integrated process control.

In this article, we demonstrate a dual-metal-gate CMOS flow with Ru (PMOS) and TaC (NMOS) on HfO<sub>2</sub>. This flow utilizes a Ru wet etching process that is highly selective to high-k dielectric and a post-dual-metal-gate dry etching stop

a) Author to whom correspondence should be addressed; electronic mail: tehsieh@cc.nctu.edu.tw

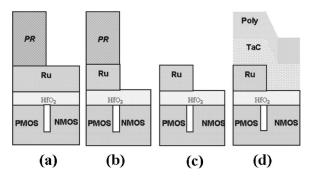

Fig. 1. CMOS dual-metal-gate fabrication integrates process flow: (a) NMOS define with photoresist, (b) first metal wet etch, (c) photoresist strip, and (d) second metal and polydeposition.

on HfO<sub>2</sub>, then with Ar/O<sub>2</sub> plasma treatment and diluted hydrofluoric (HF) ( $H_2O:49\%$  HF=100:1) (DHF) wet etching process to subsequently remove the high-k dielectric to fabricate the 75 nm devices. The etching characteristics of the HfO<sub>2</sub> film with inductively coupled plasma based on the mechanism of ion energetic reactions and ion bombardment in Ar/O<sub>2</sub> were studied. Etching behaviors of various HfO<sub>2</sub> films in DHF solution were also investigated.

# II. EXPERIMENTAL DETAILS

A metal wet etching module shown in Fig. 1 was incorporated into the conventional CMOS flow to fabricate Ru and TaC dual-metal-gate CMOS transistors. The high-k HfO<sub>2</sub> dielectrics about 2 nm thick was deposited first by atomic layer chemical vapor deposition at 350-400 °C then annealed in N<sub>2</sub> ambient at 700 °C, followed by physical vapor deposition (PVD) of about 10 nm the first metal (Ru) for PMOS transistor electrode. A mask was used to define the PMOS then patterned with *I*-line (365 nm) photoresist which served as a protection layer at the PMOS area during the first metal wet removal. A solution containing ceric ammonium nitrate ((NH<sub>4</sub>)<sub>2</sub>Ce(NO<sub>3</sub>)<sub>6</sub>) and nitric acid (HNO<sub>3</sub>) mixture was applied for Ru metal to selectively remove from the NMOS area without damaging the photoresist and the highk underlayer. The photoresist was then removed by amine base chemistry. Afterwards, the second metal (TaC) was deposited by PVD process, followed with a 150 nm polycapped with a tetraethoxysilane (TEOS) hard mask deposition. ArF (193 nm) photoresist was used to define the 75 nm gate length. The chlorine (Cl<sub>2</sub>) based chemistry was used for the TaC metal film etching, followed with an oxygen  $(O_2)$ based chemistry for the Ru film etching in a Lam etcher TCP-9400. During the Ru dry etching process, the HfO<sub>2</sub> layer served as an etching stop to control the NMOS/PMOS

TABLE I. Selectivity control of chemicals for Ru wet removal.

| Wet etching solution            | Ru etching rate (nm/min) | HfO <sub>2</sub> etching rate (nm/min) |

|---------------------------------|--------------------------|----------------------------------------|

| $(NH_4)_2Ce(NO_3)_6:HNO_3=6:1$  | 70                       | 0.06                                   |

| $(NH_4)_2Ce(NO_3)_6:HNO_3=50:1$ | 20                       | 0.007                                  |

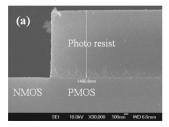

Fig. 2. SEM observation of photoresist removed by solvent: (a) before photoresist removal and (b) after photoresist removal.

area loading. A subsequent DHF wet etching solution was used to remove the high-*k* dielectric with minimum Si substrate loss to achieve the device requirement.

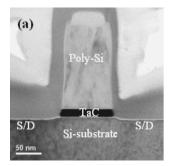

To characterize the dual metal gate on the high-k dielectric gate structure, the stoichiometry, texture, phase, and etching rate of Ru on HfO<sub>2</sub> were examined by x-ray photoelectron spectroscopy (XPS, VG Microlab-350), x-ray diffraction (XRD, PANalytical X'pert Pro-MRD) with Cu  $K_{\alpha}$  radiation, scanning electron microscopy (SEM, JEOL 6700F) operating at 10 keV, and transmission electron microscope (TEM, Philips CM-200) operating at 200 keV, respectively. The cross-sectional TEM (XTEM) samples were prepared by focus ion beam (FIB, FEI 235) operating at 30 kV with a gallium (Ga) source and thinned to about 0.1  $\mu$ m in thickness.

## III. RESULTS AND DISCUSSION

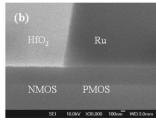

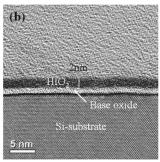

The key process required for a dual-metal-gate integration relies on the successful wet removal of the first metal (Ru) without damaging the high-k HfO<sub>2</sub> underlayer. In this study, with suitable adjustment of ceric ammonium nitrate/nitric acid ratio, the selectivity of Ru to HfO<sub>2</sub> could be controlled over 2800 without HfO<sub>2</sub> loss after 10 nm Ru metal removal (see in Table I). The capability of photoresist to protect the PMOS area was also one of the critical factors which must resist the wet etch during the Ru removal and should be removed easily after the first metal removal. Traditional O<sub>2</sub> plasma dry stripping is known to cause the damage when the HfO<sub>2</sub> dielectric surface is exposed during photoresist stripping. As shown in Figs. 2 and 3, amine based wet chemical stripping plays an important role as it removes the photore-

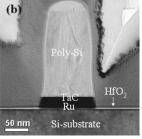

Fig. 3. High-resolution TEM inspection of HfO<sub>2</sub> thickness after Ru etching: (a) deposited film subjected to post-700 °C annealed and (b) after PR removal.

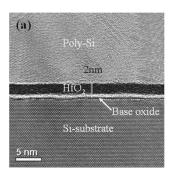

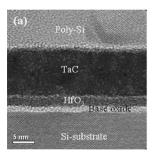

Fig. 4. Post second metal deposition: (a) NMOS: $TaC/HfO_2$  and (b) PMOS: $TaC/Ru/HfO_2$ .

sist only but has no damage to the high-k dielectric. Post second metal and polydeposition indicated that the dual-metal-gate stack of NMOS/PMOS areas is well defined in this integration scheme, as shown Fig. 4. These high-resolution XTEM micrographs evidence that the interface between TaC and  $HfO_2$  is free of interfacial contamination. This indicates that the Ru wet etching with such scheme is suitable for the dual-metal-gate integration.

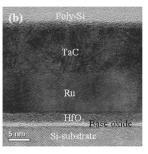

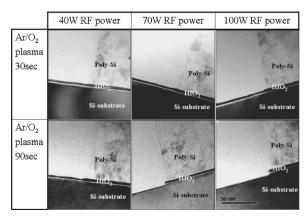

For NMOS/PMOS profile control during dual gate etching step, the proposed HfO<sub>2</sub> etching was carried out by using the DHF wet removal method instead of dry plasma etching for the lower Si substrate damage and recess control. Before the high-k dielectric HfO<sub>2</sub> wet removal, a high selectivity etching gas (Ar/O<sub>2</sub>) was applied for PMOS area Ru dry etching and stopping on the HfO<sub>2</sub> layer, as shown in Fig. 5. Both NMOS and PMOS were well controlled to stop on the high-k dielectric layer after dry etching of Ru with Ar/O<sub>2</sub>. In this study, by properly controlling the radio frequency (rf) bias power during Ru metal dry etching step and the extended over etching time with Ar/O<sub>2</sub> plasma bombardment could be contributed to remove the HfO2 layer with DHF solution. The O<sub>2</sub> gas that provided high etching selectivity of Ru metal and stopped on the HfO2 layer that followed extended overetching Ar/O<sub>2</sub> plasma implants of O ion through HfO<sub>2</sub> into substrate resulted in faster DHF etching benefit. In practice, Fig. 6 reveals that the threshold rf bias power over 70 W is required to remove HfO<sub>2</sub> film through the pretreatment condition of Ar/O<sub>2</sub> plasma bombardment for 90 s. In fact, that the bias power is related to ion plasma treated time combined sufficient energy for 4 nm HfO<sub>2</sub> film bombard-

Fig. 5. Post-dual-metal-gate etched stop on  $HfO_2$ : (a) NMOS: $TaC/HfO_2$  and (b) PMOS: $TaC/Ru/HfO_2$ . The gate surfaces are passivated with oxide, Pt-Pd, and carbon coating for XTEM specimen fabrication with FIB.

Fig. 6. Correlation between bombardment parameters and  $HfO_2$  was removed in 100:1 diluted HF solution for 60 s. The  $HfO_2$  films are examined with 4 nm thickness.

ment. The results shown in Fig. 6 also indicate that Si recess after post-DHF wet etching is controllable by rf bias power during Ar/O<sub>2</sub> plasma bombardment of HfO<sub>2</sub> film surface treatment.

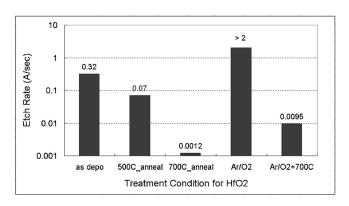

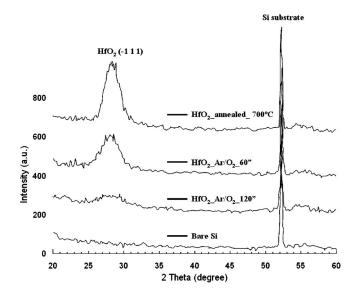

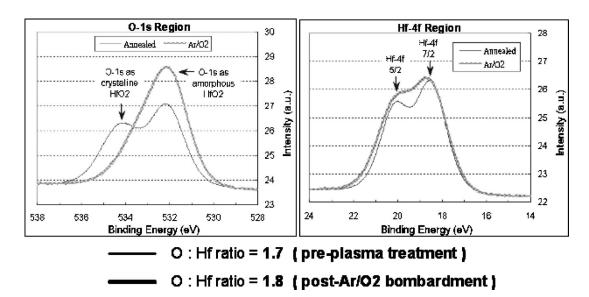

Four postsurface treatments for HfO<sub>2</sub> films, e.g., 500 and 700 °C annealing in N2 ambient, Ar/O2 plasma bombardment, and Ar/O<sub>2</sub> bombardment followed by 700 °C annealing, were examined so as to identify their effects on DHF etching rate. As shown in Fig. 7, the increase of annealing temperature reduces the etching rate of HfO2 film in DHF solution. This indicates that the etching rate decreases with the improvement of crystallinity of HfO<sub>2</sub> film. Such a result is confirmed by XRD analyses shown in Fig. 8 which shows that the crystallinity of annealed HfO<sub>2</sub> film is better than that of plasma bombarded films. Furthermore, due to the amorphism generated by the plasma bombardment, the Ar/O<sub>2</sub> bombarded HfO<sub>2</sub> film hence possesses the fastest etching rate in comparison with the HfO<sub>2</sub> films subjected to other treatments. However, the plasma bombarded HfO2 became difficult to be etched away by DHF solution after a subsequent 700 °C anneal which caused the recrystallization of HfO<sub>2</sub> film. The Ar/O<sub>2</sub> plasma bombardment induces physical transformation in HfO2 film that may accelerate the remedy of crystallinity of HfO<sub>2</sub> film during subsequent thermal treatment. The HfO<sub>2</sub> film subjected to Ar/O<sub>2</sub> bombardment

Fig. 7. 100:1 dilute HF etching rate on HfO<sub>2</sub> subjected to Ar/O<sub>2</sub> treatment.

Fig. 8. XRD intensity ratio analysis of  $HfO_2$  after  $Ar/O_2$  bombarded treatment. The amorphous  $HfO_2$  phase increased after  $Ar/O_2$  plasma bombardment.

followed by 700  $^{\circ}$ C annealing hence exhibits the lowest etching rate in DHF solution. Hence, not only plasma treatment time but also rf bias power benefits from complete physical transformation resulting in a near completely amorphous HfO<sub>2</sub> film which can be completely removed by DHF solution

To get a complete look at the differences between the two HfO<sub>2</sub> films which are annealed with 700 °C and post-Ar/O<sub>2</sub> plasma treatment, the high-resolution regions of O 1s and Hf 4f were examined. According to the result of XPS analyses of annealed and Ar/O<sub>2</sub> plasma bombarded HfO<sub>2</sub> films shown in Fig. 9, the O 1s subpeak at 534.2 eV disappears after Ar/O<sub>2</sub> bombardment whereas the O to Hf atomic concentration ratio increased followed by O ion implementation, suggesting the occurrence of phase transition. The atomic con-

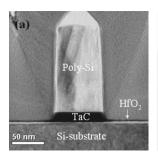

Fig. 10. Post-HfO $_2$  etching with 100:1 dilute HF solution for 60 s: (a) NMOS:TaC/HfO $_2$  and (b) PMOS:TaC/Ru/HfO $_2$ .

centration ratio was calculated from the photoelectron peak areas by subtracting a linear-type background. In addition, a correlation with XRD confirmed that the HfO2 films are amorphousized by Ar/O<sub>2</sub> plasma bombardment due to phase transition and benefited by DHF etching. The Ar/O<sub>2</sub> plasma processing contributes to chemical shift of O 1s spectra from high bonding energy peak of crystalline shifted to lower bonding energy peak of amorphous HfO2. Again, this indicates that the amorphism of high-k HfO2 dielectrics subjected to Ar/O<sub>2</sub> plasma bombarded film benefits its wet etching in DHF solution. Both NMOS and PMOS gate profiles are shown in Fig. 10; those high-k HfO<sub>2</sub> films under gate are defined by following with pretreatment condition of Ar/O<sub>2</sub>/90 s under 70 W rf bias power then post-HfO<sub>2</sub> etched by 100:1 dilute HF for 60 s. The source-drain area gate poly, metal, and high-k dielectric layers are successfully defined by this dual-metal-gate process scheme.

#### IV. CONCLUSIONS

The dual-metal-gate CMOS devices are demonstrated with Ru and TaC gate electrodes on high-k HfO<sub>2</sub> Key process modules such as a highly selective metal wet etching

Fig. 9. XPS Hf 4f and O 1s spectra from annealed and Ar/O<sub>2</sub> plasma bombarded HfO<sub>2</sub>. The O/Hf atomic ratio increased after Ar/O<sub>2</sub> plasma bombardment.

and dual-metal-gate plasma bombardment combined with wet etch process have been developed. The ceric ammonium nitrate and nitric acid mixture is used for Ru metal removal with highly selective control on the high-k HfO $_2$  Moreover, the HfO $_2$  treated with appropriate bias power Ar/O $_2$  plasma bombardment approach followed by selective DHF wet etching provides wide process window control to minimize Si substrate damage. Well-behaved CMOS transistors with gate length down to 75 nm indicate that these process modules can be readily utilized to fabricate the dual-metal-gate CMOS for below 65 nm node.

#### **ACKNOWLEDGMENTS**

This work was supported by the National Science Council of Taiwan (Grant No. NSC 93–2216–E–009–008). The authors sincerely thank Applied Material Co. and FSI Co. for their support in ALPCVD, PVD, and wet bench equipment.

- <sup>7</sup>L. Chang, S. Tang, T. J. King, J. Bokor, and C. Hu, Tech. Dig. Int. Electron Devices Meet. **2000**, 719.

- <sup>8</sup>J. Liu, H. C. Wen, J. P. Lu, and D. L. Kwong, IEEE Electron Device Lett. 26, 228 (2005).

- J. Kedzierski *et al.*, Tech. Dig. Int. Electron Devices Meet. **2002**, 247.

J. Kedzierski, D. Boyd, Y. Zhang, M. Steen, F. F. Jamin, J. Benedict, M. Ieong, and M. Haensch, Tech. Dig. Int. Electron Devices Meet. **2003**, 18 4 1

- C. H. Huang *et al.*, Tech. Dig. Int. Electron Devices Meet. **2003**, 13.4.1.

J. H. Sim, H. C. Wen, J. P. Lu, and D. L. Kwong, IEEE Electron Device Lett. **24**, 631 (2003).

- <sup>13</sup>C. Cabral et al., Int. VLSI Conf. 2004, 184.

- <sup>14</sup>Y.-C. Yeo et al., IEEE Electron Device Lett. 22, 227 (2001).

- <sup>15</sup>S. Matsuda, H. Yamakawa, A. Azuma, and Y. Toyoshima, Int. VLSI Conf. 2001, 63.

- <sup>16</sup>S. B. Samavedam *et al.*, Tech. Dig. Int. Electron Devices Meet. **2002**, 433

- <sup>17</sup>Z. B. Zhang et al., Int. VLSI Conf. 2005, 50.

- <sup>18</sup>Q. Lu et al., Int. VLSI Conf. 2000, 72.

- <sup>19</sup>S. B. Samavedam *et al.*, Tech. Dig. Int. Electron Devices Meet. **2002**, 433.

- <sup>20</sup>T. L. Li, W. L. Ho, H. B. Chen, C. H. Wang, C. Y. Chang, and C. Hu, IEEE Trans. Electron Devices **53**, 1420 (2006).

- <sup>21</sup>C. S. Park, B. J. Cho, and D. L. Kwong, IEEE Electron Device Lett. 24, 298 (2003).

- <sup>22</sup>S.-L. Zhang and M. Ostling, Crit. Rev. Solid State Mater. Sci. 28, 1 (2003).

- <sup>23</sup>S. Norasetthekul *et al.*, Appl. Surf. Sci. **187**, 75 (2002).

- <sup>24</sup>L. Sha, R. Puthenkovilakam, Y. S. Lin, and J. P. Chang, J. Vac. Sci. Technol. B **21**, 2420 (2003).

- <sup>25</sup>J. Barnett, D. Riley, T. C. Messina, P. Lysaght, and R. Carpio, Solid State Phenom. 92, 11 (2003).

<sup>&</sup>lt;sup>1</sup>The International Technology Roadmap for Semiconductors, 2003.

<sup>&</sup>lt;sup>2</sup>E. M. Vogel, K. Z. Ahmed, B. Hornung, W. K. Hensen, P. K. McLarty, G. Lucovsky, J. R. Hauser, and J. Wortman, IEEE Trans. Electron Devices **45**, 1350 (1998).

<sup>&</sup>lt;sup>3</sup>Q. Lu, D. Park, A. Kalnitsky, C. Chang, C. C. Cheng, S. P. Tay, T.-J. King, and C. Hu, IEEE Electron Device Lett. **19**, 341 (1998).

<sup>&</sup>lt;sup>4</sup>B. Cheng *et al.*, IEEE Trans. Electron Devices **46**, 1537 (1999).

<sup>&</sup>lt;sup>5</sup>Y. Abe, T. Oishi, K. Shiozawa, Y. Tokuda, and S. Satoh, IEEE Electron Device Lett. **20**, 632 (1999).

<sup>&</sup>lt;sup>6</sup>S. H. Lo, D. A. Buchaman, and Y. Taur, IBM J. Res. Dev. **43**, 327 (1999).