## Trap-state density in continuous-wave laser-crystallized single-grainlike silicon transistors

Yu-Ting Lin, Chih Chen, Jia-Min Shieh, Yao-Jen Lee, Ci-Ling Pan, Ching-Wei Cheng, Jian-Ten Peng, and Chih-Wei Chao

Citation: Applied Physics Letters 88, 233511 (2006); doi: 10.1063/1.2209198

View online: http://dx.doi.org/10.1063/1.2209198

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/88/23?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Stability of continuous-wave laser-crystallized epilike silicon transistors

Appl. Phys. Lett. 90, 073508 (2007); 10.1063/1.2644927

Extraction of trap states in laser-crystallized polycrystalline-silicon thin-film transistors and analysis of degradation by self-heating

J. Appl. Phys. 91, 3855 (2002); 10.1063/1.1446238

Erratum: "Effect of excimer laser annealing on the structural and electrical properties of polycrystalline silicon thin-film transistors" [J. Appl. Phys. 86, 4600 (1999)]

J. Appl. Phys. 87, 1588 (2000); 10.1063/1.372060

Effect of excimer laser annealing on the structural and electrical properties of polycrystalline silicon thin-film transistors

J. Appl. Phys. 86, 4600 (1999); 10.1063/1.371409

Noise performances in polycrystalline silicon thin-film transistors fabricated by excimer laser crystallization Appl. Phys. Lett. **71**, 578 (1997); 10.1063/1.119799

## Trap-state density in continuous-wave laser-crystallized single-grainlike silicon transistors

Yu-Ting Lin and Chih Chen

Department of Material Science and Engineering, National Chiao Tung University, Hsinchu 30010, Taiwan

Jia-Min Shieh<sup>a)</sup> and Yao-Jen Lee

National Nano Device Laboratories, Hsinchu 30078, Taiwan

Ci-Ling Pan

Department of Photonics, Institute of Electro-Optical Engineering, National Chiao Tung University, Hsinchu 30010, Taiwan

Ching-Wei Cheng, Jian-Ten Peng, and Chih-Wei Chao

Low Temp Poly-Silicon Technology Division, AU Optronics, Hsinchu 30078, Taiwan

(Received 3 January 2006; accepted 1 May 2006; published online 8 June 2006)

This investigation characterizes electrical characteristics of continuous-wave green laser-annealed single-grainlike silicon thin-film transistors in relation to trap-state densities. As laser power increases, highly crystalline channels form, reducing tail-state densities to as low as  $3 \times 10^{19} \, \mathrm{eV^{-1} \, cm^{-3}}$ . This occurrence is responsible for high field-effect electron mobility of 284 cm²/V s. In contrast, increasing laser power initially reduces the deep-state density and then increases it to  $3 \times 10^{16} \, \mathrm{eV^{-1} \, cm^{-3}}$ . This reversal in deep-state density and thus in the subthreshold slope as well as a saturating reduction in threshold voltage are associated with the formation of extra interface defects caused by laser-crystallization-enhanced surface roughness. © 2006 American Institute of Physics. [DOI: 10.1063/1.2209198]

Recently, high-performance polycrystalline silicon thinfilm transistors (polysilicon TFTs) on glass substrates have been implemented. They depend on the formation of lasercrystallized single-grainlike channels by sequential lateral solidification (SLS). <sup>1,2</sup> The supply of photoenergy from continuous-wave (cw) green lasers facilitates the lateral crystallization of amorphous silicon (*a*-Si), even in the absence of capping layers and laser power masking. <sup>2</sup> Hence, cw laser crystallization (CLC) is more practical than excimer-laserannealing (ELA)-based SLS. <sup>1,2</sup>

A high laser power is commonly adopted to enhance the channel crystallinity in an attempt to improve all of the electrical characteristics of laser-crystallized polysilicon TFTs.<sup>3</sup> However, doing so also roughens the channel surfaces while degrading the threshold voltage and the subthreshold slope, as reported by Angelis et al. in relation to ELA polysilicon TFTs.4 A high-speed and reliable transistor should have a thin channel, which fact explains why interfacial properties dominate the performance of transistors. Accordingly, the surface roughness of thin CLC channels is a major concern. Several methods, such as field-effect conductance<sup>5</sup> (FEC) and low-frequency noise methods<sup>6</sup>, have been developed and applied to measure channel quality in terms of the density of grain (grain boundary) and interface traps, which effectively specify the electrical parameters of the transistors. Nevertheless, these issues have seldom been addressed for CLCfabricated TFTs.

This study reveals an ultralow trap-state density in CLC polysilicon, which is consistent with the demonstration of excellent electrical characteristics. Additionally, the formation of extra interface defects induced by the laser-crystallization-enhanced surface roughness (LCESR) leads to

the reversal of deep-state density and, thus, the subthreshold slope, as well as a saturating reduction in threshold voltage.

The experiment was begun by sequentially depositing a 50 nm thick layer of  $SiN_x$ , a 150 nm thick layer of  $SiO_2$ , and a 50 nm thick a-Si film by plasma-enhanced chemical vapor deposition (PECVD) on a Corning Eagle 2000 glass substrate. Before laser crystallization, the deposited a-Si films were patterned into individual islands of 60  $\mu$ m/76  $\mu$ m (width/length) as active layers of TFTs to prevent peeling. A solid-state cw green ( $\lambda$ =532 nm) laser with an output power of 3-5 W was then guided to crystallize islands laterally by line scanning the samples at 10 cm/s. CLC experiments are conducted in ambient air at room temperature and the laser beam is incident on samples with a strip spot of  $220 \times 40 \ \mu$ m<sup>2</sup>.

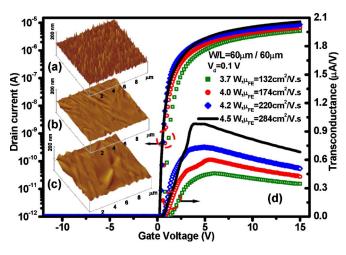

Figures 1(a)-1(c) depict the topographies of a-Si channels crystallized by the CLC method at different laser powers. As the laser power increases, CLC, instead of superlateral-growth (SLG) or even solid-phase crystallization, dominates the growth of the grains. 1,2,8 Consequently, highly crystalline channels comprised micrograins of dimensions  $3 \times 10 \ \mu m^2$  forms. The surface roughness of the channels crystallized with an incremental laser power initially declines from 8.2 nm (3-3.7 W) to 2.8 nm (3.8-4.2 W), before increasing to 5.1 nm (4.3-4.5 W), as indicated by these topographies. The initial decrease in the roughness reflects a change in the crystallization mode because the surface roughness of the SLG-crystallized channels was reported to exceed that of the CLC-crystallized channels. 1,2 The reversal in the roughening of the surface as the laser power is further increased is attributed to the increase in the numbers of hillocks at the grain boundaries, caused by high photoenergy irradiation.9

a)Electronic mail: jmshieh@mail.ndl.org.tw

FIG. 1. (Color online) AFM micrographs of channel topographies of polysilicon films crystallized by cw green laser at various laser powers of (a) 3.5, (b) 4.2, and (c) 4.5 W. (d) Transfer characteristics and transconductance curves of polysilicon TFTs made from CLC at laser powers of 3.7, 4.0, 4.2, and 4.5 W.

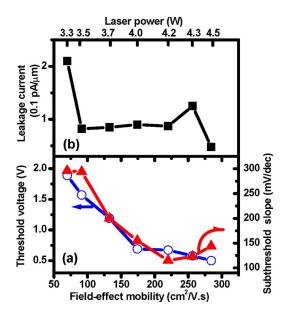

On various crystallite channels, TFTs are fabricated with conventional polysilicon TFTs. Figure 1(d) plots logarithmic transfer (drain current  $I_d$  versus gate voltage  $V_g$ ) characteristics and linear transcondcutance  $(G_m)$  curves for some representative TFTs, when a drain voltage  $V_d$  of 0.1 V was applied. Next, the maximum  $G_m$  was analyzed to yield the field-effect electron mobility  $(\mu_{\rm FE})$ , and the threshold voltage  $(V_{\rm th})$  was determined by linear extrapolation of the transcondcutance to zero. 10 The subthreshold slope (S) was also extracted from the maximum slope of the transfer curves, plotted on a semilogarithmic scale. Figure 2 plots the subthreshold slope, the threshold voltage, and the leakage current (at  $V_d$ =10 V) against field-effect mobility (laser

As expected, increasing the laser fluence increases the efficiency of grain lateral growth, forming larger grains with fewer associated defects, while considerably reducing the height of the barrier to carrier transportation in the channels,

FIG. 2. (Color online) (a) Subthreshold slope and threshold voltage and (b) minimum leakage current for polysilicon TFTs made using CLC at different laser powers in the range of 3-4.5 W.

FIG. 3. (Color online) (a) Energy distribution of DOS for polysilicon TFTs made using CLC at laser powers of 3.7, 4.0, 4.2, 4.3, and 4.5 W. For comparison, the DOS distribution for ELA-fabricated TFTs with  $\mu_{ ext{FE}}$  of 140 cm<sup>2</sup>/V s,  $V_{th}$  of 1.5 V, and S of 180 mV/decade is also presented. (b)  $\Delta V_{\mathrm{th}}$  transients for CLC polysilicon TFTs made at laser power of 4.5 W during gate stressing and hot-carrier stressing. Curve fitting is also shown. The DOS distribution for the same device after gate stressing is also shown in (a).

associated with a higher  $G_m$  [Fig. 1(d)], such that  $\mu_{\rm FE}$  is as plotted in Fig. 2.<sup>11</sup> Next, the densities of states (DOSs) of traps are examined using the FEC method for CLCfabricated TFTs, with reference to the crystallization conditions, as presented in Fig. 3(a). As the laser power increases to 4.5 W, the tail-state density clearly decreases to  $3 \times 10^{19} \text{ eV}^{-1} \text{ cm}^{-3}$  at  $E - E_F = 0.52 \text{ eV}$  where  $E_F$  is the midgap energy, whose value is almost one order of magnitude lower than that obtained from ELA-fabricated TFTs [see Fig. 3(a)]. The enlargement of grains in channels as the laser power increases not only reduces the density of grain defects but also relieves the distortion of bonds in highly crystalline silicon. <sup>13,14</sup> Therefore, channel crystallinity is strongly related to the density of distorted-bond defects, regarded as the origination of tail states. Hence, the tail-state density declines as the laser power increases, as shown in Fig. 3(a), and as indicated by ELA-related results reported elsewhere. 13 Extremely low tail-state densities associated with large grains in CLC polysilicon are responsible for the high  $\mu_{\rm FE}$  of 284 cm<sup>2</sup>/V s, independently of surface roughness.

Closely examining the four transconductance  $(G_m)$ curves in Fig. 1(d) reveals that the slope at which  $G_m$  is away from the ascending stage and declines with  $V_g$  increases with the laser power. As the surface roughness increases, the mobility reduction at high gate voltages is increased because the surface scattering increases, <sup>14</sup> which relation is consistent with the transconductance data. Note that the electric field enhanced at the rough polysilicon/SiO<sub>2</sub> interface<sup>15</sup> assists the electrons to be injected into the gate oxide. In Fig. 2(a), the threshold voltage decreases more slowly as the laser power increases above 4.0 W, suggesting that the injected electrons are trapped as negative charges in the oxide. The negative trapped charge reduces the electrical field near the drain, reducing the leakage current at high laser power [see Fig. 2(b)].

The charge trapping mechanism can be further investigated by gate stressing  $^{16}$  and hot-carrier stressing.  $^{17}$  Figure 3(b) plots the  $V_{\rm th}$  shift ( $\Delta V_{\rm th}$ ) versus the stressing time (t) for CLC-fabricated TFTs made at a laser power of 4.5 W during gate stressing ( $V_g = 20 \text{ V}$  and  $V_d = 0 \text{ V}$ ) and hot-carrier stressing  $(V_g = 8 \text{ V} \text{ and } V_d = 16 \text{ V})$ . The former test demonstrates a logarithmic time dependence of  $\Delta V_{\text{th}}$ , which is indicative of charge trapping in gate dielectrics. <sup>16</sup> Moreover, the latter test indicates the power-law time dependence of  $\Delta V_{\text{th}}$  with exponents of 0.25 ( $\sim t^{0.25}$ ), as opposed to power-law exponents in the range of 0.4–0.6 associated with deep-state generation. <sup>17</sup> Comparing DOS distributions before and after either gate stressing [see Fig. 3(a)] or hot-carrier stressing (not shown herein) shows almost overlapping trap-state densities. Hence, slightly roughened CLC polysilicon/SiO<sub>2</sub> merely induces charge trapping but trapped electrons into the gate oxide or at the interface create hardly any new deep states.

Increasing the laser power initially reduces the deepstate densities, unlike the tail-state density, to as low as  $1.0 \times 10^{16} \text{ eV}^{-1} \text{ cm}^{-3}$  at  $E - E_F = 0.25 \text{ eV}$  and then increases these to  $3 \times 10^{16} \text{ eV}^{-1} \text{ cm}^{-3}$ . Deep-state densities extracted at other energetic states of  $E-E_F=0.25-0.35$  eV also exhibit the same trend. Low-frequency noise measurements indicate that roughened surfaces formed extra interface traps, 4,6,7 which are responsible for the reversal in the deep-state density. 18 For ELA polysilicon, the impact of LCESR on the deep-state density is difficult to observe because in such a material, the deep-state density is as high as  $5 \times 10^{17} \text{ eV}^{-1} \text{ cm}^{-3}$  (at  $E - E_F = 0.25 \text{ eV}$ ), exceeding that of polysilicon-oxide traps,  $3 \times 10^{17} \text{ eV}^{-1} \text{ cm}^{-3}$ . The deepstate density of smooth and single-grainlike CLC polysilicon is below 10<sup>17</sup> eV<sup>-1</sup> cm<sup>-3</sup>, causing LCESR to change the deep-states to reverse the decline, despite the fact that increasing channel crystallinity normally reduces the density of the grain defects, including deep-states defects. Therefore, the deep-state- and/or the interface-state-dominated subthreshold slopes follow the variation in deep-states densities with laser power [see Figs. 2(a) and 3(a)]. 19,20

In summary, the measurement of the trap-state densities of CLC polysilicon TFTs was reported to characterize the electrical parameters of devices with reference to channel crystal quality and surface morphology. Ultralow trap-state densities associated with smooth and single-grainlike poly-

silicon are responsible for higher field-effect mobility, lower threshold voltage, steeper subthreshold slope, and lower leakage current than those of ELA-fabricated TFTs. Moreover, low deep-state densities remain sensitive to the interfacial states and are influenced by the LCESR effect.

The authors acknowledge funding by the National Science Council (NSC) of Taiwan and Marketech International Corp. through various grants.

- <sup>1</sup>A. Hara, M. Takei, K. Yoshino, F. Takeuchi, M. Chida, and N. Sasaki, Tech. Dig. Int. Electron Devices Meet. **2003**, 211.

- <sup>2</sup>A. Hara, M. Takei, K. Yoshino, F. Takeuchi, M. Chida, and N. Sasaki, Jpn. J. Appl. Phys., Part 1 **43**, 1269 (2004).

- <sup>3</sup>A. T. Voutsas, Appl. Surf. Sci. **208-209**, 250 (2003).

- <sup>4</sup>C. T. Angelis, C. A. Dimitriadis, M. Miyasaka, F. V. Farmakis, G. Kamarinos, J. Brini, and J. Stoemenos, J. Appl. Phys. **86**, 4600 (1999).

- <sup>5</sup>G. Fortunato and P. Migliorato, Appl. Phys. Lett. **49**, 1025 (1986).

- <sup>6</sup>A. Bonfiglietti, A. Valletta, L. Mariucci, A. Pecora, and G. Fortunato, Appl. Phys. Lett. **82**, 2709 (2003).

- <sup>7</sup>C. T. Angelis, C. A. Dimitriadis, F. V. Farmakis, G. Kamarinos, J. Brini, and M. Miyasaka, Appl. Phys. Lett. **74**, 3684 (1999).

- <sup>8</sup>G. Auvert, D. Bensahel, A. Georges, V. T. Nguyen, P. Henoc, F. Morin, and P. Coissard, Appl. Phys. Lett. **38**, 613 (1981).

- <sup>9</sup>D. K. Fork, G. B. Anderson, J. B. Boyce, R. I. Johnson, and P. Mei, Appl. Phys. Lett. **68**, 2138 (1996).

- <sup>10</sup>C. T. Angelis, C. A. Dimitriadis, F. V. Farmakis, J. Brini, G. Kamarinos, and M. Miyasaka, Appl. Phys. Lett. 76, 2442 (2000).

- <sup>11</sup>F. V. Farmarkis, J. Brini, G. Kamarinos, C. T. Angelis, C. A. Dimitriadis, M. Miyasaka, and T. Ouisse, Solid-State Electron. 44, 913 (2000).

- <sup>12</sup>T. J. King, M. G. Hack, and I. W. Wu, J. Appl. Phys. **75**, 908 (1994).

- <sup>13</sup>G. A. Armstrong, S. Uppal, S. D. Brotherton, and J. R. Ayres, Jpn. J. Appl. Phys., Part 1 37, 1721 (1998).

- <sup>14</sup>M. Miyasaka and J. Stoemenos, J. Appl. Phys. **86**, 5556 (1999).

- <sup>15</sup>N. Matsuo and A. Sasaki, Solid-State Electron. **39**, 337 (1996).

- <sup>16</sup>M. J. Powell, C. van Berkel, I. D. French, and D. H. Nicholls, Appl. Phys. Lett. **51**, 1242 (1987).

- <sup>17</sup>F. V. Farmakis, J. Brini, G. Kamarinos, and C. A. Dimitriadis, IEEE Electron Device Lett. 22, 74 (2001).

- <sup>18</sup>S. Higashi, D. Abe, Y. Hiroshima, K. Miyashita, T. Kawamura, S. Inoue, and T. Shimoda, Jpn. J. Appl. Phys., Part 1 41, 3646 (2002).

- <sup>19</sup>C. A. Dimitriadis, P. A. Coxon, L. Dozsa, L. Papadimitriou, and N. Economou, IEEE Trans. Electron Devices 39, 598 (1992).

- <sup>20</sup>T. Noguchi, Jpn. J. Appl. Phys., Part 2 **32**, L1584 (1994).