# High-Performance Poly-Silicon TFTs Using HfO<sub>2</sub> Gate Dielectric

Chia-Pin Lin, Student Member, IEEE, Bing-Yue Tsui, Senior Member, IEEE, Ming-Jui Yang, Ruei-Hao Huang, and Chao-Hsin Chien, Associate Member, IEEE

Abstract—High-performance low-temperature poly-Si thin-film transistors (TFTs) using high- $\kappa$  (HfO2) gate dielectric is demonstrated for the first time. Because of the high gate capacitance density and thin equivalent-oxide thickness contributed by the high- $\kappa$  gate dielectric, excellent device performance can be achieved including high driving current, low subthreshold swing, low threshold voltage, and high ON/OFF current ratio. It should be noted that the ON-state current of high- $\kappa$  gate-dielectric TFTs is almost five times higher than that of SiO2 gate-dielectric TFTs. Moreover, superior threshold-voltage  $(V_{\rm th})$  rolloff property is also demonstrated. All of these results suggest that high- $\kappa$  gate dielectric is a good choice for high-performance TFTs.

Index Terms—Hafnium dioxide (HfO<sub>2</sub>), high dielectric-constant dielectric, thin-film transistors (TFTs).

#### I. Introduction

OW-TEMPERATURE poly-Si (LTPS) thin-film transis-✓ tors (TFTs) have been used as pixel and driving ICs in active-matrix liquid crystal displays (AMLCDs) [1]. Recently, to realize system-on-panel (SOP), integrating driving ICs on the glass substrate are required [2]. However, it is a challenge to develop high-performance TFTs for both pixel TFTs and driving circuits [3]. To drive the liquid crystal, pixel TFTs operate at high voltages with low gate-leakage currents. In contrast, high-speed display driving circuits require TFTs to operate at low voltages and high driving currents, with a low threshold voltage. Using a thin gate oxide can increase the driving current of TFTs. Unfortunately, for a conventional gate dielectric (i.e., SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>), a thinner gate dielectric may induce higher gate-leakage current and degrade the TFT characteristics significantly [4]. In the previous studies, to preserve the physical gate-dielectric thickness while increasing the gate capacitance density and then improving the mobile carrier density in the channel region, several new high- $\kappa$  gate-dielectric materials including Al<sub>2</sub>O<sub>3</sub> and Ta<sub>2</sub>O<sub>5</sub> were suggested [5], [6]. However, the  $\kappa$  value of Al<sub>2</sub>O<sub>3</sub> is 9–10 and is not high enough, and the improvement of the device performance is not apparent [7]. On the other hand, due to narrowbandgap, it is necessary to use a thick Ta<sub>2</sub>O<sub>5</sub> as gate dielectric in TFTs to reduce the gate-

Manuscript received January 3, 2006; revised February 17, 2006. This work was supported by the National Science Council, Taiwan, R.O.C. under Contract NSC-93-2215-E-009-004. The review of this letter was arranged by Editor J. Sin.

C.-P. Lin and B.-Y. Tsui are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: cplin.ee90g@nctu.edu.tw).

M.-J. Yang, R.-H. Huang and C.-H. Chien are with the National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/LED.2006.872832

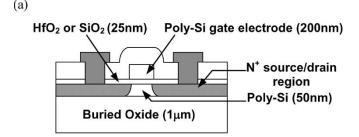

Fig. 1. Cross-sectional (a) drawing and (b) TEM of the proposed high- $\kappa$  HfO<sub>2</sub> gate-dielectric TFT structure.

leakage current [8]. Therefore, the increase of gate capacitance density is limited. Recently, hafnium dioxide (HfO<sub>2</sub>) becomes a candidate of future high- $\kappa$  gate-dielectric material in MOSFET due to its high- $\kappa$  value ( $\sim$  25), widebandgap, acceptable band alignment, and superior thermal stability with poly-Si [9], [10]. In this paper, we integrated high- $\kappa$  HfO<sub>2</sub> gate dielectric with TFTs for the first time.

# II. DEVICE FABRICATION

Fig. 1(a) and (b) shows the schematic drawing of the  $HfO_2$  gate-dielectric TFT and the cross-sectional transmission electron microscopy (TEM) micrograph of the gate structure, respectively. The fabrication started by depositing a 50-nm amorphous Si ( $\alpha$ -Si) layer at 550 °C in a low-pressure

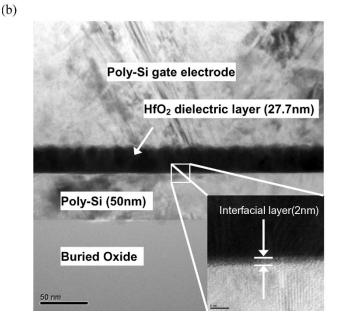

Fig. 2. Output characteristics of the TFTs using  $HfO_2$  or  $SiO_2$  as gate dielectric.

chemical vapor deposition (LPCVD) system on Si wafers capped with a 1- $\mu$ m thick thermal oxide layer. The deposited  $\alpha$ -Si layer was then recrystallized by solid phase crystallization (SPC) process at 600 °C for 24 h in a N2 ambient. Next, in order to fabricate narrow-width devices to enhance the gate controllability and reduce the influence of grainboundary defects, electron beam lithography (EBL) and reactive ion etching (RIE) were used to pattern the device active islands [11], [12]. The narrowest channel width is 0.1  $\mu$ m. Then, after removing the native oxide by dipping in diluted hydrofluoric acid (HF) solution, an HfO<sub>2</sub> thin film was deposited in a metal-organic CVD (MOCVD) system at 400 °C as gate dielectric. Oxygen and Argon were used as reactant and transmission gases with flow rates of 1000 and 200 sccm, respectively. The total pressure in the chamber is fixed at 5 mbar and the injection frequency is 3 Hz. Another 200-nm  $\alpha$ -Si layer was deposited at 550 °C in an LPCVD system and then was patterned to form gate electrode. Because of the thermal budget during the  $\alpha$ -Si gate deposition, the thick amorphous HfO<sub>2</sub> layer became polycrystalline structure, and then formed the rough top interface between gate electrode layer and HfO<sub>2</sub> film. Next, a self-aligned phosphorous ion implantation was performed at 60 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> to dope source/drain region and gate electrode. After a 300-nm-thick HF passivation layer was deposited by a plasma-enhanced CVD (PECVD) system at 300 °C, the contact holes were patterned by a two-step wet-etching process. First, the 300-nm oxide layer was etched by buffered oxide etch (BOE) solutions. Then, to raise the HfO<sub>2</sub>/SiO<sub>2</sub> selectivity, the HfO<sub>2</sub> films were etched by an isopropyl alcohol (IPA):HF mixture [13]. Additional annealing for dopants' activation was performed at 600 °C for 12 h in an N<sub>2</sub> ambient. Finally, typical Al metallization completed the fabrication process. In order to enhance the device performance, an NH<sub>3</sub> plasma treatment at 350 °C for 30 min was performed to passivate the defect states before measurements [14]. For comparison, poly-Si TFTs with a 25- and 45-nm tetra-ethoxysilane (TEOS) SiO<sub>2</sub> deposited by an LPCVD system were also fabricated with the same process flow.

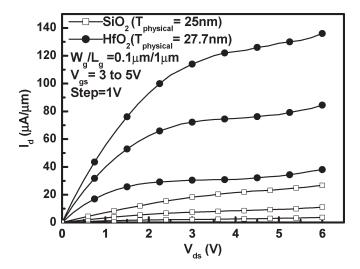

Fig. 3. Transfer characteristics of the TFTs using  $HfO_2$  or  $SiO_2$  as gate dielectric.

$\begin{array}{c} \text{TABLE} \ \ I \\ \text{Device Parameters of TFTs With 27.7-nm HfO}_2 \ \text{or} \\ \text{25-nm SiO}_2 \ \text{as Gate Dielectric at } V_{ds} = 0.1 \ \text{V} \end{array}$

| Gate dielectric                                                         | V <sub>th</sub> (V) | S.S. (V/Dec) | $\mu_{FE}(cm^2/V\text{-sec})$ | $I_{on}/I_{off}$ (@ $V_{ds}=1V$ ) |

|-------------------------------------------------------------------------|---------------------|--------------|-------------------------------|-----------------------------------|

| HfO <sub>2</sub><br>(T <sub>physical</sub> =27.7 nm)<br>(EOT=7.3 nm)    | 0.3                 | 0.28         | 39                            | 9.7x10 <sup>6</sup>               |

| LPCVD SiO <sub>2</sub><br>(T <sub>physical</sub> =25 nm)<br>(EOT=31 nm) | 1.2                 | 0.64         | 50                            | 5.4x10 <sup>6</sup>               |

Device performance was measured using an Agilent 4156 C semiconductor parameter analyzer and an Agilent 4284 A impedance analyzer. The threshold voltage is defined as the gate voltage at which the drain current reaches 100 nA \*  $W_g/L_g$ , where  $L_g$  is the drawn channel length and  $W_g$  is the drawn channel width. Effective mobility is extracted from the maximum transconductance  $(g_m)$ .

## III. RESULTS AND DISCUSSION

According to Fig. 1(b), the physical thickness of HfO<sub>2</sub> films is equal to 27.7 nm, and the interfacial SiO<sub>2</sub>-like layer is about 2 nm [15]. The equivalent-oxide thickness (EOT) and the effective dielectric constant of HfO<sub>2</sub> are extracted to be 7.3 and 20.4 nm, respectively [16]. Fig. 2 shows the typical  $I_d - V_{ds}$  for the HfO<sub>2</sub> and SiO<sub>2</sub> TFTs with the same physical gate-dielectric thickness ( $T_{\rm physical}$ ) of 27.7 and 25 nm, respectively. The drawn channel length  $(L_q)$  and channel width  $(W_q)$  are 1  $\mu$ m and 0.1  $\mu$ m, respectively. Obviously, the driving current of HfO<sub>2</sub> TFT (about 136  $\mu$ A/ $\mu$ m) is five times higher than that of SiO<sub>2</sub> TFT (about 26.7  $\mu$ A/ $\mu$ m) at  $V_{\rm ds} = 6$  V and  $V_{\rm gs} = 5$  V. Fig. 3 depicts the transfer characteristics of HfO<sub>2</sub> and  ${

m SiO_2}$  TFTs at  $V_{

m ds}=0.1$  and 1 V. The measured as well as extracted device parameters are summarized in Table I. As the gate dielectric of  $SiO_2$  is replaced by  $HfO_2$ ,  $V_{th}$  decreases from 1.2 to  $\sim 0.3$  V, S.S. decreased from 0.64 to 0.28 V/Dec,

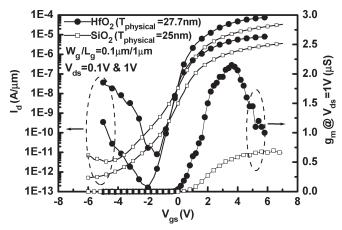

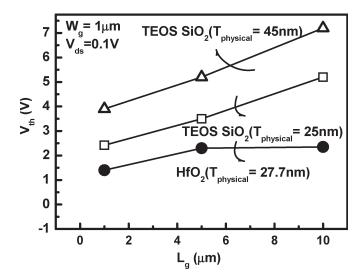

Fig. 4. Threshold-voltage rolloff of poly-Si TFTs with HfO<sub>2</sub>  $(T_{\rm physical}=27.7~\rm nm)$  and SiO<sub>2</sub>  $(T_{\rm physical}=25~\rm or~45~\rm nm)$  at  $V_{\rm ds}=0.1~\rm V.$

and  $I_{\rm on}/I_{\rm off}$  increased from  $5.4 \times 10^6$  to  $9.7 \times 10^6$ . The gate-leakage current density of HfO<sub>2</sub> TFTs is about 1  $\mu$ A/cm<sup>2</sup> at  $V_{\rm gs}=5$  V and is lower than that of SiO $_2$  TFTs by more than two times. The high gate capacitance density resulted from the high- $\kappa$  gate dielectric could effectively improve the performance of HfO2 TFTs. Moreover, for devices with the same EOT, the drawback of high gate-leakage current density of HfO<sub>2</sub> devices could be improved more effectively than that of SiO<sub>2</sub> ones because of the thicker physical thickness of HfO<sub>2</sub> [17], [18]. The EOT of HfO<sub>2</sub> TFTs at ON-state is only 7.3 nm. Possible reasons for the slightly low- $\kappa$  value of 20.4 are the poly-Si gate depletion owing to the low activation temperature and the interfacial layer between HfO2 and Si channel [19], [20]. The slightly lower effective mobility of HfO<sub>2</sub> TFTs may be due to the additional scattering from HfO2 dielectric. The OFF-state current of the HfO<sub>2</sub> TFTs increases more rapidly than that of the SiO<sub>2</sub> TFTs as the gate voltage decreases continuously. This phenomenon is explained by the higher electric field near the drain side due to thinner EOT of the HfO<sub>2</sub> TFTs. It could be relaxed by lightly doped drain (LDD) or gate overlapped lightly doped drain (GOLDD) structures [21], [22].

To examine the short-channel effect of TFTs with different gate dielectrics, the threshold-voltages  $(V_{\rm th})$  rolloff of HfO<sub>2</sub> and SiO<sub>2</sub> TFTs are compared in Fig. 4. For poly-Si TFTs, the threshold-voltage rolloff is dominated by the decreasing of number of grain boundary as the devices scale down [23]. For the long-channel poly-Si TFTs, the large number of grain boundaries in the channel raises the threshold voltage and degrades the effective mobility [24]. The HfO<sub>2</sub> TFTs with ultrathin EOT and large gate capacitance density can speedily fill the trap states at grain boundary and turn on the devices fast; therefore, not only release the grain-boundary effect but also lower the threshold voltage effectively.

# IV. CONCLUSION

High-performance TFTs with HfO<sub>2</sub> as gate dielectric, which provide thin EOT and high gate capacitance density are demonstrated for the first time. Compared to the TFTs with SiO<sub>2</sub>

as gate dielectric, the electrical characteristics including the threshold voltage, subthreshold swing, ON/OFF current ratio, carrier mobility, as well as  $V_{\rm th}$  rolloff are effectively improved. These results suggest that HfO<sub>2</sub> is a good candidate to serve as a gate-dielectric material for high-performance poly-Si TFTs.

### REFERENCES

- [1] T. Nishibe, "Low-temperature poly-Si TFTs by excimer laser annealing," in *Proc. Mater. Res. Soc. Symp.*, 2001, vol. 685E, pp. D6.1.1–D6.1.5.

- [2] B.-D. Choi, H.-S. Jang, O.-K. Kwon, H.-G. Kim, and M.-J. Soh, "Design of poly-Si TFT-LCD panel with integrated driver circuits for an HDTV/XGA projection system," *IEEE Trans. Consum. Electron.*, vol. 21, no. 3, pp. 100–103, Mar. 2000.

- [3] J. K. Lee, J. B. Choi, S. M. Seo, C. W. Han, and H. S. Soh, "The application of tetraethoxysilane (TEOS) oxide to a-Si: H TFT's as the gate insulator," in *Proc. SID Dig.*, 1998, vol. 29, pp. 439–442.

- [4] A. Takami, A. Ishida, J. Tsutsumi, T. Nishibe, and N. Ibaraki, "Threshold voltage shift under the gate bias stress in low-temperature poly-silicon TFT with the thin gate oxide film," in *Proc. Int. Workshop AM-LCD*, Tokyo, Japan, Jul. 2000, pp. 45–48.

- [5] M. Y. Um, S.-K. Lee, and H. J. Kim, "Characterization of thin film transistor using Ta<sub>2</sub>O<sub>5</sub> gate dielectric," in *Proc. Int. Workshop AM-LCD*, Tokyo, Japan, Jul. 1998, pp. 45–46.

- [6] Z. Jin, H. S. Kwok, and M. Wong, "High-performance polycrystalline SiGe thin-film transistors using Al<sub>2</sub>O<sub>3</sub> gate insulators," *IEEE Electron Device Lett.*, vol. 19, no. 12, pp. 502–504, Dec. 1998.

- [7] B. W. Busch, O. Pluchery, Y. J. Chabal, D. A. Muller, R. L. Opila, J. R. Kwo, and E. Garfunkel, "Materials characterization of alternative gate dielectrics," MRS Bull., vol. 27, no. 3, pp. 206–211, Mar. 2002.

- [8] H. S. P. Wong, "Beyond the conventional transistor," IBM J. Res. Develop., vol. 46, no. 2/3, pp. 133–168, Mar./May 2002.

- [9] C. Hobbs, H. Tseng, K. Reid, B. Taylor, L. Hebert, R. Garcia, R. Hegde, J. Grant, D. Gilmer, A. Franke, V. Dhandapani, M. Azrak, L. Prabhu, R. Rai, S. Bagchi, J. Conner, S. Backer, F. Dumbuya, B. Nguyen, and P. Tobin, "80 nm poly-Si gate CMOS with HfO<sub>2</sub> gate dielectric," in *IEDM Tech. Dig.*, 2001, pp. 651–654.

- [10] Y. Kim, C. Lim, C. D. Young, K. Mathews, J. Barnett, B. Foran, A. Agarwal, G. A. Brown, G. Bersuker, P. Zeitzoff, M. Gardner, R. W. Murto, L. Larson, C. Metzner, S. Kher, and H. R. Huff, "Conventional poly-Si gate MOS-transistors with a novel, ultra-thin Hf-oxide layer," in VLSI Symp. Tech. Dig., 2003, pp. 167–168.

- [11] N. Yamauchi, J.-J. J. Hajjar, R. Reif, K. Nakazawa, and K. Tanaka, "Characteristics of narrow-channel polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 38, no. 8, pp. 1968–1969, Aug. 1991.

- [12] Y. C. Wu, C. Y. Chang, T. C. Chang, P. T. Liu, C. S. Chen, C. H. Tu, H. W. Zen, Y. H. Tai, and S. M. Sze, "High performance and high reliability polysilicon thin-film transistors with multiple nano-wire channels," in *IEDM Tech. Dig.*, 2004, pp. 777–780.

- [13] T. K. Kang, C. C. Wang, B. Y. Tsui, and Y. H. Li, "Selectivity investigation of HfO<sub>2</sub> to oxide using wet etching," in *Proc. Semicond. Manuf. Technol.* Workshop, 2004, pp. 87–90.

- [14] H. C. Cheng, F. S. Wang, and C. Y. Huang, "Effects of NH<sub>3</sub> plasma passivation on n-channel polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 44, no. 1, pp. 64–68, Jan. 1997.

- [15] J. R. Hauser and K. Ahmed, "Characterization of ultrathin oxides using electrical C-V and I-V measurements," in *Proc. AIP Conf. Charact.* and Metrol. ULSI Technol., 1998, vol. 449, pp. 235–239.

- [16] X. Garros, C. Leroux, D. Blin, J.-F. Damlencourt, A.-M. Papon, and G. Reimbold, "Investigation of HfO<sub>2</sub> dielectric stacks deposited by ALD with a mercury probe," in *Proc. Conf. Solid-State Device Res.*, 2002, pp. 411–414.

- [17] B. H. Lee, L. Kang, W. J. Qi, R. Nieh, Y. Jeon, K. Onishi, and J. C. Lee, "Ultrathin hafnium oxide with low leakage and excellent reliability for alternative gate dielectric application," in *IEDM Tech. Dig.*, 1999, pp. 133–136.

- [18] S. Datta, G. Dewey, M. Doczy, B. S. Doyle, B. Jin, J. Kavalieros, R. Kotlyar, M. Metz, N. Zelick, and R. Chau, "High mobility Si/SiGe strained channel MOS transistors with HfO<sub>2</sub>/TiN gate stack," in *IEDM Tech. Dig.*, 2003, pp. 653–656.

- [19] J. J. Lee, J. S. Maa, D. J. Tweet, and S. T. Hsu, "Strain silicon thin film transistors fabricated on glass," *Appl. Phys. Lett.*, vol. 86, no. 3, pp. 103504.1–103504.3, 2005.

- [20] Y. Kim, G. Gebara, M. Freiler, J. Barnett, D. Riley, J. Chen, K. Torres, J. Lim, B. Foran, F. Shaapur, A. Agaral, P. Lysaght, G. A. Brown,

- C. Young, S. Borthakur, H.-J. Lin, B. Nguyen, P. Zeitzoff, G. Bersuker, D. Derro, R. Bergmann, R. W. Nurto, A. Hou, H. R. Huff, E. Shero, C. Pomarede, M. Givens, M. Mazanec, and C. Werkhoven, "Conventional n-channel MOSFET devices using single layer HfO $_2$  and ZrO $_2$  as high- $\kappa$  gate dielectrics with polysilicon gate electrode," in *IEDM Tech. Dig.*, 2001, pp. 455–458.

- [21] W. Y. So, K. J. Yoo, S. I. Park, H. D. Kim, B. H. Kim, and H. K. Chung, "Novel self-aligned LDD/offset structure for poly-Si thin film transistors," in *Proc. SID*, 2001, pp. 1250–1253.

- [22] K. Ohgata, Y. Mishima, and N. Sasaki, "A new dopant activation technique for poly-Si TFTs with a self-aligned gate-overlapped LDD structure," in *IEDM Tech. Dig.*, 2000, pp. 205–208.

- [23] S. Chopra and R. S. Gupta, "An analytical model for current–voltage characteristics of a small-geometry poly-Si thin-film transistor," *Semicond. Sci. Technol.*, vol. 15, no. 11, pp. 1065–1070, Nov. 2000.

[24] A. G. Lewis, T. Y. Huang, I. W. Wu, R. H. Bruce, and A. Chiang, "Physical

- [24] A. G. Lewis, T. Y. Huang, I. W. Wu, R. H. Bruce, and A. Chiang, "Physical mechanisms for short channel effects in polysilicon thin film transistors," in *IEDM Tech. Dig.*, 1989, pp. 349–352.