# Design of ESD Protection Diodes With Embedded SCR for Differential LNA in a 65-nm CMOS Process

Chun-Yu Lin, Member, IEEE, and Mei-Lian Fan

Abstract—The pin-to-pin electrostatic discharge (ESD) issue for a differential low-noise amplifier (LNA) was studied in this work. A new design of ESD protection diodes with an embedded silicon-controlled rectifier (SCR) was proposed to protect the gigahertz differential LNA. The proposed ESD protection design was modified from the conventional ESD protection design without adding any extra device. The SCR path was established directly from one differential input pad to the other differential input pad so the pin-to-pin ESD robustness can be improved. This design had been verified in a 65-nm CMOS process. Besides, this design had been further applied to a 24-GHz LNA in the same 65-nm CMOS process. Experimental results had shown that the proposed ESD protection design for the differential LNA can achieve excellent ESD robustness and good RF performances.

Index Terms—Differential low-noise amplifier (LNA), diode, electrostatic discharge (ESD), RF, silicon-controlled rectifier (SCR).

### I. INTRODUCTION

ANOSCALE CMOS technologies have been used to implement RF integrated circuits (ICs) with the advantages of scaling-down feature size, low power consumption, high integration capability, improving high-frequency characteristics, and low cost for mass production [1]. In an RF receiver, the low-noise amplifier (LNA) plays an important role because it is the first stage in the RF receiver. A differential configuration is used for LNA design because the advantages of common-mode noise rejection, less sensitivity to substrate noise, supply noise, and bond-wire inductance variation [2]–[4]. In addition, the differential output signals of the differential LNA can be directly connected to the differential inputs of the double balanced mixer [5].

The RF circuits realized in CMOS technologies are susceptible to electrostatic discharge (ESD) events, which may damage the IC products [6]. The LNA is usually connected to the external of the RF receiver chip. Therefore, on-chip ESD protection circuits must be added at the first stage of the RF receiver.

Manuscript received February 03, 2014; revised July 14, 2014; accepted August 31, 2014. Date of publication September 22, 2014; date of current version November 03, 2014. This work was supported by the Taiwan Semi-conductor Manufacturing Company (TSMC), by the Ministry of Science and Technology, Taiwan under Contract MOST 103-2220-E-003-001, by the Biomedical Electronics Translational Research Center, National Chiao Tung University, Taiwan, and by National Taiwan Normal University, Taiwan.

C.-Y. Lin is with the Department of Electrical Engineering, National Taiwan Normal University, Taipei 106, Taiwan (e-mail: cy.lin@ieee.org).

M.-L. Fan is with the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMTT.2014.2356975

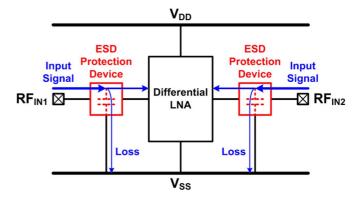

Fig. 1. Differential LNA with ESD protection devices.

As shown in Fig. 1, the ESD protection circuits are added to the input pads of the differential LNA (RF $_{\rm IN1}$  and RF $_{\rm IN2}$ ) against ESD damages. Several ESD protection designs have been reported for the RF LNA [7]–[12], including the differential LNA. Parasitic capacitance of the ESD protection device is one of the most important design considerations for a gigahertz differential LNA. A typical specification for a gigahertz RF circuit on human-body-model (HBM) ESD robustness and the maximum parasitic capacitance of the ESD protection device are 2 kV and 200 fF, respectively [13], [14]. If we consider the type of circuit designed, frequency of operation, quality factor, and acceptable reflection coefficient for the circuit, the parasitic capacitance may be more strictly limited.

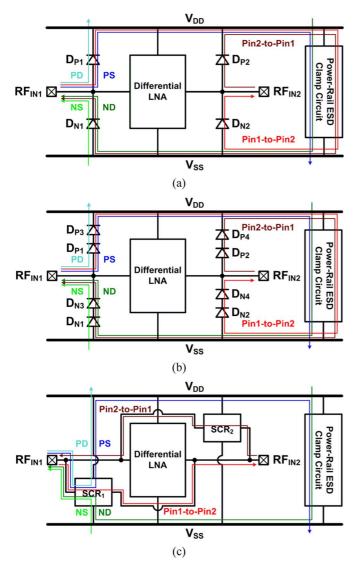

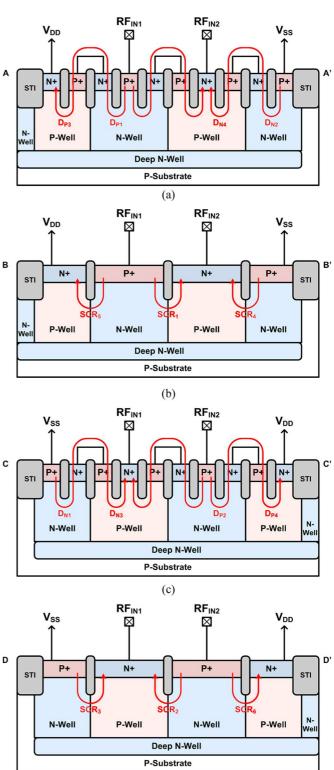

In the ESD-test standards, there are several ESD-test pin combinations. Besides the positive-to- $V_{DD}$  (PD), positive-to- $V_{SS}$ (PS), negative-to- $V_{DD}$  (ND), and negative-to- $V_{SS}$  (NS) ESD tests, the pin-to-pin ESD test is also specified to evaluate ESD robustness of the differential input pads. Under the pin-to-pin ESD test, one input pad is stressed with the other input pad relatively grounded, while all the other pads including all  $V_{DD}$ and  $V_{SS}$  pads are floating [15]. The conventional ESD protection design with dual diodes has been generally used for gigahertz differential LNAs [3], as shown in Fig. 2(a). Under pin1-to-pin2 ESD stresses, the ESD current will be discharged through the  $D_{P1}$ ,  $V_{DD}$  bus, power-rail ESD clamp circuit,  $V_{SS}$ bus, and  $D_{\rm N2}$ . The pin-to-pin ESD stress was the most critical ESD event for the differential input pads since the pin-to-pin ESD current path is longer than PD, PS, ND, or NS ESD current paths. To adapt some applications, the ESD protection design with stacked diodes has also been used [16], as shown in Fig. 2(b). The optimization on layout style of stacked diodes has been studied to achieve lower turn-on resistance, lower parasitic capacitance, and higher ESD robustness [17]. However,

Fig. 2. Differential LNA with conventional ESD protection design of: (a) dual diodes, (b) stacked diodes, and (c) cross-coupled SCR.

the pin-to-pin ESD stress was still critical in the ESD protection design with stacked diodes. The silicon-controlled rectifier (SCR) has been reported to be useful for ESD protection with low parasitic capacitance, fast enough turn-on speed, and high ESD robustness [18]. The ESD protection design with a dual SCR has been presented to improve the pin-to-pin ESD robustness [7] because the clamping voltage of the SCR is much lower than that of the diode under ESD stress. To further reduce the voltage drop under pin-to-pin ESD stress, the ESD protection design with a cross-coupled SCR has been presented [8], as shown in Fig. 2(c). Under pin-to-pin ESD stresses, the ESD current will be discharged through SCR<sub>1</sub> or SCR<sub>2</sub>. In this design, the trigger circuit of the SCR is needed to enhance the turn-on speed of the SCR under ESD stress. The cross-coupled SCR and power-rail ESD clamp circuit need to be co-designed; therefore, this ESD protection design may be hard for an RF circuit designer to apply ESD protection in the gigahertz differential LNA.

In this work, a novel ESD protection design by using ESD protection diodes with an embedded SCR is proposed for effective ESD protection in the gigahertz differential LNA. All

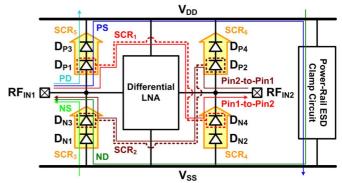

Fig. 3. Proposed ESD protection design.

the components used in the proposed design are embedded in a compact cell. The proposed ESD protection design in this paper is suitable for an RF circuit designer in order for them to easily apply ESD protection in the gigahertz differential LNA.

#### II. PROPOSED ESD PROTECTION DESIGN

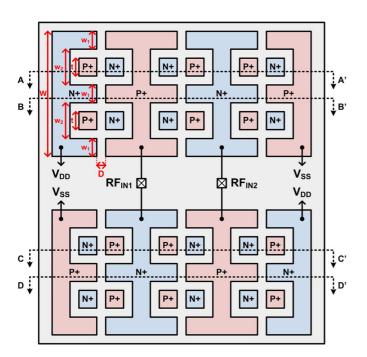

The new proposed ESD protection design utilizes stacked diodes with an embedded SCR, as shown in Fig. 3. Similar to the ESD protection design with stacked diodes in Fig. 2(b), eight diodes are used in the proposed design. Without adding an extra device, the proposed design combines P + /N-well diodes  $(D_{P1}, D_{P2}, D_{N1}, \text{ and } D_{N2})$  and P-well/N+ diodes  $(D_{P3}, D_{P4}, D_{N3}, \text{ and } D_{N4})$  to form the embedded P + /N-well/P-well/N+ SCR paths (SCR<sub>3</sub>, SCR<sub>4</sub>, SCR<sub>5</sub>, and  $SCR_6$ ) by using layout skill. Besides, by putting  $D_{P1}$  and  $D_{\rm N4}$  ( $D_{\rm P2}$  and  $D_{\rm N3}$ ) together in the layout, another embedded  $SCR_1$  ( $SCR_2$ ) exists. To implement this design, the layout top view and the device cross-sectional view of the proposed ESD protection design are shown in Figs. 4 and 5. The ESD current paths along the A-A' direction include  $D_{P3}, D_{P1}, D_{N4}, D_{N2}$ , and the parasitic stacked diodes from  $RF_{\rm IN1}$  to  $RF_{\rm IN2}$ . The ESD current paths along the B-B' direction include SCR<sub>5</sub>, SCR<sub>1</sub>, and SCR<sub>4</sub>. Similarly, the ESD current paths along the C-C' direction include  $D_{N1}, D_{N3}, D_{P2}, D_{P4}$ , and the parasitic stacked diodes from RF<sub>IN2</sub> to RF<sub>IN1</sub>, and those along the D–D' direction include  $SCR_3$ ,  $SCR_2$ , and  $SCR_6$ .

The width of diode path (T) is equal to twice the width of t in Fig. 4, and the width of the SCR path (W) is the sum of all segments of  $w_1$  and  $w_2$ . In the beginning of the ESD stress, the diode paths will turn on to discharge the initial currents and then the SCR paths will take over to discharge the primary currents. The diode path also plays the role of the trigger circuit of the SCR device to enhance its turn-on speed [19], [20]. Since the primary ESD currents are designed to be discharged through the SCR paths, the distance from anode to cathode of the SCR (D) is wished to be minimized. The turn-on resistance of the SCR can be lowered by using this layout style.

As PD ESD stress on the  $RF_{IN1}$  pad, the ESD current will be discharged by the forward-biased stacked diodes ( $D_{P1}$  and  $D_{P3}$ ) with embedded  $SCR_5$ . During PS ESD stress on the  $RF_{IN1}$  pad, the ESD current will be discharged through  $D_{P1}$  and  $D_{P3}$  with embedded  $SCR_5$  and the power-rail ESD clamp circuit. As NS ESD stress on the  $RF_{IN1}$  pad, the ESD current will be discharged by  $D_{N1}$  and  $D_{N3}$  with embedded  $SCR_3$ .

Fig. 4. Layout top view of proposed ESD protection design.

During ND ESD stress on the  $RF_{\rm IN1}$  pad, the ESD current will be discharged through the power-rail ESD clamp circuit and  $D_{\rm N1}$  and  $D_{\rm N3}$  with embedded SCR<sub>3</sub>. As pin-to-pin ESD stress from  $RF_{\rm IN1}$  to  $RF_{\rm IN2}$  (pin1-to-pin2), the ESD current can be discharged by the parasitic stacked diodes with embedded SCR<sub>1</sub>. During pin-to-pin ESD stress from  $RF_{\rm IN2}$  to  $RF_{\rm IN1}$  (pin2-to-pin1), the ESD current can be discharged by the other parasitic stacked diodes with embedded SCR<sub>2</sub>. Compared with the conventional ESD protection designs, the proposed ESD protection design provides the whole chip ESD protection for all ESD-test pin combinations with the lowest clamping voltage. Therefore, the proposed ESD protection design is expected to have better ESD robustness.

To verify the proposed design in a silicon chip, a 65-nm CMOS process is used in this work. The width of the SCR path (W) is selected to be 40  $\mu$ m, which is estimated to pass 2-kV HBM ESD tests. The widths of the diode path (T) are selected to be W/2, W/4, or W/8. The distance from anode to cathode of SCR (D) is 0.32  $\mu$ m. For comparison purposes, the ESD protection designs with dual diodes and stacked diodes are also implemented in the same 65-nm CMOS process. In each test circuit, the dimensions of diodes and power-rail ESD protection circuits are all identical. All these dimensions of test circuits are listed in Table I. These test circuits are arranged with a four-port ground–signal–ground–signal–ground (G-S-G-S-G) style in the layout to facilitate the on-wafer RF measurement.

### III. EXPERIMENTAL RESULTS OF TEST CIRCUIT

# A. Parasitic Capacitance and Insertion Loss

With the on-wafer measurement, the four-port S-parameters of the test circuits were measured by using the vector network analyzer. The source and load resistances to the test circuits are

Fig. 5. Cross-sectional view of proposed ESD protection design along: (a)A-A', (b) B-B', (c) C-C', and (d) D-D'.

(d)

kept at  $50 \Omega$ . The parasitic capacitance can be extracted from the S-parameters. In order to extract the intrinsic characteristics of the test circuits in high frequencies, the parasitic effects of the G–S–G–G-G pads have been removed by using the de-embedding technique.

| Structure          | W<br>(μm) | T<br>(μm) | D<br>(μm) | C @ 24<br>GHz (fF) | PD<br>HBM<br>(kV)   | PS<br>HBM<br>(kV)    | ND<br>HBM<br>(kV)    | NS<br>HBM<br>(kV)    | Pin-to-Pin<br>HBM<br>(kV) | Pin-to-Pin<br>TLP V <sub>t1</sub><br>(V) | Pin-to-Pin<br>TLP V <sub>hoid</sub><br>(V) | Pin-to-Pin<br>TLP I <sub>CP</sub><br>(A) |

|--------------------|-----------|-----------|-----------|--------------------|---------------------|----------------------|----------------------|----------------------|---------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|

| Proposed<br>Design | 40        | 5         |           | 121.5              | 3<br>3<br>3.25      | 3<br>3<br>3          | 3<br>3<br>3          | 3<br>3<br>3          | 2.75<br>2.75<br>2.75      | 1.3                                      | 1.1                                        | 1.1                                      |

|                    |           | 10        | 0.32      | 120.6              | 2.5<br>2.5<br>2.75  | 2.75<br>2.75<br>2.75 | 2.5<br>2.5<br>2.75   | 2.5<br>2.5<br>2.5    | 2.5<br>2.5<br>2.5         | 1.3                                      | 1.2                                        | 1.0                                      |

|                    |           | 20        |           | 113.6              | 2.25<br>2.25<br>2.5 | 2.25<br>2.5<br>2.5   | 2.25<br>2.25<br>2.25 | 2.25<br>2.25<br>2.25 | 2<br>2.25<br>2.25         | 1.6                                      | 1.4                                        | 1.0                                      |

| Dual<br>Diodes     | 40        | N/A       | N/A       | 122.9              | 2<br>2<br>2.25      | 2<br>2<br>2.25       | 2<br>2<br>2          | 2<br>2<br>2          | 1.75<br>1.75<br>2         | 2.0                                      | 2.4                                        | 0.8                                      |

| Stacked<br>Diodes  | 40        | N/A       | N/A       | 83.4               | 2.5<br>2.25<br>2.5  | 2<br>2<br>2.5        | 2<br>2<br>2.5        | 2<br>2<br>2          | 1.75<br>2<br>2            | 2.8                                      | 4.5                                        | 0.9                                      |

$\label{table I} \mbox{TABLE I}$  Design Parameters and Measurement Results of Test Circuits

Fig. 6. Measured parasitic capacitances of test circuits.

Fig. 7. Measured insertion losses of test circuits.

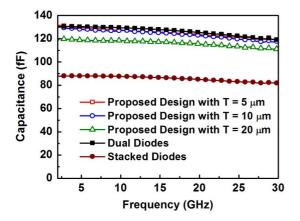

Fig. 6 shows the extracted parasitic capacitances seen at  $RF_{\rm IN1}$  or  $RF_{\rm IN2}$  of the test circuits from 1 to 30 GHz. With the narrower T, which is identical to the narrowed  $w_2$  and the widened  $w_1$ , the parasitic capacitances are slightly increased. The parasitic capacitance of the proposed design is lower than 200 fF, and the proposed ESD protection design is expected to have much better ESD robustness.

The extracted insertion losses seen at  $RF_{\rm IN1}$  or  $RF_{\rm IN2}$  of the test circuits from 1 to 30 GHz are shown in Fig. 7. At 24 GHz, the insertion loss of the proposed design with  $W=40~\mu{\rm m}$  and  $T=5~\mu{\rm m}/10~\mu{\rm m}/20~\mu{\rm m}$  is 1.43 dB/1.38 dB/1.31 dB, and those of the dual-diode and stacked-diode ESD protection are 1.41 and 1.05 dB, respectively.

### B. Leakage Current

The standby leakage currents from  $V_{DD}$  to  $V_{SS}$  of the test circuits, including the power-rail ESD clamp circuit, under 1.2-V bias are measured. At 25 °C, the leakage current of the proposed design with  $W=40~\mu\mathrm{m}$  and  $T=5~\mu\mathrm{m}/10~\mu\mathrm{m}/20~\mu\mathrm{m}$  is 4.39  $~\mu\mathrm{A}/4.31~\mu\mathrm{A}/4.31~\mu\mathrm{A}$ , while those of the dual-diode and

stacked-diode ESD protection are 4.31 and 4.34  $\mu$ A, respectively. As the temperature increased to 100 °C, the leakage current of the proposed design with  $W=40~\mu{\rm m}$  and  $T=5~\mu{\rm m}/10~\mu{\rm m}/20~\mu{\rm m}$  is 15.34  $\mu{\rm A}/15.32~\mu{\rm A}/15.23~\mu{\rm A}$ , while those of the dual-diode and stacked-diode ESD protection are 15.15 and 15.58  $\mu{\rm A}$ , respectively. The proposed ESD protection design has almost the same leakage current as the dual-diode and stacked-diode ESD protection.

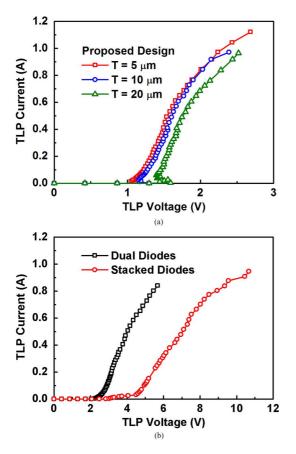

### C. ESD Robustness

The HBM ESD robustness of the test circuits have been evaluated by the ESD tester. The HBM ESD pulses are stressed to each test circuit under PD, PS, ND, NS, and pin-to-pin ESD stress conditions. The failure criterion is defined as the I-V curve seen between test pads shifting over 30% from its original curve after ESD stressed at every ESD test level. All ESD robustness of the test circuits are measured three times (three samples). All these measured ESD robustness are listed in Table I. According to the measurement results, the proposed design with  $W=40~\mu{\rm m}$  and  $T=5~\mu{\rm m}/10~\mu{\rm m}/20~\mu{\rm m}$  can pass the

Fig. 8. TLP I–V curves of: (a) proposed design and (b) conventional designs under pin-to-pin stress.

2.75-kV/2.5-kV/2-kV HBM ESD test, which is obtained from the lowest level of the test results. The dual- or stacked-diode ESD protection with the same  $W=40~\mu\mathrm{m}$  can only pass the 1.75-kV HBM ESD test. Even though the test results varied among the samples, the HBM ESD robustness of the proposed design are still higher than those of the dual- and stacked-diode ESD protection.

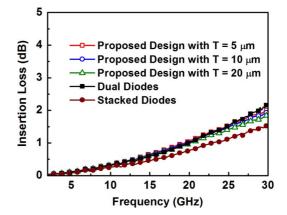

# D. Transmission-Line-Pulsing (TLP) I-V Characteristics

To investigate the turn-on behavior and the *I–V* curve in the high-current region of the ESD protection circuit, the TLP system with 10-ns rise time and 100-ns pulsewidth is used [21]. The TLP-measured *I–V* characteristics of the ESD protection circuit under pin-to-pin stress are shown in Fig. 8. The trigger voltages  $(V_{t1})$  of the proposed designs are 1.3–1.6 V, while those of the dual diodes and stacked diodes are 2.0 and 2.8 V, respectively. The holding voltage  $(V_{\text{hold}})$  of the proposed designs are 1.1-1.4 V, while those of the dual diodes and stacked diodes are 2.4 and 4.5 V, respectively. Besides, the current compression point  $(I_{\rm CP})$ , which is defined as the current level, deviates from the linearly extrapolated low-current curve by 20% [22] of the test circuits that are also measured. The  $I_{\rm CP}$ of the proposed designs are 1.0–1.1 A, while those of the dual diodes and stacked diodes are 0.8 and 0.9 A, respectively. All TLP-measured I-V characteristics are listed in Table I. The proposed ESD protection design with lower  $V_{t1}$ , lower  $V_{\text{hold}}$ , and higher  $I_{\text{CP}}$  is more suitable for ESD protection.

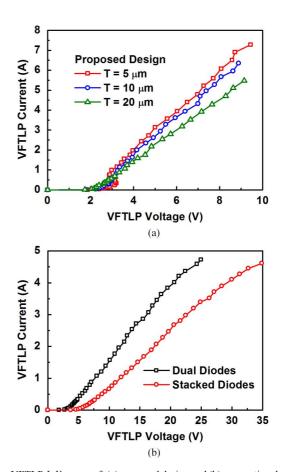

Fig. 9. VFTLP I-V curves of: (a) proposed design and (b) conventional designs under pin-to-pin stress.

The proposed ESD protection design especially has the lower clamping voltage, and it can provide effective ESD protection on the gigahertz differential LNA.

# E. Very Fast Transmisson-Line-Pulsing (VFTLP) I–V Characteristics

Another VFTLP system with 0.2-ns rise time and 1-ns pulsewidth is used to evaluate the ESD protection circuit in faster ESD-transient events. The VFTLP system can be used to capture the transient behavior of the ESD protection circuit in the time domain of the charged-device-model (CDM) ESD event [23]. The VFTLP-measured *I–V* characteristics of the ESD protection circuit under pin-to-pin stress are shown in Fig. 9. The proposed ESD protection design is fast enough to be turned on under such a fast-transient pulse.

# IV. APPLICATION OF PROPOSED ESD PROTECTION DESIGN TO 24-GHz DIFFERENTIAL LNA

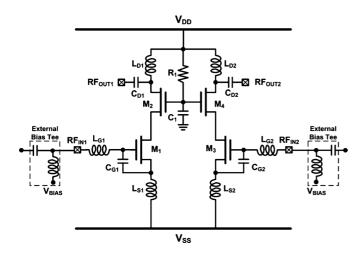

# A. Differential LNA

The differential LNA is designed to operate at 24 GHz with a  $V_{DD}$  supply of 1.2 V. The circuit schematic of the reference LNA without ESD protection is shown in Fig. 10. The architecture of common-source inductive degeneration is applied to match the source impedance (50  $\Omega$ ) at resonance. Using the cascode configuration can achieve good isolation between the input and output. Moreover, the cascode configuration reduces

Fig. 10. Differential LNA without ESD protection.

the Miller effect and provides good stability. The dimensions of the input nMOS transistors were designed according to the optimization of the noise figure (NF) [24]. The power consumption was also considered simultaneously. With the deep N-well structure, the P-well (bulk) region of each nMOS transistor can be fully isolated from the common P-substrate so the source and bulk terminals are connected together to eliminate the body effect. All of the inductors are the on-chip spiral inductors implemented by the top metal layer. The active and passive devices are fully integrated in the silicon chip in the 65-nm CMOS process.

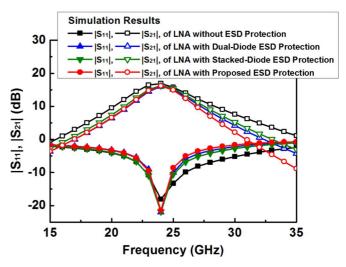

The RF characteristics of the differential LNA with and without ESD protection are simulated by using the microwave circuit simulator ADS. The LNA have been retuned after adding the ESD protection circuits. Since the device model of the proposed ESD protection design is not available in the given CMOS process, a 200-fF capacitor at each input pad of the differential LNA is used to simulate the proposed ESD protection design. Fig. 11 shows the post-layout simulation results of the differential LNA with and without ESD protection. These LNAs exhibit good input matching ( $|S_{11}| < -15 \text{ dB}$ ) around 24 GHz. The LNA without ESD protection has 16.9-dB  $|S_{21}|$  gain at 24 GHz. After adding the ESD protection circuits, the  $|S_{21}|$  gain of the LNA with dual-diode, stacked-diode, and proposed ESD protection designs are 16.0, 16.3, and 16.2 dB, respectively. The P1dB of the LNA without ESD protection, the LNA with dual diodes, the LNA with stacked diodes, and the LNA with proposed design are -14, -13, -13, and -13 dBm, respectively, and the third-order intermodulation intercept point (IIP3) are -4, -3, -3, and -3 dBm, respectively.

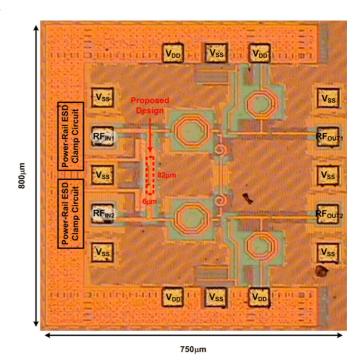

The LNA with and without ESD protection circuits have been fabricated in the same 65-nm CMOS process. The proposed ESD protection design with  $W=40~\mu m$  and  $T=10~\mu m$  is used to protect the  $RF_{IN1}$  and  $RF_{IN2}$  pads of the differential LNA. This ESD protection circuit has been verified to pass the 2.5-kV HBM ESD test. Fig. 12 shows a chip photograph of the ESD-protected LNA. For comparison purposes, the ESD protection designs with dual diodes and stacked diodes are also used to protect the  $RF_{IN1}$  and  $RF_{IN2}$  pads of the other test LNA. The area of each LNA is 750  $\mu m \times 800~\mu m$ , including all pads.

Fig. 11. Simulated  $|S_{11}|$  and  $|S_{21}|$  of the LNA with and without ESD protection.

Fig. 12. Chip photograph of differential LNA with proposed ESD protection design.

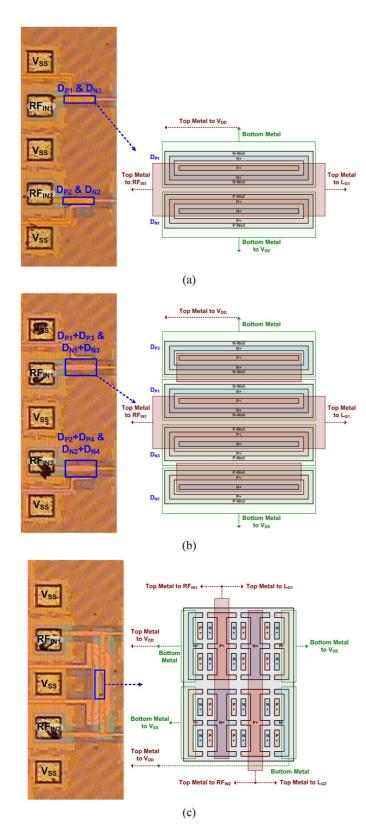

Fig. 13 shows enlarged photographs of the ESD protection circuits used in the ESD-protected LNA. The metal routing of each ESD protection circuit is also shown in Fig. 13. The ESD devices are connected by using a top metal with 10- $\mu$ m width and a bottom metal with >30- $\mu$ m width.

# B. Experimental Results

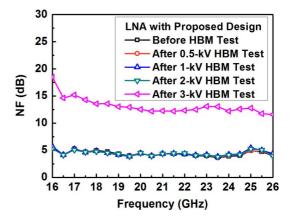

The RF characteristics are measured on wafer through G–S–G–S–G microwave probes. Each LNA operates with the 1.2-V  $V_{DD}$  supply and draws a total current of 18 mA. The used bias voltage driven through the external bias tee is 0.65 V. The RF performances of all LNA are measured before and after ESD stress. The measured  $|S_{21}|$  parameters and NFs of all the LNAs are shown in Figs. 14–21. The peak gain frequency

Fig. 13. Chip photograph and metal routing of: (a) dual-diode ESD protection, (b) stacked-diode ESD protection, and (c) proposed ESD protection.

of the LNA is shifted to about 21 GHz. The shift of the peak gain frequency may be due to the inaccurate device model as frequency higher than 20 GHz since the device model is only promised below 20 GHz in the given CMOS process. Before

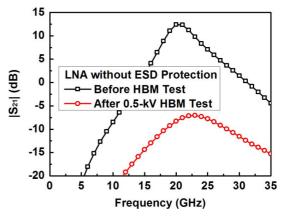

Fig. 14. Measured  $|S_{21}|$  of the LNA without ESD protection.

Fig. 15. Measured NF of the LNA without ESD protection.

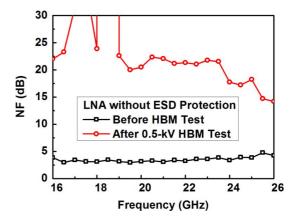

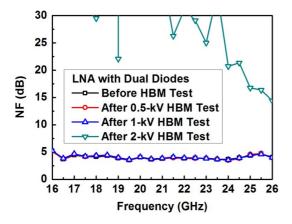

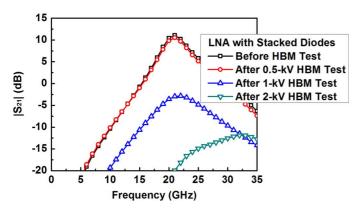

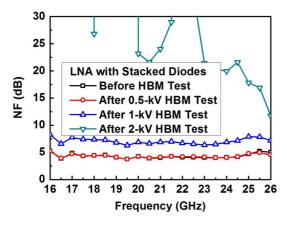

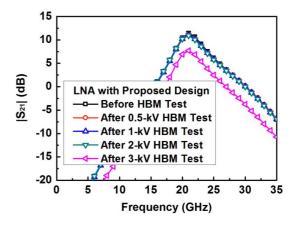

Fig. 16. Measured  $|S_{21}|$  of the LNA with dual-diode ESD protection.

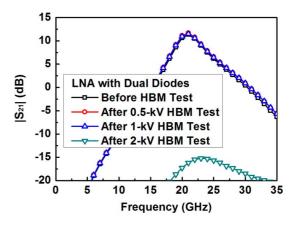

ESD stress, the  $|S_{21}|$  at 21 GHz of the LNA without ESD protection, the LNA with dual diodes, the LNA with stacked diodes, and the LNA with proposed design are 12.3, 11.3, 11.1, and 11.5 dB, respectively, the  $|S_{11}|$  at 21 GHz are all lower than -15 dB, and the NF at 21 GHz are 3.1, 3.8, 4.0, and 4.3 dB, respectively.

To verify the ESD protection ability, the RF performances of all the LNA after ESD tests are re-measured. All PD, PS, ND, NS, and pin-to-pin modes of HBM ESD stresses are performed to the LNA. The RF performances of the LNA without ESD protection are severely degraded after 0.5-kV HBM ESD tests,

Fig. 17. Measured NF of the LNA with dual-diode ESD protection.

Fig. 18. Measured  $|S_{21}|$  of the LNA with stacked-diode ESD protection.

Fig. 19. Measured NF of the LNA with stacked-diode ESD protection.

as shown in Figs. 14 and 15. The RF performances of the LNA with dual- and stacked-diode ESD protections are degraded after 2- and 1-kV HBM ESD tests, respectively, as shown in Figs. 16–19. In contrast, the RF performances of the LNA with the proposed ESD protection design are still excellent matching after 2-kV HBM ESD stress, as shown in Figs. 20 and 21.

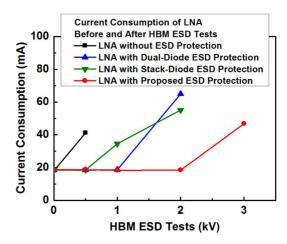

The current consumptions of all the LNA after ESD tests are re-measured. Fig. 22 shows the measured current consumptions of all the LNA before and after HBM ESD tests in which 0 kV indicates that the LNA was before the HBM ESD tests.

Fig. 20. Measured  $|S_{21}|$  of the LNA with proposed ESD protection.

Fig. 21. Measured NF of the LNA with proposed ESD protection.

Fig. 22. Measured current consumptions of the LNA before and after HBM ESD tests.

# C. Failure Analysis

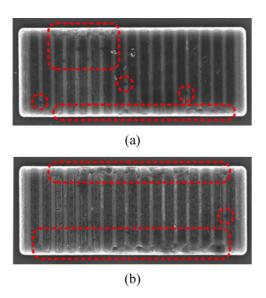

After ESD tests, the LNA with and without ESD protection circuits are analyzed. The scanning electron microscope (SEM) was used to find the failure locations.

The SEM photographs of the LNA without ESD protection after 0.5-kV HBM ESD tests are shown in Fig. 23. The failure

Fig. 23. SEM photograph of: (a)  $M_1$  and (b)  $M_3$  in the LNA without ESD protection after 0.5-kV HBM ESD tests.

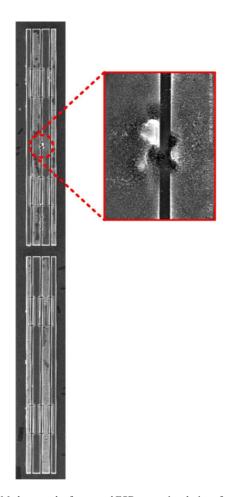

Fig. 24. SEM photograph of proposed ESD protection design after 3-kV HBM ESD tests.

points are located at the gates of  $M_1$  and  $M_3$ . The SEM photographs of the LNA with dual- and stacked-diode ESD protections after 2-kV HBM ESD tests are also taken. The failure

points are still located at the gates of  $M_1$  or  $M_3$ . The failure mechanism indicates that the conventional ESD protection design cannot effectively clamp the overshooting voltage to protect the gate oxide from damage. The SEM photographs of the LNA with proposed ESD protection design after 3-kV HBM ESD tests is shown in Fig. 24. The failure point is located at the embedded  $SCR_1$ .

### V. CONCLUSION

The proposed ESD protection diodes with an embedded SCR has been developed for the gigahertz differential LNA. Without adding an extra device, the proposed design combines P + /N-well diodes and P-well/N+ diodes to form the embedded P+/N-well/P-well/N+ SCR paths by using layout skill, and this design also includes the trigger circuit of the SCR to enhance the turn-on speed. The proposed ESD protection design has been verified in a 65-nm CMOS process with low parasitic capacitance, low clamping voltage, and high ESD robustness. The proposed ESD protection design with  $W=40~\mu\text{m}, T=10~\mu\text{m}, 120.6\text{-fF}$  parasitic capacitance, and 2.5-kV HBM ESD robustness has been applied to a differential LNA. Measurement results verify the RF performances and confirm the ESD protection ability of the proposed ESD protection design.

#### ACKNOWLEDGMENT

The authors would like to thank Prof. M.-D. Ker, National Chiao Tung University, Taiwan, and M.-H. Song, J.-C. Tseng, L.-W. Chu, K.-J. Chen, S.-M. Cheng, B.-T. Chen, C.-P. Jou, and M.-H. Tsai, all with the Taiwan Semiconductor Manufacturing Company, for their great help during design and measurement.

### REFERENCES

- B. Razavi, "CMOS technology characterization for analog and RF design," *IEEE J. Solid-State Circuits*, vol. 34, no. 3, pp. 268–276, Mar. 1999

- [2] A. Balankutty and P. Kinget, "An ultra-low voltage, low-noise, high linearity 900-MHz receiver with digitally calibrated in-band feed-forward interferer cancellation," *IEEE J. Solid-State Circuits*, vol. 46, no. 10, pp. 2268–2283, Oct. 2011.

- [3] T. Chang, J. Chen, L. Rigge, and J. Lin, "ESD-protected wideband CMOS LNAs using modified resistive feedback techniques with chip-on-board packaging," *IEEE Trans. Microw. Theory Techn.*, vol. 56, no. 8, pp. 1817–1826, Aug. 2008.

- [4] A. Bevilacqua, C. Sandner, A. Gerosa, and A. Neviani, "A fully integrated differential CMOS LNA for 3–5-GHz ultrawideband wireless receivers," *IEEE Microw. Wireless Compon. Lett.*, vol. 16, no. 3, pp. 134–136, Mar. 2003.

- [5] C. Chang, P. Wang, C. Tsai, C. Li, C. Chang, H. Shih, M. Tsai, W. Wang, K. Chan, and Y. Lin, "A CMOS transceiver with internal PA and digital pre-distortion for WLAN 802.11a/b/g/n applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, 2010, pp. 435–438.

- [6] S. Voldman, ESD: RF Technology and Circuits. New York, NY, USA: Wiley, 2006.

- [7] Y.-W. Hsiao and M.-D. Ker, "A 5-GHz differential low-noise amplifier with high pin-to-pin ESD robustness in a 130-nm CMOS process," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 5, pp. 1044–1053, May 2009.

- [8] C.-Y. Lin, M.-D. Ker, and Y.-W. Hsiao, "Design of differential lownoise amplifier with cross-coupled-SCR ESD protection scheme," *Mi*croelectron. Rel., vol. 50, no. 6, pp. 831–838, Jun. 2010.

- [9] M.-D. Ker, C.-Y. Lin, and Y.-W. Hsiao, "Overview on ESD protection designs of low-parasitic capacitance for RF ICs in CMOS technologies," *IEEE Trans. Device Mater. Rel.*, vol. 11, no. 2, pp. 207–218, Jun. 2011.

- [10] M. Tsai, S. Hsu, F. Hsueh, and C. Jou, "ESD-protected K-band low-noise amplifiers using RF junction varactors in 65-nm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 12, pp. 3455–3462, Dec. 2011.

- [11] J. Gonzalez, H. Solar, I. Adin, D. Mateo, and R. Berenguer, "A 16-kV HBM RF ESD protection codesign for a 1-mW CMOS direct conversion receiver operating in the 2.4-GHz ISM band," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 9, pp. 2318–2330, Sep. 2011.

- [12] C.-Y. Lin, L.-W. Chu, and M.-D. Ker, "ESD protection design for 60-GHz LNA with inductor-triggered SCR in 65-nm CMOS process," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 3, pp. 714–723, Mar. 2012.

- [13] C. Richier, P. Salome, G. Mabboux, I. Zaza, A. Juge, and P. Mortini, "Investigation on different ESD protection strategies devoted to 3.3 V RF applications (2 GHz) in a 0.18 μm CMOS process," *J. Electrostat.*, vol. 54, no. 1, pp. 55–71, Jan. 2002.

- [14] D. Linten, S. Thijs, M. Natarajan, P. Wambacq, W. Jeamsaksiri, J. Ramos, A. Mercha, S. Jenei, S. Donnay, and S. Decoutere, "A 5-GHz fully integrated ESD-protected low-noise amplifier in 90-nm RF CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1434–1442, Jul 2005

- [15] M.-D. Ker, T.-Y. Chen, C.-Y. Wu, and H.-H. Chang, "ESD protection design on analog pin with very low input capacitance for high-frequency or current-mode applications," *IEEE J. Solid-State Circuits*, vol. 35, no. 8, pp. 1194–1199, Aug. 2000.

- [16] M. Ruberto, O. Degani, S. Wail, A. Tendler, A. Fridman, and G. Goltman, "A reliability-aware RF power amplifier design for CMOS radio chip integration," in *Proc. IEEE Int. Rel. Phys. Symp.*, 2008, pp. 536–540.

- [17] C.-Y. Lin and M.-L. Fan, "Optimization on layout style of diode stackup for on-chip ESD protection," *IEEE Trans. Device Mater. Rel.*, vol. 14, no. 2, pp. 775–777, Jun. 2014.

- [18] Q. Cui, J. Salcedo, S. Parthasarathy, Y. Zhou, J. Liou, and J. Hajjar, "High-robustness and low-capacitance silicon-controlled rectifier for high-speed I/O ESD protection," *IEEE Electron Device Lett.*, vol. 34, no. 2, pp. 178–180, Feb. 2013.

- [19] M.-D. Ker and K.-C. Hsu, "Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 2, pp. 235–249, Jun. 2005.

- [20] M. Mergens, C. Russ, K. Verhaege, J. Armer, P. Jozwiak, R. Mohn, B. Keppens, and C. Trinh, "Speed optimized diode-triggered SCR (DTSCR) for RF ESD protection of ultra-sensitive IC nodes in advanced technologies," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 3, pp. 532–542, Sep. 2005.

- [21] S. Voldman, R. Ashton, J. Barth, D. Bennett, J. Bernier, M. Chaine, J. Daughton, E. Grund, M. Farris, H. Gieser, L. Henry, M. Hopkins, H. Hyatt, M. Natarajan, P. Juliano, T. Maloney, B. McCaffrey, L. Ting, and E. Worley, "Standardization of the transmission line pulse (TLP) methodology for electrostatic discharge (ESD)," in *Proc. EOS/ESD Symp.*, 2003, pp. 372–381.

- [22] K. Bhatia, N. Jack, and E. Rosenbaum, "Layout optimization of ESD protection diodes for high-frequency I/Os," *IEEE Trans. Device Mater. Rel.*, vol. 9, no. 3, pp. 465–475, Sep. 2009.

- [23] C. Chu, A. Gallerano, J. Watt, T. Hoang, T. Tran, D. Chan, W. Wong, J. Barth, and M. Johnson, "Using VFTLP data to design for CDM robustness," in *Proc. EOS/ESD Symp.*, 2009, pp. 286–291.

- [24] L. Belostotski and J. Haslett, "Noise figure optimization of inductively degenerated CMOS LNAs with integrated gate inductors," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 7, pp. 1409–1422, Jul. 2006.

Chun-Yu Lin (M'09) received the Ph.D. degree from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 2009.

He is currently an Assistant Professor with the Department of Electrical Engineering, National Taiwan Normal University, Taipei, Taiwan. His current research interests include ESD protection designs and biomimetic circuit designs.

Dr. Lin is currently the secretary-general of the Taiwan ESD Association.

**Mei-Lian Fan** received the B.S. degree in electrical engineering from National Dong Hua University, Hualien County, Taiwan, in 2012, and the M.S. degree from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 2014.

She is currently with National Chiao Tung University. Her current research interests include ESD protection circuit designs.