### Available online at www.sciencedirect.com

# Width-dependent anomalous $CoSi_x$ sheet resistance change by Ti and TiN capping process

Yen-Ming Chen <sup>a</sup>, George C. Tu <sup>a</sup>, Ying-Lang Wang <sup>b,\*</sup>

Department of Materials Science and Engineering, National Chiao-Tung University, Hsin-Chu, Taiwan, ROC

College of Science and Engineering, National University of Tainan, Taiwan, ROC

Available online 22 August 2005

## Abstract

In order to minimize the circuit propagation delay, self-aligned silicide (salicide) technology has been widely used to reduce source/drain/gate spreading resistance and contact resistance. Cobalt silicide (CoSi<sub>2</sub>) is the most popular silicide material beyond 0.25 µm node as it has less line width dependence than titanium silicide (TiSi<sub>2</sub>). Cobalt on silicon with TiN capping or Ti capping has been widely applied for years and demonstrates a very promising manufacturability and scalability toward 0.1 µm and below. In this work, width-dependent sheet resistance change was studied and the anomalous sheet resistance behavior was observed to be very different for these two different capping materials. The different silicide profiles around active regions and shallow trench isolation (STI) interface were identified to be the root cause for this difference. The stress built at STI and active regions played an important role for silicide formation. Experimental results can conclude that capping material selection is very crucial for deep submicron ultralarge silicon integrated (ULSI) circuit.

© 2005 Elsevier B.V. All rights reserved.

Keywords: Silicide; Resistance; Active region; Shallow trench isolation

### 1. Introduction

In order to minimize the RC propagation delay along the device shrinkage, self-aligned silicide (salicide) technology has been widely used to reduce source/drain/gate spreading resistance and contact resistance. Among all silicides, Cobalt silicide (CoSi<sub>2</sub>) is the most popular material beyond 0.25 μm node due to less line width dependence than titanium silicide (TiSi<sub>2</sub>) [1]. The single layer of cobalt on silicon has been replaced by other processes, like TiN capping and Ti capping, because of the difficulties in manufacturing [2]. The TiN capping (TiN/Co/Si) process has been reported to have a large process window with respect to the control of lateral growth [3,4]. The Ti capping (Ti/Co/Si) process has been shown to be a very promising process and its scalability toward 0.1 μm and below has been demonstrated [5,6]. The reaction

mechanisms are different in TiN capping and Ti capping processes. Ti diffuses through the Co layer and accumulates at Co/SiO2 interface in the Ti capping process, but only less Ti does in TiN capping case [7]. It is a common belief that Ti serves as an oxygen scavenger. It consumes the native oxide present because of insufficient cleaning or re-oxidation prior to Co sputter. The in-situ Ar sputter applied to remove native oxide before Co deposition is usually used for the TiN capping process, but not necessary for Ti capping process [8,9]. Recently, many researches have been evaluating the performance differences between different capping materials from the perspective of sheet resistance and junction leakage [10-13]. However, no report has yet to study the impact of capping materials to the silicide formation on narrow-width active region. In this report, the Ti and TiN capping materials were investigated on 0.1 µm process. The difference of sheet resistance between Ti and TiN capping processes were studied by applying electrical measurement and transmission electronic microscopy (TEM).

<sup>\*</sup> Corresponding author. Tel.: +886 6 505 9688; fax: +886 6 505 1262. *E-mail address:* ylwang@tsmc.com (Y.-L. Wang).

# 2. Experiment

Boron-doped, p-type Si with resistivity of 10  $\Omega$  cm and a 001 orientation were used as substrates and the 90 nm process was applied for this study. Shallow trench isolation (STI) was formed with an active region width from 2 µm to 0.1 µm to evaluate the line-width effect. The N+ source/ drain and P+ source/drain were formed with As/P and BF<sub>2</sub>/ B implant, respectively. Spike rapid thermal annealing (RTA) was then applied to active the implant dose. After HF treatment, Ti capping/TiN capping and cobalt were sputtered to substrates. The different first RTA temperature recipes were applied on both Ti capping and TiN capping samples. Selective etching was performed after the first RTA to remove the unreacted cobalt. Next, a second RTA was performed with 860 °C/35 s for both the TiN capping and Ti capping samples. The 193 nm lithography was performed for contact layer after the inter-layer dielectric layer was formed through chemical vapor deposition. Finally, copper metallization was performed. The sheet resistance of silicided N+ active region was measured from two terminal Rs bars with the width from 2 µm to 0.1 µm. Junction leakage measurements were taken from finger type active region patterns. In this study, the stress effect on silicide formation was also studied. The samples were prepared on blanket wafers and the stress was measured by stress gauge which extracted stress by measuring the changes on radius of curvature. The X-ray diffraction (XRD) was performed on silicided blanket wafers for the preferred orientation study.

# 3. Results and discussion

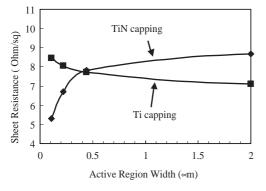

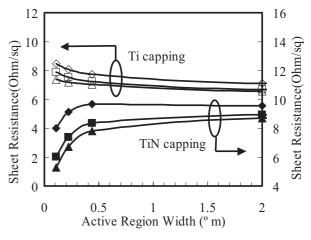

Fig. 1 showed the anomalous sheet resistance behavior for both TiN capping and Ti capping cobalt silicide. The behaviors of these two processes were very different. The sheet resistance of the TiN capping silicided active region increased as active region width decreased, while the sheet resistance of the Ti capping silicided active region decreased as active region width decreased.

Fig. 1. Sheet resistance change comparison between Ti capping and TiN capping cobalt silicide process along different active widths.

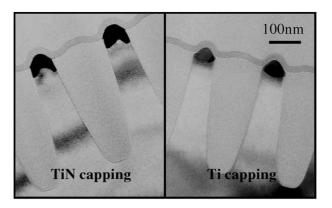

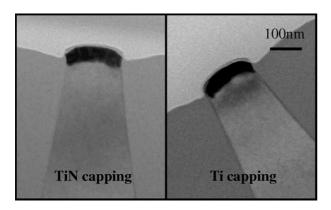

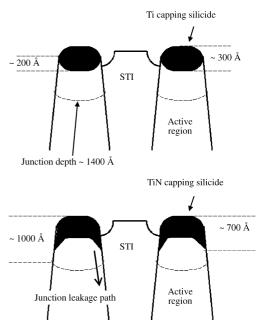

Fig. 2. The TEM cross section for TiN capping and Ti capping cobalt silicide.

The  $0.1~\mu m$  active region for both TiN capping and Ti capping silicide were compared by applying TEM cross section check. As shown in Fig. 2, the silicide formations of various capping layers were very different. The profile of silicide for the TiN capping samples showed silicide penetration at the active region edge. This anomalous "crying face" silicide growth at STI edge makes the effective active region width become larger than the design of layout drawing. The narrower the width of active region, the lower the sheet resistance of active region. In opposite to the TiN capping samples, the Ti capping samples showed active region edge silicide thinning, the so-called "smiling face" profile. The narrower active region width resulted in higher sheet resistance.

Fig. 3 showed the sheet resistance for both TiN and Ti capping samples. The TiN capping samples showed the anomalous sheet resistance roll-off became more significant when the first RTA process temperature was higher, which indicated that the anomalous silicide growth at active region edge was accelerated. Also of note was that the sheet resistance for wide active region (10  $\mu m$ ) became saturated when process temperature of RTA1 was over 510 °C. This result showed the threshold RTA1

Fig. 3. First RTA temperature effect on TiN capping ( $\blacklozenge$ , 460 °C;  $\blacksquare$ , 480 °C;  $\blacktriangle$ , 500 °C) and Ti capping ( $\diamondsuit$ , 500 °C;  $\Box$ , 520 °C;  $\triangle$ , 540 °C) cobalt silicide.

Fig. 4. TEM cross section for TiN capping and Ti capping cobalt silicide after first RTA.

temperature for completely consumed cobalt was about 510  $^{\circ}$ C. Compared to the TiN capping samples, the higher first RTA temperature slowed the anomalous sheet resistance roll-off for Ti capping one. The threshold RTA1 temperature for completely consumed cobalt was about 525  $^{\circ}$ C.

Fig. 4 showed the cross section of the silicide profiles after first RTA for TiN capping and Ti capping samples, respectively. There is no obvious difference between the profiles of these two samples, it is not like the results obtained after the second RTA. Similar profiles after the first RTA between two samples mean that the silicide profile difference at the active region edge occurred during the second RTA. When anneal temperature was around 500 °C, the forming phase was primarily CoSi, and the moving species when forming was Si. However, when process temperature was higher than 700 °C [14], the CoSi transferred to CoSi<sub>2</sub> and the moving species was Co.

Steegen et al. reported that compressive mechanical stress is induced by STI [15]. The narrower an active region becomes, the higher stress levels are that build at the active region's edges. Blanket Si substrates were prepared with silicon nitride deposited at backside of the substrate to produce compressive stress on the front side of substrate. The stress effect on silicide formation was studied. To

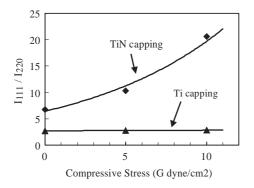

Fig. 5. Orientation intensity change by backside film stress.

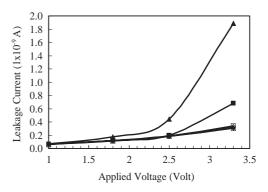

Fig. 6. First RTA temperature impact on the junction leakage current for TiN capping ( $\blacklozenge$ , 460 °C;  $\blacksquare$ , 480 °C;  $\blacktriangle$ , 500 °C) and Ti capping ( $\diamondsuit$ , 500 °C;  $\Box$ , 520 °C;  $\triangle$ , 540 °C) cobalt silicide.

produce different levels of compressive stress, the silicon nitride deposition conditions were evaluated by adjusting the gas ratio of NH<sub>3</sub>/SiH<sub>4</sub> on CVD reactor. After silicide formed on substrate front side by both Ti and TiN capping processes, the XRD check was performed. As shown in Fig. 5, the orientation preference of silicide changed as the compressive stress increased for the TiN capping process, but the orientation preference of silicide did not change for the Ti capping process. The intensity of (111) orientation  $(I_{111})$  became higher than the intensity of (220) orientation  $(I_{220})$  under compressive stress for TiN capping process. That means the compressive stress can enhance the formation for (111) CoSi<sub>2</sub>. Since the profile difference between Ti capping and TiN capping processes happened during second RTA, it was believed that compressive stress enhances the diffusion of the moving species, Co, during the CoSi to CoSi<sub>2</sub> transformation. Silicide formation of TiN

Fig. 7. Illustration for the junction leakage current path comparison between TiN and Ti capping cobalt silicide.

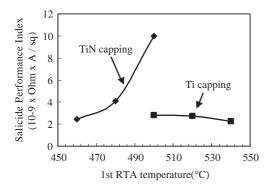

Fig. 8. Silicide performance index.

capping is enhanced by compressive stress at STI and active region interfaces, where the compressive stress is around 3 G dyn/cm<sup>2</sup>. However, the formation of the (111) CoSi<sub>2</sub> was not enhanced by compressive stress around STI and active region interface. Cheng et al. reported the stress effect on Ti silicide formation. The tensile stress enhanced the TiSi<sub>2</sub>, while the compressive stress retarded the TiSi<sub>2</sub> formation [16]. For the Ti capping process, the retarded Ti diffusion under compressive stress may make the silicide formation retarded at STI and at the active region interface. It needs further study to confirm this mechanism.

In deep submicron process, the leakage current requires careful control to ensure that the integrated circuit operates with minimal power consumption. Therefore, junction current leakage between the silicide and silicon interface also requires effective control. In this work, the active region intensive junction leakage pattern with active region width equal to 0.1 µm was measured. As Fig. 6 shows, the junction leakage of the TiN capping sample was increasing while applied voltage increased. Unlike the TiN capping process, the junction leakage for the Ti capping sample increased only slightly when the applied voltage increased. The high junction leakage of TiN capping sample resulted from the anomalous active region edge silicide growth. Furthermore, the STI edge doping anomalous re-distribution reported by Lee [17] showed that the upward doping distribution makes the junction shallower at the STI edge, and thus, enhanced the junction leakage in the TiN capping process (see Fig. 7). For the selection of the silicide, both low sheet resistance and low junction leakage are important. Fig. 8 shows the index for silicide selection. The multiple of sheet resistance and junction leakage current by 3.3 V test was used as the index. Low sheet resistance and junction leakage current are both important factors for nanodevices fabrication. According to this index, the Ti capping process showed superior performance to the TiN capping process for future deep submicron device need.

## 4. Conclusion

The anomalous silicide growth at the active region edges was reported. The TiN capping and Ti capping processes demonstrated very different behavior. High compressive stress at the STI and active region interface enhanced the silicide formation for the TiN capping process, and retarded that for Ti capping process. Penetrated silicide profile in TiN capping process induced the anomalous width-dependent sheet resistance change. This penetrated silicide profile in TiN capping process also resulted in the anomalous junction leakage as compared to the junction leakage performance of Ti capping process. The Ti capping process proved better junction leakage performance than the TiN capping process.

# Acknowledgement

The authors would like to thank the XRD measurement support from Dr. C.M. Wu.

#### References

- Q.Z. Wang, W.T. Shiau, H. Yang, J.A. Kittle, C.P. Chao, H.L. Tsai, S. Krishnan, I.C. Chen, R.H. Havemann, IEDM (1997) 107.

- [2] Q.F. Wang, A. Lauwers, B. Deweerdt, R. Verbeeck, F. Loosen, K. Maex, IEEE Trans. Semicond. Manuf. 8 (1995) 449.

- [3] A.C. Berti, V. Bolkhovsky, Proc. VLSI Multi Level Metal Integration Conf. (VMIC), 1992, p. 267.

- [4] P. Apte, A. Paranjpe, G. Pollack, IEEE Electron Device Lett. 17 (1996) 506.

- [5] Q.F. Wang, K. Maex, S. Kubicek, R. Jonckheere, B. Kerkwijk, R. Verbeeck, S. Biesemans, K. De Meyer, Proc. Symp. VLSI Technology, Kyoto, Japan, 1995, p. 17.

- [6] A. Lauwers, P. Besser, M. de Potter, E. Kondoh, N. Roelandts, A. Steegen, M. Stucchi, K. Maex, Proc. IEEE Int. Interconnect Technology Conf. (IITC), San Francisco, CA, June, 1998, p. 99.

- [7] T. Conard, E. Kondoh, H. De Witte, K. Maex, W. Vandervorst, J. Vac. Sci., A 17 (1999) 1244.

- [8] L.C. Van der Hove, IEEE Trans. Electron Devices 34 (1987) 554.

- [9] S.P. Muraka, IEEE Trans. Electron Devices 34 (1987) 2108.

- [10] K. Maex, E. Kondoh, A. Lauwers, A. Steegen, M. de Potter, P. Besser, J. Proost, Mater. Res. Soc. Symp. 525 (1998) 297.

- [11] K. Maex, A. Lauwers, P. Besser, E. Kondoh, M. de Potter, A. Steegen, IEEE Trans. Electron Devices 46 (1999) 1545.

- [12] K. Goto, A. Fushida, J. Watanabe, T. Sukegawa, K. Kawamura, T. Yamazaki, T. Sugii, IEDM (1995) 449.

- [13] J.S. Park, D.K. Sohn, Y. Kim, J.U. Bae, B.H. Lee, J.S. Byun, J.J. Kim, Appl. Phys. Lett. 73 (1998) 2284.

- [14] R.J. Schreutelkamp, P. Vandenabeele, B. Deweerdt, W. Coppye, C. Vermeiren, A. Lauwers, K. Maex, Appl. Phys. Lett. 61 (1992) 2296.

- [15] A. Steegen, Ingrid De Wolf, K. Maex, J. Appl. Phys. 86 (1999) 4290.

- [16] S.L. Cheng, H.Y. Huang, Y.C. Peng, L.J. Chen, B.Y. Tsui, C.J. Tsai, S.S. Guo, Appl. Phys. Lett. 74 (1999) 1406.

- [17] K.M. Lee, C.J. Choi, J.H. Lee, T.Y. Seong, Y.J. Park, S.W. Hong, J.G. Ahn, H.D. Lee, IEEE Trans. Electron Devices 49 (2002) 937.