## Gate-all-around polycrystalline-silicon thin-film transistors with self-aligned graingrowth nanowire channels

Ta-Chuan Liao, Tsung-Kuei Kang, Chia-Min Lin, Chun-Yu Wu, and Huang-Chung Cheng

Citation: Applied Physics Letters 100, 093501 (2012); doi: 10.1063/1.3691184

View online: http://dx.doi.org/10.1063/1.3691184

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/100/9?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Memory characteristics of laser-crystallized polycrystalline-silicon silicon-oxide-nitride-oxide-silicon thin-film transistor with location-controlled grain boundary perpendicular to the channel

Appl. Phys. Lett. 100, 244103 (2012); 10.1063/1.4724314

Bottom-gated metal-induced laterally crystallized silicon thin-film transistor with self-aligned raised source/drain Appl. Phys. Lett. **91**, 092112 (2007); 10.1063/1.2778360

Mobility enhancement of polycrystalline-Si thin-film transistors using nanowire channels by pattern-dependent metal-induced lateral crystallization

Appl. Phys. Lett. 87, 143504 (2005); 10.1063/1.2076436

High-performance polycrystalline silicon thin-film transistor with multiple nanowire channels and lightly doped drain structure

Appl. Phys. Lett. 84, 3822 (2004); 10.1063/1.1745104

Modeling and characterization of polycrystalline-silicon thin-film transistors with a channel-length comparable to a grain size

J. Appl. Phys. 89, 590 (2001); 10.1063/1.1319322

## Gate-all-around polycrystalline-silicon thin-film transistors with self-aligned grain-growth nanowire channels

Ta-Chuan Liao, <sup>1,2</sup> Tsung-Kuei Kang, <sup>3,a)</sup> Chia-Min Lin, <sup>3</sup> Chun-Yu Wu, <sup>2</sup> and Huang-Chung Cheng<sup>2</sup>

(Received 15 August 2011; accepted 13 February 2012; published online 28 February 2012)

In this letter, gate-all-around (GAA) polycrystalline silicon thin-film transistors (TFTs) with self-aligned grain-growth channels were fabricated using excimer laser crystallization (ELC) on a recessed-nanowire (RN) structure. Via the RN structure constructed by a simple sidewall-spacer formation, location-controlled nucleation and volume-confined lateral grain growth within the RN body during ELC process have been demonstrated with only one perpendicular grain boundary in each nanowire channel. Because of the high-crystallinity channel together with GAA operation mode, the proposed GAA-RN TFTs show good device integrity of lower threshold voltage, steeper subthreshold slope, and higher field-effect mobility as compared with the conventional planar counterparts. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.3691184]

Low-temperature polycrystalline silicon thin-film transistors (TFTs) have been widely used as pixel-switching elements in active-matrix display panels. Their further evolution aims at enlargement of the matrix/circuit scale, and system integration into the panel, which demands the enhancement of the TFTs' electrical performance and geometric scalability. To meet these requirements, several attempts on modifying the device structures and process techniques have been made. 1-3 Nanowire-based polycrystalline silicon TFTs with gate-all-around (GAA) or multiplegate structures have recently been reported to enhance gate controllability, thus suppressing effectively the short channel effects for geometry scaling.<sup>4–7</sup> However, most of them were prepared by solid-phase crystallization, which resulted in numerous intra- and inter-grain defects in device channels, thus causing poor field-effect mobility. Excimer laser crystallization (ELC) has become a promising method for its great potential in processing high-quality silicon grains without causing damage to glass substrates. Moreover, several modified ELC techniques for controlling the grain size and grain-boundary location of polycrystalline silicon thin films have been developed to improve electrical performance. These techniques included sequential lateral solidification,<sup>8</sup> the grain filter method, additional reflective or antireflective capping layer, 10 phase-modulated ELC, 11 dual-beam excimer laser annealing, 12 double-pulsed laser annealing, 13 selectively floating a-Si active layer,14 selectively enlarging laser crystallization, 15 and so on. However, there is a relatively little research on ELC of nanowire-type amorphous Si. In this letter, we adopted a recessed-nanowire (RN) structure for self-aligned control of the solidification direction in the device channel region of GAA TFTs during excimer laser irradiation.

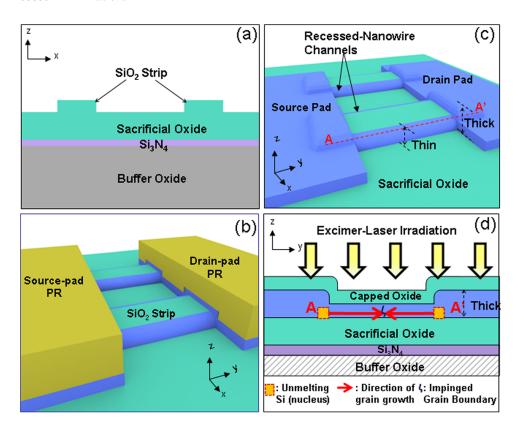

The key steps involved in processing of RN polycrystalline silicon TFTs are schematically shown in Fig. 1. A 50-nm-thick  $Si_3N_4$  (as etch-stop layer) and a 200-nm-thick tetra-ethyl-ortho-silicate (TEOS) SiO<sub>2</sub> (as sacrificial layer) films were sequentially deposited by low-pressure chemical vapor deposition (LPCVD) systems. Several strips with step height of 100-nm were patterned on the surface of the sacrificial SiO<sub>2</sub> layer by reactive ion etching (RIE), as shown in Fig. 1(a). After conformal deposition of a 100-nm-thick a-Si layer, g-line lithography was used to pattern photoresist (PR) to define the source/drain (S/D) pads, which overlapped on the two edges of those patterned SiO<sub>2</sub> strips. Subsequently, RIE was employed to remove the a-Si. The a-Si nanowire channels were patterned self-aligned to the sidewall of the SiO<sub>2</sub> strips by simply sidewall spacer formation between the S/D pads, as shown in Fig. 1(b). After the PR removal [Fig. 1(c)], a 100-nm-thick SiO<sub>2</sub> layer was capped to prevent the pattern shrinkage when a-Si nanowires were crystallized by KrF ( $\lambda = 248 \, \text{nm}$ ) excimer laser irradiation with 320 mJ/cm<sup>2</sup> at room temperature. <sup>16</sup> Figure 1(d) shows its corresponding cross-sectional illustration along the AA' direction of Fig. 1(c). Then, the suspending nanowires were constructed after both the capped SiO<sub>2</sub> and SiO<sub>2</sub>-strips were etched away (down to the Si<sub>3</sub>N<sub>4</sub> etch-stop layer) by a HF etchant. The 25-nm-thick TEOS SiO<sub>2</sub> and the 200-nm-thick phosphorous in-situ doped polycrystalline silicon were conformally deposited by the LPCVD system as the gate insulator and the gate electrode, respectively. After gate patterning, self-aligned phosphorous S/D implantation was performed at 30 keV to a dose of  $5 \times 10^{15} \, \text{cm}^{-2}$  and a 300nm-thick passivation oxide layer was deposited, followed by S/D activation. Finally, contact opening formation and metallization were carried out to complete device fabrication without any further hydrogen plasma passivation. For comparison, the conventional planar (CP) excimer-laser polycrystalline silicon TFTs were fabricated by the same process sequence.

<sup>&</sup>lt;sup>1</sup>Taiwan Semiconductor Manufacturing Company, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>2</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan

<sup>&</sup>lt;sup>3</sup>Department of Electronic Engineering, Feng-Chia University, Taichung, Taiwan

a) Author to whom correspondence should be addressed. Electronic mail: kangtk@fcu.edu.tw.

FIG. 1. (Color online) Schematic diagrams of the key fabrication steps for GAA-RN TFTs: (a) the formation of  $SiO_2$  strips, (b) and (c) the formation of a-Si deposition, nanowires, and S/D pads, and (d) the cross-sectional illustration of the capped-oxide deposition and excimer-laser crystallization along AA' direction of (c).

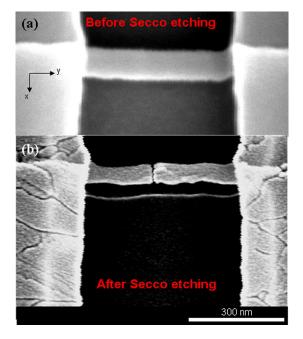

In the super lateral growth (SLG) model, the un-melted islands act as solidification seeds, from which a lateral grain growth commences. <sup>17–19</sup> According to the SLG model, a lateral temperature gradient is created between the thin and thick regions, and un-melted solid Si particles act as the seeds for lateral crystallization. If the thick region of the a-Si film is thick enough, it will be partially melted, and a lot of un-melted solid seeds will remain near the step boundary. As a result, a lateral temperature gradient is produced between the local thin and thick regions of the a-Si film, and grains will grow laterally from the un-melted solid seeds towards the completely melted region. In the proposed RN structure, as shown in Fig. 1(d), the a-Si region in the nanowire channel is thinner than that of the oxide strip sidewall of the S/D pad adjacent to the nanowire. Thus, with complete melting in the a-Si nanowire body and partial melting at the oxide-strip sidewall a-Si of the S/D pad, a lateral temperature gradient will exist between the completely melted liquid-phase region and un-melted solid-phase seeds (marked, respectively, by A and A' in Fig. 1(d)). Thus, via the RN structure, location-controlled nucleation and volume-confined lateral grain growth within the RN body during the ELC process can proceed. Figures 2(a) and 2(b) show the corresponding SEM micrographs of excimer lasercrystallized RN structure with the laser energy density of 320 mJ/cm<sup>2</sup> before and after Secco etching, respectively. The grain boundary in the RN nanowire can be clearly seen after Secco etching treatment. Because of the collision between the solidification fronts of the two S/D pads, there is only one perpendicular grain boundary existed in the middle of each RN channel. Notably, owing to the nanometersized volume of nanowire, only one nucleus at each border

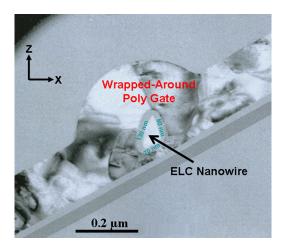

between the S/D-pad and the nanowire region (marked, respectively, by A and A' in Fig. 1(d)) can survive as the seed crystal and then grows laterally towards the volume-confined completely melted nanowire region, which accounts for the absence of parallel grain boundary in the RN channel. Figure 3 shows the cross-sectional transmission electron microscopy image of the fabricated GAA TFT with resulting excimer-laser crystallized RN channels. As can be

FIG. 2. (Color online) SEM images of recessed nanowire with excimer laser crystallization (a) before and (b) after Secco-etching treatment.

FIG. 3. (Color online) Cross-sectional transmission electron microscopy image of the fabricated GAA-RN TFTs.

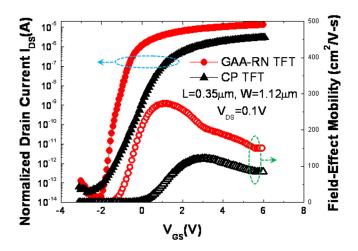

seen, there is good step-coverage on the GAA structure both for the TEOS gate oxide and phosphorous in-situ doped polyerystalline silicon gate. The vertical sidewall thickness, the horizontal width, and the bevel length of each NW channel are about 80, 70, 130 nm, respectively. Thus, the total surrounding width of each nanowire channel is 280 nm. Transfer characteristics of GAA-RN and CP TFTs are compared in Fig. 4. These devices have a gate length (L) of  $0.35 \mu m$ and a channel width (W) of 1.12  $\mu$ m, where the W of GAA-RN TFTs is defined by four nanowires with a two-dummystrip structure. The normalized drain current was defined as (measured  $I_{DS}$ )  $\times \frac{L}{W}$ . The threshold voltage (V<sub>th</sub>) was defined as the gate voltage required to obtain a normalized draincurrent of  $1 \times 10^{-8}$  A at  $V_{DS} = 0.1 \, V$ . The subthreshold swing (SS) was extracted at  $V_{DS} = 0.1 \text{ V}$ . The field-effect mobility was extracted from the peak linear transconductance at  $V_{DS} = 0.1 \text{ V}$ . For the GAA-RN devices, the linear region approaching  $V_{DS} = 0 \text{ V}$  of output characteristics performs good ohmic performance, which confirms there is no non-ideal contact effect due to the nanowire to thick S/D contacts. Owing to high-quality Si channel and GAA operation mode, the proposed GAA-RN TFTs exhibit better electrical characteristics than the conventional ones. In comparison, the mobility increases from 121 to 273 cm<sup>2</sup>/Vs, the  $V_{th}$  decreases from 0.4 to  $-0.94 \, V$ , and the SS decreases from 374 to 142 mV/decade.

In summary, via the proposed RN structure formed by a simple sidewall-spacer formation, volume-confined lateral grain growth within nanowire body during ELC has been demonstrated to form an only one perpendicular grain boundary in each Si nanowire channel. Owing to high-quality silicon channel and GAA operation mode, the proposed GAA-RN TFTs reveal high-performance characteristics as compared with the conventional planar ones.

FIG. 4. (Color online) Transfer characteristics of GAA-RN and CP TFTs.

This work was supported by the National Nano Device Laboratories, R.O.C., under Contract No. NDL 98-C05M2G-023 and the National Science Council under No. NSC 98-2218-E-009-010.

<sup>1</sup>K. Yoneda, R. Yokoyama, and T. Yamada, VLSI Symp. Circuit. Dig. 2001, 85.

<sup>2</sup>T. Nishibe and H. Nakamura, Proc. S.I.D. **2006**, 1091.

<sup>3</sup>B. Lee, Y. Hirayama, Y. Kubota, S. Imai1, A. Imaya, M. Katayama, K. Kato, A. Ishikawa, T. I. Ikeda, Y. Kurokawa *et al.*, *Dig. Tech. Pap. – Int. Solid State Circuits Conf.* **2003**, 164.

<sup>4</sup>T. C. Liao, S. W. Tu, M. H. Yu, W. K. Lin, C. C. Liu, K. J. Chang, Y. H. Tai, and H. C. Cheng, IEEE Electron Device Lett. **29**, 889 (2008).

<sup>5</sup>T. C. Liao, C. Y. Wu, S. K. Chen, M. H. Yu, T. K. Kang, and H. C. Cheng, Tech. Dig. – Int. Electron Devices Meet. 2010, 36.6.1.

<sup>6</sup>T. C. Liao, S. K. Chen, M. H. Yu, C. Y. Wu, T. K. Kang, F. T. Chien, Y. T. Liu, C. M. Lin, and H. C. Cheng, Tech. Dig. – Int. Electron Devices Meet. **2009**, 207.

M. Im, J. W. Han, H. Lee, L. E. Yu, S. Kim, C. H. Kim, S. C. Jeon, K. H. Kim, G. S. Lee, J. S. Oh *et al.*, IEEE Electron Device Lett. 29, 102 (2008).

R. S. Sposili and J. S. Im, Appl. Phys. Lett. 69, 2864 (1996).

<sup>9</sup>P. C. van der Wilt, B. D. van Dijk, G. J. Bertens, R. Ishihara, and C. I. M. Beenakker, Appl. Phys. Lett. **79**, 1819 (2001).

<sup>10</sup>L. Mariucci, R. Carluccio, A. Pecora, V. Foglietti, G. Fortunato, P. Legagneux, D. Pribat, D. Della Sala, and J. Stoemenos, Thin Solid Films 337, 137 (1999).

<sup>11</sup>C. H. Oh, M. Ozawa, and M. Matsumura, Jpn. J. Appl. Phys. Part 2 37, L492 (1998).

<sup>12</sup>R. Ishihara, A. Burtsev, and P. F. A. Alkemade, Jpn. J. Appl. Phys. Part 1 39, 3873 (2000).

<sup>13</sup>C. H. Kim, I. H. Song, W. J. Nam, and M. K. Han, IEEE Electron Device Lett. 23, 315 (2002).

<sup>14</sup>A. Hara, M. Takei, F. Takeuchi, K. Suga, K. Yoshino, M. Chida, T. Kakehi, Y. Ebiko, Y. Sano, and N. Sasaki, Jpn. J. Appl. Phys. Part 1 43, 1269 (2004).

<sup>15</sup>M. Tai, M. Hatano, S. Yamaguchi, T. Noda, S. K. Park, T. Shiba, and M. Ohkura, IEEE Trans. Electron Devices 51, 934 (2004).

M. Ozawa, C. H. Oh, and M. Matsumura, Jpn. J. Appl. Phys. 38, 5700 (1999).

J. S. Im, H. J. Kim, and M. O. Thompson, Appl. Phys. Lett. 63, 1969 (1993).

<sup>18</sup>J. S. Im and H. J. Kim, Appl. Phys. Lett. **64**, 2303 (1994).

<sup>19</sup>S. D. Brotherton, D. J. McCulloch, J. P. Gowers, J. R. Ayres, and M. J. Trainor, J. Appl. Phys. **82**, 4086 (1997).