# Electrical Reliability Issues of Integrating Low-K Dielectrics with Cu Metallization

Z. C. Wu, Z. W. Shiung, C. C. Wang, K. L. Fang, R. G. Wu, Y. L. Liu, B. Y. Tsui and M. C. Chen

Department of Electronics Engineering, National Chiao-Tung University 1001 Ta Hsueh Road, Hsinchu 300, Taiwan

W. Chang, P. F. Chou, S. M. Jang, C. H. Yu and M. S. Liang Taiwan Semiconductor Manufacturing Company No.9, Creation Rd. I, Science-Based Industrial Park Hsinchu, Taiwan

## Abstract

Electrical reliability issues of two organic aromatic low-K materials ( $K=2.6\sim2.8$ ) were investigated. Both materials show acceptable thermal stability and good dielectric barrier property against Cu penetration. C-V curve instability was observed under bias-temperature stress (BTS) for the first time. It can be explained by the model of stress induced dielectric polarization charges. This instability may be an issue of long term stability of circuits.

## Introduction

Interconnect wire parasitics (wire resistance R and intra/inter-level capacitance C) at 0.18  $\mu$  m begins to overwhelm not only the overall device delay but also the packing density, reliability, and manufacturing cost of ICs (1). To alleviate the dilemma of achieving high performance ULSI circuits without sacrificing capabilities of driving speed, crosstalk tolerance and dynamic power dissipation, it appears a must to reduce the RC time delay through the use of new materials. Therefore, process integration of Cu and low-K dielectrics has been eagerly pursued in view of their inherent benefits such as low electrical resistivity, superior electromigration resistance and low dielectric constant. However, very few studies have been performed to electrically emphasize the reliability issues of integrating low-K dielectrics with Cu (2, 3). In this work, we evaluate the dielectric barrier effectiveness for Cu penetration with regard to two species of mainstream organic aromatic low-K polymers and try to qualitatively explain the novel finding on the stress induced dielectric polarization effects, which account for electrical instabilities in C-V characteristics.

# Experimental

Electrical measurements were made on (Cu, Al)/USG(50nm)/low-K(500nm)dielectric/oxide(50nm)/p-Si oxide-sandwiched MIS capacitors. The Cu surface was further covered with a 50nm thick TaN overlayer for the prevention of

Cu oxidation. Two species of low-K dielectric were investigated; they are organic aromatic polymers with K values between 2.6 and 2.8, and are referred to hereinafter as LK1 and LK2. There is a major step of difference regarding the preparation of the LK1 and LK2 polymer samples. An adhesion promoter layer (~10nm), whose schematic structure is illustrated in Fig. 1, was first spin-on coated on the oxide surface prior to the coating of the LK2 polymer. On the other hand, this layer was not coated for the LK1 sample because the adhesion promoter material was synthesized into the bulk of the LK1 polymer. After the MIS capacitors were annealed at 400°C for 30 min in N<sub>2</sub> ambient, they were bias-temperature stressed (BTS) at 150°C with gate biases of 24 and 48V applied to produce electric fields of 0.4 and 0.8 MV/cm, respectively, for at least 30 min, which is long enough for the mobile charges to drift across the stacked insulator layer. High frequency C-V characteristics of the MIS capacitors were measured at a frequency of 1 MHz. In addition, the gate current of the MIS capacitors during the BTS was monitored, and the I-V characteristics were instantaneously measured at 150°C after the BTS. Moreover, secondary ion mass spectroscopy (SIMS) was employed to probe possible presence of Cu in the insulator layers of the MIS capacitor. Xray photoelectron spectroscopy (XPS) as well as total reflection X-ray fluorescence (TXRF) was used to measure the metallic trace element density residing in the polymer structure.

# **Results and Discussion**

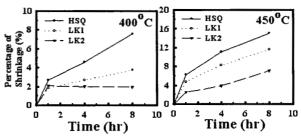

Fig. 2 shows the percentage of thickness shrinkage of HSQ (Hydrogen Silsesquioxane), LK1 and LK2 films thermally annealed in  $N_2$  ambient at 400 and 450°C as a function of annealing time. The measured data indicate that the low-K polymers show a better thermal stability than the HSQ film. In particular, the LK2 exhibits the sturdiest thermal stability.

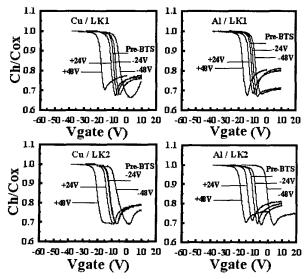

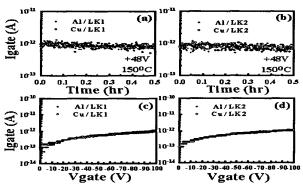

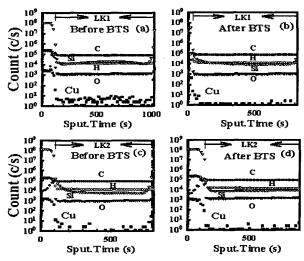

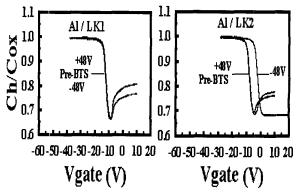

Fig. 3 shows C-V curves of the LK1 and LK2 oxidesandwiched MIS capacitors of Cu as well as Al gate before and after BTS. For both of the low-K capacitors, it is obvious that the C-V behaviors are independent of the gate metal used. This implies that the negative voltage shifts resulting from the positive bias BTS can not be attributed to the presence of Cu ions. It has been well recognized that should Cu ions readily drift into dielectrics, powerful indicators can be easily obtained not only from the reduction of gate current with stress time during the BTS but also from the fiercely increased leakage currents after the BTS (3). In this study, however, the gate current characteristics shown in Fig. 4 indicate that there are no gate current transients and differences in leakage currents between the Al and Cu gated capacitors. This shows that both LK1 and LK2 polymers act as good dielectric barriers by themselves for Cu ions drifting under these stressing conditions. Fig. 5 shows the SIMS depth profiles of a number of elements in the Cu gated oxide-sandwiched LK1 and LK2 MIS capacitor before and after the BTS; the Cu overlayers were removed prior to the SIMS measurement. The absence of Cu penetration into the polymer layers further confirms the barrier capability of both low-K polymers against Cu permeation under the stressing conditions used in this study.

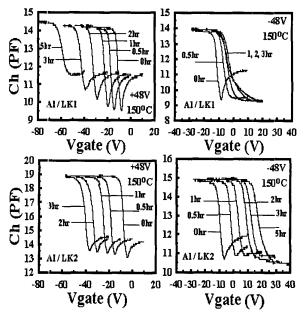

Fig. 6 shows the time dependence of C-V curve shifts for the Al-gated oxide-sandwiched low-K capacitors stressed at 150°C with +/- 48V biases. For both biasing polarities, the C-V curves made parallel shifts along the voltage axis; the C-V shifts continued even after prolonged stress of 5 hours. This may imply either a large amount of mobile ions (but not Cu ion) or stress induced polarization bound charges inherently residing in the polymer structure (3-6). A trace of elements (such as sodium) in a concentration of less than 10<sup>10</sup>cm<sup>-2</sup> was detected in the studied samples from both TXRF and XPS analyses; this is two order of magnitude smaller than the quantity required to produce the amount of C-V curve shifts observed in this study. Thus, we exclude the possibility of any major charge contribution from the mobile ions. As a result, it is reasonably presumed that stress induced dielectric polarization bound charges may be responsible for the large shift of the C-V curves. These charges may be attributed to the more polar moieties in the polymer structure (3) and need further sophisticated chemical analyses to understand their root cause. In spite of limitations imposing on the sole electrical analysis, efforts were made to find the cause regarding the distinct C-V behaviors between the LK1 and LK2 MIS capacitors stressed with a negative bias of -48V at 150°C. Under the negative -48V BTS, the positive voltage shift of C-V curves for the LK1 MIS capacitor approaches gradually a saturation value in a stress time just over one hour, while this trend was not observed for the LK2 MIS capacitors (Fig. 6). To further clarify this point, both of the Al-gated LK1 and LK2 MIS capacitors were stressed at room temperature with +/- 48V biases, as shown in Fig. 7. A positive voltage shift of about 5V resulted from the 30 min negative bias stress of -48V for the LK2 sample, while the C-V curve of the corresponding LK1 sample remained stable. The room temperature polarization effect in LK2 polymer indicates the existence of effective stress induced polarization bound negative charges which are presumably located at the polymer/oxide interfaces. This polarization effect is attributed to an adhesion layer, which is not used for the

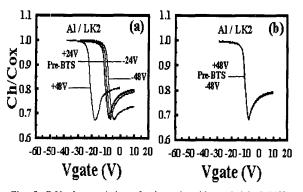

LK1 polymer, inserted between the oxide and the LK2 polymer. Without the adhesion layer at the LK2 polymer/oxide interfaces, the C-V behaviors of the LK2 MIS capacitor (Fig. 8) were found to be identical with those of the LK1 capacitor under BTS (Fig. 3 and 7). With regard to the stress induced polarization effect in the bulk of the low-K polymer, we found that both low-K polymers exhibited strong temperature dependence of polarization effect; this is evident because the C-V curves of both LK1 and LK2 samples remained fairly stable with BTS at room temperature. Similar temperature-dependent polarization effects have been observed in phosphosilicate layers and certain vapor-deposited oxides (4, 6).

#### Conclusion

Two species of organic aromatic low-K polymers (LK1 and LK2) were evaluated for structural stability against rigorous thermal treatment and for electrical reliability issues with respect to integration with Cu. It is found that the thermal stability of LK2 is superior to that of LK1 and HSQ. Although both of the low-K polymers exhibited fairly good dielectric barrier property against Cu permeation under the stressing conditions used in this study, we observed electrical instabilities in the C-V characteristics, which are presumably correlated with the stress induced dielectric polarization charges under BTS.

### References

- (1) L. Peters, Semiconductor International, Sept. 98, p. 64.

- Z. C. Wu et al., J. Electrochem. Soc., <u>146</u>, 4290(1999).

- (3) A. L. S. Loke et al., IEEE Trans. Electron Devices, ED-46, 2178(1999).

- (4) E. H. Snow and B. E. Deal, J. Electrochem. Soc., 113, 263(1966).

- E. H. Snow, A. S. Grove, B. E. Deal and C. T. Sah, J. Appl. Phys., <u>36</u>, 1664(1965).

- (6) B. E. Deal, P. J. Fleming and P. L. Castro, J. Electrochem. Soc., <u>115</u>, 300(1968).

Fig. 1 Schematic bonding structure of an adhesion promoter with X and Y representing different functional groups.

Fig. 2 Annealing time dependence of percentage shrinkage of film thickness for HSQ, LK1 and LK2 dielectrics annealed at 400 and 450  $^{\circ}$ C in N<sub>2</sub> ambient.

Fig. 3 C-V characteristics of oxide-sandwiched Cu- and Al-gated LK1 and LK2 capacitors stressed at 150°C for 30 min under various gate biases.

Fig. 4 (a)(b) current transients during BTS and (c)(d) I-V characteristics instantaneously after BTS for the oxide-sandwiched low-K capacitors biased at 150°C.

Fig. 5 SIMS depth profiles of oxide-sandwiched low-K capacitors (a)(c) before BTS, and (b)(d) after 48V/150°C BTS for 30 min.

Fig. 6 C-V characteristics of Al-gated oxide-sandwiched low-K capacitors after application of positive and negative  $48V/150^{\circ}$ C RTS

Fig. 7 C-V characteristics of Al-gated oxide-sandwiched low-K capacitors BTS at room temperature for 30 min.

Fig. 8 C-V characteristics of Al-gated oxide-sandwiched LK2 capacitors without adhesion layers stressed with +/- 48V biases at (a) 150°C and (b) room temperature for 30 min.