# Body-Tied Germanium FinFETs Directly on a Silicon Substrate

Che-Wei Chen, Cheng-Ting Chung, Guang-Li Luo, and Chao-Hsin Chien

Abstract—We fabricated body-tied Ge p-channel fin field-effect transistors (p-FinFETs) directly on a Si substrate with a high- $\kappa$ /metal gate stack. This scheme is fully compatible with Si standard processing. The FinFET structure has excellent control on the channel potential and thus can improve the short-channel effect. The diode with p+-Ge/n-Si heterojunctions illustrates a remarkably high  $I_{\rm ON}/I_{\rm OFF}>10^6$  despite the presence of misfit dislocations at the interface. The high-hole-mobility body-tied Ge p-FinFETs with a fin width  $W_{\rm Fin}$  of  $\sim\!40$  nm and a mask channel length  $L_{\rm Mask}$  of 120 nm depict a driving current of 22  $\mu{\rm A}/\mu{\rm m}$  at  $V_G=-2$  V and a low OFF-current of 3 nA/ $\mu{\rm m}$  at  $V_G=2$  V. The subthreshold characteristics with a swing of 228 mV/dec and drain-induced barrier lowering of 288 mV/V are demonstrated.

*Index Terms*—Body-tied fin field-effect transistors (FinFETs), germanium, heterojunctions, high-mobility channel.

### I. Introduction

high-mobility Ge p-channel metal-oxidesemiconductor field-effect transistor (pMOSFET) has been demonstrated as one of the possible candidates for continuously keeping up with the pace of device scaling [1]–[3]. Due to the excellent drive current and integration friendliness to the Si substrate, Ge pMOSFETs are viable for future high-speed digital-logic applications [4]-[7]. Moreover, the nonplanar fin field-effect transistor (FinFET) is an attractive replacement for the conventional planar transistor since it has better electrostatic integrity and is preferable for the ultrasmall devices [8]–[10]. To use the FinFETs for several technology nodes, there is a strong need to enhance the performance of the device with a high-mobility channel [11], [12]. However, the body-tied Ge p-channel FinFETs (p-FinFETs) have not been directly fabricated on the Si substrate yet.

In this letter, a lightly doped Ge film with low dislocation density was directly grown on an n-Si substrate channel material since we think the heteroepitaxial scheme is better

Manuscript received August 16, 2012; revised August 30, 2012; accepted September 1, 2012. Date of publication November 15, 2012; date of current version November 22, 2012. This work was supported in part by the National Science Council of Taiwan under Grant NSC 98-2221-E-009-173-MY3 and Grant NSC 101-2628-E-009-011-MY3. The review of this letter was arranged by Editor E. A. Gutiérrez-D.

C.-W. Chen and C.-T. Chung are with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: leo2591738@gmail.com).

G.-L. Luo is with the National Nano Device Laboratories, Hsinchu 30078, Taiwan.

C.-H. Chien is with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan, and also with the National Nano Device Laboratories, Hsinchu 30078,

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2012.2217473

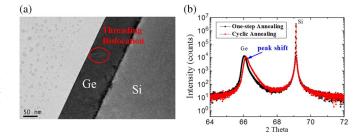

Fig. 1. (a) TEM image of a very low threading dislocation in the 120-nm blanket Ge film on the Si substrate with one-step annealing. (b) XRD of Ge on Si with one-step and cyclic annealing.

suited for the large size of the Si wafer. We find that a diode with a p<sup>+</sup>-Ge/n-Si heterojunction exhibited a relatively high  $I_{\rm ON}/I_{\rm OFF}>10^6$  despite the presence of misfit dislocations at the Ge/Si interface caused by a 4.2% lattice mismatch. The body-tied Ge p-FinFET with a fin width  $W_{\rm Fin}$  of ~40 nm and a mask channel length  $L_{\rm Mask}$  of 120 nm depicted a driving current of 22  $\mu{\rm A}/\mu{\rm m}$  and a remarkably low OFF-current of 3 nA/ $\mu{\rm m}$ .

# II. DEVICE FABRICATION

The lightly doped Ge film was grown on an n-Si (100) substrate using an ultrahigh vacuum chemical vapor deposition system after standard cleaning. After Ge deposition, the chamber temperature was raised to 900 °C annealing for 10 min (one-step annealing). Fig. 1(a) shows the cross-sectional transmission electron microscopy (TEM) image with a low threading dislocation for 120-nm blanket Ge on the Si substrate. We can see that 900 °C annealing is able to effectively reduce the threading dislocation density and improve single-crystalline Ge film quality [13]. In order to reduce threading dislocation density further, we also employed cyclic annealing through ten cycles of raising the temperature to 900 °C and then cooling it down to 420 °C over 10 min and then reheating to 900 °C and repeating the process through ten cycles [13]. In the X-ray diffraction (XRD) pattern, as shown in Fig. 1(b), we see that the position of the Ge peak shifted toward that of the Si peak, and the full-width at half-maximum [14] became more broad. These results imply the formation of a SiGe alloy at the interface by using cyclic annealing.

Active area was defined using electron-beam lithography. Boron ions were implanted (20 keV,  $1 \times 10^{15}$  cm<sup>-2</sup>) in the source/drain region. Dopant activation was performed at 500 °C for 10 s in nitrogen ambient. After the Ge fin was patterned by lithography, the Ge fin was formed by using reactive ion etching (RIE) anisotropic etching in  $\text{Cl}_2/\text{HBr}$  ambient. In addition,

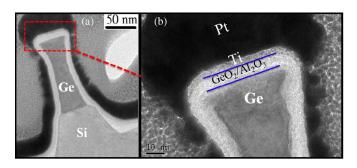

Fig. 2. (a) TEM image of the cross section of the Ge fin structure with  ${\rm GeO_2/Al_2O_3}$  and a Ti/Pt metal gate stack. (b) The gate stack structure can be clearly observed. The thickness of the  ${\rm GeO_2}$  layer is about 3 nm, and the thickness of the  ${\rm Al_2O_3}$  layer is about 5 nm.

it should be noted that the Si substrate might be etched by  $\text{Cl}_2/\text{HBr}$ , too. The spin-on-glass was coated and etched back for the device isolation. The  $\text{GeO}_2$  surface passivation using rapid thermal oxidation at 520 °C for 30 s and then atomic layer deposition (ALD)  $\text{Al}_2\text{O}_3$  high- $\kappa$  dielectric deposition was carried out after removing native oxide. The metal gate Ti (5 nm)/Pt (100 nm) was deposited by sputtering. Finally, the low-resistance Ti (5 nm)/Pt (50 nm) contact metal was defined by the liftoff process and forming gas annealing at 300 °C for 30 min. The different  $L_{\text{Mask}}$  from 1  $\mu$ m to 120 nm were fabricated.

# III. RESULTS AND DISCUSSION

Fig. 2(a) shows the cross-sectional TEM image of the Ge p-FinFET with  ${\rm GeO_2/Al_2O_3}$  and a Ti/Pt metal gate stack. The Ge fin has a  $W_{\rm Fin}$  of about 40 nm and an  $H_{\rm Fin}$  of 120 nm. Fig. 2(b) clearly shows the gate stack structure. The thickness of the  ${\rm GeO_2}$  layer was about 3 nm, and the thickness of the  ${\rm Al_2O_3}$  layer was about 5 nm.

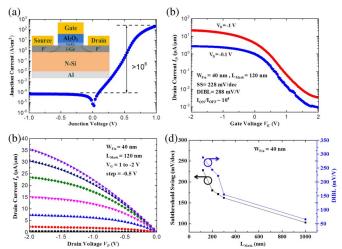

Fig. 3(a) shows the I-V characteristic of the p<sup>+</sup>-Ge/n-Si heterojunction with  $I_{\rm ON}/I_{\rm OFF} > 10^6$ . A schematic crosssectional view of the Ge p-FinFET is shown in the inset in Fig. 3(a). Leakage current density  $J_R$  is  $6.8 \times 10^{-5}$  A/cm<sup>2</sup> at -1 V. The value of  $J_R$  is remarkably low, although lots of misfit dislocations have been clearly observed at the Ge/Si interface. This result is very exciting since the dislocations may make the leakage current at the drain be intolerable via generation. Although we do not know the exact reason for such a low leakage current level right now, we think there are two possible origins: First, the energy level of the misfit dislocation is not located at and/or near the middle of the band gap, and then, the generation and recombination is not so efficient. Second, the hole concentration in Si is much lower than that in Ge [15]. Fig. 3(b) shows the  $I_{DS}$ - $V_G$  transfer characteristic of the Ge p-FinFET with an  $L_{\rm Mask}$  of 120 nm and a  $W_{\rm Fin}$  of 40 nm in the linear region at  $V_{DS} = 0.1 \text{ V}$  and in the saturation region at  $V_{DS}=1$  V. The total effective channel width ( $W_{\rm Eff}=$  $2 \times H_{\rm Fin} + W_{\rm Fin}$ ) was equal to 284 nm [16]. Drain current  $I_{DS}$  was normalized by  $W_{\rm Eff}$ . The subthreshold characteristic with subthreshold swing (S.S.) was 228 mV/dec. With the surface passivation scheme, we believe that the value of S.S. can be significantly reduced. Drain-induced barrier lowering

Fig. 3. (a) I-V characteristic of the p<sup>+</sup>-Ge/n-Si heterojunction with  $I_{\rm ON}/I_{\rm OFF}>10^6$ . (Inset) Schematic cross-sectional diagram of the Ge p-FinFET. (b)  $I_{DS}-V_G$  transfer characteristic of the Ge p-FinFET with an  $L_{\rm Mask}$  of 120 nm and a  $W_{\rm Fin}$  of 40 nm. (c)  $I_{DS}-V_{DS}$  output characteristic of the Ge p-FinFET with EOT  $\sim$ 4.9 nm. (d) S.S. and DIBL of the Ge p-FinFET with a  $W_{\rm Fin}$  of 40 nm versus  $L_{\rm Mask}$  of 120–1000 nm.

(DIBL) was 288 mV/V. This suggests that the equivalent oxide thickness (EOT) of 4.9 nm of the gate oxide is too thick and the channel dopant concentration is too low. We believe that further EOT reduction and increasing channel dopant concentration can effectively lessen DIBL. The  $I_{\rm ON}/I_{\rm OFF}$  ratio was  $\sim 10^4$ . For the Ge p-FinFET on the Si substrate, the  $I_{\rm ON}/I_{\rm OFF}$  ratio of  $\sim 10^3$  has been reported in [7] based on the rapid melting growth. Recently, a study [17] has used epitaxial Ge on the silicon on insulator (SOI) substrate for a p-FinFET, and the reported ratio was  $\sim 2 \times 10^4$ . One can see that the gate-induced drain leakage current was considerably large, particularly at  $V_G = 2 \text{ V } (I_{\text{OFF}} > 100 \text{ nA}/\mu\text{m}), \text{ in their device. Moreover,}$ the S.S. value was 350 mV/dec. Our device ( $L_{\rm Mask} = 120$  nm) not only was much smaller than that  $(L_q = 200 \text{ nm})$  in [17] but also depicted a much steeper subthreshold slope. Due to the extremely low junction leakage of the p<sup>+</sup>-Ge/n-Si heterojunction and low gate leakage (3.5 pA/ $\mu$ m at  $V_G = 2$  V), the OFF-state leakage current was as low as 3 nA/ $\mu$ m at  $V_G = 2$  V. More importantly, our device structure is a Ge body-tied FinFET, which is much preferred from the viewpoint of low cost. Threshold voltage  $V_{T(\text{lin})}$  was 0.47 V in the linear regime, and  $V_{T(\text{sat})}$ was 0.27 V in the saturation regime, which were determined by the linear extrapolation technique [18]. Certainly, these are not the required values for the high-performance circuit operation. We think  $V_T$  can be significantly shifted toward the anticipated value by adjusting the gate work function and the substrate doping profile. Fig. 3(c) shows the  $I_{DS}$ - $V_{DS}$  output characteristic of the Ge p-FinFET. The saturation current is 35  $\mu$ A/cm<sup>2</sup> at  $V_{DS}$  and  $V_{GS} = -2$  V. Both DIBL reduction and enhancement of saturation current can be also achieved through reducing EOT. Fig. 3(d) shows the S.S. and DIBL as a function of  $L_{\rm Mask}$ . We find that the values of the S.S. and DIBL of the device are acceptable for the small devices. Therefore, we demonstrated the short-channel Ge p-FinFETs directly on the Si substrate with reasonable S.S. and DIBL with a fully Si-CMOS-compatible scheme.

### IV. CONCLUSION

In conclusion, nonplanar body-tied Ge p-FinFETs directly on the Si substrate with a high- $\kappa$ /metal gate stack have been fabricated using the top-down method. The short-mask-channellength 120-nm Ge p-FinFET device with S.S. = 228 mV/dec and DIBL = 288 mV/V shows the short-channel effect, which can be improved. It also depicts a driving current of 22  $\mu$ A/ $\mu$ m at  $V_G = -2$  V and an OFF-state current of 3 nA/ $\mu$ m at  $V_G = 2$  V. The device performance can be further improved by reducing EOT and germanide formation. We think our work can shed some light on future applications of the Ge p-FinFET for the high-performance logic circuit on a large-diameter Si wafer.

# REFERENCES

- [1] S. Takagi, T. Mizuno, T. Tezuka, N. Sugiyama, T. Numata, K. Usuda, Y. Moriyama, S. Nakaharai, J. Koga, A. Tanabe, N. Hirashita, and T. Maeda, "Channel structure design, fabrication and carrier transport properties of strained-Si/SiGe-on-insulator (strained-SOI) MOSFETs," in *IEDM Tech. Dig.*, 2003, pp. 3.3.1–3.3.4.

- [2] M. Caymax, G. Eneman, F. Bellenger, C. Merckling, A. Delabie, G. Wang, R. Loo, E. Simoen, J. Mitard, B. De Jaeger, G. Hellings, K. De Meyer, M. Meuris, and M. Heyns, "Germanium for advanced CMOS anno 2009: A SWOT analysis," in *IEDM Tech. Dig.*, 2009, pp. 1–4.

- [3] D. Kuzum, J. H. Park, T. Krishnamohan, H.-S. P. Wong, and K. C. Saraswat, "The effect of donor/acceptor nature of interface traps on Ge MOSFET characteristics," *IEEE Trans. Electron Devices*, vol. 58, no. 4, pp. 1015–1022, Apr. 2011.

- [4] J. Mitard, B. De Jaeger, F. E. Leys, G. Hellings, K. Martens, G. Eneman, D. P. Brunco, R. Loo, J. C. Lin, D. Shamiryan, T. Vandeweyer, G. Winderickx, E. Vrancken, C. H. Yu, K. De Meyer, M. Caymax, L. Pantisano, M. Meuris, and M. Heyns, "Record I<sub>ON</sub>/I<sub>OFF</sub> performance for 65 nm Ge pMOSFET and novel Si passivation scheme for improved EOT scalability," in *IEDM Tech. Dig.*, 2008, pp. 1–4.

- [5] L. Witters, S. Takeoka, S. Yamaguchi, A. Hikavyy, D. Shamiryan, M. J. Cho, T. Chiarella, L.-Å. Ragnarsson, R. Loo, C. Kerner, Y. Crabbe, J. Franco, J. Tseng, W.-E. Wang, E. Rohr, T. Schram, O. Richard, H. Bender, S. Biesemans, P. Absil, and T. Hoffmann, "8 Å Tinv gate-first dual channel technology achieving low-Vt high performance CMOS," in VLSI Symp. Tech. Dig., 2010, pp. 181–182.

- [6] G. Hellings, J. Mitard, G. Eneman, B. De Jaeger, D. Brunco, D. Shamiryan, T. Vandeweyer, M. Meuris, M. Heyns, and K. De Meyer, "High performance 70-nm germanium pMOSFETs with boron LDD

- implants," IEEE Electron Device Lett., vol. 30, no. 1, pp. 88–90, Jan. 2009.

- [7] J. Feng, R. Woo, S. Chen, Y. Liu, P. Griffin, and J. Plummer, "P-channel germanium FinFET based on rapid melt growth," *IEEE Electron Device Lett.*, vol. 28, no. 7, pp. 637–639, Jul. 2007.

- [8] J. Kavalieros, B. Doyle, S. Datta, G. Dewey, M. Doczy, B. Jin, D. Lionberger, M. Metz, W. Rachmady, M. Radosavljevic, U. Shah, N. Zelick, and R. Chau, "Tri-gate transistor architecture with high- k gate dielectrics, metal gates and strain engineering," in VLSI Symp. Tech. Dig., 2006, pp. 50–51.

- [9] H. Takato, K. Sunouchi, N. Okabe, A. Nitayama, K. Hieda, F. Horiguchi, and F. Masuoka, "Impact of surrounding gate transistor (SGT) for ultrahigh-density LSIs," *IEEE Trans. Electron Devices*, vol. 38, no. 3, pp. 573– 578, Mar. 1991.

- [10] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFETs," *IEEE Electron Device lett.*, vol. 18, no. 2, pp. 74–76, Feb. 1997.

- [11] I. Ok, K. Akarvardar, S. Lin, M. Baykan, C. D. Young, P. Y. Hung, M. P. Rodgers, S. Bennett, H. O. Stamper, D. L. Franca, J. Yum, J. P. Nadeau, C. Hobbs, P. Kirsch, P. Majhi, and R. Jammy, "Strained SiGe and Si FinFETs for high performance logic with SiGe/Si stack on SOI," in *IEDM Tech. Dig.*, 2010, pp. 34.2.1–34.2.4.

- [12] B. Doyle, B. Boyanov, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, R. Rios, and R. Chau, "Tri-gate fully-depleted CMOS transistors: Fabrication, design and layout," in VLSI Symp. Tech. Dig., 2003, pp. 133–134.

- [13] H. C. Luan, D. R. Lim, K. K. Lee, K. M. Chen, J. G. Sandland, K. Wada, and L. C. Kimerling, "High-quality Ge epilayers on Si with low threading-dislocation densities," *Appl. Phys. Lett.*, vol. 75, no. 19, pp. 2909–2911, Nov. 1999.

- [14] G.-L. Luo, S.-C. Huang, C.-T. Chung, D. Heh, C.-H. Chien, C.-C. Cheng, Y.-J. Lee, W.-F. Wu, C.-C. Hsu, M.-L. Kuo, J.-Y. Yao, M.-N. Chang, C.-W. Liu, C. Hu, C.-Y. Chang, and F.-L. Yang, "A comprehensive study of Ge1-xSix on Ge for the Ge nMOSFETs with tensile stress, shallow junctions and reduced leakage," in *IEDM Tech. Dig.*, 2009, pp. 1–4.

- [15] S. M. Sze and K. K. Ng, Physics of Semiconductor Devices. Hoboken, NJ: Wiley, 2007.

- [16] H. C. Chin, X. Gong, L. Wang, H. K. Lee, L. Shi, and Y. C. Yeo, "III-V multiple-gate field-effect transistors with high-mobility In<sub>0.7</sub>Ga<sub>0.3</sub>As channel and epi-controlled retrograde-doped fin," *IEEE Electron Device Lett.*, vol. 32, no. 2, pp. 146–148, Feb. 2011.

- [17] S.-H. Hsu, C.-L. Chu, W.-H. Tu, Y.-C. Fu, P.-J. Sung, H.-C. Chang, Y.-T. Chen, L.-Y. Cho, W. Hsu, G.-L. Luo, C.W. Liu, C. Hu, and F.-L. Yang, "Nearly defect-free Ge gate-all-around FETs on Si substrates," in *IEDM Tech. Dig.*, 2011, pp. 35.2.1–35.2.4.

- [18] D. K. Schroder, Semiconductor Material and Device Characterization. Hoboken, NJ: Wiley, 2006.