# Test and Analysis of the ESD Robustness for the Diode-Connected a-IGZO Thin Film Transistors

Ya-Hsiang Tai, Hao-Lin Chiu, and Lu-Sheng Chou

Abstract—In this work, wafer level TLP testing is applied to amorphous indium–gallium–zinc–oxide (a-IGZO) thin-film transistors (TFTs) to study the factors of their electrostatic discharge (ESD) robustness. Two kinds of TFTs with  $N_2O$  and  $O_2$  treatments are subject to the ESD test. It is found that the contact resistance of the TFTs, instead of the channel quality, dominates the ESD power for them to be damaged.

Index Terms—Amorphous Indium—Gallium—Zinc Oxide thin film transistor (a-IGZO TFT), electrostatic discharge (ESD).

## I. INTRODUCTION

MORPHOUS Indium-Gallium-Zinc Oxide (a-IGZO) thin-film transistors (TFTs) have attracted more attention as one of promising candidates for next generation active matrix flat-panel displays driving element owing to their high mobility, excellent uniformity, and good applicability for low-temperature process [1]-[5]. Since the TFTs are fabricated on the glass substrates in the most applications, the electrostatic discharge (ESD) [6] is an important issue for the fabrication and reliability [7]. TFT LCDs are built from a multi-layer structure on a glass substrate to the whole product module. Most of the processes in the production combine movement, separation and friction. The different ESD types could happen in the production process. For example, some process of the friction may cause the mechanical mode (MM) ESD. The assembly process of glass and driving board may cause the chip-level charge device model (CDM) ESD [8], [9]. Besides, any movement with the human contact may cause the human body mode (HBM) ESD [10].

The transmission line pulsing (TLP) system is commonly used for CMOS device level ESD robustness testing in Integrated Circuits (ICs) is applied in this paper to simulate HBM ESD event [11]. There are a few papers using TLP to study the ESD issues of amorphous and polycrystalline silicon TFTs [12]–[20]. However, there is yet no related report regarding the effect of ESD on a-IGZO TFTs. In this work, the ESD robustness of a-IGZO TFTs in the connection of the diode-connected

Manuscript received August 03, 2012; revised February 26, 2013; accepted April 05, 2013. Date of publication May 02, 2013; date of current version August 07, 2013.

Y.-H. Tai is with the Department of Photonics & Display Institute, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: yhtai@mail.nctu.edu. tw).

H.-L. Chiu and L.-S. Chou are with the Department of Photonics & Institute of Electro-Optical Engineering, National Chiao Tung University, Hsinchu 30010, Taiwan (e-mail: dogy0304@gmail.com; tomwa.eo97g@g2.nctu.edu.tw).

Color versions of one or more of the figures are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JDT.2013.2257680

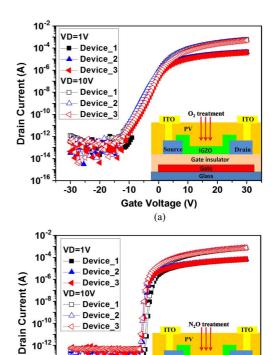

Fig. 1.  $I_D$ – $V_G$  transfer characteristics of a-IGZO TFTs with treatment of (a)  $O_2$  and (b)  $N_2O$  and their correspondent cross-section schematics.

Gate Voltage (V)

10

-20

10<sup>-16</sup>

type with different W/L fabricated on glass substrate is evaluated by the TLP measured secondary breakdown current (It2) and the breakdown voltage ( $V_{\rm BD}$ ) corresponding to it [21], [22]. Moreover, the ESD effects on the different a-IGZO TFTs with  $O_2$  and  $N_2O$  treatment are discussed.

## II. DEVICE FABRICATION

The experimental work was based on the bottom-gate TFT devices of co-planar structure with symmetrical Source/Drain (S/D) fabricated on the glass substrate. Shaped Ti/Al/Ti (50/200/50 nm) gate electrodes were capped with 400-nm-thick SiNx gate dielectric, which was deposited by plasma enhanced chemical vapor deposition (PECVD) at 370 °C. The S/D metals were deposited by DC sputtering system at room temperature with Ti/Al/Ti (50/200/50 nm). Then active layer of 30-nm-thick a-IGZO film was deposit by DC magnetron sputtering system using a target of In: Ga: Zn = 1:1:1 in atomic ratio with the O<sub>2</sub>/Ar ratio about 7%. Both N<sub>2</sub>O and O<sub>2</sub> treatments were conducted by PECVD at 170 °C with 1500 mTorr for 20 s after

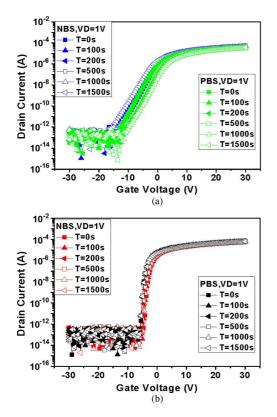

Fig. 2.  $I_D$ – $V_G$  transfer curves evolution with gate bias stress for the devices with (a)  $O_2$  treatment and (b)  $N_2O$  treatment.

the formation of IGZO thin film to obtain the different electrical characteristics for the later discussions in comparison. Both treatments were conducted at the same chamber where to form the passivation without breaking the vacuum.

After that, the devices are capped with 100 nm thick SiOx at 200 °C as protection layer to avoid the disturbance of outside surrounding. Then the via holes and ITO were patterned and shaped for device measurement. The final annealing step was conducted at 330 °C for 2 hours in the oven. The electrical characteristics are measured by Agilent 4156-C system at 25 °C in dark under 1 atmosphere pressure. The threshold voltage  $(V_T)$  is defined by the gate voltage  $(V_G)$  when the size-normalized drain current  $I_D$  reaches  $10^{-9}$  A. The subthreshold swing (S.S) and effective field mobility  $(\mu_{\rm eff})$  are extracted at drain voltage  $V_D=1$  V.

## III. DEVICE CHARACTERISTICS

Fig. 1 shows the cross section and initial transfer characteristics of fabricated devices with the two different treatments. The values of  $V_T$ ,  $\mu_{\rm eff}$  and S.S for the devices with N<sub>2</sub>O treatment are -3.93 V, 18.13 cm<sup>2</sup>/V·s, and 0.88 V/dec, accordingly, while those for O<sub>2</sub> treated samples are -2.29 V, 10.32 cm<sup>2</sup>/V·s, and 1.77 V/dec, correspondingly. It can be seen that the devices with N<sub>2</sub>O treatment have better electrical performance than O<sub>2</sub> treated devices do. The worse initial electrical characteristics of O<sub>2</sub> treated device may come from the reason that the O<sub>2</sub> treatment is a process which can generate the n-type oxygen vacancies to increase the conductivity of the device back channel as the situation in ZnO TFTs [23].

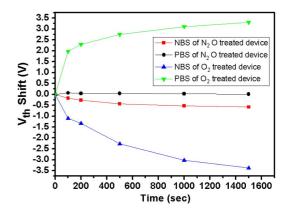

Fig. 3.  $V_{\rm T}$  shift versus stress time under NBS and PBS.

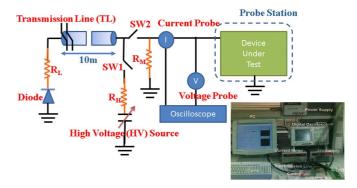

Fig. 4. Configuration of TLP system used in this paper.

For the electrical stability, the two kinds of device with different treatment were stressed with positive bias stress (PBS) of 30 V and negative bias stress (NBS) of -30 V separately. Fig. 2(a) and (b) shows the  $I_D$ – $V_G$  curves of the devices with different treatments before and after stress 1500 s. The trends of  $V_T$  shifting value versus time for the two kinds of devices under PBS and NBS are shown in Fig. 3. It is shown that devices with  $N_2O$  treatment have better electrical stability than devices with  $O_2$  treatment during the DC stress. The stress result is quite consist with previous report that devices with  $N_2O$  treatment have better electrical stability [24]–[26] owing to the effect of repairing of device back channel defect [27], [28].

#### IV. ESD TESTING AND RESULTS

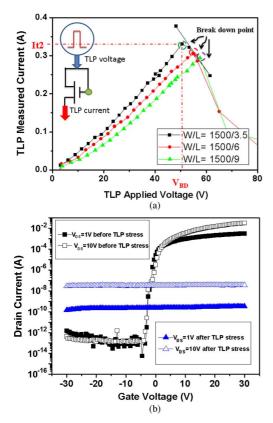

The configuration of TLP system is shown in Fig. 4 [11]. In this work, the diode-connected IGZO TFTs of different width/length (W/L) with grounded source node are subject to the ESD test as the DUTs. The TLP energy is injected from the gate/drain node to the source node, which means that the diode-connected IGZO TFT is under forward TLP stress. The failure criterion is defined when the permanent damage is observed to cause open characteristic on the TFT or the abnormal turn on resistance is observed on the TLP-measured I–V curve. At this moment, the device is expected to be permanently damaged. Fig. 5(a) shows the TLP system measurement results of the DUTs. One pair of It2 and V<sub>BD</sub> is indicated for the better illustration. One of the I<sub>D</sub>–V<sub>G</sub> curves for the damaged TFT is shown in Fig. 5(b) and

Fig. 5. TLP system measured I-V curves of the a-IGZO TFTs. (b) One of the TLP system measured device's  $I_D-V_G$  transfer curve before and after ESD testing.

compared to its initial characteristic to convince the failure of the device.

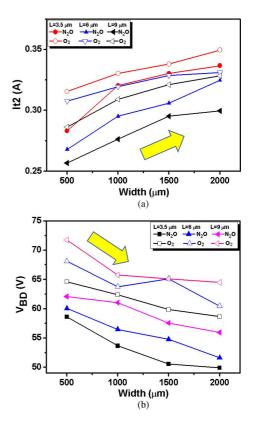

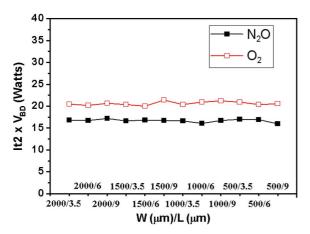

Fig. 6(a) and (b) shows the dependence of the TLP-measured It2 and  $V_{\rm BD}$  of several diode-connected devices, correspondingly. It is found that with increasing W, the value of It2 gets higher while the  $V_{\rm BD}$  becomes lower. On the other hand, with increasing L, the value of It2 becomes lower while the  $V_{\rm BD}$  becomes higher, as shown in Fig. 7(a) and (b), respectively. It is further observed that the It2 of O<sub>2</sub>-treated devices are always higher than the N<sub>2</sub>O-treated devices. Fig. 8 plots the multiplication of It2 and  $V_{\rm BD}$ , which reflects the breakdown power of ESD for the devices with different W/L. Obviously, the devices with O<sub>2</sub> treatment can sustain higher ESD power than those with N<sub>2</sub>O treatment. It hints that there might be a common mechanism resulting in the difference of the treatment effect on the devices in both ESD robustness and performance.

# V. ANALYSIS

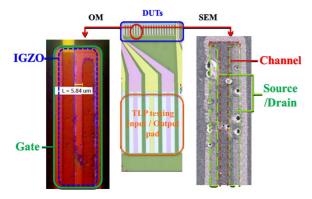

The optical microscopic (OM) observation and scanning electron microscopic (SEM) graphs of the device damaged by ESD testing are shown in Fig. 9. It is observed that the apparent damage happens not only in the channel but also the contact region, which seems even more damaged.

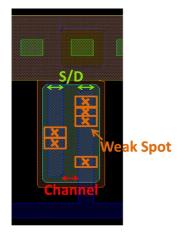

Fig. 10 illustrates the layout of the TFT testkey and the X marks which denote that the possible weak spots randomly distributed along the width. In the way of layout, the contact area scales with W. If these spots burned out at the very same moment, the ESD power should increase with W for the more

Fig. 6. (a) It2 and (b)  $V_{\rm BD}$  versus W for the same L.

Fig. 7. (a) It2 and (b)  $V_{\rm BD}$  versus L for the same W.

breakdown area. However, as shown in Fig. 8, the ESD power is independent of W. It depicts that it is the first breakdown of the weakest spot dominates the ESD power where  $V_{\rm BD}$  and It2

Fig. 8. ESD power for the devices with different W/L.

Fig. 9. OM and SEM observation of the device after the ESD testing

Fig. 10. Possible weak spots on the layout of the TFT testkey.

happen. After that, the measured TLP current corresponding to the larger TLP voltage pulse is no more significant since the device has already been damaged.

On the other hand, the contact design for the device with different L is identical. It leads us to think that the ESD power may be more related to the contact region than the channel region, which is consistent with the OM and SEM. Thus, we further analyze the devices with different treatments in the aspect of the contact resistances.

The parasitic contact resistances [29]–[31] are extracted by the measurement of  $I_D - V_G$  curves at  $V_{\rm DS} = 0.1$  V with dif-

Fig. 11. Parasitic resistance extraction for a-IGZO TFTs of (a)  $\rm O_2$  treatment and (b)  $\rm N_2O$  treatment.

ferent channel length [32]–[34], where the ON resistance of TFT  $(R_{\rm total})$  is represented as (1)

$$R_{\text{Total}} = \frac{V_{\text{DS}}}{I_{\text{DS}}} = R_D + R_S + R_{\text{ch}} \cdot L \tag{1}$$

where  $R_{\rm ch}$  is the channel resistance per unit channel length,  $R_s$  and  $R_d$  denote the source and drain resistance, respectively. With the field-effect mobility  $\mu_{\rm eff}$ , the gate insulator unit capacitor  $C_{\rm OX}$ , and the threshold voltage  $V_{\rm th}$ ,  $R_{\rm ch}$  can be represented as (2)

$$R_{\rm ch} = \frac{1}{[\mu_{\rm eff} C_{\rm OX} W (V_G - V_{\rm th} - 0.5 V_D)]}$$

(2)

By substituting (2) into (1), the contact resistances  $(R_s+R_d)$  of TFTs with different treatment can be extracted, as shown in Fig. 11. The extraction results of the contact resistance for the TFTs with  $\rm O_2$  and  $\rm N_2O$  treatment are 0.588 K $\Omega$  and 6.88 K $\Omega$ , respectively. The devices with  $\rm N_2O$  treatment have much higher contact resistance than those with  $\rm O_2$  treatment.

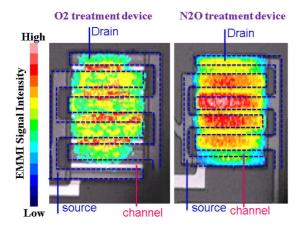

It implies that the contact resistance plays a role in the ESD robustness. The Emission Microscope (EMMI/InGaAs) observation of the devices under the gate bias of 40 V and drain bias of 20 V is further conducted to check the heat distribution. Fig. 12 shows the heat distribution of devices with  $\rm O_2$  and  $\rm N_2O$  treatments on the left and right, respectively. It is found that the hottest area of the  $\rm N_2O$  treated device is around the contact area, while that in the  $\rm O_2$  treated device is around the channel.

Such difference depicts that the current dissipates around contact area may be larger than the devices with lower contact resistance under the same applied G/D voltages. Even with better

Fig. 12. EMMI/InGaAs observation of the devices with (a) O<sub>2</sub> treatment and (b) N<sub>2</sub>O treatment under gate bias of 40 V and drain bias of 20 V.

performance and stability, the device having higher contact resistance can be less robust to ESD. Since the only differences between the two kinds of devices are the channel and contact resistances, we come to a conclusion that the contact resistance is the dominate factor that affects the ESD robustness.

#### VI. CONCLUSION

In this work, the ESD robustness of the diode-connected IGZO TFT is studied by the wafer level TLP testing. The experiment result shows that the ESD protection ability of the co-planar type diode-connected device varies with different W/L, while the multiplication of breakdown voltage and the It2 is constant. This multiplication value is corresponding to the ESD power and mainly affected by the contact resistance, instead of the active area quality. Even with the worse device performance, the devices having the lower contact resistance may sustain higher applied ESD testing voltage.

# REFERENCES

- [1] N. L. Dehuff, E. S. Kettenring, D. Hong, H. Q. Chiang, J. F. Wager, R. L. Hoffman, C. H. Park, and D. A. Keszler, "Transparent thin-film transistors with zinc indium oxide channel layer," *J. Appl. Phys.*, vol. 97, no. 6, p. 064505, 2005.

- [2] H. Q. Chiang, J. F. Wager, R. L. Hoffman, J. Jeong, and D. A. Keszler, "High mobility transparent thin-film transistors with amorphous zinc tin oxide channel layer," *Appl. Phys. Lett.*, vol. 86, no. 1, p. 013503, 2005.

- [3] M. Fryer, E. C. Colgan, E. Galligan, W. Graham, R. Horton, L. Jenkins, R. John, Y. Kuo, K. Latzko, F. Libsch, A. Lien, R. Nywening, R. Polastre, M. E. Rothwell, J. Wilson, R. Wisnieff, and S. Wright, "Planarized copper gate hydrogenated amorphous-silicon thin-film transistors for AM-LCDs," in *Mat. Res. Soc. Symp. Proc.*, 1998, vol. 37, p. 508.

- [4] P. M. Fryer, E. C. Colgan, E. Galligan, W. Graham, R. Horton, D. Hunt, K. Latzko, R. Nywening, L. Jenkins, R. John, P. Koke, Y. Kuo, F. Libsch, A. Lien, I. Lovas, R. Polastre, M. E. Rothwell, J. Souk, J. Wilson, R. Wisnieff, and S. Wright, "A six-mask TFT-LCD process using copper-cate metallurgy," in SID Dig. Tech. Papers, 1996, p. 333.

- [5] H. Sirringhaus, S. D. Theiss, A. Kahn, and S. Wagner, "Self-passivated copper gates for amorphous silicon thin-film transistors," *IEEE Elec*tron Device Lett., vol. 18, no. 3, pp. 388–390, Mar. 1997.

- [6] J. A. Salcedo, J. J. Liou, and J. C. Bernier, "Design and integration of novel SCR-based devices for ESD protection in CMOS/BiCMOS technologies," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2682–2689, Dec. 2005.

- [7] H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, "High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature RF-magnetron sputtering," *Appl. Phys. Lett.*, vol. 89, no. 11, p. 112123, 2006

- [8] F. R. Libsch and H. Abe, "ESD: How much protection is need for AMLCDs," in SID Digest Technical Papers, 1994, pp. 255–258.

- [9] Field-Induced Charged-Device Model Test Method for Electrostatic Discharge Withstand Thresholds of Microelectronic Components, JEDEC Standard JESD22-C101-A, Jun. 2000.

- [10] A. Olney, B. Gifford, J. Guravage, and A. Righter, "Real-world charged board model (CBM) failures," in *Proc. EOS/ESD Symp.*, 2003, pp. 34–43.

- [11] ESD Association Standard Test Method for Electrostatic Discharge (ESD) Sensitivity Testing—Human Body Model (HBM)—Component Level, ESD STM-5.1, 1998.

- [12] E. Fortunato, L. Pereira, P. Barquinha, A. Rego, G. Goçcalves, A. Vilà, J. Morante, and R. Martins, "High mobility indium free amorphous oxide thin film transistors," *Appl. Phys. Lett.*, vol. 92, no. 22, p. 222103, 2008.

- [13] M. Tada, S. Uchikoga, and M. Ikeda, "Power-density-dependant failure of amorphous Si TFT," in *Proc. AMLCD*, 1996, pp. 269–272.

- [14] H. Q. Chiang, J. F. Wager, R. L. Hoffman, J. Jeong, and D. A. Keszler, "High mobility transparent thin-film transistors with amorphous zinc tin oxide channel layer," *Appl. Phys. Lett.*, vol. 86, no. 1, p. 013503, 2005.

- [15] D. H. Kim, N. G. Cho, H. G. Kim, and I. D. Kim, "Highly transparent InGaZnO4 thin film transistors using Indium-doped ZnO electrodes on plastic substrate semiconductor devices, materials, processing," *Electrochem. Solid-State Lett.*, vol. 12, pp. H198–H201, 2009.

- [16] T. Yanagisawa, "Electrostatic damage and protection for TFT-LCDs," in SID Dig. Tech. Papers, 1993, pp. 735–738.

- [17] S. Uchikoga, M. Kakinoki, K. Suzuki, and M. Ikeda, "Deterioration mechanism of a-Si:H TFT caused by ESD," in *Proc. AMLCD*, 1994, pp. 128–131.

- [18] N. T. Golo, F. G. Kuper, and T. J. Mouthaan, "Analysis of the electrical breakdown in hydrogenated amorphous silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 49, no. 6, pp. 1012–1018, Jun. 2002.

- [19] N. T. Golo, F. G. Kuper, and T. J. Mouthaan, "Transmission line model testing of top-gate amorphous silicon thin film transistors," in *Proc. IRPS*, 2000, pp. 289–294.

- [20] S. C. Lee, B. C. Jeon, K. C. Moon, M. C. Lee, and M. K. Han, "Electrostatic discharge effects on polysilicon TFTs for AMLCD," in SID Dig. Tech. Papers, 2002, pp. 212–215.

- [21] B. C. Jeon, S. C. Lee, M. C. Lee, K. C. Moon, J. K. Oh, and M. K. Han, "ESD degradation analysis of poly-Si N-type TFT employing TLP (transmission line pulse) test," in *Proc. EOS/ESD Symp.*, 2002, pp. 191–196.

- [22] J. Barth, K. Verhaege, L. G. Henrry, and J. Richner, "TLP calibration, correlation, standards, new techniques," in *Proc. EOS/ESD Symp.*, 2000, pp. 85–96.

- [23] K. Remashan, D. K. Hwang, S. D. Park, J. W. Bae, G. Y. Yeom, S. J. Park, and J. H. Jang, "Effect of N<sub>2</sub>O plasma treatment on the performance of ZnO TFTs," *Electrochem. Solid-State Lett.*, vol. 11, no. 3, pp. H55–H59, 2008.

- [24] J. Park, S. Kim, C. Kim, S. Kim, I. Song, H. Yin, K. K. Kim, S. Lee, K. Hong, J. Lee, J. Jung, E. Lee, K. W. Kwon, and Y. Park, "Gate-bias stress in amorphous oxide semiconductors thin-film transistor," *Appl. Phys. Lett.*, vol. 93, no. 5, p. 053505, 2008

- Phys. Lett., vol. 93, no. 5, p. 053505, 2008.

[25] E. Fortunato, R. Barros, P. Barquinha, V. Figueiredo, S. K. Park, C. S. Hwang, and R. Martins, "Transparent p-type SnO<sub>x</sub> thin film transistors produced by reactive rf magnetron sputtering followed by low temperature annealing," Appl. Phys. Lett., vol. 97, p. 052105, 2010.

- ature annealing," *Appl. Phys. Lett.*, vol. 97, p. 052105, 2010.

[26] C. T. Tsai, T. C. Chang, S. C. Chen, I. Lo, S. W. Tsao, M. C. Hung, J. J. Chang, C. Y. Wu, and C. Y. Huang, "Influence of positive bias stress on N<sub>2</sub>O plasma improved InGaZnO thin film transistor," *Appl. Phys. Lett.*, vol. 96, no. 24, p. 242105, 2010.

- [27] M. C. Hung, H. T. Hsiao1, W. T. Lin, C. H. Tu, J. J. Chang, and P.-L. Chen, "Employ present five masks amorphous silicon thin-film transistor design and process flow to realize 5-in. InGaZnO active-matrix liquid crystal display with improved stress stability," *Jpn. J. Appl. Phys.*, vol. 50, p. 03CB0, 2011.

- [28] H. Yim, D. H. Kim, S. C. Choi, B. G. Choi, S. Lee, S. K. Kim, K. S. Park, J. U. Bae, C. D. Kim, M. Jun, and Y. K. Hwang, "Highly stable amorphous indium gallium zinc oxide thin-film transistors with N<sub>2</sub>O plasma treatment," in SID Dig. Tech. Papers, 2011, vol. 42, no. 1, pp. 1170–1172.

- [29] O. Marinov, M. Jamal Deen, U. Zschieschang, and H. Klauk, "Organic thin-film transistors: Part I—Compact DC modeling," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 2952–2961, Dec. 2009.

- [30] M. J. Deen, O. Marinov, U. Zschieschang, and H. Klauk, "Organic thin-film transistors: Part II—Parameter extraction," *IEEE Trans. Elec*tron Devices, vol. 56, no. 12, pp. 2962–2968, Dec. 2009.

- [31] M. J. Deen, M. H. Kazemeini, Y. M. Haddara, J. Yu, G. Vamvounis, S. Holdcroft, and W. Woods, "Electrical characterization of polymerbased FETs fabricated by spin-coating poly(3-alkylthiophene)," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1892–1901, Nov. 2004.

- [32] J. Kanicki, F. R. Libsch, J. Griffith, and R. Polastre, "Performance of thin hydrogenated amorphous silicon thin film transistors," *J. Appl Phys.*, vol. 69, no. 4, pp. 2339–2345, 1991.

- [33] S. Luan and G. W. Neudeck, "An experimental study of the source/ drain parasitic resistance effects in amorphous silicon thin film transistors," J. Appl. Phys., vol. 72, no. 2, p. 766, 1992.

- [34] J. Jeong, Y. Hong, J. K. Jeong, J. S. Park, and Y. G. Mo, "MOSFET-like behavior of a-InGaZnO thin-film transistors with plasma-exposed source-drain bulk region," *J. Display Technol.*, vol. 5, no. 12, pp. 495–500, Dec. 2009.

Ya-Hsiang Tai received the B.S. and Ph.D. degrees in electronic engineering from National Chiao Tung University, Taiwan, in 1990 and 1996, respectively.

He became a member of Industrial Technology Research Institute/Electronics Research & Service Organization and the TFT LCD development as a panel designer. He joined the project of low temperature polycrystalline silicon (LTPS) thin-film transistor (TFT) development in Prime View International in 2000. In 2001, he entered Toppoly Optoelectronics Corporation, to lead the team of

LTPS TFT LCD panel design. He joined the faculty of National Chiao Tung University in 2003, where he is currently a professor in the Department of Photonics and Display Institute. His current research emphases are in the areas of TFT device physics, active matrix display panel design, and system on panel.

**Hao-Lin Chiu** received the B.S. degree in electro-physics from National Chiao Tung University, Taiwan, in 2004, and the M.S. degree in electro-optical engineering in National Chiao Tung University, Taiwan, in 2006, where he is now working for his Ph.D. degree.

His current research interests include the sensor and applications of a-Si and a-IGZO TFTs.

**Lu-Sheng Chou** received the B.S. degree in physics from National Sun Yat-Sen University, Taiwan, in 2008. He is now working for his Ph.D. degree in electro-optical engineering in National Chiao Tung University, Taiwan. His current research interests include the sensor and applications of a-Si and a-IGZO TFTs.