# Improved performances in low-voltage-driven InGaZnO thin film transistors using a SiO<sub>2</sub> buffer layer insertion

Z.W. Zheng · Y.C. Chen

Received: 6 June 2013 / Accepted: 30 July 2013 / Published online: 28 August 2013 © Springer-Verlag Berlin Heidelberg 2013

**Abstract** In this paper, we report the device characteristics of indium gallium zinc oxide (IGZO) thin film transistors (TFTs) with high- $\kappa$  lanthanum aluminate (LaAlO<sub>3</sub>) based gate insulators. The IGZO TFT with single LaAlO<sub>3</sub> gate insulator has an operation voltage as low as 1.5 V but suffers a low on-off-state drive current ratio  $(I_{\rm on}/I_{\rm off})$  of  $1 \times 10^3$ , a large subthreshold swing (SS) of 0.405 V/dec and a small field effect mobility ( $\mu_{\rm FE}$ ) of 0.84 cm<sup>2</sup>/V sec. Inserting a SiO<sub>2</sub> buffer layer between IGZO active channel layer and LaAlO<sub>3</sub> gate insulator results in a reduced effective dielectric constant but with significant improved characteristics including a high  $I_{\rm on}/I_{\rm off}$  of  $6.2 \times 10^4$ , a small SS of 0.113 V/dec and a large  $\mu_{\rm FE}$  of 5.2 cm<sup>2</sup>/V sec. Such good performances can be attributed to the lowered gate leakage and reduced interface trap issue owing to the smooth SiO2 buffer layer insertion.

### 1 Introduction

At the rapid growth of flat panel display market, oxide thin film transistors (TFTs) [1–14] have attracted much attention as emerging devices that exhibit higher mobility compared to the conventional amorphous or polycrystalline silicon TFTs [15–17] and organic TFTs [18–21]. Among various oxide TFTs, ZnO-based TFTs [1–14], especially indium gallium zinc oxide (IGZO) TFTs [4–14], have been considered

Z.W. Zheng (⊠)

Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China

e-mail: wei7553@hotmail.com

YC Chen

Institute of Photonic System, National Chiao Tung University, Hsinchu 300, Taiwan

as potential candidates for flexible display applications, due to their advantages of low production cost, high mobility, excellent uniformity, good optical transparency, etc. However, the currently developing IGZO TFTs still suffer large operation voltage and low device mobility. In addition, low threshold voltage  $(V_t)$  and small subthreshold swing (SS) are also needed for high-speed operation. To solve these issues, improving the properties of active channel material in the fabrication process [7–9], such as IGZO thickness, channel composition, provides an alternative solution. Apart from the active channel layer material, the insulating material is also of great significance for high-performance TFTs. It is well known that gate dielectrics with high dielectric constant and small surface roughness allow the TFTs to have low operation voltages, because the high carrier density in the active channel layer could be induced at a relatively low voltage bias compared to traditional dielectrics and polymer insulators. Therefore, incorporating high- $\kappa$  gate materials into TFTs has been widely applied to improve the device performances [17-19].

In this paper, we report the device performances of IGZO TFTs with high- $\kappa$  lanthanum aluminate (LaAlO<sub>3</sub>) [17–19, 22] based gate dielectrics. Due to the high dielectric constant, large energy bandgap and high thermal stability of LaAlO<sub>3</sub> dielectric, low threshold voltage ( $V_t$ ) and low operation voltage can be achieved in the LaAlO<sub>3</sub>-based TFTs. However, LaAlO<sub>3</sub> dielectric still suffers interfacial issue that degrades the electron mobility as reported in the literature [22]. To solve this problem, using a SiO<sub>2</sub> buffer layer inserted between the IGZO active channel layer and LaAlO<sub>3</sub> gate insulator, improved device performances are achieved as compared to the TFTs with single LaAlO<sub>3</sub> gate dielectric, including a higher  $I_{\rm on}/I_{\rm off}$  of  $6.2 \times 10^4$ , a smaller SS of 0.113 V/dec and a larger  $\mu_{\rm FE}$  of 5.2 cm<sup>2</sup>/V sec. Such good characteristics can be attributed to lowered gate leakage cur-

938 Z.W. Zheng, Y.C. Chen

rent and reduced interfacial issue with a  $SiO_2$  buffer layer insertion [10–12, 20, 21, 23]. The present results demonstrate that IGZO TFTs with stacked LaAlO<sub>3</sub>/SiO<sub>2</sub> gate dielectrics show high potential for future high-speed and low-power applications.

## 2 Experimental details

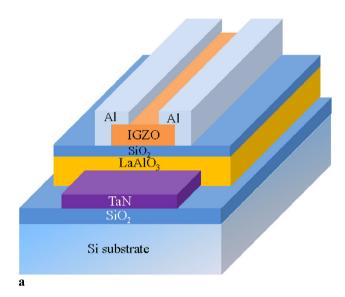

Figure 1(a) and (b) shows the schematic structure and photograph of the IGZO TFT with device micrograph in the inset, respectively. The top-contact bottom-gate type IGZO TFTs

Fig. 1 (a) Schematic structure and (b) photograph of the IGZO TFT with device micrograph in the *inset*

were prepared on the 300-nm thick insulating SiO<sub>2</sub> grown on 4-inch silicon substrates with a shadow mask process. A 50-nm thick TaN bottom gate (G) electrode was formed by physical vapor deposition (PVD) and patterned. Then, a 30-nm thick LaAlO<sub>3</sub> and 10-nm thick SiO<sub>2</sub> were deposited by e-beam evaporation at room temperature, followed by annealing in O<sub>2</sub> ambient at 400 °C to improve the gate oxide properties. Subsequently, a 40-nm thick IGZO active layer was deposited using dc reactive sputtering from an IGZO target under Ar ambient mixed with O<sub>2</sub> gas. Finally, 300-nm thick Al was thermally coated to form source (S) and drain (D) electrodes, followed by N<sub>2</sub> sintering at 300 °C to reduce contact resistance. The devices have a channel width (W)of 500  $\mu$ m and a channel length (L) of 50  $\mu$ m. The metal insulator-metal (MIM) capacitors of gate dielectrics were also fabricated side-by-side to characterize the gate capacitance and leakage current. For comparison, the TFT devices without SiO<sub>2</sub> buffer layer were also fabricated as control samples. The gate insulators were characterized by atomic force microscopy (AFM) analysis. The electrical characteristics of TFT devices were measured at room temperature using HP4156C semiconductor parameter analyzer.

#### 3 Results and discussion

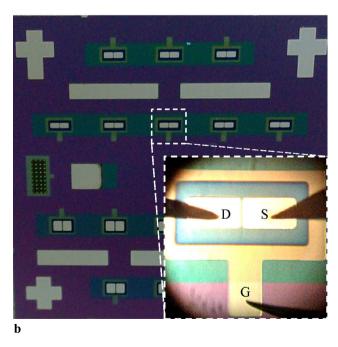

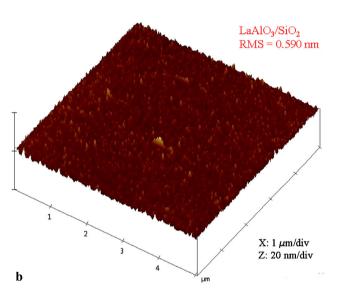

Figure 2 shows the capacitance–voltage (C-V) characteristics of the Al/[with and without SiO<sub>2</sub> buffer layer]/LaAlO<sub>3</sub>/TaN gate capacitors on the same substrate, with the current density–voltage (J-V) characteristics in the inset. A high capacitance density for gate dielectrics is needed to induce a large carrier density at a relatively low operation voltage. The high capacitance density of 62 and 23 fF/ $\mu$ m<sup>2</sup> measured at 100 kHz is obtained for the MIM capacitors without and with SiO<sub>2</sub> buffer layer, respectively, as shown in Fig. 2.

Fig. 2 C-V characteristics of Al/[with and without SiO<sub>2</sub> buffer layer]/LaAlO<sub>3</sub>/TaN gate capacitors on the same substrate, with J-V characteristics in the *inset*

It indicates the equivalent oxide thickness (EOT) of  $\sim 5.5$ and ~15 nm for single LaAlO<sub>3</sub> and stacked SiO<sub>2</sub>/LaAlO<sub>3</sub> gate dielectrics, respectively. The high dielectric constant of ~21 can be extracted for LaAlO<sub>3</sub> dielectric, while the reduced effective dielectric constant of ~10.4 is obtained for SiO<sub>2</sub>/LaAlO<sub>3</sub> gate stack. Although the insertion of SiO<sub>2</sub> buffer layer decreases effective gate capacitance and effective dielectric constant, the structure reduces the gate leakage current density  $(1.1 \times 10^{-7} \text{ A/cm}^2 \text{ @ } -1.5 \text{ V})$  further by more than one order of magnitude as compared to the single LaAlO<sub>3</sub> structure  $(2.7 \times 10^{-6} \text{ A/cm}^2 \text{ @ } -1.5 \text{ V})$  in the inset of Fig. 2. This smaller gate leakage by introducing a SiO<sub>2</sub> buffer layer could reduce the off-current level in TFT devices and improve the  $I_{\rm on}/I_{\rm off}$ , indicating that the insertion of SiO<sub>2</sub> buffer layer is a powerful solution for lowering off-state power [10-12, 20, 21, 23], in contrast to single insulator.

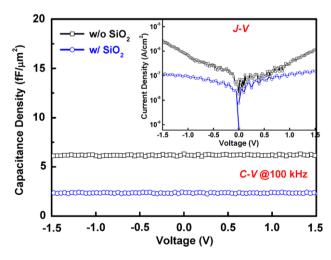

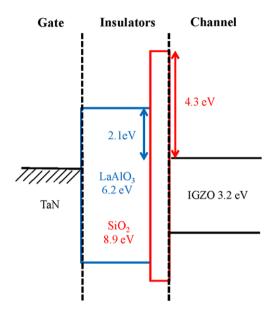

Since the surface morphology of the gate dielectrics is very critical to device performances [12–14, 21], the surface roughness of the LaAlO3 gate insulators on bottom TaN gate without and with SiO<sub>2</sub> buffer layer was examined by AFM analysis, as shown in Fig. 3(a) and (b), respectively. Smooth surfaces of single LaAlO3 and stacked SiO2/LaAlO3 dielectrics with root mean square (RMS) roughness of 0.572 and 0.590 nm are obtained, respectively. The difference in RMS roughness between single LaAlO<sub>3</sub> and SiO<sub>2</sub>/LaAlO<sub>3</sub> stack is just 0.018 nm, which is much smaller than atomic scale. It indicates that there is no degraded roughness after the deposition of SiO<sub>2</sub> buffer layer. Moreover, the SiO<sub>2</sub> buffer layer prevents the carriers moving into the gate dielectric, due to the lager conduction band offset ( $\Delta E_c$ ) of 4.3 eV between SiO2 and IGZO channel as compared to that of 2.1 eV between LaAlO<sub>3</sub> and IGZO channel [24-26], as shown in the energy band diagram in Fig. 4. This smooth surface with proper  $\Delta E_c$  as a barrier between the gate dielectric and channel is preferred and favorable to be flat gate stack to prevent gate leakage, especially for bottomgate TFT structures.

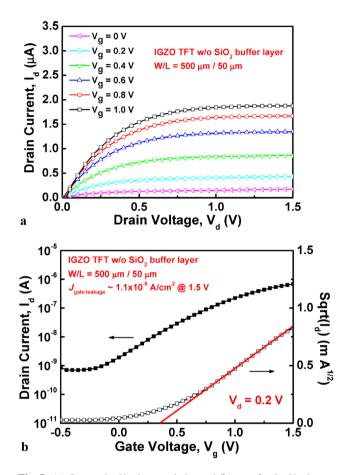

Figures 5(a) and (b) displays the output  $I_{\rm d}-V_{\rm d}$  and transfer  $I_{\rm d}-V_{\rm g}$  characteristics of the IGZO TFT without SiO<sub>2</sub> buffer layer, respectively. This TFT device behaves as in enhancement mode with good saturation characteristics and can be operated under the voltage bias as low as 1.5 V in Fig. 5(a), indicating that incorporating high- $\kappa$  LaAlO<sub>3</sub> dielectric can give an advantage of lowering the operation voltage. From the measured results, the IGZO TFT with single LaAlO<sub>3</sub> insulator shows a low  $V_{\rm t}$  of 0.36 V extracted from the linear  $I_{\rm d}^{1/2}-V_{\rm g}$  curve in Fig. 5(b) but suffers a low  $I_{\rm on}/I_{\rm off}$  of 1 × 10<sup>3</sup>, a large SS of 0.405 V/dec, which can be calculated from  $I_{\rm d}-V_{\rm g}$  curve in Fig. 5(b). Besides, a small  $\mu_{\rm FE}$  of 0.84 cm<sup>2</sup>/V sec is obtained according to the extraction from a gradual channel approximation in the linear region using the equation of  $\mu_{\rm FE}=(\partial I_{\rm d}/\partial V_{\rm g})\cdot(L/W)/V_{\rm g}$

Fig. 3 AFM images of (a) single LaAlO $_3$  and (b) stacked LaAlO $_3$ /SiO $_2$  gate insulators on bottom TaN gate

$(V_d \cdot C_g)$ , where  $I_d$ ,  $V_d$ ,  $V_g$  and  $C_g$  are the drain current, drain voltage, gate voltage and gate insulator capacitance per unit area, respectively [27].

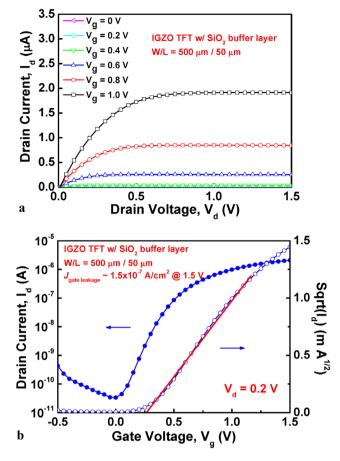

To further improve the performances of the IGZO TFTs, a SiO<sub>2</sub> was inserted as buffer layer at the interface of IGZO/LaAlO<sub>3</sub>. The output  $I_d$ – $V_d$  and transfer  $I_d$ – $V_g$  characteristics of the IGZO TFT with inserted SiO<sub>2</sub> buffer layer are shown in Fig. 6(a) and (b), respectively. Using a SiO<sub>2</sub> buffer layer, the IGZO TFT device exhibits improved performances including a high  $I_{\rm on}/I_{\rm off}$  of 6.2 × 10<sup>4</sup>, a small SS of 0.113 V/dec and a large  $\mu_{\rm FE}$  of 5.2 cm<sup>2</sup>/V sec with a low  $V_{\rm t}$  of 0.27 V. The comparison of the TFT parameters is provided in Table 1, indicating that SiO<sub>2</sub> buffer layer insertion is necessary for stable operation of the TFT. Although the effective dielectric constant of gate stack decreased with

940 Z.W. Zheng, Y.C. Chen

**Table 1** Important transistor parameters for the IGZO TFTs without and with SiO<sub>2</sub> buffer layer

| Insulator                            | Operation voltage (V) | $V_{\rm t}\left({ m V}\right)$ | $I_{ m on}/I_{ m off}$ | SS<br>(V/dec) | $\mu_{\text{FE}}$ (cm <sup>2</sup> /V sec) | $N_{\rm max}$ (cm <sup>-2</sup> ) |

|--------------------------------------|-----------------------|--------------------------------|------------------------|---------------|--------------------------------------------|-----------------------------------|

| LaAlO <sub>3</sub>                   | 1.5                   | 0.36                           | $1 \times 10^3$        | 0.405         | 0.84                                       | $2.2 \times 10^{13}$              |

| LaAlO <sub>3</sub> /SiO <sub>2</sub> | 1.5                   | 0.27                           | $6.2 \times 10^{4}$    | 0.113         | 5.2                                        | $1.3\times10^{12}$                |

Fig. 4 Energy band diagram of gate stack for the IGZO TFT

addition of the SiO<sub>2</sub> buffer layer, the device performances have been greatly improved. It can be attributed to the lowered gate leakage and reduced interfacial issue caused by SiO<sub>2</sub> insertion [10–12, 20, 21, 23]. The off-current of the TFT device decreases after the SiO<sub>2</sub> buffer layer deposition and thus improves the  $I_{\rm on}/I_{\rm off}$ , which agrees with the small gate leakage for SiO<sub>2</sub>/LaAlO<sub>3</sub> gate stack. On the other hand, the performances of TFTs are strongly influenced by the interface trap states at the interface between the active channel and gate insulator, since the field-induced carriers are confined to a very thin region close to the interface. The interface defects can produce trapping or scattering effects, leading to the degradation of  $\mu_{FE}$  and SS. From SS, we can infer the maximum density of surface states at the gate dielectric/IGZO channel interface, according to the SS equation [12]:  $N_{\text{max}} = [SS \cdot \log(e)/(kT/q) - 1] \cdot (C_g/q)$ . Here, k is the Boltzmann constant, T is absolute temperature, q is charge quantity of an electron. The  $N_{\text{max}}$  is calculated to be  $\sim 2.2 \times 10^{13}$  cm<sup>-2</sup> for the TFT device without  $SiO_2$  buffer layer insertion, while much lower  $N_{\text{max}}$  of  $\sim 1.3 \times 10^{12}$  cm<sup>-2</sup> for the TFT device after inserting SiO<sub>2</sub> buffer layer. It is well known that the TFT performances are greatly governed by the surface states at the interface. Due to the interfacial issue caused by LaAlO<sub>3</sub> [22], inserting a smooth SiO<sub>2</sub> buffer layer evaporated at room temperature without sputtering plasma damage can effectively passivate

**Fig. 5** (a) Output  $I_d$ – $V_d$  characteristics and (b) transfer  $I_d$ – $V_g$  characteristics of the IGZO TFT without SiO<sub>2</sub> buffer layer

high- $\kappa$  surface and reduce interface states near the IGZO active channel layer [10–12], resulting in the improvement of  $\mu_{FE}$  and SS. A very small SS of 0.113 V/dec was achieved, close to the theoretical minimum value of 0.060 V/dec at room temperature, which indicates low interface trap density using a SiO<sub>2</sub> buffer layer insertion.

## 4 Conclusions

We demonstrate improved performances in IGZO TFTs using a SiO<sub>2</sub> buffer layer inserted between the IGZO active channel layer and high- $\kappa$  LaAlO<sub>3</sub> gate insulator. Good TFT device characteristics are achieved simultaneously, including a low  $V_t$  of 0.27 V, a good  $I_{on}/I_{off}$  of 6.2 × 10<sup>4</sup>, a small

**Fig. 6** (a) Output  $I_d$ – $V_d$  characteristics and (b) transfer  $I_d$ – $V_g$  characteristics of the IGZO TFT with SiO<sub>2</sub> buffer layer

SS of 0.113 V/dec and a large  $\mu_{FE}$  of 5.2 cm<sup>2</sup>/V sec at operation voltage as low as 1.5 V. Such good performances were attributed to the lowered gate leakage and reduced interfacial issue caused by  $SiO_2$  buffer layer insertion. These present results show that low-voltage-driven IGZO TFTs with stacked LaAlO<sub>3</sub>/SiO<sub>2</sub> as gate insulators have a great promise for future high-speed and low-power applications.

**Acknowledgements** The authors would like to thank Prof. A. Chin from National Chiao Tung University and Dr. C.H. Cheng from National Taiwan Normal University for their support and technical help in experiments.

#### References

- R.L. Hoffman, B.J. Norris, J.F. Wager, Appl. Phys. Lett. 82, 733 (2003)

- B. Yaglioglu, H.Y. Yeom, R. Beresford, D.C. Paine, Appl. Phys. Lett. 89, 062103 (2006)

- N.L. Dehuff, E.S. Kettenring, D. Hong, H.Q. Chiang, J.F. Wager, R.L. Hoffman, C.H. Park, D.A. Keszler, J. Appl. Phys. 97, 064505 (2005)

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, Nature 432, 488 (2004)

- E. Fortunato, P. Barquinha, R. Martins, Adv. Mater. 24, 2945 (2012)

- 6. J.C. Park, H.N. Lee, IEEE Electron Device Lett. 33, 818 (2012)

- H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, H. Hosono, Appl. Phys. Lett. 89, 112123 (2006)

- S.Y. Huang, T.C. Chang, M.C. Chen, S.W. Tsao, S.C. Chen, C.T. Tsai, H.P. Lo, Solid-State Electron. 61, 96 (2011)

- S.Y. Lee, D.H. Kim, E. Chong, Y.W. Jeon, D.H. Kim, Appl. Phys. Lett. 98, 122105 (2011)

- J.H. Na, M. Kitamura, Y. Arakawa, Appl. Phys. Lett. 93, 063501 (2008)

- 11. H.H. Hsu, C.Y. Chang, C.H. Cheng, IEEE Electron Device Lett. 34, 768 (2013)

- F. Zhou, H.P. Lin, L. Zhang, J. Li, X.W. Zhang, D.B. Yu, X.Y. Jiang, Z.L. Zhang, Curr. Appl. Phys. 12, 228 (2012)

- Y.J. Cho, J.H. Shin, S.M. Bobade, Y.B. Kim, D.K. Choi, Thin Solid Films 517, 4115 (2009)

- H.H. Hsu, C.Y. Chang, C.H. Cheng, Appl. Phys. A 112, 817 (2013)

- C.W. Chen, T.C. Chang, P.T. Liu, H.Y. Lu, K.C. Wang, C.S. Huang, C.C. Ling, T.Y. Tseng, IEEE Electron Device Lett. 26, 731 (2005)

- K.M. Chang, W.C. Yang, C.P. Tsai, IEEE Electron Device Lett. 24, 512 (2003)

- B.F. Hung, K.C. Chiang, C.C. Huang, A. Chin, S.P. McAlister, IEEE Electron Device Lett. 26, 384 (2005)

- M.F. Chang, P.T. Lee, S.P. McAlister, A. Chin, IEEE Electron Device Lett. 29, 215 (2008)

- 19. M.F. Chang, P.T. Lee, S.P. McAlister, A. Chin, IEEE Electron Device Lett. **30**, 133 (2009)

- 20. M. Kitamura, Y. Arakawa, Appl. Phys. Lett. 89, 223525 (2006)

- J.H. Na, M. Kitamura, D. Lee, Y. Arakawa, Appl. Phys. Lett. 90, 163514 (2007)

- 22. I.Y.K. Chang, S.W. You, P.C. Juan, M.T. Wang, J.Y.M. Lee, IEEE Electron Device Lett. 30, 161 (2009)

- G. Wang, D. Moses, A.J. Heeger, H.M. Zhang, M. Narasimhan, R.E. Demaray, J. Appl. Phys. 95, 316 (2004)

- H. Cho, E.A. Douglas, B.P. Gila, V. Craciun, E.S. Lambers, F. Ren,

S.J. Pearton, Appl. Phys. Lett. 100, 012105 (2012)

- L.F. Edge, D.G. Schlom, S.A. Chambers, E. Cicerrella, J.L. Freeouf, B. Hollander, J. Schubert, Appl. Phys. Lett. 84, 726 (2004)

- 26. J. Robertson, Rep. Prog. Phys. 69, 327 (2006)

- S.M. Sze, K.K. Ng, *Physics of Semiconductor Devices*, 3rd edn. (Wiley, New Jersey, 2007), p. 308