# Modeling Mechanical Stress Effect on Dopant Diffusion in Scaled MOSFETs

Yi-Ming Sheu, Sheng-Jier Yang, Chih-Chiang Wang, Chih-Sheng Chang, Li-Ping Huang, Tsung-Yi Huang, Ming-Jer Chen, *Senior Member, IEEE*, and Carlos H. Diaz, *Senior Member, IEEE*

Abstract—The effect of shallow trench isolation mechanical stress on MOSFET dopant diffusion has become significant, and affects device behavior for sub-100-nm technologies. This paper presents a stress-dependent dopant diffusion model and demonstrates its capability to reflect experimental results for a state-of-the-art logic CMOS technology. The proposed stress-dependent dopant diffusion model is shown to successfully reproduce device characteristics covering a wide range of active area sizes, gate lengths, and device operating conditions.

Index Terms—Dopant diffusion, mechanical stress, modeling, MOSFET, shallow trench isolation (STI), simulation, strain.

#### I. INTRODUCTION

S A RESULT of the aggressive downscaling of CMOS technology, shallow trench isolation (STI)-induced mechanical stress increases in magnitude with reduced device active areas, causing a nonnegligible impact on device performance [1]–[4]. Both experimental work and numerical simulations have been conducted to calculate the STI stress magnitude and distribution encountered in scaled MOSFETs [5]–[9]. The results show that the silicon stress level near the STI region is high. As design rules or layout dimensions scale down, the high-stress region encroaches further into the MOSFET channel. Thus, STI mechanical stress has a significant influence on state-of-the-art device performance.

Earlier work studying the mechanical stress effect has been focused on the MOSFET drive current shift, either in the form of localized or planar stress conditions [1]–[3], [6], [10]–[14]. Several studies have been performed to link STI mechanical stress to mobility changes while accounting for the observed current shift [2], [12], [13], although no threshold voltage shift mechanism has been investigated. Scott *et al.* [14] have investigated both the drive current and threshold voltage shift, suggesting a difference in stress-induced diffusivity as the plausible origin of the threshold voltage shift. So far, however, there has been no

Manuscript received June 14, 2004. This work was supported by the National Science Council under Contract NSC 93-2215-E-009-024. The review of this paper was arranged by Editor C.-Y. Lu.

M.-J. Chen is with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

Digital Object Identifier 10.1109/TED.2004.841286

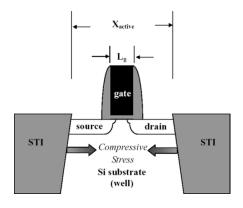

Fig. 1. Schematic cross section of the device along channel length direction with active area size  $X_{\rm active}$  and gate length  $L_g$  both as parameters. The stress condition is compressive mainly because of the lower thermal expansion rate of STI oxide compared to silicon, and the thermal gate oxidation-induced volume expansion at the STI edge.

further elaboration on this aspect. On the other hand, there has been a great deal of work devoted to dopant diffusion behavior in silicon under the influence of mechanical stress [15]–[19]. Cowern et al. [15] proposed a strain-induced dopant diffusivity model of boron diffusion in SiGe. Ahn et al. [17] concluded that in the presence of high-stress nitride film, phosphorus diffusion in the silicon was retarded, whereas antimony diffusion was enhanced. Aziz [18] established a relationship between hydrostatic pressure and biaxial strain via thermodynamic formulation, while accommodating calculation of the activation energy shift due to strain. Based on Azizs and Cowerns theoretical work [15], [18], Zangenberg et al. [19] critically reviewed the findings over the past ten years and further identified the strain effect on boron and phosphorus diffusion in SiGe. However, most studies in the area of mechanical stress-induced dopant diffusion changes remain in fundamental research, i.e., at the silicon material level, and have not yet been extended to semiconductor device characterization and modeling.

It is well recognized that the key MOSFET parameters, such as threshold voltage, drain-induced barrier lowering, body factor, and subthreshold swing, are all strongly dependent on dopant distribution details. Thus, it is crucial to examine stress-dependent dopant diffusion for scaled MOSFETs under mechanical stress.

In this paper, we present a stress-dependent diffusion model and incorporate it into a two-dimensional (2-D) process simulation environment to assess the doping distribution effect in scaled MOSFETs. The proposed model is corroborated by extensive experimental data in a sub-100-nm CMOS technology.

Y.-M. Sheu is with the Department of Advanced Device Technology, Taiwan Semiconductor Manufacturing Company 8, Hsinchu 300, Taiwan, R.O.C. He is also with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: ymsheu@tsmc.com).

S.-J. Yang, C.-C. Wang, C.-S. Chang, L.-P. Huang, T.-Y. Huang, and C. H. Diaz are with the Department of Advanced Device Technology, Taiwan Semi-conductor Manufacturing Company 8, Hsinchu 300, Taiwan, R.O.C.

# II. STRESS-DEPENDENT DIFFUSION MODEL AND MODELING METHODOLOGY

#### A. Stress-Dependent Diffusion Model

Several approaches dealing with dopant diffusion dependencies on strain are briefly described in the preceding section. The general concept of these approaches is to express dopant diffusion under mechanical stress in an Arrhenius form [15], [18], [19]. For example, in the case of a compressively strained SiGe layer where Cowern studied boron diffusion [15], the stress condition is regarded as biaxial and the dopant diffusion dependence follows the Arrhenius form

$$D_S = D_I \exp\left[-\frac{sQ'}{kT}\right] \tag{1}$$

where  $D_S$  is the dopant diffusivity under strain,  $D_I$  is the dopant diffusivity without strain, s is the biaxial strain in the plane of the SiGe layer, and Q' is the activation energy per strain.

Analogous to the above strained SiGe layer, we develop a stress-dependent dopant diffusion model for dopant diffusion under STI mechanical stress, named the volume-change-ratio-induced diffusion activation energy shift model (VIDAESM). The volume change ratio  $V_{\rm cr}$  is a function of position due to nonuniform stress distributions. In this paper, the MOSFET width is large enough to allow the three-dimensional stress effect to be reduced to the 2-D one. The activation energy involved is the product of a dopant-dependent coefficient and volume change ratio, meaning that (1) can be rewritten in the case of dopant diffusion under STI mechanical stress

$$D_S(T, x, y) = D_I(T) \exp \left[ -\frac{\Delta E_S V_{cr}(T, x, y)}{kT} \right]$$

(2)

where  $D_S$  is the dopant diffusivity under strain,  $D_I$  is the dopant diffusivity without strain,  $V_{\rm cr}$  is the volume change ratio due to stress,  $\Delta E_S$  is the activation energy per volume change ratio depending on the dopant species, and T is the temperature. When the strain is small, the volume change ratio can be expressed as

$$V_{\rm cr}(T, x, y) \cong \varepsilon_t(T, x, y) \equiv \varepsilon_{xx}(T, x, y) + \varepsilon_{yy}(T, x, y) + \varepsilon_{zz}$$

(3)

where  $\varepsilon_{xx}$  is the strain along the channel length direction,  $\varepsilon_{yy}$  is the strain in the direction perpendicular to the silicon surface,  $\varepsilon_{zz}$  is the strain along the channel width direction, and  $\varepsilon_t$  is the strain summation of  $\varepsilon_{xx}$ ,  $\varepsilon_{yy}$ , and  $\varepsilon_{zz}$ . Note that  $\varepsilon_{zz}$  is zero in the 2-D simulation due to wide structures adopted. Therefore, (2) becomes

$$D_S(T, x, y) = D_I(T) \exp\left[-\frac{\Delta E_S \varepsilon_t(T, x, y)}{kT}\right].$$

(4)

A 2-D numerical process simulator TSUPREM4 is chosen to perform the process simulation. TSUPREM4 is capable of simulating intrinsic dopant diffusion, three-stream dopant-point

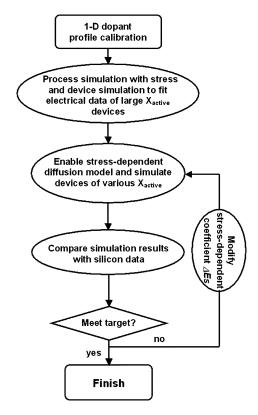

Fig. 2. Flow chart of the modeling procedure.

Fig. 3. I–V calibration result of a short-channel nMOSFET with large  $X_{\rm active}$  for (a)  $V_D=0.05$  V and (b)  $V_D=1$  V.  $L_g=65$  nm and  $X_{\rm active}=10$   $\mu$ m. Symbols stand for the silicon data. Solid lines are the calibrated simulation result.

defect pairing diffusion, the oxidation-enhanced diffusion

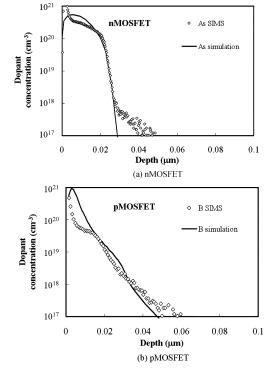

Fig. 4. SIMS and calibration results of 1-D dopant profile for (a) nMOSFET and (b) pMOSFET.

effect, the dopant clustering effect, and the dislocation loop effect. For assessment of mechanical stress, the simulator also simultaneously solves force balance equations while taking into account thermal expansion, intrinsic stress, geometry rearrangement after etch and deposition processes, and the thermal oxidation process [20]. The stress-dependent diffusion model VIDAESM has been incorporated into the simulator through the user-specified equation interface to adaptively calculate stress-dopant diffusivity during the process simulation.

#### B. Modeling Methodology

To model stress-dependent dopant diffusion for various stress levels, we designed and fabricated a series of MOSFETs with various active area sizes. Fig. 1 schematically shows the cross section view of a test device along the channel direction. The mechanical stress effect was explored here with active area size,  $X_{\rm active}$ , and gate length  $L_g$ , both used as the main structural parameters.

The flow chart of the modeling procedure is shown in Fig. 2. First, the one-dimensional (1-D) dopant profiles were processed using blanket control wafers, which covered the range of the process conditions of the device wafers. The results were then taken as stress-free dopant profiles and used to calibrate the dopant diffusion parameters without stress-dependent models.

Second, 2-D MOSFET structures were simulated using the mechanical stress model. Calibrated diffusion parameters were employed to simulate a large  $X_{\rm active}$  MOSFET, where the stress level is low. All front-end major process steps from the STI

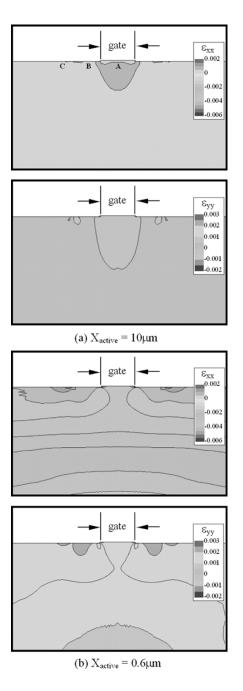

Fig. 5. Simulated strain distribution in the silicon of entire front-end process for Lg= 65 nm, (a)  $X_{\rm active}=10~\mu{\rm m}$ , (b)  $X_{\rm active}=0.6~\mu{\rm m}$ . A small  $X_{\rm active}$  causes a much higher strain.

to the source/drain anneal were considered. The corresponding simulation geometries were calibrated using transmission electron microscope cross-sectional images. Some fine tuning of the 2-D dopant profile parameters, such as implant lateral straggles and segregation factors, are needed to fit the silicon device current–voltage (I–V) characteristics. Fig. 3 shows the calibration result of a short-channel nMOSFET I–V with a large X<sub>active</sub>.

Next, with the stress distribution known, the stress-dependent diffusion models were introduced to simulate MOSFETs with varying  $X_{\rm active}$  values. After implementing the stress-dependent diffusion model, process simulation results were used

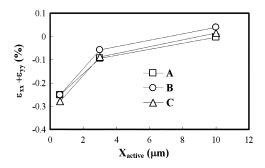

Fig. 6. Magnitude of strain versus  $X_{\rm active}$  corresponding to three points A, B, and C in Fig. 4.

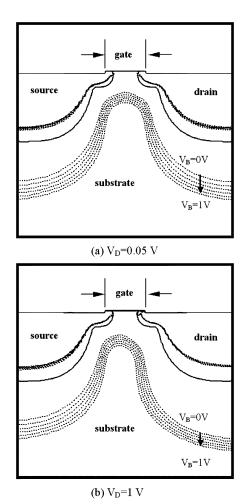

Fig. 7. Depletion region boundaries with substrate bias  $V_{\rm B}$  for 65-nm nMOSFET at (a)  $V_D=0.05~{\rm V}$  and (b)  $V_D=1~{\rm V}$ .

as device simulation inputs. MEDICI was chosen as the numerical device simulator. The device modeling parameters, such as carrier mobility, work function, and silicon/oxide interface charges were calibrated to fit the  $\emph{I-V}$  of large  $X_{\rm active}$  MOSFETs. Then, device simulations with various  $X_{\rm active}$  values were performed and compared with silicon device data. The above procedure was iterated from process to device cycle until the current-voltage data was all satisfactorily reproduced in all cases. The  $\Delta E_S$  values from the previous work [15] were employed as the initial guess values. It is worth noting that the numerical convergence and simulation speed were not greatly

Fig. 8.  $I\!-\!V$  comparison among experimental data, simulation without stress-dependent diffusion model, and simulation with stress-dependent diffusion model for a small  $X_{\rm active}$  MOSFET at (a)  $V_D=0.05$  V and (b)  $V_D=1$  V.  $L_g=65$  nm and  $X_{\rm active}=0.6~\mu{\rm m}$ . Symbols stand for the silicon data. Dashed lines are the simulation without stress-dependent diffusion model. Solid lines are the simulation with stress-dependent diffusion model.

influenced after implementing VIDAESM. The simulation time incorporating VIDAESM increases by about 7% compared to that without VIDAESM.

### III. EXPERIMENTAL AND COMPARISONS

The silicon wafers were fabricated using novel CMOS processes. The control wafers for 1-D SIMS analysis were processed using the same thermal steps as device wafers. Fig. 4 displays SIMS results for both n– and pMOSFET. The implant conditions were BF $_2$  2 keV  $1\times10^{15}$  cm $^{-3}$  and As 2 keV  $1\times10^{15}$  cm $^{-3}$  for ultrashallow junction calibration and the junction depths are around 260 angstroms for both devices. The calibrated simulation profile is also plotted in Fig. 4. The calibration procedure included the fine-tuning of implant damage, dopant-point defect pairing diffusion, silicon-oxide dopant segregation, oxidation enhanced diffusion models, dopant clustering models, dopant-defect clustering models, and intrinsic diffusion models.

The stress simulation involved the main process steps, which are STI formation, gate oxidations, and poly-gate formation in sequence. Viscoelastic oxidation model was used to simulate the stress-dependent oxide growth. The Youngs moduli used were  $1.87 \times 10^{12}$  dyne/cm<sup>2</sup> for the silicon and  $6.6 \times 10^{11}$  dyne/cm<sup>2</sup> for the oxide layers. The intrinsic stress used is  $-1.5 \times 10^9$  dyne/cm<sup>2</sup> for the STI oxide and  $3.3 \times 10^8$  dyne/cm<sup>2</sup> for gate spacer oxide. The other parameters follow the default values in the TSUPREM4 manual [20].

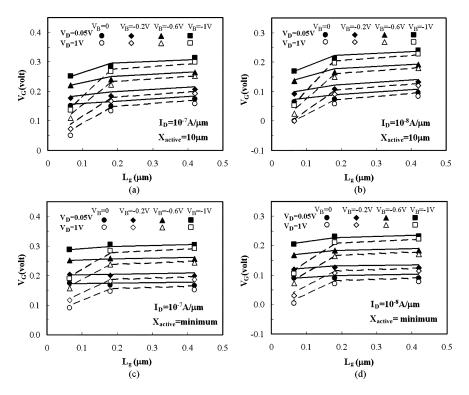

Fig. 9. Comparison of experimental and simulated nMOSFET  $V_G$  at different  $I_D$  level for various  $L_g$  and  $X_{\rm active}$ . Minimum  $X_{\rm active}$  for Lg = 65 nm is 0.6  $\mu$ m, for Lg = 0.18  $\mu$ m is 0.74  $\mu$ m, and for Lg = 0.42  $\mu$ m is 1  $\mu$ m. Final set of dopant diffusion parameters can model MOSFETs of different  $X_{\rm active}$  under various drain voltages and substrate biases. Symbols stand for silicon data. Solid lines represent simulations with stress-dependent diffusion model. (a)  $I_D = 10^{-7}$  A $\mu$ m,  $X_{\rm active} = 10 \ \mu$ m; (b)  $I_D = 10^{-8}$  A $\mu$ m,  $X_{\rm active} = 10 \ \mu$ m; (c)  $I_D = 10^{-8}$  A $\mu$ m,  $X_{\rm active} = 10 \ \mu$ m; (c)  $I_D = 10^{-8}$  A $\mu$ m,  $X_{\rm active} = 10 \ \mu$ m; (c)  $I_D = 10^{-8}$  A $\mu$ m,  $X_{\rm active} = 10 \ \mu$ m; (c)  $I_D = 10^{-8}$  A $\mu$ m,  $I_D = 10^{-8}$  A $\mu$ m,

The stress distribution results for different  $X_{\text{active}}$  values are given in Fig. 5. It can be seen that the polarity of the strain  $\varepsilon_{\rm xx}$ in the lateral direction is negative, meaning that the MOSFET core area experiences a compressive stress. On the other hand, strain  $\varepsilon_{yy}$  in the vertical direction is tensile with a magnitude much smaller than  $\varepsilon_{xx}$ . In particular, Fig. 5(b) reveals that  $\varepsilon_{xx}$  drastically increases in magnitude with decreasing  $X_{

m active}$ values. Three reference points A, B, and C are chosen to inspect the value of the strain. A is at the center of the gate, B is 75 nm away from the gate center and C is 150 nm from the gate center. The depth of these points is 20 nm from the silicon surface. Fig. 6 highlights the magnitude of the strain versus the  $X_{\text{active}}$  value at points **A**, **B**, and **C** in Fig. 5. The negative polarity of the strain means that the general strain conditions in the active area are compressive, and the magnitude increases rapidly as the value of  $X_{\text{active}}$  decreases. The compressive stress mainly comes from lower thermal expansion rate of the STI oxide compared to silicon, and the thermal gate oxidation-induced volume expansion at the STI edge. As  $X_{\text{active}}$ decreases, the STI approaches the MOSFET core region and increases the magnitude of compressive stress.

The MOSFET channel width in the silicon experiment was fixed at 10  $\mu$ m, large enough to ensure that the stress along the channel width direction is negligible. Simulations were conducted to evaluate the mechanical stress along the channel width direction. The results showed that the average strain level for channel width  $W=10~\mu{\rm m}$  is around -0.02%, which is at least two orders of magnitude lower than the peak strain level used in this paper. The MOSFET design set consisted of  $X_{\rm active}$  values

from 0.6 to 10  $\mu m$  and  $L_g$  from 65 nm to 0.42  $\mu m$ . It has been recognized that boron and phosphorus diffusion are retarded by compressive strain [15], [19], [21]. The stress simulation results show that the MOSFET channel stress and strain magnitudes for  $X_{\rm active}=10~\mu m$  are around  $-1\times10^8$  dyne/cm² and -0.04%, respectively. As the  $X_{\rm active}$  value shrinks to 0.6  $\mu m$ , the corresponding stress and strain magnitudes become around  $-5\times10^9$  dyne/cm² and -0.4%, respectively. The compressive strain level in the channel region is quite close to the strain produced by 10% germanium in silicon, which falls within the range of Cowern's and Zangenberg's studies [15], [19].

In the present paper, the impurities introduced to form nMOSFET are boron, indium, arsenic, and phosphorus, while pMOSFET employed boron and arsenic. Boron, arsenic, and phosphorus were all retarded by STI stress as encountered in fitting the silicon MOSFET I-V data. Indium was not considered as a fitting variable because it was observed to be almost immobile during the thermal process, meaning that a dopant profile change due to mechanical stress would hardly be observed. As will be mentioned later, the nMOSFETs threshold voltage was observed to increase as the  $X_{

m active}$  value decreases. The subthreshold I-V with a low drain bias is strongly dependent on the accurate doping profile of the MOSFET shallow core region, which is mainly related to arsenic source/drain extension doping and boron halo doping. In high drain bias cases, the subthreshold *I–V* depends significantly on the deeper part of the MOSFET doping profile, which is related to phosphorus source/drain, indium halo, and boron halo tail doping profiles. As the gate length varies, the extent of the superposition of

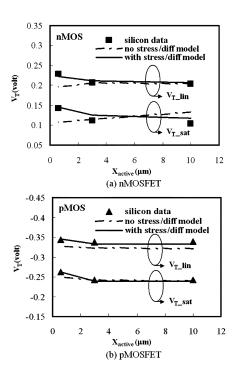

Fig. 10. Experimental and simulated threshold voltage dependence on  $X_{\rm active}$  of (a) nMOSFET and (b) pMOSFET. NMOSFET threshold voltage  $V_T$  is more dependent on  $X_{\rm active}$  than the p-type counterpart. Simulation with stress-dependent diffusion model is able to describe stress-induced  $V_T$  shift.

tilt-implanted halo doping varies accordingly. Moreover, as the substrate bias increases in magnitude, the depletion region further extends into the substrate from the source, channel and drain regions, considerably influencing subthreshold *I–V* characteristics. Thus, biasing the MOSFET substrate can serve as a means of verification for the stress-dependent diffusion model. Fig. 7 shows the depletion region boundaries of a 65-nm nMOSFET for low and high drain voltages.

After numerical iterations were completed, the effects of gate lengths, gate voltages, drain voltages, and substrate biases simultaneously matched with the nMOSFET subthreshold *I–V* data. This is sufficient to claim that the resulting dopant distributions for the whole device core region are correct. To assess the creditability of this model, device I–V simulations with and without VIDAESM were performed and compared. Fig. 8 shows the detailed I-V comparison for a small  $X_{\text{active}}$  MOSFET with and without VIDAESM. In the absence of VIDAESM, the simulation fails to correctly describe the I-V dependency on  $X_{\text{active}}$ . Fig. 9 displays a series of comparisons with measured gate voltage at different drain current levels for different combinations of gate lengths, active area sizes, drain voltages, and substrate biases. Remarkably, the extracted diffusion parameter set is able to reproduce all the silicon data well. The broad range of gate lengths, active areas, drain voltages and substrate biases employed in this experiment confirm that the VIDAESM model is indeed suited for modeling the mechanical stress effect on scaled MOSFETs. To further ensure the extracted parameter set also valid for pMOSFETs, threshold voltage dependence on  $X_{\text{active}}$  is simulated and compared with silicon data for both nMOSFETs and pMOSFETs. Fig. 10 shows the final results. It can be seen that the nMOSFET threshold voltage increases with

| Impurity                             | Boron | Phosphorus | Arsenic |

|--------------------------------------|-------|------------|---------|

| $\Delta E_S$ (eV/volume shift ratio) | -7    | -30        | -14     |

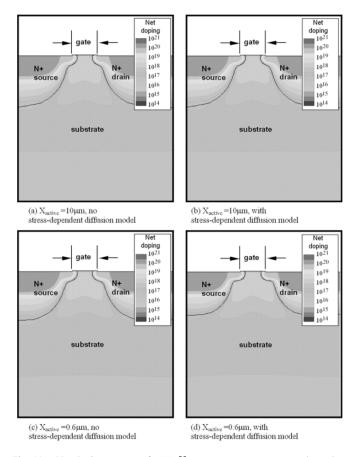

Fig. 11. Net doping contours for (a)  $X_{\rm active}=10~\mu{\rm m}$ , no stress-dependent model, (b)  $X_{\rm active}=10~\mu{\rm m}$ , with stress-dependent model, (c)  $X_{\rm active}=0.6~\mu{\rm m}$ , no stress-dependent model, and (d)  $X_{\rm active}=0.6~\mu{\rm m}$ , with stress-dependent model. For  $X_{\rm active}=0.6~\mu{\rm m}$ , the source/drain junction is significantly shallower in the MOSFET core region when the stress-dependent diffusion model is turned on. The gate length is 65 nm.

decreasing  $X_{\rm active}$  values while pMOSFET threshold voltage is relatively insensitive to  $X_{\rm active}$ . The trends for both nMOSFETs and pMOSFETs are adequately described by the extracted parameter set.

Finally, Table I lists the extracted  $\Delta E_S$  values for all impurities involved. The  $\Delta E_S$  for phosphorus is -30 eV per volume shift ratio and is largest among the impurities. The  $\Delta E_S$  for arsenic is -14 eV per volume shift ratio, whereas the  $\Delta E_S$  for boron is -7 eV. These coefficients confirm diffusion retardation by the compressive stress in pure silicon, excluding the Ge chemical effect in strained SiGe experiments. Fig. 11 illustrates the 2-D contour of the nMOSFET net doping concentration for a gate length of 65 nm. As shown in the figure, for  $X_{\rm active} = 10~\mu{\rm m}$ , the dopant contours with and without the stress-dependent model are comparable, while the source/drain junction for  $X_{\rm active} = 0.6~\mu{\rm m}$  is significantly shallower and effective gate length is longer in the MOSFET core region when the stress-dependent diffusion model is introduced. To more

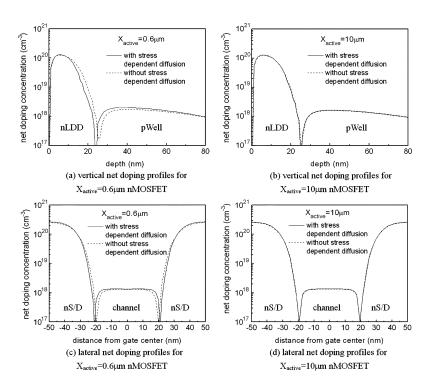

Fig. 12. Dopant profiles of (a) vertical direction for  $X_{\rm active} = 0.6~\mu \rm m$  nMOSFET, (b) vertical direction for  $X_{\rm active} = 10~\mu \rm m$  nMOSFET, (c) lateral direction for  $X_{\rm active} = 0.6~\mu \rm m$  nMOSFET, and (d) lateral direction for  $X_{\rm active} = 0.6~\mu \rm m$  nMOSFET. The vertical profiles are taken at gate edge and the lateral profiles are taken at 15-nm-deep cutlines of the device. Solid lines are simulation with stress-dependent diffusion model and dashed lines are without stress-dependent diffusion model.  $X_{\rm active} = 0.6~\mu \rm m$  with stress-dependent model device exhibits significant retardation of dopant diffusion.

clearly visualize the effect of the stress-dependent model, one can inspect the dopant profile along specific cutlines. Fig. 12 displays corresponding vertical and lateral doping profiles for a 65 nm gate length nMOSFET with  $X_{\rm active}$  as a parameter. As can be seen, significant dopant diffusion retardation prevails at small  $X_{\rm active}$  values and this explains an increase in threshold voltage as the  $X_{\rm active}$  decreases.

## IV. CONCLUSION

This paper has proposed an accurate stress-dependent dopant diffusion model. The model has been implemented into process and device simulators and has been validated by the extensive experimental data. A complete set of MOSFET devices with various gate lengths and active areas have been designed and fabricated from state-of-the-art sub-100-nm process for model verification. Retarded dopant diffusion for phosphorus, boron, and arsenic has been observed and explained by calibrated dopant profiles while accurately accounting for silicon threshold voltage changes and *I–V* behaviors. The major benefit of this model is that only a single set of physically based diffusion parameters is required to reproduce device subthreshold characteristics for different active areas, gate lengths, drain voltages, and substrate biases. The proposed model therefore can serves as a compact and accurate method for practically dealing with STI mechanical stress-dependent dopant diffusion in ultralarge scale devices.

# REFERENCES

- [1] Y. M. Sheu, K. Y. Y. Doong, C. H. Lee, M. J. Chen, and C. H. Diaz, "Study on STI mechanical stress-induced variations on advanced CMOSFETs," in *Proc. ICMTS*, Mar. 2003, pp. 205–208.

- [2] R. A. Bianchi, G. Bouche, and O. Roux-dit-Buisson, "Accurate modeling of trench isolation-induced mechanical stress effects on MOSFET electrical performance," in *IEDM Tech. Dig.*, Dec. 2002, pp. 117–120.

- [3] K. W. Su, Y. M. Sheu, C. K. Lin, S. J. Yang, W. J. Liang, X. Xi, C. S. Chiang, J. K. Her, Y. T. Chia, C. H. Diaz, and C. Hu, "A scaleable model for STI mechanical stress effect on layout dependence of MOS electrical characteristics," in *Proc. Custom Integrated Circuits Conf.*, Sep. 2003, pp. 245–248.

- [4] A. Toda, N. Ikarashi, H. Ono, S. Ito, T. Toda, and K. Imai, "Local lattice strain distribution around a transistor channel in metal-oxide-semiconductor devices," *Appl. Phys. Lett.*, vol. 79, pp. 4243–4245, Dec. 2001.

- [5] D. Chidambarrao, J. P. Peng, and G. R. Srinivasan, "Stresses in silicon substrates near isolation trenches," *J. Appl. Phys.*, vol. 70, pp. 4816–4822, Nov. 1991.

- [6] Y. M. Sheu, C. S. Chang, H. C. Lin, S. S. Lin, C. H. Lee, C. C. Wu, M. J. Chen, and C. H. Diaz, "Impact of STI mechanical stress in highly scaled MOSFETs," in *Proc. Int. Symp. VLSI-TSA*, Oct. 2003, pp. 269–272.

- [7] V. Senez, T. Hoffmann, E. Robiliart, G. Bouche, H. Jaouen, M. Lunenborg, and G. Carnevale, "Investigations of stress sensitivity of 0.12 CMOS technology using process modeling," in *IEDM Tech. Dig.*, Dec. 2001, pp. 831–834.

- [8] V. Senez, A. Armigliato, I. De Wolf, G. Carnevale, R. Balboni, S. Frabboni, and A. Benedetti, "Strain determination in silicon microstructures by combined convergent beam electron diffraction, process simulation, and micro-Rama spectroscopy," J. Appl. Phys., vol. 94, pp. 5574–5583, Nov. 2003.

- [9] B. Dietrich, V. Bukalo, A. Fischer, K. F. Dombrowski, E. Bugiel, B. Kuck, and H. H. Richter, "Raman-spectroscopic determination of inhomogeneous stress in submicron silicon devices," *Appl. Phys. Lett.*, vol. 82, pp. 1176–1178, Feb. 2003.

- [10] K. Rim, J. L. Hoyt, and J. F. Gibbons, "Fabrication and analysis of deep submicron strained-Si N-MOSFETs," *IEEE Trans. Electron Devices*, vol. 47, no. 7, pp. 1406–1415, Jul. 2000.

- [11] S. Ito, H. Namba, K. Yamaguchi, T. Hirata, K. Ando, S. Koyama, S. Kuroki, N. Ikezawa, T. Suzuki, T. Saitoh, and T. Horiuchi, "Mechanical stress effect of etch-stop nitride and its impact on deep submicron transistor design," in *IEDM Tech. Dig.*, Dec. 2000, pp. 247–250.

- [12] A. Lochtefeld and D. A. Antoniadis, "Investigating the relationship between electron mobility and velocity in deeply scaled NMOS via mechanical stress," *IEEE Electron Device Lett.*, vol. 22, no. 12, pp. 591–593, Dec. 2001.

- [13] A. Hamada, T. Furusawa, N. Saito, and E. Takeda, "A new aspect of mechanical stress effects in scaled MOS devices," *IEEE Trans. Electron Devices*, vol. 38, no. 4, pp. 895–900, Apr. 1991.

- [14] G. Scott, J. Lutze, M. Rubin, F. Nouri, and M. Manley, "NMOS drive current reduction caused by transistor layout and trench isolation-induced stress," in *IEDM Tech. Dig.*, Dec. 1999, pp. 827–830.

- [15] N. E. B. Cowern, P. C. Zlam, P. C. van der Sluis, D. J. Gravesteijn, and W. B. Boer, "Diffusion in strained Si(Ge)," *Phys. Rev. Lett.*, vol. 72, pp. 2585–2588, Apr. 1994.

- [16] S. Chaudhry and M. E. Law, "The stress assisted evolution of point and extended defects in silicon," *J. Appl. Phys.*, vol. 82, pp. 1138–1146, Aug. 1997

- [17] S. T. Ahn, H. W. Kennel, J. D. Plummer, and W. A. Tiller, "Film stress-related vacancy supersaturation in silicon under low-pressure chemical vapor deposited silicon nitride films," *J. Appl. Phys.*, vol. 64, pp. 4914–4918, Nov. 1988.

- [18] M. J. Aziz, "Thermodynamics of diffusion under pressure and stress: relation to point defect mechanisms," *Appl. Phys. Lett*, vol. 70, pp. 2810–2812, May 1997.

- [19] N. R. Zangenberg, J. Fage-Pedersen, J. L. Hansen, and A. N. Larsen, "Boron and phosphorus diffusion in strained and relaxed Si and SiGe," *J. Appl. Phys.*, vol. 94, pp. 3883–3890, Sep. 2003.

- [20] Synopsys TSUPREM-4 User Guide, Synopsys Inc., Jun. 2003.

- [21] H. Park, K. S. Jones, J. A. Slinkman, and M. E. Law, "The effects of strain on dopant diffusion in silicon," in *IEDM Tech. Dig.*, Dec. 1993, pp. 303–306.

Chih-Chiang Wang received the B.S. degree in physics science from Fu-Jen University, Xinzhuang, Taiwan, R.O.C., and the M.S. degree in electro-optical engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1989 and 1991, respectively.

In 1991, he joined the Electronics Research and Service Organization (ERSO/ITRI) and worked for the 0.7 and 0.5- $\mu$ m DRAM devices design and 0.25 logic devices development departments. He joined the Taiwan Semiconductor Manufacturing

Company (TSMC) Hsinchu, in 1998. Since 2001, he has been the Manager of the TCAD team, Device Engineering Division and is responsible for process and device calibration/simulation. His work primarily focuses on aggressive CMOS technology and the related models development. He has been involved in the technologies development and TCAD calibration for 0.18-, 0.15-, and 0.13- $\mu$ m, and 90-nm technologies, and in stress/SiGe-related modeling and simulation.

Chih-Sheng Chang received the B.S. and M.S. degrees in electrical engineering from National Taiwan University, Taipei, Taiwan, R.O.C., in 1986 and 1990, respectively, and the Ph.D. degree from the Department of Electrical and Computer Engineering, University of Illinois, Urbana, in 1996.

Since 1999, he has been with Taiwan Semiconductor Manufacturing Company (TSMC), Ltd., Hsinchu, where he has worked on TCAD, MOS device design, and RF devices optimization and characterization. He has been the main device

designer for TSMC's 0.15- and 0.13-mm high-speed devices. Currently, he is a Technology Manager in the Communication Technology Department, Logic Technology Division, where he is in charge of the development of RF active and passive devices for 0.18-mm, 0.13-mm, and 90-nm technologies. His current research interests include active and passive devices for RF CMOS technology, metal gate/high- $\kappa$  gate stack for advance CMOS technology, and device physics for strained MOS devices.

Yi-Ming Sheu was born in Hsinchu, Taiwan, R.O.C., in 1968. He received the B.S. degree in material science and engineering from National Cheng-Kung University, Tainan, Taiwan, in 1991, and the M.S. degree in optical science from National Central University, Zhongli, Taiwan, in 1996. He is currently pursuing the Ph.D. degree in the Department of Electronics Engineering at National Chiao-Tung University, Hsinchu.

In 1997, he joined the Taiwan Semiconductor Manufacturing Company (TSMC) Hsinchu, and is

currently engaged in advanced CMOS device design.

**Li-Ping Huang** received the M.S. degree from National Tsing Hua University of Applied Physics, Hsinchu, Taiwan, R.O.C., in 1991.

In 2001, he joined the TCAD group of the Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu. Currently, his interests include process and device simulation.

Sheng-Jier Yang was born in Taipei, Taiwan, R.O.C., in 1964. He received the B.S. degree from Tatung Institute of Technology, Tatung, Taiwan, in 1987, the M.S. degree from National Central University, Zhongli, Taiwan, in 1989 and the Ph.D. degree from Arizona State University, Tempe, in 2000, all in chemical engineering.

From 2000 to 2002, he was a Device Engineer with PowerOn Technologies, Inc. Phoenix, where he was working on optimizing discrete power MOSFETs for application voltages ranging from 20 to 800 V. Since

2002, he has been with the Taiwan Semiconductor Manufacturing Company (TSMC) Hsinchu, Taiwan. His current focus is on characterizing stress-induced impact on MOSFETs.

Tsung-Yi Huang was born in Kaohsiung, Taiwan, R.O.C., in 1969. He received the B.S. degree in physics science from National Tsing-Hua University (NTHU), Hsinchu, Taiwan in 1992, and the M.S. and Ph.D. degrees in electrical engineering from Tsing-Hua University, Hsinchu, in 1994 and 2001, respectively.

From 1997 to 2002, he worked at Avant! as a TCAD Engineer. In July 2002, he joined the Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu, as the Technological Manager for device

profile modeling. His research includes high-voltage device characteristics modeling, junction engineering, and modeling for advanced CMOS technologies. He is currently developing modeling and simulation for dopant diffusion in strained and strain-relaxed SiGe.

Ming-Jer Chen (S'78–M'79–SM'98) received the B.S. degree in electrical engineering (with highest honors) in 1977 from National Cheng-Kung University, Tainan, Taiwan, and the Ph.D. degree in electronics engineering in 1985 from National Chiao-Tung University (NCTU), Hsinchu, Taiwan.

In 1985, he joined the faculty of the Department of Electronics Engineering, NCTU, where he became Full Professor in 1993. From 1987 to 1992, he served as a consultant for the Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu, where

he led a team from NCTU and Electronics Research and Service Organization (ERSO/ITRI) to build up a series of process windows and design rules. He has been granted six U.S. patents and six Taiwanese patents covering the high-precision analog capacitors, 1-T SRAM cell, dynamic threshold MOS, and ESD protection. From 2000 to 2001, he was a Visiting Professor at the Department of Electrical Engineering and the Center for Integrated Systems, Stanford University, Stanford, CA. His research interests have long been focused on the technology reliability physics and currently on nanoscale electronics. He has graduated 12 Ph.D. students and more than 80 Master's students.

Dr. Chen is a member of Phi Tau Phi.

Carlos H. Diaz (M'86–SM'98) received the B.S. and M.S. degrees in electrical engineering from Universidad de Los Andes, Bogota D.C., Colombia, and the Ph.D. degree in electrical engineering from the University of Illinois at Urbana.

He joined Taiwan Semiconductor Manufacturing Company (TSMC)'s Research and Development team, Hsinchu, Taiwan, R.O.C., in 1998 where he is currently Deputy Director, Logic Technology Division. Before joining TSMC, he was a Member of the Technical Staff in the ULSI Laboratory,

Hewlett-Packard (HP) Laboratories, Palo Alto, CA, working on process integration, device design, and physics reliability. While at HP, he was also a Lecturer on VLSI technology for University of California, Berkeley extension program. He holds 15 U.S. patents, has published more than 60 papers in technical journals and international conferences, and has coauthored one book.

Dr. Diaz was the recipient of two SRC inventor awards. He is TSMC's representative to the ITRS PIDS TWG. He served at the Solid State Devices and Materials International Conference, the International Conference on Simulation of Semiconductor Processes and Devices, the IEEE International Reliability Physics Symposium, and the EOS/ESD Symposium program committees. Currently, he is a member of the VLSI Technology Symposium and the IEEE International Electron Devices Meeting technical program committees.