# Two-dimensional photo-mapping on CMOS single-photon avalanche diodes

Jau-Yang Wu, Ping-Keng Lu, and Sheng-Di Lin\*

Department of Electronics Engineering, National Chiao Tung University, 1001 University Road, Hsinchu 30010, Taiwan

\*sdlin@mail.nctu.edu.tw

**Abstract:** Two-dimensional (2-D) photo-count mapping on CMOS single photon avalanche diodes (SPADs) has been demonstrated. Together with the varied incident wavelengths, the depth-dependent electric field distribution in active region has been investigated on two SPADs with different structures. Clear but different non-uniformity of photo-response have been observed for the two studied devices. With the help of simulation tool, the non-uniform photo-counts arising from the electric field non-uniformity have been well explained. As the quasi-3D distribution of electric field in the active region can be mapped, our method is useful for engineering the device structure to improve the photo-response of SPADs.

©2014 Optical Society of America

OCIS codes: (040.0040) Detectors; (040.1345) Avalanche photodiodes (APDs); (040.6040) Silicon.

#### References and links

- 1. S. Cova, M. Ghioni, A. Lotito, I. Rech, and F. Zappa, "Evolution and prospects for single-photon avalanche diodes and quenching circuits," J. Mod. Opt. **51**(9–10), 1267–1288 (2004).

- I. Rech, D. Resnati, A. Gulinatti, M. Ghioni, and S. Cova, "Self-suppression of reset induced triggering in picosecond SPAD timing circuits," Rev. Sci. Instrum. 78(8), 086112 (2007).

- R. J. Walker, J. A. Richardson, and R. K. Henderson, "A 128x96 pixel event-driven phase-domain ΔΣ-based fully digital 3D camera in 0.13 µm CMOS imaging technology," in *IEEE ISSCC. Dig. Tech. Pap.* (2011), 410–412.

- C. Niclass, M. Soga, H. Matsubara, M. Ogawa, and M. Kagami, "A 0.18μm CMOS SoC for a 100 m-range 10-frame/s 200 96-pixel time-of flight depth sensor," in *IEEE ISSCC Dig. Tech. Papers* (2013), 488–489.

E. Fisher, I. Underwood, and R. K. Henderson, "A reconfigurable single-photon-counting integrating receiver

- E. Fisher, I. Underwood, and R. K. Henderson, "A reconfigurable single-photon-counting integrating receiver for optical communications," IEEE J. Solid-State Circuits 48(7), 1638–1650 (2013).

- M. Gersbach, Y. Maruyama, R. Trimananda, M. W. Fishburn, D. Stoppa, J. A. Richardson, R. Walker, R. Henderson, and E. Charbon, "A time-resolved, low-noise single-photon image sensor fabricated in deep-submicron CMOS technology," IEEE J. Solid-State Circuits 47(6), 1394–1407 (2012).

- C. Veerappan, C. Bruschini, and E. Charbon, "Sensor network architecture for a fully digital and scalable SPAD based PET system," in *IEEE Nuclear Science Symposium Conference Record (NSS/MIC)* (2012), 1115–1118.

- L. H. C. Braga, L. Gasparini, L. Grant, R. K. Henderson, N. Mas-sari, M. Perenzoni, D. Stoppa, and R. Walker, "An 8x16-pixel 92kSPAD time-resolved sensor with on-pixel 64 ps 12b TDC and 100MS/s real-time energy histogramming in 0.13 µm CIS technology for PET/MRI applications," in *IEEE Int. Solid-State Circuits Conf.* Dig. Tech. Papers (2013), 486–487.

- A. Ingargiola, M. Assanelli, A. Gallivanoni, I. Rech, M. Ghioni, and S. Cova, "Avalanche buildup and propagation effects on photon-timing jitter in Si-SPAD with non-uniform electric field," Proc. SPIE 7320, 73200K (2009).

- V. Savuskan, I. Brouk, M. Javitt, and Y. Nemirovsky, "An estimation of single photon avalanche diode (SPAD) photon detection efficiency (PDE) non-uniformity," IEEE Sens. J. 13(5), 1637–1640 (2013).

- F. Guerrieri, S. Tisa, A. Tosì, and F. Zappa, "Single-photon camera for high-sensitivity high-speed applications," Proc. SPIE 7536, 753605 (2010).

- D. Stoppa, L. Pancheri, M. Scandiuzzo, L. Gonzo, G.-F. Dalla Betta, and A. Simoni, "A CMOS 3-D imager based on single photon avalanche diode," IEEE Trans. Circ. Syst. 54(1), 4–12 (2007).

- 14. J. Burm, Y. Choi, S. R. Cho, M. D. Kim, S. K. Baek, D. Y. Rhee, B. O. Jeon, H. Y. Kang, and D. H. Jang, "Edge gain suppression of a planar-type InGaAs-InP avalanche photodiodes with thin multiplication layers for 10-Gb/s applications," IEEE Photon. Technol. Lett. 16(7), 1721–1723 (2004).

- A. Tosi, F. Acerbi, A. Dalla Mora, M. A. Itzler, and X. Jiang, "Active area uniformity of InGaAs/InP singlephoton avalanche diodes," IEEE Photon. J. 3(1), 31–41 (2011).

- M. W. Fishburn, Y. Maruyama, and E. Charbon, "Reduction of fixed-position noise in position-sensitive singlephoton avalanche diodes," IEEE Trans. Electron. Dev. 58(8), 2354–2361 (2011).

- 17. M. Gersbach, J. Richardson, E. Mazaleyrat, S. Hardillier, C. Niclass, R. K. Henderson, L. Grant, and E. Charbon, "A low-noise single-photon detector implemented in a 130 nm CMOS imaging process," Solid-State Electron. **53**(7), 803–808 (2009).

- 18. S. M. Sze, Physics of Semiconductor Devices, 2nd ed. (Wiley, 1981), pp. 771–772.

- F. Z. Hsu, J. Y. Wu, and S. D. Lin, "Low-noise single-photon avalanche diodes in 0.25 μm high-voltage CMOS technology," Opt. Lett. 38(1), 55–57 (2013).

- J. Richardson, E. A. G. Webster, L. Grant, and R. Henderson, "Scaleable single-photon avalanche diode structures in nanometer CMOS technology," IEEE Trans. Electron. Dev. 58(7), 2028–2035 (2011).

E. A. G. Webster and R. K. Henderson, "A TCAD and spectroscopy study of dark count mechanisms in single-

- E. A. G. Webster and R. K. Henderson, "A TCAD and spectroscopy study of dark count mechanisms in singlephoton avalanche diodes," IEEE Trans. Electron. Dev. 60(12), 4014–4019 (2013).

- 22. L. Pancheri and D. Stoppa, "Low-noise CMOS single-photon avalanche diodes with 32 ns dead time," in *Proc.* 37th ESSDERC (2007), 362–365.

- C. Niclass, K. Ito, M. Soga, H. Matsubara, I. Aoyagi, S. Kato, and M. Kagami, "Design and characterization of a 256 x 64-pixel single-photon imager in CMOS for a MEMS-based laser scanning time-of-flight sensor," Opt. Express 20(11), 11863–11881 (2012).

- 24. C. Veerappan, J. Richardson, R. Walker, D. U. Li, M. W. Fishburn, D. Stoppa, F. Borghetti, Y. Maruyama, M. Gersbach, R. K. Henderson, C. Bruschini, and E. Charbon, "Characterization of large-scale non-uniformities in a 20 k TDC/SPAD array integrated in a 130 nm CMOS process," in *Proc. IEEE Eur. Solid-State Device Res. Conf.* (2011), 331–334.

- C. Niclass, M. Sergio, and E. Charbon, "A single photon avalanche diode array fabricated in 0.35 μm CMOS and based on an event-driven readout for TCSPC experiments," Proc. SPIE 6372, 63720S (2006).

- N. Faramarzpour, M. J. Deen, S. Shirani, and Q. Fang, "Fully integrated single photon avalanche diode detector in standard CMOS 0.18-µm technology," IEEE Trans. Electron. Dev. 55(3), 760–767 (2008).

- S. Radovanovic, "High-speed photodiodes in standard CMOS technology," Ph.D. dissertation, Univ. of Twente, Enschede, The Netherlands (2004).

- 28. G. Chynoweth and K. G. McKay, "Photon emission from avalanche breakdown in silicon," Phys. Rev. 102(2), 369–376 (1956).

- G. L. Teh, W. K. Chim, Y. K. Swee, and Y. K. Co, "Spectroscopic photon emission measurements of n-channel MOSFET's biased into snapback breakdown using a continuous-pulsing transmission line technique," Semicond. Sci. Technol. 12(6), 662–671 (1997).

- O. Breitenstein, J. Bauer, J.-M. Wagner, N. Zakharov, H. Blumtritt, A. Lotnyk, M. Kasemann, W. Kwapil, and W. Warta, "Defect-induced breakdown in multicrystalline silicon solar cells," IEEE Trans. Electron. Dev. 57(9), 2227–2234 (2010).

- D. Lausch, K. Petter, H. V. Wenckstern, and M. Grundmann, "Correlation of pre-breakdown sites and bulk defects in multicrystalline silicon solar cells," Phys. Stat. Sol. RRL 3(2–3), 70–72 (2009).

- 32. Sentaurus User Guide, Synopsys, Mountain View, CA, USA (2011).

## 1. Introduction

In Geiger mode operation, single-photon avalanche diodes (SPADs) exhibit higher sensitivity while its excellent timing resolution is comparable with the photomultiplier tubes (PMTs) [1]. Unlike bulky PMTs operated at very high voltage, semiconductor-based SPADs are operated at much lower voltage, of small volume, and easily integrated with control and sensing circuit [2, 3]. Recently, circuit-integrated SPADs fabricated with CMOS technology have been successfully implemented in many applications such as the 3-D imaging [4], range finding [5], integrating receiver for optical communications [6], fluorescence lifetime image microscopy (FLIM) [7], and positron emission tomography (PET) [8, 9]. The advantage of SPADs over other conventional photodiodes is its capability of counting single photons. The photon detection efficiency (PDE), defined as the ratio between the numbers of detected photons and of incident photons, is governed by the product of photon absorption probability and avalanche trigger probability. By applying higher excess bias on a SPAD, one can increase the electric field as well as the trigger probability so its PDE can be enhanced. At the same time, the buildup time of avalanche could be reduced and resulting a smaller jitter [10]. Therefore, in practice, SPADs operated at high excess bias are desired as long as their dark count rates (DCRs) are acceptable. High excess bias could effectively boost the device performance when the build-up electric field is uniform over the active region because the uniformity is important for obtaining a reliable result in the applications of weak light detection and timing resolution. For example, when photons arrive at different positions of the active region, the non-uniform response time due to electric field distribution would cause inconsistent results and worsen the timing jitter.

Few works addressed the issue previously. The non-uniformity in PDE between multipixels of CMOS-SPAD array has been reported [11]. Due to the variation of the breakdown voltage from pixel to pixel, the PDE appears to be non-uniform between pixels. This appeared a serious problem in multi-pixels' applications, such as weak light imaging and recognition systems [12, 13]. Within a single device, the uniformity of electric field distribution has been studied on InGaAs/InP SPADs by using 2-D mapping of photon counts [14, 15]. For siliconbased CMOS-SPADs, previous work used the charge-coupled-device (CCD) camera to take their breakdown flash image. The breakdown flash arising from the impact ionization could indicate the electric field distribution [16, 17] through the field dependence of ionization rate. The method has two problems. First, the physical mechanism involved in the photon-induced breakdown is different from that in the breakdown flash so the breakdown flash distribution is not a direct evaluation of photo-response non-uniformity. Second, since the breakdown-flash method collected the photons from every depth in the device together, it cannot resolve the depth distribution of electric field.

In this paper, we study the wavelength-dependent 2-D mapping of photon counts for two different CMOS-SPADs at various excess biases. The first SPAD with the guard-ring structure shows uniform distribution of photon counts at its central region but the guard-ring degrades the photon detection capability around the edge. The second SPAD exhibits nonuniform photon-count distribution at high excess bias but it is wavelength-dependent. Nonuniformity becomes clearer for the shorter incident wavelength. Since the absorption length of photons increases with increasing wavelengths, the wavelength-dependent photon-count distribution could be attributed to the depth-dependent electric field. In addition, the breakdown flash image and device simulation have also been implemented to compare with the results of 2-D photo-count mapping.

#### 2. Measurement and device characteristics

### 2.1. Device structure and dark characteristics

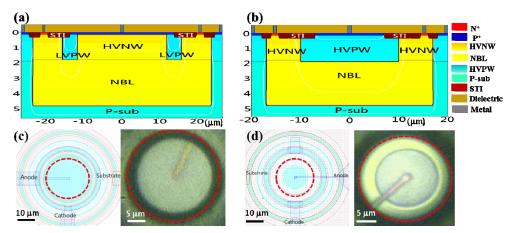

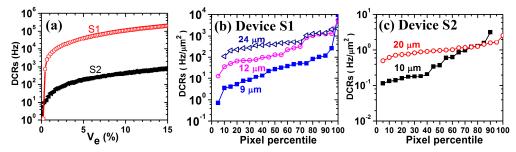

Two different structures of SPADs, denoted as S1 and S2, are fabricated by TSMC 0.25 µm high voltage CMOS process as shown in Figs. 1(a) and 1(b), respectively. The active region of S1 consists of P+/HVNW (high-voltage n-well) with LVPW (low-voltage p-well) guard ring to prevent the corner breakdown [18]. The deep p-n junction in S2 is formed by HVPW/NBL (high-voltage p-well/n buried layer) which is a virtual guard-ring structure [19, 20]. The layouts and photo images of the devices are shown in Figs. 1(c) and 1(d). By using a semiconductor parameter analyzer (HP 4145B), we measured the I-V characteristics and the breakdown voltage of the devices. The DCR measurement used a passive quenching circuit consisting of a 430-k $\Omega$  resistor in series with anode of SPADs to quench the avalanche current. A  $50\Omega$  resistor is used for impedance match with the counter in series with cathode of SPADs. The avalanche current was sensed through an ac coupled capacitor (10 nF) and the signal was amplified by a photon counting unit (C9744) and then counted by a dual channel counter (SR 400). The shallow-junction structure S1 has a breakdown voltage  $V_{bd}$  of 23 V and its DCR is about 110 kHz at 10% excess bias  $V_e$  that is defined as  $V_e = (V_{bias} - V_{bd}) / V_{bd}$ . The other structure S2 has a deep junction and a breakdown voltage of about 75 V and its DCR is about 400 Hz at 10% excess bias V<sub>e</sub>. The bias-dependent DCRs of the two devices are shown in Fig. 2(a). The huge difference of DCRs between the two kinds of devices has been discussed previously [19]. In addition, by investigating the DCRs on 20 chips, we illustrated the distribution of DCRs in Fig. 2(b) for S1 and in Fig. 2(c) for S2. Usually, the devices with smaller active area exhibit lower DCRs but the DCRs uniformity degrades due to the defect density fluctuation in CMOS process [21, 22]. For our devices S1 and S2, the smaller devices show larger device-to-device variations in the DCRs. The 20-µm S2 device has the best uniformity as shown in Fig. 2(c). The low value and small device-to-device variations in the DCRs could be because of the active region of structure S2 is distant from the defects near the surface. Comparing with that in previous works [7, 22–24], our results show highly uniform DCRs distribution, which is a merit for array applications.

Fig. 1. Schematic structures of 24-μm-diameter S1 (a) and 20-μm-diameter S2 (b). The layouts and the top-viewed photo images of two devices S1 (c) and S2 (d). The active breakdown region is enclosed with red dashed circle.

Fig. 2. (a) Bias-dependent DCRs of device S1 of 24- $\mu$ m diameter and device S2 of 20- $\mu$ m diameter. The pixels percentile of DCRs at 5% excess bias (V<sub>c</sub>) for devices S1 (b) and S2 (c).

### 2.2. Photon detection characteristics

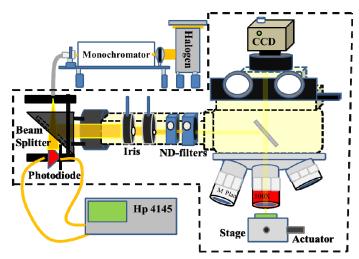

The photo-response experiments under the condition of low after-pulsing probability (< 2%) are implemented by using a passive quenching circuit with 430 k $\Omega$  resistors. The system for 2-D photo-count mapping and PDE measurement is schematically illustrated in Fig. 3. To characterize the PDE of our SPADs, white light from a 1000 W halogen source was dispersed by a monochromator, coupled into a fiber, and then transmitted into a microscope in the dark box. The shutter in front of the monochromator (not shown) can be automatically turned on and off so the light and dark counts can be taken under the almost same condition. A polkadot beam-splitter separates the incident photons into two beams, one for the real-time monitoring photodiode (Thorlabs, FDS100-CAL) and the other one for the SPADs under test. With a zero-aperture iris on the microscope and 100X near-infrared objective lens, the spot size can be less than 1  $\mu$ m for 2-D photo-count mapping or around the respective diameters of the SPADs for PDE measurement. To perform 2-D mapping of photon counts, a high-precision stage driven by two computer-controlled actuators (Thorlabs Z825B) is placed under the objective lens. Note that, for 2-D mapping, the incident photon flux is about the same for all wavelengths to avoid any power-dependent effect.

Fig. 3. Schematic PDE and 2-D mapping measurement system in a dark box.

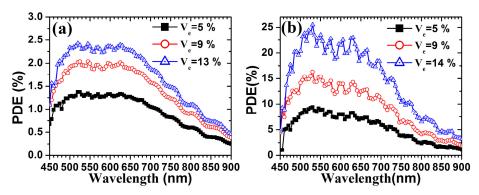

The bias- and wavelength-dependent PDE of two devices are plotted in Fig. 4. Clear oscillations in PDE spectra due to the passivation layers in CMOS process are observed for both structures. The PDE of device S2 is about 25% which is much higher than that of S1 due to a thicker depletion region formed by the lightly-doped junction. The PDE of device S1 could be improved by simply removing the passivation layer and by depositing the anti-reflection layers on the device surface, which is available in CMOS image-sensor technology [25].

Fig. 4. PDE spectra of (a) device S1 and (b) device S2 at various excess biases.

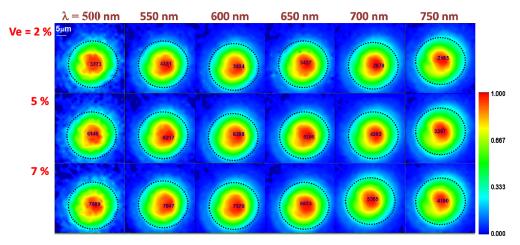

In Fig. 5, the 2-D photo-count mappings on device S1 of 24- $\mu$ m diameter at various wavelengths and bias voltages are shown. Two clear regions with high (red) and low (green) photo-counts are spotted and they are nearly the same at all wavelength and biases. The ring-shape outer region of low photo-counts arises from the junction depletion between the LVPW guard ring and HVNW layer as the photo-generated carriers cannot trigger the avalanche breakdown [25]. The circular-like high photo-counts region at the center is about  $8-12~\mu m$  in diameter so the one-side depletion width is about  $6-8~\mu m$ . This large depletion width is problematic when one would like to shrink the device size for array applications. Nevertheless, the high photo-count region exhibits a pretty uniform distribution at nearly all wavelengths and biases. In Fig. 6, for the deep-junction device S2, the 2-D mapping of photo-counts exhibits quite differently. Aside from the outer ring of low photo-counts (green), which could be caused by either the depletion at HVPW/HVNW junction or by the presence of STI layer near the surface, the center region also shows a bias- and wavelength-dependent non-uniformity. The non-uniform distribution of photo-counts becomes more significant at

shorter wavelength and higher excess bias. This will be discussed in detail in the simulation section later. Note that, by summing up the photo-counts at every point, we have confirmed that the total counts show a similar trend with the PDE spectra plotted in Fig. 4.

Fig. 5. 2-D mapping of photon counts on the 24- $\mu$ m device S1 at various wavelengths and excess biases  $V_e$ . The active breakdown region is enclosed with black dashed circle.

Fig. 6. 2-D mapping of photon counts on the 20- $\mu$ m device S2 at various wavelengths and excess biases V<sub>e</sub>. The active breakdown region is enclosed with black dashed circle.

It is clear that, through our 2-D photo-count mapping at various wavelengths, we can reveal the photon response of the SPADs with high-spatial resolution and, more interestingly, the depth-dependent electric field distribution. Because the absorption length of photons increases with increasing wavelengths, the generation of photo-carriers concentrates only in a shallow region for short-wavelength incidence [27]. This could quantitatively tell the electric field distribution in depth. Together with the 2-D mapping of photo-counts, a quasi-3D distribution of electric field in SPADs could be investigated. Actually, this has been clearly demonstrated in the row with a fixed excess bias (for example,  $V_e = 9\%$ ) in Fig. 6. The centered non-uniformity of photo-counts distribution decreases with the increasing wavelengths, indicating that the non-uniformity of electric field is more serious at the shallower region. Additionally, at a fixed wavelength (for example,  $\lambda = 750$  nm) in Fig. 6, the non-uniformity of photo-counts increases with the increasing bias voltages, as expected.

## 2.3. Breakdown flash image

It has been known for long that, when a p-n junction is reversely biased above the breakdown voltage, it emits photons of a broad and continuous energy during the avalanche process [28]. By capturing the emission image, one can therefore reveal the electric field distribution and defect locations in devices, such as MOSFET [29], solar cell [30] and SPADs [16, 17]. However, in the measurement of breakdown flash from SPADs, as the photons emitted from all the depths are collected together, the depth-dependent information is missed. Even worse, defects in the active region could induce a localized breakdown and give rise to a brighter flash, which would overshadow the actual electric-field distribution [31]. We performed the breakdown flash measurement for two reasons here. The first one is to compare the two methods of the 2-D photo-count mapping and the breakdown flash image. The other one is to verify that the centered non-uniform photo-count distribution originates from the electric field distribution. The breakdown flash image is captured with a liquid nitrogen cooled CCD mounted on a spectrometer at undispersed grating angle. The passive quenching circuit with a small resistor of  $100 \text{ k}\Omega$  is used to obtain a clear image of the breakdown flash.

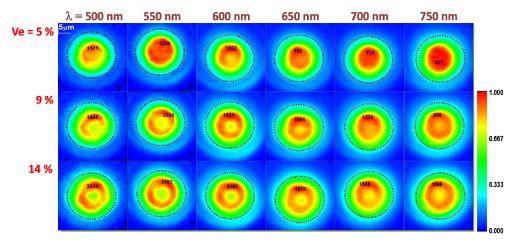

In Fig. 7(a), the photo picture (the first one on the left, denoted as Light) and breakdown flash images of device S1 biased at  $V_e = 9\%$ , 17%, and 26% are shown. Clearly, the breakdown flash is mainly emitted from the two locations in the active region. The locations with bright flash vary from chip to chip so it could be caused by the randomly localized defects rather than by the non-uniform electric field.

Fig. 7. Breakdown flash images of (a) device S1 and (b) device S2 at different excess bias. Both upper left images are illuminated by a halogen light. All the flash images are taken with integration time of 5 minutes. The active breakdown region is enclosed with red dashed circle.

The breakdown flash image of device S2 in Fig. 7(b) exhibit a very different pattern from that of device S1. A large bright region around the center of the device is spotted. This pattern appears in almost all devices S2 under test so it could arise from the electric field distribution in the active region. However, comparing with the 2-D photo-count mapping in Fig. 6, the centered non-uniformity of photo-counts is not resolvable in the breakdown flash image. We reckon that, because the breakdown flash collected the photons from all depth, the centered non-uniformity were smeared out. It is similar to that we sum up the 2-D photo-count mappings at all wavelengths and at a fixed bias in Fig. 6. In addition, a brighter ring-shape region is observed around the active region in Fig. 7(b). This ring-shape region corresponds to the STI layer, which reduces the absorption of breakdown flash by silicon layer so a brighter ring image emerges.

## 3. Simulations and discussions

## 3.1. Electric field distribution

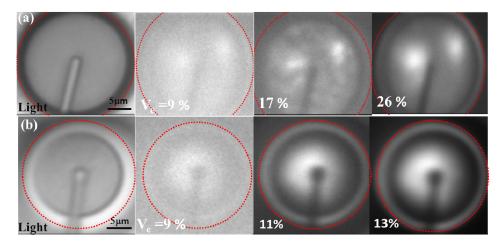

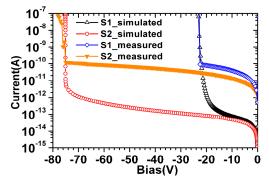

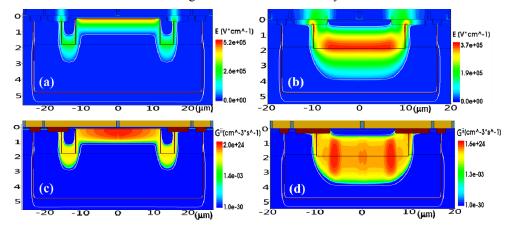

We have simulated the electric field distribution in both structures with Synopsys Sentaurus TCAD 2013. The simulated structures are identical to those in Figs. 1(a) and 1(b) with a Gaussian doping profile created by the structure editor tool [32]. The simulated I-V curves of devices S1 and S2, together with the measured ones, are shown in Fig. 8. The breakdown voltage V<sub>bd</sub> is well fitted by properly choosing the doping concentrations of each layer. The difference between the simulated and experimental dark currents below V<sub>bd</sub> is clearly because the simulated structure did not include the parasitic leakage paths such as CMOS dielectric stack, surface generation and deep level traps [21]. In Fig. 9, the calculated electric field and impact ionization distributions at  $V_e = 0\%$ , that is, at the breakdown voltage, for both devices are illustrated. Comparing the electric field distributions in Figs. 9(a) and 9(c), the depletion width in device S2 is thicker than that in device S1 due to its lower doping concentration. As a result, device S2 has a higher breakdown voltage and a higher PDE. It is also clear in Fig. 9 that the electric field and impact ionization rate distributions in device S1 are more uniform comparing with those in device S2. As shown in Fig. 9(c), the impact ionization rate in center region of device S1 is higher, which is consistent with our observation in the 2-D photoncount mapping in Fig. 5. On the other hand, interestingly, the impact ionization rate distribution in device S2 (see Fig. 9(d)) shows two hot spots at the HVPW-NBL junction under the interface of P+/STI. These spots have relatively high impact ionization rate due to the slightly high electric field there (see Fig. 9(b)). These two hot spots could correspond to the ring shape observed in Fig. 6 as our simulation is two dimensional. Because the ring shape region in Fig. 6 is wavelength- and voltage-dependent. We have to perform the biasdependent simulation as follows.

Fig. 8. Simulated and measured I-V characteristics of device S1 of 24- $\mu$ m diameter and device S2 of 20- $\mu$ m diameter.

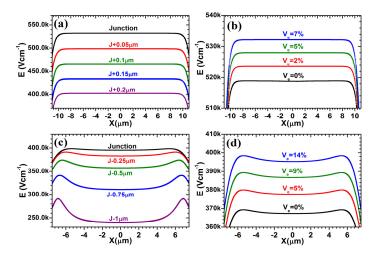

To simulate the electric field distribution above breakdown voltage, we take off the avalanche impact-ionization generation in the simulation tool. This is physically valid for SPADs as it is actually one of the bi-stable states when there is no dark count or photon count and hence no carrier exists in the active region [21]. In Fig. 10, the electric fields at various depths for two devices at various excess biases are plotted against the lateral positions. Note that, for clarity, the depths measured from the junction are denoted as J + d, where d = 0 to + 0.2 µm for device S1 and d = 0 to -1.0 µm for device S2. One can clearly see a uniform electric field distribution at all depths and all biases for device S1 in Figs. 10(a) and 10(b). In contrast, device S2 exhibits a highly depth- and bias-dependent distribution of electric field, as seen in Figs. 10(c) and 10(d). This non-uniformity in electric field distribution becomes more significant at shallower depths and at higher excess biases, which is consistent with the 2-D mappings in Fig. 6. Therefore, we confirm that the ring shape in 2-D photo-count mappings arises from the non-uniform 3-D electric field distribution in the device S2. This

non-uniformity could be caused by the lateral junction of HVNW/HVPW and by the n-contact location but further investigations are needed to clarify this issue.

Fig. 9. Simulated electric field and impact ionization distributions for device S1, (a) and (c), and for device S2, (b) and (d), respectively, at breakdown voltage.

Fig. 10. Simulated electric field strength along lateral direction of device S1, (a) and (b), and device S2 (c) and (d). The depth-dependent curves in (a) and (c) are obtained with  $V_e = 7\%$  for S1 and  $V_e = 14\%$  for S2, respectively.

## 3.2. Guard-ring depletion

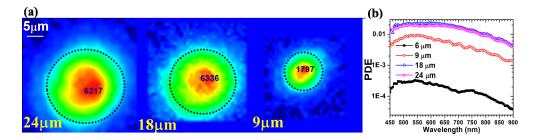

Our method of 2-D photo-count mapping is useful for characterize the photo-response of SPADs. As an example, we have also studied the devices S1 with various diameters. For device S1, which shows a more uniform electric field distribution, its active area is restricted by the lateral depletion from the guard-ring. The 2-D mappings of photon-counts and the PDE measurement for the devices of 6, 9, 18, and 24  $\mu$ m diameters are shown in Figs. 11(a) and 11(b). In Fig. 11(a), the centered sensing area in 9- $\mu$ m device becomes extremely small (< 5  $\mu$ m). This is also revealed with the PDE measurement shown in Fig. 11(b). The devices with 24 and 18  $\mu$ m show almost the same PDE but the PDEs decreases dramatically for 9 and 6  $\mu$ m devices. It consists with the fact that the guard-ring structure could be a problem as the device size becomes small [26].

Fig. 11. (a) 2-D mapping of photo-counts for devices S1 of diameter 24, 18, and 9  $\mu m$  at  $V_e$  = 9% for the incident wavelength of 550 nm. The active breakdown region is enclosed with black dashed circle. (b) PDE spectra for devices S1 of diameter 24, 18, 9, and 6  $\mu m$  at  $V_e$  = 9%.

We further calculate the inactive distance of device S1 and device S2 by following the method proposed in [16]. The estimated inactive distance of device S1 is about 2  $\mu m$  at  $V_e = 5\%$  for the incident light of 520 nm wavelength and decreases with excess bias. This result accords with the measurement of 2-D photo-count mapping and evidences that the lower detection efficiency of 9 and 6  $\mu m$  devices results from the greater part of inactive area. The estimated inactive distance of device S2 is approximately 2.3  $\mu m$  and remains almost constant for any excess bias. The width of inactive area consists with the TCAD simulations and the measurements.

#### 4. Conclusion

We have presented a method of 2-D photo-count mapping on Si-based SPADs. The method can be used to examine the 3-D electric field uniformity in the device by varying the incident wavelengths. A comprehensive study on two structures demonstrates how the electric field distribution affects the photo-response characteristic. It is evident that, by combining with the simulation tool, the 2-D photo-count mapping could provide a guide to improve device sensitivity with proper structure engineering, which is crucial for various applications on weak light detection.

# Acknowledgments

We are grateful to the National Center for High-performance Computing for computer time and facilities and the National Chip Implementation Center (CIC) for their help on chip fabrication. This work was financially supported by the NSC and ATU program of MOE in Taiwan. We thank S. C. Li and F.Z. Hsu for chip tape-out.