Home Search Collections Journals About Contact us My IOPscience

Performance comparison of titanium-oxide resistive switching memories using  $\text{GeO}_{\chi}$  and  $\text{AlO}_{\chi}$  capping layers for flexible application

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2014 Jpn. J. Appl. Phys. 53 061502

(http://iopscience.iop.org/1347-4065/53/6/061502)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 25/12/2014 at 02:47

Please note that terms and conditions apply.

# Performance comparison of titanium-oxide resistive switching memories using GeO<sub>x</sub> and AlO<sub>x</sub> capping layers for flexible application

Kun-I Chou<sup>1</sup>, Chun-Hu Cheng<sup>2</sup>, and Albert Chin<sup>1\*</sup>

Received January 4, 2014; accepted March 11, 2014; published online May 19, 2014

To meet the requirements of flexible memory applications, we have compared two capping layers of  $GeO_x$  and  $AlO_x$  on a  $TiO_y$  resistive random access memory (RRAM) at room temperature. A Ni/ $GeO_x$ / $TiO_y$ /TaN RRAM shows a large resistance window of >  $10^2$ , 85 °C retention, a high-resistance-state (HRS) activation energy ( $E_a$ ) of 0.52 eV, and a good DC cycling of  $10^3$  cycles, which are significantly better than those of a Ni/ $AlO_x$ / $TiO_y$ /TaN RRAM, which has a high-defect-density dielectric of  $AlO_x$ . © 2014 The Japan Society of Applied Physics

#### 1. Introduction

Flexible electronics are attractive for next-generation display technology. One challenge in the fabrication of flexible electronics is the lack of a nonvolatile memory (NVM) for system-on-chip (SoC) function. The conventional floatinggate or charge-trapping flash memory<sup>1,2)</sup> is difficult to integrate into flexible substrates owing to the severely degraded gate oxide quality at low temperatures.<sup>3,4)</sup> Therefore, several NVM types such as ferroelectric randomaccess memories (FeRAMs),<sup>4)</sup> magnetic random-access memories (MRAMs), and resistive random-access memories (RRAMs)<sup>5–17)</sup> are being investigated. RRAMs have attracted much attention for next-generation NVM applications owing to their simple structure, small cell size, and high speed. On the other hand, RRAMs have inherent merits of a lowertemperature process and a simpler structure for flexible electronics applications. 18-24) However, they require costly noble metal electrodes and poor resistance distribution. Such a poor distribution prevents further memory array realization, in sharp contrast to the existing sub-tera-bit flash memory. To address these issues, we previously developed ultralowpower RRAMs<sup>6-8)</sup> to lessen the dielectric stress. The Ni/ GeO<sub>x</sub>/high-κ/TaN RRAMs show a negative temperature coefficient (TC), opposite to other conductive-filament-type RRAMs owing to ion migration.

In this paper, we present a room-temperature Ni/GeO $_x$ /TiO $_y$ /TaN RRAM device with 0.28  $\mu$ W set power, low 25  $\mu$ W reset power, fast switching (10  $\mu$ s) and a stable endurance in the 1000 cycling test. For comparison, we also investigate a room-temperature Ni/AlO $_x$ /TiO $_y$ /TaN RRAM device, which has a similar switching power but markedly poor endurance and poor switching uniformity owing to the defect-rich AlO $_x$  dielectric processed at room temperature. The present results demonstrate that the room-temperature Ni/GeO $_x$ /TiO $_y$ /TaN RRAM has high potential for future flexible memory applications.

## 2. Experimental procedure

The RRAM devices were fabricated on standard Si wafers. For VLSI backend integration, the process was started by depositing a 200-nm-thick  $SiO_2$  layer on the Si substrates. Then, 100 nm TaN was prepared by physical vapor deposition (PVD). After patterning the bottom TaN electrode, a 15-nm-thick  $TiO_v$  film and a 6-nm-thick  $GeO_x$  layer were

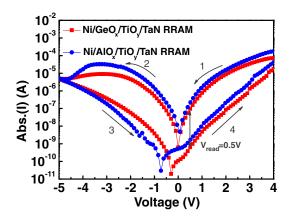

**Fig. 1.** (Color online) Swept  $I\!-\!V$  curves of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN and Ni/AlO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices.

deposited at room temperature to form the stacked structure of  $\text{GeO}_x/\text{TiO}_y$ . Lastly, a 50-nm-thick Ni layer was deposited and patterned to form the top electrode with an area of  $11300\,\mu\text{m}^2$  in the RRAM device. For comparison, the Ni/  $\text{AlO}_x/\text{TiO}_y/\text{TaN}$  RRAM device was also fabricated with a 6-nm-thick  $\text{AlO}_x$  capping layer on  $\text{TiO}_y$ . Here, Ni provides a low-cost solution for a high-work-function (5.1 eV) electrode, which has been implemented in high- $\kappa$  DRAM capacitors.<sup>25</sup>)

## 3. Results and discussion

Figure 1 shows the current–voltage (I-V) switching characteristics of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN and Ni/AlO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices on the SiO<sub>2</sub> isolation layer. The formingfree and self-compliance current switching characteristics are measured, which are vital for simplifying the circuit design without the need for a high-current forming process and extra current compliance. The low self-compliance set currents of 78 and 73  $\mu A$  at 4 V and low reset currents of 2.3 and 5  $\mu A$  at -5 V are measured in  $\text{AlO}_x/\text{TiO}_v$  and  $\text{GeO}_x/\text{TiO}_v$  RRAM devices, respectively. The switching windows at a reading voltage of 0.5 V for  $\text{AlO}_x/\text{TiO}_y$  and  $\text{GeO}_x/\text{TiO}_y$  RRAM devices are  $130 \times$  and  $152 \times$ , respectively. From resistive I-Vcurves, these two RRAM devices show close switching high/low-resistance-state (HRS/LRS) currents and resistance windows. Although the AlO<sub>x</sub>/TiO<sub>y</sub> RRAM and GeO<sub>x</sub>/TiO<sub>y</sub> RRAM devices have similar switching characteristics, the AlO<sub>x</sub>/TiO<sub>y</sub> RRAM device shows poor endurance character-

<sup>&</sup>lt;sup>1</sup>Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 30010, Taiwan, R.O.C.

<sup>&</sup>lt;sup>2</sup>Department of Mechatronic Technology, National Taiwan Normal University, Taipei 106, Taiwan, R.O.C. E-mail: albert\_achin@hotmail.com

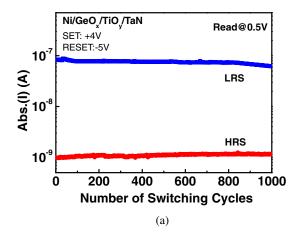

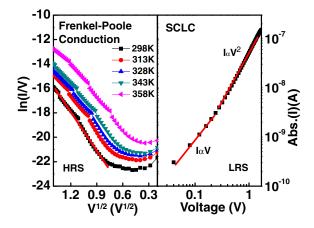

**Fig. 2.** (Color online) Endurance cycling of (a) Ni/GeO $_x$ /TiO $_y$ /TaN and (b) Ni/AlO $_x$ /TiO $_y$ /TaN RRAM devices.

istics [Fig. 2(b)] in the 100 cycling test under set/reset conditions of 4 V/-5 V. The degraded resistance windows after cycling 100 times are about 42% in the AlO<sub>x</sub>/TiO<sub>y</sub> RRAM device. The step like deteriorations at LRS may be caused by electron trapping near the Ni/AlO<sub>x</sub> interface, which results in unstable switching behavior and window shrinking during continued cycling. Unlike the degraded memory window of the AlO<sub>x</sub>/TiO<sub>y</sub> RRAM device, the GeO<sub>x</sub>/ TiO<sub>v</sub> RRAM exhibits stable *I–V* switching at both HRS and LRS currents and large HRS/LRS ratio. In contrast to GeO<sub>x</sub>/ TiO<sub>v</sub>, an unstable HRS current and a gradually reduced LRS current are obtained in AlO<sub>x</sub>/TiO<sub>y</sub> RRAMs, which indicates that the presence of defect centers in the AlO<sub>x</sub>/TiO<sub>y</sub> stack or near the electrode interface affects resistive switching characteristics. From the endurance results, it is demonstrated that the poor HRS/LRS switching behaviors during cycling are dominated by trap-controlled Frenkel-Poole (FP) conduction through trapping and detrapping effects.

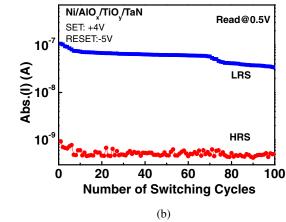

To understand the low switching power, we have analyzed the current conduction mechanism, as shown in Fig. 3. We apply a negative voltage to the top Ni electrode for electron injection for us to measure and fit I–V characteristics under HRS conditions. The good agreement between the measured and fitting HRS currents suggests that the currents are conducted via the FP emission mechanism:

$$J \propto E \exp\left(\frac{\sqrt{q^3 E/\pi\varepsilon}}{k_{\rm B} T}\right)$$

. (1)

**Fig. 3.** (Color online) I–V curves of the HRS and LRS of Ni/GeO $_x$ /TiO $_y$ /TaN RRAM obtained by fitting with FP and space-charge-limited current mechanisms.

Here, J is the current density; E, the applied electric field; q, the elementary charge;  $\varepsilon$ , the dynamic permittivity;  $k_{\rm B}$ , Boltzmann's constant; and T, the temperature. The increasing HRS current with increasing temperature is due to the high hopping emission rate, which increases FP conduction. <sup>26</sup> In order to reach LRS, a positive voltage is applied to the top Ni electrode, where electrons were injected from the bottom TaN electrode. At a low electric field, LRS exhibits space-charge-limited current (SCLC) with trap control, since the slopes are proportional to V.

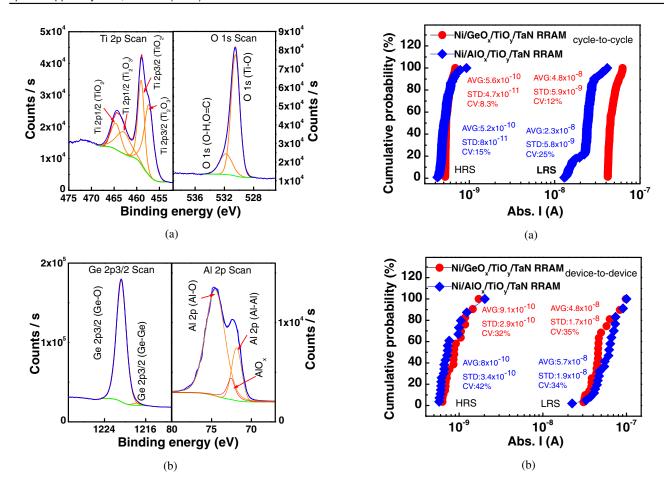

We have further conducted X-ray photoelectron spectroscopy (XPS) to study the current conduction mechanism. To precisely analyze material bonding, the film samples of TiO<sub>x</sub>, AlO<sub>x</sub>, and GeO<sub>x</sub> are pretreated by in situ Ar bombardment for 10 s under 6 to  $8 \times 10^{-8}$  Torr to remove the native oxide on the sample surface. Figures 4(a) and 4(b) show the Ti 2p, and O 1s, and Ge 2p<sub>3/2</sub> and Al 2p XPS spectra, respectively. The nonstoichiometric TiO dielectric has different titanium energy peaks such as Ti 2p<sub>3/2</sub> (Ti<sup>4+</sup>) and Ti  $2p_{3/2}$  (Ti<sup>3+</sup>), as shown in Fig. 4(a). The different Ti ion chemical states were measured in the TiO dielectric, indicating the formation of charged oxygen vacancies, which is favorable for resistance switching in RRAM devices under appropriate biasing conditions. In Fig. 4(b), the Ge 2p<sub>3/2</sub> XPS spectrum reveals that the composition of the roomtemperature-processed GeO dielectric is close to stoichiometric. However, the Al 2p XPS spectrum shows three different binding energies corresponding to different valence bonds, namely,  $Al_2O_3$  ( $Al^{3+} = 74.5 \text{ eV}$ ), Al-Al bonds  $(Al^{2+} = 71.8 \text{ eV})$ , and  $AlO_x$  (72.5 eV) of the AlO dielectric. The different Al ion chemical states indicate the formation of charged oxygen vacancies and an oxygen-deficient dielectric layer, which may lead to temperature-dependence leakage current even with a large bandgap.

Good uniformity is the fundamental challenge in the fabrication of RRAM devices for NVM array applications. Only few RRAM papers showed the cycle-to-cycle (C2C) distribution in the same device, rather than the NVM-array-required device-to-device (D2D) distribution among different devices.  $^{5-21}$  Figures 5(a) and 5(b) show the C2C and D2D current distributions of the  $\text{GeO}_x/\text{TiO}_y$  and  $\text{AlO}_x/\text{TiO}_y$  RRAM devices, respectively. Because of the different mean

**Fig. 4.** (Color online) XPS spectra of (a) Ti 2p and O 1s, and (b) Ge 2p3 and Al 2p of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN and Ni/AlO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices.

**Fig. 5.** (Color online) (a) C2C and (b) D2D current distributions of Ni/GeO $_x$ /TiO $_y$ /TaN and Ni/AlO $_x$ /TiO $_y$ /TaN RRAM devices.

values, the coefficient of variation (CV) was used to evaluate the distribution. The CV is a normalized measure of dispersion of a probability distribution, defined as the ratio of standard deviation ( $\sigma$ ) to mean value ( $\mu$ ). The C2C current CVs of LRS for AlO<sub>x</sub>/TiO<sub>y</sub> and GeO<sub>x</sub>/TiO<sub>y</sub> RRAMs are 25 and 12%, whereas the C2C current CVs of HRS for AlO<sub>x</sub>/ TiO<sub>v</sub> and GeO<sub>x</sub>/TiO<sub>v</sub> RRAMs are 15 and 8.3%, respectively. In Fig. 5(a), the AlO<sub>x</sub>/TiO<sub>y</sub> RRAM shows poor current distribution in bulk-limited self-compliance LRS. The unstable resistance switching can be attributed to the defect-rich AlO<sub>x</sub> capping layer that affects bulk vacancy control in LRS. Figure 5(b) shows the D2D current distributions of the  $GeO_x/TiO_y$  and  $AlO_x/TiO_y$  RRAMs. In HRS, the  $AlO_x/TiO_y$ RRAM shows the worse D2D distribution, resulting from the poor surface coverage uniformity of the defect-rich AlO<sub>x</sub> layer. The only way to improve the poor HRS/LRS distributions in AlO<sub>x</sub>/TiO<sub>y</sub> RRAM is oxygen annealing to remove defects, but high-temperature annealing is not allowed for flexible electronics.

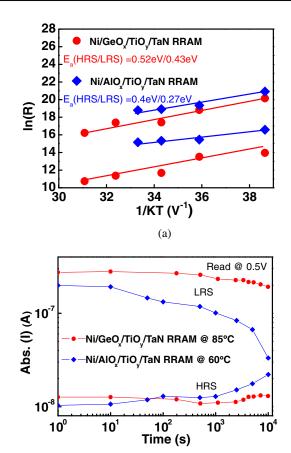

To study the conduction mechanism, we have measured the temperature-dependent current at LRS and HRS. The LRS activation energy ( $E_a$ ) of 0.43 eV for  $\text{GeO}_x/\text{TiO}_y$  RRAM is close to that of negative TC in highly defective Si governed by hopping conduction,<sup>28</sup> which suggests LRS mechanism are related by hopping via defects in  $\text{GeO}_x/\text{TiO}_y$  RRAMs, as shown in Fig. 6(a). Such hopping conduction and negative TC were observed previously in GeO.<sup>29</sup> Oxygen vacancies can be formed at a very low temperature, which degrade

GeO<sub>2</sub>/Ge MOSFETs,<sup>30)</sup> but they are very useful for RRAMs. However, a much lower LRS activation energy (0.27 eV) is obtained for the  $AlO_x/TiO_y$  RRAM, where the HRS/LRS resistance change may be dominated by electron tunneling via shallow traps in the thin defect-rich  $AlO_x$  tunneling barrier.

Good retention and endurance are the essential characteristics for NVM. Figure 6(b) shows the retention of GeO<sub>x</sub>/ TiO<sub>v</sub> and AlO<sub>x</sub>/TiO<sub>v</sub> RRAM devices. From the results, the AlO<sub>x</sub>/TiO<sub>y</sub> RRAM shows a very poor data retention characteristic such that the memory window is closed after  $10^4$  s at low 60 °C retention, compared with the  $GeO_x/TiO_y$ RRAM. Besides, the degraded HRS current at 60 °C retention can be attributed to the  $E_a$  in HRS (0.4 eV) being lower than  $0.52 \,\mathrm{eV}$  of the  $\mathrm{GeO}_x/\mathrm{TiO}_v$  RRAM device. This is because a high-temperature annealing for defect removal in the AlO<sub>x</sub> dielectric is necessary. The electrons pile up near the Ni/AlO<sub>x</sub> interface from the defect-rich AlO<sub>x</sub> layer, leading to window shrinking in LRS. In HRS, the defect-related current leakage from the defect-rich AlO<sub>x</sub> layer leads to window shrinking during the high-temperature retention test. Although the Al<sub>2</sub>O<sub>3</sub> dielectric has a large bandgap of 8.8 eV, the defect-rich AlO<sub>x</sub> layer processed at room temperature still cannot be prevented from having a degraded HRS current owing to thermally assisted tunneling via a lowered Ni/AlO<sub>x</sub> barrier under the high-temperature retention test.

### 4. Conclusions

The Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM provides good switching

**Fig. 6.** (Color online) (a) Activation energy and (b) retention of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN and Ni/AlO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices.

(b)

characteristics with a low self-compliance set current of 73  $\mu$ A at 4 V and a low reset current of 5  $\mu$ A at -5 V, a good switching window of  $152\times$ , and stable data retention at 85 °C for  $10^4$  s. Such good RRAM performance characteristics compared with Ni/AlO<sub>x</sub>/TiO<sub>y</sub>/TaN are related to the well-bonded GeO<sub>x</sub> dielectric deposited by room-temperature fabrication using a very suitable room-temperature flexible RRAM process. The room-temperature Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM with such good characteristics shows great promise in future flexible memory applications.

#### Acknowledgement

This work was supported by the National Science Council of Taiwan.

- A. Chin, C. C. Laio, C. Chen, K. C. Chiang, D. S. Yu, W. J. Yoo, G. S. Samudra, T. Wang, I. J. Hsieh, S. P. McAlister, and C. C. Chi, IEDM Tech. Dig., 2005, p. 165.

- C. Y. Tsai, T. H. Lee, A. Chin, H. Wang, C. H. Cheng, and F. S. Yeh, IEDM Tech. Dig., 2010, p. 110.

- M. F. Chang, P. T. Lee, S. P. McAlister, and A. Chin, IEEE Electron Device Lett. 30, 133 (2009).

- 4) N.-C. Su, S.-J. Wang, and A. Chin, IEEE Electron Device Lett. 31, 201 (2010)

- R. Yasuhara, T. Yamamoto, I. Ohkubo, H. Kumigashira, and M. Oshima, Appl. Phys. Lett. 97, 132111 (2010).

- 6) C.-H. Cheng, F.-S. Yeh, and A. Chin, Adv. Mater. 23, 902 (2011).

- C. H. Cheng, C. Y. Tsai, A. Chin, and F. S. Yeh, IEDM Tech. Dig., 2010, p. 448.

- 8) C. H. Cheng, A. Chin, and F. S. Yeh, Symp. VLSI Tech. Dig., 2010, p. 85.

- U. Russo, D. Ielmini, C. Cagli, A. L. Lacaita, S. Spiga, C. Wiemer, M. Perego, and M. Fanciulli, IEDM Tech. Dig., 2007, p. 775.

- C. H. Cheng, P. C. Chen, Y. H. Wu, F. S. Yeh, and A. Chin, IEEE Electron Device Lett. 32, 1749 (2011).

- 11) L. Zhang, R. Huang, D. Gao, D. Wu, Y. Kuang, P. Tang, W. Ding, A. Z. H. Wang, and Y. Wang, IEEE Electron Device Lett. 30, 870 (2009).

- 12) S. Yu, B. Gao, H. Dai, B. Sun, L. Liu, X. Liu, R. Han, J. Kang, and B. Yu, Electrochem. Solid-State Lett. 13, H36 (2010).

- 13) K. I. Chou, C. H. Cheng, Z. W. Zheng, M. Liu, and A. Chin, IEEE Electron Device Lett. 34, 505 (2013).

- 14) C. Y. Lin, S. Y. Wang, D. Y. Lee, and T. Y. Tseng, J. Electrochem. Soc. 155, H615 (2008).

- 15) I. Hwang, M. J. Lee, G. H. Buh, J. Bae, J. Choi, J. S. Kim, S. Hong, Y. S. Kim, I. S. Byun, S. W. Lee, S. E. Ahn, B. S. Kang, S. O. Kang, and B. H. Park, Appl. Phys. Lett. 97, 052106 (2010).

- 16) B. Gao, B. Sun, H. Zhang, L. Liu, X. Liu, R. Han, J. Kang, and B. Yu, IEEE Electron Device Lett. 30, 1326 (2009).

- 17) N. Xu, B. Gao, L. F. Liu, B. Sun, X. Y. Liu, R. Q. Han, J. F. Kang, and B. Yu, Tech. Dig. Symp. VLSI, 2008, p. 100.

- 18) S. H. Jin, Y. K. Lee, C. A. Lee, J. W. Kim, B. G. Park, and J. D. Lee, 61st Device Research Conf. (DRC) Tech. Dig., 2003, p. 185.

- M. F. Chang, P. T. Lee, S. P. McAlister, and A. Chin, Appl. Phys. Lett. 93, 233302 (2008).

- 20) M. J. Lee, C. B. Lee, S. Kim, H. Yin, J. Park, S. E. Ahn, B. S. Kang, K. H. Kim, G. Stefanovich, I. Song, S. W. Kim, J. H. Lee, S. J. Chung, Y. H. Kim, C. S. Lee, J. B. Park, I. G. Baek, C. J. Kim, and Y. Park, IEDM Tech. Dig., 2008, p. 85.

- 21) J. W. Seo, J.-W. Park, K. S. Lim, S. J. Kang, Y. H. Hong, J. H. Yang, L. Fang, G. Y. Sung, and H.-K. Kim, Appl. Phys. Lett. 95, 133508 (2009).

- S. Kim, H. Moon, D. Gupta, S. Yoo, and Y. K. Kyu, IEEE Trans. Electron Devices 56, 696 (2009).

- Z. Q. Wang, H. Y. Xu, X. H. Li, X. T. Zhang, Y. X. Liu, and Y. C. Liu, IEEE Electron Device Lett. 32, 1442 (2011).

- 24) S. Kim and Y. K. Choi, Appl. Phys. Lett. 92, 223508 (2008).

- 25) W. B. Chen and A. Chin, Appl. Phys. Lett. 95, 212105 (2009).

- 26) C. C. Yeh, T. P. Ma, N. Ramaswamy, N. Rocklein, D. Gealy, T. Graettinger, and K. Min, Appl. Phys. Lett. 91, 113521 (2007).

- 27) I. L. Liu, P. Shen, and S. Y. Chen, J. Phys. Chem. C 114, 7751 (2010).

- 28) A. Chin, K. Lee, B. C. Lin, and S. Horng, Appl. Phys. Lett. 69, 653 (1996).

- N. Sasi, C. Balasubramanian, and S. K. Narayandass, Phys. Status Solidi 103, 475 (1987).

- 30) K. C. Chiang, C. H. Cheng, H. C. Pan, C. N. Hsiao, C. P. Chou, A. Chin, and H. L. Hwang, IEEE Electron Device Lett. 28, 235 (2007).