# RF, DC, and Reliability Characteristics of ALD HfO<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub> Laminate MIM Capacitors for Si RF IC Applications

Shi-Jin Ding, Hang Hu, Chunxiang Zhu, *Member, IEEE*, Sun Jung Kim, Xiongfei Yu, Ming-Fu Li, *Senior Member, IEEE*, Byung Jin Cho, *Senior Member, IEEE*, Daniel S. H. Chan, *Senior Member, IEEE*, M. B. Yu, Subhash C. Rustagi, *Senior Member, IEEE*, Albert Chin, and Dim-Lee Kwong, *Senior Member, IEEE*

Abstract—High-performance metal—insulator—metal capacitors using atomic layer-deposited HfO<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub> laminate are fabricated and characterized for RF and mixed-signal applications. The laminate capacitor can offer high capacitance density (12.8 fF/ $\mu$ m²) up to 20 GHz, low leakage current of 4.9  $\times$  10<sup>-8</sup> A/cm² at 2 V and 125 °C, and small linear voltage coefficient of capacitance of 211 ppm/V at 1 MHz, which can easily satisfy RF capacitor requirements for year 2007 according to the International Technology Roadmap for Semiconductors. In addition, effects of constant voltage stress and temperature on leakage current and voltage linearity are comprehensively investigated, and dependences of quadratic voltage coefficient of capacitance ( $\alpha$ ) on frequency and thickness are also demonstrated. Meanwhile, the underlying mechanisms are also discussed.

Index Terms—Atomic layer-deposit (ALD),  $HfO_2$ - $Al_2O_3$  laminate, metal-insulator-metal (MIM) capacitor, radio frequency (RF), reliability.

# I. INTRODUCTION

THE DRAMATIC increase in wired and wireless communications has triggered the demand for metal-insulator-metal (MIM) capacitors, which can offer low parasitic capacitance, low voltage coefficients, and high quality factor for RF applications [1]. With an increase in levels of integration and the scale-down of chip size, future technology generations will require integrated RF MIM capacitors with higher capacitance density in view of lower system cost. High capacitance density can be achieved by utilizing either high dielectric constant (high- $\kappa$ ) materials or very thin insulator layers. However, leakage current and reliability issues limit the aggressive thickness scaling [2]. Therefore, high- $\kappa$  materials are much preferred as a possible solution. In the last two years,

Manuscript received September 18, 2003; revised March 2, 2004. This work was supported in part by Institute of Microelectronics (Singapore) under Grant R-263-000-235-592 and in part by the National University of Singapore under Grant R-263-000-221-112. The review of this paper was arranged by Editor G. Groeseneken.

S.-J. Ding, H. Hu, C. Zhu, S. J. Kim, X. Yu, M.-F. Li, B. J. Cho, and D. S. H. Chan are with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 119260 (e-mail: elezhucx@nus.edu.sg).

M. B. Yu and S. C. Rustagi are with the Institute of Microelectronics, Singapore 117685.

A. Chin is with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 30050, Taiwan, R.O.C.

D.-L. Kwong is with the Department of Electrical and Computer Engineering, University of Texas, Austin, TX 78712 USA.

Digital Object Identifier 10.1109/TED.2004.827367

various high- $\kappa$  dielectrics, such as HfO<sub>2</sub> [3]–[5], AlTaO<sub>x</sub> [6], Tb-doped HfO<sub>2</sub> [3], (HfO<sub>2</sub>)<sub>1-x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>x</sub> [7], Al<sub>2</sub>O<sub>3</sub> [8], [9], AlTiO<sub>x</sub> [9], and Ta<sub>2</sub>O<sub>5</sub> [8], [10], have been explored to replace conventional silicon dioxide and silicon nitride for MIM capacitors. However, the challenge still remains to achieve high capacitance density especially in RF regime, while maintaining minimal leakage current, acceptable voltage coefficients of capacitance (VCCs), and so on under the thermal budget of a back-end process.

An HfO<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub> laminate has been evaluated in metal-insulator-poly-silicon structure for dynamic random access memory (DRAM) application, showing excellent leakage characteristics [11], where capacitance density and leakage current are of great importance. However, in the case of RF MIM capacitors, RF performances and voltage linearity are emphasized in particular. Thus, it is desirable to investigate the characteristics of the HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> laminate for MIM capacitors application. In this paper, we employed alternate 1-nm  $\mathrm{Al_2O_3}$  and 5-nm  $\mathrm{HfO_2}$  as an insulator for MIM capacitor. The 1-nm Al<sub>2</sub>O<sub>3</sub> layers were acted as the contacting layers to the bottom and top electrodes to improve the metal/dielectric interface quality, as suggested by Ishikawa et al. [10]. As a result, high performance MIM capacitors using the atomic layer-deposited (ALD) HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> laminate have been demonstrated successfully, suggesting that it is a very promising candidate for next generation RF and mixed signal IC applications.

# II. EXPERIMENTS

The MIM capacitors were fabricated on  $4-\mu m$  SiO<sub>2</sub> deposited on Si wafer. The sputtered Ta–TaN layers were used as the bottom electrode, where Ta was used to reduce the parasitic resistance of the electrode and TaN served as a barrier layer. After that, the laminate dielectrics with alternate Al<sub>2</sub>O<sub>3</sub> (1 nm) and HfO<sub>2</sub> (5 nm) layers were deposited using ALD technique at 320 °C, and the beginning and end layers were 1-nm Al<sub>2</sub>O<sub>3</sub>, respectively. Al<sub>2</sub>O<sub>3</sub> were deposited using tri-methyl aluminum and water, and HfO<sub>2</sub> were deposited using HfCl<sub>4</sub> and water. Three thicknesses of laminate (13, 31, and 43 nm) were deposited. Then, TaN was reactively sputtered as the top electrode, followed by the forming gas annealing at 420 °C for 30 min to reduce leakage current. Finally, a photolithography step and dry etching were adopted to define the MIM capacitors. In consideration of RF characterization, the coplanar transmission lines were

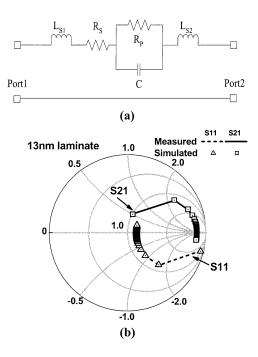

Fig. 1. (a) Equivalent circuit model for capacitor simulation in RF regime. (b) Typical measured and simulated two-port *S*-parameters for the 13-nm laminate MIM capacitor.

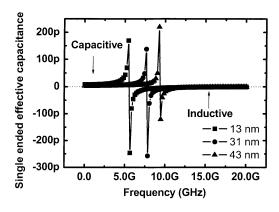

Fig. 2. High-frequency responses of the laminate MIM capacitors with three thicknesses from 50~MHz to 20~GHz.

fabricated, and also served as the top and bottom electrodes; here, Al was used as the contact pads after TaN top electrode formation. The maximum temperature in the device fabrication was 420 °C considering the compatibility with the CMOS back-end of line process.

Capacitances from 10 kHz to 1 MHz were measured using a HP4284A precision LCR meter. For RF characterization, the scattering (S) parameters were measured on-wafer using HP 8510C netpaper analyzer with the GGBs air coplanar probes for ground–signal–ground (GSG) configuration. The measured S-parameters were de-embedded from a dummy device and the high-frequency capacitance plus parasitic parameters were extracted using an equivalent circuit model and IC-CAP software. Leakage currents were measured using a HP4155B semi-conductor parameter analyzer. To study dependence of VCCs on constant voltage stress (CVS), capacitance–voltage (C–V) characteristics were measured with an interruption of stress after

different stress time. The breakdown of the laminate was characterized by monitoring the change of leakage current during CVS.

### III. RESULTS AND DISCUSSIONS

# A. RF Characteristics of the Laminate MIM Capacitors

In order to investigate the capacitance characteristics of the laminate MIM capacitors in RF regime, we first establish the equivalent circuit model for extractions of capacitance and parasitic parameters, as shown in Fig. 1(a). The  $R_p$  and C describe the basic model of high- $\kappa$  laminate MIM capacitors, where  $R_p$  originates from the high- $\kappa$  dielectric loss.  $R_s, L_{s1}$ , and  $L_{s2}$  denote the parasitic resistance and inductances from the coplanar transmission, respectively. Notably, the series resistance is more critical than the parallel one at high frequencies, and becomes a limiting factor for performance of capacitor in RF regime [12]. In addition, the dummy structure is also made for de-embedding purpose during RF measurement [13]. After the S-parameters measurements of both the device under test (DUT) and the dummy device, the following procedures are used to de-embed the parasitic from the bondpads [14], [15]:

$$[S_{\text{DUT/dummy}}] \Rightarrow [Y_{\text{DUT/dummy}}]$$

(1)

$$Y_{\text{capacitor}} = Y_{\text{DUT}} - Y_{\text{dummy}}.$$

(2)

As a result, the measured two-port S-parameters (S11 and S21) after de-embedding shunt elements are obtained. In comparison with the elements shown in Fig. 1(a), the shunt elements (not shown) represent the coupling of the top and bottom electrodes to ground through SiO2 and Si substrate, which can be suppressed by integrating the capacitors far away (or beneath the final metal level) from Si substrate. Therefore, the simulated two-port S-parameters are obtained using the aforementioned equivalent circuit by IC-CAP [16]. The typical two-port S-parameters are illustrated in Fig. 1(b) for the 13-nm laminate MIM capacitor. It can be found that the measured and simulated data points over the entire frequency range from 50 MHz to 20 GHz are in very good agreement, which suggests that the equivalent circuit model is suitable and reliable for the capacitor modeling and parameters extraction. In addition, the transition from capacitive to inductive behavior in Fig. 2 is due to the parasitic inductances which are believed to be associated with the interconnect and extrinsic to the MIM structure. The above phenomenon can be understood from the simplified impedance formula of capacitor  $Z = R + j(\omega L - (1/(\omega C)))$ . At a certain high frequency, the capacitor undergoes the transition from capacitive to inductive behavior. From Fig. 2 it is observed that the resonance frequencies are 5.5, 7.7, and 9.3 GHz for the 13-, 31-, and 43-nm laminate MIM capacitors, respectively. The different resonance points result from the different capacitance values due to different dielectric thicknesses. However, the useful operating frequency range of MIM capacitor can be further extended by means of reducing the series parasitic resistance.

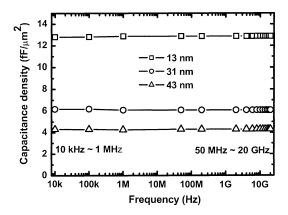

Fig. 3 presents the capacitance densities measured at low frequency (10 kHz-1 MHz) and those extracted in RF regime. It is revealed that all of the laminate MIM capacitors can offer

Fig. 3. Frequency dependences of capacitance densities from 10 kHz to 20 GHz for the 13-, 31-, and 43-nm laminate capacitors.

nearly constant capacitance densities of 4.3, 6.1, and 12.8 fF/ $\mu$ m<sup>2</sup> for 43, 31, and 13-nm laminates from 10 kHz to 20 GHz, respectively. The calculated dielectric constant of the laminate is around 19, which indicates that the incorporation of a small quantity of Al<sub>2</sub>O<sub>3</sub> can still preserve high enough dielectric constant. Compared to other dielectrics such as AlTiO<sub>x</sub> [9], silicon nitride [17], the HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> laminate dielectric exhibits remarkably improved frequency dependence under the thermal budget of back-end of line process, which is of great importance for circuit application as well as the circuit design perspective. Regarding the 13-nm laminate MIM capacitor, the capacitance density of 12.8 fF/ $\mu$ m<sup>2</sup> can fit the density requirement of RF capacitor up to year 2007 according to the International Technology Roadmap for Semiconductors [18].

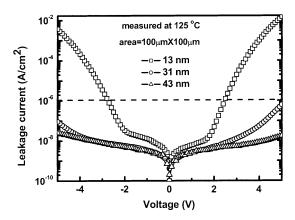

# B. Leakage and Breakdown Characteristics of the Laminate MIM Capacitor

To stringently evaluate leakage characteristics of the laminate MIM capacitors, J-V characteristics are measured at the maximum operating temperature 125 °C. Fig. 4 shows dependence of leakage current density (J) on biasing voltage at 125 °C for MIM capacitors with different thicknesses of laminate. It is noticed from Fig. 4 that the leakage current decreases with the increase of the laminate thickness at the same voltage. Table I compares leakage currents and capacitance densities of other high- $\kappa$  MIM capacitors together with the 13-nm laminate MIM capacitor. It can be found that the 13-nm HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> laminate MIM capacitor can provide much smaller leakage current than those of HfO<sub>2</sub> and Tb-doped HfO<sub>2</sub> MIM capacitors while maintaining the similar capacitance density. Such a small leakage current density for the laminate MIM capacitor is attributed to incorporations of 1-nm Al<sub>2</sub>O<sub>3</sub> layers. It exploits the merits of large band gap of Al<sub>2</sub>O<sub>3</sub> which helps to reduce leakage current and slow oxygen diffusion through Al-O matrix resulting in improved interface properties [19]. Besides, the intermediate amorphous Al<sub>2</sub>O<sub>3</sub> layers inhibit the continuous crystal growth of HfO2, thereby eliminate the grain boundary channels extending from one electrode to the other, and further contribute to the reduced conductivity [20].

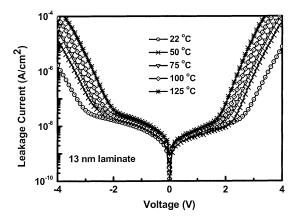

Fig. 5 presents J–V curves for the 13-nm laminate MIM capacitor measured at several different temperatures. It is found

Fig. 4.  $J\!-\!V$  characteristics of the 13-, 31-, and 43-nm laminate capacitors at 125  $^{\circ}\mathrm{C}.$

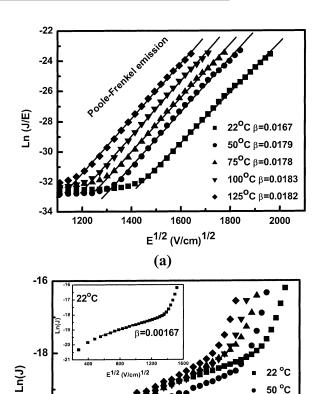

that the leakage current at low voltages exhibits weak temperature dependence in comparison with that at high voltages, i.e., compared to the leakage current at 50 °C, the leakage currents at 125 °C increase by 1.6 and 24.8 times at 1 and 3 V, respectively. Moreover, the J-V characteristics exhibit two distinct regions. One is the low bias region (typically at < 2 V), where the leakage current increases slowly with the applied voltage; the other is the high bias region (>2 V), where the leakage current increases quickly with the applied voltage. The phenomena reflect different current transport mechanisms. It is believed that the Poole-Frenkel (P-F) emission is due to field-enhanced thermal excitation of trapped electrons, so the conduction process at high bias in Fig. 5 is likely dominated by P-F emission. To further verify the possible effect, ln(J/E) versus  $E^{1/2}$  is plotted in Fig. 6(a) at different temperatures, together with extracted slope  $(\beta)$  by linear fitting. According to [21] we can deduce that the refractive index of the laminate is close to 1.8 in the case of 22 °C, which is in good agreement with the reported refractive index (1.6–2.0) of ALD HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> nanolaminate [22], suggesting the dominant P-F emission at high electric field. At the same time, it is also found that the transition to P-F emission shifts from 2.4 to 1.6 MV/cm with increasing the temperature from 22 to 125 °C. However, uncontrollable occurrence of charge trapping (as revealed in Fig. 8) during the I-V measurements probably increases uncertainty in the P-F plotting. To make a clear and final conclusion on the conduction mechanism, the measurement temperature range has to be increased. On the other hand,  $\ln(J)$  versus  $E^{1/2}$  at low voltages is also plotted in Fig. 6(b), where the inset presents Schottky fitting for the measurement temperature of 22 °C. According to the resulting slope, the calculated refractive index is about 9, which is much larger than that of ALD HfO<sub>2</sub>. Thus, it can be considered that the Schottky emission is not a unique conduction mechanism at low bias. It has been reported that trap-assisted-tunneling (TAT) current at low voltage (electric field) shows weak temperature dependence, weaker electric-field-dependence than P-F current, and a very prominent "knee" feature due to a significant change of J-V slope in the case of the transition from TAT to P-F emission [2]. The aforementioned features are in good agreement with J-V characteristics in Fig. 5, indicating that the leakage current at low electric field likely includes the TAT contribution.

| Dielectric                     | ALD HfO <sub>2</sub> -Al <sub>2</sub> O <sub>3</sub> laminate | ALD HfO <sub>2</sub>       | Sputtered Tb-doped HfO <sub>2</sub> |

|--------------------------------|---------------------------------------------------------------|----------------------------|-------------------------------------|

|                                | [this work]                                                   | [4]                        | [3]                                 |

| Capacitance density            | -                                                             |                            | · · ·                               |

| $(fF/\mu m^2)$                 | 12.8                                                          | 13                         | 13.3                                |

| Leakage current                | 6×10 <sup>-9</sup> @ 1V                                       | 1.55×10 <sup>-6</sup> @ 1V | _                                   |

| at 125 °C (A/cm <sup>2</sup> ) | 4.9×10 <sup>-8</sup> @ 2V                                     | _                          | 2×10 <sup>-7</sup> @ 2V             |

$TABLE\ \ I$  Comparison of the  $HfO_2-Al_2O_3$  Laminate MIM Capacitor With  $HfO_2$  and Tb-Doped  $HfO_2$  MIM Capacitors

Fig. 5. J-V characteristic of the 13-nm laminate MIM capacitor as a function of temperature.

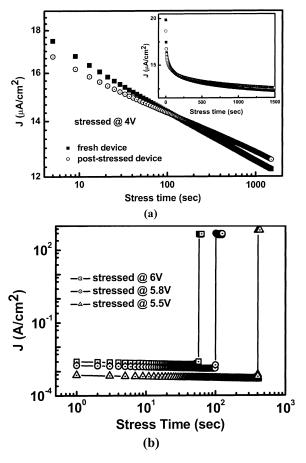

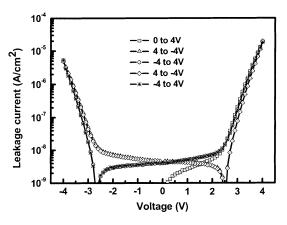

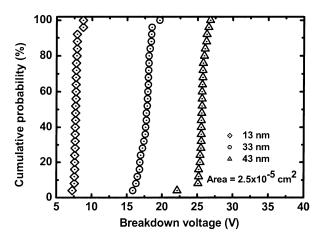

Fig. 7(a) shows the evolution of leakage current during CVS for 13-nm laminate. It can be found that the leakage current reduces swiftly at the beginning of stress, followed by a gentle decrease with stress time. In respect of the fresh capacitor, the leakage current decreases by about 38% with increasing stress time to 1500 s under 4 V stress. Subsequently, the stress voltage is removed and the device is kept at zero bias for 10 h, and then the leakage current is remeasured under the same voltage stress. As shown in Fig. 7(a), the leakage current at the starting point is remarkably recovered after 10 hours interruption, i.e., to 94% of the original. This indicates that charge trapping and detrapping occur in the laminate MIM capacitor [23]. On the other hand, the quick decrease of leakage current at initial times under CVS suggests the creation and charging of traps occur mostly near the interface of dielectric/electrode [24]. Fig. 7(b) shows the characteristics of leakage current versus stress time for the 13-nm laminate under different CVS. When the stress time surpasses a critical point, the leakage current exhibits a sudden rise, which is a typical characteristic of hard breakdown. To measure the current dependence on biasing voltage and time, the applied voltage varies from the negative voltage to the positive voltage and back, and the corresponding current is shown in Fig. 8. It is noticed that J-V curves exhibit a good symmetry for positive and negative polarities, which is ascribed to a symmetrical structure of the current MIM capacitor different from MOS capacitor with SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate stacks [25]. Furthermore, from Fig. 8 cusps are observed where the current crosses zero, and indicate the size of the hysteresis loop and transient conductivity [26]. It can be found that the laminate MIM capacitor exhibits the similar hysteresis under both biasing directions due to charge trapping. In addition, the cumulative probability plots of breakdown voltage are indicated in Fig. 9 for different thick-

(b) Fig. 6. (a) Plot of  $\ln(J/E)$  versus  $E^{1/2}$  as a function of temperature together with the linear fitting for the 13-nm laminate MIM capacitor. (b) The plot of  $\ln(J)$  versus  $E^{1/2}$  as a function of temperature, where the inset graph is Schottky emission fitting for 22 °C.

800

$E^{1/2} (V/cm)^{1/2}$

400

75 °C

100 °C

125 °C

1600

1200

ness laminate MIM capacitors. In the case of 50% probability of failure, the breakdown voltages corresponding to the 13-, 31-, and 43-nm laminate MIM capacitors are respectively equal to 7.6, 17.8, and 25.6 V, i.e., the corresponding breakdown field is about 6 MV/cm.

# C. Effect of Frequency, Temperature, and Constant Voltage Stress on VCCs

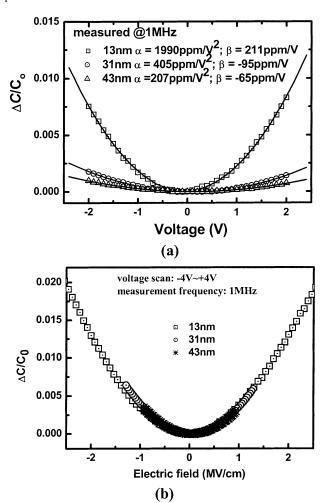

VCCs are very important parameters for MIM capacitor applications, and can be obtained by fitting the measured data with a second order polynomial equation of  $C(V) = C_0(\alpha V^2 + \beta V + 1)$ , where  $C_0$  is the zero-biased capacitance,

Fig. 7. (a) Characteristics of leakage current versus stress time under 4-V stress for the 13-nm laminate MIM capacitor, and the inset shows the corresponding curves in linear scale (solid square and open round represent the as-stressed and restressed after an interruption of 10 h, respectively). (b) Typical breakdown characteristics of the 13-nm laminate under different CVS.

Fig. 8. J-V measurements showing the hysteresis loop of the 13-nm laminate MIM capacitor.

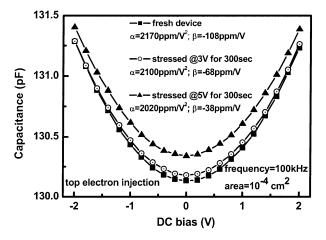

$\alpha$  and  $\beta$  represent the quadratic and linear voltage coefficients of capacitance, respectively. Fig. 10(a) shows bias-dependent normalized capacitance ( $\Delta C/C_0$ ) fitted by the abovementioned equation and the resulting VCCs as well. Obviously,  $\alpha$  decreases with increasing the laminate thickness. In the case of the 13-nm laminate MIM capacitor,  $\beta$  is equal to 211 ppm/V at 1 MHz, which can easily meet RF capacitor requirement (1000 ppm/V) [18]. Moreover, electric field (E) dependence of  $\Delta C/C_0$  is also presented in Fig. 10(b), showing a very

Fig. 9. Cumulative probability dependent on breakdown voltage of the MIM capacitors with different thicknesses of laminate.

Fig. 10. (a) Voltage-dependent normalized capacitance  $(\Delta C/C_0)$  at 1 MHz for the 13-, 31-, and 43-nm laminate capacitors, fitted by a second-order polynomial equation. (b) Corresponding plot of  $\Delta C/C_0$  versus electric field (E).

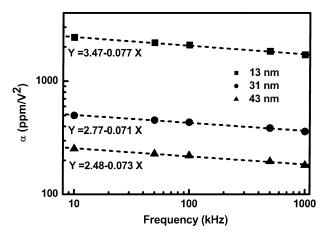

similar dependence of  $\Delta C/C_0$  on E regardless of the dielectric thickness. In addition, the effect of the applied frequency on  $\alpha$  is also demonstrated in Fig. 11. It can be noticed that logarithmic  $\alpha(\log \alpha)$  decreases linearly with a logarithmic increase in frequency, while maintaining a similar slope in spite of the laminate thickness, i.e.,  $\alpha$  decreases by about

Fig. 11. Frequency dependence of  $\alpha$  for the 13-, 31-, and 43-nm laminate capacitors, showing a linear fitting in log–log scale.

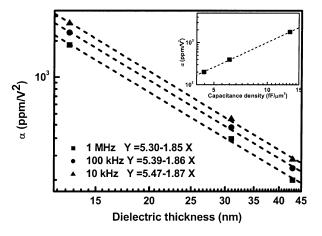

30% when the applied frequency increases from 10 kHz to 1 MHz. Furthermore, we plot  $\alpha$  versus thickness as well as capacitance density, as shown in Fig. 12. It is found that  $\alpha$  linearly decreases with increasing the thickness of laminate in log-log scale, exhibiting a similar slope despite of the applied frequency. Similarly, the linear dependence of  $\alpha$  on capacitance density is also observed in a log-log scale (see the inset in Fig. 12). However,  $\beta$  does not exhibit the aforementioned frequency and thickness dependences. The foregoing results reveal that  $\alpha$  is correlated with the applied frequency and dielectric thickness. The frequency dependence of  $\alpha$  can be explained as the change of relaxation time with different carrier mobility in insulator, and the thickness dependence of  $\alpha$  is an intrinsic property due to electric field polarization [27].

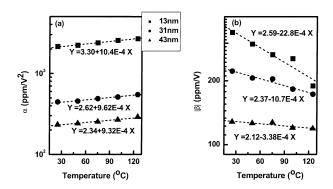

For temperature coefficient of capacitance (TCC), we have measured C-V characteristics of the laminate MIM capacitors at 100 kHz as a function of temperature. The TCCs for all the three laminates are observed to be smaller than 200 ppm/°C, and the TCC for the 13-nm laminate capacitor is 182 ppm/°C. Meanwhile, temperature dependences of VCCs are also analyzed, as presented in Fig. 13. It is indicated that the  $\log \alpha$  increases linearly as a function of the temperature, and the slope becomes smaller with increasing the laminate thickness. This suggests that the thinner laminate has stronger temperature dependence. On the other hand, logarithmic absolute value of  $\beta(\log |\beta|)$  reduces with the temperature. Similarly, the variation of  $\beta$  with temperature is more remarkable for the thinner laminate.

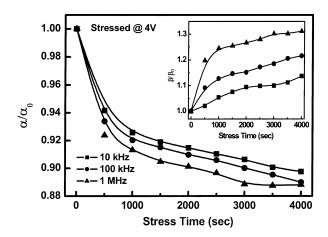

In the case of 13-nm laminate of our interest, the VCCs dependence on CVS have been investigated. Fig. 14 shows stress time dependences of normalized VCCs ( $\alpha/\alpha_0$  and  $\beta/\beta_0$ ) under CVS with different frequencies. Noticeably,  $\alpha$  decreases and  $\beta$  increases with stress time at each frequency. Additionally, it is noted that the variations of  $\alpha$  and  $\beta$  at the beginning of stress are large, subsequently following small changes. The trend accords with the evolution of leakage current under CVS in the inset of Fig. 7(a) due to charge trapping. Fig. 15 illustrates the effects of different CVS on capacitance and VCCs. It can be observed that the capacitance of the MIM capacitor increases with CVS, and the magnitudes of VCCs decrease. The increase in capacitance is correlated with the generation of new dipoles in the dielectric due to charge trapping, hereby modulating the dielectric constant [28], and higher CVS can cause more charge trap-

Fig. 12. Laminate thickness dependence of  $\alpha$  at 10 kHz, 100 kHz, and 1 MHz with a linear fitting in log–log scale, where the inset shows a linear dependence of  $\alpha$  on capacitance density in log–log scale.

Fig. 13. Temperature dependences of  $\alpha$  and  $\beta$  at 100 kHz for the 13-, 31-, and 43-nm laminate capacitors

Fig. 14. Dependence of  $\alpha/\alpha_0$  on stress time at 10 kHz, 100 kHz, and 1 MHz. The inset shows stress time dependence of  $\beta/\beta_0$  at the same frequencies.  $\alpha_0$  and  $\beta_0$  represent the data before voltage stress,  $\alpha$  and  $\beta$  denote the data after different time stress.

ping at deep traps [24], accordingly leading to larger increase in capacitance, as shown in Fig. 15. Additionally, the carrier mobility becomes smaller under CVS, leading to a higher relaxation time and smaller VCCs [27]. Table II summarizes variations of VCCs and leakage current under different measuring conditions. In comparison with the prestressed device, the resulting VCCs and leakage current reduce after CVS for 1500 s.

Fig. 15. *C–V* characteristics of the 13-nm laminate MIM capacitor under different CVS, and the corresponding VCCs are also presented.

# TABLE II VCCs and Leakage Current Under Different Conditions for the 13-nm Laminate MIM Capacitor (Measurement Temperature: 22 $^{\circ}$ C; Frequency: 100 kHz; CVS: 4 V; area: $1 \times 10^{-4}$ cm<sup>2</sup>)

| Parameters                    | α (ppm/V²) | β (ppm/V) | Leakage current (A/cm²) |

|-------------------------------|------------|-----------|-------------------------|

| Pre-stress                    | 2212       | -285      | 2.06×10 <sup>-5</sup>   |

| After 1500 sec stress         | 2132       | -338      | 1.40×10 <sup>-5</sup>   |

| After 1hr stress interruption | 2194       | -306      | 1.96×10 <sup>-5</sup>   |

After interruption of CVS for 1 h, the resultant VCCs are recovered observably together with the leakage current, which should be attributed to charge detrapping after electrical stress removing. In a word, the consistent variations of VCCs and leakage current further reveal that the VCCs are likely related to charge trapping and detrapping in the dielectric under and after electrical stress.

# IV. CONCLUSION

MIM capacitors using ALD HfO<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub> laminate are fabricated and characterized for RF and mixed-signal applications. The laminate capacitor can offer high capacitance density (12.8 fF/ $\mu$ m<sup>2</sup>) up to 20 GHz, low leakage current (4.9 × 10<sup>-8</sup> A/cm<sup>2</sup> at 2 V and 125 °C), breakdown electric field of ~6 MV/cm, small linear VCC (211 ppm/V) and TCC of 182 ppm/ °C. In addition, the HfO<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub> laminate exhibits seemingly P–F emission at high electric field, and the leakage current at low electric field likely results from both Schottky emission and TAT contributions. Besides,  $\alpha$  exhibits a linear decrease with frequency and dielectric thickness in log–log scale, respectively. The decreases of VCCs and leakage current under CVS and then the increases after CVS should be ascribed to charge trapping and detrapping.

# REFERENCES

- A. Kar-Roy, C. Hu, M. Racanelli, C. A. Compton, P. Kempf, G. Jolly, P. N. Sherman, J. Zheng, Z. Zhang, and A. Yin, "High density metal insulator metal capacitors using PECVD nitride for mixed signal and RF circuits," in *Proc. IITC*, 1999, pp. 245–247.

- [2] T. Remmel, R. Ramprasad, and J. Walls, "Leakage behavior and reliability assessment of tantalum oxide dielectric MIM capacitors," in *Proc. Int. Rel. Phys. Symp.*, 2003, pp. 277–281.

- [3] S. J. Kim, B. J. Cho, M. F. Li, C. Zhu, A. Chin, and D.-L. Kwong, "HfO<sub>2</sub> and lanthanide-doped HfO<sub>2</sub> MIM capacitors for RF/mixed IC applications," in *Symp. VLSI Tech. Dig.*, 2003, pp. 77–78.

- [4] X. Yu, C. Zhu, H. Hu, A. Chin, M. F. Li, B. J. Cho, D.-L. Kwong, P. D. Foo, and M. B. Yu, "A high-density MIM capacitor (13 fF/μm²) using ALD HfO₂ dielectrics," *IEEE Electron Device Lett.*, vol. 24, pp. 63–65, Feb. 2003.

- [5] H. Hu, C. Zhu, Y. F. Lu, M. F. Li, B. J. Cho, and W. K. Choi, "A high-performance MIM capacitor using HfO<sub>2</sub> dielectrics," *IEEE Electron Device Lett.*, vol. 23, pp. 514–516, Sept. 2002.

- [6] M. Y. Yang, C. H. Huang, A. Chin, C. Zhu, M. F. Li, and D.-L. Kwong, "High-density MIM capacitors using AlTaO<sub>x</sub> dielectrics," *IEEE Electron Device Lett.*, vol. 24, pp. 306–308, May 2003.

- [7] H. Hu, C. Zhu, X. Yu, A. Chin, M. F. Li, B. J. Cho, D.-L. Kwong, P. D. Foo, M. B. Yu, X. Liu, and J. Winkler, "MIM capacitors using atomic-layer-deposited high-κ (HfO<sub>2</sub>)<sub>1-x</sub>(Al<sub>2</sub>O<sub>3</sub>)<sub>x</sub> dielectrics," *IEEE Electron Device Lett.*, vol. 24, pp. 60–62, Feb. 2003.

- [8] Y. L. Tu, H. L. Lin, L. L. Chao, D. Wu, C. S. Tsai, C. Wang, C. F. Huang, C. H. Lin, and J. Sun, "Characterization and comparison of high-k metalinsulator-metal (MiM) capacitors in 0.13 μm Cu BEOL for mixed-mode and RF applications," in Symp. VLSI Tech. Dig., 2003, pp. 79–80.

- [9] S. B. Chen, C. H. Lai, A. Chin, J. C. Hsieh, and J. Liu, "High-density MIM capacitors using Al<sub>2</sub>O<sub>3</sub> and AlTiO<sub>x</sub> dielectrics," *IEEE Electron Device Lett.*, vol. 23, pp. 185–187, Apr. 2002.

- [10] T. Ishikawa, D. Kodama, Y. Matsui, M. Hiratani, T. Furusawa, and D. Hisamoto, "High-capacitance Cu/Ta<sub>2</sub>O<sub>5</sub>/Cu MIM structure for SoC applications featuring a single-mask add-on process," in *IEDM Tech. Dig.*, 2002, pp. 940–942.

- [11] J.-H. Lee, J. P. Kim, Y.-S. Kim, H.-S. Jung, N.-I. Lee, H.-K. Kang, K.-P. Suh, M.-M. Jeong, K.-T. Hyun, H.-S. Baik, Y. S. Chung, X. Liu, S. Ramanathan, T. Seidel, J. Winkler, A. Londergan, H. Y. Kim, J. M. Ha, and N. K. Lee, "Mass producion worthy HfO<sub>2</sub>–Al<sub>2</sub>O<sub>3</sub> laminate capacitor technology using Hf liquid precursor for sub-100-nm DRAMs," in *IEDM Tech. Dig.*, 2002, pp. 221–224.

- [12] H. Ng, K. W. Chew, J. X. Li, T. T. Tjoa, L. N. Goh, and S. F. Chu, "Characterization and comparison of two metal-insulator-metal capacitor schemes in 0.13 μm copper dual damascene metallization process for mixed-mode and RF applications," in *IEDM Tech. Dig.*, 2002, pp. 241–244.

- [13] S. B. Chen, J. H. Chou, A. Chin, J. C. Hsieh, and J. Liu, "RF MIM capacitors using high-k Al<sub>2</sub>O<sub>3</sub> and AlTiO<sub>x</sub> dielectrics," in *Proc. IEEE MTT-S Int. Microwave Symp.*, vol. 1, 2002, pp. 201–204.

- [14] D. M. Pozar, Microwave Engineering. New York: Wiley, 1998.

- [15] C. H. Huang, M. Y. Yang, A. Chin, C. X. Zhu, M. F. Li, and D. L. Kwong, "High density RF MIM capacitors using high- $\kappa$  AlTaO $_x$  dielectrics," in *Proc. IEEE MTT-S Int. Microwave Symp.*, June 2003.

- [16] IC-CAP Manual, 1998. Hewlett Packard.

- [17] J. A. Babcock, S. E. Balster, A. Pinto, C. Dirnecker, P. Steinmann, R. Jumpertz, and B. El-Kareh, "Analog characteristics of metal-insulator-metal capacitors using PECVD nitride dielectrics," *IEEE Electron Device Lett.*, vol. 22, pp. 230–232, May 2001.

- [18] The International Technology Roadmap for Semiconductors, 2001. Semiconductor Industry Association.

- [19] G. D. Wilk, R. M. Wallace, and J. M. Anthony, "High-k gate dielectrics: Current status and materials properties considerations," *J. Appl. Phys.*, vol. 89, no. 10, pp. 5243–5275, 2001.

- [20] K. Kukli, J. Ihanus, M. Ritala, and M. Leskela, "Tailoring the dielectric properties of HfO<sub>2</sub>-Ta<sub>2</sub>O<sub>5</sub> nanolaminates," *Appl. Phys. Lett.*, vol. 68, no. 26, pp. 3737–3739, 1996.

- [21] S. M. Sze, Physics of Semiconductor Devices, 2nd ed. New York: Wiley, p. 402.

- [22] C. D'Emic, E. Gusev, M. Copel, J. Newbury, H. Hovel, P. Kozlowski, J. Bruley, and R. Murphy, "Growth and characterization of Al<sub>2</sub>O<sub>3</sub>:HfO<sub>2</sub> nanolaminate films deposited by atomic layer deposition (ALD)," in *Proc. Electrochemical Society Meeting*, Paris, France, Apr. 27–May 2 2003.

- [23] S. Yamamichi, A. Yamamichi, D. Park, T. J. King, and C. Hu, "Impact of time dependent dielectric breakdown and stress-induced leakage current on the reliability of high dielectric constant (Ba, Sr)TiO<sub>3</sub> thin-film capacitors for Gbit-scale DRAMs," *IEEE Trans. Electron Devices*, vol. 46, pp. 342–347, Mar. 1999.

- [24] R. S. Scott and D. J. Dumin, "The transient nature of excess low-level leakage currents in thin oxides," *J. Electrochem. Soc.*, vol. 142, pp. 586–590, 1995.

- [25] A. Kerber, E. Cartier, R. Degraeve, L. Pantisano, Ph. Roussel, and G. Groeseneken, "Strong correlation between dielectric reliability and charge trapping in SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate stacks with TiN electrodes," in Symp. VLSI Tech. Dig., 2002, pp. 76–77.

- [26] K. Chu, J. P. Chang, M. L. Steigerwald, R. M. Fleming, R. L. Opila, D. V. Lang, R. B. Van Dover, and C. D. W. Jones, "Material and electrical characterization of carbon-doped Ta<sub>2</sub>O<sub>5</sub> films for embedded dynamic random access memory applications," *J. Appl. Phys.*, vol. 91, pp. 308–315, 2002.

- [27] C. Zhu, H. Hu, X. Yu, S. J. Kim, A. Chin, M. F. Li, B. J. Cho, and D. L. Kwong, "Voltage and temperature dependence of capacitance of high-k HfO<sub>2</sub> MIM capacitors: A unified understanding and prediction," in *IEDM Tech. Dig.*, 2003, pp. 879–882.

- [28] C. Besset, S. Bruyère, S. Blonkowski, S. Crémer, and E. Vincent, "MIM capacitance variation under electrical stress," *Microelectron. Reliab.*, vol. 43, pp. 1237–1240, 2003.

Shi-Jin Ding received the B.S. degree from Fuyang Normal College, Anhui Province, China, in 1994, the M.S. degree from Hangzhou University, Zhejiang Province, China, in 1998, and the Ph.D. degree from Fudan University, Shanghai, China, in 2001.

He was a Research Fellow of Alexander Humboldt Foundation of Germany with the Faculty of Engineering, Kiel University (Christian-Albrechts-Universität zu Kiel), Kiel, Germany, from October 2001 to November 2002. In February 2003, he joined Silicon Nano Device Laboratory, Department of Elec-

trical and Computer Engineering, National University of Singapore, as a Research Fellow. His research interests include high dielectric constant (high- $\kappa$ ) MIM capacitors for RF/analog IC applications, low- $\kappa$  materials for microelectronics, copper metallization of low- $\kappa$  films, polymer-metal nanocomposites, and thermodynamics of CVD diamond as well as inorganic luminescence materials. He has authored and coauthored more than 50 technical papers.

Dr. Ding was awarded the Humboldt Research Fellowship of Germany in 2001.

Hang Hu, photograph and biography not available at the time of publication.

Chunxiang Zhu (S'97–M'02) received the B.S. and M.S. degrees in electrical engineering from Xidian University, Xi'an, China, in 1992 and 1995, and the Ph.D. degree in electrical engineering from Hong Kong University of Science and Technology, Kowloon, in 2001.

He joined the Department of Electrical and Computer Engineering, National University of Singapore, as an Assistant Professor in 2001. His current research interests are frontend CMOS devices and processes including high- $\kappa$  gate dielectrics and high

mobility Ge MOSFETs, passive devices, and nonvolatile memory.

Sun Jung Kim received the degree in electronic engineering from Kyung-pook National University, Taegu, Korea, in 1996 and the M.Eng. degree in electrical and computer engineering from National University of Singapore in 2001. He is currently pursuing the Ph.D. degree in the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore.

His research interests include ALD of high- $\kappa$  dielectrics, high- $\kappa$  MIM capacitors, and silicon RF/mixed-signal passive devices.

**Xiongfei Yu** received the B.S degree in materials science and engineering from Zhejiang University, Hangzhou, China, in 1996. He is currently pursuing the Ph.D degree at the National University of Singapore.

He was an Assistant Engineer at the Institute of Microelectronics, Chinese Academy of Sciences, from 1996 to 2000, working on deep sub-micrometer Si CMOS process technology. In 2000, he joined the Microelectronics Fabrication Facility, Hong Kong University of Science and Technology, as a Visiting

Scholar. He is currently with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore. His research interests include the high- $\kappa$  materials for CMOS gate dielectrics and metal–insulator–metal capacitor applications.

**Ming-Fu Li** (M'91–SM'99) received the degree from the Department of Physics, Fudan University, Shanghai, in 1960.

After graduation, he joined the University of Science and Technology of China (USTC) as a Teaching assistant and then lecturer. In 1978, he joined the Graduate School faculty, Chinese Academy of Sciences, Beijing, and became a professor in 1986. He has also served as Adjunct Professor at the Institute of Semiconductors, Chinese Academy of Sciences, Fudan University, and USTC, Hefei.

He was a Visiting Scholar at Case Western Reserve University, Cleveland, OH, in 1979, and at the University of Illinois at Urbana-Champain from 1979 to 1981 and was a Visiting Scientist at the University of California at Berkeley and Lawrence Berkeley National Laboratories, Berkeley, CA, from 1986 to 1987 and 1990 to 1991, respectively. He joined the Department of Electrical Engineering, National University of Singapore in 1991 and became a Professor in 1996. His current research interests are in the areas of CMOS device technology, reliability, quantum modeling, and analog IC design. He has published over 200 research papers and two books, including *Modern Semiconductor Ouantum Physics* (New York: World Scientific, 1994).

Dr. Li has served on several international program committees and advisory committees in international semiconductor conferences in China, Japan, Canada, Germany, and Singapore.

**Byung Jin Cho** (M'97–SM'01) received the B.S. degree in electrical engineering from Korea University, Seoul, in 1985 and the M.S. and Ph.D. degrees in electrical engineering from Korea Advanced Institute of Science and Technology (KAIST), Daejong, in 1987 and 1991, respectively.

From 1991 to 1993, he was with Interuniversity MicroElectronic Center (IMEC), Leuven, Belgium, as a Research Fellow, where he worked on advanced silicon processing. In 1993, he joined the Memory R&D Division of Hyundai Electronics Ind. Com-

pany, Korea, as a Section Manager, where he led a research team for the process development for 256M and 1G DRAM and Flash EEPROM. Since 1997, he has been with the Department of Electrical and Computer Engineering, National University of Singapore (NUS), where he is currently an Associate Professor. He is the Supervisor of the Silicon Nano Device Laboratory (SNDL) at NUS. His research interests are front-end CMOS processes including high- $\kappa$  gate dielectrics and metal gate, isolation and junction technologies, nanoscale CMOS device structures, advanced NVM devices, and device reliability. He has published over 100 technical papers and holds more than 30 patents.

**Daniel S. H. Chan** (SM'96) received the B.Sc. and M.Sc. degrees in electrical engineering from the Institute of Science and Technology, University of Manchester, Manchester, U.K., in 1970 and 1971, respectively, and the Ph.D. degree from Salford University, Salford, U.K., in 1975.

He joined the Hong Kong Polytechnic as a Lecturer in 1977 and, in 1980, joined the Electrical and Computer Engineering Department, National University of Singapore, where he is now a Professor. His present research interests are in charge

beam-induced currents, cathodoluminescence, photon emission microscopy, and semiconductor device reliability. He has published 80 journal papers and holds six patents.

Dr. Chan's paper on the Single Contact Optical Beam Induced Current technique won the Best Paper award in 2000 from the International Symposium of Test and Failure Analysis.

M. B. Yu, photograph and biography not available at the time of publication.

**Subhash C. Rustagi** (SM'00) received the M.Sc. and Ph.D. degrees in physics from Kurukshetra University, Kurukshetra, Haryana, India, in 1975 and 1981, respectively.

He joined the Centre for Applied Research in Electronics, Indian Institute of Technology Delhi, India, in 1982. He moved to the Integrated Circuits and System Laboratory, Institute of Microelectronics, Singapore, as Member of Technical Staff in April, 1999, where he is in charge of the device modeling group. He has published about 30 papers

in refereed journals and conferences. His research interests include device modeling and characterization, RF model and test chip development, RF ESD, and characterization of the substrate noise.

**Albert Chin** received the Ph.D. degree from the Department of Electrical Engineering, University of Michigan, Ann Arbor, in 1998.

He was with AT&T-Bell Labs from 1989 to 1990, and General Electric's Electronic Lab from 1990 to 1992. He is a Professor at the National Chiao Tung University, Hsinchu, Taiwan, R.O.C., and was Deputy Director of the Nanometer Center, University System of Taiwan, and Visiting Professor at the Silicon Nano Device Lab, National University of Singapore. He has published more than 200 technical

papers and presentations. His research interests include Si VLSI, III-Vs, and RF devices. He is the pioneer in the Ge-On-Insulator (GOI), high- $\kappa$  Al2O3 and La2O3 gate dielectrics, fully NiSi-NiGe gates, resonant cavity photodetector, and high-mobility strain-compensated HEMT, etc. His high- $\kappa$  gate dielectrics and GOI works have been cited by high-quality IEDM and VLSI symposia papers from IC fabs, universities, and in the *Electrical Engineering Times*. He also developed very high resistivity Si using an ion implantation process, generated traps, and much-improved RF performance close to GaAs has been realized up to 100 GHz. The developed metal-gate/high- $\kappa$ /GOI MOSFETs and semi-insulating Si processes are followed by several research labs and currently in pilot runs at IC fabs. He is currently working on GOI, high- $\kappa$ , metal gate, RF Si, nano-CMOS, and memory technologies.

Dr. Chin has given invited talks at the IEDM and other conferences in the US, Japan, Korea (i.e., Samsung Electronics), etc.

**Dim-Lee Kwong** (A'84–SM'90) received the B.S. degree in physics and the M.S. degree in nuclear engineering from the National Tsing Hua University, Taipei, Taiwan, R.O.C., in 1977 and 1979, respectively. He received the Ph.D. degree in electrical engineering from Rice University, Houston, TX.

He was an Assistant Professor with the Electrical Engineering Department, University of Notre Dame, Notre Dame, IN, from 1982 to 1985. He was a Visiting Scientist with the IBM General Technology Division, Essex Junction, VT, during the summer of 1985, working on 4-Mb DRAM technology. He joined the Microelectronic Research Center and the Department of Electrical and Computer Engineering, The University of Texas, Austin, in 1985 as an Assistant Professor. He was promoted to Associate Professor in 1985 and to Full Professor in 1990. He is the author of more than 470 referred archival publications and has been awarded more than 20 U.S. patents. His current areas of research interests include rapid thermal CVD technology for the growth and deposition of semiconductor materials compatible with ULSI processes, advanced dielectrics for logic, analog, and memory devices, metal gate electrode, shallow junctions, and high-κ dielectrics. Thirty-five students received the Ph.D. degree under his supervision.

Dr. Kwong has received numerous awards, including the IBM Faculty Development Award in 1984 and the Engineering Foundation Teaching Award from the University of Teaxs, Austin, in 1994, and holds the Earl N. and Margaret Brasfield Endowed Fellowship.