# Fully Silicided NiSi Gate on La<sub>2</sub>O<sub>3</sub> MOSFETs

C. Y. Lin, M. W. Ma, Albert Chin, *Senior Member, IEEE*, Y. C. Yeo, *Member, IEEE*, Chunxiang Zhu, *Member, IEEE*, M. F. Li, *Senior Member, IEEE*, and Dim-Lee Kwong

Abstract—We have fabricated the fully silicided NiSi on La $_2$ O $_3$  for n- and p-MOSFETs. For 900 °C fully silicided CoSi $_2$  on La $_2$ O $_3$  gate dielectric with 1.5 nm EOT, the gate dielectric has large leakage current by possible excess Co diffusion at high silicidation temperature. In sharp contrast, very low gate leakage current density of  $2\times10^{-4}$  A/cm $^2$  at 1 V is measured for 400 °C formed fully silicided NiSi and comparable with Al gate. The extracted work function of NiSi was 4.42 eV, and the corresponding threshold voltages are 0.12 and -0.70 V for respective n- and p-MOSFETs. Electron and hole mobilities of 156 and 44 cm $^2$ /V-s are obtained for respective n- and p-MOSFETs, which are comparable with the HfO $_2$  MOSFETs without using H $_2$  annealing.

Index Terms—CoSi<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, MOSFET, NiSi.

#### I. INTRODUCTION

IGH current drive capability is the main technology challenge for continuously scaling down the VLSI technology with improved MOSFET performance. To increase the drive current of MOSFET, the thickness of both inversion channel and poly gate depletion region should be decreased. Therefore, high- $\kappa$  gate dielectrics [1]–[9] and metal gates [7]–[12] are required to increase the total gate capacitor density under inversion. Among various metal gates, the fully silicided poly-Si gate using  $CoSi_2$  has low resistance ( $\sim 2 \Omega/\square$ ) and the potential of process compatibility with current VLSI technology [12]. In this study, we have compared the fully silicided CoSi<sub>2</sub> and NiSi gate on La<sub>2</sub>O<sub>3</sub> MOSFETs. The NiSi has been applied to VLSI process for its low resistivity, low process temperature and immunity from narrow line effect. Both NiSi/La<sub>2</sub>O<sub>3</sub> n- and p-MOSFETs using low temperature NiSi show much lower gate leakage current than CoSi<sub>2</sub>/La<sub>2</sub>O<sub>3</sub> MOSFETs and good device characteristics are evidenced from the comparable electron and hole mobilities with HfO<sub>2</sub> MOSFETs without H<sub>2</sub> annealing [2], [3].

### II. EXPERIMENTAL

Standard 4-in p- and n-type Si wafers were used for n- and p-MOSFETs. The source and drain region were implanted with

Manuscript received January 24, 2003; revised March 13, 2003. This work was supported in part by the National Science Council of Taiwan, R.O.C., under Grant 90-2215-E-009-052. The review of this letter was arranged by Editor B. Yu.

C. Y. Lin, M. W. Ma, and A. Chin are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: achin@cc.nctu.edu.tw).

Y. C. Yeo, C. Zhu, and M. F. Li are with the Silicon Nano Device Lab, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 119260.

D.-L. Kwong is with the Department of Electrical and Computer Engineering. The University of Texas, Austin, TX 78752 USA.

Digital Object Identifier 10.1109/LED.2003.812569

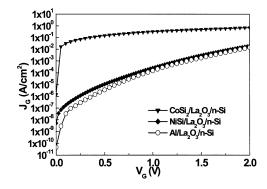

Fig. 1.  $J_G$ – $V_G$  characteristics of NiSi/La<sub>2</sub>O<sub>3</sub>, Al/La<sub>2</sub>O<sub>3</sub> and CoSi<sub>2</sub>/La<sub>2</sub>O<sub>3</sub> capacitors measured under accumulation. The large leakage current density in CoSi<sub>2</sub>/La<sub>2</sub>O<sub>3</sub> capacitor can not be used for device application. The device area is 100  $\mu$ m× 100  $\mu$ m.

50 KeV As<sup>+</sup> or 10 KeV B<sup>+</sup> for respective n- and p-MOSFETs, and followed by  $900 \sim 950\,^{\circ}\text{C}$  and  $30 \sim 60\,\text{s}$  RTA. To form the La<sub>2</sub>O<sub>3</sub> gate dielectric, the La film was first deposited thermally on HF-vapor passivated Si under high vacuum and followed by oxidation and annealing under low pressure condition at 425 °C [5]. An interface oxide of  $0.3 \sim 0.6$  nm was found that may be due to lack of previous *in-situ* native oxide removal process [4], [5]. A formed La<sub>2</sub>O<sub>3</sub> thickness of  $\sim 5.5$  nm is measured by Ellipsometer. The fully silicided gate electrode was formed by depositing 15 nm amorphous Si on La<sub>2</sub>O<sub>3</sub>, depositing 15 nm Ni or 10 nm Co, and followed by silicidation using RTA. For CoSi<sub>2</sub>, conventional two step silicidation is used to achieve the required low resistivity: the first step silicidation was performed at 500 °C for 30 s and the second phase transformation was executed at 900 °C [13]-[15]. For NiSi, only one-step RTA at 400 °C for 30 s was performed because low resistivity silicide can be obtained at such low temperature [16]. For comparison, Al metal gate devices were also fabricated. The fabricated silicide/La<sub>2</sub>O<sub>3</sub> MOSFETs were further characterized by capacitance-voltage (C-V) and current-voltage (I-V) measurements.

### III. RESULTS AND DISCUSSION

Fig. 1 shows the comparison of gate dielectric leakage current of NiSi/La $_2$ O $_3$ , Al/La $_2$ O $_3$  and CoSi $_2$ /La $_2$ O $_3$  capacitors. The large leakage current in CoSi $_2$ /La $_2$ O $_3$  capacitor may be due to the excess metal diffusion [17] at high silicidation temperature (900 °C) through La $_2$ O $_3$  dielectric

$$L_D = (Dt)^{1/2} = D_0^{1/2} e^{-E_a/2kT} t^{1/2}.$$

(1)

Here, the  $L_D$ , D, t, and T are the diffusion length, coefficient, time, and temperature, respectively. The diffusion length depends on the annealing temperature exponentially, but such high temperature is required to achieve the low resistance of  $CoSi_2$

LIN et al.: FULLY SILICIDED NISI GATE

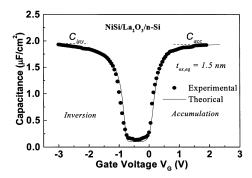

Fig. 2. C-V characteristics of NiSi/La<sub>2</sub>O<sub>3</sub> transistor. The gate length is  $10~\mu$ m and width is  $100~\mu$ m. The measurement frequency is 100~kHz.

[13]–[15]. In addition, excess Co may be released during second 900 °C RTA for phase transformation from CoSi into CoSi<sub>2</sub> once underneath Si is fully consumed:

$$CoSi \rightarrow \frac{1}{2}CoSi_2 + \frac{1}{2}Co. \tag{2}$$

The difference between this result and previous report [12] may be due to the low metal diffusion through nitrided oxide [18]. In contrast, very low leakage current density of  $2\times 10^{-4}~\rm A/cm^2$  at 1 V is measured in fully silicided NiSi and comparable with Al gate. Besides, a low NiSi sheet resistance  $(\rho_{\rm NiSi}/d_{\rm NiSi})$  of  $8~\Omega/\Box$  is measured at 400 °C silicidation even at a thin NiSi thickness  $d_{\rm NiSi}$  of  $\sim~30~\rm nm$ . Therefore, the low silicidation temperature for low resistivity NiSi is important to preserve the good gate dielectric integrity and prevent excess metal diffusion through gate dielectric.

We have further characterized the NiSi/La<sub>2</sub>O<sub>3</sub> capacitor. Fig. 2 shows high frequency C-V characteristics of NiSi/La<sub>2</sub>O<sub>3</sub> transistor. The identical value of inversion and accumulation capacitance indicates that the NiSi gate is fully silicided without poly-Si depletion. A relatively high interface trap density of  $\sim 10^{12} \text{ eV}^{-1}/\text{cm}^2$  is measured without using previous H<sub>2</sub> annealing [5]. An equivalent-oxide-thickness (EOT) of 1.5 nm is obtained from the measured capacitance, which has  $\sim 4$ orders of magnitude lower leakage current than SiO<sub>2</sub> at the same EOT. Because excess Ni or Co must be used to avoid poly-Si depletion, the low silicidation temperature is the key step to maintain low Ni diffusion through gate capacitor and cause large leakage current. The extracted work function from the flat band voltage  $(V_{\rm FB})$  as a function of different La<sub>2</sub>O<sub>3</sub> thickness is 4.42 eV, which is lower than the work function of Ni ( $\sim 5$  eV [10]). This result also suggests low metal diffusion into NiSi/La<sub>2</sub>O<sub>3</sub> interface [17], [18] during RTA to control the work function, which is consistent with the low leakage current shown in Fig. 1.

Fig. 3(a) and (b) show the  $I_D$ - $V_D$  and  $I_D$ - $V_G$  characteristics of fully silicided NiSi/La<sub>2</sub>O<sub>3</sub> MOSFETs, respectively. Reasonable subthreshold swing of 102 and 124 mV/dec are measured for respective n- and p-MOSFETs. The threshold voltage ( $V_{\rm TH}$ ) was further extracted from  $I_D$ - $V_G$  plot at a  $|V_D|$  of 50 mV, and  $V_{\rm TH}$  of 0.12 and -0.70 V are obtained for n- and p-MOSFETs, respectively. The large  $V_{\rm TH}$  for p-MOSFET may be due to the relatively small NiSi work function, because a larger work function ( $\sim$  5.6 eV [7]) is required for high- $\kappa$  gate dielectric than conventional SiO<sub>2</sub>.

Fig. 3. (a)  $I_D-V_D$  and (b)  $I_D-V_G$  characteristics of La<sub>2</sub>O<sub>3</sub> (EOT=1.5 nm) n- and p-MOSFETs using fully silicided NiSi gate electrode. The gate length is 10  $\mu$ m and width is 100  $\mu$ m.

-0.5 0.0 0.5

Gate Voltage (V)

1.0

1.5 2.0

10<sup>-11</sup>

10<sup>-12</sup> -2.0 -1.5 -1.0

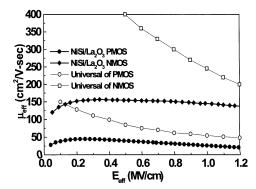

Fig. 4. Extracted electron and hole mobilities of  $\text{La}_2\text{O}_3$  n- and p-MOSFETs using fully silicided NiSi gate electrode.

Fig. 4 shows the extracted electron and hole motilities versus gate electric field. The electron and hole mobilities for respective n-and p-MOSFETs are 156 and 44 cm $^2$ /V-s. These mobility values are comparable with the Si<sub>3</sub>N<sub>4</sub> [9] or HfO<sub>2</sub> MOSFETs without using H<sub>2</sub> annealing [2], [3], which indicates the successful integration of fully silicided NiSi gate on La<sub>2</sub>O<sub>3</sub> MOSFETs. Further increasing mobility may be expected using H<sub>2</sub> or D<sub>2</sub> annealing to passivate the high- $\kappa$  dielectric defects [2], [3], [5], [19].

## IV. CONCLUSION

Good device performance of fully silicided NiSi/La<sub>2</sub>O<sub>3</sub> n-and p-MOSFETs is demonstrated with a low NiSi resistance of 8  $\Omega/\Box$  formed at 400 °C. In contrast, the same gate dielectric has large leakage using fully silicided CoSi<sub>2</sub> formed at a

high temperature of 900 °C. The low resistance at low temperature silicidation is the main advantage for fully silicided NiSi to avoid excess Ni diffusion through gate dielectric.

#### REFERENCES

- [1] C. H. Lee, J. J. Lee, W. P. Bai, S. H. Bae, J. H. Sim, X. Lei, R. D. Clark, Y. Harada, M. Niwa, and D. L. Kwong, "Self-aligned ultra thin HfO<sub>2</sub> CMOS transistors with high quality CVD TaN gate electrode," in *Symp. VLSI Tech. Dig.*, 2002, pp. 82–83.

- [2] K. Onishi, C. S. Kang, R. Choi, H. J. Cho, S. Gopalan, R. Nieh, E. Dharmarajan, and J. C. Lee, "Reliability characteristics, including NBTI, of polysilicon gate HfO<sub>2</sub> MOSFET's," in *IEDM Tech. Dig.*, 2001, pp. 659–662.

- [3] K. Onishi, C. S. Kang, R. Choi, H. J. Cho, S. Gopalan, R. Nieh, R. Krishnan, and J. C. Lee, "Effect of high temperature forming gas anneal on HfO<sub>2</sub> MOSFET performance," in *Symp. VLSI Tech. Dig.*, 2002, pp. 22–23.

- [4] A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, "Device and reliability of high-k Al<sub>2</sub>O<sub>3</sub> gate dielectric with good mobility and low D<sub>it</sub>," in Symp. VLSI Tech. Dig., 1999, pp. 135–136.

- [5] A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, and W. J. Chen, "High quality La<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics with equivalent oxide thickness 5–10 Å," in *Symp. VLSI Tech. Dig.*, 2000, pp. 16–17.

- [6] A. Chin, C. S. Liang, C. Y. Lin, C. C. Wu, and J. Liu, "Strong and efficient light emission in ITO/Al<sub>2</sub>O<sub>3</sub> suprelattice tunnel diode," in *IEDM Tech. Dig.*, 2001, pp. 171–174.

- [7] Y. C. Yeo, P. Ranade, T. J. King, and C. Hu, "Effects of high-k gate dielectric materials on metal and silicon gate workfunctions," *IEEE Elec*tron Device Lett., vol. 23, pp. 342–344, June 2002.

- [8] Y. C. Yeo, P. Ranade, Q. Lu, R. Lin, T. J. King, and C. Hu, "Effects of high K dielectrics on the workfunctions of metal and silicon gates," in Symp. VLSI Tech. Dig., 2001, pp. 49–50.

- [9] Y. C. Yeo, Q. Lu, P. Ranade, H. Takeuchi, K. J. Yang, I. Polishchuk, T. J. King, C. Hu, S. C. Song, H. F. Luan, and D. L. Kwong, "Dual-metal gate CMOS technology with ultrathin silicon nitride gate dielectric," *IEEE Electron Device Lett.*, vol. 22, pp. 227–229, May 2001.

- [10] I. Polishchuk, P. Ranade, T. J. King, and C. Hu, "Dual work function metal gate CMOS transistors by Ni-Ti interdiffusion," *IEEE Electron Device Lett.*, vol. 23, pp. 200–202, Apr. 2002.

- [11] H. Zhong, S. N. Hong, Y. S. Suh, H. Lazar, G. Heuss, and V. Misra, "Properties of Ru-Ta alloys as gate electrodes for NMOS and PMOS silicon devices," in *IEDM Tech. Dig.*, 2001, pp. 467–470.

- [12] B. Tavel, T. Skotnicki, G. Pares, N. Carrière, M. Rivoire, F. Leverd, C. Julien, J. Torres, and R. Pantel, "Totally silicided (CoSi<sub>2</sub>) polysilicon: A novel approach to very low-resistive gate (~ 2 Ω/□) without metal CMP nor etching," in *IEDM Tech. Dig.*, 2001, pp. 815–828.

- [13] Y. H. Wu, W. J. Chen, S. L. Chang, A. Chin, S. Gwo, and C. Tsai, "Improved electrical characteristics of CoSi<sub>2</sub> using HF-vapor pretreatment," *IEEE Electron Device Lett.*, vol. 20, pp. 200–202, May 1999.

- [14] Q. Z. Hong, W. T. Shiau, H. Yang, J. A. Kittl, C. P. Chao, H. L. Tsai, S. Krishnan, I. C. Chen, and R. H. Havemann, "CoSi<sub>2</sub> with low leakage and low sheet resistance at 0.065 μm gate length," in *IEDM Tech. Dig.*, 1997, pp. 107–110.

- [15] J. S. Park, D. K. Sohn, J. U. Bae, C. H. Han, and J. W. Park, "The effect of Co incorporation on electrical characteristics of n<sup>+</sup>/p shallow junction formed by dopant implantation into CoSi<sub>2</sub> and anneal," *IEEE Trans. Electron Devices*, vol. 47, pp. 994–998, May 2000.

- [16] C. Y. Lin, W. J. Chen, C. H. Lai, A. Chin, and J. Liu, "Formation of Ni germano-silicide on single crystalline Si<sub>0.3</sub>Ge<sub>0.7</sub>/Si," *IEEE Electron Device Lett.*, vol. 23, pp. 464–466, Aug. 2002.

- [17] Y. H. Lin, Y. C. Chen, K. T. Chan, F. M. Pan, I. J. Hsieh, and A. Chin, "The strong degradation on 30 Å oxide integrity contaminated by copper," *J. Electrochem. Soc.*, vol. 148, no. 4, pp. F73–F76, 2001.

- [18] Y. H. Lin, F. M. Pan, Y. C. Liao, Y. C. Chen, I. J. Hsieh, and A. Chin, "The Cu contamination effect in oxynitride gate dielectrics," *J. Electrochem.* Soc., vol. 148, no. 4, pp. G627–G629, 2001.

- [19] B. C. Lin, Y. C. Cheng, A. Chin, T. Wang, and C. Tsai, "The deuterium effect on SILC," in 30th Solid State Devices and Materials (SSDM) Tech. Dig., 1998, pp. 110–111.