# A New Process-Variation-Immunity Method for Extracting Capacitance Coupling Coefficients in Flash Memory Cells

Caleb Yu-Sheng Cho, Ming-Jer Chen, Senior Member, IEEE, Jia-Han Lin, and Chiou-Feng Chen

Abstract—Overestimation of capacitance coupling coefficients in flash memory cells is encountered in the subthreshold slope method. By means of a two-parameters subthreshold current model  $I_D = I_o \exp[q(V_{GB} - nV_{SB})/nkT]$ , a mathematical formulation of the subthreshold swing ratio in the subthreshold slope method is constructed to isolate the measurement errors caused by process variations from the errors traditionally caused by bulk capacitance coupling. To minimize the effect of process variations, a new method is developed based on the model. In this method, the control gate voltage shift due to weak body effect is measured in flash memory cells in subthreshold, while the corresponding slope factor n is adequately deduced from threshold voltage versus source-to-substrate bias measurement in dummy devices. The corrected capacitance coupling coefficients show large improvements compared to the design values, and the updated errors are found to be close to that caused solely by bulk capacitance coupling. The method is also fast since only a small source-to-substrate bias of 0.1 V is needed for implementation of weak body effect, and thereby it can be used as an in-line monitor of capacitance coupling coefficients.

*Index Terms*—Body effect, capacitance coupling, flash memory, mismatch, MOSFETs, subthreshold.

# I. INTRODUCTION

■ APACITANCE coupling coefficients are a very important performance parameter in flash memory cells. Particularly, high-speed write/erase operations can be promised provided that capacitance coupling coefficients are well controlled. Thus, precise extraction of capacitance coupling coefficients in a flash memory manufacturing process is essential. To meet fast extraction requirements, the subthreshold slope method dedicated to a pair of test vehicles (i.e., flash memory cells and dummy transistors) was devised [1] and very recently was reported to be the most accurate [2] in terms of a small error of typically 0.03 due to bulk capacitance coupling (see [2, Fig. 3]). On the other hand, current mismatch between identically drawn devices due to process variations can be more prominent if biased in subthreshold [3]-[7]. In other words, the subthreshold slope method should show considerable sensitivities to current mismatch between flash memory cells and dummy transistors, a

Manuscript received March 12, 2002; revised April 22, 2002. This work was supported by the National Science Council of Taiwan, R.O.C., under Contract NSC 89-2215-E-009-114. The review of this letter was arranged by Editor C.-P. Chang.

C. Y.-S. Cho, M.-J. Chen, and J.-H. Lin are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C. C.-F. Chen is with Actrans Systems, Inc., Santa Clara, CA 95054 USA. Publisher Item Identifier S 0741-3106(02)05979-7.

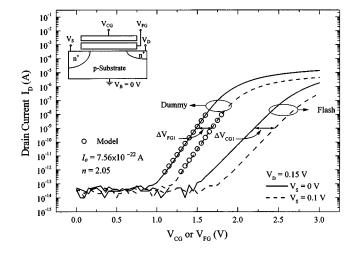

Fig. 1. Drain currents measured as a function of control gate voltage  $(V_{CG})$  in flash memory cell and floating gate voltage  $(V_{FG})$  in dummy transistor.  $V_D=0.15$  V and  $V_S=0$  and 0.1 V. The extracted control gate voltage shift  $(\Delta V_{CG1})$  and floating gate voltage shift  $(\Delta V_{FG1})$  are labeled at specific subthreshold current level of  $10^{-9}$  A. The extracted values of  $I_o$  and n for two subthreshold current–voltage (I-V) of a dummy transistor are shown.

concerned issue not yet clarified fully before [2]. In this work we will figure out that the subthreshold slope method can produce an error as large as 0.13 and an existing subthreshold conduction model can identify process variations, rather than traditionally bulk capacitance coupling, as the primary origin of the errors. To minimize the effect of process variations, a new method is straightforwardly developed.

# II. SUBTHRESHOLD SLOPE METHOD

The NOR-type gate stack flash memory cells with gate width and length of 0.45  $\mu m$  and 0.4  $\mu m$  respectively were used in this work. The dummy transistors were identically drawn flash memory cells but with control gate shorted to underlying floating gate. They were manufactured by a 0.4  $\mu m$  process technology with 100 Å thick tunnel oxide. The substrate was tied to ground (substrate bias  $V_B=0$ ) throughout the work. Fig. 1 shows the measured drain current at drain voltage  $V_D=0.15$  V and source voltage  $V_S=0$  versus control gate voltage  $(V_{CG})$  in flash devices and floating gate voltage  $(V_{FG})$  in dummy devices, respectively. The subthreshold slope method yielded subthreshold swing ratios as depicted in Fig. 2 for four different die positions on wafer, which are unreasonably high as compared with the design values of about 0.6. The error,

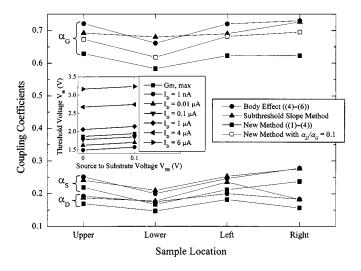

Fig. 2. Gate, drain, and source coupling coefficients extracted from various methods, plotted versus four different locations on the wafer. Involved voltage shifts are:  $\Delta V_{CG1}$  ranges from 0.24 V to 0.25 V;  $\Delta V_{CG2}$  from 0.24 V to 0.25 V;  $\Delta V_{CG0}$  from -0.06 V to -0.05 V;  $\Delta V_{FG1}$  from 0.19 V to 0.20 V; and  $\Delta V_{FG2}$ from 0.19 V to 0.20 V. The inset of the figure shows the extracted  $V_{th}$  versus  $V_{SB}$  for the position "Left" by the maximum transconductance extrapolation and the constant current forcing.

which is defined the subthreshold swing ratio minus 0.6, ranges from 0.08 to 0.13, significantly exceeding that ( $\approx$ 0.03) arisen from bulk capacitance coupling [2]. Thus, there should exist the other origins.

We trace previous overestimation of  $\alpha_G$ s to process variations, as achieved by a subthreshold current model for source-tosubstrate bias  $V_{SB} = 0$  [7]:  $I_D = I_o \exp(qV_{GB}/nkT)$ , where  $I_o$  is the current factor, n is the slope factor, and  $V_{GB} = V_G V_B$ . According to this model, we can have a set of current factor  $I_{of}$  and slope factor  $n_f$  to characterize a flash memory cell while due to process variations another set of  $I_{od}$  and  $n_d$  ought to be used for a "mirrored" or dummy transistor. For the first time, the subthreshold swing ratio in the subthreshold slope method is mathematically formulated:  $S_d/S_f = \alpha_G(n_d/n_f)$ , where  $S_d$  and  $S_f$  represent subthreshold swings in dummy transistors and flash memory cells, respectively. At least two new insights can be drawn here. Firstly, the subthreshold slope method is strikingly immune to  $I_o$  variation. Secondly, the condition of  $n_d > n_f$  can satisfactorily interpret the large errors, as confirmed by the fitted  $n_d$  of around 2.0~2.1 that is partly demonstrated in Fig. 1. Such abnormally high value of  $n_d$ , relative to the typical value of 1.7 in the same MOS process, suggests significant interface state produced when shorting the control gate to floating gate. More evidences of  $n_d > n_f$  are given later.

in dummy transistors can be effectively eliminated via an expression that relates the slope factor n to threshold voltage  $V_{th}$  versus  $V_{SB}$  measurement [7]

III. NEW METHOD Fortunately, the influence of interface state components Further, we limit  $V_{SB}$  to the range between 0 and 0.1 V, i.e., the case of weak body effect. Under this situation, the existing three-parameters subthreshold conduction current-voltage (I-V) model [7] can reduce to a two-parameters version:  $I_D = I_o \exp[q(V_{GB} - nV_{SB})/nkT]$ ; that is,  $I_o$  and n are constants, regardless of  $V_{SB}$  between 0 and 0.1 V as verified in Fig. 1. The same condition also ensures use of a linear version of (1):  $n = 1 + (V_{th2} - V_{th1})/0.1$  V, where  $V_{th1}$ and  $V_{th2}$  are threshold voltages measured at  $V_{SB} = 0$  and 0.1 V, respectively. Two schemes for  $V_{th}$  extraction, namely, the maximum transconductance extrapolation and the constant current forcing, produce almost the same results as shown in the inset of Fig. 2. For example, both methods yield a mean of n = 1.74 for the position "Left" with a very small standard deviation of 0.05, which is in close proximity to 1.7 in the same MOS process.

Then incorporating the two-parameters subthreshold I-V model to a well known relationship  $V_{FG}$  $\alpha_G V_{CG} + \alpha_D V_D + \alpha_S V_S + \alpha_B V_B + Q_{FG}/C_T$  [8], we derive out the following equation for the case of weak body effect in flash memory cells in terms of  $V_S = \Delta V_S$  (=0.1 V)

$$n\Delta V_S = \alpha_G \Delta V_{CG1} + \alpha_S \Delta V_S \tag{2}$$

where  $\Delta V_{CG1}$  is the control gate voltage shift as illustrated in Fig. 1 for  $V_D = 0.15$  V. Similarly the bias configuration of  $V_S = 0.15 \text{ V}$  and  $V_D = \Delta V_D$  (= 0.1 V) expresses another control gate voltage shift ( $\Delta V_{CG2}$ ) as

$$n\Delta V_D = \alpha_G \Delta V_{CG2} + \alpha_D \Delta V_D. \tag{3}$$

Regarding drain coupling coefficient  $\alpha_D$ , we measured a third control gate voltage shift ( $\Delta V_{CG0}$ ) under the same subthreshold current in flash memory cells at  $V_S = 0$  for two  $V_D$ s of 0.15 and 0.35 V. This readily leads to [1]

$$\alpha_G/\alpha_D = 0.2 \,\text{V}/|\Delta V_{CG0}|. \tag{4}$$

The source coupling coefficient  $\alpha_S$  can be assessed in the similar way.

Substituting the measured voltage shifts into above equations, the capacitance coupling coefficients can be solved out as displayed in Fig. 2. Indeed, the corrected  $\alpha_G$ s in Fig. 2 show improved agreements and except for the position "Lower," the errors are substantially reduced down to that due to bulk capacitance coupling only. In Fig. 2, the new method yields  $\alpha_D/\alpha_G$  of around 0.27. If this ratio is intentionally reduced to 0.1 such as to reflect the situation quoted in [2], the resultant error for position "Lower" again can be described by bulk capacitance coupling.

Finally, we present more evidences. Firstly, the I-V in dummy devices measured under  $V_S = \Delta V_S$  (=0.1 V) and  $V_D = 0.15 \text{ V}$  is together plotted in Fig. 1. For the same subthreshold current, the corresponding floating gate voltage shift ( $\Delta V_{FG1}$ ) traditionally could be related to the control gate voltage shift ( $\Delta V_{CG1}$ ) by

$$n = 1 + dV_{th}/dV_{SB}. (1) \Delta V_{FG1} = \alpha_G \Delta V_{CG1} + \alpha_S \Delta V_S. (5)$$

The bias configuration of  $V_S=0.15$  V and  $V_D=\Delta V_D$  (=0.1 V) deals with another floating gate voltage shift ( $\Delta V_{FG2}$ ) in dummy transistors

$$\Delta V_{FG2} = \alpha_G \Delta V_{CG2} + \alpha_D \Delta V_D. \tag{6}$$

The resulting  $\alpha_G$ s as shown in Fig. 2 are found to be comparable with those from the subthreshold slope method, revealing that i) they have the common origins of  $n_d > n_f$  and ii) to meet equal subthreshold current between flash and dummy devices, current mismatch inevitably introduces significant errors in floating gate potential shifts such as  $\Delta V_{FG1}$  in Fig. 1. Secondly, all the  $\alpha$ s of the new method in Fig. 2 sum up to an amount of very close to unity, indicating that the bulk coupling coefficient  $\alpha_B$  is considerably very small, consistent with the error of 0.03 due to bulk capacitance coupling [2].

### IV. CONCLUSION

The subthreshold slope method has practically experienced overestimation of  $\alpha_G$ s in flash memory cells. Process variations as the primary origin of the errors have been judged by means of a two-parameters subthreshold current model. A new method incorporating weak body effect has been developed. The errors

have been substantially improved down to that constituted by bulk capacitance coupling itself.

## REFERENCES

- [1] M. Wong, D. K.-Y. Liu, and S. S.-W. Huang, "Analysis of the sub-threshold slope and the linear transconductance techniques for the extraction of the capacitance coupling coefficients of floating-gate devices," *IEEE Electron Device Lett.*, vol. 13, no. 11, pp. 566–568, Nov. 1992.

- [2] L. Larcher, P. Pavan, L. Albani, and T. Ghilardi, "Bias and W/L dependence of capacitive coupling coefficients in floating gate memory cells," *IEEE Trans. Electron Devices*, vol. 48, pp. 2081–2089, Sept. 2001.

- [3] K. R. Lakshmikumar, R. A. Hadaway, and M. A. Copeland, "Characterization and modeling of mismatch in MOS transistors for precision analog design," *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 1057–1066, Dec. 1986.

- [4] M. J. M. Pelgrom, A. C. J. Duinmaiger, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. SC-24, pp. 1433–1440, Oct. 1989.

- [5] F. Forti and M. E. Wright, "Measurement of MOS current mismatch in the weak inversion region," *IEEE J. Solid-State Circuits*, vol. SC-29, pp. 138–142, Feb. 1994.

- [6] M. J. Chen, J. S. Ho, and T. H. Huang, "Dependence of current match on back-gate bias in weakly inverted MOS transistors and its modeling," *IEEE J. Solid-State Circuits*, vol. 31, pp. 259–262, Feb. 1996.

- [7] M. J. Chen and J. S. Ho, "A three-parameters-only MOSFET subthreshold current CAD model considering back-gate bias and process variation," *IEEE Trans. Computer-Aided Design*, vol. 16, pp. 343–352, Apr. 1997.

- [8] A. Kolodny, S. T. K. Nieh, B. Eitan, and J. Shappir, "Analysis and modeling of floating-gate EEPROM cells," *IEEE Trans. Electron Devices*, vol. ED-33, pp. 835–844, June 1986.