# Characteristics of $Pb(Zr_{0.53}Ti_{0.47})O_3$ on Metal and $Al_2O_3/Si$ Substrates

C. L. Sun, a S. Y. Chen, a,z M. Y. Yang, and Albert Chin

<sup>a</sup>Department of Materials Science and Engineering and <sup>b</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan

We have fabricated Pb(Zr $_{0.53}$ Ti $_{0.47}$ )O $_3$  on Pt and Pb(Zr $_{0.53}$ Ti $_{0.47}$ )O $_3$  on 4 nm Al $_2$ O $_3$ /Si substrates. Although Pb(Zr $_{0.53}$ Ti $_{0.47}$ )O $_3$  on Pt has a larger dielectric constant and grain size than those on Al $_2$ O $_3$ /Si, the Pb(Zr $_{0.53}$ Ti $_{0.47}$ )O $_3$  thin films on both substrates show good capacitance-voltage characteristics and the same threshold voltage shift of  $\sim$ 3.6 V. Moreover, the leakage current density of Pb(Zr $_{0.53}$ Ti $_{0.47}$ )O $_3$  on Al $_2$ O $_3$ /Si at -10 V is nearly three orders of magnitude lower than that of Pb(Zr $_{0.53}$ Ti $_{0.47}$ )O $_3$  on Pt. The comparable memory characteristics and the lower leakage current of Pb(Zr $_{0.53}$ Ti $_{0.47}$ )O $_3$  on Al $_2$ O $_3$ /Si are important for continuous scaling down the ferroelectric memory.

© 2001 The Electrochemical Society. [DOI: 10.1149/1.1409398] All rights reserved.

Manuscript submitted January 22, 2001; revised manuscript received July 11, 2001. Available electronically October 8, 2001.

Ferroelectric random access memory (FRAM) using hysteresis characteristics of ferroelectric materials has the advantages of higher speed and lower power consumption than Flash memory and electrically erasable-programmable read-only memory (EEPROM). Currently, the cell structure of FRAM is one-transistor and one capacitor (1T1C), and the ferroelectric thin films are deposited on metal to form a metal/ferroelectric/metal (MFM) capacitor structure.<sup>2-8</sup> On the other hand, one transistor (1T) ferroelectric metal oxide semiconductor field effect transistor (FeMOSFET) type memory is very attractive because it has not only the same small 1T cell structure as Flash memory but also the merits of FRAM mentioned above. Furthermore, the leakage current in a capacitor of 1T1C cell may limit further shrinkage because the thinner ferroelectric dielectric, smaller area, and hence the higher capacitance/area the general scaling trends for memory. Therefore, 1T FeMOSFET is a highly desirable device for the next generation memory. However, little progress has been achieved in 1T FeMOSFET memory because ferroelectric materials must be integrated as a gate dielectric to form the metal/ferroelectric/Si (MFS), but the strong interface reaction between most ferroelectric materials and Si degrades the device characteristics. 9 In this paper, we have integrated  $Pb(Zr_{0.53}Ti_{0.47})O_3$  (PZT) on Si using  $Al_2O_3^{-10,11}$  as both interface reaction barrier between PZT and Si and gate dielectric for MOSFET. We have compared PZT on Al<sub>2</sub>O<sub>3</sub>/Si with PZT on metal and the nearly three orders magnitude of lower leakage current is another advantage of the MFS structure using PZT on Al<sub>2</sub>O<sub>3</sub>/Si.

### **Experimental**

Four inch, p-type Si(100) wafers were used in this study with a typical resistivity of 10  $\Omega$  cm. For the MFM structure, 150 nm Pt was first deposited on 20 nm Ti/200 nm SiO<sub>2</sub>/Si by E-beam evaporation, which was used as the bottom electrode. For the fabrication of MFS structure, 4 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric was formed on Si following our previously reported procedure. 10,111 The typical dielectric constant and bandgap of Al<sub>2</sub>O<sub>3</sub> are 9.5 and 8.8 eV, respectively. Then PZT ferroelectric thin films were deposited on both Pt/Ti/SiO<sub>2</sub>/Si and Al<sub>2</sub>O<sub>3</sub>/Si by chemical solution deposition method using multiple spin coating at 4000 rpm for 30 s. For the chemical solution synthesis, lead acetate trihydrate, zirconium isopropoxide, and titanium isopropoxide were used as precursors and dissolved in the solvents composed of acetic acid and methanol in sequence. 12 The advantages of chemical solution deposition used in this study are the simplicity and the accuracy of composition control. The Zr/Ti ratio of PZT was chosen to be 53/47, that is, near the morphotropic phase boundary. After each coating the wet films were pyrolyzed at 450°C for several minutes and the multiple-layer films were

annealed at 700°C for 1 h. Au was used as the upper electrode for both capacitor structures with area of  $5 \times 10^{-4}$  cm², and Al the bottom electrode was used for MFS capacitor at the bake side of the Si substrates. We used X-ray diffraction (XRD) to determine the phase and the crystallinity of PZT. The surface morphology and the thickness of PZT were observed by atomic force microscopy (AFM) and secondary electron microscopy (SEM), respectively. Capacitance-voltage (C-V) and current density-voltage (*J-V*) characteristics were measured to check the electric properties of ferroelectric PZT.

### **Results and Discussion**

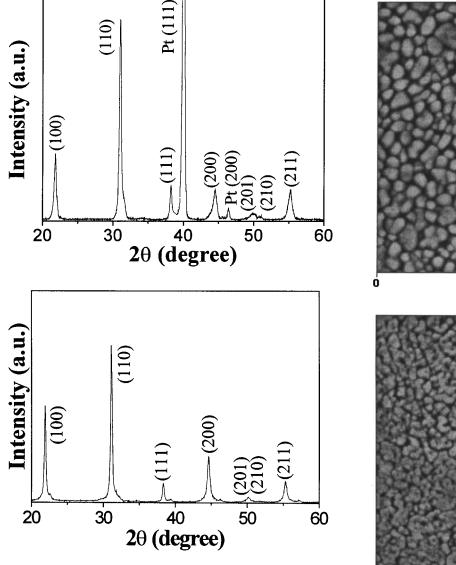

Figures 1a and b show the XRD patterns of PZT films deposited on Pt and 4 nm Al<sub>2</sub>O<sub>3</sub>/Si, respectively. The thickness of each PZT film is determined from the cross-sectional SEM images, to be 250 nm. As shown in Fig. 1a, the structure of PZT on Pt/Ti/SiO<sub>2</sub>/Si is polycrystalline without a preferred orientation which is the typical XRD spectra for PZT on Pt electrode. The high Pt peak intensity in Fig. 1a suggests that Pt has a polycrystalline structure, and this is quite different from the amorphous Al<sub>2</sub>O<sub>3</sub> structure on Si. As shown in Fig. 1b, the structure of PZT on Al<sub>2</sub>O<sub>3</sub> is also polycrystalline, and the PZT film has the stable ferroelectric perovskite phase rather than the nonferroelectric pyrochlore phase. The full width at halfmaximum (fwhm) for the main peaks of PZT on Pt and Al<sub>2</sub>O<sub>3</sub> are 0.30 and 0.35°, and the relative peak intensity is 1.2 times higher for PZT on Pt than PZT on Al<sub>2</sub>O<sub>3</sub>. Thus, although the Al<sub>2</sub>O<sub>3</sub> gate dielectric is only 4 nm, high quality ferroelectic PZT is still successfully produced in this process.

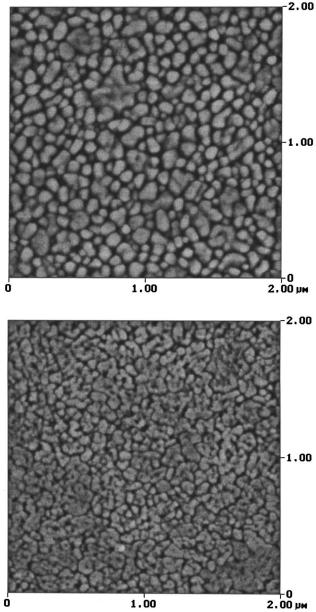

We have used AFM to study the microstructures of deposited PZT. As shown in Fig. 2a, the PZT film deposited on Pt has a grain size of 100 nm that is larger than the grain size of 65 nm for PZT deposited on  $Al_2O_3/Si$  shown in Fig. 2b. The reason for polycrystalline PZT on Pt with larger grain size than on  $Al_2O_3$  is because polycrystalline PZT may be more easily nucleated on polycrystalline Pt than on amorphous  $Al_2O_3$ . The roughness of PZT on Pt is 4.48 nm that is also larger than 1.96 nm of PZT on  $Al_2O_3/Si$ . The larger rms roughness of PZT on Pt is due to the larger polycrystalline grains of PZT formed on polycrystalline Pt instead of amorphous  $Al_2O_3$ .

C-V characteristics at 1 MHz were further measured to study the electrical properties of PZT on Pt and  $Al_2O_3$  buffered Si. Figure 3a shows C-V characteristics of PZT films on Pt and the C-V curves with a typical butterfly pattern because of the ferroelectric nature of PZT.  $^{13,14}$  Although the C-V curves are slightly asymmetric, a large peak voltage difference of 3.59 V is obtained after  $\pm 10$  V applied bias that is due to the ion shift by the electric field. This large memory window is important for memory device design rather than symmetric concern. Figure 3b shows C-V characteristics of PZT

z E-mail: sychen@cc.nctu.edu.tw

Figure 1. XRD patterns of 250 nm PZT on (a, top) Pt/Ti/SiO $_2$ /Si and (b, bottom) 4 nm Al $_2$ O $_3$ /Si.

films on  $Al_2O_3/Si$ . The hysteresis in C-V curves is due to the ferroelectric properties of PZT, which is negligible in  $Al_2O_3$  gate dielectric.  $^{10,11}$  The small capacitance value at positive gate bias shown in Fig. 3b is due to the small series capacitance in the Si depletion region. However, there is no such effect on the MFM structure shown in Fig. 3a because of the negligible depletion width of the metal. Besides the voltage drop in  $Al_2O_3$  gate dielectric, the threshold voltage shift ( $\Delta V_T$ ) measured in PZT on  $Al_2O_3/Si$  is 3.6 V that is almost the same as that in MFM case shown in Fig. 3a. The higher threshold voltage shift is important because it will give a large memory window. Because the threshold voltage shift is directly related to the electric field in PZT ( $E_{PZT}$ ), we have therefore solved the  $E_{PZT}$  of the stacked gate PZT/ $Al_2O_3$  as

$$E_{\rm PZT} = V_{\rm g} / \left( d_{\rm PZT} + \frac{\varepsilon_{\rm PZT}}{\varepsilon_{\rm Al_2O_3}} d_{\rm Al_2O_3} \right)$$

[1]

where  $\varepsilon$  is the dielectric constant and d the thickness of thin films. This equation is from the electric field continuity in PZT and  $Al_2O_3$  by the relation

Figure 2. AFM images of 250 nm PZT on (a, top) Pt/Ti/SiO $_2$ /Si and (b, bottom) 4 nm Al $_2$ O $_3$ /Si.

$$E_{\text{Al}_2\text{O}_3} = E_{\text{PZT}} \frac{\varepsilon_{\text{PZT}}}{\varepsilon_{\text{Al}_2\text{O}_3}}$$

[2]

According to Eq. 1, a smaller dielectric constant or a thinner thickness of PZT will increase  $E_{\rm PZT}$  in our stacked gate structure and hence increase the memory window. The large memory window for PZT on Al<sub>2</sub>O<sub>3</sub>/Si is due to the relative by smaller dielectric constant of 121 obtained from C-V, which is lower than that of 515 for PZT on Pt. The large dielectric constant in the MFM capacitance may be due to the larger grain size of ferroelectric films shown in Fig. 2a. We have also studied the thickness-dependent memory effect. Figure 3c shows a thicker 420 nm PZT on Al<sub>2</sub>O<sub>3</sub>/Si stacked gate dielectric. A small memory window of only 2 V is obtained for the same  $\pm 10$  V applied voltages, and the small gate capacitance of 60 pF is also not desirable for MOSFET application.

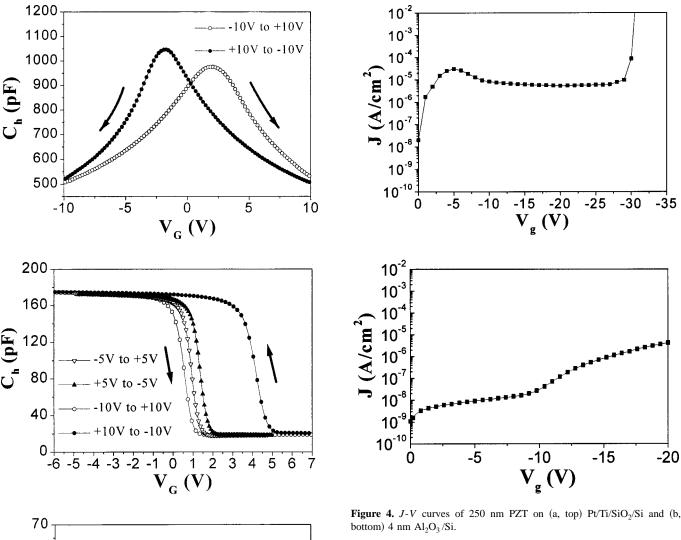

We have also investigated the capacitor leakage current because it is one of the important properties of capacitors. Figure 4a and b

60 50 40 0V to  $\pm 10V$ 20 10V to -10V 10 -5 -4 -3 -2 -1 0 1 2 V<sub>G</sub> (V) 3 5

Figure 3. C-V curves of (a, top) 250 nm PZT on Pt/Ti/SiO<sub>2</sub>/Si, (b, center) 250 nm PZT on 4 nm Al<sub>2</sub>O<sub>3</sub>/Si, and (c, bottom) 420 nm PZT on 4 nm Al<sub>2</sub>O<sub>3</sub>/Si.

show leakage current density-voltage (J-V) characteristics in MFM and MFS structures, respectively. The leakage current density of PZT on Pt is  $1.0 \times 10^{-5}$  A/cm<sup>2</sup> at -10 V that is comparable to the previously reported data. <sup>15</sup> A high breakdown electric field of  $1.2 \times 10^6$  V/cm also suggests the good PZT quality. In contrast, the leakage current density of PZT on Al<sub>2</sub>O<sub>3</sub>/Si is only  $3.1 \times 10^{-8} \,\mathrm{A/cm^2}$  at  $-10 \,\mathrm{V}$  that is nearly three orders of magnitude

lower than that in the MFM structure. Because the dielectric leakage current is the well known Fowler-Nordheim (F-N) tunneling at high field, the smaller leakage current is due to the additional large bandgap Al<sub>2</sub>O<sub>3</sub> gate dielectric<sup>10</sup> because of the exponential dependence of F-N tunneling current on the bandgap

$$J = \frac{q^3 E_{\rm D}^2}{16\pi^2 \hbar \phi_{\rm D} m_{\rm D}^*} \exp \left( -\frac{4(2m_{\rm D}^*)^{0.5} \phi_{\rm D}^{3/2}}{3\hbar q E_{\rm D}} \right)$$

[3]

where  $E_{\rm D}$ ,  $m_{\rm D}^*$ , and  $\phi_{\rm D}$  are the dielectric electric field, effective mass, and barrier height, respectively.

Table I summarizes the comparison of PZT on Pt and Al<sub>2</sub>O<sub>3</sub>/Si. The advantages of PZT on Al<sub>2</sub>O<sub>3</sub>/Si are the smaller leakage current, smoother surface, and comparable memory window with PZT on Pt. The relatively lower dielectric constant is desirable for PZT in a stacked gate dielectric because the larger electric field will drop on PZT which will in turn give a larger memory window. The successful integration PZT on Al<sub>2</sub>O<sub>3</sub> without an interface reaction is important for further 1T FeMOSFET development. 16,17

# Conclusions

We have compared PZT on Pt and 4 nm Al<sub>2</sub>O<sub>3</sub>/Si substrates. Both MFM and MFS capacitors show good capacitance-voltage characteristics and almost the same threshold voltage shift of 3.6 V. The PZT/Al<sub>2</sub>O<sub>3</sub>/Si further has nearly three orders magnitude lower leakage current density at -10 V than that of PZT/Pt. The compa-

| Table I. ( | Characteristics | of | MFM | and | MFS | capacitors. |

|------------|-----------------|----|-----|-----|-----|-------------|

|------------|-----------------|----|-----|-----|-----|-------------|

|     | $\Delta V_{\rm T} ({ m V})$ at $\pm 10~{ m V}$ | $\epsilon$ of PZT | Grain size (nm) of PZT | RMS roughness (nm) of PZT | Leakage current density (A/cm $^2$ ) at $-10~\text{V}$ |

|-----|------------------------------------------------|-------------------|------------------------|---------------------------|--------------------------------------------------------|

| MFM | 3.59                                           | 515               | ~100                   | 4.48                      | $1.0 \pm 10^{-5} \\ 3.1 \pm 10^{-8}$                   |

| MFS | 3.60                                           | 121               | ~65                    | 1.96                      |                                                        |

rable memory characteristics and the lower leakage current of PZT on  $Al_2O_3/Si$  are important for continuous scaling down of the ferroelectric memory.

# Acknowledgments

This work has been support by the National Science Council of Taiwan, contract NSC88-2218-009-011 and NSC89-2215-E-009-100.

National Chiao Tung University assisted in meeting the publication costs of this article.

#### References

- 1. J. F. Scott, Phys. World, 8:2, 46 (1995).

- W. Wu, K. H. Wong, C. L. Mak, C. L. Choy, and Y. Z. Zhang, J. Appl. Phys., 88, 2068 (2000).

- 3. D. Bao, N. Mizutani, X. Yi, and L. Zhang, Appl. Phys. Lett., 77, 1041 (2000).

- 4. N. A. Basit, H. K. Kim, and J. Blachere, Appl. Phys. Lett., 73, 3941 (1998).

- 5. Y. Chen, Y. K. Fang, M. J. Sun, and J.-R. Chen, Appl. Phys. Lett., 69, 812 (1996).

- S. H. Kim, D. J. Kim, J. P. Maria, A. I. Kingon, S. K. Streiffer, J. Kim, O. Auciello, and A. R. Krauss, *Appl. Phys. Lett.*, 76, 496 (2000).

- 7. S. Y. Chen and V. C. Lee, J. Appl. Phys., 87, 3050 (2000).

- 8. S. Y. Chen and V. C. Lee, J. Appl. Phys., 87, 8024 (2000).

- Y. Shichi, S. Tanimoto, T. Goto, K. Kuroiwa, and Y. Tarui, *Jpn. J. Appl. Phys.*, *Part* 1, 33, 5172 (1994).

- A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, and W. J. Chen, in Proceedings of Symposium on VLSI Technology, 16 (2000).

- A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, in *Proceedings of Symposium on VLSI Technology*, 135 (1999).

- J. M. Schwartz, L. F. Francis, and L. D. Schmidt, *Mater. Res. Soc. Symp. Proc.*, 310, 281 (1993).

- K. R. Udayakumar, P. J. Schuele, J. Chen, S. B. Krupanidhi, and L. E. Cross, J. Appl. Phys., 77, 3981 (1995).

- F. K. Chai, J. R. Brews, R. D. Schrimpf, and D. P. Birnie III, J. Appl. Phys., 82, 2505 (1997).

- D. Dimos, R. W. Schwartz, and S. J. Lockwood, J. Am. Ceram. Soc., 77, 3000 (1994).

- A. Chin, M. Y. Yang, C. L. Sun, and S. Y. Chen, IEEE Electron Device Lett., 22 (2001).

- A. Chin, M. Y. Yang, S. B. Chen, C. L. Sun, and S. Y. Chen, in Proceedings of 59th Device Research Conference, Notre Dame, IN, June 2001.