# Stack Gate PZT/Al<sub>2</sub>O<sub>3</sub> One Transistor Ferroelectric Memory

Albert Chin, Senior Member, IEEE, M. Y. Yang, C. L. Sun, and S. Y. Chen

Abstract—We have developed single transistor ferroelectric memory using stack gate PZT/Al $_2$ O $_3$  structure. For the same  $\sim$ 40 Å dielectric thickness, the PZT/Al $_2$ O $_3$ /Si gate dielectric has much better C-V characteristics and larger threshold voltage shift than those of PZT/SiO $_2$ /Si. Besides, the ferroelectric MOSFET also shows a large output current difference between programmed on state and erased off state. The <100 ns erase time is much faster than that of Flash memory where the switching time is limited by erase time.

Index Terms—Al<sub>2</sub>O<sub>3</sub>, ferroelectric, memory, PZT.

### I. INTRODUCTION

ERROELECTRIC material devices have been discovered for over three decades to be for over three decades to be good candidates for memory [1], and currently 4 MB one-transistor and one-capacitor (1T1C) structure has been developed [2]. In comparison with Flash memory or DRAM, the 1T1C ferroelectric RAM has much faster access time than Flash memory and much longer retention time than DRAM [2]. However, it is desirable to further develop 1T ferroelectric MOSFET (FeMOSFET) structure for memory application because the 1T structure has simpler process steps and smaller size than 1T1C cell. Unfortunately, achieving good interface between ferroelectric dielectric and Si is difficult because most ferroelectric films will easily react with Si to form a nonferroelectric interfacial layer even at temperatures as low as 500 °C [3], [4]. Furthermore, the diffusion of Pb from ferroelectric Pb(Zr,Ti)O<sub>3</sub> (PZT) or Li from LiNbO<sub>3</sub> into Si may also be expected to degrade the device integrity and cause process integration problem, because metal ion contamination is an important concern in VLSI [5]. In this letter, we have developed 1T FeMOSFET memory using Al<sub>2</sub>O<sub>3</sub> gate dielectric [6], [7] as a buffer layer between PZT and Si. In comparison with other buffer layers used for 1T ferroelectric memory [8]–[10], high k Al<sub>2</sub>O<sub>3</sub> has not only good gate dielectric integrity but also excellent diffusion barrier property. The stack gate PZT/Al<sub>2</sub>O<sub>3</sub> FeMOSFET memory also has the advantage of structure compatible with high k Al<sub>2</sub>O<sub>3</sub> MOSFET logic used for sub-100 nm VLSI generation [11].

Manuscript received February 15, 2001; revised April 4, 2001. This work was supported by the National Science Council of Taiwan, R.O.C., under Contract NSC 89-2215-E-009-099. The review of this letter was arranged by Editor S. Kawamura.

A. Chin and M. Y. Yang are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: achin@cc.nctu.edu.tw).

C. L. Sun and S. Y. Chen are with the Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. Publisher Item Identifier S 0741-3106(01)05414-3.

# II. EXPERIMENTAL

P-type 4-in (100) Si wafers were used in this study. After device isolation and source/drain definition, the 22 Å Al layer is deposited by evaporation where HF-vapor passivation and in-situ desorption [6], [7], [12] are used to suppress the native oxide formation before Al deposition. The deposited Al is first oxidized at a temperature of 400 °C for 1 h by oxygen to a thickness of 38 Å followed by an 800 °C annealing for 30 min in nitrogen ambient. Then the 2500 Å PZT layer was spin-coated on Al<sub>2</sub>O<sub>3</sub> gate dielectric by the sol-gel method [13], dried at 90 °C for 30 sec, and finally annealed at 700 °C. Al electrodes were formed by thermal evaporation for source, drain and gate, and the channel length and width were 4  $\mu$ m and 100  $\mu$ m, respectively. The reason why using Al metal gate on PZT is because Al is widely used for VLSI process, even though Pt, Ir, and their oxide compounds have higher work-function and probably lower leakage current than Al. For comparison, FeMOS capacitor using 40 Å thermal SiO<sub>2</sub> as buffer layer was also fabricated. The device performance was characterized by C-V and I-Vmeasurements.

### III. RESULTS AND DISCUSSION

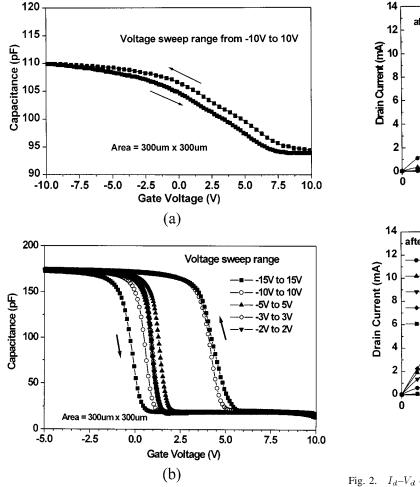

Fig. 1(a) and (b) show the 1 MHz C-V characteristics of FeMOS capacitor with stack gate PZT/SiO2/Si and PZT/Al<sub>2</sub>O<sub>3</sub>/Si structures, respectively. As shown in Fig. 1(a), the PZT/SiO<sub>2</sub> gate dielectric has only a small threshold voltage shift of 1.3 V, and the distorted C-V curves without proper depletion suggest strong interdiffusion or interface reaction between PZT and Si. In sharp contrast, PZT/Al<sub>2</sub>O<sub>3</sub> gate dielectric shown in Fig. 1(b) has well-behaved C-V characteristics from inversion to depletion regions, which suggests the good barrier property of Al<sub>2</sub>O<sub>3</sub> gate dielectric. Furthermore, larger threshold voltage shift and higher capacitance than those of PZT/SiO<sub>2</sub> are observed that are important for memory application. The threshold voltage change increases from 0.5 to 5 V for applied gate voltage increasing from  $\pm 5$  to  $\pm 15$  V difference, which can be used for multilevel memory. The threshold voltage difference is due to polarization reversal in ferroelectric PZT film after applying different polarity of gate voltage.

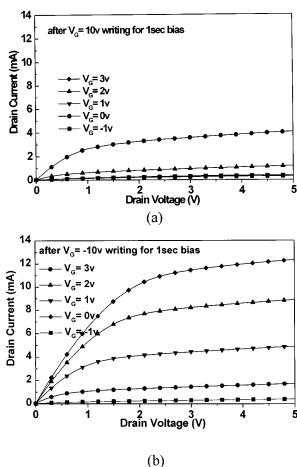

Fig. 2(a) and (b) show the  $I_D$ – $V_D$  characteristics of the 4  $\mu$ m PZT/Al<sub>2</sub>O<sub>3</sub>/Si FeMOSFET after writing on (+10 V) and off (-10 V) gate voltage for 1 s, respectively. Then small gate voltages from -1 to 3 V are applied for the  $I_D$  measurements, and good transistor  $I_D$ – $V_D$  characteristics are obtained in both cases. The large  $I_D$  difference after writing +10 V and -10 V

Fig. 1. C-V characteristics of (a) PZT/SiO<sub>2</sub>/Si and (b) PZT/Al<sub>2</sub>O<sub>3</sub>/Si capacitors. The capacitor size is  $9\times10^{-4}~\rm cm^2$ .

gate voltage is due to the threshold voltage shift that is consistent with C--V results in Fig. 1(b). This result clearly demonstrates the memory operation of the stack gate PZT/Al<sub>2</sub>O<sub>3</sub>/Si FeMOSFET. The high drive current of 125  $\mu$ A/ $\mu$ m at 4  $\mu$ m gate length is desirable for high speed memory circuit, which is due to the small thickness of Al<sub>2</sub>O<sub>3</sub> and high k property of PZT.

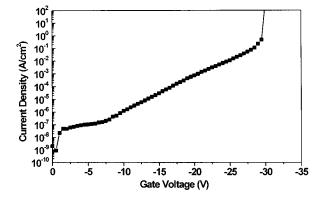

Gate dielectric property is another important factor for practical VLSI application. Fig. 3 shows the gate leakage current density of the PZT/Al<sub>2</sub>O<sub>3</sub>/Si FeMOS. A high breakdown voltage of 30 V is measured that gives a breakdown electric field of 1.2 MV/cm for a 2500 Å dielectric thickness. This large breakdown voltage ensures possible multiple-level memory application shown in Fig. 1(b). Low leakage current densities of  $1\times10^{-6}$  and  $3\times10^{-5}$  A/cm² are measured at applied gate voltage of 10 and 15 V respectively, which allows parallel program/erase like Flash memory to further increase the write speed.

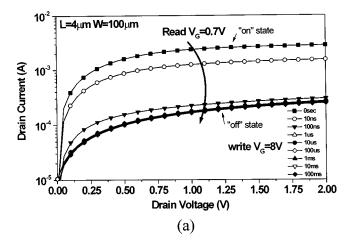

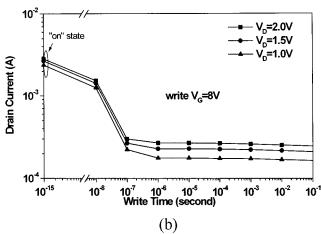

We have further characterized the erase speed of this 1T memory. Fig. 4(a) shows the erase pulse (write 0) width dependent  $I_d$ – $V_d$  characteristics from 10 ns to 100 ms and Fig. 4(b) is the time-dependent drain current evolution. Only less than 100 ns at 8 V is needed to switch from on state to off state,

Fig. 2.  $I_d$ – $V_d$  characteristics of PZT/Al<sub>2</sub>O<sub>3</sub> FeMOSFET after applying (a) 10 V and (b) -10 V for 1 s, respectively. The gate length of the FeMOSFET is 4  $\mu$ m.

Fig. 3. Gate leakage current of PZT/Al $_2$ O $_3$ /Si capacitor with size of 50  $\mu$  m  $\times$  50  $\mu$  m.

which is due to the rapid polarization reversal of ferroelectric PZT film. Furthermore, the obtained one order magnitude of  $I_D$  difference between on and off states can be distinguished by the sense amplifier in a memory circuit. Because the access time of Flash memory is limited by the slow erase time, the much faster erase time of this new device is important for nonvolatile memory application. The other important memory characteristics of fatigue and retention of this 1T memory will be discussed in our future research.

Fig. 4. (a)  $I_d$ – $V_d$  characteristics of FeMOSFET after 8 V voltage applied to gate with different erase pulse width, and (b) time-dependent drain current evolution from (a).

## IV. CONCLUSION

Ferroelectric 1T memory with low gate leakage current density and high erase speed has been successfully demonstrated

using PZT/Al $_2$ O $_3$ /Si structure. The use of high k Al $_2$ O $_3$  in the stack gate 1T memory makes this device compatible with advanced VSLI process.

### REFERENCES

- [1] J. L. Moll and Y. Tarui, "A new solid state resistor," *IEEE Trans. Electron Devices*, vol. ED-10, p. 338, 1963.

- [2] N. W. Jang, Y. J. Song, H. H. Kim, D. J. Jung, B. J. Koo, S. Y. Lee, S. H. Joo, K. M. Lee, and K. Kim, "A novel 1T1C capacitor structure for high density FRAM," in *Symp. VLSI Technology*, 2000, pp. 34–35.

- [3] Y. Shichi, S. Tanimoto, T. Goto, K. Kuroiwa, and Y. Tarui, "Interaction of PbTiO<sub>3</sub> films with Si substrate," *Jpn. J. Appl. Phys.*, vol. 33, no. 9B, pp. 5172–5177, 1994.

- [4] E. Tokumitsu, K. Itani, B. K. Moon, and H. Ishiwara, "Preparation of Pb(Zr,Ti)O<sub>3</sub> films on Si substrates using SrTiO<sub>3</sub> buffer layers," in *Proc. Mater. Res. Soc. Symp.*, vol. 361, 1995, pp. 427–432.

- [5] International Technology Roadmap for Semiconductors, p. 119, 1999.

- [6] A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, "Device and reliability of high-K Al<sub>2</sub>O<sub>3</sub> gate dielectric with good mobility and low D<sub>it</sub>," in *Symp. VLSI Technology*, 1999, pp. 133–134.

- [7] A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, and W. J. Chen, "High quality La<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics with equivalent oxide thickness 5–10Å," in *Symp. VLSI Technology*, 2000, pp. 16–17.

- [8] Y. Lin, B. R. Zhao, H. B. Peng, B. Xu, H. Chen, F. Wu, H. J. Tao, Z. X. Zhao, and J. S. Chen, "Growth and polarization features of highly (100) oriented Pb(Zr<sub>0.53</sub>Ti<sub>0.47</sub>)O<sub>3</sub> films on Si with ultrathin SiO<sub>2</sub> buffer layer," *Appl. Phys. Lett.*, vol. 73, no. 19, pp. 2781–2783, 1998.

- [9] K. H. Kim, "Metal-ferroelectric-semiconductor (MFS) FET's using LiNbO<sub>3</sub>/Si (100) structures for nonvolatile memory application," *IEEE Electron Device Lett.*, vol. 19, pp. 204–206, June 1998.

- [10] E. Tokumitsu, R. Nakamura, and H. Ishiwara, "Nonvolatile memory operations of metal-ferroelectric-insulator-semiconductor (MFIS) FET's using PLZT/STO/Si(100) structures," *IEEE Electron Device Lett.*, vol. 18, pp. 160–162, Apr. 1997.

- [11] D. A. Buchanan, E. P. Gusev, E. Cartier, H. Okorn-Schmidt, K. Rim, M. A. Gribelyuk, A. Mocuta, A. Ajmera, M. Copel, S. Guha, N. Bojarczuk, A. Callegari, C. D'Emic, P. Kozlowski, K. Chan, R. J. Fleming, P. C. Jamison, J. Brown, and R. Arndt, "80 nm poly-silicon gated n-FET's with ultra-thin Al<sub>2</sub>O<sub>3</sub> gate dielectric for ULSI applications," in *IEDM Tech. Dig.*, 2000, pp. 605–608.

- [12] A. Chin, W. J. Chen, T. Chang, R. H. Kao, B. C. Lin, C. Tsai, and J. C.-M. Huang, "Thin oxides with *in-situ* native oxide removal," *IEEE Electron Device Lett.*, vol. 18, pp. 417–419, Sept. 1997.

- [13] S. Y. Chen, C. M. Wang, and S. Y. Cheng, "Role of perovskite PMN in phase formation and electrical properties of high dielectric Pb(Mg<sub>x</sub>,Zn<sub>1-x</sub>)<sub>1/3</sub>Nb<sub>2/3</sub>O<sub>3</sub> ceramics," *Mat. Chem. Phys.*, vol. 52, no. 3, pp. 207–213, 1998.