# Improvement on Intrinsic Electrical Properties of Low-k Hydrogen Silsesquioxane/Copper Interconnects Employing Deuterium Plasma Treatment

Po-Tsun Liu,<sup>a,\*</sup> Ting-Chang Chang,<sup>b,c,\*\*,z</sup> Ya-Liang Yang,<sup>c</sup> Yi-Fang Cheng,<sup>d</sup> Jae-Kyun Lee,<sup>e</sup> Fu-Yung Shih,<sup>e</sup> Eric Tsai,<sup>e</sup> Grace Chen,<sup>e</sup> and Simon M. Sze<sup>a,c</sup>

The interaction between copper interconnects and low-*k* hydrogen silsesquioxane (HSQ) film was investigated using a Cu/HSQ/Si metal insulation semiconductor capacitor and deuterium plasma post-treatment. Owing to serious diffusion of copper atoms in HSQ film, the degradations of dielectric properties are significant with the increase of thermal stress. The leakage current behavior in high-field conduction was well explained by the Poole-Frenkel (P-F) mechanism. By applying deuterium plasma treatment to HSQ film, however, the leakage current was decreased and P-F conduction can be suppressed. In addition, the phenomena of serious Cu penetration were not observed by means of electrical characteristic measurements and secondary ion mass spectroscopy analysis, even in the absence of diffusion barrier layers. This indicates that copper diffusion in low-*k* HSQ film can be effectively blocked by deuterium plasma post-treatment. Therefore, further improvement in resistance-capacitance reduction can be obtained due to the minimized thickness requirement for conventional barriers such as inorganic Si<sub>3</sub>N<sub>4</sub> and metallic TaN layers.

© 2000 The Electrochemical Society. S0013-4651(99)08-022-2. All rights reserved.

Manuscript submitted August 6, 1999; revised manuscript received October 25, 1999.

As ultralarge-scale integrated (ULSI) circuits are scaled down, interconnect structures with two or more metal levels have become the dominant tendency to produce high-density circuits and enhance device performance. In these designs, the linewidth and spacings between metal interconnects also are made smaller. The smaller line dimension increases the resistivity of the metal lines and the narrower interline spacing increases the parasitic capacitance between the lines so that copper with low resistivity (1.67  $\mu\Omega$  cm for bulk) and high electromigration resistance and new interlayer dielectric (ILD) materials with low-dielectric constant (k < 3) are required to reduce the resistance-capacitance (RC) delays associated with the metal interconnect system. These candidates for low-k dielectric films<sup>1,2</sup> have been based either on spin-on deposition<sup>3</sup> or chemical vapor deposition (CVD).4 One of the most promising low-k materials is siloxane-based hydrogen silsesquioxane (HSQ)<sup>5-8</sup> having the general formula  $(HSiO_{3/2})_{2n}$ , n=2, 3, etc., available as flowable oxide (FOX) from Dow Corning, Inc. HSQ is an inorganic material that can be considered as a derivative of SiO<sub>2</sub> in which one of the four oxygen atoms bonded to every silicon atom is replaced by hydrogen. This class of inorganic spin-on dielectric has a low dielectric constant (about 2.8), available non-etchback process, planarization, and good gap-filling characteristics. 9,10 Furthermore, the low dielectric properties can be achieved if the density of Si-H bonding is maintained at a high level and the formation of -OH bonds and absorption or creation of water in the film is minimized.<sup>7,11</sup> Therefore, the integration of HSQ film as an interlayer dielectric (ILD) into multilevel interconnects has received much attention. 12-14. However, the use of copper interconnects has some issues in integrated circuit (IC) application, because it is easy to diffuse into the dielectric films to degrade the reliability. For this reason, copper interconnects formed by damascene process need the deposition of some conventional barrier layers such as inorganic Si<sub>3</sub>N<sub>4</sub> and metallic TaN layers at the interface between dielectric films and copper lines, forming a cladding structure to prevent Cu from penetrating through dielectric films. These barrier layers usually have high resistivity or high di-

electric constant (for  $\mathrm{Si_3N_4}$ ), which cause a higher via resistance and higher equivalent parasitic capacitance. For example, the resistivity of Ta is 146  $\mu\Omega$  cm, and that of TaN is 275  $\mu\Omega$  cm. According to Huang *et al.*, <sup>15</sup> the ranges on measured sheet resistance of 0.3  $\mu$ m Cu interconnects using Ta and TaN as a barrier are from 0.04 to 0.05  $\Omega/\Box$ . The sheet resistance of Cu interconnection is about 0.048  $\Omega/\Box$  and almost no difference between the use of Ta and TaN as a barrier. However, the via resistance of the cladding structure with TaN barrier is about 1.3  $\Omega$  in a thickness of 400 Å and higher than that with Ta (1.0  $\Omega$ ) barrier. These barrier layers would tend to the increase in the RC delay and offset partial advantages of the copper interconnect system. In the search for a high-performance metallization system, it is necessary for the enhancement in the resistance of low-k dielectrics to copper diffusion to minimize the thickness requirement for conventional barrier layers.

In this work, we have investigated the influence of copper on the intrinsic dielectric properties of low-*k* HSQ film. Leakage current behavior also was intensively studied, since a relatively high electric field may be produced even for a low applied operation field in deep subquarter micron interconnection devices. In addition, deuterium plasma post-treatment was applied on HSQ film for the first time instead of conventional high-resistivity or high-dielectric-constant barrier layer minimizing the increase in RC delay in order to obtain a better performance in the copper interconnect system.

## Experimental

The wafers were spin-coated with a single layer of flowable oxide (HSQ) and baked sequentially on a hot plate at 150, 200, and 300°C, for 1 min, followed by furnace curing at 400°C for 1 h in nitrogen atmosphere. Under each condition, film stress, shrinkage, refractive index, and IR absorption spectra were evaluated. Then, samples were treated with deuterium plasma on as-cured HSQ film. The deuterium plasma was operated at a pressure of 300 mTorr and with a deuterium gas flow rate of 300 sccm in a plasma-enhanced chemical vapor deposition (PECVD) reaction chamber. Radio frequency (rf) power of 100 W, which established the deuterium plasma, was applied to the upper electrode and the wafers were placed on the bottom by grounded electrode, which can be rotated for improving uniformity, at a substrate temperature up to 300°C. Metal insulation semiconductor ca-

<sup>&</sup>lt;sup>a</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, HsinChu 300, Taiwan

<sup>&</sup>lt;sup>b</sup>Department of Physics, National Sun Yat-Sen University, Taiwan

<sup>&</sup>lt;sup>c</sup>National Nano Device Laboratory, HsinChu 300, Taiwan

<sup>&</sup>lt;sup>d</sup>Institute of Materials Science and Engineering, National Chiao Tung University, HsinChu 300, Taiwan

<sup>&</sup>lt;sup>e</sup>Dow Corning Taiwan, Incorporated, Chungli, Taiwan

<sup>\*</sup> Electrochemical Society Student Member.

<sup>\*\*</sup> Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: tcchang@ndl.gov.tw

pacitors (MIS) were manufactured by sputtering a copper layer onto the HSQ film as the top electrode. Following copper deposition, samples were annealed at the temperature region of 425-500°C for 30 min in nitrogen atmosphere. A Keithley model 82 capacitance-voltage (CV) meter was used to measure the dielectric constant of the HSQ film. The capacitor was measured at 1 MHz with an ac bias for high-frequency capacitance-voltage (C-V) curves. The midgap interface density ( $D_{\rm it}$ ) was derived from high-frequency C-V and quasi-static C-V measurements. Leakage current-voltage (I-V) characteristics and secondary ion mass spectroscopy (SIMS) analysis of HSQ film was used to investigate the diffusion of copper.

#### **Results and Discussion**

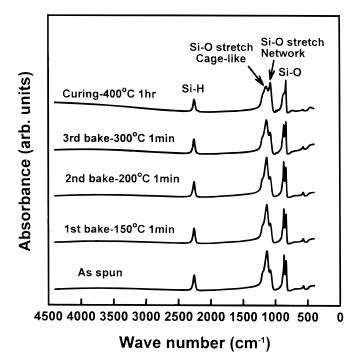

Figure 1 shows Fourier transform infrared (FTIR) spectra of HSQ film before and after a series of baking and curing steps. The important regions in the FTIR spectrum of HSQ film are the S-H stretching peak near 2250 cm<sup>-1</sup>, a Si-O stretching cage-like peak near 1130 cm<sup>-1</sup>, a Si-O stretching network peak near 1070 cm<sup>-1</sup>, Si-O bending cage-like peak near 863 cm<sup>-1</sup>, and a Si-O bending network peak near 830 cm<sup>-1</sup>. Most of solvent is eliminated up to 150°C, then HSO film melt at 200°C baked temperature. At 300°C baked temperature, flow occurs and additional bond rearrangement gives film greater strength to resist cracking and decreased surface roughness. 16 During the baking process, the FTIR spectra of HSQ are almost the same. After a 400°C curing process, however, the peak of the Si-O stretching vibration and that of the bending vibration significantly change. It is clearly shown that the chemical structure of HSQ film changes from cage-like to a three-dimensional network structure to provide sufficient mechanical integrity to withstand subsequent processing.

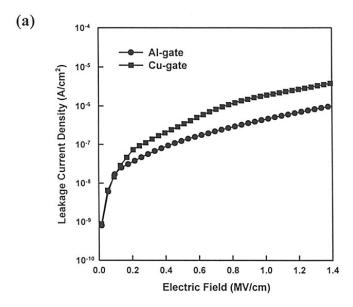

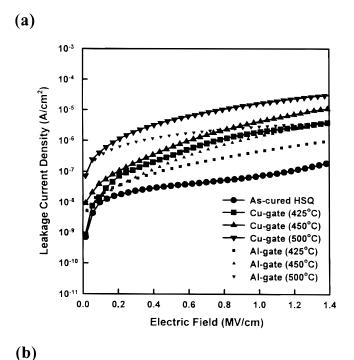

First, control samples were fabricated following the same processing sequence of Cu/HSQ/Si capacitors except that an Al gate instead of Cu metallization was used to investigate the impact of copper on low-*k* HSQ film. Figures 2a and b shows the leakage current density and dielectric constant of Al- and Cu-gate samples, respectively, after being subjected to a thermal annealing at 425°C for 30 min. Experimental results show that both the leakage current density and dielectric constant of Cu gate samples are increased when

Figure 1. FTIR spectra of HSQ before and after a series of bake and curing steps.

compared with those of the Al gate. However, the dielectric degradations of HSQ film worsen with increase in annealing temperature.

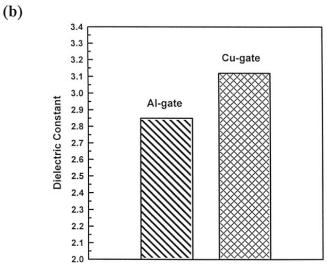

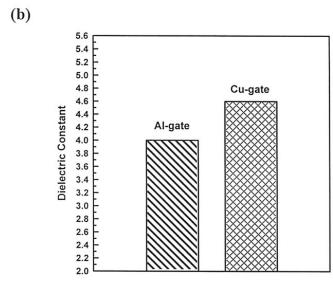

Figures 3a and b show the leakage current density and dielectric constant of Al- and Cu-gate samples, respectively, after being subjected to elevated thermal stress at 500°C. When annealing HSQ films at 500°C, the HSQ film properties are degraded due to the pyrolysis of the HSQ film. During thermal stress, Si-H bonds in HSQ film are easily broken at the elevated annealing temperature, which causes the generation of dangling bonds and moisture absorption<sup>11,17</sup> in the HSQ film invariably resulting in the increase of leakage current and permittivity for the Al-electrode samples. In addition, it is observed that the leakage current density of HSQ with a Cu gate is much higher than that with an Al gate, with an increase of as much as one order of magnitude, especially in the high-field-conduction region. On the other hand, the dielectric constant of the Cu-electrode samples is also increased drastically. This seems to indicate that Cu diffusion may play a role in the degradation of HSQ film as well. According to previous documents, 18,19 it has been verified that copper tends to diffuse into silicon dioxide to degrade the dielectric properties resulting in increased leakage current. Therefore, it is presumed that the increased leakage current of Cu-electrode samples results from copper diffu-

**Figure 2.** Dielectric properties of Cu- and Al-gate samples after being subjected to thermal stress at 425°C for 30 min: (a) leakage current density of HSQ film as a function of electric field and (b) dielectric constant of Cu- and Al-gate HSQ film.

sion into the siloxane-based HSQ film. This inference can be confirmed further by the analysis of SIMS depth profiles and the investigation on the mechanism of leakage current conduction.

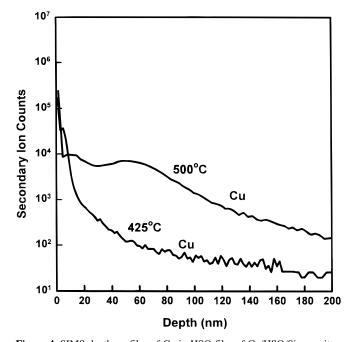

Figure 4 shows the SIMS depth profiles of copper in HSQ film of Cu-electrode samples after being subjected to a thermal stress at 425 and 500°C for 30 min. The copper profile shows a high level of copper is observed at the surface of the HSQ film and an exponential-like decay in the HSQ bulk. In addition, it is observed that the copper content in the HSQ film is increased with the increase of annealing temperature.

The variations in electrical characteristics of HSQ film with the increase of thermal stress can be summarized in Fig. 5a and b, which shows the leakage current density and dielectric constant of Al- and Cu-gate samples after being subjected to thermal stresses ranging from 425 to 500°C, respectively, for 30 min. In comparison with Alelectrode samples, it is obvious that the pyrolysis of low-*k* HSQ and Cu diffusion simultaneously play important roles in the case of Cu-electrode samples. Both the leakage current and dielectric constant of HSQ with the Cu electrode are significantly increased with the

(a) 10-Al-gate Cu-gate Leakage current Density (A/cm²) 10-10 10-10-10 0.0 0.6 0.8 1.2 1.4 Electric Field (MV/cm)

**Figure 3.** Dielectric properties of Cu- and Al-gate samples after being subjected to thermal stress at 500°C for 30 min: (a) leakage current density of HSQ film as a function of electric field and (b) dielectric constant of Cu- and Al-gate HSQ film.

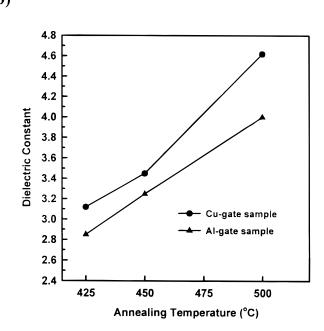

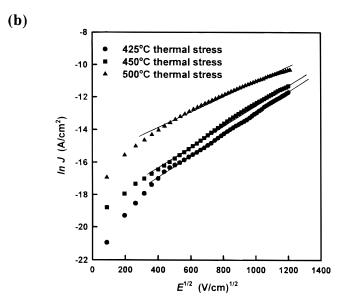

increase of annealing temperature due to serious degradation of dielectric properties resulting from thermal stress and copper diffusion into the HSQ film. Leakage current behaviors of HSQ film with the Cu gate can be investigated further on the leakage current (*J*)-electric field (E) characteristics such as a log J vs. log E and log J vs.  $E^{1/2}$ plots, as shown in Fig. 6a and b, respectively. At the low electrical field region, the leakage current density is nearly linear to applied field. The slopes of the linear fitting curves are 1.10, 0.901, and 0.962 for samples stressed at 425, 450, and 500°C, respectively, in the log J vs. log E plot. The linear lines represent the nearly ohmic conduction in low electric field, as shown in Fig. 6a, and little change in current density with a change of electrode from Cu to Al. These results seem to suggest that the leakage current conduction is primarily governed by bulk-limited conduction. The bulk-limited conduction is due to the presence of a large amount of defects in films. To confirm this point of view, the plot of the leakage current density vs. the square root of the applied electric field was observed, as shown in Fig. 6b. It is found that the leakage current density is linearly related to the square root of the applied electric field. The linear variations of the current correspond either to Schottky emission<sup>20,21</sup> or to the Poole-Frenkel (P-F) mechanism.<sup>22,23</sup>

The Schottky-Richardson emission generated by the thermionic effect is caused by electron transport across the potential energy barrier via field-assisted lowering at a metal-insulator interface. The current density (J) in the Schottky emission can be quantified by the following equation

$$J = A * T^2 \exp\left(\frac{\beta_s E^{1/2} - \phi_s}{k_B T}\right)$$

[1]

where  $\beta_s = (e^3/4\pi\epsilon_0\epsilon)^{1/2}$ , e is the electronic charge,  $\epsilon_0$  the dielectric constant of free space,  $\epsilon$  the high-frequency relative dielectric constant,  $A^*$  the effective Richardson constant, T absolute temperature, E applied electric field,  $\phi_s$  the contact potential barrier, and  $k_B$  the Boltzmann constant. The P-F emission is due to field-enhanced thermal excitation of trapped electrons in the insulator into the conduction band. The current density is given by

$$J = J_0 \exp \left( \frac{\beta_{PF} E^{1/2} - \phi_{PF}}{k_B T} \right)$$

[2]

**Figure 4.** SIMS depth profiles of Cu in HSQ film of Cu/HSQ/Si capacitors after being subjected to thermal stress at 425-500°C for 30 min.

where  $J_0 = \sigma_0 E$  is the low-field current density,  $\sigma_0$  the low-field conductivity,  $\beta_{\rm PF} = (e^3/\pi \epsilon_0 \epsilon)^{1/2}$ , and  $\phi_{\rm PF}$  the height of trap potential well. For trap states with coulomb potentials, the expression is virtually identical to that of the Schottky emission. The barrier height, however, is the depth of the trap potential well, and the quantity  $\beta_{\rm PF}$  is larger than in the case of Schottky emission by a factor of 2.<sup>23</sup>

Distinction between the two processes can be done by comparing the theoretical value of  $\beta$  with the experimental one obtained by calculating the slope of the curve log J- $E^{1/2}$ . The relative dielectric constant determined from capacitance measurements of samples with the Cu gate is about 3.1 at 425°C, 3.4 at 450°C, and 4.6 at 500°C, respectively. They yield the various values of the constant  $\beta$ , as shown in Table I. The slope ( $\beta/k_BT$ )) of the straight line portion of curve in

**Figure 5.** Dielectric properties of Al- and Cu-gate HSQ film after various thermal annealing temperatures (425-500°C) for 30 min: (a) leakage current density of HSQ film as a function of electric field and (b) dielectric constant of HSQ film as a function of thermal annealing temperature.

**Figure 6.** (a) Log J vs. log E characteristics of Cu-gate HSQ. Linear lines represent the nearly ohmic conduction at the initial low field. (b) J-E curves on a log J vs.  $E^{1/2}$  plot of Cu-gate HSQ showing P-F conduction at the high field region.

Fig. 6b gives a value of  $6.475 \times 10^{-24}$  at  $425^{\circ}$ C,  $6.393 \times 10^{-24}$  at  $450^{\circ}$ C, and  $5.42 \times 10^{-24}$  J(m/V) $^{1/2}$  at  $500^{\circ}$ C for  $\beta$ , respectively, closer to  $\beta_{PF}$  than  $\beta_s$ . These results are strongly reasonable to believe that carriers are transported through the HSQ film of Cu/HSQ/Si capacitors by the field-enhanced P-F mechanism. It also indicates that a lot of traps resulting in P-F conduction are generated due to copper diffusion into HSQ film.

From these observations, the leakage current mechanism of Cugate HSQ film can be summarized as follows. In comparison with

Table I. The various values of the dielectric constant and the constant  $\beta$  at 425, 450, and 500°C.

| Temperature (°C)                                                                                  | 425°C                                                | 450°C                                              | 500°C                                              |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Dielectric constant $\beta_s$ (J m <sup>1/2</sup> V <sup>1/2</sup> ) $\beta_{PE}$ (= 2 $\beta$ s) | $3.12$ $3.43 \times 10^{-24}$ $6.87 \times 10^{-24}$ | $ 3.45 3.26 \times 10^{-24} 6.53 \times 10^{-24} $ | $ 4.62 2.82 \times 10^{-24} 5.64 \times 10^{-24} $ |

Al-electrode samples, higher temperatures cause higher leakage currents of Cu-electrode samples. This is due to an enhancement in thermal excitation of trapped electrons in the HSQ film. Under higher thermal stress, large amounts of copper will diffuse into HSQ film and generate a lot of trap centers in HSQ film with the increase of annealing temperature. In addition, the increasing Cu content in the HSQ film tends to lower the potential drop across the surface region, causing a larger fraction of applied voltage to drop across the rest of the HSQ film. This can be modeled as a thinning in the effective HSQ thickness. The increase in electric field and the generation of defects (i.e., traps) enhance the P-F conduction mechanism. As a result, the leakage current is significantly increased with the increase of annealing temperature when compared with that of Al-electrode samples. The generation of defects also speeds up the dielectric degradation of HSQ film, causing increased dielectric constant. Furthermore, the thinning in the effective thickness leads to larger measured capacitance, according to the relation  $C = \epsilon_0 \epsilon A/d_{\text{eff}}$ , where A is the area of the top electrode and  $d_{\rm eff}$  is the effective film thickness.

Therefore, a higher dielectric constant derived from the measurement of MIS capacitors would be obtained if the effect of thinning in effective thickness were not considered.

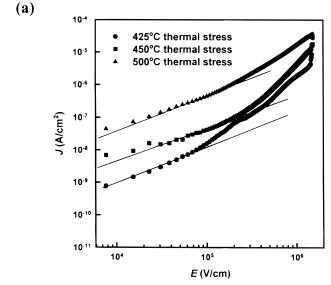

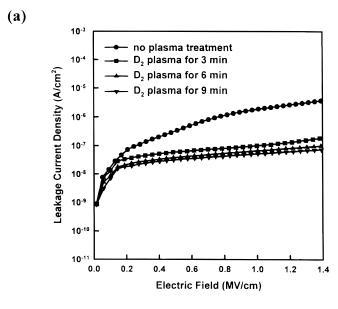

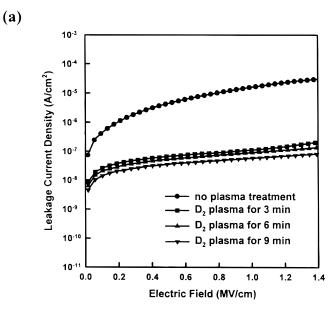

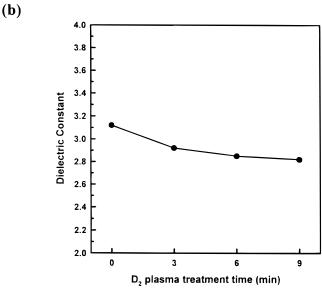

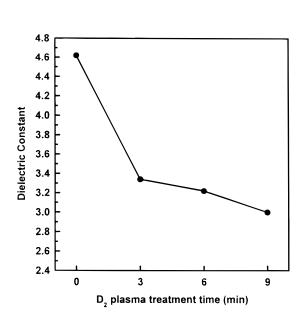

To alleviate this degradation, we applied deuterium ( $D_2$ ) plasma treatment on the as-cured HSQ film instead of a high-resistivity and high-dielectric-constant diffusion barrier layer between Cu-gate and HSQ film. Figures 7a and b show the leakage current and dielectric constant, respectively, of  $D_2$ -plasma-treated HSQ film in Cu-electrode samples after subjection to thermal stress at a temperature of 425°C for 30 min. The leakage current and dielectric constant are decreased with the increase of  $D_2$ -plasma treatment time. It is observed especially that the reduction of leakage current at the high-electric-field region is significant. Furthermore, more elevated thermal stress was applied on the HSQ treated with  $D_2$  plasma treatment to investigate the effect of deuterium plasma. Figure 8a and b shows the leakage current and dielectric constant, respectively, of  $D_2$ -plasma-

Figure 7. Dielectric properties of various  $D_2$ -plasma-treated samples with Cu gate after being subjected to a thermal stress at 425°C for 30 min: (a) leakage current density of treated HSQ film as a function of electric field and (b) dielectric constant of treated HSQ film as a function of  $D_2$  plasma treatment time.

Figure 8. Dielectric properties of various  $D_2$ -plasma-treated samples with Cu gate after being subjected to a thermal stress at 500°C for 30 min: (a) leakage current density of treated HSQ film as a function of electric field and (b) dielectric constant of treated HSQ film as a function of  $D_2$  plasma treatment time.

**(b)**

treated HSQ film in Cu-electrode samples after being subjected to thermal stress at  $500^{\circ}$ C for 30 min. Surprisingly, the leakage current of HSQ with  $D_2$  plasma treatment at the high electric field region is kept almost the same as that of samples with  $D_2$  plasma treatment in Fig. 7a. Compared with untreated samples, a reduction in leakage current of approximately two orders of magnitude is observed for  $D_2$ -treated samples. In addition, the dielectric constant of HSQ with  $D_2$  plasma treatment still maintains at a low value (about 3) after treatment time of 9 min. Therefore, it clearly shows that deuterium plasma treatment can effectively restore the properties of a damaged film to a similar state as an as-cured HSQ film.

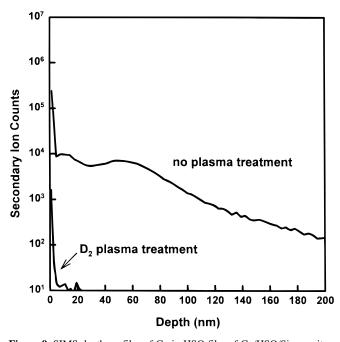

A material analysis technique was carried out to observe the distribution of Cu atoms in the HSQ film. Figure 9 shows the SIMS depth profiles of copper in HSQ film of Cu-electrode samples after a thermal stress at  $500^{\circ}$ C for 30 min. Consistent with our electric characteristics, a significant amount of Cu atoms are observed in the untreated sample. However, the profile of the Cu in a D<sub>2</sub>-treated sample revealed a very shallow Cu penetration and only a slight amount of Cu appeared within 20 nm of the surface, even after applying thermal stress at an elevated temperature. This clearly shows the phenomenon of copper diffusion into HSQ film was significantly reduced by deuterium plasma treatment.

The mechanism responsible for  $D_2$  plasma treatment can be explained using the electrical characteristic measurement of interface trap density ( $D_{it}$ ), which is evaluated from the high-frequency and quasi-static C-V characteristic<sup>24</sup> as follows

$$D_{\rm it} = \frac{C_{\rm HSQ}}{q} \left( \frac{C_{\rm lf}/C_{\rm HSQ}}{1 - C_{\rm lf}/C_{\rm HSQ}} - \frac{C_{\rm hf}/C_{\rm HSQ}}{1 - C_{\rm hf}/C_{\rm HSQ}} \right)$$

[3]

where  $C_{\rm HSQ}$  is the HSQ capacitance, which was measured with MIS capacitor bias at accumulation polarity  $C_{\rm lf}$  and  $C_{\rm hf}$  are the quasi-static and high-frequency capacitance of Cu/HSQ/Si MIS capacitors, respectively.

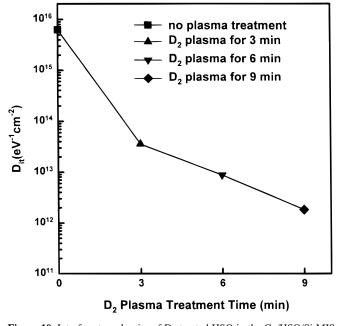

All the parameters of the MIS capacitors were automatically calculated by computer from the data measured by the Keithley package 82 system. Figure 10 shows the trap density of the Cu/HSQ/Si MIS capacitors after applying thermal stress at 500°C. From the variation in trap density, it is found that the trap density of no-D<sub>2</sub>-plasma-treated HSQ film is the largest. In addition, the trap density

experimental results are explained as follows. During the thermal annealing process, the high temperature makes Cu active, possessing a considerable quantity of kinetic energy and diffusing easily into the siloxane-based HSQ film. In addition, a variety of bonding destruction and recombination occurred simultaneously, making the structure of HSQ change from cage-like monomer into network-like polymer at the temperature higher than 400°C. Si and O elements play an important role during the linking process. A great amount of uncovered Si bonds would exist due to a small fraction of incomplete recombination of Si-O bonds and Si-H bonds broken at the elevated temperature. The uncovered Si bonds are imperfect bonds (i.e., dangling bonds or defects) which would result in unstable film. In the absence of a diffusion barrier layer between Cu and low-k HSQ film, unstable dangling bonds would come in contact with Cu atoms having a high kinetic energy. This heightens the probability of interaction with Cu and makes copper easy to diffuse through these defects, increasing the diffusion paths of Cu atoms into HSQ film. More elevated annealing temperature would significantly raise the Cu kinetic energy and speed up the pyrolysis of film, generating much more dangling bonds to enhance Cu diffusion into HSQ. In addition, Cu diffusion by way of defects in HSQ bulk forms trap centers resulting in increased leakage current, which is increased with the increase of annealing temperature. The degradation of dielectric properties attributed to the presence of Cu would also lead to more dangling bonds (i.e., higher trap density) in untreated HSQ film. D<sub>2</sub> plasma post-treatment has been proposed to enhance the dielectric properties of oxide and reduce the hot-electron degradation in metal oxide semiconductor transistors due to its significant achievement on the passivation of dangling bonds resulting in reduced interface state generation. 25-27 Similarly, the effect of  $D_2$  treatment also appeared in our work. By applying D<sub>2</sub> plasma treatment on as-cured HSQ film, a lot of D2 radicals are provided. The active D2 radicals can react with the uncovered Si bonds, forming passivation layers either on the surface or in the bulk. It is thought that a porous HSQ structure is helpful for the diffusion of D<sub>2</sub> radicals with small volume. Hence, the trap density of HSQ films after D<sub>2</sub> plasma treatment is decreased, indicating the reduction in the concentration of dangling bonds. In addition, the passivation layers reduce the probability of reaction with Cu and effectively reduce the diffusion paths of Cu penetration through HSQ. Therefore, the Cu content in HSQ after D<sub>2</sub> plasma

is decreased with the increase of D<sub>2</sub> plasma treatment time. These

**Figure 9.** SIMS depth profiles of Cu in HSQ film of Cu/HSQ/Si capacitors after being subjected to a thermal stress for 30 min at 500°C.

Figure 10. Interface trap density of  $D_2$ -treated HSQ in the Cu/HSQ/Si MIS capacitors after thermal stress at 500°C for 30 min.

treatment is much less than that in untreated HSQ, which also is consistent with our SIMS data as shown in Fig. 9.

#### **Conclusions**

Dielectric degradation of Cu/HSQ/Si structure was observed at elevated temperature stress due to copper penetration into HSQ film. Even in absence of diffusion barrier layers, however, dielectric properties of HSQ can be maintained by D<sub>2</sub> plasma treatment. D<sub>2</sub> plasma treatment effectively passivates the dangling bonds exposed in the structure of HSQ film and reduces the trap's content, suppressing the P-F conduction mechanism performed in leakage current behavior. Furthermore, the passivation layer significantly blocks copper diffusion at the low-k HSQ/copper interface and effectively restores the properties of a damaged film to a similar state as an as-cured HSQ film. The additional signal transmission delay produced from the induction of high-resistivity or high-permittivity diffusion barriers can be minimized when applying D<sub>2</sub> plasma treatment associating with rather thin barrier layer. Therefore, higher-performance operation in Cu interconnect systems can be achieved.

### Acknowledgment

This work was performed at the National Nano Device Laboratory and was supported by Dow Corning Taiwan, Incorporated, and the National Science Council of the Republic of China under contract no. NSC 88-2215-E-317-009.

The National Nano Device Laboratory, Taiwan, assisted in meeting the publication costs of this article.

#### References

- The National Technology Roadmap for Semiconductors, Semiconductor Industry Association, San Jose, CA (1997).

- P. A. Kohl, Q. Zhao, K. Patel, D. Schmidt, S. A. Bidstrup-Allen, R. Shick, and S. Jayaraman, in *Dielectric Material Integration for Microelectronics*, W. D. Brown, S. S. Ang, M. Loboda, S. Sammakia, R. Singh, and H. S. Rathore, Editors, PV 98-3, p. 169, The Electrochemical Society Proceedings Series, Pennington, NJ (1998).

- R. Y. Leung, T. Nakano, S. Case, B. Sung, J. J. Yang, and D. K. Choi, No. 97-ISMIC-222D, in *Proceedings of the Third International Dielectrics for ULSI Multilevel Interconnection Conference*, DUMIC, p. 19, Santa Clara, CA, Feb 10-11, 1907

- G. Sugahara, N. Aoi, M. Kubo, K. Arai, and K. Sawada, No. 97-ISMIC-222D, in Proceedings of the Third International Dielectrics for ULSI Multilevel Interconnection Conference, DUMIC, p. 19, Santa Clara, CA, Feb 10-11, 1997.

- 5. M. G. Albrecht and C. Blanchette, J. Electrochem. Soc., 145, 4019 (1998).

- M. J. Loboda, C. M. Grove, and R. F. Schneider, J. Electrochem. Soc., 145, 2861 (1998).

- H. Meynen, R. Uttecht, T. Gao, M. Van Hove, S. Vanhaelemeersch, and K. Maex, in *Dielectric Material Integration for Microelectronics*, W. D. Brown, S. S. Ang, M. Loboda, S. Sammakia, R. Singh, and H. S. Rathore, Editors, PV 98-3, p. 29, The Electrochemical Society Proceedings Series, Pennington, NJ (1998).

- 8. T. C. Chang, P. T. Liu, F. Y. Shih, and S. M. Sze, Electrochem. Solid-State Lett., 2, 390 (1999).

- B. T. Ahlburn, G. A. Brown, T. R. Seha, and T. F. Zoes, No. 95-ISMIC-101D, in Proceedings of the International Dielectrics for ULSI Multilevel Interconnection Conference, DUMIC, p. 36, Santa Clara, CA (1995).

- 10. N. H. Hendricks, Mater. Res. Soc. Symp. Proc., 443, 3 (1996).

- D. Thomas, G. Smith, and L. Nguyen, No. 97-ISMIC-222D, in Proceedings of the Third International Dielectrics for ULSI Multilevel Interconnection Conference, DUMIC, p. 361, Santa Clara, CA, Feb 10-11, 1997.

- J. Wataerloos, H. Meynen, B. Coenegrachts, T. Gao, J. Grillaert, and L. Van den hove, No. 97-ISMIC-222D, in *Proceedings of the Third International Dielectrics* for ULSI Multilevel Interconnection Conference, DUMIC, p. 310, Santa Clara, CA, Feb 10-11, 1997.

- S. Bothra, L. Q. Qian, M. Weiling, and D. Pramanik, No. 97-ISMIC-222D, in Proceedings of the Third International Dielectrics for ULSI Multilevel Interconnection Conference, DUMIC, p. 273, Santa Clara, CA, Feb 10-11, 1997.

- V. M. Gayay, A. Acovic, B. Aryarwala, G. Endicott, M. Shapiro, and S. Yankee, No. 96-ISMIC-106, in *Proceedings of the 13th International VLSI Multilevel Interconnection Conference*, VMIC, p. 116, June 18-20, 1996.

- Y. Huang, T. R. Yew, W. Lur, and S. W. Sun, No. 98-ISMIC-108, in Proceedings of the International VLSI Multilevel Interconnection Conference, VMIC, p. 33 (1998).

- 16. Dow Corning Corporation, Fox User Group Meeting, Midland, MI, USA (1996).

- J. N. Bremmer, Y. Liu, K. G. Gruszynski, and F. C. Dall, No. 97-ISMIC-222D, in Proceedings of the Third International Dielectrics for ULSI Multilevel Interconnection Conference, DUMIC, p. 333, Santa Clara, CA, Feb 10-11, 1997.

- J. D. McBrayer, R. M. Swanson, and T. W. Sigmon, J. Electrochem. Soc., 133, 1242 (1986).

- A. L. S. Loke, C. Ryu, C. P. Yue, J. S. H. Cho, and S. S. Wong, *IEEE Electron. Device Lett.*, EDL-19, 177 (1998).

- J. G. Simmons, in *Handbook of Thin Film Technology*, L. I. Maissel and R. Glang, Editors, Chap. 14, p. 25, McGraw-Hill, New York (1970).

- P. Hesto, in *Instabilities in Silicon Devices*, G. Barvotlin, A. Vapaille, Editors, Vol. 1, Chap. 5, p. 263, North-Holland, Amsterdam (1986).

- J. G. Simmons, in *Handbook of Thin Film Technology*, L. I. Maissel and R. Glang, Editors, Chap. 14, p. 28, McGraw-Hill, New York (1970).

- S. M. Sze, Physics of Semiconductor Devices, Chap. 7, p. 402, Wiley, New York (1981)

- D. K. Schroder, Semiconductor Material and Device Characterization, Chap. 6, p. 371, Wiley-Interscience, New York (1998).

- 25. J. W. Lyding, K. Hess, and I. C. Kizilyalli, *Appl. Phys. Lett.*, **68**, 2526 (1996).

- R. A. B. Devine, J. L. Autran, W. L. Warren, K. L. Vanheusdan, and J. C. Rostaing, *Appl. Phys. Lett.*, 70, 2999 (1997).

- W. F. Clark, T. G. Ference, T. B. Hook, K. M. Watson, S. W. Mittl, and J. S. Burnham, IEEE Trans. Electron Devices, ED-20, 48 (1999).