# Micromachining on (111)-oriented silicon

Bruce C.S. Chou a,\*, Chung-Nan Chen b, Jin-Shown Shie b

Received 21 October 1998; received in revised form 12 November 1998; accepted 16 November 1998

#### Abstract

Micromachining on (111)-oriented silicon in various alkaline solutions was studied. By means of spoke and donut-like etching patterns, the experiment shows that  $\langle 110 \rangle$  directions have the highest etch rate and the final emergent periphery is hexagon bounded on the bottom surface plane. The six sidewalls are defined by {111} planes, which can be derived from its crystal geometry, having three facets with inclining angles of 70.5° and another three with declining angles of 109.5° respect to the (111) surface plane. SEM pictures show that aqueous KOH solution results in smooth surface morphology due to its higher etch rate of residual oxide existed in the silicon, while the other etchants such as hydrazine ( $N_2H_4$ ) and tetramethyl ammonium hydroxide (TMAH) induce seriously wavy roughness. Moreover, various concentrations of KOH solution have been studied to determine the (110)/(111) etch ratio, and the ratio more than 100 were demonstrated. Using this method, suspended single-crystal silicon (c-Si) microstructures were fabricated for some potential uses such as thermopile, silicon bolometer, mass flow transducer and other force microsensors. As an application example, shallow-gap  $\mu$ -Pirani vacuum sensor demonstrated its high pressure measuring capability as high as  $10^3$  Torr. © 1999 Elsevier Science S.A. All rights reserved.

Keywords: Micromachining; (111)-oriented; Suspended c-Si microstructures; Shallow-gap; μ-Pirani vacuum sensor

## 1. Introduction

Anisotropic etching of silicon has been used in the semiconductor industry since it was first discovered in the middle of the 1960s [1,2], especially, applications in the V-MOS [3] and SOI [4] related semiconductor devices fabrication. This state-of-the-art technique is widely used in MEMS for various types of sensors, actuators and optical components [5].

Till now, most of reported etching characteristics or related implementations have been based on the use of (100)- or (110)-oriented silicon wafers because of mature understanding of related etching behavior. For example, V-groove etching techniques on (100)-oriented wafers are characterized by the different etch rates of three major crystallographic planes (100), (110) and (111). The slowest etch rate always appears at {111} planes, which define the final emergent facets if the etch time is long enough. Therefore, V-shape and U-shape grooves bounded by four

{111} facets can be obtained using (100)- and (110)-oriented silicon, respectively. Nevertheless, few reports [6–8] about anisotropic etching of (111)-oriented silicon were announced due to its inherent hard etching of wafer plane itself, and was thought to be useless in MEMS application.

This paper is to describe the bulk machining behavior of (111)-oriented silicon in various alkaline solutions and related applications including large-size floating c-Si microstructures and shallow-gap  $\mu$ -Pirani vacuum sensor fabrication. Using spoke and donut-like patterns, etching characteristics of various crystallographic planes were observed. Moreover, the (110)/(111) etch ratio was studied for realistic applications and the optimal concentration of KOH for this experiment was presented.

# 2. Crystal stereography

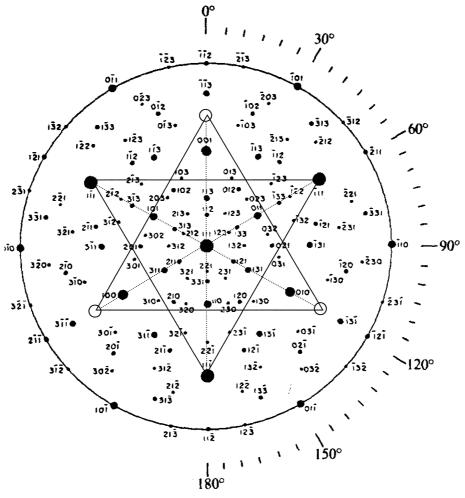

At atmospheric pressure, silicon has a diamond cubic structure. Its anisotropic etching behavior strongly depends on the crystal orientation. Fig. 1 is the crystallographic projection of (111)-oriented silicon. The  $\langle 111 \rangle$  axis of a

<sup>&</sup>lt;sup>a</sup> Precision Instrument Development Center (PIDC), National Science Council, 20 R&D Road VI, Hsinchu Science-Based Industrial Park, Hsinchu 300, Taiwan, R.O.C.

b Institute of Electro-Optical Engineering, National Chiao Tung University 1001 Ta Hsueh Road, Hsinchu 300, Taiwan, R.O.C.

<sup>\*</sup> Corresponding author. Tel.: +886-3-5779911 Ext. 318; Fax: +886-3-5009041; E-mail: bruce@pidc.gov.tw

Fig. 1. Crystallographic projection of (111)-oriented silicon.

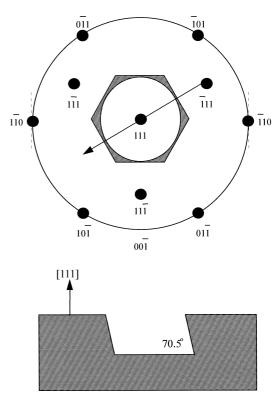

cubic system is an axis of hexagonal symmetry. The  $\{111\}$  planes projected from both the top  $(\bullet)$  and the bottom  $(\bigcirc)$  hemispheres have been marked on this stereographic projection. The three (111) planes  $(\bullet)$  are  $109.5^{\circ}$  to the surface plane, and they are  $60^{\circ}$  to each other. Another three (111) planes  $(\bigcirc)$  are  $70.5^{\circ}$  to the surface plane, and also  $60^{\circ}$  to each other. At the periphery of the projected plane, there are six (110) planes perpendicular to the surface plane.

## 3. Experimental

All experiments were performed using p-type, (111)-oriented, 4-inch silicon wafers. Various concentrations (10–60 wt.%) of aqueous KOH solution and other anisotropic etchants hydrazine (80 wt.%), TMAH (22 wt.%) were used to determine the etching characteristics on the silicon wafers. Etching solution was kept in a Pyrex glass vessel with reflux condenser and thermostat to maintain the concentration and temperature of the solution constant, respectively. The set-up temperature for KOH was 80°C,

hydrazine 100°C, and TMAH 80°C. No stirrer was used to agitate the solution.

After RCA cleaning, nitride film was deposited on the wafer by LPCVD. Then, the normal lithography and nitride etch steps were done to produce desired patterns including testing spoke, donut patterns. The lateral etch rate was measured by SEM pictures observation and the vertical etch rate was measured by step profiler. SEM photographs were also used for the surface morphology observation.

## 4. Results and discussion

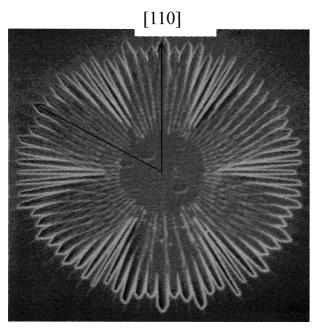

Fig. 2 shows an after-etch SEM picture using a spoke pattern in aqueous KOH solution. In this picture, the arrows mean the <110> direction. It is obvious that the six <110> directions corresponding to the six  $\{110\}$  planes appeared at the periphery of the (111) surface plane define the fastest etching fronts. The result is due to the spirit of aqueous KOH solution that has the highest etch rate at  $\{110\}$  planes, and this feature is often adopted to obtain deep U-groove on (110)-oriented silicon.

Fig. 2. Etching profile of a spoke pattern on (111) silicon wafer. The arrows correspond to  $\langle 110 \rangle$  directions.

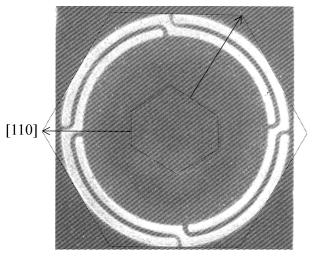

When a donut-like pattern was used, the etching result is depicted in Fig. 3. The final emerging periphery is hexagonal (outer). This outer hexagon, which is bounded by six {111} facets on the bottom (111) surface, has an equal angle of 120° and equal side length. The inner hexagon is the remaining silicon island bounded by six {110} facets corresponding to the <110 > directions (arrows). (Because the photograph is not in good contrast, we represent these hexagons with drawn dot line.) This inner hexagon implies {110} planes dominate the etching profile, which agrees with the result from Fig. 2. Fig. 4 is

Fig. 3. Etching front observation with a donut-like open. The outer hexagon is bounded by  $\{111\}$  planes and the inner hexagon is, nevertheless, defined by  $\{110\}$  facets corresponding to the  $\langle 110 \rangle$  arrow directions.

Fig. 4. The upper drawing is the simplified scheme of Figs. 1 and 3. The lower one reveals the parallelism of the opposite facets following the arrow direction.

the simplified drawing of Figs. 1 and 3, and the side view follows the arrow direction in this figure. Any pair of opposite facets of the outer hexagon is parallel, and any two neighboring facets have inclining and declining angles with respect to the surface plane. That means the boundary line between any two neighboring (111) facets is not sharp and straight, but complicated and twisted from inclining (declining) to declining (inclining) plane. This result is quite different from the anisotropic etching profile on (100) and (110) orientation wafers. Fig. 5 is the SEM picture of a cleaved sample that shows the parallel effect following the arrow direction described in Fig. 4.

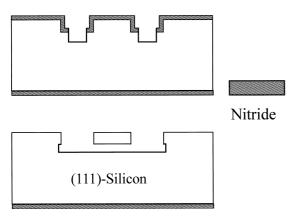

One application of the etching technology mentioned above is to form floating c-Si microstructures [6–8]. The process is schematically shown in Fig. 6 and briefly described as: first, a masking material such as LPCVD silicon-rich nitride [9] is deposited on the silicon for its low-stress characteristic and almost attack-free from anisotropic etchants. The first lithography step defines the first etch windows. The nitride film is etched using reactive ion etching (RIE) system, and then the naked silicon is etched to a desired depth using the same RIE system. The following process is to deposit second layer of nitride on the silicon wafer. The second lithography step was done with the second open windows that has a few micrometers shrinkage from the corresponding first etch window edge. Also, dry etch step removes the unwanted nitride film and

Fig. 5. A cleaved sample that shows the parallel effect following the arrow direction described in Fig. 4.

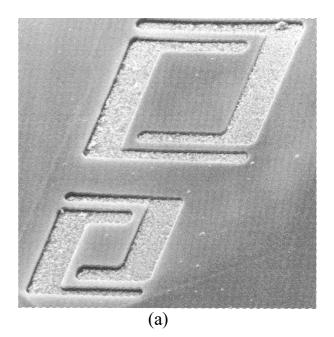

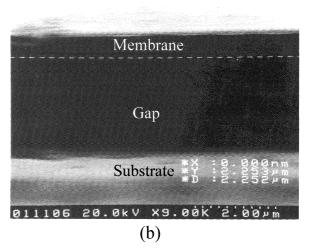

the remaining nitride to protect the top and the side of the preferred silicon microstructures with preformed thickness. Another RIE step is used to etch the naked silicon to the second desired depth for final anisotropic etching. This final RIE step is to etch trench with vertical walls so as to expose the {110} planes to the anisotropic etchants. During the etching, the underside of the floating silicon structures is protected because it is a (111) plane and etches very slowly. Fig. 7(a) is a SEM photograph of suspended c-Si microstructures with membrane dimensions of  $50 \times 50$  and  $100 \times 100 \, \mu \text{m}^2$ . Note that the white particles appear on the etch window is due to the KOH residue, and it can be easily removed by filtering the etch solution before using it. A particle-free picture is therefore shown in Fig. 7(b) to demonstrate the filtration result, on which white KOH residues are not seen on the bottom surface anymore. At the same time, the after-etch surface morphology due to various solutions was also studied and is shown in Fig. 8.

Fig. 6. Brief process steps for fabrication of floating c-Si microstructures.

Fig. 7. SEM picture of floating c-Si microstructures. Note that the white particles appear on the etch window is due to the KOH residue. (b) A close-up view of particle-free picture results from filtering KOH solution before using it.

It is obvious that KOH etching results in smooth surface due to its higher etch rate of residual oxide existed in the silicon, while the other two etchants such as hydrazine  $(N_2H_4)$  and tetramethyl ammonium hydroxide (TMAH) induce seriously wavy roughness.

In order to obtain large-size floating c-Si structures, the (110)/(111) etch rate ratio is the key parameter to success. From the literature [10], it was said that a KOH solution has very large (110)/(111) ratio more than 400 however, our experiment has the ratio value no more than 120 that is consistent with the other report [6]. Nevertheless, this is good enough to use it to obtain large-size silicon microstructures, which is suitable for thermopile, silicon bolometer, mass flow transducer and other force microsen-

Fig. 8. After-etch morphology on (111) surface plane due to various solutions, left KOH, middle TMAH and right hydrazine.

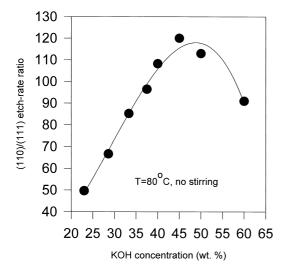

sors uses. Fig. 9 is a relation of various KOH concentrations vs. (110)/(111) ratio. A slight difference from the reported data [3,5] has indicated that about 45 wt.% KOH solution has the highest ratio to apply in this experiment.

### 5. Shallow-gap μ-Pirani vacuum sensor

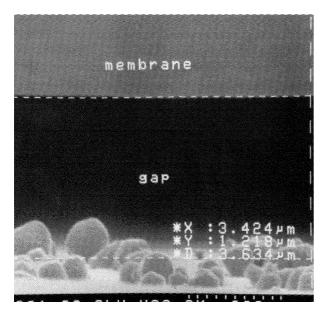

Owing to the very slow etch rate on the (111) surface plane and high etch rate in the lateral direction, besides the suspended silicon microstructures formed in Fig. 7, another interesting feature is shallow gap formation under the

Fig. 9. The relation of (110)/(111) etch ratio and various concentrations of aqueous KOH solution. In this experiment, 45-wt.% KOH solution has the ratio value as high as 120.

floating structure. The shallow-gap technique in microfabrication is usually defined by a sacrificial layer, and its wet etching removal [10,11]. The sacrificial layer thickness determines the final spacing between the upper floating device and the lower substrate. Thinner sacrificial layer will suffer a sticking effect between the microstructures and the substrate due to surface extension force of liquid after wet etch of the sacrificial layer, but larger spacing has the problem of step coverage when the upper structure and sensing material cross over the sacrificial layer. Using the micromachining technique on (111)-oriented silicon, we can solve the sticking problem effectively by forming a larger spacing between the floating structure and its related substrate to reduce capillary force. One thing is noted that this gap can be tuned to be larger or smaller by post-etch control through selection of the etching solution and control of the etching condition including temperature and time. Furthermore, this method is a full planar process. It does not suffer the same step coverage problem that happened in the sacrificial layer process. Fig. 10 is a SEM picture showing the shallow gap of about 1 µm between the upper floating structure and the lower substrate. In this figure, the displayed \*Y value is the distance between the two parallel dash lines that denote the margins of the suspended structure and the underneath substrate. Also, the white particles on the bottom are the KOH residues whose elimination is discussed above.

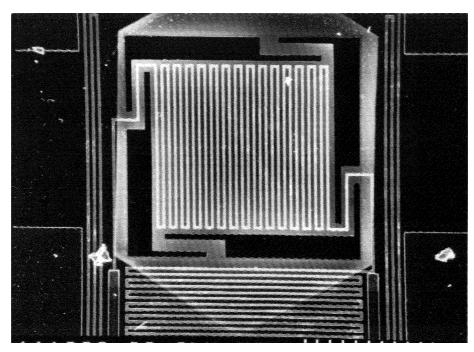

To realize the application of this shallow-gap forming methodology, Fig. 11 shows a fabricated  $\mu$ -Pirani vacuum sensor based on this technique. This sensor has an active floating element of  $300 \times 300 \ \mu m^2$  for gas pressure sensing and an on-substrate dummy for temperature compensation [12]. Its brief process flow is introduced as: the

Fig. 10. Shallow gap formation using (111) silicon wafer. Note that the gap can be as small as around 1 um as denoted by the displayed \*Y value.

floating membrane was made of low-stress silicon-rich nitride with a thickness of 0.4  $\mu m$  deposited by LPCVD. Platinum film of 0.15  $\mu m$  in thickness was deposited on the nitride membrane by E-gun evaporation for both the sensor and the dummy. PECVD nitride of 0.8  $\mu m$  thick was used for passivation. Each kink-shape lead has a length of 150  $\mu m$  and a width of 20  $\mu m$ , and the sensor has a resistance of about 3  $k\Omega$ . A wheatstone bridge constant bias circuit including partial temperature compensation method was arranged for the vacuum pressure mea-

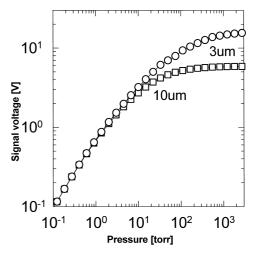

Fig. 12. High-pressure measurement using shallow-gap  $\mu$ -Pirani vacuum sensor. The circles ( $\bigcirc$ ) are those measured with a gap of 3  $\mu$ m, another 10  $\mu$ m-gap sensor is depicted in square symbols ( $\square$ ).

surements. A more complete configuration is referred to the previous report [12].

Fig. 12 shows the measuring result in the high pressure regime. The circles ( $\bigcirc$ ) are those measured with shallow gap of 3  $\mu$ m formed by 45 wt.% aqueous KOH solution. It is obvious that the detectable high pressure is up to  $10^3$  Torr. When we use another concentration of aqueous KOH solution, another 10  $\mu$ m-gap sensor can be obtained. Its pressure measurement result is also depicted in Fig. 12 with square symbols ( $\square$ ). Compared to the 3- $\mu$ m-gap sensor, it is less sensitive in the high-pressure measurement. This comparison result is mainly due to variations in

Fig. 11. Fabricated μ-Pirani vacuum sensor with shallow gap formed underneath the floating membrane.

the transition pressure, the physical definition of the highest detectable pressure, being inversely proportional to the spacing between the hot resistor and its substrate heat sink [12].

#### 6. Conclusions

Anisotropic etching characteristics of (111)-oriented silicon wafer and related applications were studied. Experimental results show that the highest etch rate appears in the  $\langle 110 \rangle$  directions, and the (110)/(111) ratio can be as high as 120 using 45-wt.% aqueous KOH solution. Floating c-Si microstructures can therefore be obtained for its many potential applications. A new shallow-gap formation method is also demonstrated to fabricate  $\mu$ -Pirani vacuum sensor with high pressure measurement capability, and this method makes the shallow gap tunable simply using 'post-etch control'—selection of the etching solution and control of the etching condition including temperature and time.

## Acknowledgements

The authors would like to express their appreciation to the Semiconductor Research Center of NCTU and the Nano Device Laboratory of NSC for the sample preparation and device fabrication.

#### References

- [1] D.B. Lee, Anisotropic etching of silicon, J. Appl. Phys. 40 (1959)

- [2] K.E. Bean, P.S. Gleim, The influence of crystal orientation on silicon semiconductor processing, IEEE Proc. 57 (1969) 1469–1476.

- [3] K.E. Bean, Anisotropic etching of silicon, IEEE Trans. Electron Devices 25 (1978) 1185–1193.

- [4] K.E. Bean, W.R. Runyan, Dielectric isolation: comprehensive, current and future, J. Electrochem. Soc.: Reviews and News 124 (1977) 5c. 12c

- [5] K.E. Peterson, Silicon as a mechanical material, IEEE Proc. 70 (1982) 420–457.

- [6] M. Kimura, M. Yoshida, N. Suzuki, Schottky barrier thermistor on the micro-air-bridge, Transducers '93, Yokohama, Japan, 1993, pp. 746–749.

- [7] G. Ensell, Free standing single-crystal silicon microstructures, J. Micromech. Microeng. 5 (1995) 1–4.

- [8] B.C.S. Chou, Thermal-conductivity micro pressure sensor, PhD dissertation, 1997, NCTU, Taiwan, ROC.

- [9] Bruce C.S. Chou, Jin-Shown Shie, Chung-Nan Chen, Fabrication of low-stress dielectric thin-film for microsensor applications, IEEE Electron Device Lett. 18 (1997) 599–601.

- [10] R.T. Howe, Surface micromachining for microsensors and microactuators, J. Vac. Sci. Technol. B 6 (1988) 1809–1813.

- [11] B.C.S. Chou, J.S. Shie, An Innovative Pirani Pressure Sensor, Transducers '97 Chicago, USA, 1997, pp. 1465–1468.

- [12] J.S. Shie, Bruce C.S. Chou, Y.M Chen, High performance Pirani vacuum gauge, J. Vac. Sci. Technol. A 13 (1995) 2972–2979.

Bruce C.S. Chou received his MS degree from National Tsing Hua University in 1991 and PhD degree from the institute of Electro-Optical Engineering, National Chiao Tung University, Hsinchu, Taiwan, in 1997, majoring in Si-based micromachining, microthermal sensors fabrication. Since then, he has been working in PIDC on the combination of excimer laser micromachining and CMOS-based Microsystems.

Chung-Nan Chen received his BS degree in physics from Chinese Culture University of Taiwan in 1988. He is currently a PhD candidate in Institute of Electro-Optical Engineering of National Chiao Tung University. His research is in the design and fabrication of thermal sensors.

Jin-Shown Shie earned his BSEE degree from National Cheng Kung University of Taiwan in 1965, and his MSEE degree from National Chiao Tung University in 1968, majoring in semiconductors. In 1972 he received his PhD degree from Department of Materials Science, SUNY, USA. Since then he has joined with National Chiao Tung University. He is currently a faculty member of Institute of Electro-Optical Engineering. His current interest is in the field of photodetections, particularly in room-temperature operated infrared FPA detectors and the system.