# A 10-Gb/s OEIC with Meshed Spatially-Modulated Photo Detector in 0.18- $\mu$ m CMOS Technology

Shih-Hao Huang, Wei-Zen Chen, Yu-Wei Chang, and Yang-Tung Huang

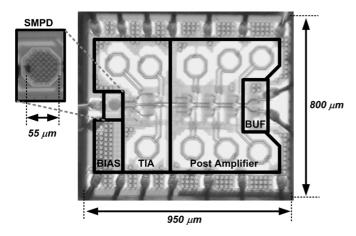

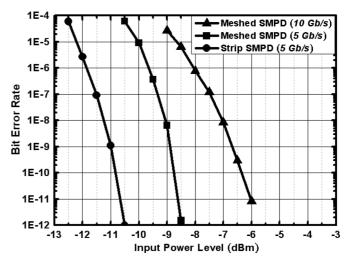

Abstract—This paper describes the design of a 10-Gb/s fully integrated CMOS optical receiver, which consists of a novel spatially-modulated photo detector (SMPD), a low-noise trans-impedance amplifier (TIA), and a post-limiting amplifier on a single chip. The bandwidth of proposed meshed SMPD can be boosted up to 6.9 GHz under a reverse-biased voltage of 14.2 V. The measured responsivity of the meshed SMPD is 29 mA/W as illuminated by 850-nm light source. To compensate the relatively low responsivity of on-chip CMOS photo detector (PD), a high-gain TIA with nested feedback and shunt peaking is proposed to achieve low-noise operation. The optical receiver is capable of delivering 25-k $\Omega$  conversion gain when driving 50- $\Omega$  output loads. For a PRBS test pattern of  $2^7-1$ , the 10-Gb/s optoelectronic integrated circuit (OEIC) has optical sensitivity of -6 dBm at a bit-error rate (BER) of  $10^{-11}$ . Implemented in a generic 0.18- $\mu$ m CMOS technology, the chip area is 0.95 mm by 0.8 mm. The trans-impedance amplifier, post amplifier, and output buffer respectively drain 38 mW, 80 mW, and 27 mW from the 1.8-V supply.

Index Terms—Optical receiver, optoelectronic integrated circuit (OEIC), spatially-modulated photo detector (SMPD), transimpedance amplifier (TIA), limiting amplifier (LA).

# I. INTRODUCTION

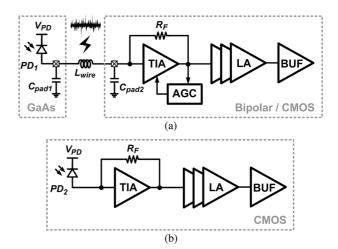

ATA communication over optical links benefits from wider bandwidth and lower channel loss compared to electrical counterparts. They are widely deployed for long-haul telecommunications as network backbone. Nowadays, with the increasing speed of backplane interconnects and electronics devices interfaces for short reach data link, such as HDMI [1], [2], USB [2], and light peak [3] technologies, optical links are drawing more and more attentions in these applications for their superiorities in less cross-talk, lower EMI, and fewer equalizer needed for data rate up to 10 Gb/s. Conventionally, an optical receiver is composed of multi-chips in different technologies [4]–[7]. For example, the PD is implemented in more expensive InGaAs or GaAs technology, while the TIA and post-limiting amplifier are fabricated using Bipolar/CMOS or BiCMOS process, as is shown in Fig. 1(a). To realize a cost effective optical receiver front-end for pervasive adaptation, monolithically integrated optoelectronic integrated circuits (OEICs) have

Manuscript received April 26, 2010; revised December 24, 2010; accepted February 08, 2011. Date of publication March 17, 2011; date of current version April 22, 2011. This paper was approved by Associate Editor Darrin Young. This work was supported by projects under contracts NSC 98-2221-E-009-134 and 97-EC-17A-03-S1-005, and was partially sponsored by MediaTek Inc.

The authors are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 30010, Taiwan (e-mail: wzchen@mail.nctu.edu.tw).

Digital Object Identifier 10.1109/JSSC.2011.2116430

Fig. 1. (a) Hybrid and (b) monolithic optical receiver front-end.

drawn tremendous research efforts [8]–[17] recently. As shown in Fig. 1(b), an on-chip PD, a TIA, and a post-limiting amplifier are integrated on a single chip. It benefits from less cross-talk and interference by eliminating bonding wire inductor ( $L_{\rm wire}$ ) for system chips integration. Besides, its signal bandwidth can be increased by eliminating the bonding pad and ESD parasitic capacitance ( $C_{\rm pad1}$  and  $C_{\rm pad2}$ ) at the input node of TIA. They provide potential solutions to sustain high-speed and data-intensive platform in the future [3].

Light detection in CMOS technology is performed by a reverse-biased P/N junction diode, which is mainly comprised of the substrate to well junction and diffusion to well junction. As the penetration depth (16.7  $\mu$ m) of the 850-nm light into silicon is much deeper than the shallow well or diffusion region, a large portion of carriers are generated in the substrate and lead to slowly diffusive currents, which limit the operating speed of photo detector to tens of MHz range.

Typically, the bandwidth of OEIC can be enhanced to achieve high-speed operation by getting rid of the slowly diffusive carriers in the photo detector [8]–[17]. From technology aspect, this approach can be achieved by using SOI [9] or BiCMOS [10] process, but it requires non-standard CMOS technology and additional cost. [11] proposes a CMOS photo detector comprising of diffusion/well junctions and employing deep  $N_{\rm well}$  for  $P_{\rm substrate}$  diffusive carrier isolation. However, the photo detector exhibits an 8X larger parasitic capacitance that impedes high-speed operation. To reduce the parasitic capacitance of the CMOS photo diodes, [12] employs a  $P_{\rm diffusion}/N_{\rm well}$  PD with the active region of 16.54  $\mu m$  by 16.54  $\mu m$ , which is only 1/9 the cross-sectional area of a multi-mode fiber. But it also suffers from the degradation of responsivity.

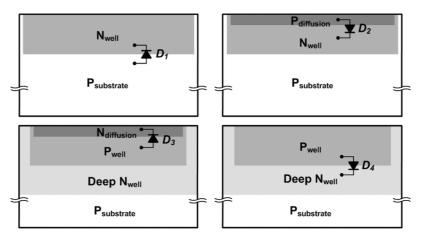

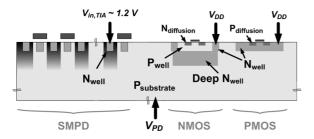

Fig. 2. P/N photo diodes in generic triple-well CMOS technology.

On the other hand, the PD bandwidth can also be compensated with an equalizer from circuit prospective [10], [15]–[17]. However, due to the slowly roll-off characteristic of the CMOS-PD frequency response [17], a high-order and sophisticated equalizer is required for practical usage under PVT variations.

To realize a high-speed CMOS optical receiver, a meshed spatially-modulated photo detector (SMPD) is proposed in this design. Compared to conventional strip SMPD [8], [13]–[16], it increases the effectiveness of slow-carrier cancellation by equalizing the diffusive distance. A common shortage of SMPD is its relatively lower responsivity, it demands more stringent noise performance for the succeeding amplification stage. In this paper, a low-noise TIA with nested feedback is also proposed to achieve the design goal.

This paper is organized as follows. Section II describes the photo detectors in CMOS technology, including conventional P/N photo diodes, the strip SMPD, and the proposed meshed SMPD. Section III describes the detail circuit implementation of this 10-Gb/s OEIC. Section IV summarizes the measurement results, and Section V gives a conclusion.

#### II. CMOS PHOTO DETECTORS

## A. Conventional P/N Junction Photo Diodes

Fig. 2 shows the conventional P/N junction PDs in CMOS technology. The depletion regions for photo sensing in  $D_1$ ,  $D_2$ ,  $D_3$ , and  $D_4$  are composed of  $P_{\rm substrate}/N_{\rm well}$ ,  $P_{\rm diffusion}/N_{\rm well}$ ,  $P_{\rm well}/N_{\rm diffusion}$ , and  $P_{\rm well}/deep\ N_{\rm well}$  junctions respectively.

As  $D_1$  is illuminated, the depletion region generates fast drift current whereas the neutral P-region and N-region generate slow diffusion current. Because the depth for the  $N_{\rm well}$  region is shallow ( $< 3~\mu \rm m$ ) from the silicon surface and the absorption length of silicon is about 16.7  $\mu \rm m$  at 850-nm wavelength, there is approximately only 16% of the photon absorption in the well region, and a large portion of photocurrent is generated in the  $P_{\rm substrate}$  region, which leads to slow diffusion current. It severely limits the bandwidth of  $D_1$ . To eliminate the diffusive current generated in the  $P_{\rm substrate}$  region,  $D_2$ ,  $D_3$ , and  $D_4$  are surrounded by  $N_{\rm well}$  or deep  $N_{\rm well}$  to achieve wider bandwidth.

Under the reversed biased-voltage of 1.2 V, the octagon PDs (from  $D_1$  to  $D_4$ ) with the span of 55  $\mu$ m have capacitances of

Fig. 3. (a) Top view and (b) cross-sectional view of a strip SMPD.

299 fF, 1952 fF, 1773 fF, and 1233 fF respectively by simulation. In spite of bandwidth improvement of  $D_2$ ,  $D_3$ , and  $D_4$ , their shallower P-region and N-region with heavier doping concentration result in lower responsivity, and introduce larger junction capacitance to the TIA. On the contrary,  $D_1$  has a better responsivity [17] and smallest intrinsic parasitic capacitance. To circumvent its bandwidth limitation, spatially-modulated layout topology with  $P_{\rm substrate}$  to  $N_{\rm well}$  junction PD is proposed.

# B. Strip SMPD

Fig. 3 shows the layout view and cross-sectional view of strip SMPD, which is composed of a row of  $P_{\rm substrate}$  to  $N_{\rm well}$  junction photo detectors alternately covered and uncovered with

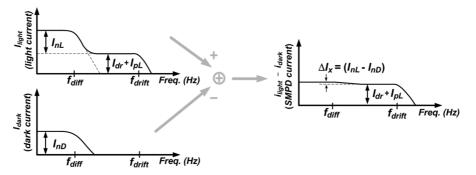

Fig. 4. Frequency response of a spatially-modulated PD.

light-blocking materials, such as metal layers. The covered detectors are named dark detectors, while the uncovered detectors are named light detectors. As the slow diffusive carriers from  $P_{\rm substrate}$  diffuse in all directions, the light detectors capture the fast drift carriers and slow diffusive carriers, while the dark detectors capture only the slow diffusive carriers. Fig. 4 depicts the photo current components of the light detectors and dark detectors. By applying the outputs of dark and light detectors to a differential TIA, the slowly diffusive carriers can be partially removed. Let  $I_{nL}$  and  $I_{nD}$  respectively represent the electron diffusion current of the light and dark detectors in the  $P_{\rm substrate}$  neutral region,  $I_{pL}$  be the hole diffusion current in the Myell neutral region, and  $I_{dr}$  be the drift current in the depletion region. The differential photo current of SMPD can be expressed as  $(I_{\rm light}-I_{\rm dark})$

$$I_{\text{light}} - I_{\text{dark}} = (I_{nL} + I_{dr} + I_{pL}) - I_{nD}$$

$$= (I_{nL} - I_{nD}) + I_{dr} + I_{pL}$$

(1)

Since  $I_{dr}$  is a high-speed component and  $I_{pL}$  also has wide-bandwidth response thanks to shallow diffusion depth, the remaining differential current component  $(I_{nL} - I_{nD})$  would determine the overall PD bandwidth according to (1). By applying this spatially-modulated layout topology, the -3-dB bandwidth of strip SMPD can be increased from about 10 MHz to 850 MHz [15]. However, it is still insufficient for multi-Gb/s operations.

# C. Meshed SMPD

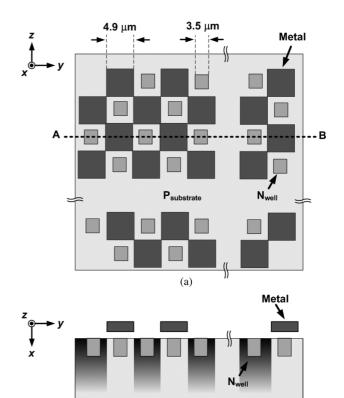

In order to more effectively cancel the slowly diffusive carriers, this paper proposes two-dimensionally meshed SMPD architecture. The layout view and cross-sectional view of the meshed SMPD are shown in Fig. 5(a) and Fig. 5(b) respectively. A meshed SMPD consists of a mesh of photo detectors alternatively covered and uncovered by light blocking metal layer. Compared to the prior art using a strip SMPD layout scheme, the slow diffusive carriers generated from P<sub>substrate</sub> can be more equally captured by the neighbored dark detectors. Also, the meshed structure reduces the distance that photo carriers drift. Thus, it benefits from smaller R-C delay and wider intrinsic bandwidth. As a result, high-speed optical detection can be achieved by the proposed meshed SMPD, but at the expense of reduced responsivity because a large portion of carriers are slowly diffusive and removed by using the spatially-modulated layout topology.

Fig. 5. (a) Top view and (b) cross-sectional view of a meshed SMPD.

(b)

On the other hand, to alleviate the reflectivity of optical light incident to the detectors so as to improve its responsivity, passivation layers above the active region of SMPD are removed. By using the impedance-transformation approach [18], the effective impedance (Z) and the reflectance (r) of the photo detector can be derived as

$$Z = \eta_D \frac{\eta_{Si} \cos(kd) + i\eta_D \sin(kd)}{\eta_D \cos(kd) + i\eta_{Si} \sin(kd)}$$

(2)

$$r = \left| \left( \frac{Z - \eta_0}{Z + \eta_0} \right)^2 \right| \tag{3}$$

where  $\eta_D$ ,  $\eta_{Si}$ , and  $\eta_o$  respectively represent the intrinsic impedance of dielectric layers, silicon substrate, and air; k and d are the wave-number and thickness of the dielectric layers. With 850-nm incident light, theoretical calculations show that

10

Fig. 6. Integration of the SMPD and transistors in CMOS technology.

the reflectance (r) is around 0.13 and can be reduced to 0.05 by removing the passivation layers.

Besides, the responsivity can also increased by applying a high reverse-biased voltage over the meshed SMPD. It enlarges the depletion region at both the horizontal and vertical junctions, so as to generate more drift carriers. Since the slowly diffusive carriers are generated in the neutral  $P_{\rm substrate}$  region farther away from  $N_{\rm well}$ , they can be more equally captured by the light and dark detectors.

However, a high reverse-biased voltage over the SMPD may induce high substrate noise current. To circumvent this issue, all the active circuits are surrounded by voltage islands isolated by deep  $N_{\rm well}$  and  $N_{\rm well}$ . Another concern arisen from high reverse-biased voltage is the junction-breakdown issue. As shown in Fig. 6, the cathode of SMPD is connected to the input node of TIA is about 1.2 V. For a PD reverse-biased voltage of 14.2 V, the  $P_{\rm substrate}$  region is biased at -13 V and the maximum reverse-biased voltage happens at the  $P_{\rm substrate}/N_{\rm well}$  (or deep  $N_{\rm well}$ ) junction, which is around 14.8 V  $(1.8-(-13)\ V)$ . Thus, the applicable PD reverse-biased voltage is limited by the tolerable junction breakdown voltage in CMOS technology.

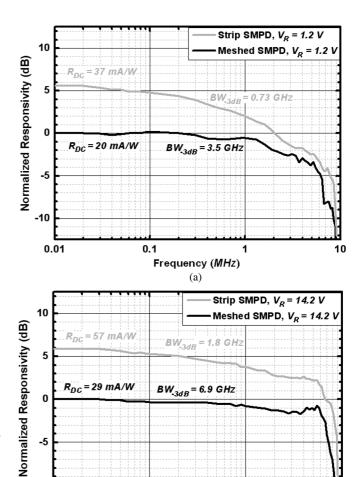

To investigate the effects of reverse-biased voltage  $(V_R)$  on the responsivity and bandwidth of CMOS PD,  $V_R$  of 1.2 V and 14.2 V are applied. Their performance is characterized using an optical receiver with chip on board assembly. The in-band gain variation is caused by the series bonding inductor during measurement. The measured frequency responses of the strip and meshed SMPDs are illustrated in Fig. 7. In the strip SMPD, the strips of  $P_{\text{substrate}}/N_{\text{well}}$  detectors are all 2.1- $\mu$ m wide, separated by a 1.4  $\mu$ m wide  $P_{well}$  region, where the width with minimum design rules is implemented. The light and dark detectors interleave within an octagon of 55  $\mu$ m  $\times$  55  $\mu$ m to comply with the diameter of multi-mode optical fiber. On the other hand, the light and dark detectors of the meshed SMPD are composed of  $3.5 \ \mu m \times 3.5 \ \mu m$  squares with N<sub>well</sub> spacing of 1.4  $\mu m$ . The light and dark junction diodes interleave in both Y and Z directions, as is illustrated in Fig. 5.

To evaluate the PDs' performance, their responsivity-bandwidth product is chosen as a figure of merit. Compared to the conventional strip SMPD, the meshed SMPD has a better responsivity-bandwidth product which can be improved by 2.6X and 2.0X under a reverse-biased voltage of 1.2 V and 14.2 V respectively. For the meshed SMPD, its responsivity is 20 mA/W in the low-voltage mode, and is boosted to 29 mA/W in the high-voltage mode. It demonstrates that the responsivity can be improved by 1.5X by increasing  $V_R$ .

Fig. 7. Measured frequency responses of strip and meshed SMPD under the reverse-biased voltage of (a) 1.2 V and (b) 14.2 V respectively.

Frequency (MHz)

0.1

0.01

Table I summaries the performance of SMPDs and a commercial PD (TPD-8D12-052). For CMOS PDs, the strip SMPD has a larger responsivity though, its -3-dB bandwidth is much lower. On the contrary, the meshed SMPD under a reverse-biased voltage of 14.2 V has  $f_{-3\mathrm{dB}}$  of 6.9 GHz, which is suitable for 10-Gb/s operation without an equalizer. Besides, the intrinsic PD capacitance is compatible to that of the commercial PD.

## III. RECEIVER CIRCUITS DESIGN

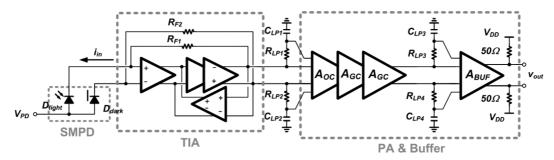

The architecture of the 10-Gb/s optical receiver is shown in Fig. 8, which integrates an on-chip meshed SMPD, a fully-differential TIA, followed by an input offset compensator  $(A_{OC})$ , two stages of voltage gain cells  $(A_{GC})$ , and a current-mode output buffer  $(A_{BUF})$ . The TIA converts tiny photo current generated from the meshed SMPD to a voltage signal of several millivolts, whose output voltage is further coupled to the post-limiting amplifier to enlarge the signal to a digital level of more than 400 mV. Since the SMPD's responsivity is only 29 mA/W, no automatic gain control circuit is needed. For a

Fig. 8. Proposed CMOS OEIC with the meshed SMPD.

TABLE I Comparison of SMPDs and Commercial PD for  $\lambda=850~\mathrm{nm}$

| Diode Type                  | Tech.        | Responsivity<br>(mA/W) | f. <sub>3dB</sub><br>(GHz) | C <sub>PD</sub> <sup>(1)</sup><br>( <b>fF</b> ) | V <sub>R</sub><br>(V) |

|-----------------------------|--------------|------------------------|----------------------------|-------------------------------------------------|-----------------------|

| Strip SMPD                  | 0.18-µm CMOS | 37                     | 0.73                       | 368                                             | 1.2                   |

| Strip SMPD                  | 0.18-µm CMOS | 57                     | 1.8                        | 213                                             | 14.2                  |

| Meshed SMPD                 | 0.18-µm CMOS | 20                     | 3.5                        | 354                                             | 1.2                   |

| Meshed SMPD                 | 0.18-µm CMOS | 29                     | 6.9                        | 206                                             | 14.2                  |

| TPD-8D12-052 <sup>(2)</sup> | GaAs         | 650                    | 9                          | 220                                             | 1.5                   |

- (1): CMOS SMPDs' CPD are simulated by HSPICE.

- (2): PIN PD, 10-Gb/s photo diode from True-Light Corp.

short-distance interconnect application, the targeted input sensitivity is -6 dBm, and the corresponding input-referred noise current should be less than 1  $\mu$ A<sub>rms</sub> for bit-error rate (BER) of less than  $10^{-12}$ . To alleviate the noise contributed from the post amplifier, the TIA is designed to provide as high conversion gain as possible, which is 66 dB $\Omega$  in this design. On the other hand, the -3-dB bandwidth of the TIA is designed to be around 7.0 GHz as a compromise between input-referred noise and ISI [19]. Also, the post amplifier provides conversion gain of 22 dB and -3-dB bandwidth of 10 GHz.

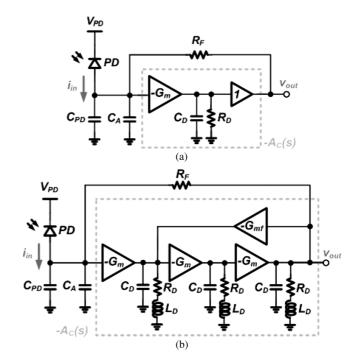

# A. Trans-Impedance Amplifier

Typically, a high-sensitivity TIA is based on a common-source amplifier with shunt-shunt feedback. As shown in Fig. 9(a),  $C_A$  and  $C_D$  denote input and output capacitances of the core amplifier  $A_C(s)$ ,  $C_{\rm PD}$  is the PD's parasitic capacitance. Given that  $R_F \gg R_D$  and  $C_{\rm IN} = C_{\rm PD} + C_A$ , the TIA gain  $(T_z)$  can be derived as

$$T_Z(s) \approx \frac{R_F}{\frac{R_F C_{\rm IN} C_D}{g_m} s^2 + \frac{R_F C_{\rm IN} + R_D C_D}{g_m R_D} s + 1} \tag{4}$$

The corresponding natural frequency  $(\omega_n)$  and damping factor  $(\delta)$  can be shown as

$$\omega_n = \sqrt{\frac{g_m}{R_F C_{\rm IN} C_D}} \tag{5}$$

$$\varsigma = \frac{1}{2} \frac{R_F C_{\rm IN} + R_D C_D}{\sqrt{g_m R_D^2 R_F C_{\rm IN} C_D}} \tag{6}$$

For a maximally-flat gain response ( $\delta=0.707$ ), the -3-dB bandwidth ( $\omega_{-3\mathrm{dB}}$ ) of the TIA can be derived as

$$\omega_{-3\text{dB}} = \frac{\sqrt{2}g_m R_D}{R_F C_{\text{IN}}} \tag{7}$$

Fig. 9. (a) Shunt-shunt feedback TIA and (b) proposed nested-feedback TIA.

and the dominant pole frequency,  $\omega_p = (R_D C_D)^{-1}$ , of the core amplifier should be at least  $\sqrt{2}\omega_{-3\mathrm{dB}}$ .

On the other hand, the input-referred noise spectral density  $(\overline{I_{\text{in,TIA}}^2})$  can be derived as [19]

$$\overline{I_{\text{in,TIA}}^2} = \frac{4kT}{R_F} + \frac{1}{R_F^2} \left( \frac{4kT}{g_m} + \frac{4kT}{g_m^2 R_D} \right)$$

(8)

According to (8), a low-noise TIA demands a high open-loop gain core amplifier  $(g_m R_D)$  and the closed-loop gain  $(R_F)$  should be as high as possible. To achieve the targeted bandwidth  $(\omega_{-3\mathrm{dB}})$ , the voltage gain of core amplifier should be increased as well. Both lead to a narrower dominant pole frequency  $(\omega_p)$ , which imposes severe trade-off between high sensitivity, high gain, and wide bandwidth TIA design.

In this design, the  $C_{\rm PD}$  and  $C_A$  are about 220 fF and 45 fF respectively, a 10-Gb/s, 66-dB $\Omega$  TIA demands a core amplifier with -3-dB bandwidth of more than 10 GHz and voltage gain of more than 24 dB. The corresponding gain bandwidth product is about 160 GHz, which is very challenging to be implemented in 0.18- $\mu$ m CMOS technology with device  $f_T$  of only 50 GHz [5].

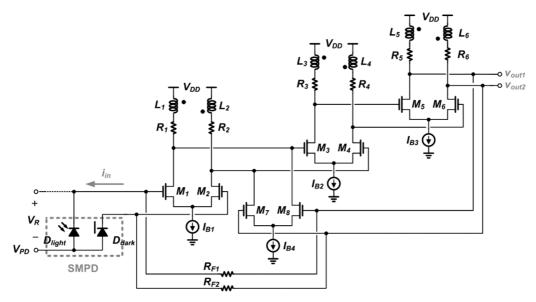

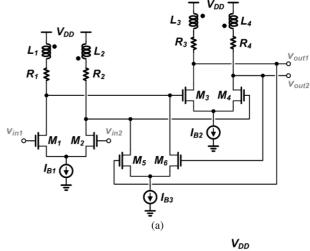

Fig. 10. Circuit schematic of proposed TIA

To overcome the bottleneck, this paper proposes a TIA incorporating both active and passive nested feedback with transformer shunt peaking. Fig. 9(b) illustrates the circuit architecture. The inner loop is a voltage amplifier composing of another trans-conductance gain stage  $(G_{\rm m})$  followed by a transimpedance amplifier with active feedback  $(G_{mf})$ . The outer loop comprising the passive feedback resistor  $(R_F)$  performs the current to voltage conversion.

Fig. 10 shows the detailed circuit schematic of the nested-feedback TIA. The photo currents generated from the light and dark detectors are applied to the differential input of the TIA to perform current subtraction. Let  $g_m$  denote the trans-conductance of  $M_1$  to  $M_6$ ,  $g_{mf}$  be the trans-conductance of  $M_7$  and  $M_8$ ,  $R_D$  be the resistance of  $R_1$  to  $R_6$ ,  $L_D$  be the inductance of  $L_1$  to  $L_6$ , and  $C_D$  be the parasitic capacitance at the drain node of  $M_1$  to  $M_6$ , the transfer function of the proposed TIA's core amplifier can be derived as

$$A_C(s) = \frac{g_m}{g_{mf}} \left( 1 + \frac{1}{g_{mf} g_m^2 Z_D^3(s)} \right)^{-1} \tag{9}$$

where

$$Z_D(s) = \frac{R_D + sL_D}{1 + sC_DR_D + s^2C_DL_D}$$

(10)

and the transfer function of the proposed TIA can be derived as

$$T_Z(s) = \frac{v_{\text{out}}(s)}{i_{\text{in}}(s)} = \frac{R_F}{1 + (1 + sC_{\text{IN}}R_F)A_C^{-1}(s)}$$

(11)

By choosing  $g_m \gg g_{mf}$ ,  $(A_c)^{-1}$  approaches zero and the TIA conversion gain  $(T_z)$  can be approximated as

$$T_Z = \frac{R_F}{1 + A_C^{-1}} \approx R_F \tag{12}$$

According to (10), shunt-peaking technique extends the bandwidth of core amplifier by introducing a zero and an additional pole at higher frequency. For a maximally-flat response,  ${\cal L}_D$  can be chosen as

$$L_D = \frac{R_D^2 C_D}{2.41} \tag{13}$$

and the corresponding bandwidth can be improved by 1.72X compared to that without inductive peaking [20]. Under this criterion,  $Z_D(s)$  can be simplified as

$$Z_D(s) \approx \frac{R_D}{1 + 0.58sC_DR_D} \tag{14}$$

As the -3-dB bandwidth of the  $Z_D^3(s)$  is reduced by 0.51X compared to  $Z_D(s)$  [5], to simplify the derivation,  $Z_D^3(s)$  can be approximated as

$$Z_D^3(s) \approx \frac{R_D^3}{1 + 1.14sC_DR_D}$$

(15)

By substituting (15) into (9) and (11), a high-order TIA frequency response can be approximated as a two pole model without losing much design insight.

$$T_{Z}(s) = \frac{R_{F}}{1 + \frac{2}{g_{m}^{3}R_{D}^{3}} + \left(\frac{2C_{1N}R_{F}}{g_{m}^{3}R_{D}^{3}} + \frac{1.14C_{D}R_{D}}{g_{m}^{3}R_{D}^{3}}\right)s + \frac{1.14C_{D}R_{D}C_{1N}R_{F}}{g_{m}^{3}R_{D}^{3}}s^{2}}$$

$$(16)$$

The corresponding natural frequency  $(\omega_n)$  and damping factor  $(\delta)$  can be derived as

$$\omega_n \approx g_m R_D \sqrt{\frac{g_m}{1.14 C_D C_{\rm IN} R_F}} \tag{17}$$

$$\varsigma = \frac{C_{\text{IN}}R_F + 0.57C_DR_D}{\sqrt{(g_m^3 R_D^3 + 2)(1.14C_{\text{IN}}R_F C_D R_D)}}$$

(18)

Compare (17) to (5),  $\omega_n$  can be improved by a factor of  $g_m R_D$ , which is about 3.5 (V/V) in this design.

For adequate voltage swing, the output common-mode voltage of the differential pairs in Fig. 10 is about 0.5 V.

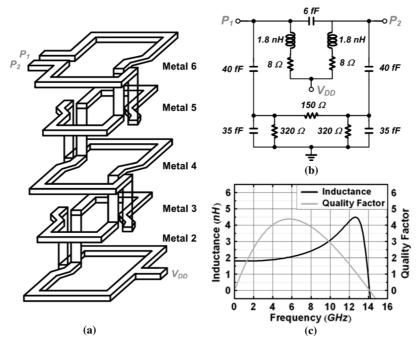

Fig. 11. 3-D symmetric transformer (a) architecture, (b) lumped model, and (c) EM simulation results.

TABLE II

DESIGN VALUES FOR THE NESTED-FEEDBACK TIA

| Parameter          | Value           |  |  |

|--------------------|-----------------|--|--|

| W/L <sub>1-6</sub> | 48 μm / 0.18 μm |  |  |

| W/L <sub>7-8</sub> | 1.4 μm /0.18 μm |  |  |

| I <sub>B1-3</sub>  | 7 mA            |  |  |

| I <sub>84</sub>    | 0.2 mA          |  |  |

| R <sub>1-6</sub>   | 145 Ω           |  |  |

| R <sub>F1-2</sub>  | 2100 Ω          |  |  |

| L <sub>1-6</sub>   | 1.8 nH          |  |  |

Table II summarizes the device parameters. In order to minimize chip area occupied by the peaking inductors, all the differential inductors ( $L_1-L_2$ ,  $L_3-L_4$ , and  $L_5-L_6$ ) are realized as 3-D transformer [7]. Fig. 11 shows the architecture, lumped model, and the parameters of the 3-D transformer by EM simulation. The inductance in each branch is 1.8 nH and the self-resonant frequency is 14.1 GHz. Although its quality factor is relatively low by using lower metal layer, this is not an issue for shunt-peaking application with a maximally-flat gain response.

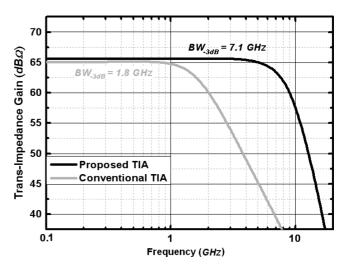

Fig. 12 illustrates the performance comparisons between the proposed TIA and a conventional TIA. By applying the nested-feedback technique, a core amplifier with 25.5 dB voltage gain and 11 GHz -3-dB bandwidth can be achieved. Thus, the proposed TIA bandwidth can be extended to 7.1 GHz with a high gain of 66 dB $\Omega$ . On the contrary, a conventional TIA faces severely direct trade-off between gain and bandwidth performance. Under the same gain requirement, the achievable -3-dB is less than 2 GHz.

Fig. 12. Simulated magnitude response of proposed and conventional TIA.

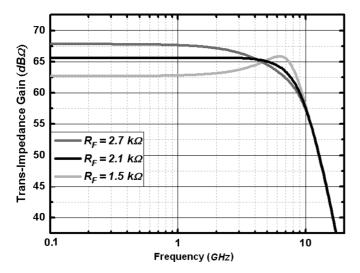

Another concern related to multi-path feedback is the gain peaking issue. The phenomena are investigated by changing  $R_F$  and the corresponding frequency responses are summarized in Fig. 13. It reveals that a smaller  $R_F$  results in a wider bandwidth but a higher gain peaking, which also corresponds with (17) and (18). As a consequence, a feedback resistor  $R_F$  of 2.1  $k\Omega$  is chosen to maximize its gain and bandwidth performance without severe gain peaking.

The input-referred noise current  $\overline{I_{n,TIA}^2}$  of the TIA can be derived as

$$\overline{I_{\text{in,TIA}}^2} = \frac{8kT}{R_F} + \frac{1}{R_F^2} \left[ \overline{V_{n,SC}^2} + \frac{1}{g_m^2} \left( g_{mf}^2 \overline{V_{n,SC}^2} + g_{mf}^2 \frac{\overline{V_{n,SC}^2}}{g_m^2 R_D^2} \right) \right]$$

(19)

Fig. 13. Simulated magnitude response of TIA with different  $R_F$ .

where  $\overline{V_{n,SC}^2}$  represents the input-referred noise voltage of a single-stage source coupled pair, and can be expressed as

$$\overline{V_{n,SC}^2} = 2\left(\frac{4kT}{g_m} + \frac{4kT}{g_m^2 R_D}\right)$$

(20)

The input-referred noise current of the TIA is about 0.64  $\mu A_{\rm rms}$  by simulation.

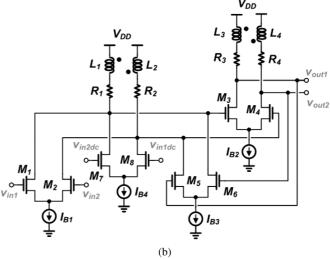

## B. Post-Limiting Amplifier

The post amplifier is composed of three stage voltage amplifiers, comprising of a subtractor followed by two voltage gain cells. Fig. 14(a) shows the circuit schematic of gain cell, which is based on Cherry-Hooper architecture with inductive peaking. By shunt-shunt feedback, all the nodes in the circuit become low impedance for wide bandwidth operations. It has been shown in [5] that the active feedback can increase the GBW of the gain cell beyond the technology  $f_T$ . Fig. 14(b) shows the input stage of the post amplifier, which functions as an input buffer as well as an offset subtractor. The input offset voltage ( $V_{\rm in1dc}$ and  $V_{\rm in2dc}$ ), which is derived from TIA output and a low pass filter, is converted to a compensation current to be subtracted from the input signal  $(V_{in1} \text{ and } V_{in2})$  by the source-coupled pair  $(M_7 - M_8)$ . Besides, to facilitate the characterization of the optical receiver without significantly introducing capacitive load to the preceding stage, an  $f_T$  doubler output buffer is adopted [19].

The number of gain stage in post amplifier is chosen as a compromise between gain and bandwidth requirements as well. Assuming each gain cell is identical and approximated by a two-pole amplifier, its conversion gain, A(s), can be described as

$$A(s) = \frac{A_S \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2} \tag{21}$$

where  $A_s$  denotes the small-signal DC gain,  $\zeta$  is the corresponding damping factor, and  $\omega_n$  is the natural frequency. Let the targeted -3-dB bandwidth of an N-stage cascaded amplifier

Fig. 14. (a) Gain cell and (b) subtractor of the post amplifier.

be  $\omega_c$ , and the total conversion gain be  $A_c$ . For a flat band response, the required gain-bandwidth product (GBW) per stage can be expressed as [4]

GBW =

$$\omega_c \times \left(\frac{1}{2^{1/N} - 1}\right)^{1/4} \times A_c^{1/N}$$

(22)

Assuming the conversion gain of subtractor is less than that of the voltage gain cell by -6 dB, and the insertion loss of the output buffer is about -5 dB, the conversion gain of each gain cell is designed to be 11 dB, so as to enlarge TIA output signal to a logic level of more than 400 mV. The bandwidth of each gain cell is 14 GHz to minimize ISI induced data jitter.

The input-referred noise current of the optical receiver can be expressed as

$$\overline{I_{\text{in,RX}}^2} = \frac{8kT}{R_F} + \frac{1}{R_F^2} \left[ \overline{V_{n,Ac}^2} \right] + \frac{1}{R_F^2} \left[ \overline{V_{n,PA}^2} \right]$$

(23)

where  $\overline{V_{n,Ac}^2}$  and  $\overline{V_{n,PA}^2}$  respectively represent the input-referred noise voltage of the TIA's core amplifier and the post amplifier. As the input sensitivity of the CMOS OEIC is mainly limited by the responsivity of the photo detector, it can be seen from (23) that  $R_F$  should be chosen as large as possible.

Fig. 15. Die photo of proposed OEIC with meshed SMPD.

However, the overall bandwidth becomes severely limited and it burns much more power to sustain the bandwidth. In this design, about 50% input-referred noise current contributed from the feedback resistor  $R_F$ , 30% from the TIA's core amplifier, and 20% comes from the post amplifier.

### IV. EXPERIMENTAL RESULTS

The receiver IC is mounted on a printed-circuit board (PCB) for measurement. The pulse pattern generator (Anritsu MU181020A) sends a PRBS  $2^7-1$  test pattern to modulate an 850-nm VCSEL (New Focus) as a light source. The eye diagrams are captured by Agilent 86100C and the BER performance are characterized using Anritsu MU181040A. To measure the input power sensitivity accurately, an optical power attenuator (OZ Optics) is adopted, and the extinction ratio is 7.4 dB.

The chip micrograph is shown in Fig. 15. Fabricated in a generic 0.18- $\mu$ m CMOS technology, this chip size is 0.95 mm by 0.8 mm. The meshed SMPD is laid out in an octagon, and the area is  $55 \times 55 \ \mu m^2$  to comply with the diameter of the multimode fiber. The SMPDs are powered with a variable supply voltage,  $V_{\rm PD}$ , (from 0 V to -13 V), while the receiver circuits are operated under the 1.8-V supply. The total power dissipation is 145 mW, among which 27 mW is consumed by the output buffer. By cascading TIA and post-limiting amplifier on a single chip, the optical receiver provides a conversion gain of 88 dB $\Omega$ . With an 18- $\mu$ A<sub>pp</sub> input current, the optical receiver is capable of delivering 450-mV<sub>pp</sub> differential voltage swings to 50- $\Omega$  output loads directly.

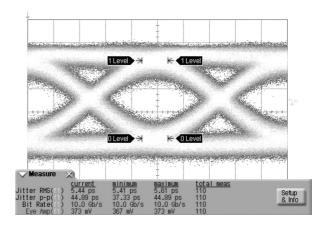

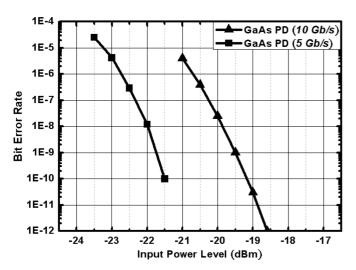

Fig. 16 shows the bit error rate performance of CMOS OEIC with strip and meshed SMPD respectively. Under a reverse-biased voltage of 14.2 V, the input sensitivity of OEIC with meshed SMPD is -6 dBm for the BER of less than  $10^{-11}$ . On the other hand, as the strip SMPD has a better responsivity compared to the meshed SMPD, for a 5-Gb/s operation, the input sensitivity of the OEIC with strip and meshed SMPD are -10.5 and -8.5 dBm respectively. Fig. 17 shows the measured 10-Gb/s eye diagram at the sensitivity level. With -6 dBm incident optical power, the measured data jitter is 5.44 ps<sub>rms</sub> (44.89 ps<sub>pd</sub>). The data eye becomes fussy with strip SMPD. By

Fig. 16. BER performance of OEIC with the SMPDs under reverse-biased  $14.2\ V$

Fig. 17. Measured 10-Gb/s eye diagram of the OEIC with a meshed SMPD under -6-dBm input optical power level.

a single pole approximation, the -3-dB bandwidth can be estimated based on the rise time  $t_{\rm rise}$ , (from 10% to 90%), which can be described as

$$f_{H-3\text{dB}} = \frac{0.35}{t_{\text{rise}}} \tag{24}$$

Based on eye diagram in Fig. 17, it suggests that the overall bandwidth is around 5.8 GHz, which is limited by the rise time of light source (VCSEL), SMPD, and receiver all together.

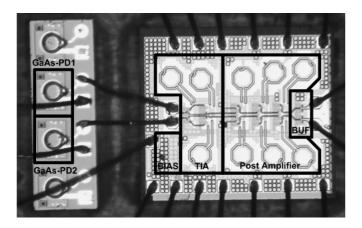

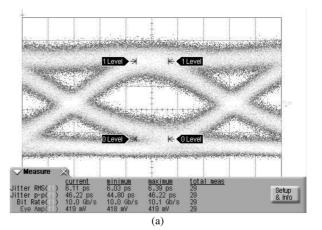

In order to fully characterize the performance of the receiver circuit itself, an external GaAs PIN PD (TPD-8D12-052) with responsivity of 0.65 A/W for 850-nm optical wavelength is also applied to identical OEIC without on-chip CMOS detector. The chip micrograph is shown in Fig. 18. Fig. 19 summarizes the BER performance. With the external PD, the input sensitivity level of the optical receiver at 10 Gb/s is -18.6 dBm and -19 dBm for BER of less than  $10^{-12}$  and  $10^{-10}$  respectively. Fig. 20 shows the measured eye diagrams at 10 Gb/s with incident optical power at sensitivity (-18.6 dBm) and overloaded (-5 dBm) power level, and the corresponding data jitter are 6.11 ps<sub>rms</sub> (46.22 ps<sub>pp</sub>) and 3.76 ps<sub>rms</sub> (21.66 ps<sub>pp</sub>)

Fig. 18. Dies of commercial PDs and proposed optical receiver.

Fig. 19. BER performance of this optical receiver with a commercial PD.

respectively. Thus, the minimum input current  $(I_{\rm in,mim})$  of the optical receiver at BER of less than  $10^{-12}$  can be calculated as

$$I_{\rm in, mim} = R \times P_{\rm sen} = 0.65 (A/W) \times 13.8 (\mu W) \approx 9(\mu A)$$

(25)

where the PD's responsivity (R) is 0.65 A/W, and the input optical power  $(P_{\rm sen})$  is -18.6 dBm.

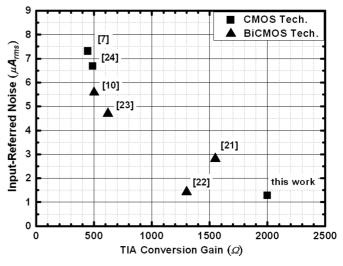

Fig. 21 shows the performance benchmark of the prior art at 10-Gb/s operations [7], [10], [21]–[24]. It can be seen that the TIAs with higher conversion gain generally have lower input-referred noise current and thus better input sensitivity. The input-referred noise current  $(I_{n,in})$  is calculated by

$$I_{n,in} = \frac{I_{\text{in,min}}}{Q} \tag{26}$$

where  $I_{\rm in,min}$  is the minimum input current for a designated BER, and Q is the quality factor which reflects its BER performance [19] ( $Q \sim 6$  for  $BER = 10^{-9}$  and  $Q \sim 7.04$  for BER =  $10^{-12}$ ). Our proposed TIA has a conversion gain of 66 dB $\Omega$  and input-referred noise of 1.27  $\mu$ A, which manifests superior performance compared to the prior art.

Table III summarizes the integrated OEIC performance comparisons. For fully integrated CMOS OEICs, this work mani-

Fig. 20. Measured eye diagram with input optical power of (a) -18.6 dBm and (b) -5 dBm.

Fig. 21. Performance benchmark of 10-Gb/s OEIC and receiver amplifier in terms of gain and input-referred noise. ([10] and this work are OEICs.)

fests the highest conversion gain and operating speed, and is the first one capable of operating up to 10 Gb/s in generic CMOS technology without an adopting sophisticated equalizer. That of [10] has a better sensitivity and is also capable of operating up to 10 Gb/s. However, it is fabricated in BiCMOS process and consumes more than twice DC power.

| Spec.              | [11]                         | [17]                         | [16]                          | [10]                         | This work                  |

|--------------------|------------------------------|------------------------------|-------------------------------|------------------------------|----------------------------|

| PD Type            | Lateral PIN <sup>(1)</sup>   | PN                           | Strip SMPD                    | PIN <sup>(3)</sup>           | Meshed SMPD <sup>(4)</sup> |

| PD Capacitance     | 1600 fF                      | 280 fF                       | 1000 fF                       | 60 fF                        | 206 fF                     |

| PD Bandwidth       | 1.9 GHz                      | < 0.01 GHz                   | 0.5 GHz                       | 2.2 GHz                      | 6.9 GHz                    |

| PD Responsivity    | 73 mA/W                      | 560 mA/W                     | 5 mA/W                        | 260 mA/W                     | 29 mA/W                    |

| Architecture       | TIA + LA                     | TIA + EQ(2)                  | TIA + EQ + LA                 | TIA + EQ + LA                | TIA + LA                   |

| Data Rate          | 2.5 Gbps                     | 3 Gbps                       | 4.5 Gbps                      | 11 Gbps                      | 10 Gbps                    |

| PRBS Type          | 2 <sup>31</sup> -1           | 2 <sup>31</sup> -1           | 2 <sup>7</sup> -1             | 2 <sup>31</sup> -1           | 2 <sup>7</sup> -1          |

| TIA Gain           | 1 kΩ                         | 0.85 kΩ                      | 4.5 kΩ                        | 0.5 kΩ                       | 2 kΩ                       |

| Sensitivity at BER | -4.5 dBm at 10 <sup>-9</sup> | -19 dBm at 10 <sup>-11</sup> | -3.4 dBm at 10 <sup>-12</sup> | -8.9 dBm at 10 <sup>-9</sup> | -6 dBm at 10 <sup>-9</sup> |

| Power              | 138 mW                       | 34 mW                        | 74 mW                         | 310 mW                       | 145 mW                     |

| Technology         | 0.18-µm CMOS                 | 0.18-µm CMOS                 | 0.13-µm CMOS                  | 0.5-µm BiCMOS                | 0.18-µm CMOS               |

TABLE III OEIC Performance Comparison for  $\lambda=850~\mathrm{nm}$

- (1): 6-V supply power is needed to bias a lateral PIN.

- (2): single-ended.

- (3): 17-V supply power is needed to bias a PIN.

- (4): -13-V supply power is needed to bias a meshed SMPD.

# V. CONCLUSION

This paper presents monolithic CMOS optical receiver, integrating a photo detector, a trans-impedance amplifier, and a post-limiting amplifier on a single chip. A novel meshed SMPD and shunt-peaking techniques are adopted for multi-Gb/s operations. For 5-Gb/s and 10-Gb/s operations, the input sensitivity of the CMOS OEIC is -8.5 dBm and -6 dBm respectively. With external GaAs photo detector, the measured input sensitivity of the optical receiver is -19 dBm at 10 Gb/s. The developed techniques show strong potential to be applied in multi-lanes intra-chip, inter-chip, and backplane interconnects.

## ACKNOWLEDGMENT

The authors would like to thank TSMC for chip fabrication.

#### REFERENCES

- S.-C. Liu et al., "Optical sub-assembly solution for single fiber optical HDMI connector," in Proc. SPIE, 2009, vol. 7229, pp. 722906-1-722906-10.

- [2] N. Ledentsov, "Ultra-high speed components for data networks," VI Systems GmbH, Berlin, Germany, Aug. 2009 [Online]. Available: http://www.v-i-systems.com/\_data/inow-2009-vis.pdf

- [3] J. Ziller *et al.*, "Light Peak overview," Intel Corp., San Jose, CA, Jan. 2010 [Online]. Available: http://www.intel.com/go/lightpeak/

- [4] A. K. Petersen et al., "Front-end CMOS chipset for 10 Gb/s communication," in *IEEE Radio Frequency Integrated Circuits (RFIC) Symp. Dig.*, 2002, pp. 93–96.

- Dig., 2002, pp. 93–96.

[5] S. Galal et al., "10-Gb/s limiting amplifier and laser/modulator driver in 0.18-μm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 12, pp. 2138–2146, Dec. 2004.

- [6] B. Analui et al., "Multi-pole bandwidth enhancement technique for trans-impedance amplifiers," in Proc. IEEE Eur. Solid-State Circuits Conf. (ESSCIRC), 2002, pp. 303–306.

- [7] W.-Z. Chen et al., "A 1.8-V, 10-Gb/s fully integrated CMOS optical receiver analog front-end," *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp. 1388–1398, Jun. 2005.

- [8] C. Hermans et al., "A high-speed 850-nm optical receiver front-end in 0.18-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 41, no. 7, pp. 1606–1614, Jul. 2006.

- [9] S. M. Csutak et al., "High-speed monolithically integrated silicon optical receiver fabricated in 130-nm CMOS technology," *IEEE Photon. Technol. Lett.*, vol. 14, no. 4, pp. 516–518, Apr. 2002.

- [10] R. Swoboda et al., "11 Gb/s monolithically integrated silicon optical receiver for 850 nm wavelength," in *IEEE Int. Solid-State Circuits Conf.* (ISSCC) Dig. Tech. Papers, 2006, pp. 904–911.

- [11] W.-Z. Chen et al., "A 2.5 Gbps CMOS fully integrated optical receiver with lateral PIN detector," in Proc. IEEE Custom Integrated Circuits Conf. (CICC), 2007, pp. 293–296.

- [12] T. K. Woodward et al., "1-Gb/s integrated optical detectors and receivers in commercial CMOS technologies," *IEEE J. Sel. Topics Quantum Electron.*, vol. 5, no. 2, pp. 146–156, Mar./Apr. 1999.

- [13] C. Rooman et al., "Asynchronous 250 Mb/s optical receivers with integrated detector in standard CMOS technology for optocoupler applications," *IEEE J. Solid-State Circuits*, vol. 35, no. 7, pp. 953–958, Jul. 2000

- [14] M. Jutzi et al., "2-Gb/s CMOS optical integrated receiver with a spatially modulated photodetector," *IEEE Photon. Technol. Lett.*, vol. 17, no. 6, pp. 1268–1270, Jun. 2005.

- [15] W.-Z. Chen et al., "A 3.125 Gbps CMOS fully integrated optical receiver with adaptive analog equalizer," in Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC), 2007, pp. 396–399.

- [16] F. Tavernier et al., "Power efficient 4.5 Gbit/s optical receiver in 130 nm CMOS with integrated photodiode," in Proc. IEEE Eur. Solid-State Circuits Conf. (ESSCIRC), 2008, pp. 162–165.

- [17] S. Radovanović et al., "A 3-Gb/s optical detector in standard CMOS for 850-nm optical communication," *IEEE J. Solid-State Circuits*, vol. 40, no. 8, pp. 1706–1717, Aug. 2005.

- [18] S. M. Sze, Physics of Semiconductor Devices. New York: Wiley, 2007.

- [19] B. Razavi, Design of Integrated Circuits for Optical Communications. New York: McGraw-Hill, 2003.

- [20] T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits. Cambridge, MA: Cambridge Univ. Press, 1998.

- [21] J. C. Huang et al., "Broadband transimpedance amplifier in 0.35-μm SiGe BiCMOS technology for 10-Gb/s optical receiver analog front-end application," in Proc. IEEE Custom Integrated Circuits Conf. (CICC), 2008, pp. 245–248.

- [22] A. Schild et al., "Amplifier array for 12 parallel 10 Gb/s optical-fiber links fabricated in a SiGe production technology," in *IEEE Radio Fre*quency Integrated Circuits (RFIC) Symp. Dig., 2002, pp. 89–92.

- [23] T. D. Ridder et al., "A 2.7 V 9.8 Gb/s burst-mode TIA with fast automatic gain locking and coarse threshold extraction," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2008, pp. 220–221.

- [24] W.-Z. Chen et al., "A 90-dBΩ 10-Gb/s optical receiver analog front-end in a 0.18-μm CMOS technology," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 3, pp. 358–365, Mar. 2007.

Shih-Hao Huang was born in Taiwan in 1983. He received the B.S. degree in electric and control engineering and the M.S. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2005 and 2008, respectively. Currently, he is working toward the Ph.D. degree in electronics engineering at the same university.

His research interests focus on integrated circuit designs for high-speed CMOS optical communication systems.

**Wei-Zen** Chen received the B.S., M.S., and Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1992, 1994, and 1999, respectively.

From 1999 to 2002, he was with the Department of Electrical Engineering, National Central University, Chung-Li, Taiwan. Since 2002, he joined the Department of Electronics Engineering, National Chiao-Tung University, where he is now a Full Professor. He is the Deputy Executive Director of the National SoC Program (NSoC) and coordinator

of National Project of Intelligent Electronics (NPIE) in Taiwan, and also serves as IEEE Solid-State Circuit Society Taipei Chapter chairman starting from 2008

Dr. Chen's research focuses on mixed-signal integrated circuit for wireless and wireline communication systems. He is a member of Phi Tau Phi honorary scholar society, technical program committee member of the IEEE Custom Integrated Circuits Conference (CICC), IEEE Asian Solid-State Circuit Conference (A-SSCC), and IEEE ASICON.

Yu-Wei Chang was born in Taiwan in 1980. He received the B.S. degree in electronics engineering from National Chiao-Tung University, Taiwan, in 2002, the M.S. degree in biophotonics engineering from National Yang-Ming University, Taiwan, in 2004, and the Ph.D. degree in electronics engineering from National Chiao-Tung University in 2009. He also received the Ph.D. Dissertation Award from National Chiao-Tung University.

His research interests include optoelectronic devices and integrated circuits for applications in high-speed networks and biomedical diagnosis.

Dr. Chang is a member of the Phi Tau Phi Scholastic Honor Society.

Yang-Tung Huang was born in Taiwan in 1955. He received the B.S. degree in electrophysics and the M.S. degree in electronics from National Chiao-Tung University, Hsinchu, Taiwan, in 1978 and 1982, respectively, and the Ph.D. degree in electrical and computer engineering (minor in optical sciences) from the University of Arizona, Tempe, in 1990.

He is a Professor and the chairman of the Department of Electronics Engineering and the Institute of Electronics, and a Joint Professor at the Department of Biological Science and Technology, National

Chiao-Tung University. He is also the program leader of Electronics and Photonics for National Program on Nano Technology (NPNT). He has been the Director of the Institute of Electronics for three years, the Director of Semiconductor Research Center for two years, and the Director of Nano Facility Center for four years. His current research includes integrated optics, photonic crystal waveguides, bio-optoelectronics, and optoelectronic switching networks.

Dr. Huang received the Outstanding Research Award from the National Science Council in 1998.