# A Physical Model for the Correlation Between Holding Voltage and Holding Current in Epitaxial CMOS Latch-Up

Ming-Jer Chen, *Member, IEEE*, Hun-Shung Lee, *Student Member, IEEE*, Jyh-Huei Chen, Chin-Shan Hou, *Member, IEEE*, Chaun-Sheng Lin, and Yeh-Ning Jou

Abstract—A new physical model concerning the holding points for latch-up in epitaxial CMOS structures is established by combining the lateral p-i-n high level injection and the vertical BJT base push-out formula. The model matches adequately the correlation between holding voltage and holding current extensively measured from different combinations of temperatures, epitaxial layer thicknesses, and anode-to-cathode spacings. This is also the case for the two-dimensional device simulations. A quantitative analysis based on the model consistently judges the crucial role of the vertical BJT base push-out width in producing the observed correlation. The potential merits of the model in extended applications are outlined.

## I. INTRODUCTION

ASED on three different fabrication processes [1]–[3] for the epitaxial CMOS latch-up structures, Sleeter and Enlow [1] reported a new finding of a correlation between holding voltage and holding current. One interested in this correlation may raise the following questions: Does a correlation between holding voltage and holding current exist for other processes and over temperatures? What is the underlying physics? What are the implications? and What additional applications are suggested? On the other hand, a novel physically-based analytical model for the latch-up holding voltage was developed by Seitchik *et al.* [4]. In this letter, we establish a new linking between the work [1] and [4], and attempt to answer the above questions.

## II. PHYSICAL MODEL

The lateral p-i-n diode high level injection and the vertical BJT base push-out formula as cited in [4] for epitaxial CMOS latch-up have been separately modified adequately for the holding point case [5]

$$I_H = q(\mu_n + \mu_p) \frac{\eta P_0}{2} [V_H - 1V] \frac{hW}{L} + I_{\text{sub}}$$

(1)

Manuscript received November 10, 1997; revised April 8, 1998. This work was supported by the National Science Council under Contract NSC 86-2215-E-009-029.

M.-J. Chen, H.-S. Lee, J.-H. Chen, and C.-S. Lin are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan. R.O.C.

C.-S. Hou is with the Logic Technology R&D Department, Taiwan Semi-conductor Manufacturing Company, Hsinchu 300, Taiwan, R.O.C.

Y.-N. Jou is with the Reliability and Failure Analysis Department, Vanguard International Semiconductor Corporation, Hsinchu 300, Taiwan, R.O.C. Publisher Item Identifier S 0741-3106(98)05550-5.

$$h = \frac{t_{\text{epi}}}{1 + \frac{N_{\text{epi}}(V_H/2)}{\eta P_o(kT/q)}}$$

(2)

where  $V_H$  and  $I_H$  are the holding voltage and holding current, respectively;  $\mu_n$  and  $\mu_p$  are the electron and hole mobilities, respectively;  $\eta(=0.7$  throughout the work) is the calibration factor accounting for the nonuniform nature of the vertical carrier density distribution at the mid-point between anode and cathode;  $P_o$  is the surface carrier density evaluated at the mid-point; h is the vertical BJT base push-out width at the mid-point; h is the device width; h is the anode-to-cathode spacing; h is part of the h that does not traverse the whole h-region; h-region; h-region is the epitaxial layer thickness; and h-region is the dopant concentration of the low-doped epitaxial layer. By combining both equations with the common factor h-region eliminated, we obtain

$$V_H = \frac{1}{2} V + \frac{1}{2} \sqrt{1V^2 + 4\alpha^2 \beta (I_H - I_{\text{sub}})}$$

(3)

$$\alpha = \sqrt{\frac{4kT/q}{q(\mu_n + \mu_p)N_{\text{epi}}W}} \tag{4}$$

$$\beta = \frac{L}{h} \left( \frac{t_{\text{epi}}}{h} - 1 \right). \tag{5}$$

Obviously, (3) can serve as a physical model for the correlation between  $V_H$  and  $I_H$ : for  $I_H \gg I_{\rm sub}$  the  $V_H$  follows the square root of  $I_H$ , as originally observed in [1].

### III. EXPERIMENTAL AND SIMULATION EVIDENCE

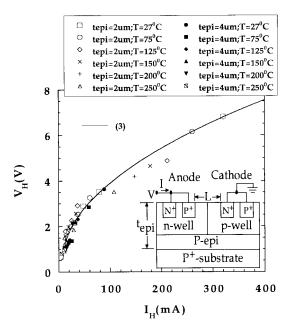

A large variety of latch-up stripe-type structures formed on a p-type epitaxial layer/p<sup>+</sup> substrate, having two different epitaxial layer thicknesses and four different anode-to-cathode spacings, were fabricated by a 0.35- $\mu$ m CMOS process. Each of the structures had the same device width  $W=30~\mu$ m. The measured doping profiles are given in [5]. By means of the three different measurement methods [5], a large amount of the latch-up I-V characteristics were produced in a wide temperature range of 27–250 °C. The holding points obtained from these I-V characteristics are depicted in Fig. 1 in terms of the scatter plot of holding voltage versus holding current. By fitting (3) to the data points in Fig. 1, the  $\alpha^2\beta$  and  $I_{\rm sub}$  were simultaneously extracted to be 0.1264 V<sup>2</sup>/mA and 10.02 mA, respectively. From Fig. 1 we can observe that almost all the

Fig. 1. The scatter plot of the measured holding voltages and currents (symbols) from two different effective epitaxial layer thicknesses of 2 and 4  $\mu$ m, four different anode-to-cathode spacings of 1.6, 2.0, 2.4, and 5  $\mu$ m, and six different temperatures of 27, 75, 125, 150, 200, and 250 °C. A curve from (3) is together plotted. The inset schematically shows the cross section of the latch-up stripe-type structures in a 0.35- $\mu$ m process.

holding points fall on or around the same curve provided by (3).

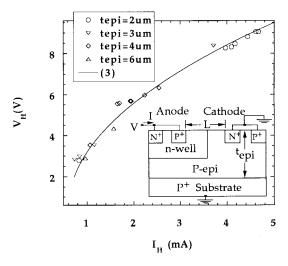

On the other hand, a two-dimensional device simulation using MEDICI was performed on the latch-up structures with the epitaxial layer thickness, the anode-to-cathode spacing, and the temperature, all as input parameters. The process parameters and the physical models were kept the same for each simulations [5]. The holding voltage and holding current obtained from all the simulated I-V characteristics are together compared in a scatter plot as shown in Fig. 2. Reproduction of the simulation data points in Fig. 2 by (3) leads to  $\alpha^2\beta=18.43~{\rm V^2/mA}$  and  $I_{\rm sub}=0.62~{\rm mA}$  for  $W=1~\mu{\rm m}$ .

The presence of the above experimental and MEDICI data as well as those from the other processes [5] indeed proves the existence of the correlation between  $V_H$  and  $I_H$ , and this correlation is essentially independent of temperature, epitaxial layer thickness, and anode-to-cathode spacing. It is specially noteworthy that the extracted  $\alpha^2\beta$  in Fig. 2 is different from that in Fig. 1. Such difference can be attributed to the different W and different  $N_{\rm epi}$  used in the model. For the latter, as schematically shown in the inset of Figs. 1 and 2,  $N_{\rm epi}=1\times10^{15}~{\rm cm}^{-3}$  in simulation structures while in 0.35- $\mu$ m process the p-well was formed on the p-epi layer, thus effectively increasing the value of  $N_{\rm epi}$ . Then according to (4) the value of  $\alpha^2\beta$  in 0.35  $\mu$ m process is greatly lowered as compared with the simulation case.

# IV. QUANTITATIVE ANALYSIS AND DISCUSSION

To explain why in the above work the factor  $\alpha^2\beta$  can be regarded as a constant, a quantitative analysis was performed

Fig. 2. The scatter plot of the simulated holding voltages and currents (symbols) for four different epitaxial layer thicknesses of 2, 3, 4, and 6  $\mu$ m, four different anode-to-cathode spacings of 4, 6, 8, and 10  $\mu$ m, and five different temperatures of 27, 75, 150, 200, and 250 °C. A curve from (3) is together plotted. The inset schematically shows the cross section of the latch-up simulation structures.

TABLE I THE FOUR DIFFERENT STRUCTURES AND THE CORRESPONDING SIMULATED VALUES OF  $V_H$  ,  $I_H$  ,  $P_o$  , and h

| t <sub>epi(um)</sub> | L(um) | V <sub>H</sub> (V) | IH(mA) | P <sub>O</sub> (cm <sup>-3</sup> ) | h*(um) | h**(um) |

|----------------------|-------|--------------------|--------|------------------------------------|--------|---------|

| 4                    | 10    | 6.3                | 2.50   | 2.0 ×10 <sup>17</sup>              | 2.04   | 2.23    |

| 4                    | 8     | 3.5                | 1.06   | 9.7 x10 <sup>16</sup>              | 1.92   | 2.14    |

| 2                    | 6     | 9.0                | 4.67   | 4.0 ×10 <sup>17</sup>              | 1.01   | 1.02    |

| 2                    | 4     | 2.8                | 0.83   | 8.4 ×10 <sup>16</sup>              | 0.92   | 0.94    |

<sup>\*</sup> the location of the carrier density equal to 10 Nepi

on the simulation structures. The results are presented in Table I that lists the simulated h values for  $t_{\rm epi}=4~\mu{\rm m}$  with two different L of 8 and 10  $\mu{\rm m}$  as well as for  $t_{\rm epi}=2~\mu{\rm m}$  with two different L of 4 and 6  $\mu{\rm m}$ . The simulation results show that an increase in  $t_{\rm epi}$  is followed by an increase in h. One of the plausible interpretations is that the corresponding decreased holding voltage or equivalently the decreased collector to base voltage for a vertical BJT predominantly gives rise to an increase in the base push-out width [6]. To provide better insights, we rewrite (5) to

$$h = \frac{L(-1 + \sqrt{1 + (4\beta t_{\rm epi}/L)})}{2\beta}.$$

(6)

Equation (6) transparently describes the effects of changing  $t_{\rm epi}$  or L on h for a given  $\beta$ . The calculated h values using (6) corresponding to Table I are listed in Table II. In Table II, we also list the calculated h from (2) directly using the simulated  $P_o$  and  $V_H$  listed in Table I both as input parameters. From Table II, we can observe that all the calculated values of h

<sup>\*\*</sup> the width of the flat portion of the potential profile

#### TABLE II

The Four Different Structures and the Corresponding Calculated Values of h and  $I_H$ . In Calculation,  $\alpha=2.08~{\rm V/mA^{1/2}}$  and  $\beta=4.25~{\rm for}~\mu_n=1000~{\rm cm^2/V\cdot S},~\mu_p=500~{\rm cm^2/V\cdot S},~N_{\rm epi}=1\times 10^{15}~{\rm cm^{-3}}, W=1~\mu{\rm m},$  and  $kT/q=0.025\,86~{\rm V}$

| t <sub>epi(um)</sub> | L (um) | h*(um) | h**(um) | IH***(mA) |

|----------------------|--------|--------|---------|-----------|

| 4                    | 10     | 2.11   | 2.13    | 2.53      |

| 4                    | 8      | 1.96   | 2.00    | 0.78      |

| 2                    | 6      | 1.12   | 1.24    | 7.06      |

| 2                    | 4      | 0.98   | 1.05    | 0.69      |

<sup>\*</sup> from (6)

from two different sources (2) and (6) are not only close to each other, but also to the simulated values in Table I. The corresponding  $I_H$  values are also given in both tables, from which the calculated  $I_H$  by (1) using the simulated  $P_o$  and  $V_H$  as input parameters appears to be comparable with the simulated ones. The above self-consistent analysis thus judges the vertical BJT base push-out width as the cause of the observed correlation.

The potential merits of the model in extended applications have been in part demonstrated elsewhere [5] in terms of a scaling law for the holding voltage [7] as well as a guideline projected for the low voltage CMOS integrated circuits. Another application is creation of a new physically-based analytical model for high-temperature latch-up, which significantly advances the work of [4] and [5] in this area and will be reported in the future.

#### REFERENCES

- [1] D. J. Sleeter and E. W. Enlow, "The relationship of holding points and a general solution for CMOS latchup," *IEEE Trans. Electron Devices*, vol. 39, pp. 2592–2599, Nov. 1992.

- [2] A. G. Lewis, R. A. Martin, T. Y. Huang, J. Y. Chen, and M. Koyanagi, "Latchup performance of retrograde and conventional n-well CMOS technologies," *IEEE Trans. Electron Devices*, vol. ED-34, pp. 2156–2164, Oct. 1987.

- [3] G. Krieger, "Bipolar transistor action and transport effects relating to CMOS latchup," *IEEE Trans. Electron Devices*, vol. ED-34, pp. 1719–1728, Aug. 1987.

- [4] J. A. Seitchik, A. Chatterjee, and P. Yang, "An analytic model of holding voltage in epitaxial CMOS," *IEEE Electron Device Lett.*, vol. EDL-8, pp. 157–159, Apr. 1987.

- [5] M. J. Chen, C. S. Hou, P. N. Tseng, R. Y. Shiue, H. S. Lee, J. H. Chen, J. K. Jeng, and Y. N. Jou, "A compact model of holding voltage for latch-up in epitaxial CMOS," in *IEEE Int. Reliab. Phys. Symp. Proc.*, 1997, pp. 339–345.

- [6] S. K. Ghandhi, Semiconductor Power Devices. New York: Wiley, 1977, pp. 162–170.

- [7] A. G. Lewis, R. A. Martin, T. Y. Huang, J. Y. Chen, and R. H. Bruce, "Scaling CMOS technologies with constant latch-up immunity," in *Symp. VLSI Technol.*, 1986, pp. 23–24.

<sup>\*\*</sup> from (2) with  $P_{O}$ , and  $V_{H}$  from Table I

<sup>\*\*\*</sup> from (1) with Po, VH, and h from Table I