國 立 交 通 大 學

奈米科技研究所

碩 士 論 文

高功函數鋁金屬奈米晶體於非揮發性記憶體之

應用

Study of High Work Function Metal Nanocrystals

in Nonvolatile Memory Applications

指導教授：許鉅宗 博士

研究 生：朱昶龍

中 華 民 國 九 十 七 年 六 月

# 高功函數铱金屬奈米晶體於非揮發性記憶體之應用

## Study of High Work Function Iridium Metal Nanocrystals in Nonvolatile Memory Application

研究學生：朱 昶 龍

Student : Chang-Lung Chu

指導教授：許 鈺 宗

Advisor : Jeng-Tzong Sheu

國立交通大學

奈米科技研究所

碩士論文

A Thesis

Submitted to Institute of Nanotechnology

College of Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of Master

in

Nanotechnology

June 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年六月

# 高功函數鎵金屬奈米晶體於非揮發性記憶體之應用

學生：朱昶龍

指導教授：許鉅宗 博士

國立交通大學 奈米科技 學系（研究所）碩士班

## 摘要

近來非揮發性奈米晶體記憶體被用來廣泛的研究來克服傳統的浮動閘極記憶體的極限。利用奈米晶體被用來克服傳統浮動閘極元件在微縮時遇到電荷流失的問題、容許更薄的穿隧氧化層、更低的工作電壓，及更好的容忍度和電荷保存能力。比較半導體奈米晶體和金屬奈米晶體兩者，金屬奈米晶體作為浮動閘極有許多優點：對於電容特性改變量、較多種可供利用並設計的功函數、在費米能階周圍有高的狀態密度以及不易受載子侷限效應所引起能階擾動等等。本研究，利用鎵(Ir)取代浮動閘極的地位的原因有兩個，一個是它擁有較高的功函數，另一個則是對於非揮發性記憶體的製程應用中具有良好熱穩定性。Ir 金屬形成奈米晶體的方法為透過超薄的金屬膜和快速退火(RTA)的製程來完成其製備。本研究針對鎵奈米晶體的形成條件以及研究製作在  $\text{SiO}_2$  與  $\text{HfO}_2$  層中置入 Ir 奈米晶體後的電容結構的特性，做了一系列實驗和討論。並在論文最後試著將此技術應用在記憶體元件上。

# Study of High Work Function Iridium Metal Nanocrystals in Nonvolatile Memory Application

Student : C. L. Chu

Advisors : Dr. J. T. Sheu

Department ( Institute ) of Nanotechnology

National Chiao Tung University

## ABSTRACT

Recently, nonvolatile memory with nanocrystals (NCs) has been widely studied to overcome limitations of conventional floating gate memory. The use of NCs as distributed floating gates minimized the problems of charge loss encountered in conventional floating-gate devices, allowing thinner tunnel oxide and, thereby, a smaller working voltage, better endurance and retention, and faster program/erase (P/E) speed.

Compared to the semiconductor NCs, metallic NCs as floating gates possesses several advantages, such as larger change of electric capacity, stronger coupling with the conduction channel, a wide range of available work functions, higher density of states around the Fermi level, and a smaller energy perturbation due to carrier confinement.

In this thesis, iridium was chosen as floating gates for its properties of high work function and thermal stability for NVM application. The metallic thermal agglomeration was investigated using thin iridium films under different rapid thermal annealing (RTA). Mechanism of nanocrystals formation has been investigated. A MOS capacitor with iridium NCs (Ir-NCs) embedded in  $\text{SiO}_2$  and  $\text{HfO}_2$  layers has been demonstrated for investigation of electrical properties. Furthermore, incorporation of Ir-NCs into process of MOSFETs has been demonstrated for the feasibility of this study in NVM application.

## 誌謝

本論文能順利完成，最感謝的就是我的老師 許鈺宗博士讓我有機會進入碩士的生涯並且在這就學階段所提供的指導，以及讓我學習到真正做研究的方法與態度。沒有在這優良的環境下學習，我想我碩士生活的成長不會如此茁壯與順遂。

第二個最感謝的人則是 泰瑞學長。若非一路跟著學長學習和實驗，我想我的馬步無法札實；若非來自不同領域，我想我可能還是井底之蛙，始終對於電子領域畫地自限。

感謝實驗室其他的學長。家豪學長的生活經驗和故事提供我很多生活上的幫助和體認，而學長耐心解說我們的疑惑也是我到現在一直很欽佩的。 振嘉學長，當我遇到問題時會常常給我方向與指導。 柏均學長熱心的幫忙讓我學會放鬆自己。 煥恆學長的為人處事與心思細膩使我佩服不已。

感謝實驗室的同學，子訓和欣霖和奕貞。 這些一起上課打拼與實驗的日子，將是我難忘的一段回憶。這兩年的互相扶持，也讓我從你們身上學了更多，也看到更多我需要更進步的地方。

感謝實驗室所有的學弟妹，盈傑、履安、伯勳、昭睿、治廷。 這些日子的相處，總是給我很多歡笑，使我釋放壓力後能有繼續往前的力量。

最後感謝我的父母親和女友，沒有你們在我身後的支持，我可能還無法踏入這個學術的殿堂；沒有你們的陪伴，我的生活不會如此富足；沒有你們的體貼，我也無法順利走到今天的成就。你們的付出給我一路讓我勇往直前的動力，也是我向上的力量泉源。最後的最後，感謝這兩年所遇到的夥伴，要謝的人還有很多，因此我感謝緣分，謝謝大家。

# 目 錄

頁次

|                                               |     |

|-----------------------------------------------|-----|

| 中文摘要.....                                     | i   |

| 英文摘要.....                                     | ii  |

| 誌謝.....                                       | iii |

| 目錄.....                                       | iv  |

| 表目錄.....                                      | vi  |

| 圖目錄.....                                      | vii |

| 一、緒論.....                                     | 1   |

| 1-1 前言.....                                   | 1   |

| 1-1-1 浮動閘極記憶體的特性和微縮限制.....                    | 1   |

| 1-1-2 未來趨勢與微縮研究方向.....                        | 3   |

| 1-2 論文架構與文獻回顧.....                            | 6   |

| 1-3 實驗動機.....                                 | 14  |

| 二、元件使用機制與實驗流程.....                            | 15  |

| 2-1 元件機制.....                                 | 15  |

| 2-1-1 热電子注入(Hot electron injection).....      | 15  |

| 2-1-2 F-N 穿遂(Fowler-Nordheim tunneling) ..... | 15  |

| 2-2 實驗流程.....                                 | 18  |

| 2-2-1 奈米晶體形成(Nanocrystals formation).....     | 18  |

| 2-2-2 電容的製作(Capacitor).....                   | 19  |

| 2-2-3 元件的製作(Device).....                      | 20  |

| 三、奈米晶體(Nanocrystal)的特性和討論.....                | 24  |

| 3-1 奈米點的形成.....                               | 24  |

| 3-1-1 接觸角和奈米晶體的形成.....                        | 24  |

|                                             |           |

|---------------------------------------------|-----------|

| 3-1-2 機台金屬膜厚度的確認.....                       | 28        |

| 3-1-3 溫度對奈米晶體的變化.....                       | 29        |

| 3-1-4 初始金屬膜厚度對奈米晶體變化.....                   | 30        |

| 3-1-5 热處理時間對奈米晶體變化.....                     | 34        |

| 3-1-6 奈米晶體的 XPS 圖譜.....                     | 36        |

| 3-2 結論.....                                 | 38        |

| <b>四、電容(Capacitor)及元件(Device)量測與討論.....</b> | <b>39</b> |

| 4-1 電容的量測.....                              | 40        |

| 4-1-1 電容能帶設計.....                           | 40        |

| 4-1-2 金屬功函數測試.....                          | 41        |

| 4-1-3 穿遂氧化層厚度的影響.....                       | 43        |

| 4-1-4 阻絕氧化層的測漏電.....                        | 44        |

| 4-1-5 電容電性量測與分析.....                        | 47        |

| 4-1-6 F-N tunneling 的驗證.....                | 51        |

| 4-1-7 電子顯微鏡拍攝電容剖面圖.....                     | 53        |

| 4-2 元件的應用.....                              | 56        |

| 4-2-1 電子顯微鏡驗證元件上的金屬奈米點.....                 | 56        |

| 4-2-2 元件量測結果.....                           | 57        |

| <b>五、結論與未來方向.....</b>                       | <b>61</b> |

| 參考文獻.....                                   | 63        |

# 表 目 錄

|                                          |    |

|------------------------------------------|----|

| 表 1-1、ITRS PID 裡指出未來的研究趨勢以及可能發展到的尺度..... | 4  |

| 表 1-2、利用 RTA 方法所製作出來的金屬奈米晶體的比較.....      | 12 |

| 表 2-1、CHEI 和 FN-tunneling 比較.....        | 17 |

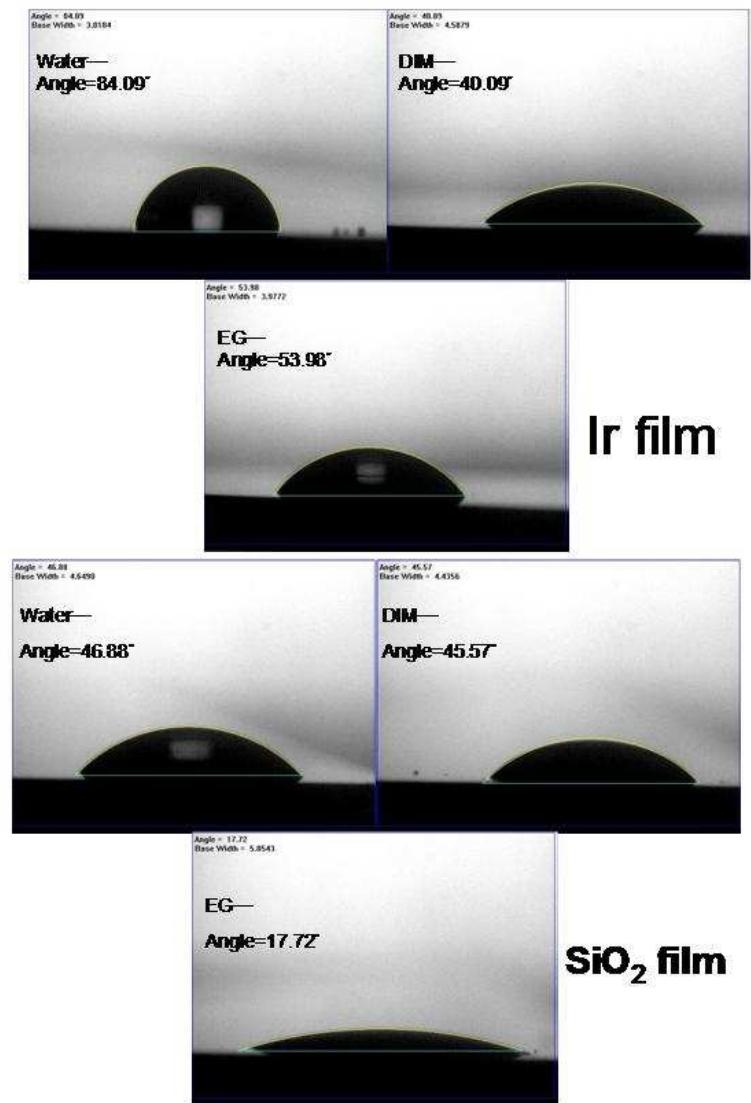

| 表 3-1、不同的膜對三個液滴所量測到的接觸角整理.....           | 25 |

| 表 4-1、Ir 不同晶向及功函數的差異.....                | 43 |

# 圖 目 錄

|                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------|----|

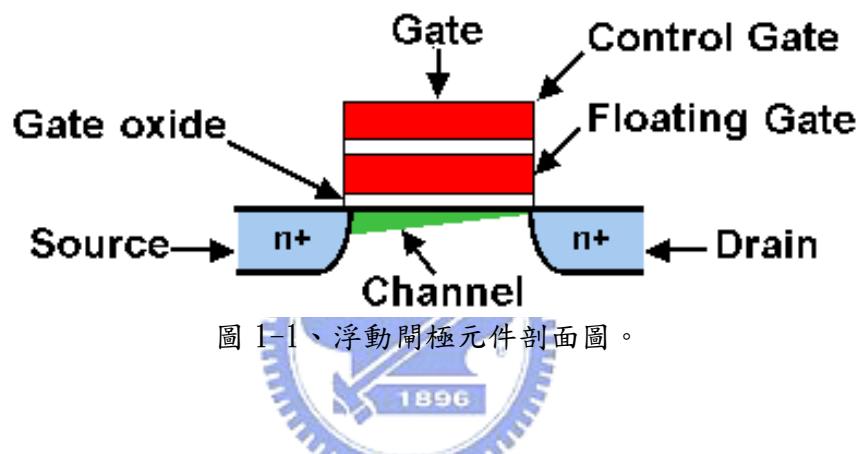

| 圖 1-1 浮動閘極元件剖面圖.....                                                                                                                   | 2  |

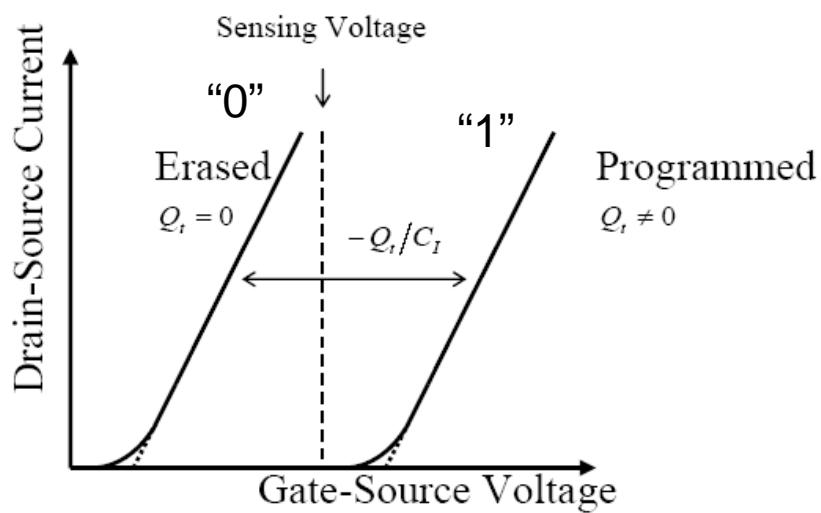

| 圖 1-2 浮動閘極元件對電流-電壓曲線 ID-VG.....                                                                                                        | 2  |

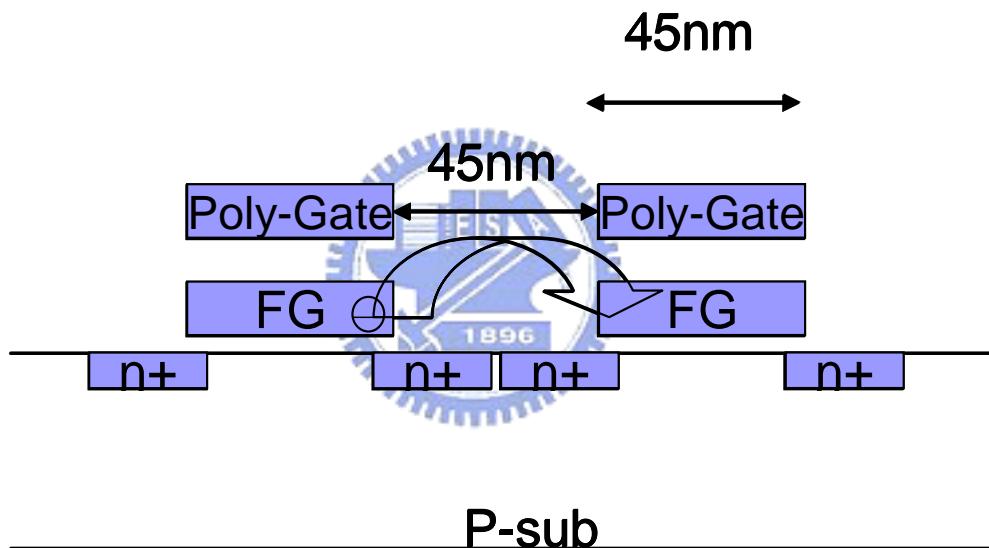

| 圖 1-3 浮動閘極在 45nm 以下產生的 coupling effect 示意圖.....                                                                                        | 3  |

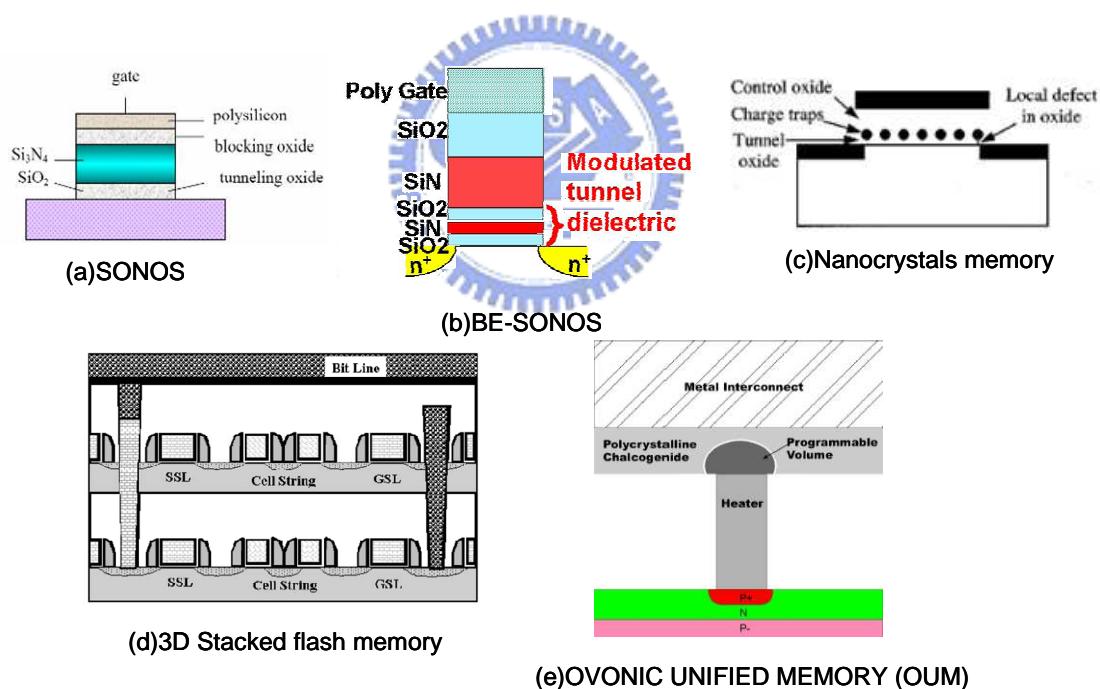

| 圖 1-4 為克服微縮問題的 Non-volatile memory 研究方向.....                                                                                           | 5  |

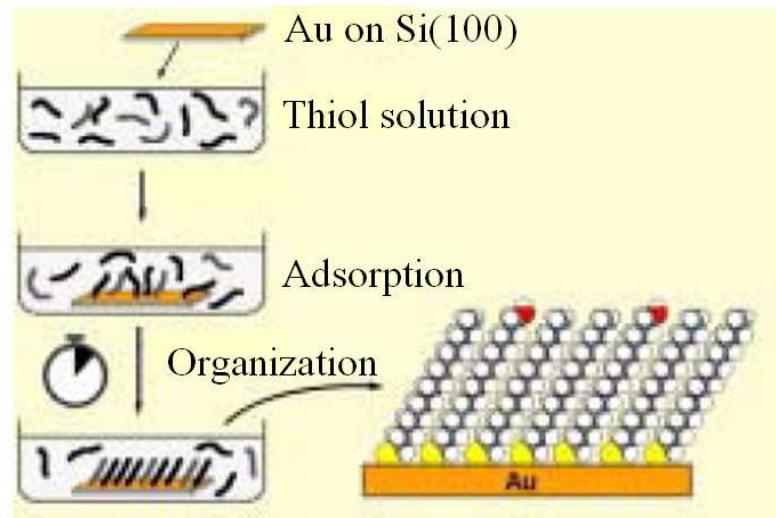

| 圖 1-5 SAM 機制示意圖.....                                                                                                                   | 7  |

| 圖 1-6 不同基材及基材厚度對 Ni film 的影響 .....                                                                                                     | 7  |

| 圖 1-7 金粒子在不同尺寸下有不同的熔點.....                                                                                                             | 8  |

| 圖 1-8 不同的初始金屬膜厚度對 Ni nanocrystals 的影響.....                                                                                             | 9  |

| 圖 1-9 Ni film 在 20nm SiO <sub>2</sub> 經過 RTA850°C 對不同退火時間的影響.....                                                                      | 9  |

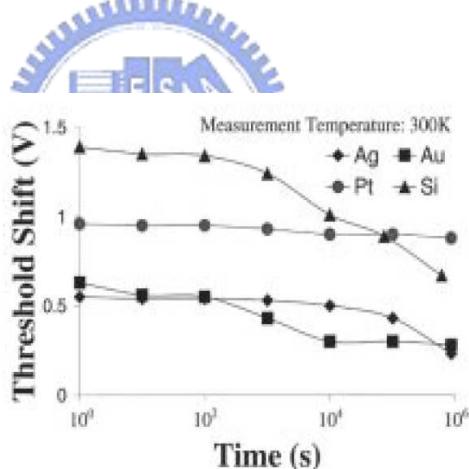

| 圖 1-10 不同金屬奈米晶體對 retention time 的效果.....                                                                                               | 10 |

| 圖 1-11 金屬奈米晶體記憶體的電流-電壓曲線.....                                                                                                          | 11 |

| 圖 1-12 Ir 4f 的訊號鋒在退火前和退火後的比較；插圖為 XPS 對於 iridium、silicon 和 oxygen 原子 depth profiles.....                                                | 13 |

| 圖 1-13 IrO <sub>2</sub> 奈米點經過退火之後對磁滯的變化插圖為 IrO <sub>2</sub> 的 TEM 圖底下為沒有 IrO <sub>2</sub> 的對照組中間插圖顯示含有 IrO <sub>2</sub> 奈米點的磁滯曲線 ..... | 13 |

| 圖 1-14 浮動閘極元件的等效電容圖.....                                                                                                               | 14 |

| 圖 2-1 上圖為 HEI 模式下圖為 FN-tunneling 模式對操作在元件的示意圖.....                                                                                     | 16 |

| 圖 2-2 F-N tunneling 在 MOS 結構的示意圖.....                                                                                                  | 17 |

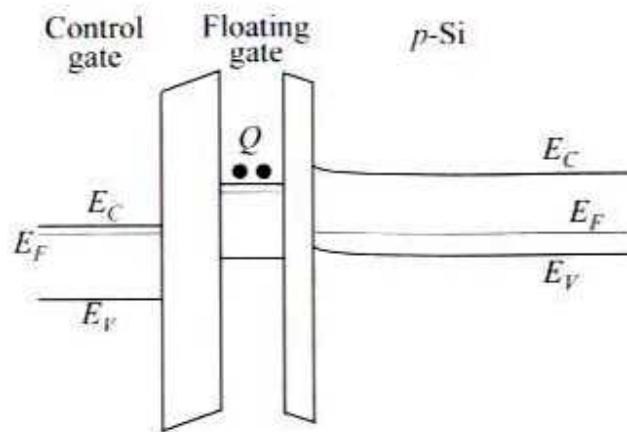

| 圖 2-3 電子侷限在 FG 的位能井之中.....                                                                                                             | 17 |

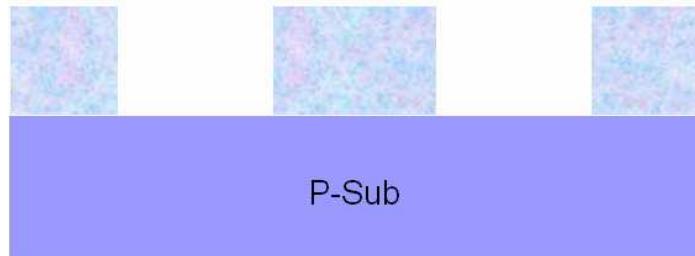

| 圖 2-4 P-Type 晶片經過 RCA clean.....                                                                                                       | 18 |

| 圖 2-5 水平爐管長 Dry oxide 8nm.....                                                                                                         | 18 |

| 圖 2-6 利用 Sputter 長 Ir 膜.....                                                                                                           | 19 |

| 圖 2-7 RTA 之後形成奈米晶體.....                                                                                                                | 19 |

| 圖 2-8 利用 E-gun 疊上 HfO <sub>2</sub> 的薄膜.....                                                                                            | 20 |

|                                                      |    |

|------------------------------------------------------|----|

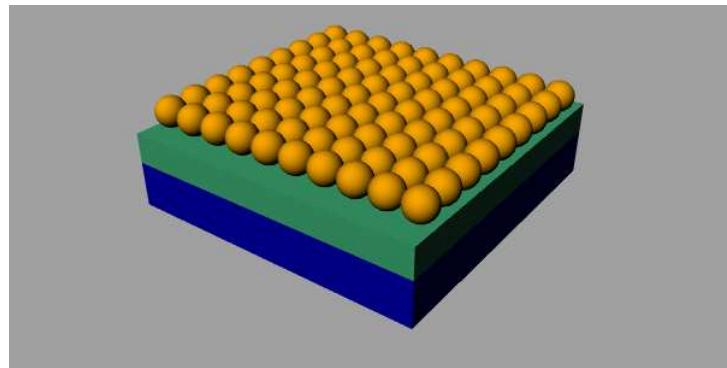

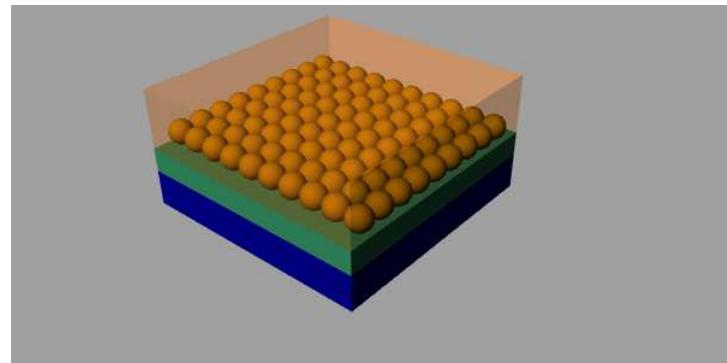

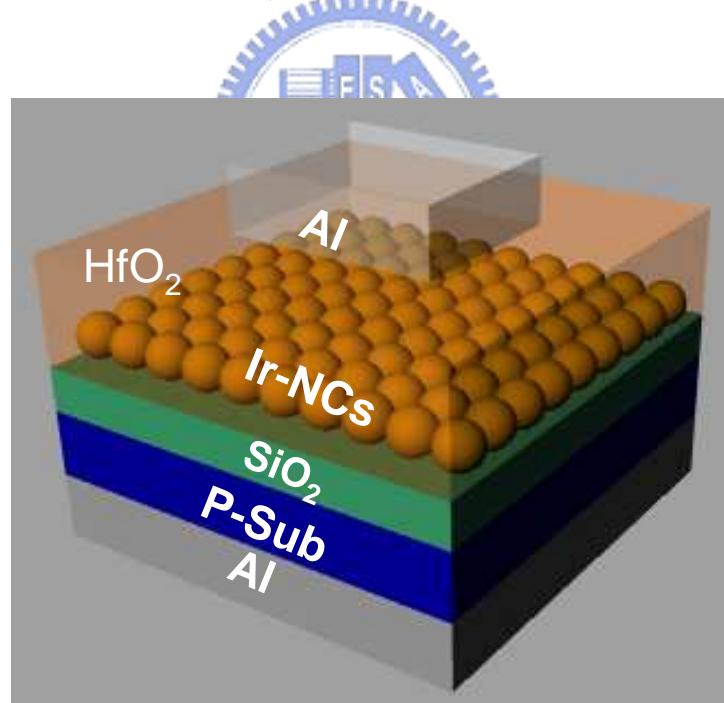

| 圖 2-9 奈米晶體電容結構示意圖.....                               | 20 |

| 圖 2-10 用水平爐管長出 $\text{SiO}_2$ 膜.....                 | 21 |

| 圖 2-11 Define S/D region.....                        | 21 |

| 圖 2-12 Implantation 之後用 RTA 做活化處理(activation).....   | 21 |

| 圖 2-13 定義出 AA 區.....                                 | 22 |

| 圖 2-14 用爐管長出 Dry oxide 6~8nm.....                    | 22 |

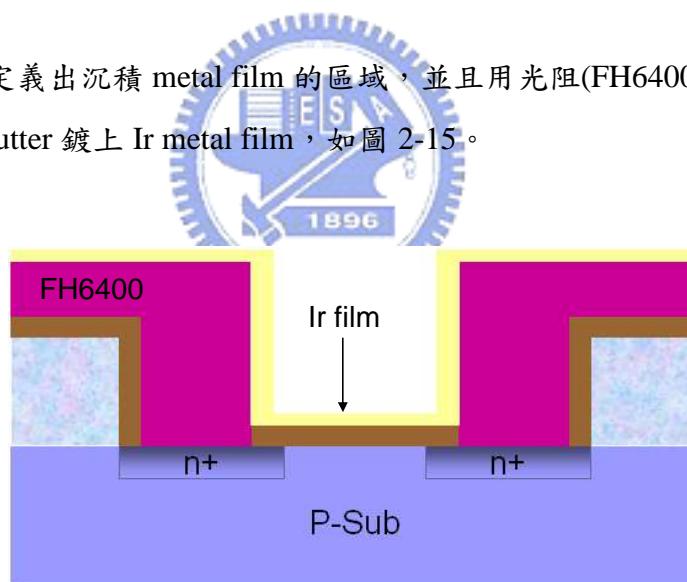

| 圖 2-15 沉積 Ir metal film.....                         | 22 |

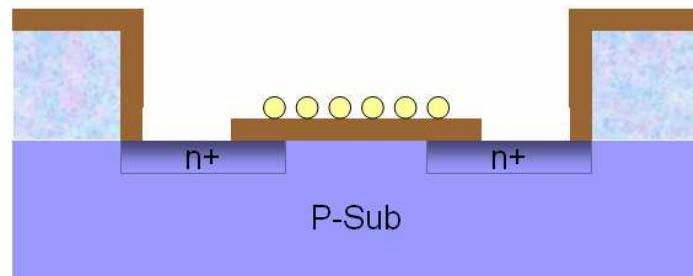

| 圖 2-16 光阻 Lift-off 後經過 RTA 製成形成奈米晶體.....             | 23 |

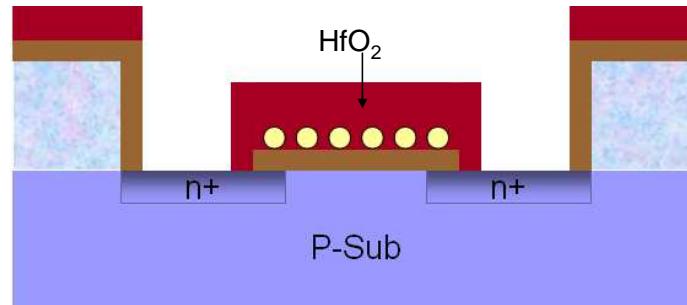

| 圖 2-17 用 E-gun 疊上阻擋層並挖開 contact hole.....            | 23 |

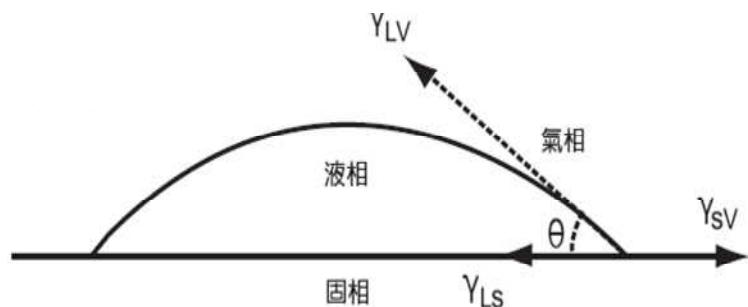

| 圖 3-1 接觸角量測的示意圖.....                                 | 24 |

| 圖 3-2 二種膜對三種液滴的接觸角量測結果.....                          | 25 |

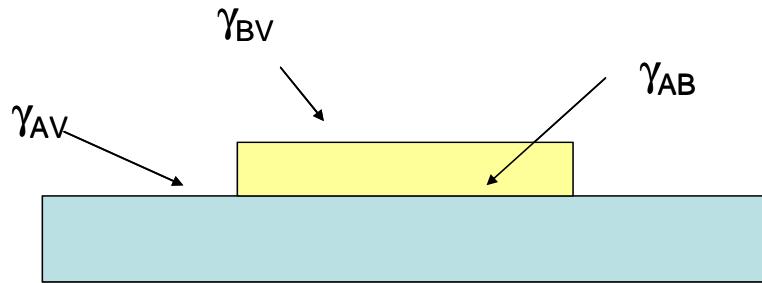

| 圖 3-3 固體和固體之間的表面張力示意圖.....                           | 27 |

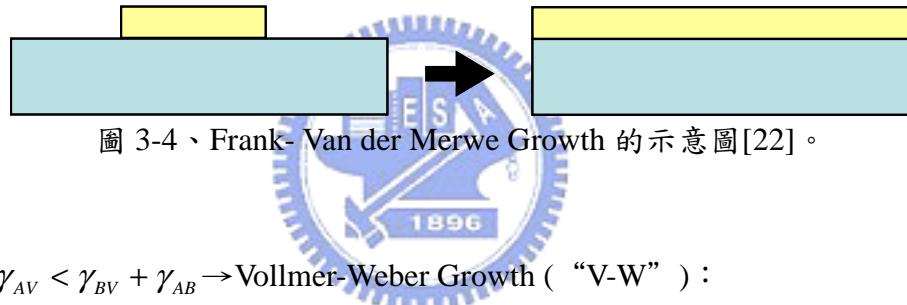

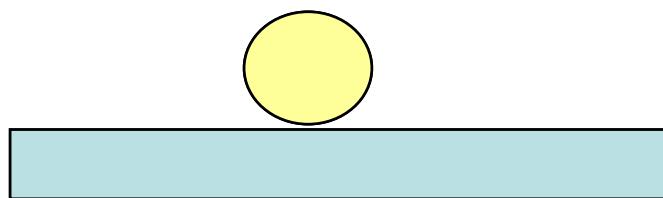

| 圖 3-4 Frank- Van der Merwe Growth 的示意圖.....          | 27 |

| 圖 3-5 Vollmer-Weber Growth 的示意圖.....                 | 27 |

| 圖 3-6 Stranski-Krastanov growth 的示意圖.....            | 28 |

| 圖 3-7 金屬膜厚度 TEM 橫剖面圖.....                            | 29 |

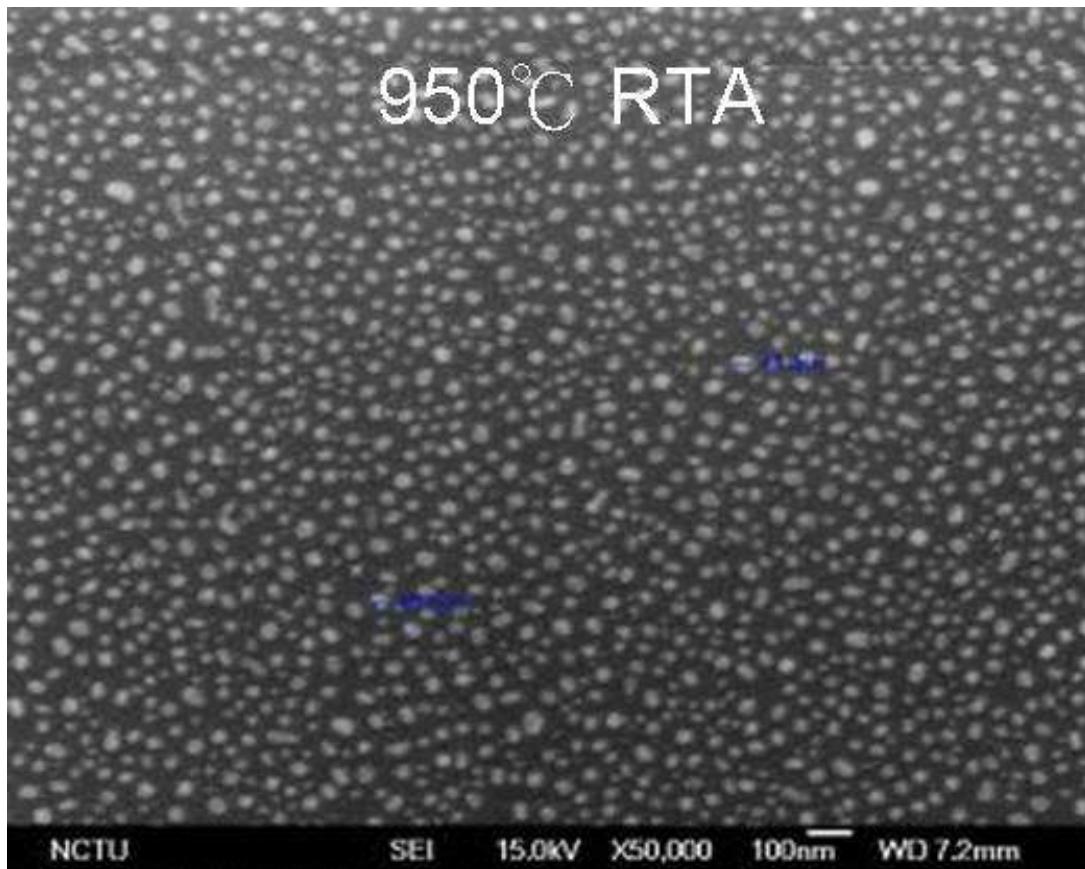

| 圖 3-8 經過 RTA 700°C、800°C 和 950°C 60s 热處理的 SEM 圖..... | 30 |

| 圖 3-9 圖 3-8(c)的五萬倍 SEM 影像圖.....                      | 31 |

| 圖 3-10 不同金屬膜厚度在 RTA 950°C 60s 热處理後 SEM 影像圖.....      | 32 |

| 圖 3-11 不同金屬膜厚度在 RTA 950°C 60s 热處理後 AFM 影像.....       | 33 |

| 圖 3-12 RTA 950°C 對於不同時間變化的 SEM 圖.....                | 35 |

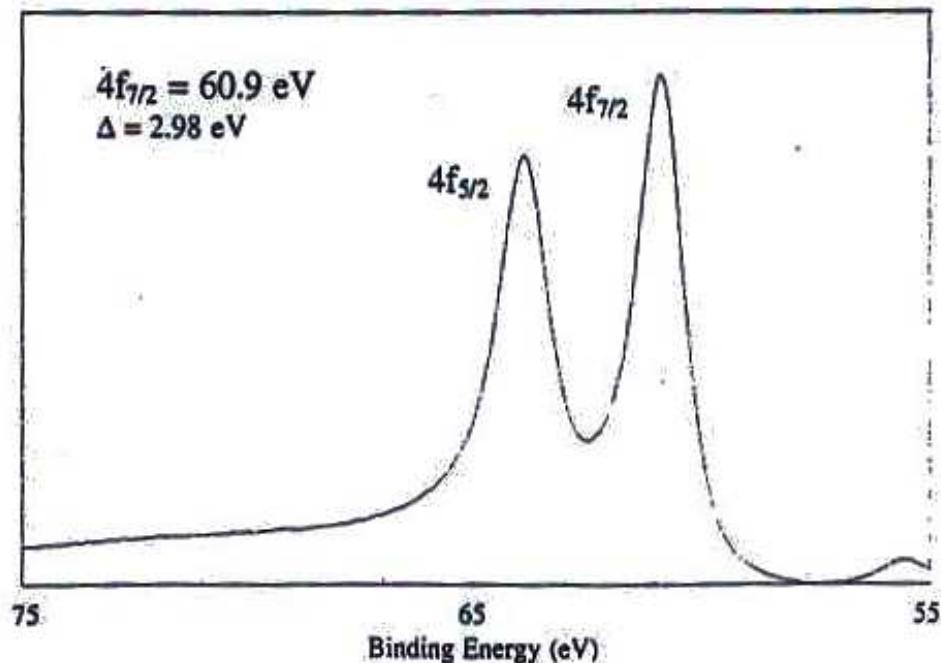

| 圖 3-13 Ir 在 XPS 圖譜裡的 Character peak.....             | 37 |

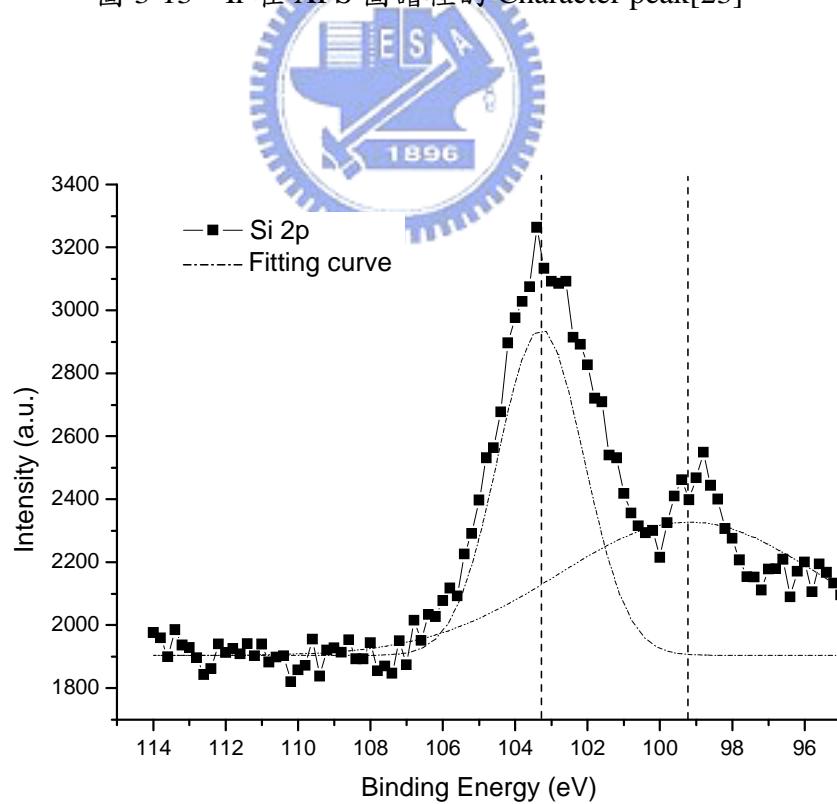

| 圖 3-14 以 Si 的特徵峰值去做 XPS 校正的動作.....                   | 37 |

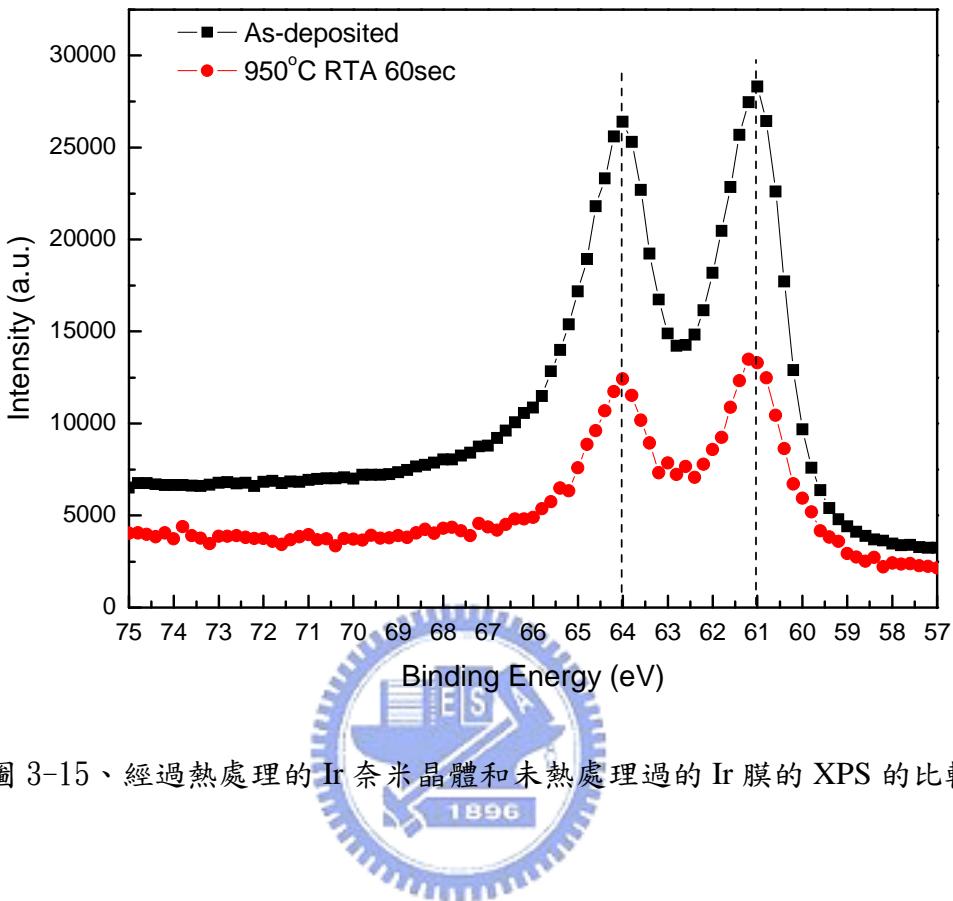

| 圖 3-15 經過熱處理的 Ir 奈米晶體和未熱處理過的 Ir 膜的 XPS 的比較。.....     | 38 |

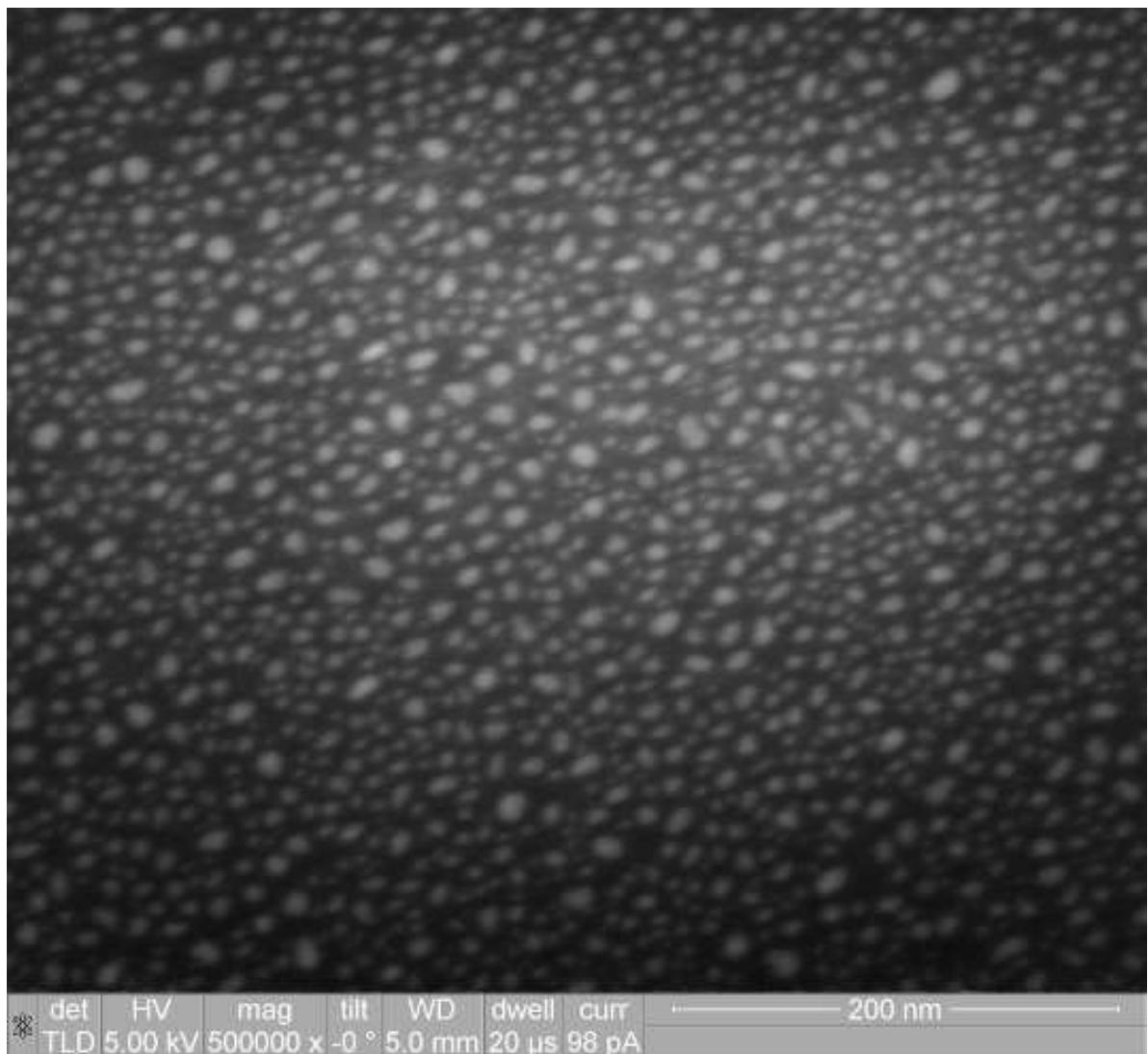

| 圖 3-16 即將應用在電容和元件上的 Ir-NCs 的 SEM 圖.....              | 39 |

| 圖 4-1 電容能帶示意圖.....                                   | 40 |

|                                                                    |    |

|--------------------------------------------------------------------|----|

| 圖 4-2 電容能帶三種操作狀態示意圖.....                                           | 41 |

| 圖 4-3 Ir gate 和 Al gate 的 C-V 曲線圖.....                             | 42 |

| 圖 4-4 穿隧氧化層厚度對 C-V 圖的影響.....                                       | 44 |

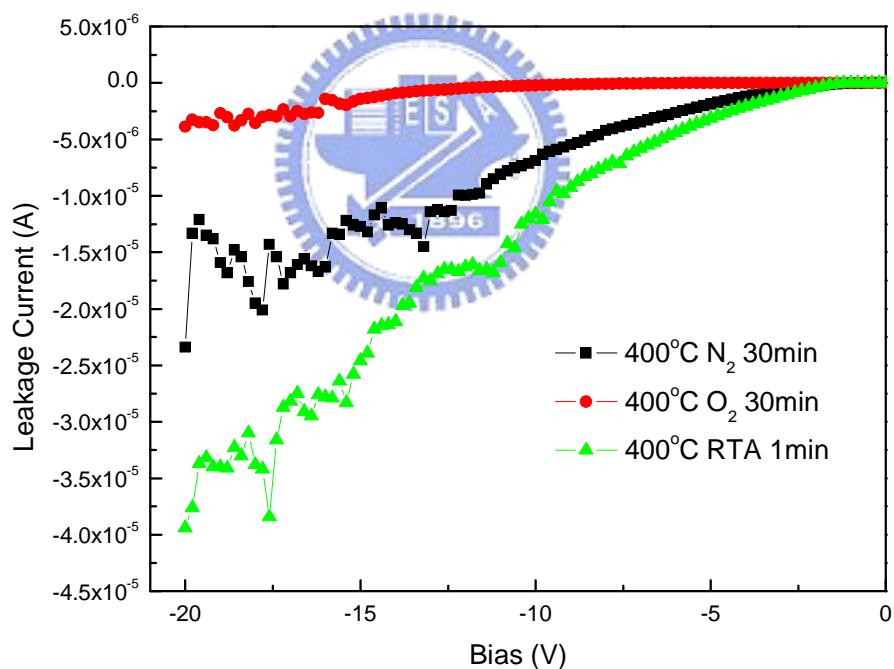

| 圖 4-5 HfO <sub>2</sub> 不同的修補條件下的 I-V 圖.....                        | 45 |

| 圖 4-6 HfO <sub>2</sub> 不同的修補條件下的 C-V 圖.....                        | 46 |

| 圖 4-7 電容成品的俯視圖.....                                                | 47 |

| 圖 4-8 Ir 奈米晶體與對照組的 C-V 圖比較.....                                    | 48 |

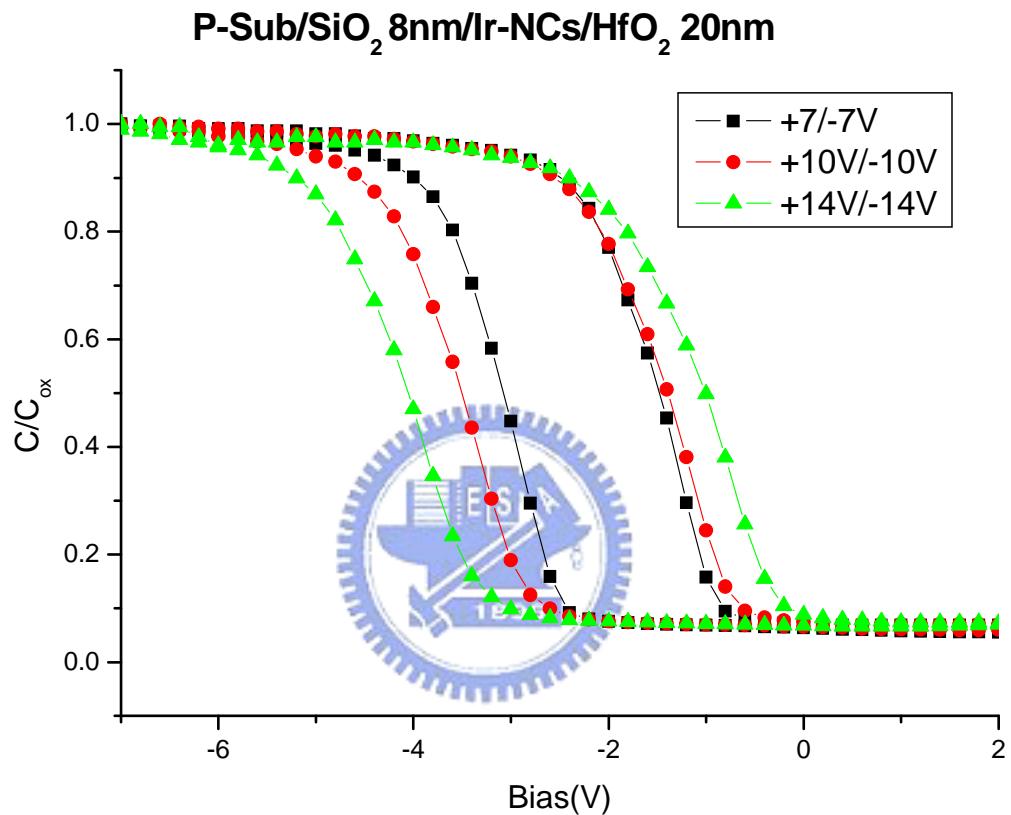

| 圖 4-9 不同偏壓對於 Ir-NCs 的 C-V 圖.....                                   | 49 |

| 圖 4-10 Ir-NCs 電荷保存能力.....                                          | 50 |

| 圖 4-11 兩種溫度下的電容 I-V 圖.....                                         | 52 |

| 圖 4-12 兩種溫度下的 ln(J) 對電場作圖.....                                     | 52 |

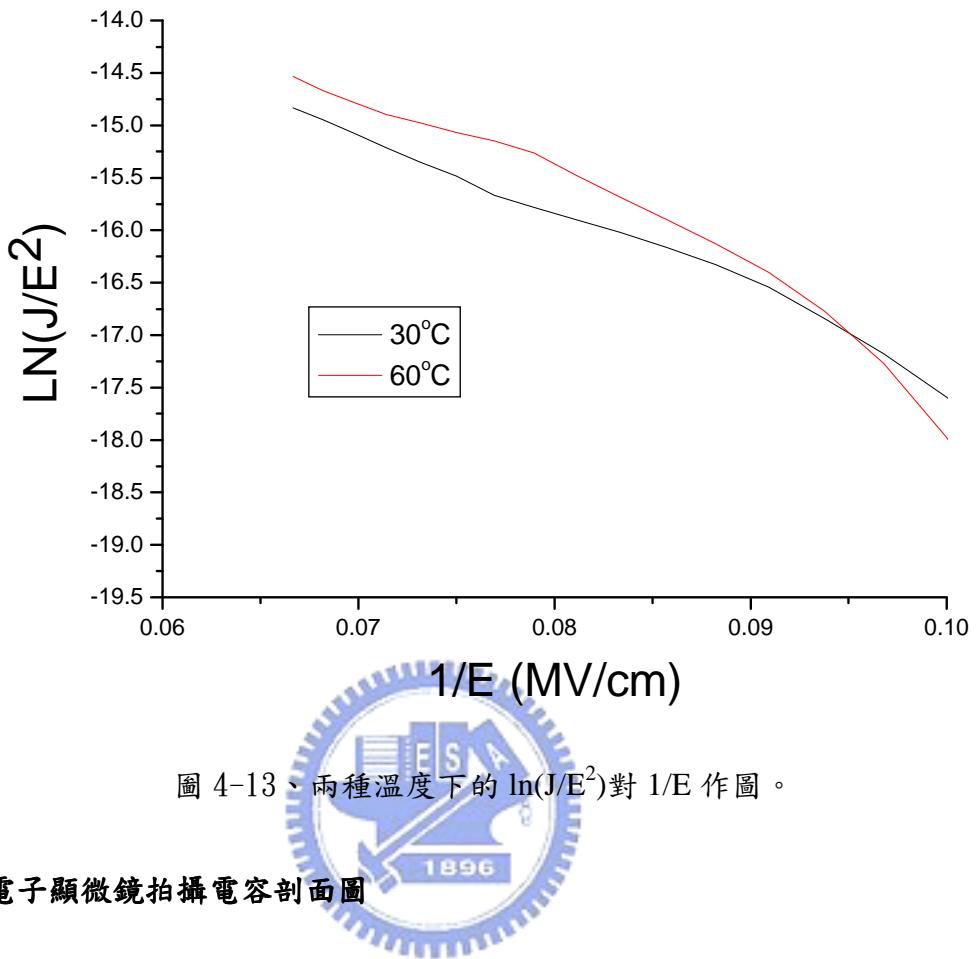

| 圖 4-13 兩種溫度下的 ln(J/E <sup>2</sup> ) 對 1/E 作圖.....                  | 53 |

| 圖 4-14 電容的 TEM 剖面圖.....                                            | 54 |

| 圖 4-15 元素受到電子束激發後會釋放出三種訊號.....                                     | 55 |

| 圖 4-16 EDS 分析的資料.....                                              | 55 |

| 圖 4-17 元件的 RTA 製程之後的 SEM 圖.....                                    | 56 |

| 圖 4-18 元件上 Ir-NCs 的確認圖.....                                        | 57 |

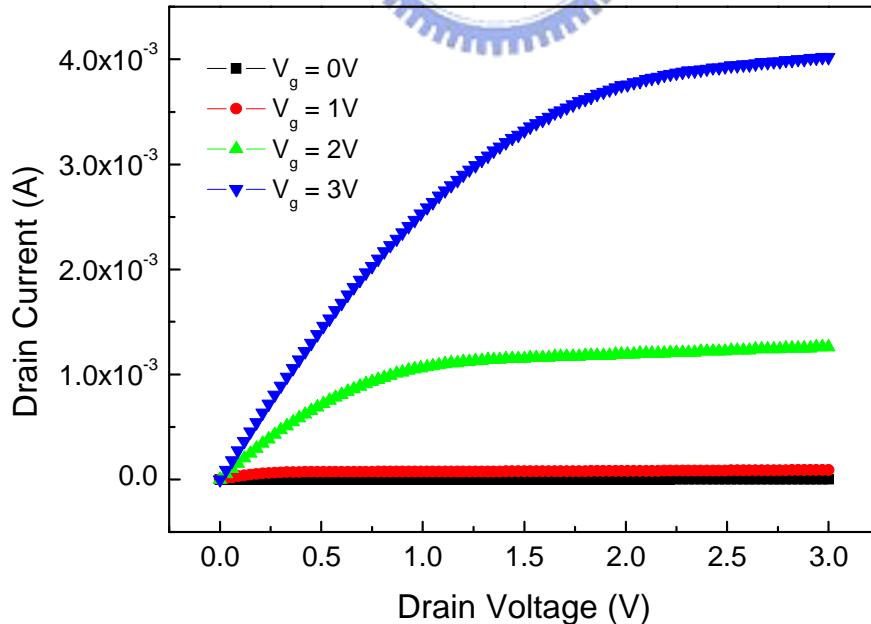

| 圖 4-20 Ir-NCs 元件的 I <sub>d</sub> —V <sub>d</sub> 圖.....            | 58 |

| 圖 4-21 元件 Program& Erase 示意圖.....                                  | 59 |

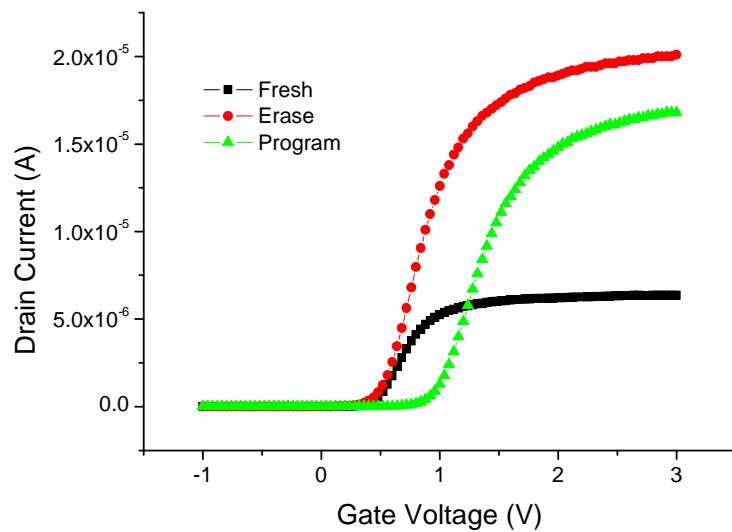

| 圖 4-22 Ir-NCs 記憶體元件的寫入和清除的操作 I <sub>d</sub> —V <sub>g</sub> 圖..... | 60 |

# 第一章

## 緒論

### 1-1 前言

記憶體(Memory)是目前在電子 3C 產品中扮演不可或缺的角色，耳熟能詳 DRAM、SRAM 和 Flash memory 等都是記憶體的家族成員。而 flash memory 被拿來做可攜式的裝置應用，如數位相機的記憶卡、USB 隨身碟、個人影音設備如 iPod 等等。

隨著製程能力的進步，微影技術的演進，使得單位面積可容納的 Cell 數目增加，記憶體的容量也越來越大，從一開始 MB 等級的商業化產品到目前已經普及化的 GB 等級的記憶體，吾人可以看到這顯著的變化。

而在 2007 年的十月左右華碩(ASUS)帶動了低價筆記型電腦的熱潮，Eee PC 的熱賣不僅代表 flash memory 技術的進步更代表了革命性觀念演進，以 flash memory 構成運算速度較快、體型較輕薄、但成本也比較高的(SSD)固態硬碟開始真正取代了硬碟的功用。

目前工業化的 Non-volatile memory(NVM)分為 floating gate (FG) memory 和 nitride storage device 為兩大主流，前者為目前市面上主流的記憶體商品的結構而後者主要應用在軍事及航太科技上面。由於 soft error 的現象，受到 UV-light 等幅射照射之下會使得電子從 FG 激發後流失，使 Threshold voltage 的 shift 量( $\Delta V_{th}$ )減少，造成邏輯上“0”和“1”的誤判，因此在航太科技上都以 nitride storage device 的 memory 為主。

#### 1-1-1 Floating gate memory 的特性和微縮(scale down)限制

把焦點移回主要的 FG 結構中，這種 flash memory 的結構如下頁圖 1-1 所示，其特色為一般 MOSFET 的控制閘極(control gate)和通道層(tunnel oxide or gate oxide)之間夾一層浮動

閘極(floating gate)。flash memory 採用 EEPROM's 的方法，對於每一個 cell 都可以利用電的方法去做清除(erase)和寫入(write)的動作。透過控制閘極來控制它的電位，而電位的改變量則是由浮動閘極所儲存的電荷來影響。當電子儲存在浮動閘極的時候，會使元件的臨界電壓(Threshold voltage)向右位移；而浮動閘極內沒有儲存電荷時，元件的 Threshold voltage 向左位移，如圖 1-2 所示，在文獻回顧的時候會深入說明。吾人利用此特性定義當電荷存滿 FG 時為個邏輯狀態(ex: “1”)電荷移除的狀態定義為另一個邏輯狀態(ex: “0”)。如此一來便組成電子產品重要的二進位運算。

圖 1-2、浮動閘極元件對電流-電壓曲線  $I_D-V_G$ 。

傳統的 Floating gate memory 遇到一些瓶頸，由於傳統的浮動閘極的電荷儲存和消除的動作時必須透過熱電子注入(Channel Hot Electron Injection ; CHIE)或是直接穿隧(direct tunneling)的模式來完成，而這兩種模式必須透過大電壓完成，因此都存在著能源消耗的問題(Power consumption)。另外當微影技術(Photolithography Process)越來越進步的時候，尺寸的縮小使得 coupling effect 越來越明顯，coupling effect 在元件尺寸微縮到 45nm 以下時原本有儲存在浮動閘極的電荷跳到鄰近的浮動閘極(如圖 1-3)使臨界電壓過於接近造成邏輯電路上的判別誤差，使得“1”和“0”的混淆，造成資料上的損毀。而這個現象是傳統 FG memory 在未來在微縮發展上的重大問題。

圖 1-3、浮動閘極在 45nm 以下產生的 coupling effect 示意圖。

### 1-1-2 未來趨勢與微縮研究方向

國際半導體技術藍圖 ( International Technology Roadmap for Semiconductors ; ITRS ) 是全球半導體產業需求15年展望的重要參考文獻，概括了產業的技術挑戰，提出了可能的解決方案，然後再由半導體製造商和設備材料供應商接手來去決定選擇哪一種技術和執行細

節。ITRS針對Floating gate memory的限制上也提供了一些可行的解決方向，在ITRS Process Integration, DEVICES, AND STRUCTURES 2007 edition[3]裡面他們認為對於高密度(32nm以下)的非揮發性記憶體(NVM)而言，通道的介電層和多晶矽間的介電層(interpoly dielectric)的微縮能力受到介電材料的性質和其幾何結構影響。本研究可以從下表1-1為擷取ITRS製作的表格中看到之後大略的發展趨勢。

表 1-1、ITRS PID 裡指出未來的研究趨勢以及可能發展到的尺度。

| Year of Production                 | 2007  | 2008  | 2009  | 2010  | 2011  |

|------------------------------------|-------|-------|-------|-------|-------|

| NAND FLASH technology-F(mm)        | 51    | 45    | 40    | 36    | 32    |

| Cell type(FG,CT,3D,etc)            | FG    | FG    | FG    | FG/CT | CT    |

| Tunnel oxide thickness(nm)         | 6-7   | 6-7   | 6-7   | 6-7   | 6-7   |

| Interpoly dielectric material      | ONO   | ONO   | ONO   | ONO   | ONO   |

| Interpoly dielectric thickness(nm) | 10-13 | 10-13 | 10-13 | 10-13 | 10-13 |

| Year of Production                 | 2012           | 2013           | 2014           | 2015           |

|------------------------------------|----------------|----------------|----------------|----------------|

| NAND FLASH technology-F(mm)        | 28             | 25             | 22             | 20             |

| Cell type(FG,CT,3D,etc)            | CT             | CT-3D          | CT-3D          | CT-3D          |

| Tunnel oxide thickness(nm)         | 6-7            | 6-7            | 6-7            | 6-7            |

| Interpoly dielectric material      | High- $\kappa$ | High- $\kappa$ | High- $\kappa$ | High- $\kappa$ |

| Interpoly dielectric thickness(nm) | 9-10           | 9-10           | 9-10           | 9-10           |

從表 1-1 可以看到 cell type 分兩種，CTF 有別於浮動閘極(FG)元件，它是將電荷儲存於絕緣體之內 (silicon nitride)。由於電荷是獨立儲存，完全不會彼此干擾 (interference)，也不會有 FG 在微縮之下碰到的 coupling effect 的困擾，CTF 的結構至少可以微縮至 20nm 以下。。CTF 之傳統結構為 SONOS 結構如圖 1-4(a)，此結構是透過能帶設計(Band gap engineer)將電荷儲存於氮化矽 ( $\text{Si}_3\text{N}_4$ ) 內，並透過上下兩層二氧化矽 ( $\text{SiO}_2$ ) 來阻絕電荷流失。其構想出現的時間幾乎與浮動閘極元件的發明同期(1967 年 MNOS 結構由 Wegener [4]等人提出；而 FG 結構由施敏與 D. Kahng[5]提出)但是 CTF 也有缺陷，那就是電荷極難抹除 (erase)。因為電荷是儲存在氮化矽之深度能井 (deep traps)，無法像浮動閘極元件般消除，因此必須設計超薄的 tunnel oxide 以提供電洞直接穿遂 (hole direct tunneling) 用來抹除電子。然而，超薄的穿遂層造成了元件電荷容易遺失。所以 SONOS 元件的發明很早，卻不曾被採用在商業應用。而旺宏電子依據 SONOS 改良發表 BE-SONOS 技術結構如

圖 1-4(b)[6]，旺宏認為此項設計可以突破 45nm 的製程障礙；另一方面其他公司如三星電子公司也有人做類似的研究 TANOS 等。而在學術界發展奈米晶體 nanocrystals(NCs)為儲存電荷中心(charge center)的結構來取代 FG memory 的研究見圖 1-4(c)[7]，它的核心概念也是透過能帶的設計使電荷能有效保留在 NCs 之中，不同的金屬以及不同的成形方法都被廣泛的研究，而相關的文獻在 1-2 會做跟本論文相關的文獻整理和探討。也有一群研究者在幾何上的排列做研究如 Soon -Moon Jung 等人所提出的 3-D 堆疊結構如圖 1-4(d)[8]如此一來能有效提高 cell 的密度增大記憶體容量。

除了這系列的研究之外，也有人捨棄掉這些理論和架構，發展出另外一套記憶體的操作模式例如 FE-RAM、MTJ-RAM、PCM 等，以目前最常聽到的相變化記憶體(又名 OUM 如圖 1-4(e))為例透過非晶相(amorphous)和結晶相(crystal)所造成電阻的不同定義出“1”和“0”的狀態達成記憶體的效果。

圖 1-4、為克服微縮問題的 Non-volatile memory 研究方向。

## 1-2 論文架構與文獻回顧

在開始文獻回顧之前，先簡單介紹一下內容的編排，本論文劃分三大部分，第一部分為奈米晶體的形成(Nanocrystals formation)，第二部份為應用在電容結構上的試做(Capacitor)，最後則是試驗放置在記憶體元件上的特性(Nonvolatile Memory Device)。因此本研究的文獻回顧也是依照類似的順序來說明，從奈米晶體的形成到奈米晶體的記憶體的應用，最後把與本研究材料相關的論文做個簡單的連接。

### 奈米晶體的形成(Nanocrystals formation)

一般奈米晶體的形成方法有很多種，有的是透過化學的方式，目前常聽到的成熟技術為自組裝單分子薄膜層(Self-assembled monolayer, SAM)，利用共價鍵將小分子結合，而形成完整的巨型分子。再透過氫鍵、凡得瓦爾力及其他共價鍵(靜電力、親疏水作用力等)的協同作用，形成複雜穩定的結構。最後由一個或多個大分子作為結構基石，經多次的重複自組裝過程，排列成奈米結構如圖 1-5。有的是利用 ALD(Atomic Layer Deposition)的方法長出一層奈米晶體。更常被拿來運用的方法則是在生成薄膜後透過快速升溫退火爐(Rapid thermal annealing；RTA)的方法，在很多相關 Nanocrystal capacitor 的論文裡都用到這個方法，如張鼎張教授所發表的”Nickel nanocrystals with  $\text{HfO}_2$  blocking oxide for nonvolatile memory application”[9]便是一個例子。當然形成奈米晶體的目的不是只能應用在記憶體上面，也有許多人利用在感測器、發光元件等其他應用上，本論文不詳加論述。

對於RTA所造成的影响及奈米晶體的生成影響因素，Gong-Ru Lin 等人[10]提到Ni nanocrystals的形成受到下列四個因素影響：

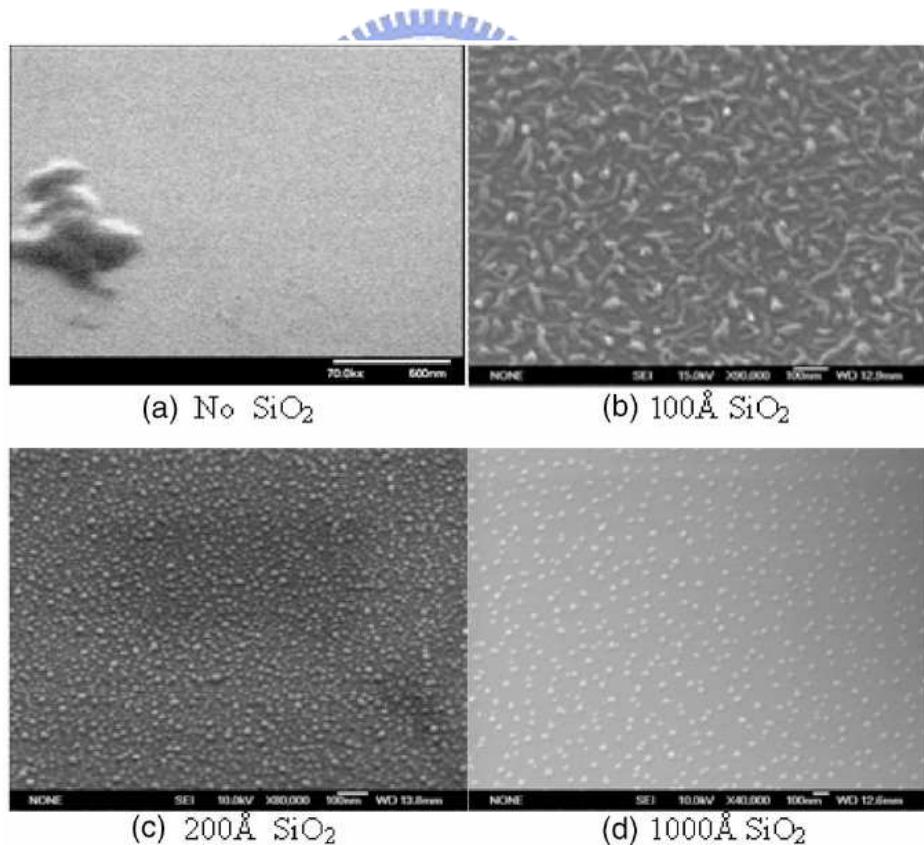

#### (1) Thermal conductivity (熱傳導的能力)：

熱傳導的能力，會影響到thermal energy的儲存，文章中指出矽(Si)的傳導能力為148W/mK，而二氧化矽( $\text{SiO}_2$ )為1.35W/mK，本研究可以從下頁圖1-6的(a)和(b)中可以看到Ni的變化，代表Si儲存的能量不夠讓Nickel film有足夠的能量來開始形成Ni nanocrystals。而(b)~(d)可以看到不同的 $\text{SiO}_2$ 厚度對於thermal conductivity的貢獻。他們認為在20nm的厚度的時候，Ni nanocrystals的成形效果最明顯。然而在

100nm的時候，thermal energy過多造成Ni nanocrystals的size過大以致於密度下降。

圖 1-5、SAM 機制示意圖。

圖 1-6、不同基材及基材厚度對 Ni film 的影響[10]。

## (2) Metal film thickness ↓ Nanocrystals shrinks

(初始的金屬膜厚度下降，奈米晶體隨之變小)

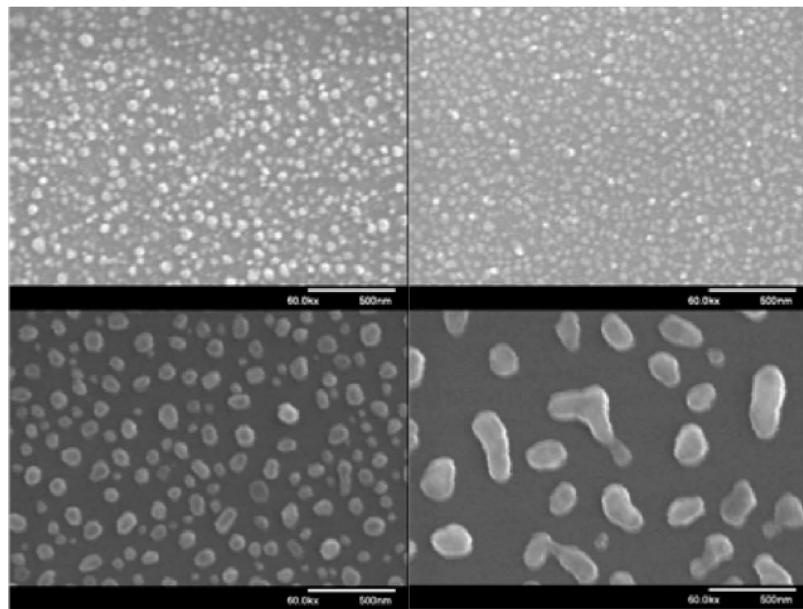

他們也提到金屬膜厚度對於奈米晶體的影響，厚度越薄金屬奈米晶體的尺度會隨之變小。本研究參考另外一篇文獻，以金(Au)為例，見下圖1-7[11]厚度不同熔點也會隨之下降，晶體的金熔點大概落在1300°C而厚度越薄對溫度的反應也越敏感。回到Gong-Ru Lin的文章，他們用不同的金屬厚度(3nm~20nm)經過相同的熱處理後再用SEM去做觀察如下頁圖1-8[10]，可以明顯發現在相同的熱處理下奈米晶體有不同的表面形貌。

圖 1-7、金粒子在不同尺寸下有不同的熔點[11]。

## (3) Adhesion(附著力)

文中也有提到金屬膜對於基材間的附著力之間的影響，他們提出了附着力越大的介面(interface)會使金屬奈米晶體會越難形成的現象，但是在此文獻中沒有提出相關驗證的方法。本論文在3-1-1會嘗試利用接觸角(contact angle)和SEM的影像去做相關探討。

圖 1-8、不同的初始金屬膜厚度對 Ni nanocrystals 的影響。

(左上：3nm 右上：5nm 左下：10nm 右下：20nm)[10]

#### (4) Anneal temperature or annealing time(退火溫度和退火時間)

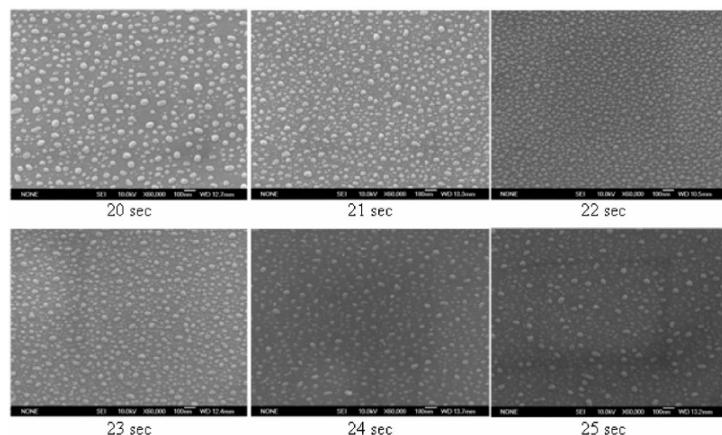

熱處理(thermal process)製程會影響奈米晶體的尺寸和密度，而與之最相關的兩個熱處理參數為退火溫度和退火時間。本研究從Gong-Ru Lin等人所寫的文獻可以看到他們的RTA溫度為850度然後做跟時間相關的變化所產生的影響可以參考下圖1-9。由此本研究可以知道熱處理在nanocrystal的形成扮演了主要關鍵角色，在之後本研究也會針對溫度和時間變化做類似的研究。在下一個主題會把相關的金屬以及RTA的溫度和時間做一個整理，請見表1-2。

圖 1-9、Ni film 在 20nm SiO<sub>2</sub> 經過 RTA850°C 對不同退火時間的影響[10]。

## 奈米晶體記憶體的特性

前文提到的charge trap類型的奈米晶體記憶體的研究，已在學術界的文獻上被廣泛的研究，在2002年IEEE Trans. Elec. Dev.裡面Zengtao Liu等人[12][13]，對於金屬奈米晶體記憶體從設計和製造到電性上的表現做了一系列的整理和論述。

使用金屬奈米晶體的好處有三點：

- (1) 功函數(work function)的設計，對於電子來說是很好的捕捉因子(trap center)，可以造成和SONOS結構一樣有很深的位能井。

- (2) 奈米尺度的大小所產生的能階分裂，有利於更多的電子的儲存。

- (3) 由於奈米晶體是埋置(embed)在介電層上，彼此互相被絕緣體所絕緣，所以當電子流失(charge loss)的時候，並不會有全部同時流失的情況，因此可以提高記憶的時間(Retention time)，如圖1-10[13]。

圖 1-10 不同金屬奈米晶體對 retention time 的效果[13]。

另外由於是記憶體元件特性，因此本研究必須驗證金屬奈米晶體元件是否能和圖1-2的特性一樣擁有臨界電壓的變化。奈米晶體就像取代傳統的浮動閘極的地位，按照Threshold voltage的公式：

$$V_{th} = \frac{|Q'_{SD} (max)|}{C_{ox}} + \phi_{ms} + 2\phi_{fp} - \frac{Q}{C_{ox}} \quad (1-1)$$

其中

$C_{ox}$  = 氧化層電容

$\phi_{ms}$  = 金屬和半導體之間的位障

$\phi_{fp}$  = 費米能階(Fermi level)到本質費米能階(Intrinsic Fermi level)的距離

$Q$  = 氧化層中的電荷量

若整個結構確定的話，也就是材料固定的狀況下能影響 $V_{th}$ 的條件只有最後一項也就是可以化簡成如下：

$$\Delta V_{th} = -\frac{\Delta Q_{FG}}{C_{FG}} \quad (1-2)$$

$\Delta V_{th}$  = 臨界電壓的偏移

$Q_{FG}$  = 浮動閘極中的電荷量

$C_{FG}$  = 浮動閘極電容，

如此一來便可以直接看出當奈米晶體儲存電子的時候， $Q < 0$ ，因此會比沒有儲存電子的時候大( $\Delta V_{th} > 0$ )，相反的，當奈米晶體所抓住的電子被排開，使其中的電荷  $Q > 0$ ，則  $\Delta V_{th} < 0$ 。與圖 1-2 的相同電性也顯示在奈米晶體的記憶體上，見圖 1-11。

圖 1-11、金屬奈米晶體記憶體的電流-電壓曲線[13]。

下表1-2為利用RTA方法所製作的奈米晶體做不同金屬材料在溫度和時間的參數下所形成奈米晶體的大小(size)和密度的比較。本研究可以發現利用RTA方法的製作，密度最高只能到達 $10^{12}$  尺度的密度，另外經過熱處理之下產生的奈米晶體也都有大小不易統一控制的通病。

表 1-2、利用 RTA 方法所製作出來的金屬奈米晶體的比較。

| NCs material | Density               | Diameter Size( nm) | $\Phi$ m(eV) | RTA method         | Reference                               |

|--------------|-----------------------|--------------------|--------------|--------------------|-----------------------------------------|

| Ni           | $3.9 \times 10^{12}$  | 5                  | 5.15         | 500°C 60s          | Appl. Phys. Lett. 90, 222104(2007) [9]  |

| Co           | $2.13 \times 10^{12}$ | 6~8                | 5.0          | 500°C 60s          | Appl. Phys. Lett. 90, 132102 (2007)[14] |

| Pt           | N.A.                  | 2~3                | 5.65         | 900~950 °C 30s     | IEEE Trans. Elec. Dev. 49, 9 (2002)[12] |

| W            | $5 \times 10^{11}$    | 5                  | 4.55         | 900~950 °C 30~120s | Appl. Phys. Lett. 87, 113110 (2005)[15] |

### 材料的熱穩定性

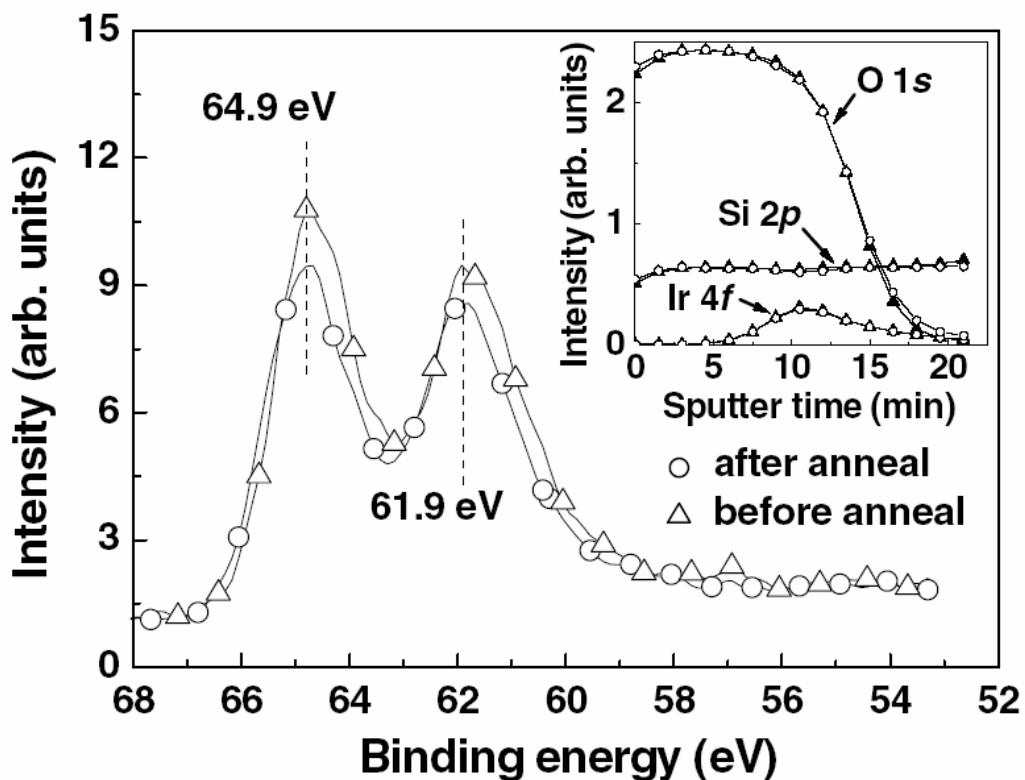

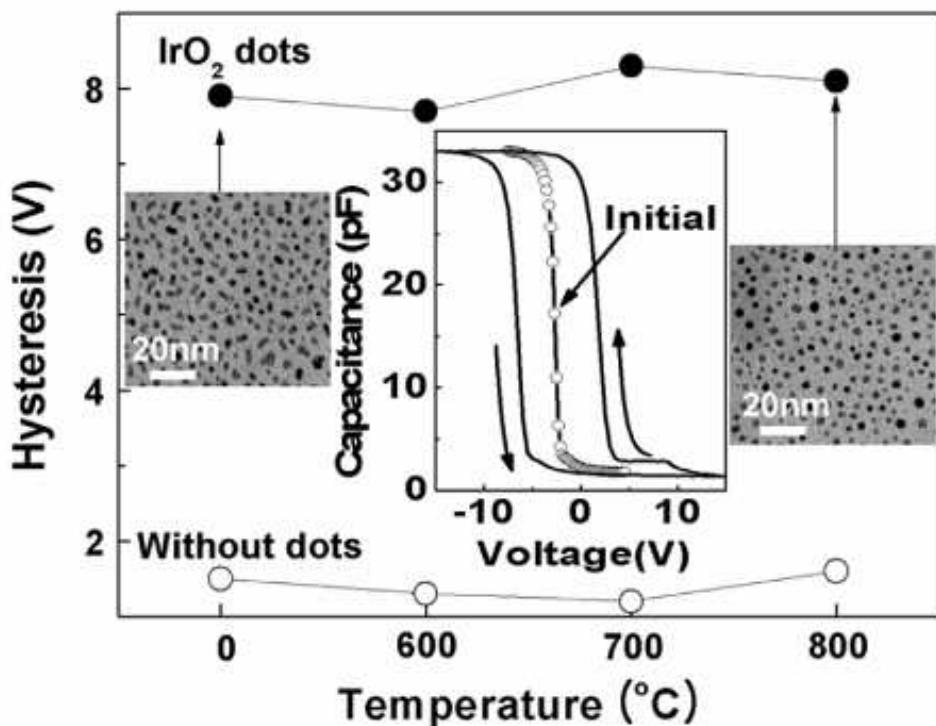

材料的熱穩定性能力影響到對於CMOS製程的相容適應力，傳統的CMOS製程會有很多熱處理製程，連帶會產生許多thermal budget，thermal budget會影響奈米晶體的形成和大小的一致性，甚至造成元件電性的劣化。另外對於熱穩定性高的材料，可以更進一步搭配self-aligned的製程。Self aligned process的特色就是將元件結構每層堆疊完畢之後，再用離子佈植(Ion implantation)和退火(thermal annealing)之後就可以完成電晶體的製作，比傳統的製作流程減少許多微影的動作。本研究引用三星電子公司研究IrO<sub>2</sub>的文獻[16]來提出驗證材料的熱穩定性的方法，下頁圖1-12即是利用X-ray光電子質譜儀(X-ray Photoelectron Spectroscopy ; XPS)去針對IrO<sub>2</sub>的表面做元素上的分析，在經過800°C 20min的高溫爐管之下，Ir 4f的peak依然幾乎沒有shift證明了材料不會受到熱處理的影響。插圖則是說明在ALD生長環境下，iridium、silicon和oxygen原子對於sputter 時間所產生的強度變化。另外他們也透過電性和TEM影像的分析證明IrO<sub>2</sub>奈米晶體對於高溫製程有很強的穩定性如下頁圖1-13，本研究也可以看到電性的表現也十分穩定，不受到高溫爐管退火變化。

圖 1-12、Ir 4f 的訊號峰在退火前和退火後的比較；插圖為 XPS depth profiles 對於 iridium、silicon 和 oxygen 原子。[16]。

圖 1-13、IrO<sub>2</sub> 奈米點經過退火之後對磁滯的變化插圖為 IrO<sub>2</sub> 的 TEM 圖底下為沒有 IrO<sub>2</sub> 的對照組中間插圖顯示含有 IrO<sub>2</sub> 奈米點的磁滯曲線[16]。

## 1-3 實驗動機與目標

本研究透過目前現有的實驗設備與材料來製作奈米晶體記憶體，並透過這些設備使本論文能有一個完整的架構與討論。

本研究的動機分成下列二項：

### (1) Use metal Nanocrystals (使用金屬奈米晶體)：

本研究透過金屬奈米晶體的高功函數(high work-function)的特點，創造高位能井來增進retention time，也藉著金屬的位能井讓穿隧氧化層(tunnel oxide)更薄。而利用Ir當研究目標是因為它的熱穩定性和它的高功函數(約5.27eV)，所以近程目標為期望此材料能達成增進retention time的目標。遠程目標則是希望以後能應用在self-aligned的製程上面。

### (2) Use high- $\kappa$ material (使用高介電係數的材料)：

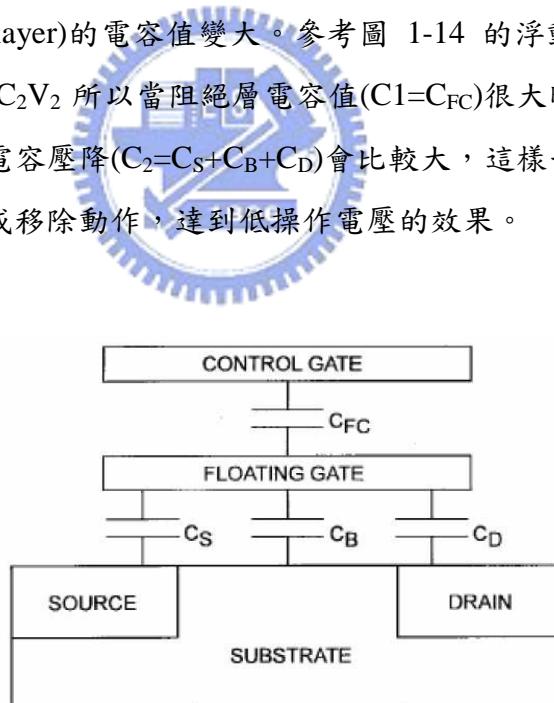

本論文使用高介電係數的材料來當阻擋層的材料利用高介電係數導致阻擋層(blocking layer)的電容值變大。參考圖 1-14 的浮動閘記憶體的等效電容圖，由於  $C_1V_1=C_2V_2$  所以當阻絕層電容值( $C_1=C_{FC}$ )很大時其所跨的壓降會比較小，而穿隧層電容壓降( $C_2=C_S+C_B+C_D$ )會比較大，這樣一來本研究可以做更有效的電荷寫入或移除動作，達到低操作電壓的效果。

圖 1-14、浮動閘極元件的等效電容圖。

這個論文的目標則是透過 RTA 的製程和薄膜的厚度調變利用 SEM 等儀器去檢驗，讓奈米晶體的分布和大小達到一個較理想的狀況，並且利用此高功函數的特性去製造較深位能井；利用高介電材料去達到低操作電壓的效果。

## 第二章

# 元件使用機制與實驗流程

### 2-1 元件機制

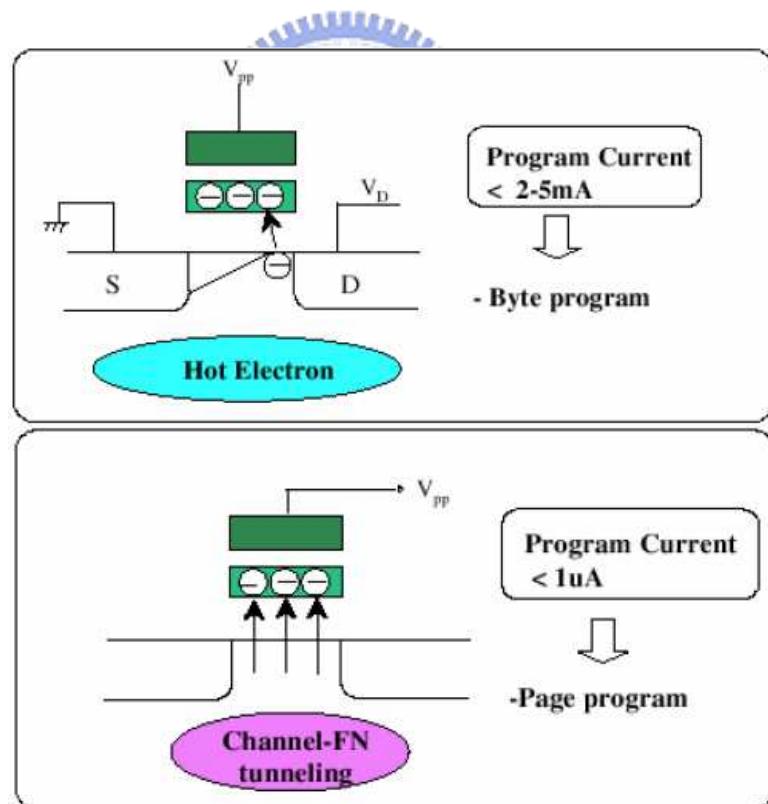

目前元件最常見的使用機制為兩種一種是熱電子注入(Hot electron injection)另一種為F-N 穿遂(Fowler-Nordheim tunneling)，以下為兩者做簡單介紹，並在這小節之後會做一個表2-1去比較這兩種機制的特色。這兩個機制的目的在於改變控制浮動閘極(Floating gate)內的電荷量，來改變浮動閘極的電位，進而判斷記憶體元件是在“1”或“0”的狀態。

#### 2-1-1 热電子注入(Hot electron injection)

熱電子注入(HEI)的機制是相對的簡單，一個電子從接地的源極(Source)獲得能量往汲極(Drain)移動，當加速電場超過 $100\text{ kV/cm}$ ，電子就有足夠的能量透過控制閘極(control gate)改變方向並且穿越 $\text{SiO}_2$ 的能障然後到達浮動閘極(FG)。(如圖2-1)其狀態又因為是從通道注入到FG，因此也有些人將這現象稱作Channel hot electron injection(CHEI)。

熱電子注入(HEI)的特點就是快速，因為這時元件已經操作在飽和區，所以電子已經被加速到電子在半導體中速度的極限，大約為 $10^7\text{ cm/s}$ ，這時，再被控制閘極吸引上去，相對的就比F-N 穿遂的速度快，時間通常在1到10微秒( $1\text{~}10\text{ }\mu\text{s}$ )，因此通常用在將電子注入浮動閘極層。

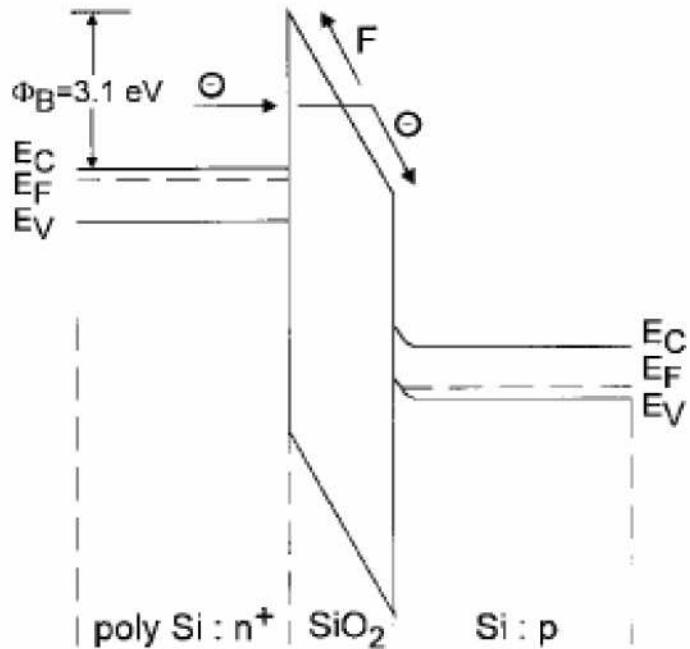

#### 2-1-2 F-N 穿遂(Fowler-Nordheim tunneling)

穿遂機制(Tunneling mechanism)是從量子力學中帶入薛丁格方程式(Schrödinger equation)所導出的機制。不同於古典物理的概念，近代物理的學家認為電子等微觀粒子能夠穿過它們本來無法通過的“牆壁”的現象。這是因為根據量子力學，微觀粒子具有

波的性質，而有不為零的機率穿過能障壁。換句話說，人也有機會去穿過牆壁，只是這個機率在巨觀世界裡面微乎其微，因此到現在還沒有發現這現象。

穿隧在電子學裡面分成兩個類型一個是直接穿隧(direct tunneling)，另外一個是F-N穿隧(Fowler-Nordheim tunneling)請參見圖2-1[17]。以金屬-氧化物-半導體(MOS)的結構來說，直接穿隧發生在中間的夾層很薄的時候( $\text{SiO}_2 < 3\text{nm}$ )會發現有穿隧電流的現象；大於這個厚度就很難有成功的直接穿隧現象。然而F-N tunneling 不同於直接穿隧，因為它會隨著MOS操作的電壓上升，而使測量到的電流上升。從能帶的MOS結構來解說，電極所施加的電壓會使的氧化層的等效寬度變小如圖2-2，因此電子從Si穿過氧化層的機率就因此上升。浮動閘極元件可以利用F-N 穿隧(F-N tunneling)使源極(Source)的電子穿過穿隧氧化層(tunneling oxide)到達浮動閘極，接著關閉電壓，電子就會被侷限(trap)在由穿隧氧化層(tunneling oxide)和控制氧化層(control oxide)之間的位能井內(如圖2-3)。

圖 2-1、上圖為 HEI 模式下圖為 FN-tunneling 模式對操作在元件的示意圖[17]。

圖 2-2、F-N tunneling 在 MOS 結構的示意圖。

圖 2-3、電子侷限在 FG 的位能井之中 [18]。

表 2-1、CHEI 和 FN-tunneling 比較[19]。

| CHEI 模式                                                                                                                                                   | FN-tunneling 模式                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Low power consumption<br>—single external power supply                                                                                                    | High power consumption<br>—complicated circuitry technique                                         |

| High oxide field<br>—thinner oxide thickness required<br>—higher trap generation rate<br>—severer read disturbance issue<br>—highly technological problem | Low oxide field<br>—oxide can be thicker<br>—highly oxide integrity<br>—low read disturbance issue |

| Slower programming speed                                                                                                                                  | Faster programming                                                                                 |

## 2-2 實驗流程

這一節會詳細介紹本論文的實驗製程，包含打底工作的奈米晶體形成研究、以及電容結構的製作與量測，更進一步的應用在元件上。

### 2-2-1 奈米晶體的形成(The process flow of nanocrystals formation)

奈米晶體形成的實驗步驟是相當簡單的，其實驗步驟如下：

(1) 用 P-type (100) 晶片做 RCA clean 的處理如圖 2-4。

圖 2-4、P-Type 晶片經過 RCA clean。

(2) 經過 RCA clean 之後，送進高溫水平爐管 950°C 乾式氧化層 8nm 如圖 2-5。

圖 2-5、水平爐管長 Dry oxide 8nm。

(3) 長完  $\text{SiO}_2$  後利用 N&K 膜厚測厚儀做確認後破片。

(4) 之後再利用本實驗室的 Ion beam sputter 做金屬 Ir 膜的疊加(見下頁圖 2-6)。

(5) 利用 RTA 热製程形成奈米晶體 (見下頁圖 2-7)。

(6) 利用材料分析儀器如 SEM、AFM 和 XPS 等做材料的分析。

圖 2-6、利用 Sputter 長 Ir 膜。

圖 2-7、RTA 之後形成奈米晶體。

## 2-2-2 電容的製作(The process flow of capacitor)

- (1) 用 P-type (100) 阻值  $1\sim10\Omega\cdot\text{cm}$  的晶片做 RCA clean 的處理如圖 2-4。

- (2) 經過 RCA clean 之後，送進高溫水平爐管  $950^\circ\text{C}$  乾式氧化層  $8\text{nm}$  如圖 2-5。

- (3) 用 N&K 膜厚測厚儀做  $\text{SiO}_2$  的確認後破片。

- (4) 利用 Ion beam sputter 做金屬 Ir 膜的疊加如圖 2-6。

- (5) 參考前面的研究利用其調整出的參數做 RTA 的熱處理如圖 2-7。

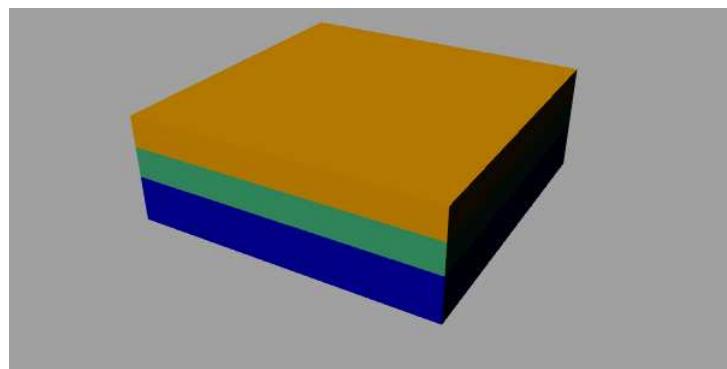

- (6) 利用雙電子槍蒸鍍系統(Dual E-Gun Evaporation System)打  $\text{HfO}_2$  靶材，使奈米晶體覆蓋上高介電材料的阻擋層  $30\text{nm}$ (High- $\kappa$  blocking layer)如下頁圖 2-8。

- (7) 鍍完的高介電材料用爐管去作 Densify，目的是為了修補物理蒸鍍(PVD)製程中出現的缺陷(defect)。

- (8) 透過熱阻絲蒸鍍系統(thermal coater)正鍍鋁電極  $300\text{nm}$ 。

(9) 用黃光微影製程定義出鋁電極的圖形。

圖 2-8、利用 E-gun 疊上  $HfO_2$  的薄膜。

(10) 利用蝕刻鋁的溶液(蝕刻 Al 溶液 =  $H_2O + CH_3COOH + H_3PO_4 + HNO_3$ )，加熱至 40~60°C 後，把鋁蝕刻掉，而受到光組保護的地方則會保護 Al 不受蝕刻液侵蝕。

(11) 最後在 P-Sub 底部也鍍上 Al 300nm 電極，製程便到此為止。其電容整個結構如圖 2-9。

(12) 將完成的電容做電性分析。

圖 2-9、奈米晶體電容結構示意圖。

### 2-2-3 元件的製作(The process flow of capacitor)

(1) 用 P-type (100) 阻值  $1\sim10\Omega.cm$  的晶片做 RCA clean 的處理如圖 2-4。

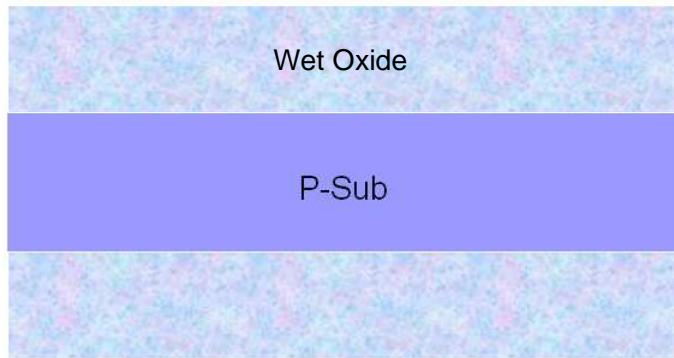

(2) 用水平爐管到 1050 度長濕式氧化層(wet oxide layer)如下頁圖 2-10。

圖 2-10、用水平爐管長出  $\text{SiO}_2$  膜。

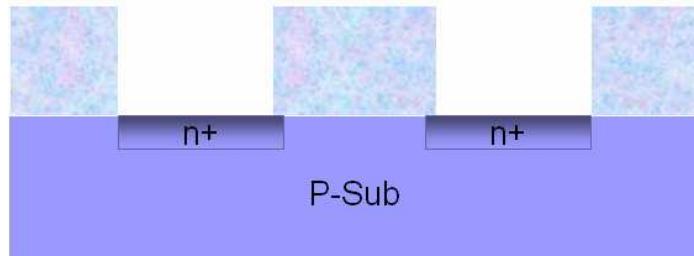

- (3) 用黃光微影製程定義出 Source/Drain 的區域(Define S/D region)之後用 BOE 蝕刻液 etch  $\text{SiO}_2$  形成圖 2-11 的結構。

圖 2-11、Define S/D region。

- (4) 定義出 S/D 的區域後做中電流離子布植(Ion implantation)做磷的佈植。

- (5) 之後用 RTA  $950^\circ\text{C}$  30s 去做活化讓 S/D 的區域形成  $\text{n}^+$  如圖 2-12。

圖 2-12、Implantation 之後用 RTA 做活化處理(activation)。

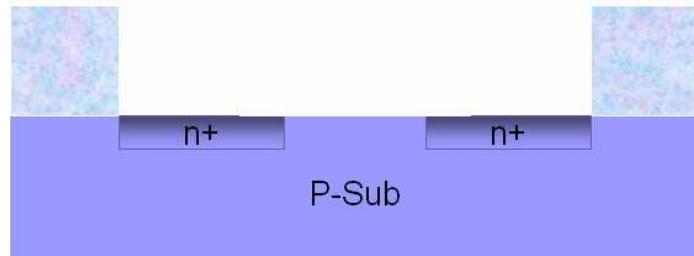

- (6) 之後用黃光定義出主動區(Activation area；AA 區)之後，再利用 BOE etch 多餘的  $\text{SiO}_2$ 。如下頁圖 2-13。

- (7) 利用水平爐管  $950^\circ\text{C}$  長 Dry oxide 6~8nm 做為 tunnel oxide。如圖 2-14。

圖 2-13、定義出 AA 區。

圖 2-14、用爐管成長 Dry oxide 6~8nm。

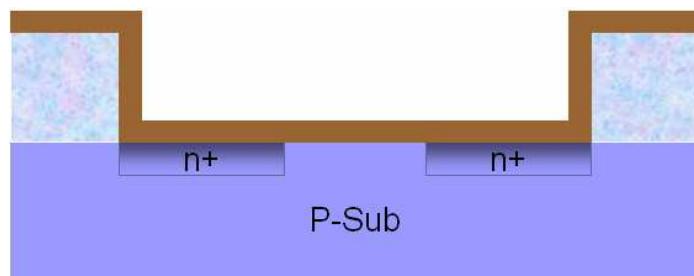

- (8) 用黃光定義出沉積 metal film 的區域，並且用光阻(FH6400)保護 S/D region，再用 Sputter 鍍上 Ir metal film，如圖 2-15。

圖 2-15、沉積 Ir metal film。

- (9) 把光阻用丙酮(Acetone)Lift-off 去除乾淨後，放進 RTA 進行熱處理形成奈米晶體，如下頁圖 2-16。

- (10) 接者利用 E-GUN 的電子束打  $HfO_2$  靶材沉積阻擋層蓋住 Ir 奈米晶體，之後先用黃光定出 contact hole 然後再用 BOE etch 後，緊接者送進爐管作 Densify 的動作，修補 blocking layer 的 defect。結果如下頁圖 2-17 所示。

圖 2-16、光阻 Lift-off 後經過 RTA 製成形成奈米晶體。

圖 2-17、用 E-gun 疊上阻擋層並挖開 contact hole。

(11) 再來利用熱阻絲蒸鍍系統(thermal coater)把挖出來的 contact hole 鍍上一層 300 nm 的鋁，鍍完之後再把電極的區域定義出來(Define contact pad)最後完成如圖 2-18 的元件。

圖 2-18、元件橫剖面示意圖。

# 第三章

## 奈米晶體的特性和討論

### 3-1 奈米晶體的形成

在開始製作 Ir nanocrystal 時，本研究參考 1-2 提到的文獻回顧，並且從他們提到的條件中，加入到本實驗的控制條件中。期望能在有限的時間和機台能力的限制中接近本研究預期的目標：奈米晶體的密度越高(density ↑)奈米晶體的大小和形狀的一致性高(size & shape uniformity ↑)。以下就是對於參數的實驗結果和討論，在 3-2 的結論裡面會顯現目前為止的最好的狀況。

3-1-1 接觸角和奈米晶體的形成

本研究用  $\text{SiO}_2$  和 Ir 金屬膜來做接觸角的量測，量測方法的示意圖如圖 3-1。接觸角是常被用來判斷表面能的方法之一，本實驗透過接觸角來換算表面能。滴三種液體分別為 Water、DIM(diiodomethane)、EG(ethylene glycol)並且從中量測其接觸角。如下頁圖 3-2 顯示的結果，綜合整理的接觸角的數據如下表 3-1。

圖 3-1、接觸角量測的示意圖[20]。

圖 3-2、二種膜對三種液滴的接觸角量測結果。

表 3-1、不同的膜對三個液滴所量測到的接觸角整理。

|                  | Water  | DIM    | EG     |

|------------------|--------|--------|--------|

| Ir metal film    | 84.09° | 40.09° | 53.98° |

| SiO <sub>2</sub> | 46.88° | 45.57° | 17.72° |

而本研究利用參考文獻[21]提到的公式去推導出各個膜的表面張力(surface tension)，表面張力的單位為mJ/m<sup>2</sup>，乘以面積的時候就為所謂的表面能的單位(surface energy)，因此實驗上通常都用表面張力當做比較表面能的指標。透過 Lifshitz-van der Waals (LW) 和 Lewis acid-base (AB) 理論，表面張力可以表示成下面這個式子：

$$\gamma_i = \gamma_i^{LW} + \gamma_i^{AB} = \gamma_i^{LW} + 2\sqrt{\gamma_i^+ \gamma_i^-} \quad (3-1)$$

其中  $\gamma^{LW}$  為非極化的項目也就是 dispersion(apolar terms) 而  $\gamma^{AB}$  則是極化的項目(polar terms)可以分成電子接受態(electron acceptor;  $\gamma^+$ )和電子提供態(electron donor;  $\gamma^-$ )，i 則為固、液、氣相中某一相的代號。本研究透過 Young-Dupre equation 也就是下面所列的(3-2)式可以推算出固液之間的界面的表面張力。

$$(1 + \cos\theta)\gamma_L = 2(\sqrt{\gamma_s^{LW} \gamma_L^{LW}} + \sqrt{\gamma_s^+ \gamma_L^-} + \sqrt{\gamma_s^- \gamma_L^+}) \quad (3-2)$$

其中三個液體的  $\gamma^{LW}$ 、 $\gamma^+$ 、 $\gamma^-$  的值如下：

|         |                                     |                                  |                                  |

|---------|-------------------------------------|----------------------------------|----------------------------------|

| Water : | $\gamma^{LW} = 21.8 \text{ mJ/m}^2$ | $\gamma^+ = 25.5 \text{ mJ/m}^2$ | $\gamma^- = 25.5 \text{ mJ/m}^2$ |

| DIM :   | $\gamma^{LW} = 29 \text{ mJ/m}^2$   | $\gamma^+ = 1.92 \text{ mJ/m}^2$ | $\gamma^- = 47 \text{ mJ/m}^2$   |

| EG :    | $\gamma^{LW} = 50 \text{ mJ/m}^2$   | $\gamma^+ = 0 \text{ mJ/m}^2$    | $\gamma^- = 0 \text{ mJ/m}^2$    |

將表 3-1 所整理出來的結果和上面的值帶入(2)式做聯立方程式解可以分別得到下面的結果，然後再代入(3-1)式可以得到膜的表面能。運算結果如下：

|                       |                                       |                                    |                                   |                                    |

|-----------------------|---------------------------------------|------------------------------------|-----------------------------------|------------------------------------|

| Ir film :             | $\gamma^{LW} = 39.565 \text{ mJ/m}^2$ | $\gamma^+ = 3.611 \text{ mJ/m}^2$  | $\gamma^- = 0.055 \text{ mJ/m}^2$ | $\gamma_s = 40.456 \text{ mJ/m}^2$ |

| $\text{SiO}_2$ film : | $\gamma^{LW} = 36.705 \text{ mJ/m}^2$ | $\gamma^+ = 31.208 \text{ mJ/m}^2$ | $\gamma^- = 0.897 \text{ mJ/m}^2$ | $\gamma_s = 47.286 \text{ mJ/m}^2$ |

由此可知在不同膜的表面能差異，本實驗數據透過接觸角所求得的表面張力來解釋在固—固介面所發生的行為[22]，在固體和固體之間存在一個界面能(interface energy)  $\Delta G$  其示意圖如圖 3-3。

界面能可以表示成和這三種表面張力相關：

$$\Delta G \propto \gamma_{BV} - \gamma_{AV} + \gamma_{AB} \quad (3-3)$$

圖 3-3 固體和固體之間的表面張力示意圖[22]。

而在固—固界面的時候有三種成長模式：

(1)  $\gamma_{AV} > \gamma_{BV} + \gamma_{AB} \rightarrow$  Frank—Van der Merwe Growth :

此種模式為界面能  $\Delta G < 0$  固體會和固體兩者之間會成為層狀結構，也就是形成完整的膜(圖 3-4)。

圖 3-4、Frank- Van der Merwe Growth 的示意圖[22]。

(2)  $\gamma_{AV} < \gamma_{BV} + \gamma_{AB} \rightarrow$  Vollmer-Weber Growth ( “V-W” ) :

此種模式為為界面能  $\Delta G > 0$  的時候上層的膜會內縮成球狀以求表面能和界面能能達到最小值如圖 3-5。

圖 3-5、Vollmer-Weber Growth 的示意圖[22]。

(3) Stranski-Krastanov Growth ( “S-W” ) :

由於第一層和第二層膜之間有不同的晶格常數(lattice constant)，造成應力的方向分布不均勻以至於上層的材料在內聚時會受到應力方向而有不同方向的應變，例如 Ge 在 Si(001)上面結球的狀況如圖 3-6。

圖 3-6、Stranski-Krastanov growth 的示意圖。

從接觸角所量測到的表面張力，數據代入 3-3 式可以得到  $\Delta G \propto -7 + \gamma_{AB}$  AB 為 Ir 和 SiO<sub>2</sub> 之間的界面的表面張力，由於本研究無法從現有的儀器中直接推估  $\gamma_{AB}$  的值，但是從上面的理論來推測，在未經過熱處理前，平衡狀態為  $\Delta G < 0$ ，所以會形成層狀結構。

而在熱處理的時候，當熱能到達某個臨界值的時候會影響到界面能的能量使得  $\Delta G > 0$  進入 Vollmer-Weber Growth 的模式，也就是使上層的膜產生內聚的現象，這也是為什麼本研究可以透過 RTA 的製程來製作 nanocrystals。

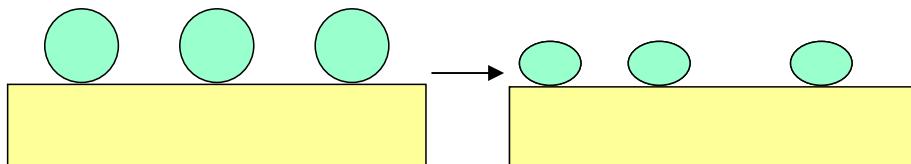

### 3-1-2 機台金屬膜厚度的確認

由於 Ion beam sputter 是本實驗是新進的儀器，對於裡面的靶材材料和膜厚的數據沒有相關的資料庫，再加上它是屬於 PVD 製程的機台，厚度會隨著操作者的習慣、Ar 氣體流量、QCM 不能專一偵測同種靶材等因素產生實際膜厚的差異。因此在展開奈米晶體的研究的時候，薄膜真實的厚度在研究過程裡扮演了十分關鍵的參數之一，所以本研究必須去做 TEM 橫剖面圖並且予以校正。採用的作法為 Si 晶片上成長一層 7nm 的 thermal oxide 之後再用 Ir 靶材在 Sputter 機台中轟擊約 1 分 44 秒，QCM 顯示頻率為 1.5nm，之後利用 PECVD 疊上 20nm 的 TEOS oxide。下一步則是分別透過 SEM 室的 JEOL JFC-1600 Auto Fine coater 把 Pt 用 10mA 滅鍍 20s 和離子束聚焦顯微鏡(Focus Ion Beam；FIB)在開始切橫剖面的 sample 前再度滅鍍一層 Pt，之後把試片送去 TEM 作確認。如下頁圖 3-7 為 TEM 橫剖面圖，圖中由左而右依序顯示 Si-sub、SiO<sub>2</sub>、Ir、TEOS SiO<sub>2</sub>、Pt(sputter)和 Pt(FIB)。因此可以從 TEM 的比例尺中去反推 Ir 的厚度，從圖中得到當 QCM 為 1.5nm 的時候實際上 Ir 為 4.5nm。

圖 3-7 金屬膜厚度 TEM 橫剖面圖。

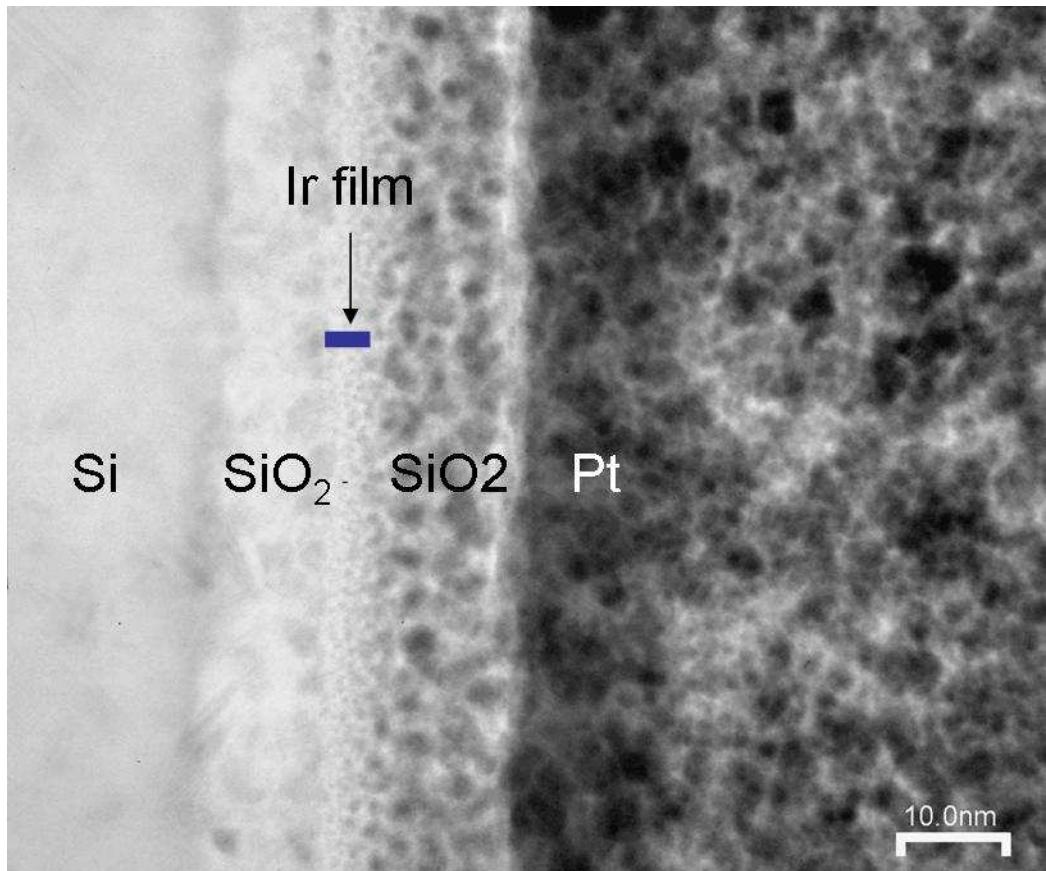

### 3-1-3 溫度對奈米晶體變化

3-1-1 討論到透過 RTA 製程來製造奈米晶體，但是如果溫度不夠的話，熱能無法有效影響到界面能即無法大於 0( $\Delta G > 0$ )，沒有足夠能量形成奈米晶體。因此本研究首先對於溫度作相關的研究。由於選擇的材料在金屬狀態的時候熔點為  $2466^{\circ}\text{C}$ ，屬於高溫的金屬，因此本實驗參考 Pt 和 W 的製造條件，再搭配吾人傳統 CMOS 製程可能遇到的溫度，本研究選定從  $600^{\circ}\text{C}$ 、 $700^{\circ}\text{C}$ 、 $800^{\circ}\text{C}$ 、 $950^{\circ}\text{C}$  的區間去做研究，在 RTA 之後透過 SEM 和 AFM 去做奈米晶體確認的動作。

在這一小節調變的參數為溫度，起始的金屬膜膜厚在經過 TEM 的校正之後推估在 6 nm，而 RTA 時間皆為 60s。結果如下頁圖 3-8 和 3-9，從圖片中可以明顯的看出在  $700^{\circ}\text{C}$  以前沒有奈米晶體的形成，圖 3-8 的(a)則為 particle 非 Ir-NCs，而  $800^{\circ}\text{C}$  圖 3-8(b)的時候溫度的變數已經對 Ir 的膜開始有反應了，然而  $800^{\circ}\text{C}$  所能提供的熱能並不能讓奈米晶體的形狀一致，並且密度也不夠高。

而  $950^{\circ}\text{C}$  的圖片可以看到 Ir 奈米晶體的形狀接近球狀，而在五萬倍(圖 3-9)的 SEM 圖中可以看出其均勻性有顯著的提升。而放大到圖 3-8 的(c)十萬倍時用 SEM 的影像初估奈米晶體的大小有落在  $20\text{nm}$  的範圍，而有些奈米晶體還無法成型，因此像個條狀的形狀。

圖 3-8、經過 RTA  $700^{\circ}\text{C}$ 、 $800^{\circ}\text{C}$  和  $950^{\circ}\text{C}$  60s 热處理的 SEM 圖。

造成這現象可能的原因為之前 1-2 文獻提到的因素，起始的金屬膜厚所影響奈米晶體的大小和退火時間等因素，這些在後面的小節會做相關的討論。

圖 3-9、圖 3-8(c)的五萬倍 SEM 影像圖。

### 3-1-4 初始金屬膜厚度對奈米晶體變化

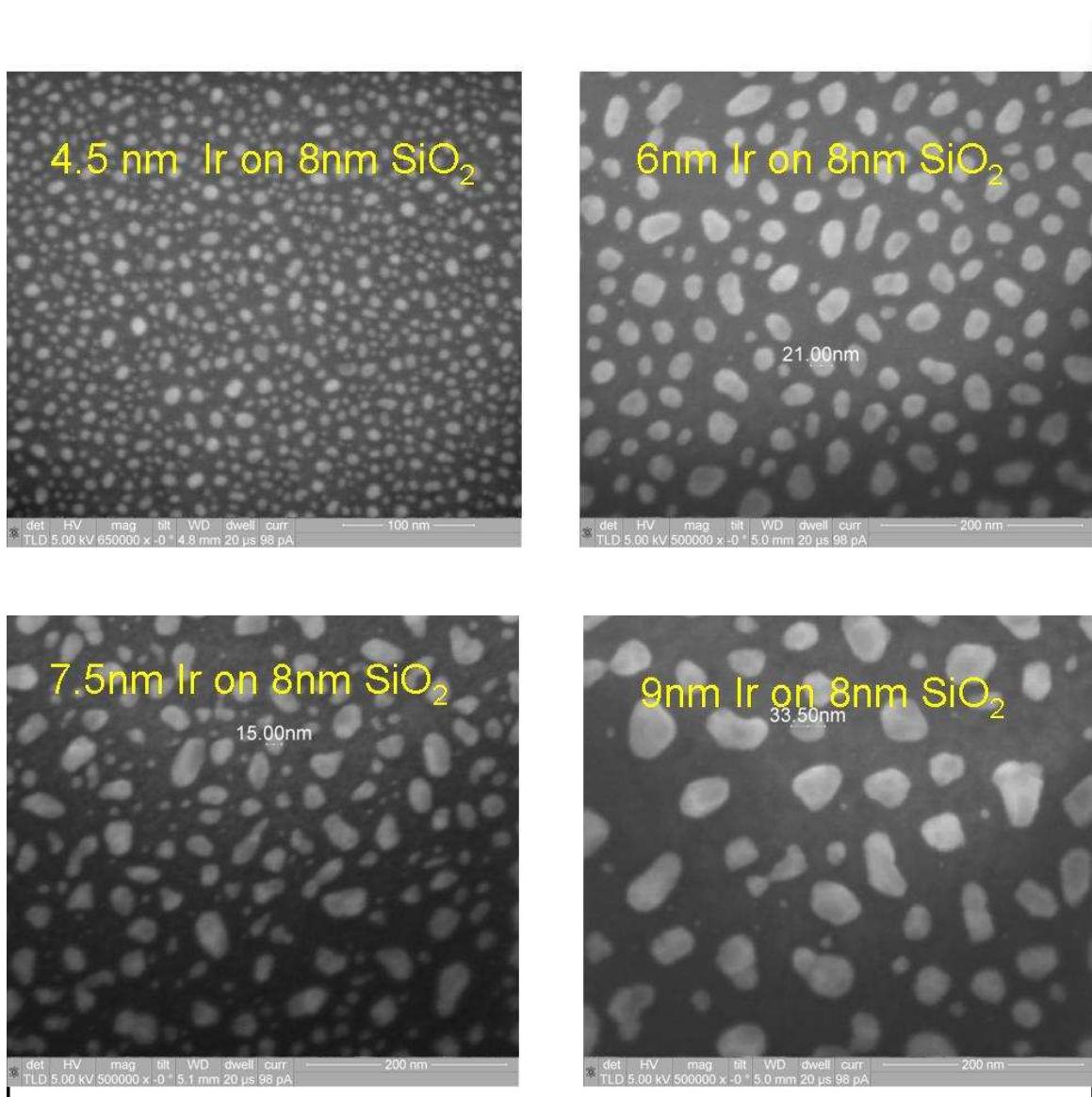

在 1-2 的文獻回顧的單元裡面有提到金屬膜厚度會影響在相同 RTA 热處理過後的奈米晶體的表面形貌以及密度。在圖 1-8 提到金在不同尺寸下有不同的熔點，相同的在 Ir 金屬膜上也有類似的特性，因此當在上一小節成功測試出在何種溫度下做 RTA 热處理製程能有效形成 Ir 的奈米晶體。開始繼續往下研究，本小節著手在起始的 Ir 金屬膜上做研究。

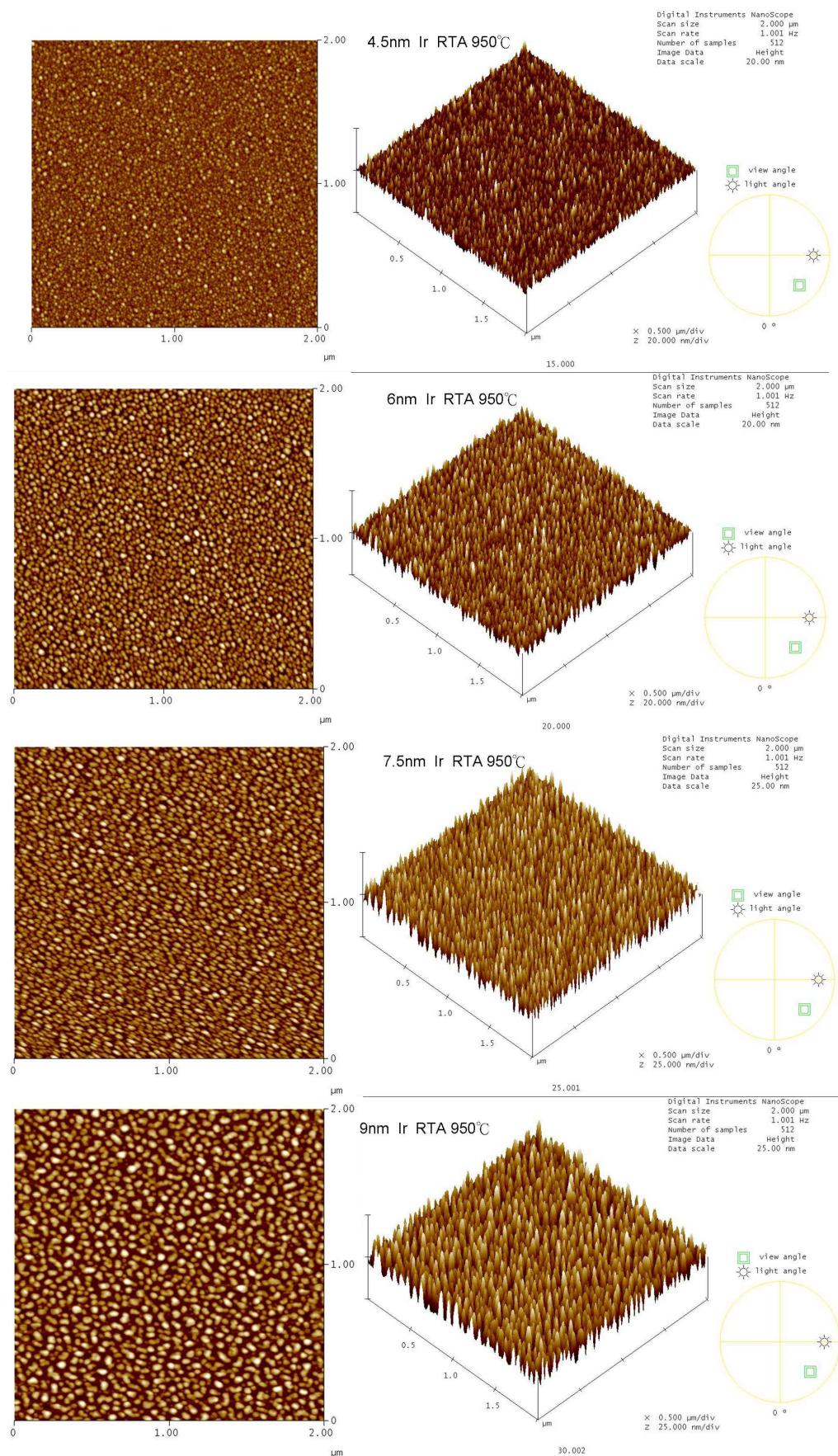

此實驗試著減少或增加膜的厚度，也就是透過 sputter 時間的減少或是延長來做控制，上一節的主題所測試的樣品 Ir 厚度為 6 nm，因此以此為底加減膜厚，也就是做了 4.5 nm、6 nm、7.5 nm、9 nm 的起始厚度的 Ir 金屬膜，經過同樣的 950°C 60 秒的熱處理之後用 SEM 和 AFM 去做分析，如下頁圖 3-10 和 33 頁的圖 3-11。

圖 3-10、不同金屬膜厚度在 RTA 950°C 60s 热處理後 SEM 影像。

圖 3-10 和圖 3-8 的影像略有不同，原因是因為圖 3-10 是利用 FIB 中的 SEM 所拍到的影像為 50 萬倍，和所上的 SEM 極限 20 萬倍有一大段的差距，不過可以在圖 3-10 的 6 nm Ir metal film RTA 過後的 SEM 圖中可以重複確認其再現性—奈米晶體在此條件下結成球狀的大小剛好落在之前所提到的 20 nm。

圖 3-11、不同金屬膜厚度在 RTA 950°C 60s 热處理後 AFM 影像。

圖3-11為不同厚度的Ir膜經過RTA 950°C 热處理的DI AFM(diffractiion ion AFM)影像，從2-D和3-D立體圖中可以明顯看到Ir起始膜厚所造成的變化，不只在SEM上看到的平面形狀的變化，越厚的起始金屬膜造成的roughness會越大，這是因為奈米晶體內縮是一個三維空間的過程也就是Vollmer-Weber Growth模式，奈米晶體的成長會往降低界面能的方向進行，因此在這裡可以看到AFM影像上的變化，也相對驗證SEM所看到的趨勢：當初始膜越厚的時候實驗上得到的奈米晶體大小越大，形狀也越不均勻，而密度也隨著奈米晶體越大而降低。

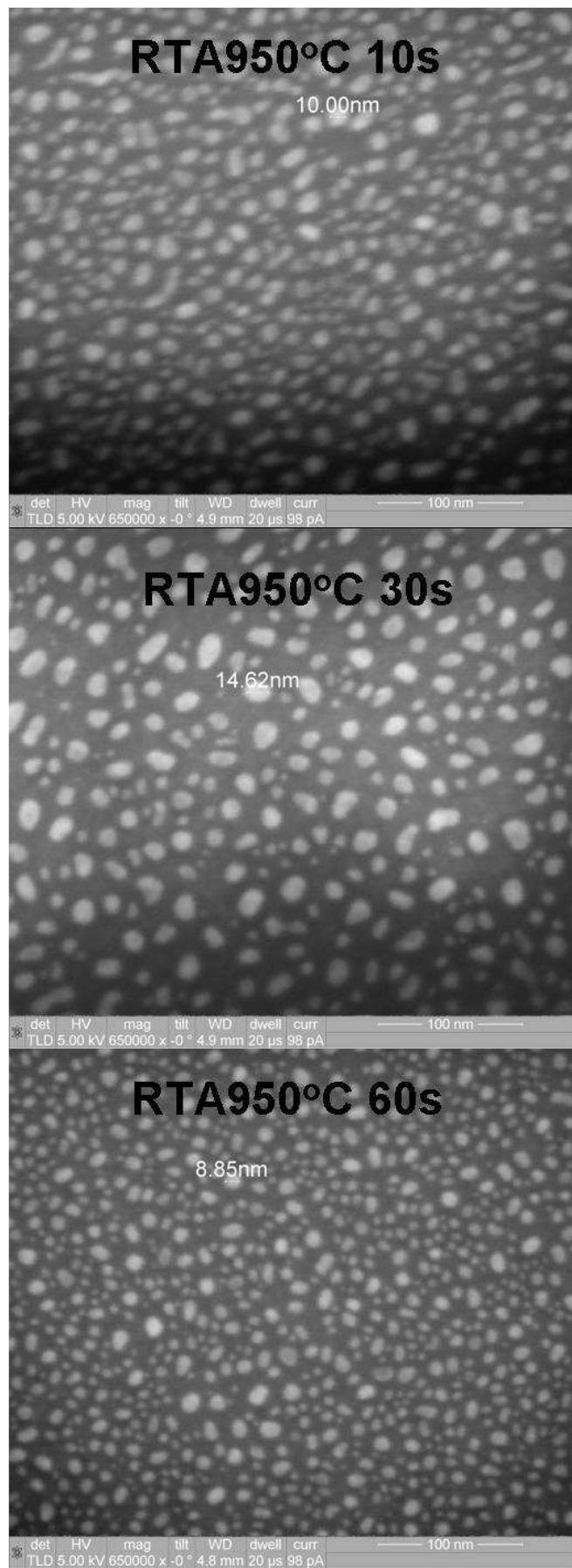

### 3-1-5 热處理時間對奈米晶體變化

從上一小節的研究中我們可以對於初始金屬膜厚度對奈米晶體變化、溫度對奈米晶體變化這兩項參數中可以得到一個較佳的條件，本研究以 Ir 4.5 nm 的初始金屬膜和 950 °C 的溫度為條件繼續往下作時間相關的研究。

實驗設計為 60 秒為底，往上減少時間和秒數，這是因為 RTA 機台在 950°C 的高溫環境下容易在長時間持溫之後，溫度會往上飄移，造成變數增加，使得吾人無法做有效的分析。因此本實驗採用降低 RTA 時間的參數來研究其趨勢。在這個小節的實驗選擇三種參數 10 s 、 30 s 和 60 s 。

在經過不同 RTA 時間之後將試片拿去拍 SEM 如下頁圖 3-12，可以發現 10 秒的時候就已經有奈米晶體的形成，代表 950°C 已經突破 Ir 金屬膜的熔點，因此已經開始產生變化，然而持溫的時間太短，以至於提供的熱能(thermal energy)不夠讓已經成核的點開始把 Ir 內聚在一起，所以我們 RTA 950°C 10s 的條件下的 SEM 圖，能看到許多條狀和不規則形狀的 Ir ；而 30 秒的 SEM 圖則可以發現，Ir 的形狀變的比較均勻和一致，但是大小大概都落在 14~28 nm 左右，表示增加持溫時間也增加了 thermal energy 以致 30 秒的表面形貌會比 10 秒的表面形貌來的均勻和一致，然而在 60 秒的時候可以從 SEM 的影像看到足夠的 thermal energy 讓 Ir 能夠內聚在一起，60 秒的圖提供了 NCs 的大小大約為 8 nm 上下，比 30 秒的時後更加縮小了一點，這三張圖顯現出持溫時間對於奈米晶體形狀和大小的影響。

圖 3-12、RTA 950°C 對於不同時間變化的 SEM 圖。

Ir 奈米晶體的形狀和持溫時間的關係圖也間接說明了之前在 3-1-1 利用接觸角量到的表面能和 Vollmer -Weber Growth 理論所推測出來的行為假說符合，因此吾人可以在許多奈米晶體製備的相關文獻中看到他們都強調對於熱能的改變即熱處理的參數調配的重要性。

### 3-1-6 奈米晶體的 XPS 圖譜

由於某些金屬在經過某個條件下熱處理的製程之後金屬可能會發生鍵結的改變，例如本實驗室也在發展的 Ni silicide 的研究，便是利用此現象來完成元件的製作。這個原因是由於熱能所提供的能量不會只轉化成單一種能量，也就是實際上無法要求熱能能夠完全轉移到能改變形狀的界面能能量上，一些熱能甚至會轉移到提供化學反應的反應能，利用此反應能小於 0 的時候來發生化學反應產生界面之間的鍵結(如： $\text{NiSi}_2$ )，有些熱能會提供物體修補缺陷的能力，也就是材料界常稱的回復(recovery)機制，然而更多的熱能會選擇散失的方法以致於無法有效利用其能量。

雖然熱能是不易控制的能量，但是卻也是人們最容易製造出來的能量之一，因此即使擁有無法專一性轉化的缺點，吾人還是經常利用熱處理的方法去製備奈米晶體。在奈米晶體的實驗上必須要注意的是在熱處理的過程，能量是否引發奈米晶體產生化學反應形成 silicide 或者是我們不想要的化合物，因此我們必須用到 X-ray photoelectron spectroscopy (XPS)來分析其成分是否有變化，確保實驗中的奈米晶體為純的金屬奈米點，而不是化合物。

在分析 XPS 的資料之前必須先去收集 Ir 的 XPS 資料，參考 Handbook 所提供的 Ir 在 XPS 分析的資料如下頁圖 3-13[23]，從圖上可以看到 Ir 4f 的 peak 分成兩個峰值一個是  $4f_{7/2}=60.9\text{eV}$ ，另外一個則是  $4f_{5/2}=64\text{eV}$ ，因此在這一節的實驗拿兩種試片一個是經過熱處理形成 Ir 奈米晶體的試片，另一個則是沒經過 RTA 處理的 Ir 膜，接者利用同步輻射中心 U5 光束線進行 XPS 分析。由於光束線(Beam line)每做完一次 XPS 的分析後，光源的波長會有所變動，因此我們必須在同一個分析過程裏面拿其他元素的資料來做 XPS 校正才能確保實驗的資料是正確可靠的。由於奈米晶體的試片是把 Ir-NCs 佈植在  $\text{SiO}_2$  上，所以必須透過 Si 的特徵峰來做校正 XPS 的圖譜的動作如圖 3-14。之後才能準確判斷兩種條件的 Ir peak 的位置是否正確。

圖 3-13、Ir 在 XPS 圖譜裡的 Character peak[23]。

圖 3-14、以 Si 的特徵峰值去做 XPS 校正的動作。

圖 3-15、經過熱處理的 Ir 奈米晶體和未熱處理過的 Ir 膜的 XPS 的比較。

從圖 3-15 可以發現經過我們  $950^{\circ}\text{C}$  RTA 热處理的試片和未經過熱處理的 Ir 膜的試片，兩者之間並沒有發生峰值的 shift 的現象，這個資料可以證明我們的試片並沒有因為高溫的熱處理所產生的熱能而產生 silicide 或者是產生其他可能的化合物，因此我們推定我們所形成的 NCs 是屬於純金屬的 Ir 奈米晶體。

## 3-2 結論

在上一節透過 Vollmer-Weber Growth ( “V-W” )的理論和其他參數的變動來驗證並推測奈米晶體的形成機制，也透過 TEM 和 XPS 兩項儀器的輔助，來增加本實驗的嚴謹性以及重覆確認我們的實驗目標以及方向的正確性。

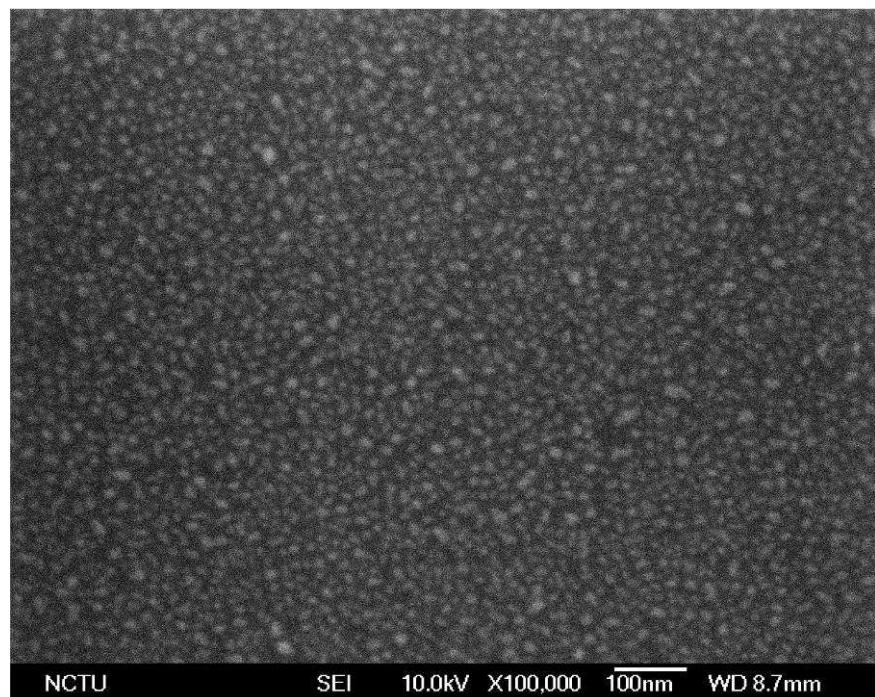

綜合 3-1 所討論的項目和條件，我們找到一個較佳的條件，這個條件為 Ir 4.5nm 的

厚度經過 RTA 950°C 60s 的熱處理。我們得到的結果如圖 3-16，奈米晶體在此條件下平均大小為 8nm，密度則為  $6 \times 10^{11}/\text{cm}^2$ 。我們在這裡暫時結束奈米晶體繼續深入的研究，下一章就開始應用目前較佳的條件去試著應用在電容和元件上面。

圖 3-16、即將應用在電容和元件上的 Ir-NCs 的 SEM 圖。

# 第四章

## 電容及元件量測與討論

### 4-1 電容的量測

本章接續上一章的實驗，也就是應用 Ir 的奈米晶體的形成條件，製作出電容和元件，在電容部份由於構造相對簡單，因此可以驗證一些理論並且可以排除在多道製程手續後產生人為或是機器的誤差，以下是對於電容各項條件的實驗與分析。

#### 4-1-1 電容能帶設計

在 1-2 文獻回顧的時候提到含有奈米晶體的元件皆是透過能帶設計讓奈米晶體發揮電荷捕抓中心(charge center)的功用。由於電容(capacitor)是記憶體元件的前驅物，因此我們利用電容的結構，簡單的來介紹我們的電容能帶的結構，以及讀寫時的能帶變化示意圖。

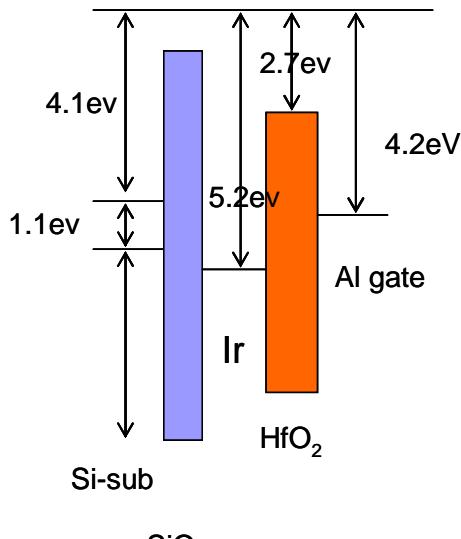

圖 4-1、電容能帶示意圖。

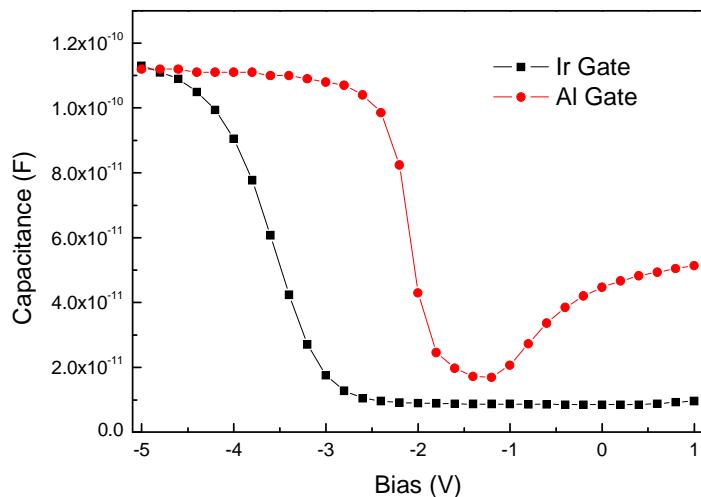

本實驗的電容構造以及製備在 2-2-2 的電容實驗流程中已經提過了，而採用的 High- $\kappa$  材料  $\text{HfO}_2$  能隙(bandgap)為 6eV 而  $\text{SiO}_2$ eV 的能帶為 9；Al 電極的功函數則為 4.2，而吾人研究的主軸 Ir 奈米晶體功函數約 5.2eV。依照文獻上的數據畫出本研究的電容能帶示意圖(Band offsets of capacitor)如圖 4-1。圖 4-1 是電容在尚未加電壓的能帶圖此時就可以看到 Ir-NCs 所提供的深位能井。而圖 4-2 則是前文 2-1-2 所提到利用 F-N tunneling 機制來彎曲能帶進行電子儲存在 Ir-NCs 裡面(program)或是進行電子的移除(erase)；而在電子儲存在 Ir 的時候會造成位能井的變化類似圖 2-3，此時如果電壓操作在出現 F-N tunneling 之下時候，電子不會受電壓的影響而改變它所在的能階，我們稱此時量到的電壓值為 read 的狀態。紀錄、抹除和讀取的三種能帶示意圖如圖 4-2。

圖 4-2、電容能帶三種操作狀態示意圖。

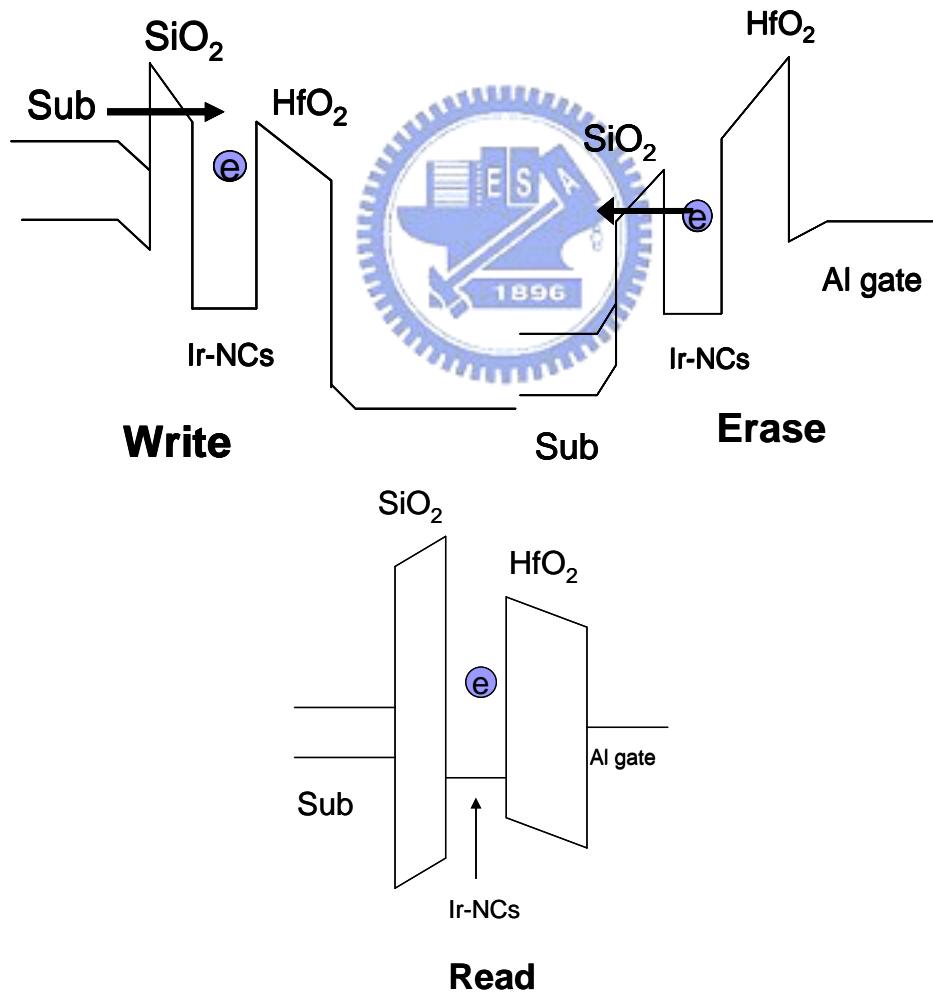

#### 4-1-2 金屬功函數的測試

上一節簡單的介紹本實驗的能帶結構，但是由於上一節是根據文獻資料所繪製的能帶圖。因此本研究為了在實驗上求嚴謹，再加上 Ir 是比較不常見到的材料，所以對於 Ir 的功函數仍然必須用實驗來輔助驗證其功函數的差別。

驗證的方法其實很簡單，在  $\text{SiO}_2$  上製作兩種金屬 gate，一個是廣為大家使用的 Al gate 而另外一個則是本實驗採用的奈米晶體的材料所製作出來的 Ir gate。也就是類似傳統的 MOS 結構只是將金屬分成兩種來做比較。測試的方法很簡單，利用 C-V 的曲線來做分析與比較。透過 4-1 式可以得到功函數和電容值對於  $V_{FB}$  的關係。

$$V_{FB} = \phi_{ms} - \frac{Q}{C_{ox}} \quad (4-1)$$

而 Al 的功函數  $\phi_{ms} = 4.2\text{eV}$ ，為了簡單有效的驗證，假設兩邊的  $C_{ox}$  是完美(perfect)的 oxide 層因此，兩個試片量測 C-V 所產生 Flat-band voltage shift( $\Delta V_{FB}$ )則會因為  $\frac{Q}{C_{ox}}$  互

相抵消而轉化成下列 4-2 式，

$$|\Delta V_{FB}| \approx |\phi_{ms}^{\text{Al}}| - |\phi_{ms}^{\text{Ir}}| \quad (4-2)$$

根據量測到的 C-V 圖(如圖 4-3)可以看到 Ir gate 和 Al gate 的差異，而從圖中也可以明顯看到  $\Delta V_{FB}$  的值落在 1.2V 左右，代入到 4-2 式即可得到 Ir 的功函數約為 5.4eV。

圖 4-3、Ir gate 和 Al gate 的 C-V 曲線圖。

而在參考文獻[24]所提到的 Ir 在不同晶向會有不同的功函數，如下表 4-1。Ir 的平均功函數為 5.27eV 這和我們所測量到的 5.4eV 有點出入，可能的原因為本實驗在假設的時候忽略了氧化層的缺陷和厚度的差異，所造成的高估；另外一個可能的原因或許就如文獻提到的線索，即是所採用的 Ir 奈米晶體的生成會沿著某一個晶向的反應較好，因此拉高了 Ir 的所計算出來的功函數。只是這方面的驗證必須利用高解析度電子顯微鏡(HRTEM)拍攝出繞射影像(diffractio image)等方法才能做更進一步的確認。

表 4-1、Ir 不同晶向及功函數的差異[24]。

|                         |                   |

|-------------------------|-------------------|

| Ir<br>$\Phi(\text{eV})$ | 5.27(平均值)         |

|                         | $\Phi(\text{晶向})$ |

|                         | 5.42 (110)        |

|                         | 5.76 (111)        |

|                         | 5.67 (100)        |

|                         | 5.00 (210)        |

#### 4-1-4 穿隧氧化層厚度的影響

不同的穿隧氧化層(tunnel oxide)厚度對於電容結構會有重要的影響，tunnel oxide 越厚，電荷要穿透到 Ir-NCs 的機率越低，換句話說若要儲存電荷必須加上更大的電壓才能到達 Ir 的奈米晶體的位能井；然而太薄的 tunnel oxide 則相反，電荷容易穿隧過去，也意味著所加的電壓可以下降，但是卻有個致命傷就是電荷保存能力下降，奈米晶體所存的電荷會很容易的流失。這點可以從 C-V 圖(圖 4-4)獲得印證，4nm 的  $\text{SiO}_2$  所儲存電荷能力較高，但是相對也容易流失因此實驗裡可以看到 4 nm 的  $\text{SiO}_2$  曲線形狀是不完整的磁滯曲線。相對 8 nm 的  $\text{SiO}_2$  的曲線則是完整的磁滯圖形只是儲存的電荷較少所以 memory window 較小。由此可知電荷的移動能力和電荷保存能力是兩者無法兼得，所以為了有完整的 C-V 曲線，本論文仍然依照 ITRS 預測的 8 nm 左右  $\text{SiO}_2$  為條件做電容結構來測試 Ir 金屬奈米晶體。

圖 4-4、穿隧氧化層厚度對 C-V 圖的影響。

#### 4-1-4 阻絕氧化層的測漏電

由於 high- $\kappa$  材料必須經過 E-gun 製備因此會有許多的缺陷(defects)，而這些缺陷會使得儲存的電子受到影響，造成 C-V 曲線的不一致，而這種電性上的不一致對於做電子方面的應用是一個很大的問題。因此需要一個能調控的參數來減少物理氣相沉積(PVD)製程所造成的缺陷，而熱製程對於(defects)缺陷的修補是最好的應用方法，因為缺陷的地方通常都是(free energy)自由能比較高的地方，對熱能的變化會比較敏銳，而這些熱能讓缺陷能夠有動力去修補起來降低其自由能。

因此本研究對於修補方面設計了三種參數，由於阻絕氧化層(blocking oxide)是屬於後段的製程，為了不要影響到前段的製程的條件，吾人把溫度範圍降低到以爐管的待機溫度為主也就是溫度鎖定在 400°C 為主。在阻絕氧化層疊完之後分為三種狀況來測試修補的現象：

- (1) RTA 400°C 1 min

- (2) 爐管 400°C 30 min 期間充滿氧氣(O<sub>2</sub>)

- (3) 爐管 400°C 30 min 期間充滿氮氣(N<sub>2</sub>)

而其他的製程就如第二章所列的電容製程一樣，只是排除加入 Ir-NCs 的手續以減少我們分析的變數。

製作完的結構拿來做 I-V 側漏電測試如圖 4-5 和 C-V 的電容測試如下頁圖 4-6，我們測試的結果中可以發現從 I-V 和 C-V 的方面 RTA 1min 的環境下對於阻絕氧化層的修復是最少的，而爐管的部份和 RTA 相比起來有顯著的進步，這驗證了前文所提到的熱能對於缺陷修補的能力的貢獻。

圖 4-5 HfO<sub>2</sub> 不同的修補條件下的 I-V 圖。

從實驗過程中進一步來探討爐管在不同條件下造成電性上差異的原因，由於 HfO<sub>2</sub> 是透過物裡氣相沉積(PVD)來製作的，因此在鍵結的部份通常較不如利用化學氣相沉積的完全，PVD 較易形成 HfO<sub>x</sub> 的結構，因此必須藉由熱處理的過程來修補結構的不完整，而通入氧氣比通入氮氣漏電還少的原因推測為氧氣可以直接提供 O 原子讓 HfO<sub>x</sub> 能直接

利用形成  $\text{HfO}_2$ ，而氮氣則沒有此效果，除了可以在圖 4-5 看到漏電的狀況的差異之外也能在下頁圖 4-6 從 C-V 圖的變化便可以知道缺陷修補的比較，因為氧氣修補缺陷較完整因此 defect trap 電荷的數目比較低，所以 C-V 曲線中所打開的 window( $\Delta V_{FB}$ )為最窄，因此吾人使用此條件進行製程的修補動作，也就是一般人所稱的 Densify 的動作。

圖 4-6  $\text{HfO}_2$  不同的修補條件下的 C-V 圖。

另外利用這個實驗也可以驗證材料的介電常數，根據圖 4-6 得到的電容值，透過 4-3 的公式，來計算介電係數的  $\kappa$  值。

$$C = \kappa \epsilon_0 \frac{A}{d} \quad (4-3)$$

$d$ =氧化層的厚度

$A$ =電極面積

$$\epsilon_0 = 8.85 \times 10^{-12} (\text{F/m})$$

本實驗厚度  $d=35\text{nm}$  而電極面積則為  $300 \times 300 \mu\text{m}^2$ ，而我們量到的電容值  $C = 35 \times 10^{-11} (\text{F/m})$  代入 4-3 式即可得到  $\text{HfO}_2$  的介電常數  $\kappa \approx 15.3$  與文獻提到的值為 15 接近。這也驗證了此材料在經過熱處理後仍然保有其介電常數。

#### 4-1-5 電容電性量測與分析

本小節分為兩大項目做量測分析，一個是電容的磁滯曲線也就是 C-V 圖另一個是對於記憶體元件最重要的量測項目也就是 retention time 代表我們的電荷的保存能力以下分別做細項介紹。

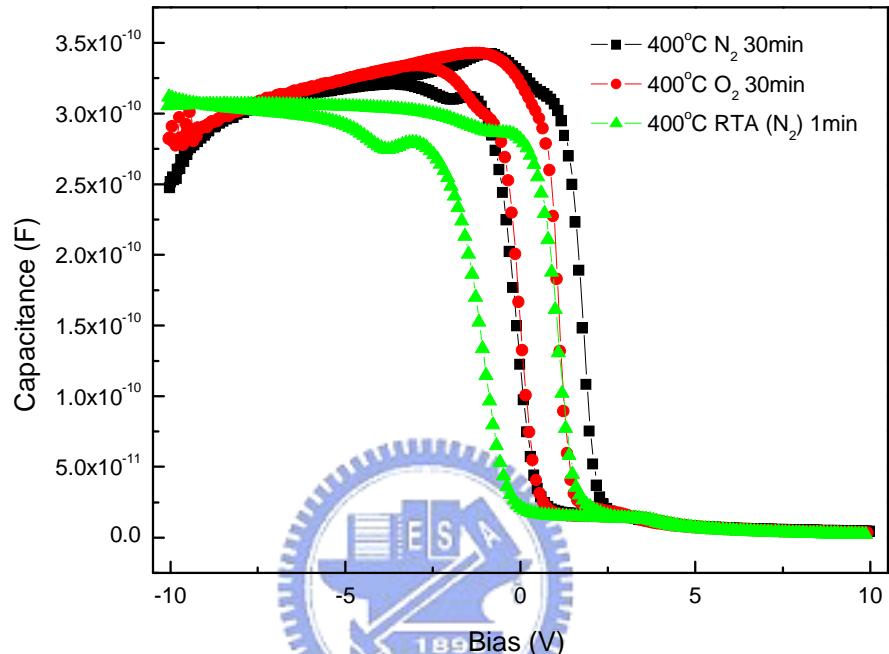

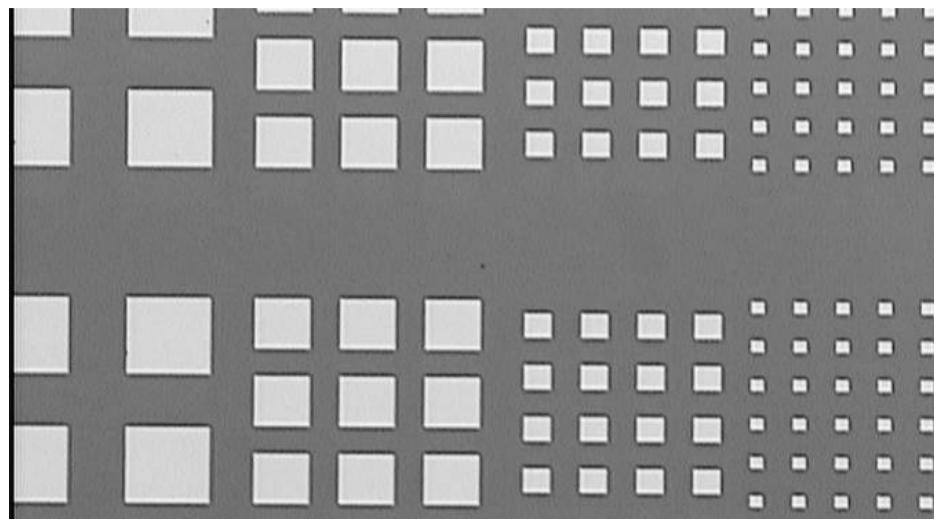

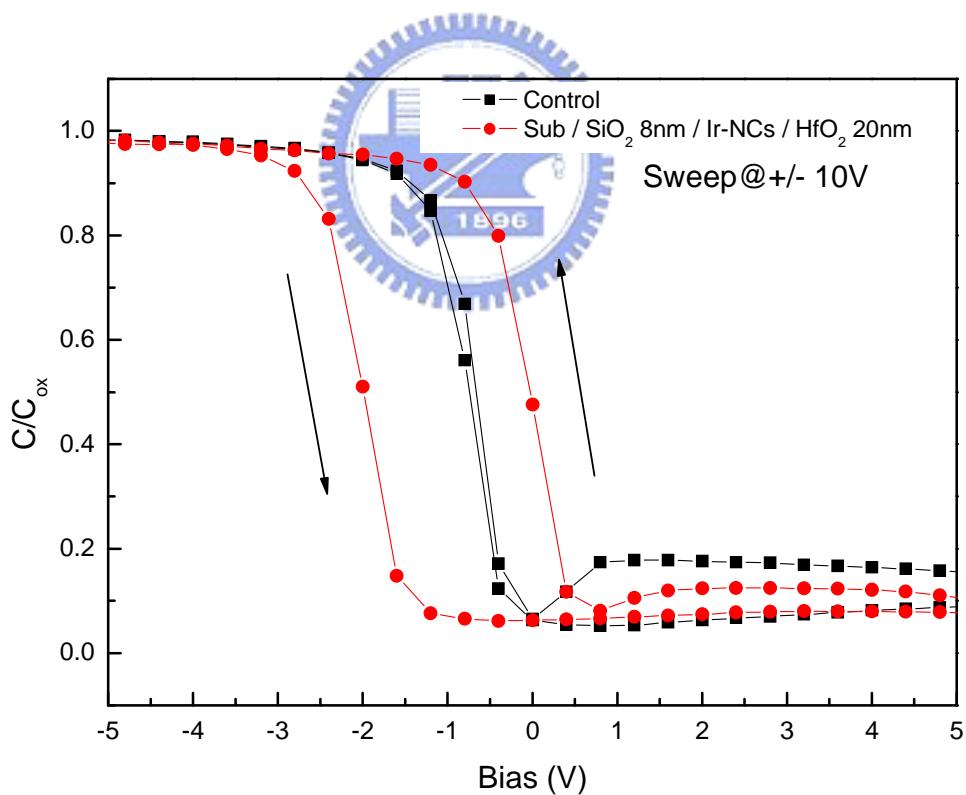

##### A. C-V 圖的量測

Ir 奈米晶體的電容成品的俯視圖如圖 4-7 可以看到，由左到右的差別為電極大小的不同從右邊的  $50 \times 50 \mu\text{m}^2$  到右二為實驗主要量測的  $100 \times 100 \mu\text{m}^2$  及左二的  $200 \times 200 \mu\text{m}^2$  和最左邊所顯現的  $300 \times 300 \mu\text{m}^2$ 。平帶電壓公式如下：

$$V_{FB} = \phi_{ms} - \frac{Q_{ss}}{C_{ox}} \quad (4-4)$$

其中  $Q_{ss}$  是等效的固定氧化物電荷，而  $\phi_{ms}$  則是金屬-半導體的功函數差。當一個奈米記憶體電容做出來之後， $\phi_{ms}$  和  $C_{ox}$  已經是個定值，因此當  $Q_{ss}$  變化時會產  $V_{FB}$  的位移。C-V 曲線會隨著氧化物電荷的參數變化而顯現平行的移動，然而，C-V 曲線會保持與理想特性相同的形狀。由本實驗量測的結果下圖 4-7，以純氧化層電容作為對照組(control 組)，由此實驗結果可推測我們的 Ir 奈米晶體在電荷捕捉時主要為捕捉電子。而對照組可證明本論文中的 Ir 奈米晶體能有效的儲存電荷，從圖 4-8 可以看的出來在經過+10~-10 之間的掃描(Sweep)可發現 Ir 奈米晶體可以大約開 2 V 的 memory window，即  $\Delta V_{FB} \approx 2 \text{ V}$ 。

圖 4-7、電容成品的俯視圖(OM)。

根據圖 4-8 可以推論並計算一個 Ir 奈米晶體所帶的電荷，此時利用下列的公式(4-5)來算出我們電容每平方公分所帶的電荷總量再利用，從 FIB SEM 所擷取的圖片中所估計到的奈米晶體密度即可得到每一個 Ir 晶體捕捉電荷的能力。

$$N = \left( \frac{C_{ox}}{Q} \right) \times \Delta V_{FB} \quad (4-5)$$

$$C_{ox} = 2 \times 10^{-11} \text{ (F)}$$

$$\text{又 } \Delta V_{FB} \doteq 2 \text{ V}$$

$$\text{電極面積 } 100 \times 100 \mu \text{m}^2$$

$$N \doteq 2.25 \times 10^{12} / \text{cm}^2$$

$$\text{奈米晶體密度為 } 6 \times 10^{11} / \text{cm}^2$$

每一個 Ir 奈米晶體能儲存大約 4 個電子或是電洞。

圖 4-8、Ir 奈米晶體與對照組的 C-V 圖比較。

本小節也測試了不同的電壓掃描(sweep)所帶來的變化，如下頁圖 4-9，可以明顯的看出當我們掃描的電壓越大時，會使電荷儲存在 Ir-NCs 的量越多，造成 memory window 越大( $\Delta V_{FB} \uparrow$ )，也可以看到我們的電容對於負偏壓的反應比較明顯，也說明了 Ir 奈米晶體對於電子比較敏感。

圖 4-9、不同偏壓對於 Ir-NCs 的 C-V 圖。

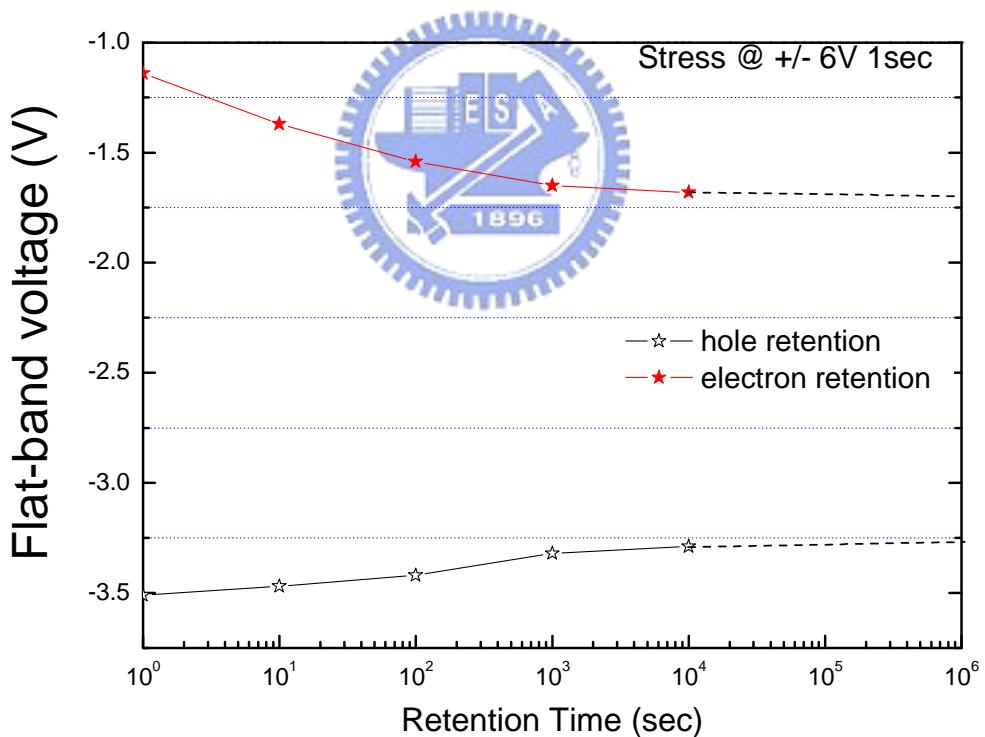

### B. 電荷保存力 (Retention)

電荷保存能力一直是記憶體元件應用上最重要的參考能力之一，因為非揮發記憶體的基本要求，即是所寫入的資料要必須能夠長時間保存，也就是我們將電荷困在 Ir-NCs 中來維持 $\Delta V_{th}$ 的值，維持邏輯上“1”和“0”的判讀能力。

我們量測的方法如下：

1. 找出 C-V 曲線的沒有開 memory window 的電壓(+2.5V~-2.5V)確認其狀態不會造成電荷的移動也就是圖 4-2 的 read 狀態。

2. 紿一稍大的電壓 Stress 一次(+6V 1sec)。

3. 縮小範圍掃 C-V 曲線(2.5V 到-2.5V)確認有  $\Delta V_{th}$ 。

4. 縮小電壓範圍掃其 C-V 曲線(2.5 V 到 0 V)。

5. 紀錄電容值，每隔一段時間區間重複步驟 4。

6. 從負方向給一較大的電壓再次 Stress(-6V 1sec)。

7. 縮小範圍掃 C-V 曲線(2.5V 到-2.5V)確認有  $\Delta V_{th}$ 。

8. 縮小電壓範圍掃其 C-V 曲線(0 到-2.5 V)。

9. 紀錄電容值每一段時間區間重複步驟 8。

量測結果如圖 4-10 我們可以發現電荷仍然會隨著時間的增長而收斂，不過從量測結果來看即使到  $10^4$  s， $\Delta V_{FB}$  仍然有約 1.6 V 的大小而這個大小也已經足夠被用來判別我們記憶體邏輯上“1”和“0”的狀態。

圖 4-10、Ir-NCs 電荷保存能力。

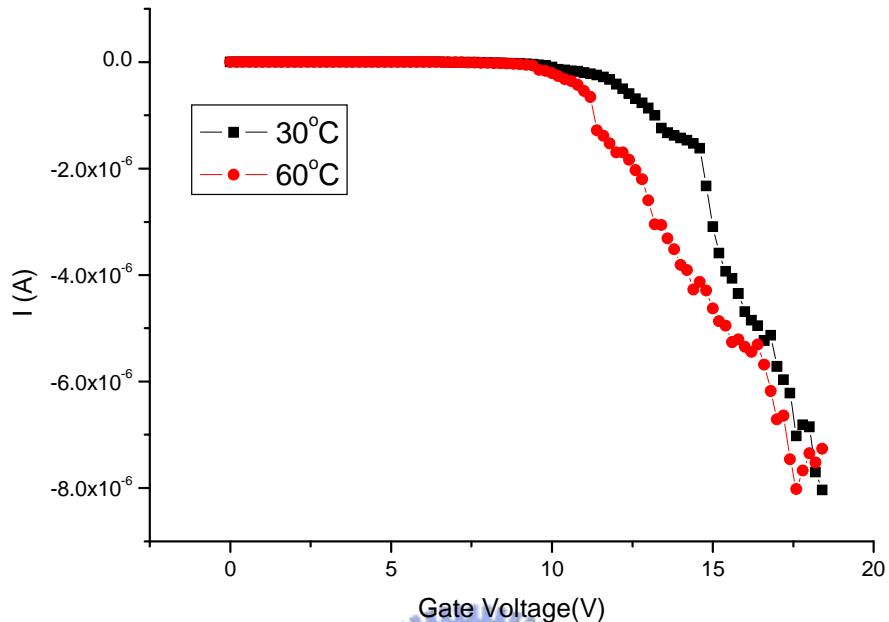

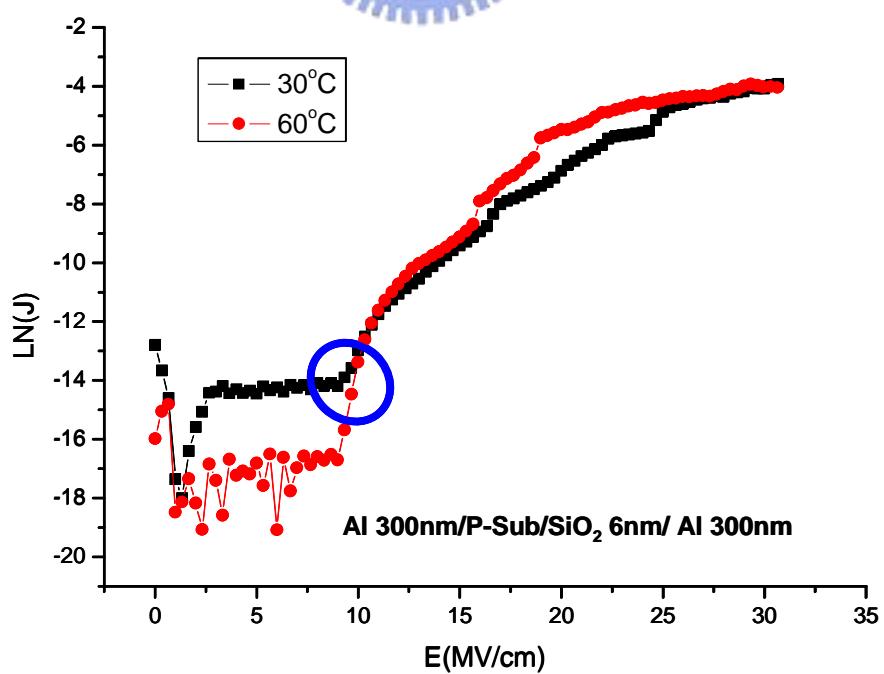

#### 4-1-6 F-N tunneling 的驗證

在 4-1-5 量完電容的特性和討論之後，接者必須驗證的是電荷以什麼形式進入到本論文所製作的 Ir-NCs 的位能井裡面。由於穿隧電流的萃取在量測上有其困難度，無法用整個電容結構去做這方面的驗證，原因其實很直觀，這是因為厚度太厚穿隧電流的取得會更加困難，因為就如 2-1-2 所提到穿隧電流是伴隨著能帶的彎曲(band bending)而產生，所以厚度越大就需要更大的電壓去扭曲，造成判讀上容易出現不一致，另一方面當夾層過多時所得到的電流可能會有其他機制參與其中例如 Hopping conduction、Frankel-Pool conduction 等。

因此為了驗證實驗中的電容是採用此 F-N 機制來讓電荷移動並儲存，採用了典型的 MOS 結構，中間氧化層的夾層經由 N&K 膜後測厚儀推算為 6 nm，金屬則為電極用的厚度 300 nm。將此元件拿去做 I-V 的量測。如圖 4-11 把電容加到 20 V 後可以發現電流在 9 V 附近的時候開始上升到  $10^{-6}$  的 order。將電流密度(J)取 ln 對電場(E)做圖可以明顯發現電流值在大約 10 MV/cm 時會開始出現大電流，這和實驗經驗所得到  $\text{SiO}_2$  在 10 MV/cm 時有穿隧電流的現象發生吻合。(參見圖 4-12)

取樣兩種不同溫度的原因是因為穿隧電流不會隨著溫度變化而改變，因此利用 F-N tunneling 的公式來進一步處理我們的數據，其公式如下[25]：

$$J = \alpha E^2 \exp\left[\frac{-E_c}{E}\right] \quad (4-6)$$

$$\text{移項取 ln} \Rightarrow \ln\left(\frac{J}{E^2}\right) = \ln \alpha - \frac{E_c}{E} \quad (4-7)$$

$$\alpha = \frac{q^3}{8\pi\hbar\phi_b} \frac{m}{m^*} = 1.54 \times 10^{-6} \frac{(m/m^*)}{\phi_b} \left(\frac{A}{V^2}\right) \quad (4-8)$$

$$E_c = 4 \sqrt{2m^*} \frac{\phi_b^{3/2}}{3\hbar q} = 6.83 \times 10^7 \sqrt{(m^*/m)\phi_b^3} \left(\frac{V}{cm}\right) \quad (4-9)$$

m:自由電子質量。

$m^*$ :電子在二氧化矽能隙中的有效質量(effective mass)。

$\phi_b$ :Si-SiO<sub>2</sub> 介面的能障高，單位為 eV。

由 4-7 式，將  $\ln\left(\frac{J}{E^2}\right)$  對  $\frac{1}{E}$  作圖，看圖形時是否為一直線來做判斷是否為 F-N tunneling。而在圖 4-13 可以明顯看到兩條接近平行的直線，而這個範圍便是 F-N

tunneling 機制的範圍，也是本研究電容工作電壓範圍，所以間接證明本研究的電容是操作在 F-N tunneling 機制下。

圖 4-11、兩種溫度下的電容 I-V 圖。

圖 4-12、兩種溫度下的  $\ln(J)$  對電場作圖。

圖 4-13、兩種溫度下的  $\ln(J/E^2)$  對  $1/E$  作圖。

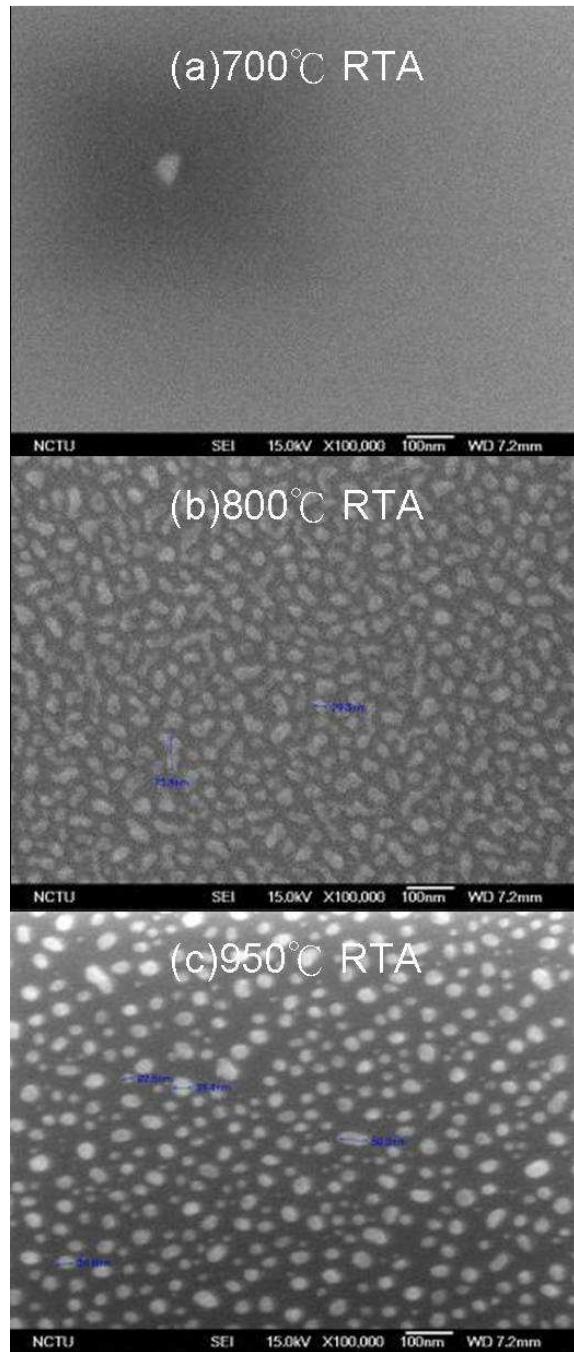

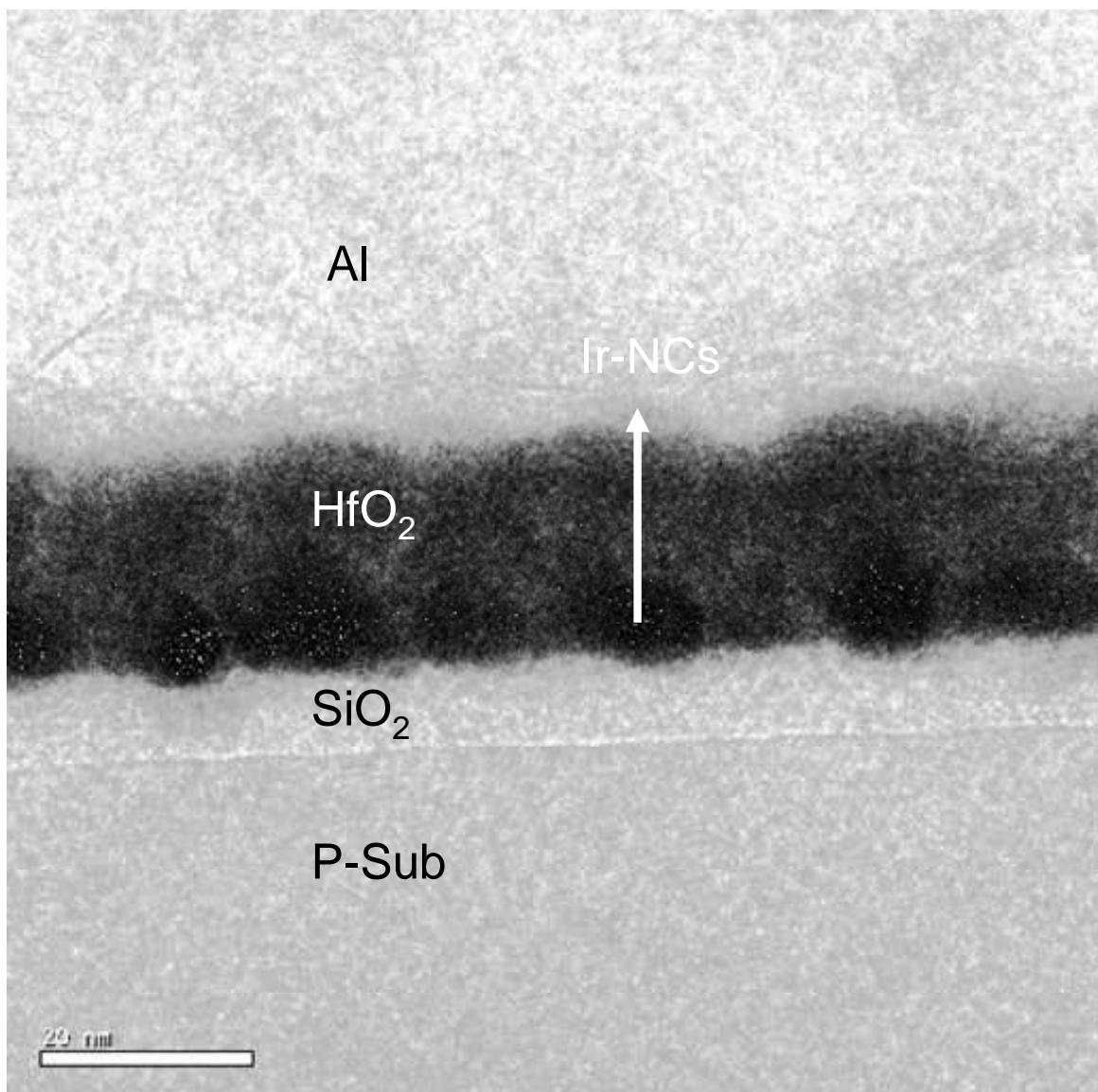

#### 4-1-7 電子顯微鏡拍攝電容剖面圖

雖然在 C-V 圖上可以明顯看到電性的改變，但是對於 Ir 奈米晶體的結構欠缺一個強而有力的證明，因此將量測之後的電容試片利用離子數聚焦顯微鏡(FIB)切出吾人要的橫剖面圖區塊之後，在利用奈米中心的高解析度場射掃描電子顯微鏡暨能量散佈分析儀(High-Resolution Cold Field Emission Scanning Electron Microscope & Energy Dispersive Spectrometer)來拍攝橫剖面影像。

成像如圖 4-14，在 4-14 可以發現 Ir-NCs 如第三章所討論出來的結果一樣，形成球狀佈植在  $\text{SiO}_2$  上，另外由於 Hf 的原子序為 72 而 Ir 的原子序為 77，由於兩者原子序過於接近，所以在影像對比上無法與跟  $\text{SiO}_2$  相比有明顯的對比。

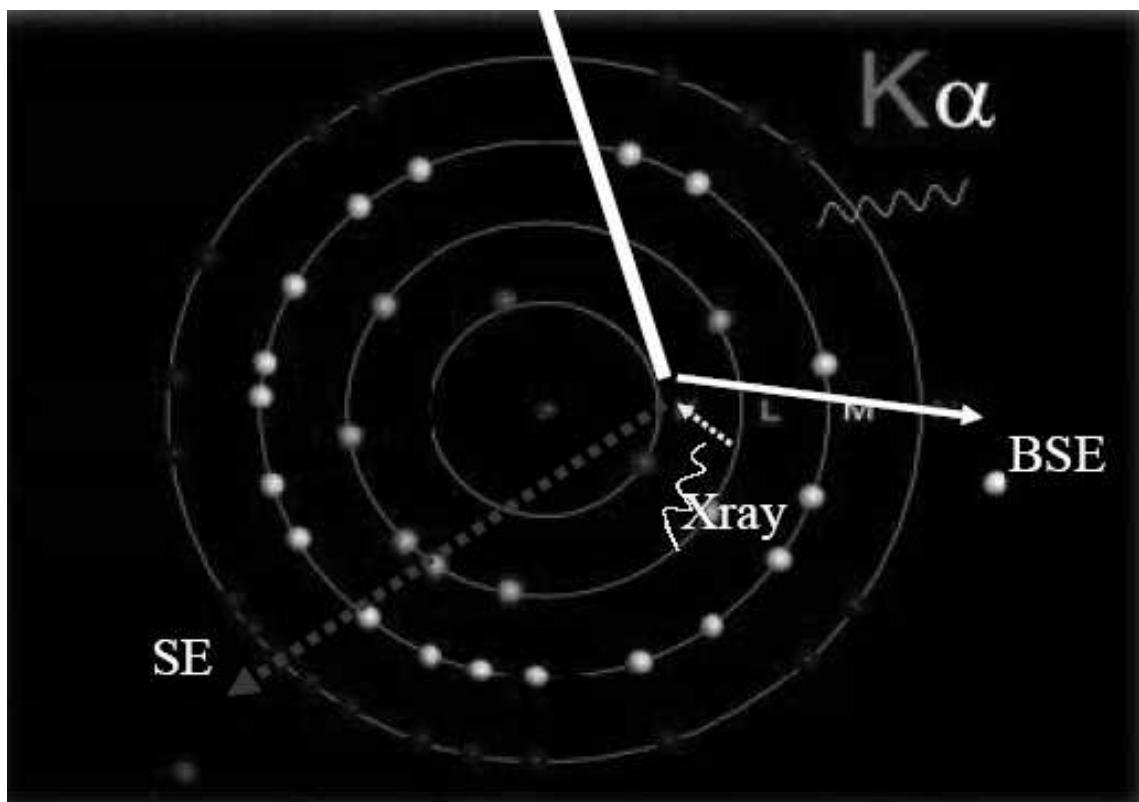

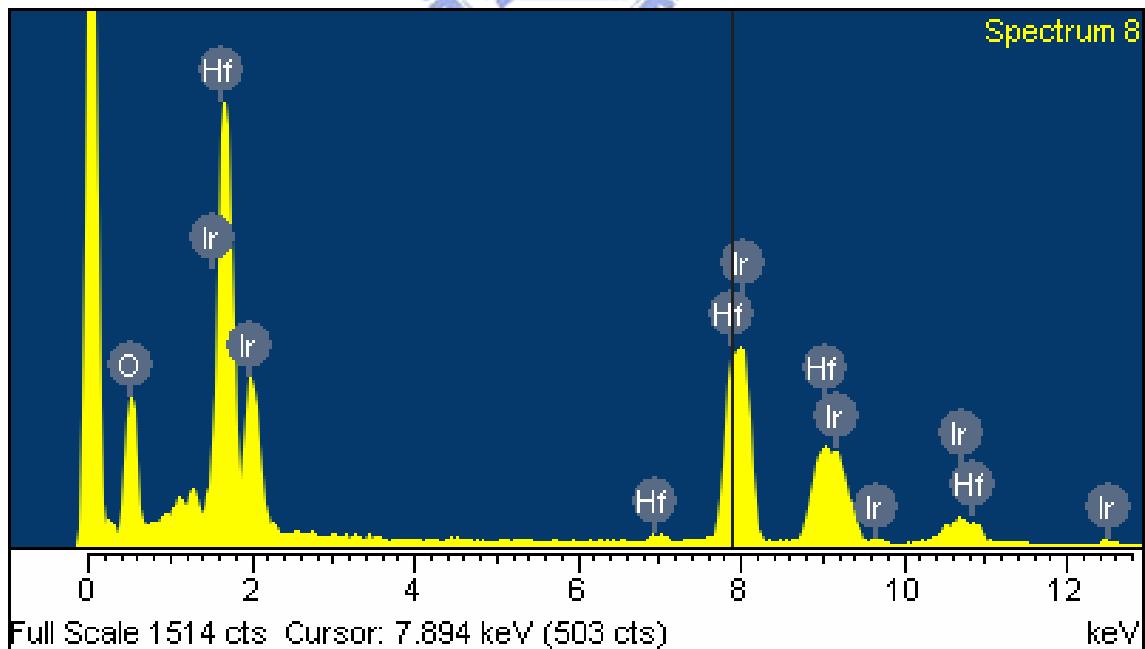

另外本研究也利用 TEM 的附件—能量散佈分析儀(EDS)，透過電子束打擊元素時會激發電子能量的躍遷，而激發成為高能量的電子會脫離電子軌域及原子核的吸引產生二次電子(SE)或是背向散射電子(BSE)、和特徵 X-ray(character x-ray)等訊號出來如圖 4-15[26]，。被電子束激發而放射出來之 X-ray 穿過薄的鉻窗 (Beryllium Window, Be) 或

超薄的高分子膜窗甚至是無窗型的偵測器中，激發矽晶接收器產生電子電洞對，再轉換成電流，經放大器及脈衝處理器( Pulse Processor )的處理後，送至能量數位轉化器 ( Energy-to-Digital Converter ) 處理由多頻道分析儀( Multi-channel Analyzer, MCA ) 將X光能量信號存入其對應之頻道位置。特徵X-ray就如同人的身分証一樣，我們透過分析特徵X-ray可以對應到各元素完成材料的。因此在圖中奈米晶體附近做EDS分析可以得到Ir以及覆蓋住Ir的HfO<sub>2</sub>的元素如圖4-16，從這裡可以清楚驗證本研究的結構的正確性與奈米晶體的大小。

圖 4-14、電容的 TEM 剖面圖。

圖 4-15、元素受到電子束激發後會釋放出三種訊號[26]。

圖 4-16、EDS 分析的資料。

## 4-2 元件的應用

接著在第三階段把電容的參數在往下推展到試著去製作記憶體的元件，流程如第二章所提到的過程，做簡單的測試證明元件的特性。。

### 4-2-1 電子顯微鏡驗證元件上的金屬奈米點

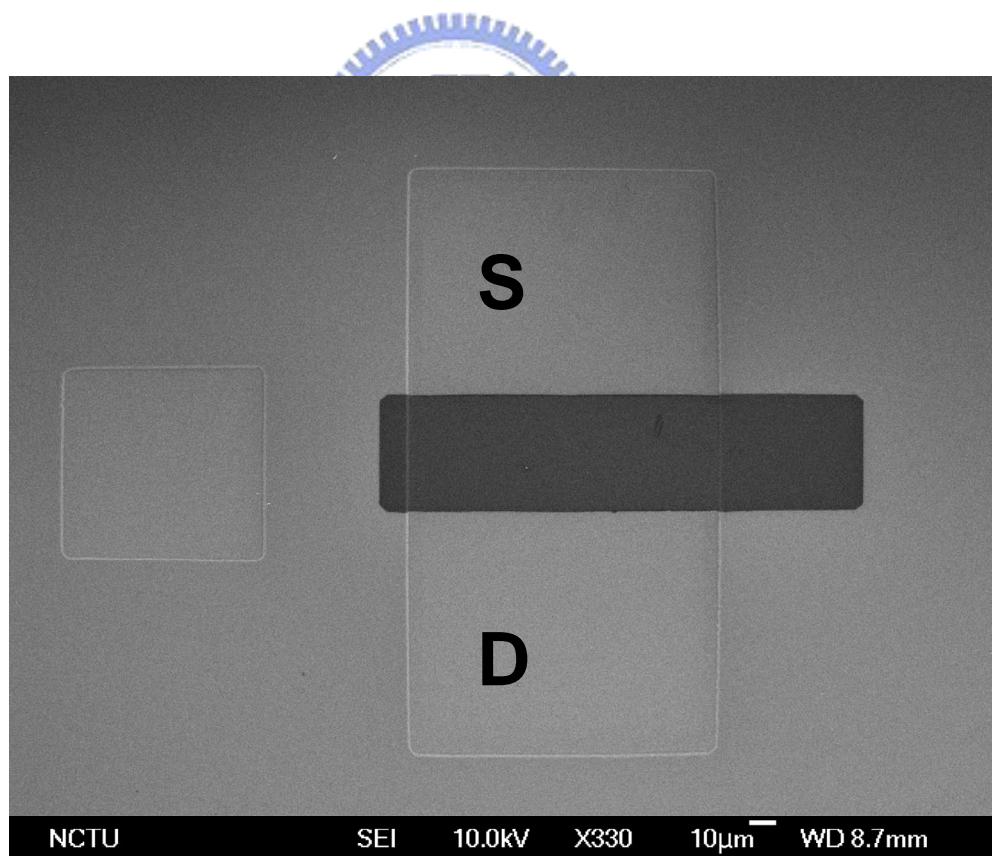

由於元件的製程較為繁瑣，因此製程中製作元件時，確認到Ir-NCs的形成才能繼續往之後的製程來完成整個元件，所以在RTA製程之後，便分片出來在SEM底下做確認。圖4-17是整個device的圖左右各為source和drain端，中間黑色的區塊為我們利用黃光定義出疊Ir film的區域，疊完後去除光阻後RTA，也就是定義給Ir-NCs的區域，經過SEM放大圖4-17的黑色區塊後的影像確認(圖4-18)證實有Ir-NCs的生成。

圖 4-17、元件的 RTA 製程之後的 SEM 圖。

圖 4-18、元件的 Ir-NCs 確認圖。

#### 4-2-2 元件量測結果

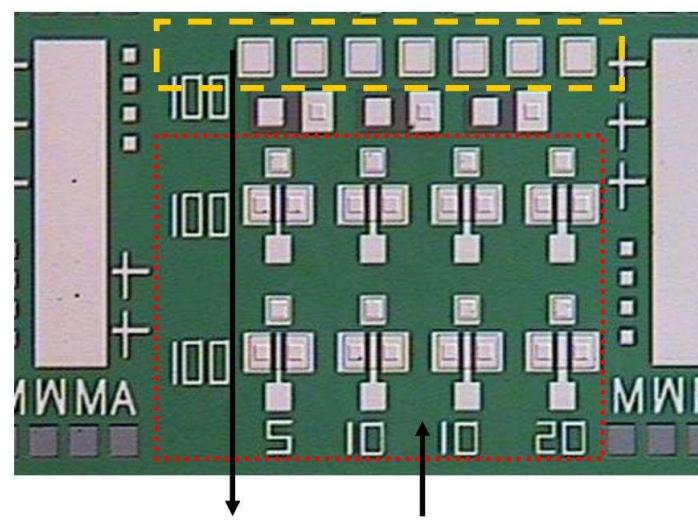

本實驗製作出來的元件俯視圖如圖 4-19，可以清楚的從旁邊的數字看出 channel 寬度為  $100\mu\text{m}$  長度則為  $5\mu\text{m}$ 、 $10\mu\text{m}$ 、 $20\mu\text{m}$ ，在 device 的上面則為元件電容測試區，可測試在元件製程所製造出來的夾層電容是否可以正確工作。

圖 4-19、元件成品的俯視。

本實驗所製作的元件對照第二章流程，各種膜的厚度分別如下：第二步驟的 Wet oxide 為 500 nm 目的用來擋住 Ion implantation 的 implant，定義出 S/D 的區域。第七步驟的 tunnel oxide 為 7 nm；第八步驟的 Ir 金屬膜為 4.5 nm；第十步驟的 High- $\kappa$  HfO<sub>2</sub> 膜為 35 nm。最後一步元件正面和背面用的鋁電極分別為鍍 300 nm。

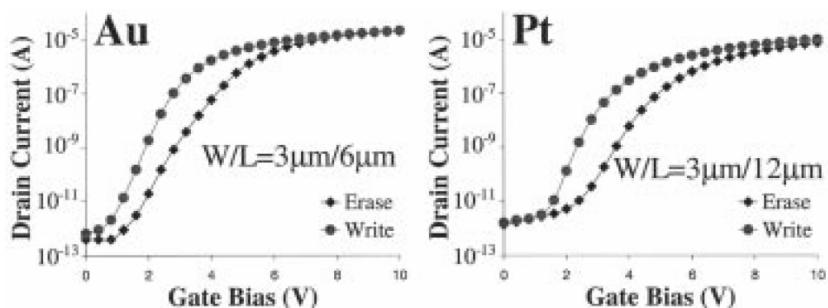

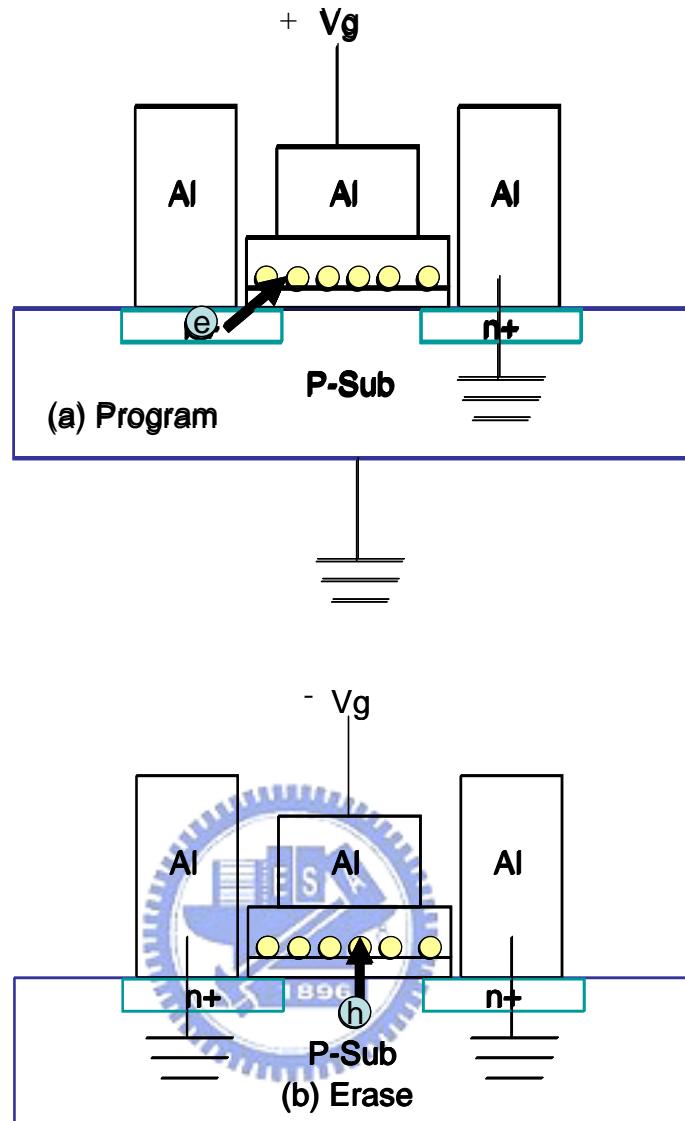

本論文利用 10  $\mu$ m 的通道長度和 100  $\mu$ m 通道寬度的元件來做量測得到  $I_d$  及  $V_d$  圖可以證明此種製程下所製作的元件擁有場效電晶體的特性(圖 4-20)。另外一個主要測試則是利用此元件做記憶體元件的 program & erase 的效果。根據 2-1 所提到元件的操作機制和 4-1-6 的 FN-tunneling 的驗證加上本實驗的光罩設計 gate 的區域和 Source/Drain 區域互相覆蓋大約 10  $\mu$ m 的長度，換句話說也就是 Source 和 Drain 兩端各深入 Gate 的區域 10  $\mu$ m，因此依據這些線索可為元件繪製 program & erase 的示意圖(圖 4-21)，本實驗利用 F-N tunneling 的現象以及 Source 和 Drain 端深入的結構可以輕易地利用電壓造成能帶彎曲的效果從 Source 端汲取電子到 Ir 奈米晶體的位能井裡，形成電子的儲存 (program)，也就是類似圖 4-22 的紅線的狀態。而電荷的移除靠 P-type 提供電洞到 Ir 奈米晶體的位能井裡面和電子中和以降低  $V_{th}$ ，此時即類似圖 4-22 的綠線狀態(erase)。

圖 4-20、Ir-NCs 元件的  $I_d$ — $V_d$  圖。

(通道長度 10  $\mu$ m 寬度 100  $\mu$ m)

圖 4-21、元件 Program& Erase 示意圖。

根據上圖 4-21 的原理，來作 program & erase 的檢驗，其操作狀態為  $V_{ds}$  為 0.1V，一開始量測  $V_G$  對  $I_d$  的圖形如圖 4-22 的黑線(fresh)接者我們加壓(plus 8V 1秒)一次再對其元件量測  $V_G$  對  $I_d$  如圖 4-22 的紅線(program)，而我們加負偏壓(plus -8V 1秒)一次，再對元件量測  $V_G$  對  $I_d$  可得到圖 4-22 的綠線(erase)。而紅線(program)和綠線(erase)之間的電壓差  $\Delta V_{th}$  大約為 0.5V，證明有電荷的儲存造成  $V_{th}$  的位移，元件能產生記憶的效果。

圖4-22、Ir-NCs記憶體元件的寫入和清除的操作  $I_d-V_g$  圖。

(通道長度  $10 \mu m$  寬度  $100 \mu m$ )

# 第五章

## 結論與未來方向

結論：

Ir 奈米晶體的形成：

1. 溫度的變化對於利用 RTA 製程來製備奈米晶體是一個最關鍵也最重要的參數，不只溫度的高低影響著金屬膜的開始發生變化的條件，甚至會影響其鍵結產生化合物的狀態，因此本類型的研究在製備此類奈米晶體的時候必須要掌控其金屬的變化。

2. 退火時間的增加可以持續供給熱能讓奈米晶體克服其界面能，得到更密集，尺寸更小的奈米晶體，然而退火時間如果過長的話反而會使得奈米晶體彼此融合成為更大的奈米晶體。因此實驗的參數除了溫度之外，更要控制其退火時間在一個極限值，以求得到奈米晶體最好的效果。

3. 起始金屬膜對於獲得高密度、尺寸越小的奈米晶體有所幫助，只是當金屬膜越薄的時候，也必須要注意到此時金屬膜的均勻度或是否成膜的問題。

4. 本研究試著利用接觸角去計算出表面能套用 Vollmer-Weber Growth 來解釋奈米晶體的內縮現象。

5. 利用 XPS 的實驗來確認本研究所探討的 Ir 奈米晶體的熱穩定性，並且證明他是可耐高溫熱處理的金屬。

6. 本論文的 Ir 奈米晶體的形成條件為 4.5 nm 的 Ir 經過 950°C RTA 60s 可以得到 Ir-NCs 尺寸 8nm 密度  $6 \times 10^{11}/\text{cm}^2$

Ir 奈米晶體電容及元件：

1. 本論文利用和 Al 金屬 gate 的比較驗證 Ir 的功函數。

2. 穿隧氧化層厚度越薄，電荷越容易穿越，但是相對電荷保存能力也越差。因此本研究必須調到最穩定的狀態。

3. 經過 E-gun(PVD) 製程的膜，內部會有許多缺陷，因此必須透過熱處理去修補。而

修補的能力可以透過 C-V 圖的曲線和 I-V 的測漏電來比較。

4. 從實驗中驗證了 Ir 奈米晶體是透過 F-N tunneling 機制來移動電荷。

5. 利用電子顯微鏡證明電容的結構與 Ir 奈米晶體的大小。

6. 本研究從電容量測結果中可以得到關於 memory window 及 retention time 等資訊，在 $+/‐10V$  的掃描之下  $\Delta V_{FB} \approx 2V$ ，retention time 則可以預測到  $10^6 s$ 。

7. 本研究成功的試做出含有 Ir 奈米晶體的記憶體元件，並且擁有場效電晶體的特性。

未來方向：

以本論文的研究為基礎提供幾個未來可能的研究方向，供各位有興趣的先進參考：

1. 可設計 self-alignment 的光罩與製程，讓耐高溫的金屬奈米晶體可以完全發揮其特性。並且減少元件的製程手續。

2. 透過能帶設計吾人可以建立起不同的材料來改進一些傳統元件在微縮時會遇到的困難，而能帶設計可以從三種方向去做研究：

- (a) 調控介電層能帶—透過介電材料的特性吾人可以掌控其電容值，即使總電壓不高也能利用  $C_1V_1=C_2V_2$  的原理讓發生穿隧現象的地方所跨的壓降為最大。

- (b) 調控金屬功函數—不只在於純金屬的調控，對於化合物(silicide)的功函數及其形成所造成的能帶變化也有極大的研究空間。另一方面 silicide 的金屬奈米晶體由於擴散速率較慢，可以減少對氧化薄膜的擴散現象也降低破壞穿隧氧化層的機會。

- (c) 複合材料，利用不同的材料造成能帶緩衝的效果，形成不對稱結構的電容，可以使電場分布更均勻，目前在學術研究上已經能看到相關的文獻，例如穿隧氧化層的結構採用  $SiO_2/SiN_x$  的不對稱結構[27]。

3. 利用不同的溫度所製備不同的金屬奈米晶體做雙層的結構以增加電荷的保存能力。

## 參考文獻

- [1] S. M. Sze, Physics of Semiconductor Device, 2<sup>nd</sup>, 1985.

- [2] Neamen, Semiconductor physics and devices basic principles, 3<sup>rd</sup>, 1992.

- [3] ITRS, “Process Integration, DEVICES, AND STRUCTURES 2007 edition”, PP.36-50, 2007

- [4] H.A.R. Wegener , A.J Lincoln, H.C Pao, M.R O'Connell, R.E Oleksiak, H Lawrence , “The variable threshold transistor, a new electrically-alterable, non-destructive read-only storage device,” in IEDM Tech Dig, PP.70,1967.

- [5] D. Kahng and S. M. Sze, “A floating gate and its application to memory devices,” Bell Syst. Tech, J., vol.46, PP.1288 ,1967.

- [6] C.Y Lu, T.C Lu, R Liu, “Non-volatile memory technology - today and tomorrow” in Proceedings of 13th IPFA, PP18-23,2006.

- [7] J Jin Lee, D.L. Kwong, Metal Nanocrystal Memory With High- $\kappa$  Tunneling Barrier for Improved Data Retention,” IEEE Trans. Electron Devices, vol. 52, PP. 507-511, Apr. 2005.

- [8] S.M. Jung, J. Jang, W. Cho, H. Cho, J. Jeong, Y. Chang, J. Kim, Y. Rah, Y. Son, J. Park, M. Song, K. Kim, J. Lim and K. Kim, “Three Dimensionally Stacked NAND Flash Memory Technology Using Stacking Single Crystal Si Layers on ILD and TANOS Structure for Beyond 30nm Node,” in IEDM Tech Dig, PP.1-4,2006.

- [9] F. M. Yang, T. C. Chang, P. T. Liu, U. S. Chen , P. H. Yeh, Y. C. Yu , J. Y. Lin, S. M. Sze , J. C. Lou, “Nickel nanocrystals with HfO<sub>2</sub> blocking oxide for nonvolatile memory application,” App. Phys. Lett., 90, 222104,2007.

- [10] G. Lin, H. Kuo, H. Lin, C. Kao, “Rapid self-assembly of Ni nanodots on Si substrate covered by a less-adhesive and heat-accumulated SiO<sub>2</sub> layers,” App. Phys. Lett., 89, 073108,2006.

- [11] Ph. Buffat, and J. P. Borel, “Size effect on the melting temperature of gold particles”, Phys.Rev.A,Vol.13, PP.2287-2298, Jun 1976.

- [12] Z. Liu, C. hungho Lee, V. Narayanan, G. Pei, and E. C. Kan, “Metal Nanocrystal Memories—Part I: Device Design and Fabrication”, IEEE Trans. Electron Devices, vol. 49, PP.1606-1613 ,Sept 2002.

- [13] Z. Liu, C. hungho Lee, V. Narayanan, G. Pei, and E. C. Kan, “Metal Nanocrystal Memories—Part II: Electrical Characteristics”, IEEE Trans. Electron Devices, vol. 49, PP.1614-1622, Sept 2002.

- [14] F. M. Yang, T. C. Chang, P. T. Liu, U. S. Chen and P. H. Yeh, Y. C. Yu and J. Y. Lin,S. M. Sze and J. C. Lou, “Memory characteristics of Co nanocrystal memory device with HfO<sub>2</sub> as blocking oxide” App. Phys. Lett., 90,13102,2007.

- [15] S..K. Samanta, W.J. Yoo, G. Samudra, E.S. Tok, L.K. Bera, N. Balasubramanian,“Tungsten nanocrystals embedded in high-k materialsfor memory application” App. Phys. Lett., 87,113110,2005.

- [16] S. Choi, Y. Cha, B. Seo,S. Park, J. Park, S. Shin, K. S. Seo,J. Park, Y. Jung, Y. Park, Y. Park, I. Yoo, S. Choi,“Atomic-layer deposited IrO<sub>2</sub> nanodots for charge-trap flash-memory devices,” J. Phys. D: App. Phys.,40, PP.1426-1429,2007.

- [17] <http://www.saifun.com/> “NVM Technology overview”

- [18] S. M. Sze Semiconductor Devices: Physics and Technology, 2<sup>nd</sup>, 2002.

- [19] 黃調元 ,“記憶體元件與製程”上課講義,頁67,2007 .

- [20] 柯賢文 ,“表面張力的應用,”科學發展月刊 ,411期 , 頁48-51, 2007.

- [21] F. Ko, C. Wu, M. Chen, J. Chen, T. Chu,“Soft-mold-induced self-construction of polymer patterns under microwave irradiation,” App. Phys. Lett., 90,191901,2007

- [22][http://hamers.chem.wisc.edu/chem630\\_surfaces](http://hamers.chem.wisc.edu/chem630_surfaces).

- [23] J. F. Moulder, W. F. Stickle, P.E. Sobol,“Handbook of X-ray Photoelectron Spectroscopy,” PP. 179,1993.

- [24] H.B. Michaelson, "The work function of the elements and its periodicity," *J. Appl. Phys.*, vol. 48, PP.4729-4733, Nov,1977.

- [25] K. Ashihara, H. Nakane, H. Adachi, "Experimental Confirmation of Flower Nordheim Plot at Several Micro-Meters Emitter to Anode Distance," Muroran Institute of Technology,27-1 Mizumoto- cho, Muroran, PP. 104-107.

- [26] <http://acade.must.edu.tw/> "SEM/EDS 構造與原理探討"

- [27] W.R.Chen, T.C. Chang, J.L. Yeh, S. M. Sze, C.Y. Chang, "Reliability characteristics of NiSi nanocrystals embedded in oxide and nitride layers for nonvolatile memory application," *App. Phys. Lett.*,92,152114,2008.