## 國立交通大學

資訊學院 資訊學程 碩士論文

全數位高解析度寬頻頻率合成器之設計

The Study of High-resolution and Wide-bandwidth

Frequency synthesizer

研究生:吳青峰

指導教授:許騰尹 博士

中華民國九十七年七月

#### 全數位高解析度寬頻頻率合成器之設計

## The Study of High-resolution and Wide-bandwidth

#### Frequency synthesizer

研究生:吳青峰 Student: Cheng-Feng Wu

指導教授:許騰尹 博士 Advisor: Dr. Terng-Yin Hsu

#### 國立交通大學

A Thesis

Submitted to College of Computer Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of Master of Science

in

**Computer Science**

July 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年七月

## 全數位高解析度寬頻頻率合成器之設計

學生:吳青峰 指導教授:許騰尹 博士

國立交通大學資訊學院資訊學程碩士班

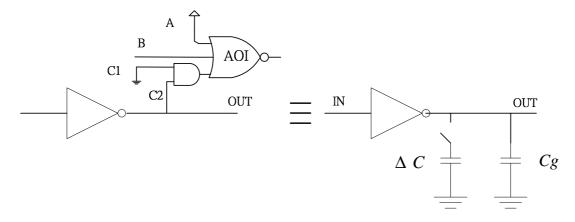

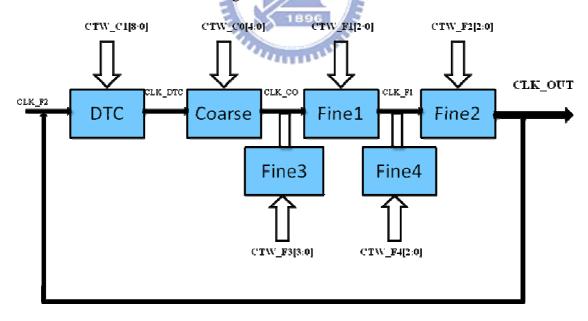

全數位頻率合成器為現今電路設計中之一個重要部份,特別是應用在個人數位行動通訊之系統晶片。而數位振盪器的輸出直接影響到頻率合成器的效能好壞,本論文特別專注於數位振盪器之效能提升,在此使用了標準元件中的 AOI/OAI 之原生電容做為數位可變電容器,可將最小控制位元之頻率解析度提高至 10fs,利用四級的微調單元及使用數位轉時間轉換器來加大頻率操作範圍並節省晶片面積,在反相延遲信號線加入反及閘做為致能開關,來降低不必要之功率消耗,並搭配低複雜度之頻率追蹤演算法,在一般條件下可在 30 週期數內鎖定頻率,達成大頻率操作範圍及高解析度之目的,並且為低功率消耗低晶片面積之設計,整個設計皆使用標準元件,因此可在更短的設計時間

內轉換不同製程,在數位振盪器的關鍵元件配置部份,採用標準元件之手動的擺放和繞線,以確保設計符合要求,也節省了若使用全客製化設計之心力,經由 HSpice 的模擬,可得本設計有 187KHz 到 345MHz 之操作範圍且最小控制位元可達 10fs 之解析度。

## The Study of High-resolution and Wide-bandwidth frequency synthesizer

Student: Cheng-Feng Wu Advisor: Dr. Terng-Yin Hsu

Degree Program of Computer Science

National Chiao Tung University

The most important part of modern circuit design is the all-digital frequency synthesizer. That especially for the personal mobile communication application in SoC design. The output of digitally-controlled oscillator (DCO) will directly impact the performance of the frequency synthesizer. This thesis is focus on the performance enhancement of the DCO. The proposed DCO used AOI/OAI standard cells to form as digital controlled varactor. It could increase the LSB frequency resolution to 10fs. Four fine tune cell and digital to time converter are used to archive wide frequency operation range without big chip area. This work added enable cell such as NAND into the inverter delay line. It can prevent unnecessary power dissipation. To combine a low complexity frequency tracking algorithm that frequency locking time is within 30 clock cycles in typical case. Thus, this work is a wide operation range, high frequency resolution, low power and small chip size design. In this work all the cells are standard cell. It makes process switch more quickly. The place and route of the DCO key components are done by manual. This ensures that the design is under specification and is also saving the effort if done by fully-customer. Through HSpice simulation, this work can operate at 187KHz~345MHz, the LSB controlled frequency resolution is 10fs.

#### Acknowledgement

This thesis describes research work I performed in the Integration System and Intellectual Property (ISIP) Lab during my graduate studies at National Chiao Tung University (NCTU). This work would not have been possible without the support of many people. I would like to express my most sincere gratitude to all those who have made this possible.

First and foremost I would like to thank my advisor Dr. Terng-Yin Hsu for the advice, guidance, and funding he has provided me with. I feel honored by being able to work with him.

I am very grateful to every members of ISIP Lab for their supports and suggestions. I would like to thank them for being with me through the happy and hard times.

Finally, and most importantly, I want to thank my parents for their unconditional love and support they provide me with. It means a lot to me.

Cheng-Feng Wu

June 2008

## **Table of Contents**

| 摘要           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| <u>ABST</u>  | RACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | III  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| <u>ACKN</u>  | NOWLEDGEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IV   |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| <u>TABLI</u> | E OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| LIST C       | OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VII  |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| LIST C       | OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VIII |

|              | The state of the s |      |

| <u>CHAP</u>  | PTER 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 1.1.         | THESIS BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1    |

| 1.2.         | THESIS BACKGROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| <u>CHAP</u>  | PTER 2 OVERVIEW OF FREQUENCY SYNTHESIZER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 2.1.         | OVERVIEW OF FREQUENCY SYNTHESIZER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3    |

| 2.1.1.       | . DIRECT ANALOG SYNTHESIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3    |

| 2.1.2.       | . DIRECT DIGITAL SYNTHESIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4    |

|              | . Indirect Synthesis Using Phase Locking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| 2.2.         | OVERVIEW OF PHASE-LOCKED LOOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| <u>CHAP</u>  | PTER 3 THE PROPOSED ALL-DIGITAL PHASE-LOCKED LOOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7    |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3.1.         | ALL-DIGITAL PHASE-LOCKED LOOP ARCHITECTURE OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 3.2.         | BASIC CONCEPT OF DCO IMPLEMENTATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| 3.2.1.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3.2.2.       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| 3.2.3.       | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 2 2          | STANDARD CELL-BASED DIGITAL-CONTROL-OSCILLATOR (DCO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12   |

| 3.3.1        | 1. DIGITAL TO TIME CONVERTER DTC   | 13         |

|--------------|------------------------------------|------------|

|              | 2. COARSE-TUNE CELL                |            |

| 3.3.3        | 3. FINE-TUNE CELL                  | 15         |

| <u>CHAF</u>  | APTER 4 SIMULATION AND LAYOUT      | 17         |

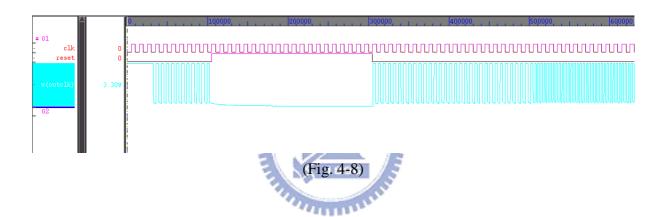

| 4.1.         | SPICE SIMULATION                   | 17         |

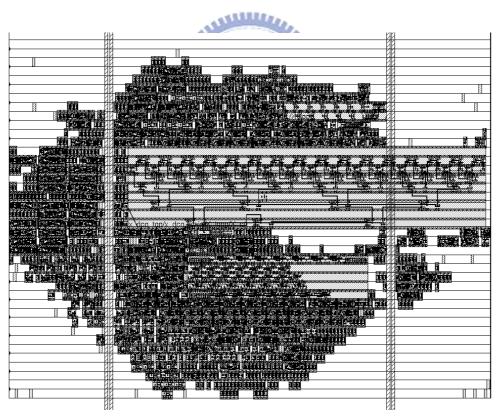

| 4.2.         | LAYOUT                             | 19         |

| <u>CHAF</u>  | APTER 5 CONCLUSION AND FUTURE WORK | 22         |

| 5.1          | CONCLUSION                         | 22         |

| 5.2          | FUTURE WORK                        | 22         |

| <u>BIBLI</u> | LIOGRAPHY                          | <u>2</u> 3 |

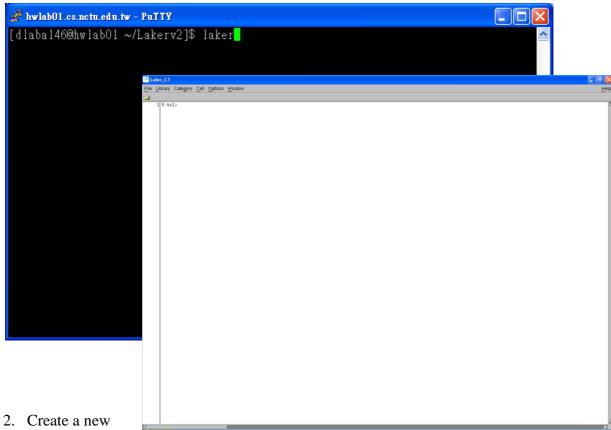

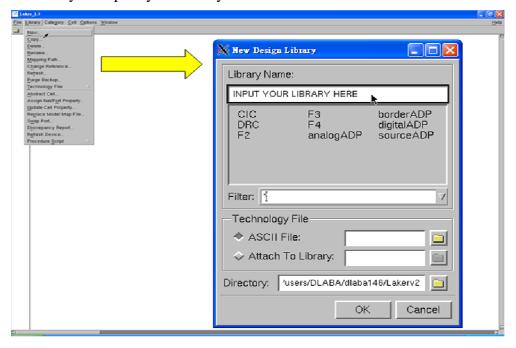

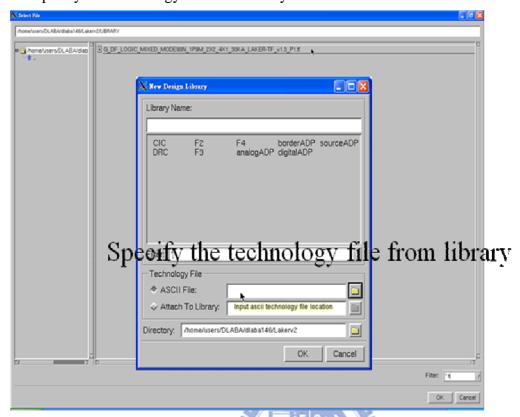

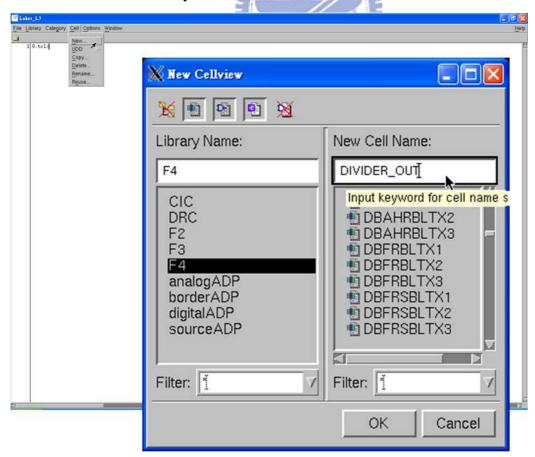

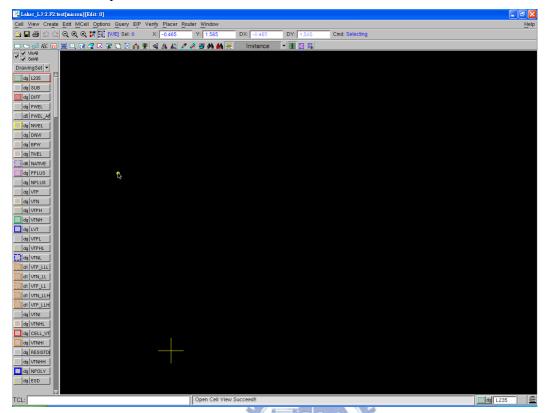

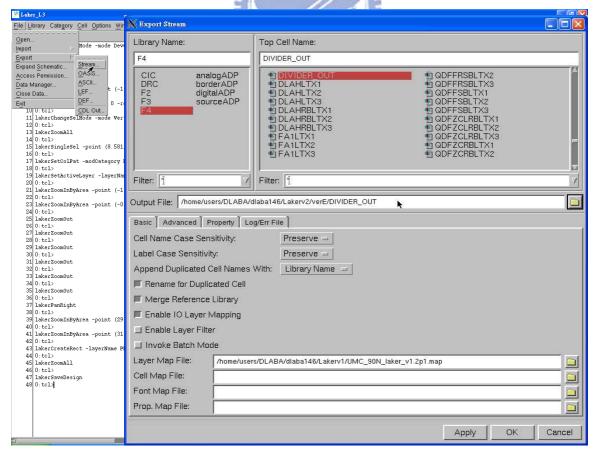

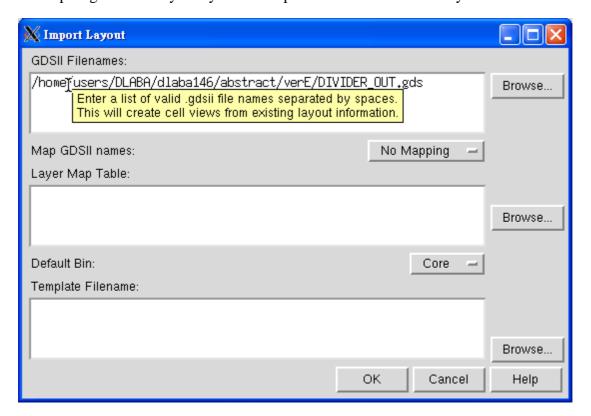

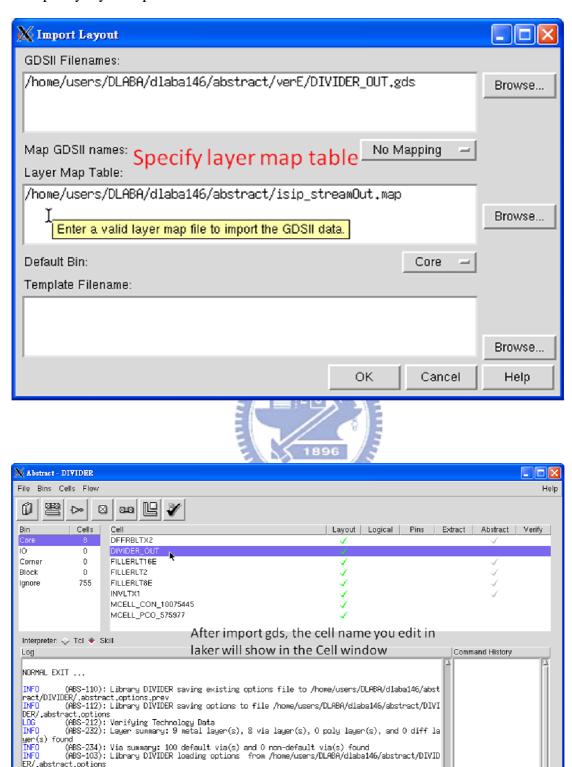

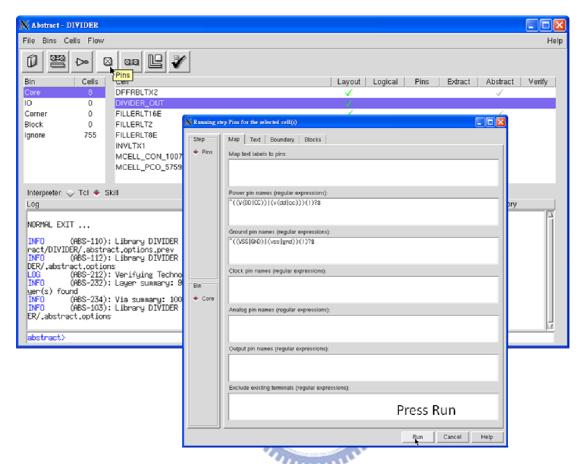

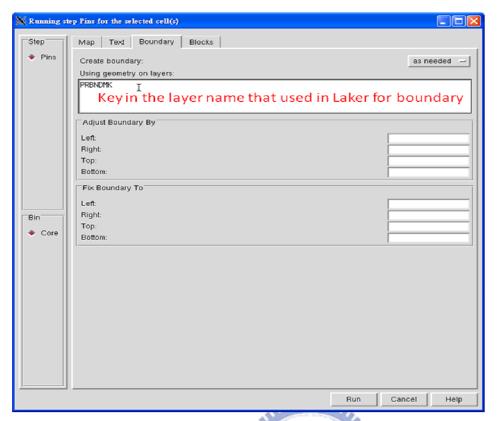

| <u>APPE</u>  | PENDIX A - LAKER TOUR              | 24         |

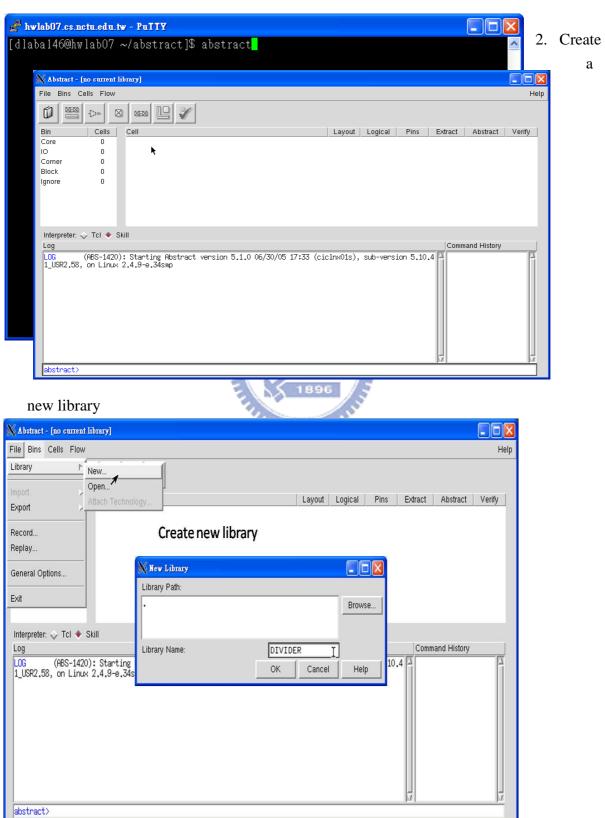

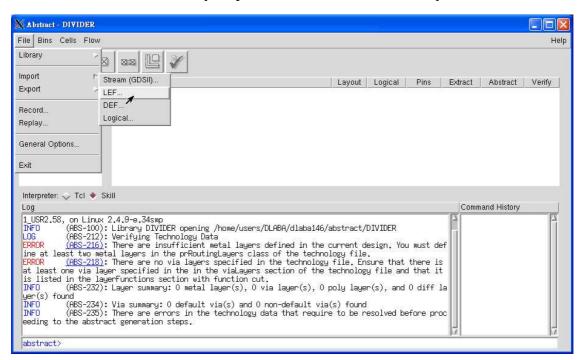

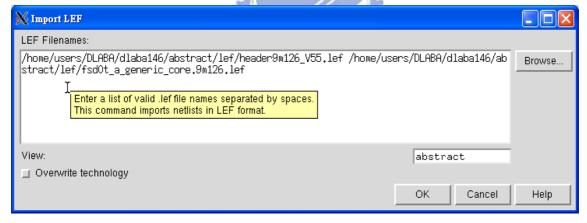

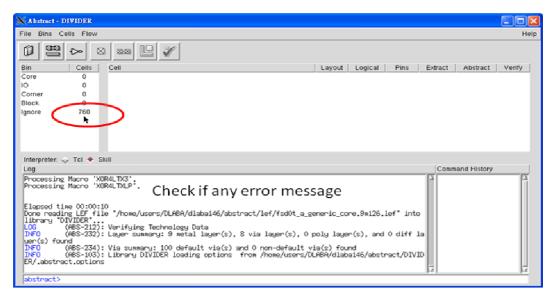

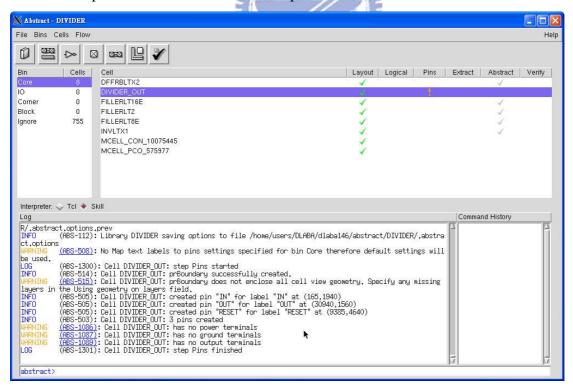

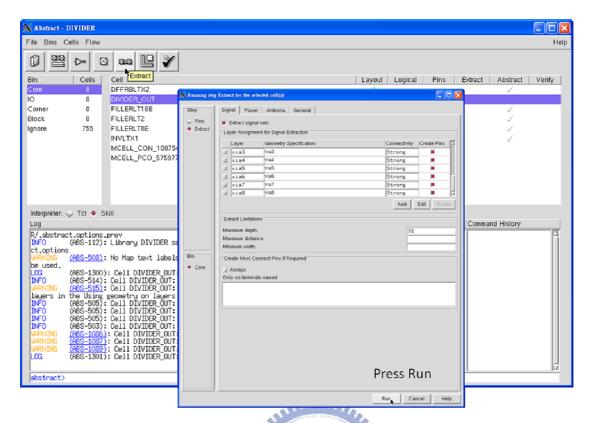

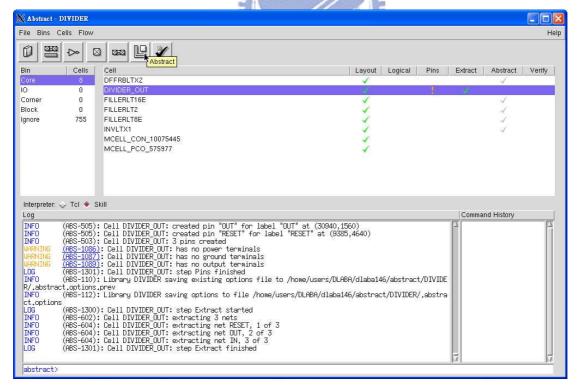

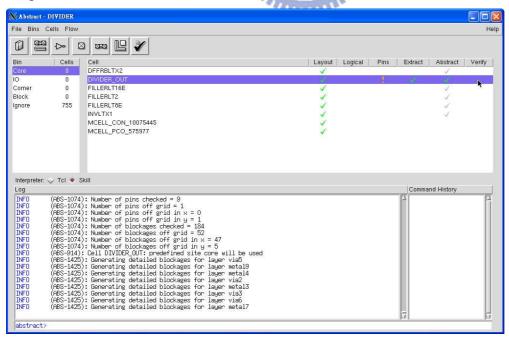

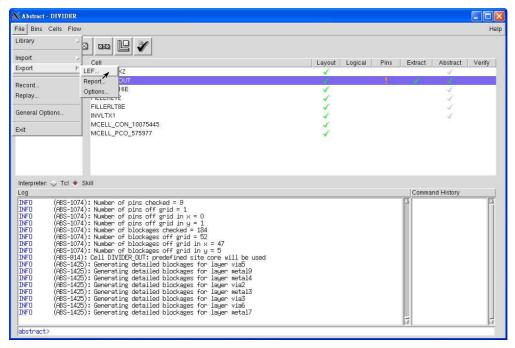

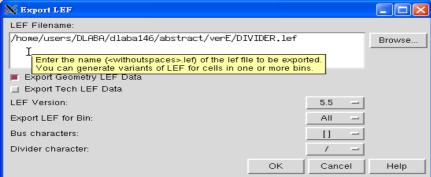

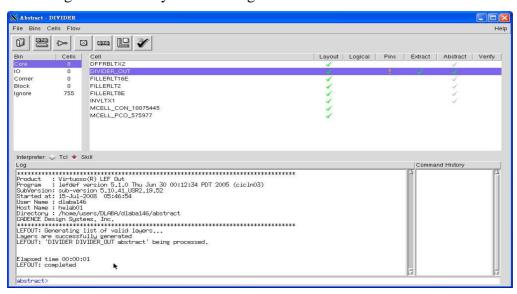

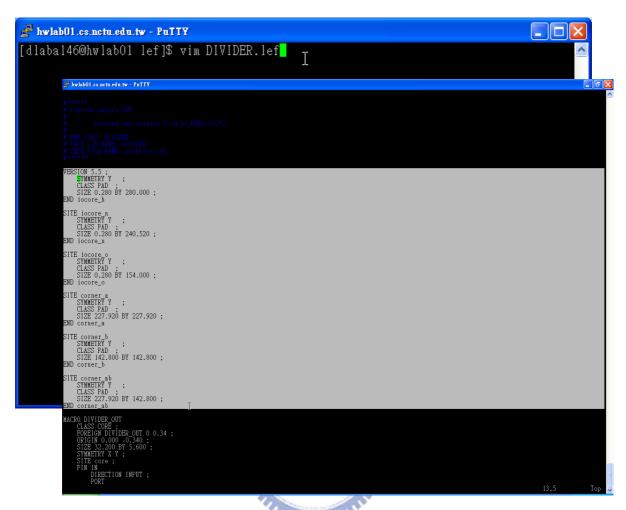

| <u>APPE</u>  | PENDIX B - ABSTRACT TOUR.          | 27         |

|              |                                    |            |

## **List of Tables**

| Table 3.1 | 13 |

|-----------|----|

| Table 4-1 | 21 |

## **List of Figures**

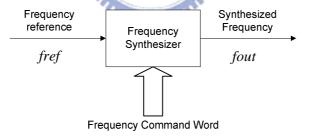

| (Fig. 2-1)   |             |              | 3        |

|--------------|-------------|--------------|----------|

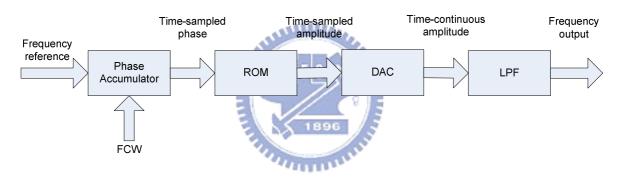

| (Fig. 2-2)   |             |              | 4        |

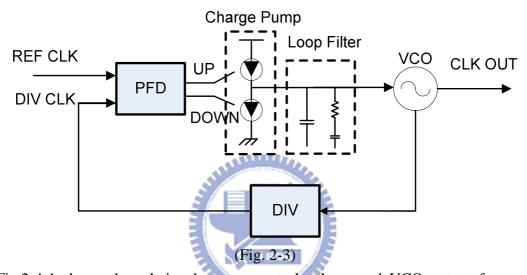

| (Fig. 2-3)   |             |              | 5        |

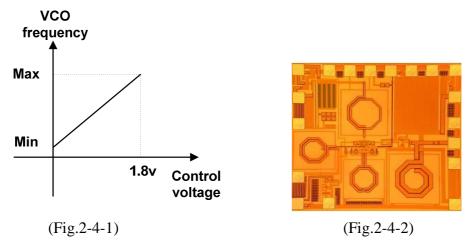

| (Fig.2-4-1)  | (           | (Fig.2-4-2)  | 5        |

| (Fig.2-5)    |             |              | 6        |

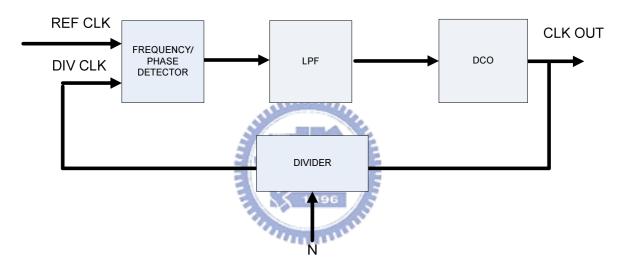

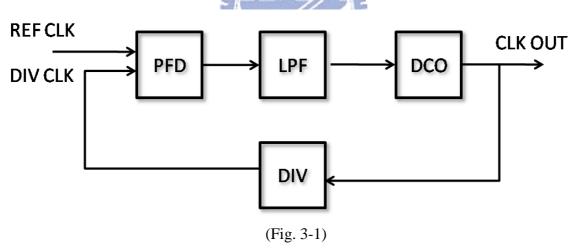

| (Fig. 3-1)   |             |              | 7        |

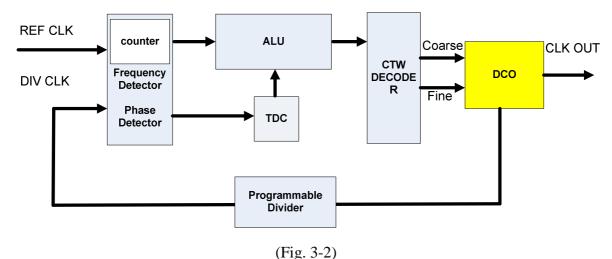

| (Fig. 3-2)   |             |              | 8        |

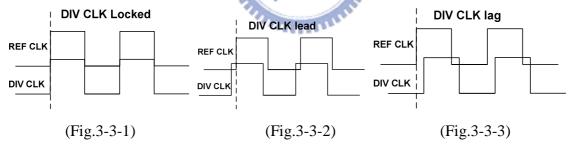

| (Fig.3-3-1)  | (Fig.3-3-2) | (Fig.3-3-3)  | 8        |

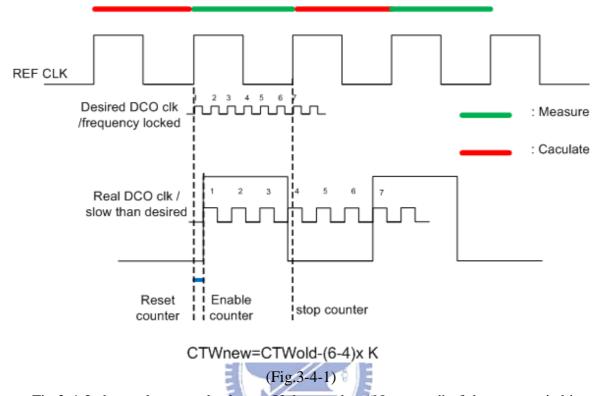

| (Fig.3-4-1)  |             |              | 9        |

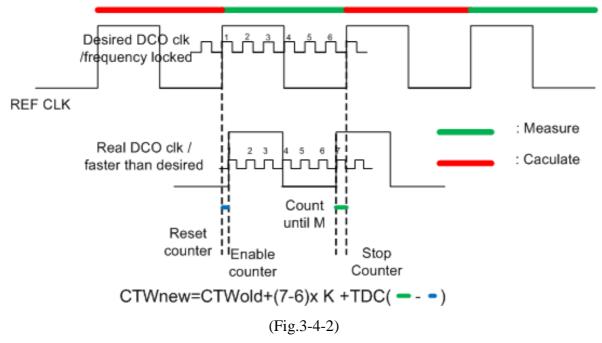

| (Fig.3-4-2)  |             |              | 9        |

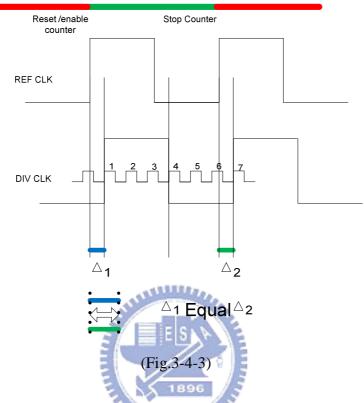

| (Fig.3-4-3)  |             |              | 10       |

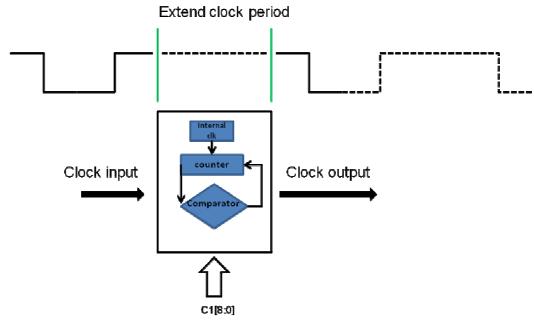

| (Fig.3-5)    |             |              | 11       |

| (Fig. 3-6)   |             |              | 11<br>12 |

| (Fig. 3-7)   |             |              |          |

| (Fig. 3-8)   |             |              | 12       |

|              |             |              | 13       |

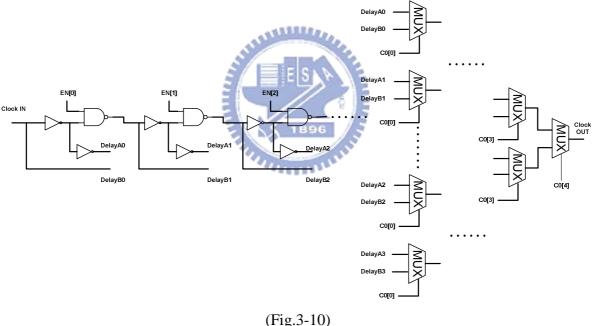

| (Fig.3-10)   | <u> </u>    |              | 14       |

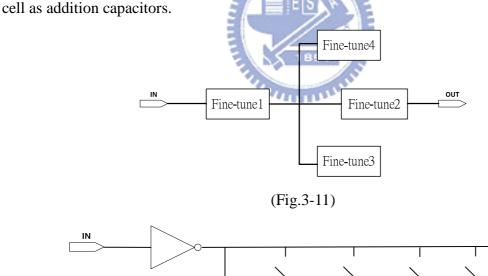

| (Fig.3-11)   |             | V 1896 2     | 15       |

| (Fig.3-12)   |             | V            | 15       |

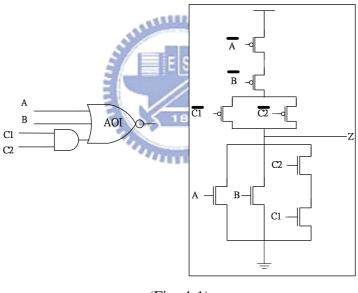

| (Fig. 4-1)   |             |              | 17       |

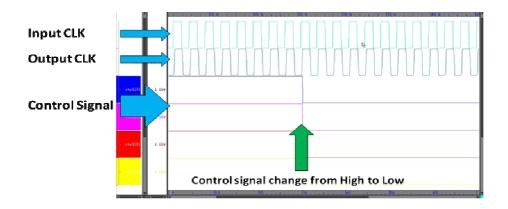

| (Fig. 4-2)   |             |              | 18       |

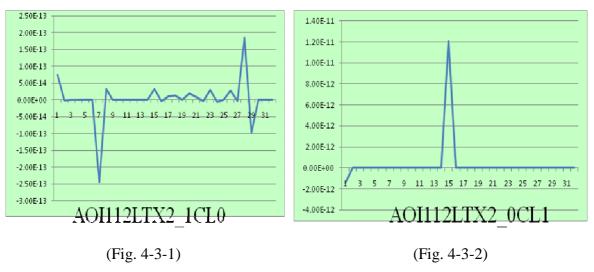

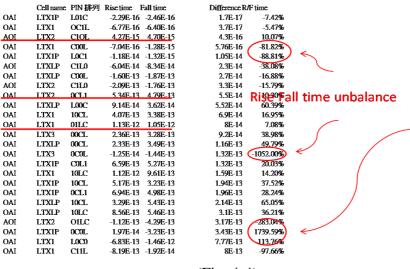

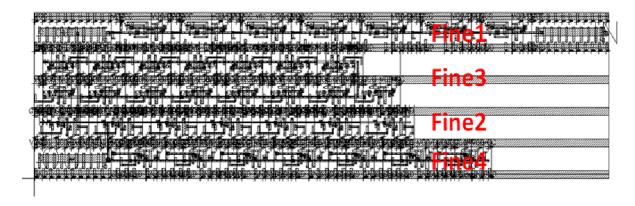

| (Fig. 4-3-1) |             | (Fig. 4-3-2) | 18       |

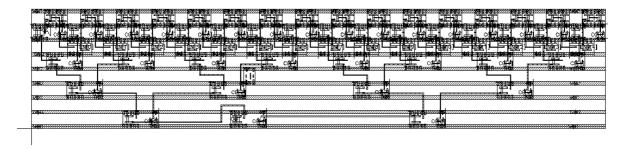

| (Fig. 4-4)   |             |              | 19       |

| (Fig. 4-5)   |             |              | 19       |

| (Fig. 4-6)   |             |              | 20       |

| (Fig. 4-7)   |             |              | 20       |

| (Fig. 4-8)   |             |              | 21       |

## **Chapter 1**

#### Introduction

#### 1.1. Thesis Background

As Very Large Scale Integrated circuits (VLSI) techniques become more and more complexity, the functions also become more and more powerful. In modern System-on-Chip (SoC) design, one single chip could contain many functions such as audio process, video process, and wireless communication. In recently year, personal mobile communication is getting more and more popular. There are many kinds of wireless communication techniques had been development and become standard. All of these communication techniques have same demand such as low power, low cost, high performance and process portable.

Frequency synthesizer is widely using in SoC applications. The SoC design needs a good performance clock generator. Because of the design of frequency synthesizer is a trade-off among phase noise, frequency resolution, power consumption, area-cost, circuit complexity and design time. How to balance those parameters and gain the most benefit in SoC? The analog design with fully-customer layout provided the high performance in SoC. However, the analog design implies the big chip area, high power consumption and variance with PVT. Fully-customer layout takes big effort and is not easy to switch process.

If the module in SoC design is reusable and portable, it may save design time. If used PLL based frequency synthesis, it may have good performance of phase noise. If used all digital phase-locked loop (ADPLL) based frequency synthesis, it could save power consumption, area-cost and circuit complexity. How to combine those advantages in a practical way is very important.

#### 1.2. Thesis Motivation

There are some advantages compare the ADPLL based with the analog based frequency synthesizer design. Traditional analog loop filter costs a lot of chip areas, since it uses resistance and capacitor. Digital loop filters gives benefits such as programmable parameters, robustness against noise and less power consumption. Digital design also can prevent to DC offset and drift phenomena. The digital design has another advantage that is the Electronic

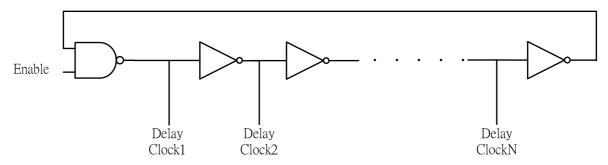

Design Automation (EDA) tools. With the EDA tools help, designers can do Place and Route (P&R) easily. However, it is not the same situation for the most critical components such as DCO. The designers need to set proper constraints to the EDA tools; otherwise the EDA tools will not synthesis the desired circuits. For example, a delay chain composed of cascade inverters might be optimized to one inverter by EDA P&R tools. Besides, the critical path usually cannot allow changing the routing layer. Changing the routing layer means that via has been added so that the capacitance may become unpredictable. Therefore, a semi-fully layout art has been proposed. This design only used CIC 90nm technology standard cell library without any other customer cell. The semi-fully layout art is place standard cell but routing by manual. This art gets the advantages both of analog and digital design.

Clock generator is the most important component of frequency synthesizer. In the analog designs, voltage controlled oscillator (VCO) are usually used to providing low phase noise frequency. This advantage comes with many disadvantages such as power consumption, area cost. Those issues make VCO is not suitable for mobile application. In this work, the proposed DCO is high-resolution and wide-bandwidth; moreover, it is a low power and small area design. Those good properties make the DCO to fit low power and mobile application.

## 1.3. Thesis Organization

The organization of this thesis is as follows:

In chapter 2, it is a brief to the applications of the Frequency synthesizer. And introduce the advantage of the Frequency synthesizer based on ADPLL.

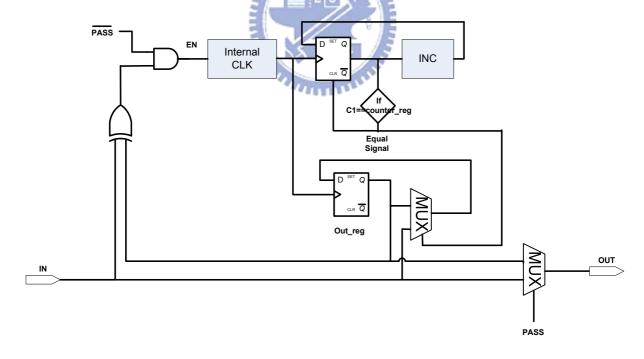

In chapter 3, the proposed ADPLL is introduced. A detailed description of the idea and simulation are given. Including how we used standard cell to complete coarse tune and fine tune cell in DCO.

In chapter 4, we illustrated the hardware implementation and layout. A detailed description of the DCO implementation has illustrated.

In chapter 5, some concluding remarks will be derived from this research. Finally, we describe several design issues that needed to be further explored in the near future.

## Chapter 2

## **Overview of Frequency Synthesizer**

There are many applications need clock synchronization or frequency multiplication. Several methods could meet the functional required but how to balance the cost and performance should never be ignored. In this chapter, gives a discussion about the advantages and disadvantages between those different approaches.