國立交通大學

電機學院 IC 設計產業研發碩士班

碩士論文

一個操作於 2.4GHz 的無參考訊號源之無線

1Mbps QPSK 解調器

A 2.4GHz Crystal-less Single-Chip Wireless

Receiver for 1Mbps QPSK Demodulation

研究生：區威文

指導教授：陳巍仁 教授

中華民國九十八年九月

一個操作於 2.4GHz 的無參考訊號源之無線 1Mbps QPSK 解

調器

A 2.4GHz Crystal-less Single-Chip Wireless Receiver for

1Mbps QPSK Demodulation

研究 生：區威文

Student : Wei-Wen Ou

指 導 教 授：陳巍仁

Advisor : Wei-Zen Chen

國 立 交 通 大 學

電 機 學 院 IC 設 計 產 業 研 發 碩 士 班

碩 士 論 文

A Thesis

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Industrial Technology R & D Master Program on

IC Design

September 2009

Hsin-Chu, Taiwan, Republic of China

中 華 民 國 九 十 八 年 九 月

# 一個操作於 2.4GHz 的無參考訊號源 之無線 1Mbps QPSK 解調器

學生:區威文

指導教授:陳巍仁 教授

國立交通大學電機學院產業研發碩士班

## 摘要

本論文以 QPSK(Quaternary Phase Shift Keying) 數位調變技術實現的鎖相資料解調變電路，其架構基於單一鎖相迴路，藉由追蹤發射端的射頻頻率產生參考訊號，與直接資料解調，同時不需外接石英晶體振盪器，做為參考訊號源，改善傳統架構無線通訊系統傳送端與接收端本地振盪頻率誤差的問題，適用短距離無線通訊系統。整合了相頻偵測器(PFD)、充電泵(Charge Pump)、迴路濾波器(Loop Filter)、壓控振盪器(VCO)、除頻器(Divider)，低雜訊放大器(LNA)，混波器(Mixer)，後級放大器(Post Amplifier)，頻率檢知器(Frequency Discriminator)與解調變電路(Demodulation)於單一晶片中，達到低功率，低成本與高度整合的目的。

本論文的晶片是使用台灣積體電路公司的  $0.18\mu\text{m}$  互補金氧半導體的製程製作，工作於 2.4GHz 頻段支援短距離傳輸通訊系統，功率消耗小於 20mW，接收數位調變訊號 QPSK，靈敏度約為  $-70\text{dBm}$ ，位元錯誤率  $10^{-3}$ ，資料率為 1Mbps，相位雜訊在距離載波頻率 1MHz 時小於  $-110\text{dBc/Hz}$ 。

# **A 2.4 GHz Crystal-less Single-Chip Wireless Receiver for 1Mbps**

## **QPSK Demodulation**

Student: Wei-Wen Ou

Advisor: Wei-Zen Chen

Industrial Technology R & D Master Program of

Electrical and Computer Engineering College

National Chiao Tung University

### **ABSTRACT**

This paper focusing on QPSK(Quaternary Phase Shift Keying) data demodulator utilizing phase locking technique. The architecture is based on phase locked loop which extracts timing information directly from received RF signal and further demodulates the received data pattern. In other words, it works without reference crystal oscillator and the problem of local oscillator frequency in alignment between transmitter and receiver ends could readily be solved with this new architecture. The main application of this work is for short range wireless communication system. This chip includes PFD, Charge Pump, Loop Filter, VCO, Divider, LNA, Mixer, Post Amplifier, Frequency Discriminator, and Demodulator and several other digital blocks. This is a chip of high integration level and low power consumption.

This chip is fabricated in TSMC 0.18 $\mu$ m CMOS technology. It operates at a rate of 2.4GHz and it is well suited for short range data processing. The measured power consumption is below 20mW, the sensitivity for receiving 1Mbps digital modulated QPSK signal is -70dBm with a BER no larger than

$10^{-3}$ . Also the measured phase noise is well below -110dBc/Hz at an frequency offset of 1MHz.

## 致謝

首先要感謝我的指導教授--陳巍仁博士，三年來細心與不倦的指導，使我在研究領域與待人處世上都得到了不少寶貴的經驗，從一開始對電路完全的陌生，到現在能完成這本論文，使我獲益匪淺。

這段漫長的研究生活，必須要感謝本實驗室的台柱金牌-台祐、建文、金牌-松諭、得獎無數的黃董、Lulu 裕學長、巧玲學姐、順天與邱 99，有了您們的幫忙這本論文才能完成得這麼順利。也要感謝實驗室中共同努力的伙伴們，宅帥、威宇、萬謙、阿邦、建名、99 範、北鴨、小州哥、老大、紹岐、國維、ㄎㄎ華、宗恩、歐陽、塔哥、小賴、彥緯、祥哥、Kitty、星爺、書瑾、小毅、文杰、建軒、川逸、新進的新血豔婷、建宏、逸弘、仲廷、與郭老師實驗室的同學與學弟...等，由於您們的幫忙與鼓勵讓我在碩士生涯中真添了不少美好的回憶，祝福您們在未來的路上能夠一帆風順。

此外特別要感謝我的家人，一直默默的在我背後的支持與鼓勵，也要謝謝我的女友亞攻，從大學時代至今一直陪伴我走過無數次的低潮，盡力給我協助。

該感謝的人還很多，對於一路上曾經給我幫助過的各位在此一併獻上感謝之意，千言萬語道不盡我對大家的感謝，一切進在不言中。

文威區

大交城風于

98年9月

# 目錄

|                                                          |     |

|----------------------------------------------------------|-----|

| 摘要 .....                                                 | i   |

| ABSTRACT .....                                           | ii  |

| 致謝 .....                                                 | iv  |

| 圖目錄 .....                                                | vii |

| 表目錄 .....                                                | x   |

| 第一章 簡介 .....                                             | 1   |

| 1.1 相關背景與動機 .....                                        | 1   |

| 1.2 組織架構 .....                                           | 4   |

| 第二章 系統架構 .....                                           | 5   |

| 2.1 頻率合成器簡介 .....                                        | 5   |

| 2.2 無參考訊號源之無線接收器與資料解調器 .....                             | 8   |

| 3.1 系統工作原理 .....                                         | 11  |

| 3.1.1 頻率追蹤步驟 .....                                       | 12  |

| 3.1.2 相位頻率追蹤及資料解調 .....                                  | 13  |

| 3.2 迴路頻寬設計 .....                                         | 16  |

| 3.3 系統模擬 .....                                           | 17  |

| 第四章 電路設計與實現 .....                                        | 19  |

| 4.1 低雜訊放大器設計 (Low Noise Amplify) .....                   | 19  |

| 4.2 吉伯特雙旁帶混波器 (Double-balanced Gilbert-Type mixer) ..... | 24  |

| 4.3 後級放大器之設計 (Post Amplifier) .....                      | 27  |

| 4.6 壓控振盪器 (Voltage-Controller Oscillator) .....          | 40  |

| 4.7 除頻器之設計 (Divider) .....                               | 45  |

| 4.8 頻率檢知器之設計 (Frequency Discriminator) .....             | 49  |

| 第五章 佈局與量測結果 .....                                        | 52  |

| 5.1. 晶片佈局 (Chip Layout) .....                            | 52  |

|                                       |    |

|---------------------------------------|----|

| 5.2. 量測環境 (Measurement Setup) .....   | 54 |

| 5.3. 量測結果 (Measurement Results) ..... | 55 |

| 第六章 結論.....                           | 62 |

# 圖目錄

## 第一章

|                         |   |

|-------------------------|---|

| 圖 1-1 無線近身網路的概念 .....   | 1 |

| 圖 1-2 典型之射頻無線傳輸系統 ..... | 2 |

## 第二章

|                                       |    |

|---------------------------------------|----|

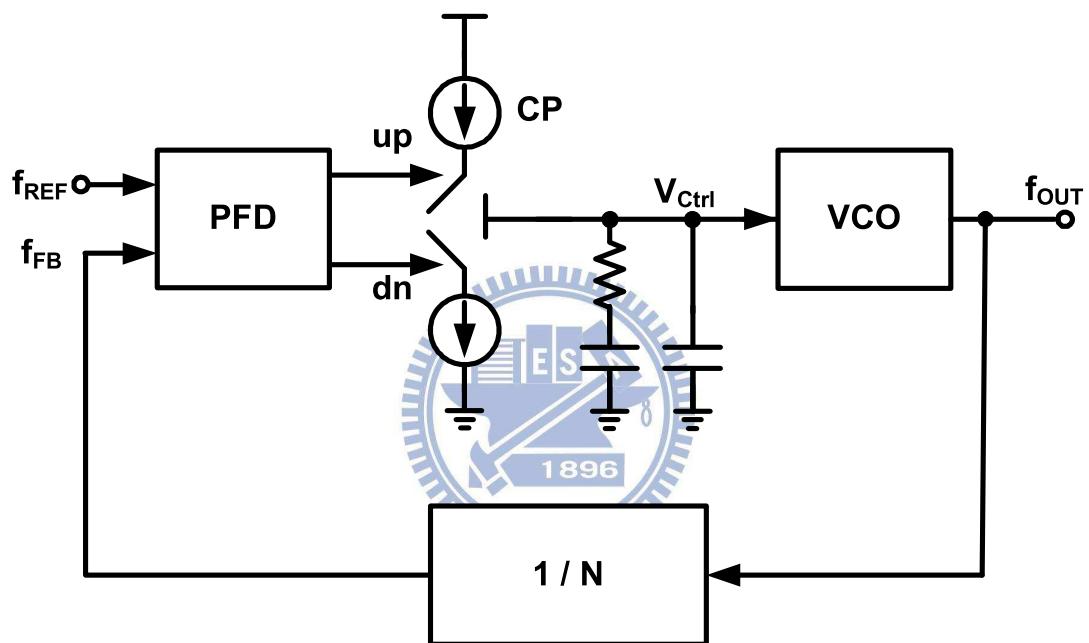

| 圖 2-1 頻率合成器架構圖 .....                  | 5  |

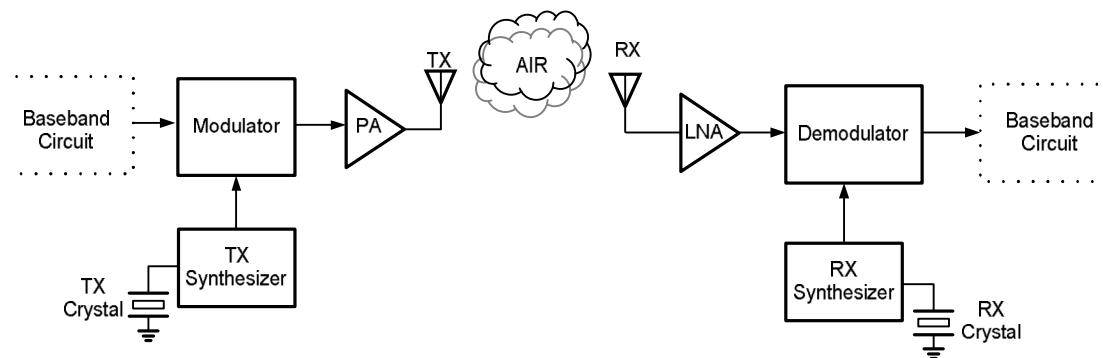

| 圖 2-2 無線通訊系統示意圖 .....                 | 6  |

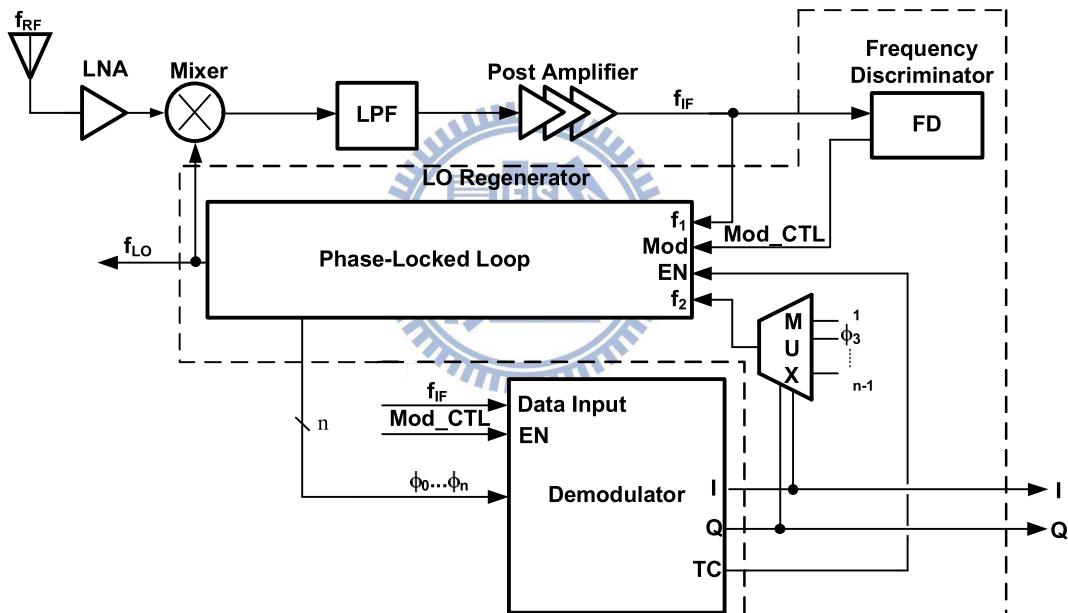

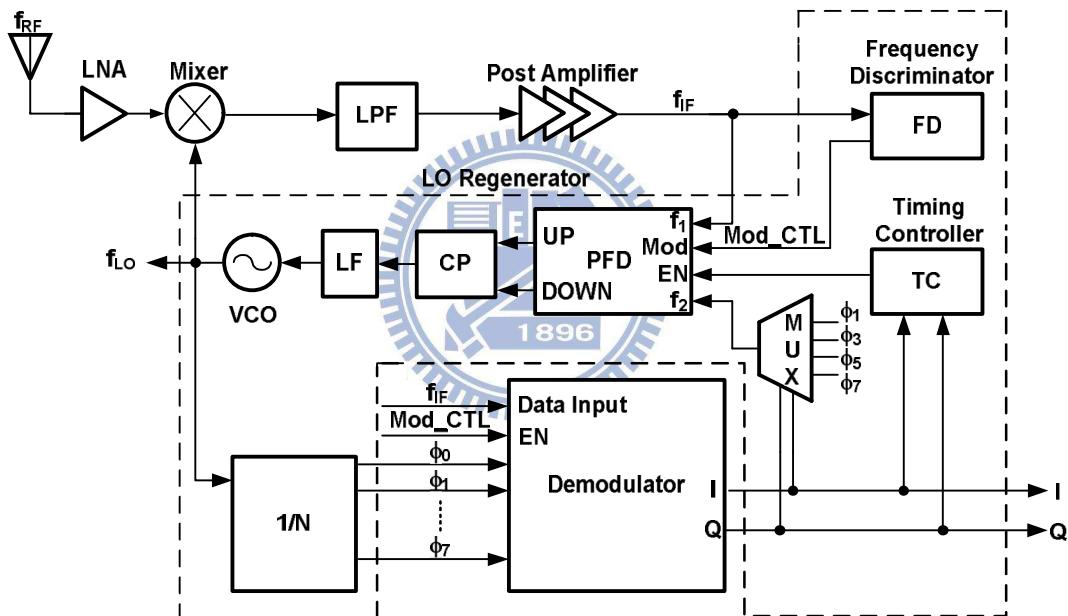

| 圖 2-3 無參考訊號源之無線接收器與資料解調器 .....        | 8  |

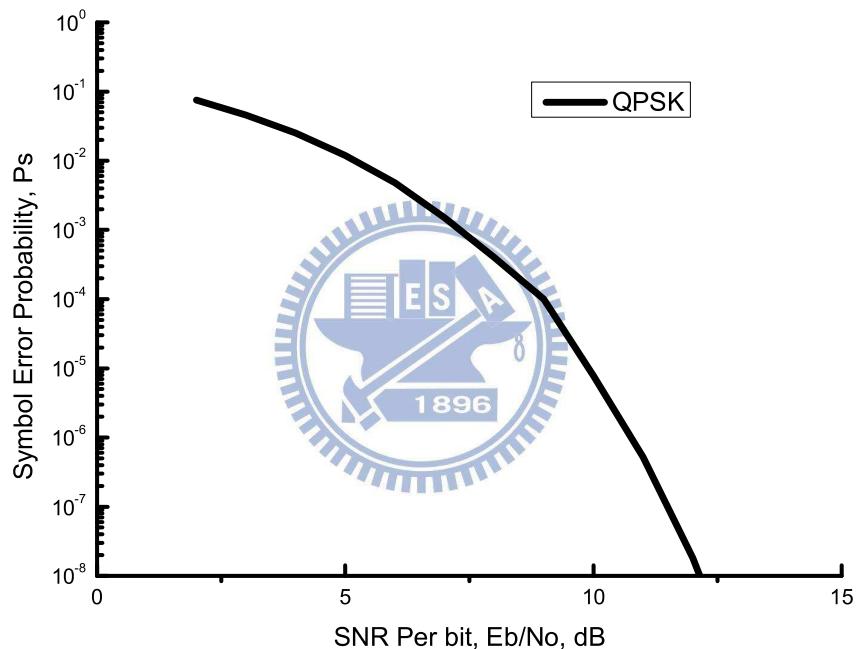

| 圖 2-4 QPSK 解調器的符號錯誤機率與訊號雜訊比的關係圖 ..... | 10 |

## 第三章

|                                                                                           |    |

|-------------------------------------------------------------------------------------------|----|

| 圖 3-1 電路系統架構圖 .....                                                                       | 11 |

| 圖 3-2 頻率追蹤模式 .....                                                                        | 12 |

| 圖 3-3 資料解調模式 .....                                                                        | 13 |

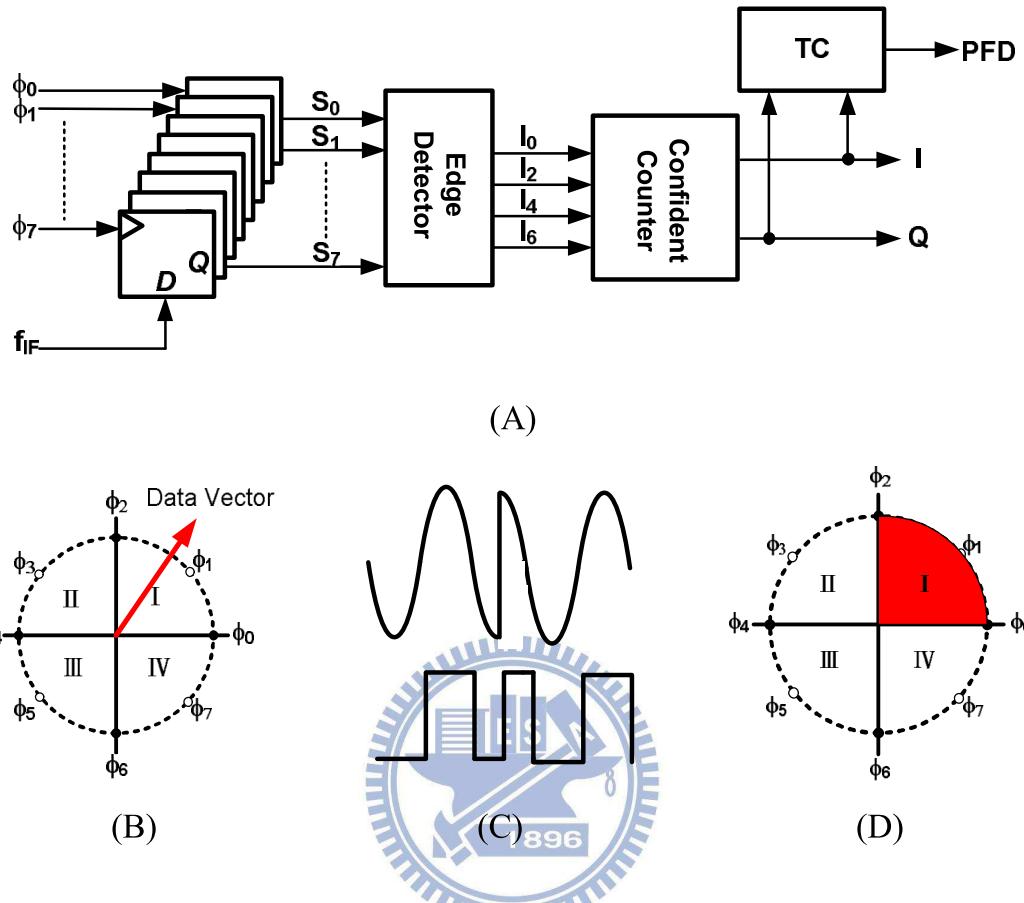

| 圖 3-4 (A) 相位選擇器, (B) 相域圖, 資料向量落於 $\Phi_1$ 與 $\Phi_2$ , (C) 資料的起始狀態, (D) 解碼後對應到的調變資料相位。 .. | 15 |

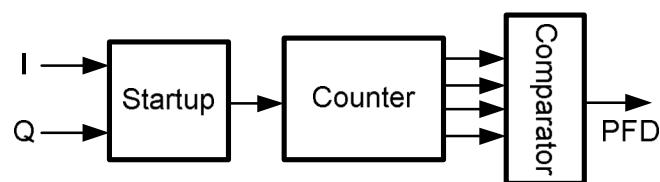

| 圖 3-5 時間控制器內部架構 .....                                                                     | 15 |

| 圖 3-6 時序圖 .....                                                                           | 15 |

| 圖 3-7 Matlab 系統模擬結果 .....                                                                 | 17 |

| 圖 3-8 接收端本地振盪頻率穩定圖與資料解調 .....                                                             | 18 |

## 第四章

|                                                                                      |    |

|--------------------------------------------------------------------------------------|----|

| 圖 4-1 (A) $G_m$ -Boosted common-gate LNA (B) $G_m$ -Boosted Common-gate 之等效電路圖 ..... | 19 |

| 圖 4-2 (A) 電感退化組態的共源極低雜訊放大器 (B) 共閘極低雜訊放大器 .....                                       | 20 |

| 圖 4-3 共閘極組態低雜訊放大器之雜訊貢獻 .....                                                         | 21 |

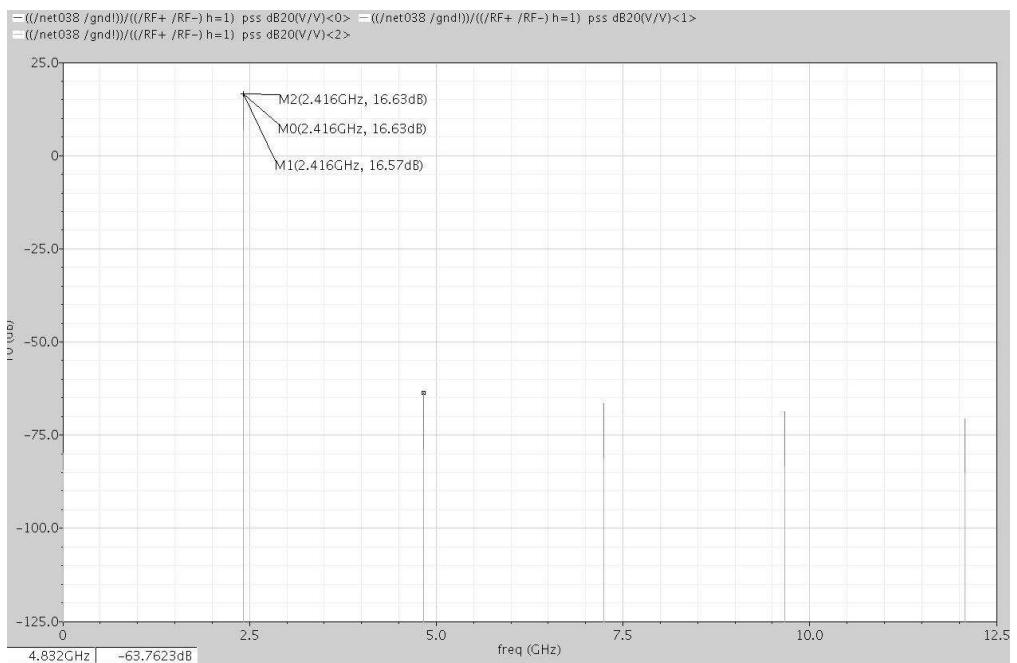

| 圖 4-4 功率增益 (Power Gain) .....                                                        | 22 |

| 圖 4-5 雜訊因數 (Noise Figure) .....                                                      | 22 |

| 圖 4-6 輸入反射參數 ( $S_{11}$ Return Loss) .....                                           | 23 |

| 圖 4-7 加入的靜態電流機制吉伯特雙旁帶混波器 .....                                                       | 25 |

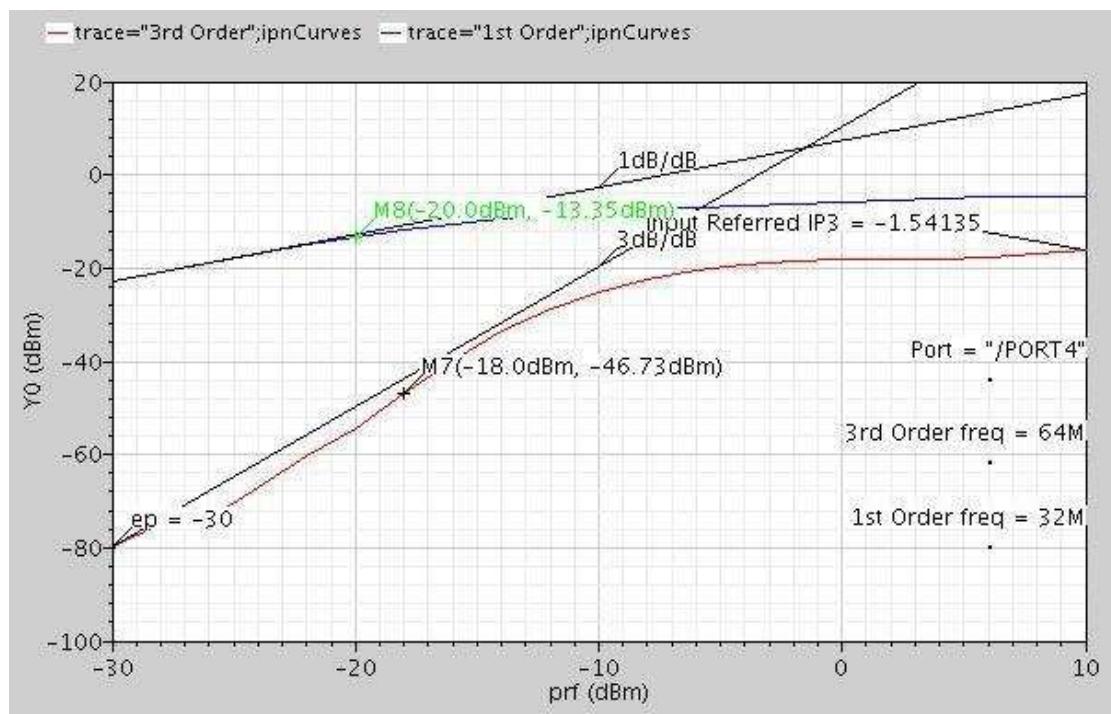

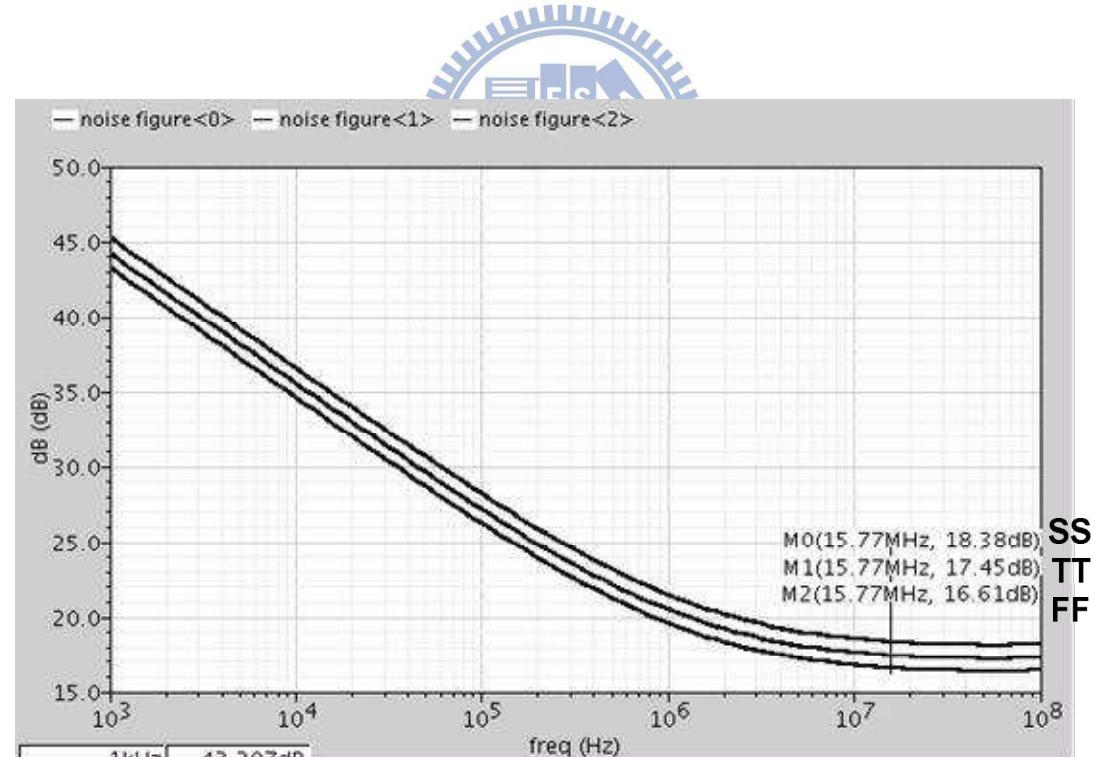

| 圖 4-8 輸入三階截止點(IIP3) .....                                                            | 26 |

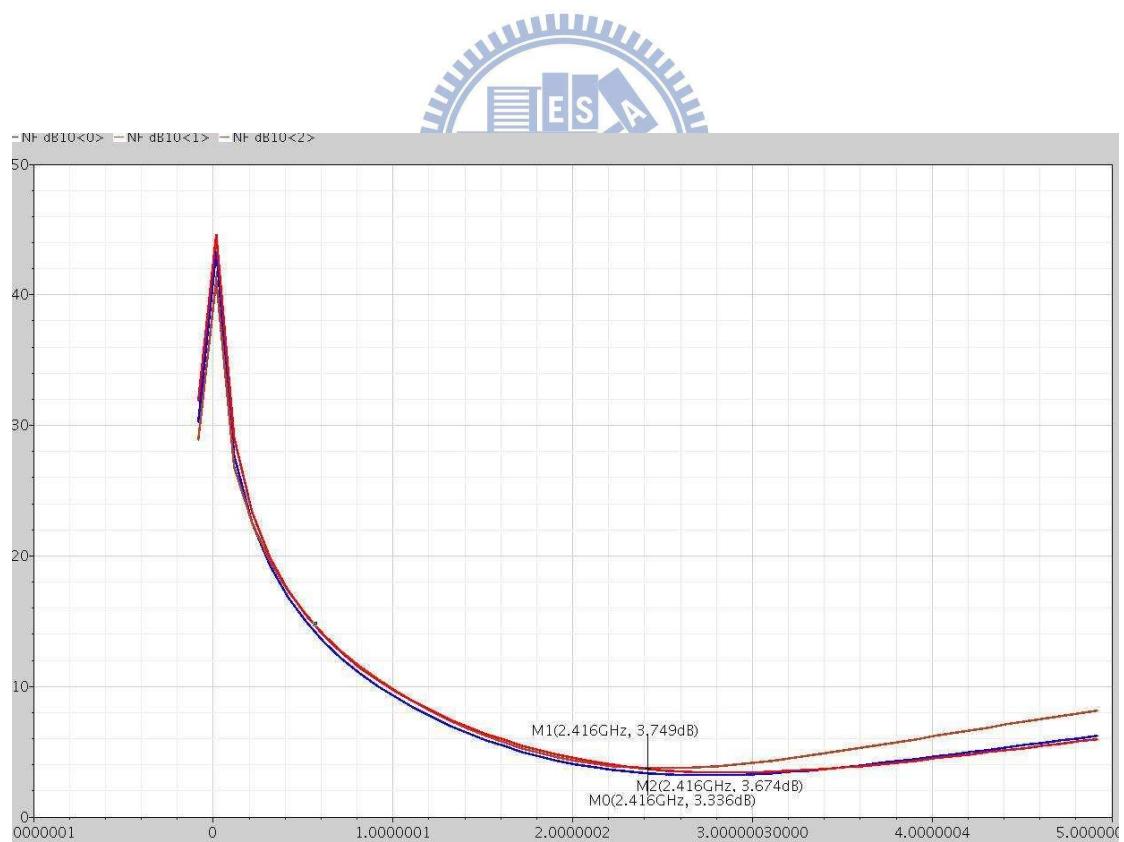

| 圖 4-9 雜訊因數(Noise Figure) .....                                                       | 26 |

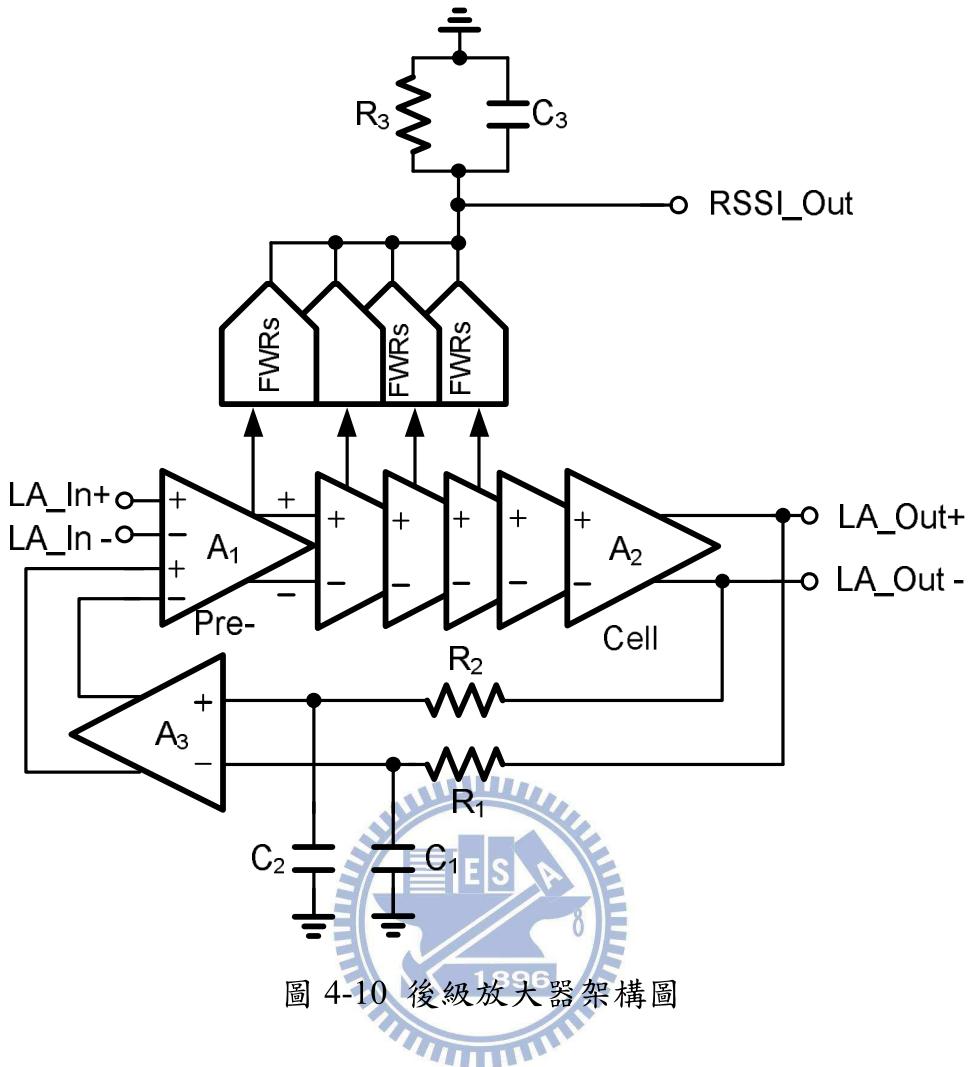

| 圖 4-10 後級放大器架構圖 .....                                                                | 28 |

| 圖 4-11 $A_2$ 放大器電路圖 .....                                                            | 29 |

|                                                     |    |

|-----------------------------------------------------|----|

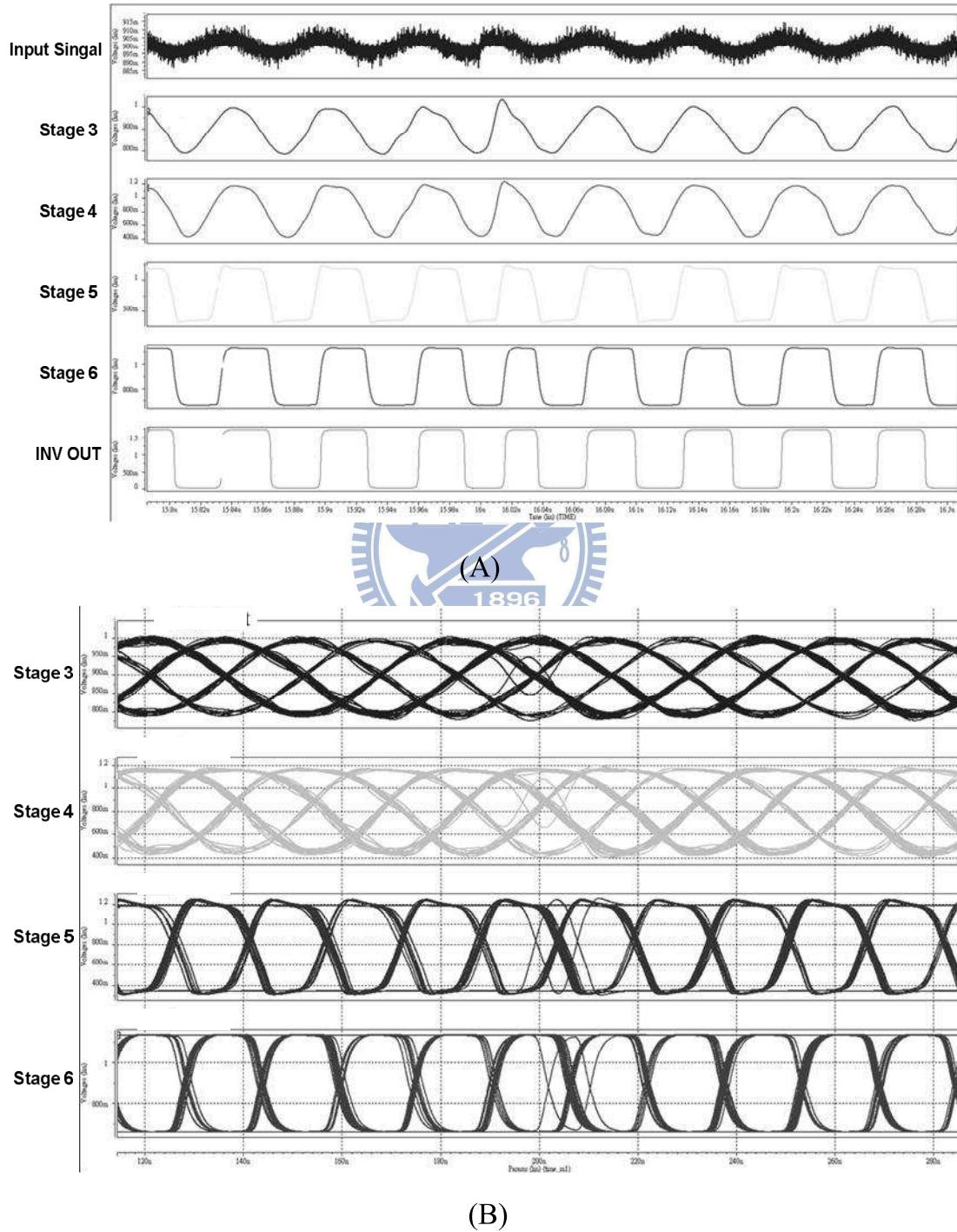

| 圖 4-12 (A) 輸入訊號與各級的輸出結果 (B)輸出波形之眼圖                  | 30 |

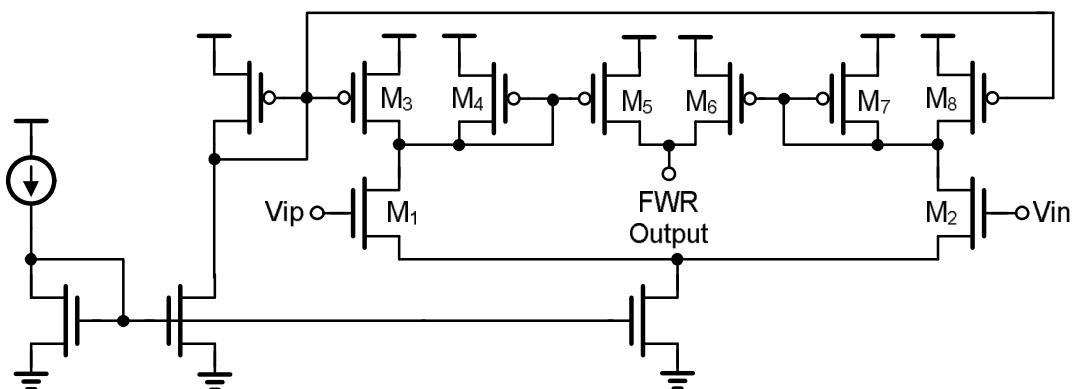

| 圖 4-13 為接收訊號強度指示(RSSI)之電路圖                          | 31 |

| 圖 4-14 接收訊號強度指示輸入與輸出的關係                             | 32 |

| 圖 4-15 (A) 相位頻率檢測器 (B) 相位和頻率檢測器的狀態圖(C) 相位和頻率檢測器的時序圖 | 34 |

| 圖 4-16 (A)相位和頻率檢測器的內部電路，(B)相位和頻率檢測器的特徵圖             | 35 |

| 圖 4-17 相位頻率偵測器中的 D 型正反器                             | 35 |

| 圖 4-18 充電汞電路架構                                      | 36 |

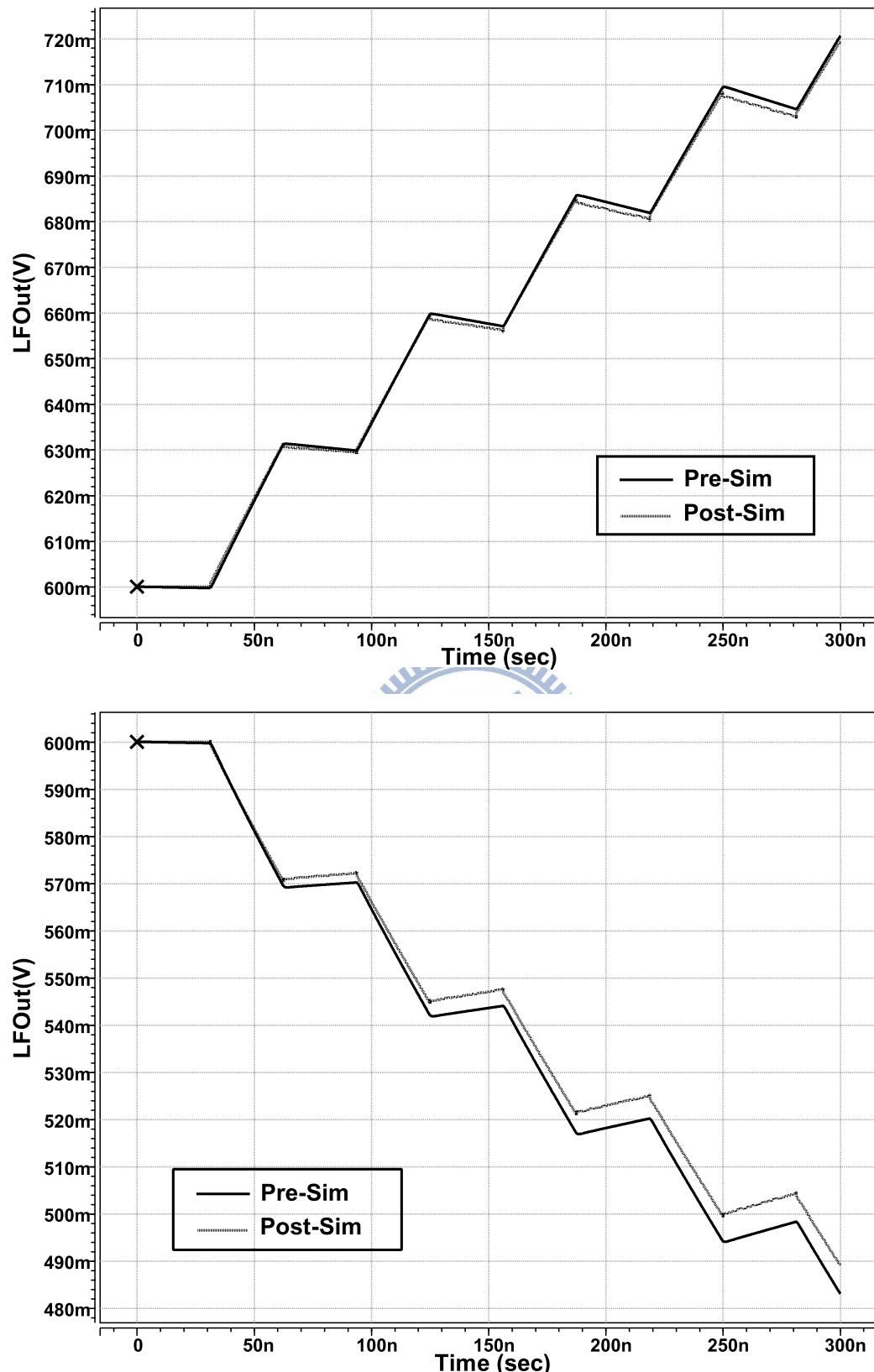

| 圖 4-19 充電汞充/放電的模擬結果                                 | 37 |

| 圖 4-20 充電汞充電與放電電流匹配度                                | 38 |

| 圖 4-21 二階迴路濾波器                                      | 38 |

| 圖 4-22 開迴路轉移函數波德圖                                   | 39 |

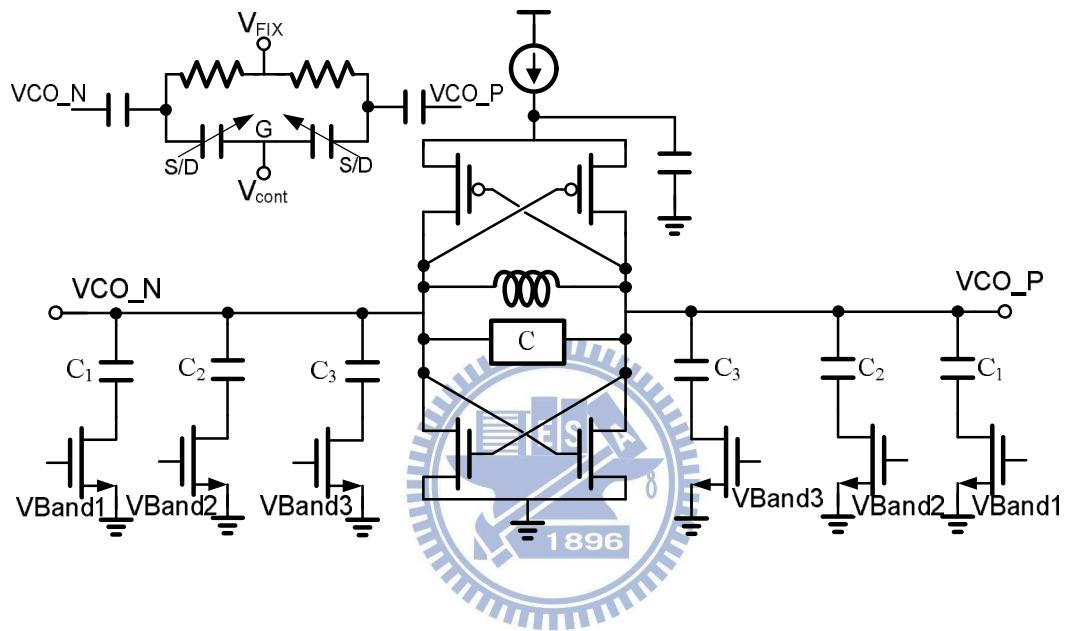

| 圖 4-23 互補式偶合壓控振盪器電路架構                               | 40 |

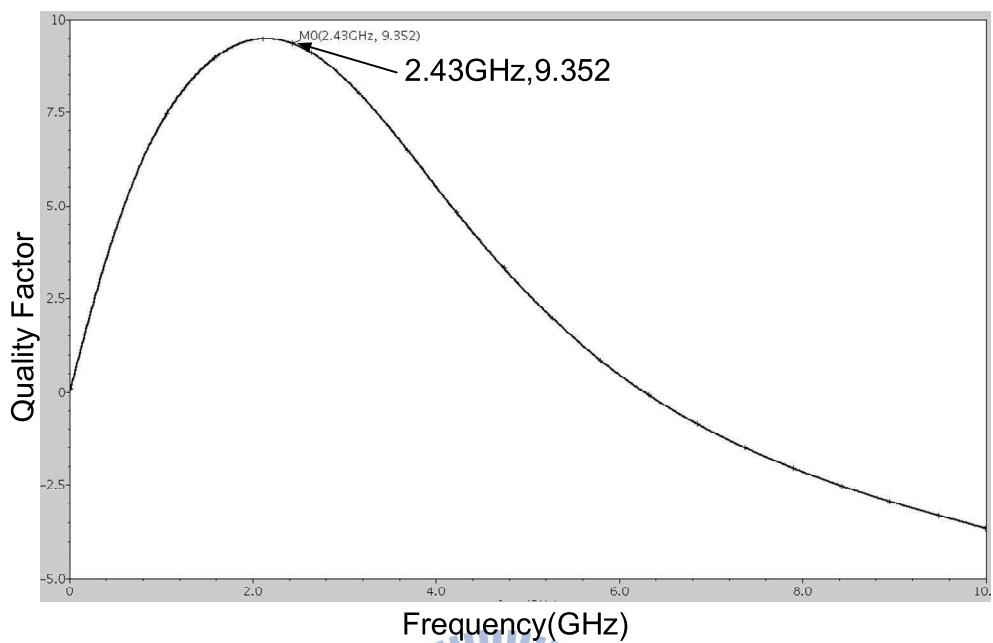

| 圖 4-24 電感品質因數對頻率的關係                                 | 42 |

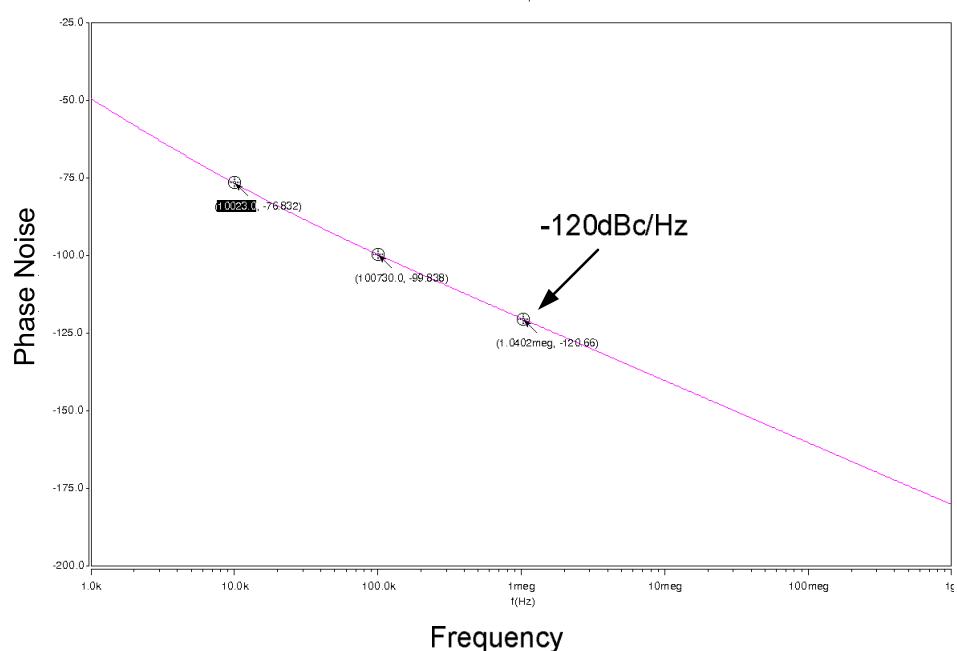

| 圖 4-25 壓控振盪器的相位雜訊模擬結果                               | 42 |

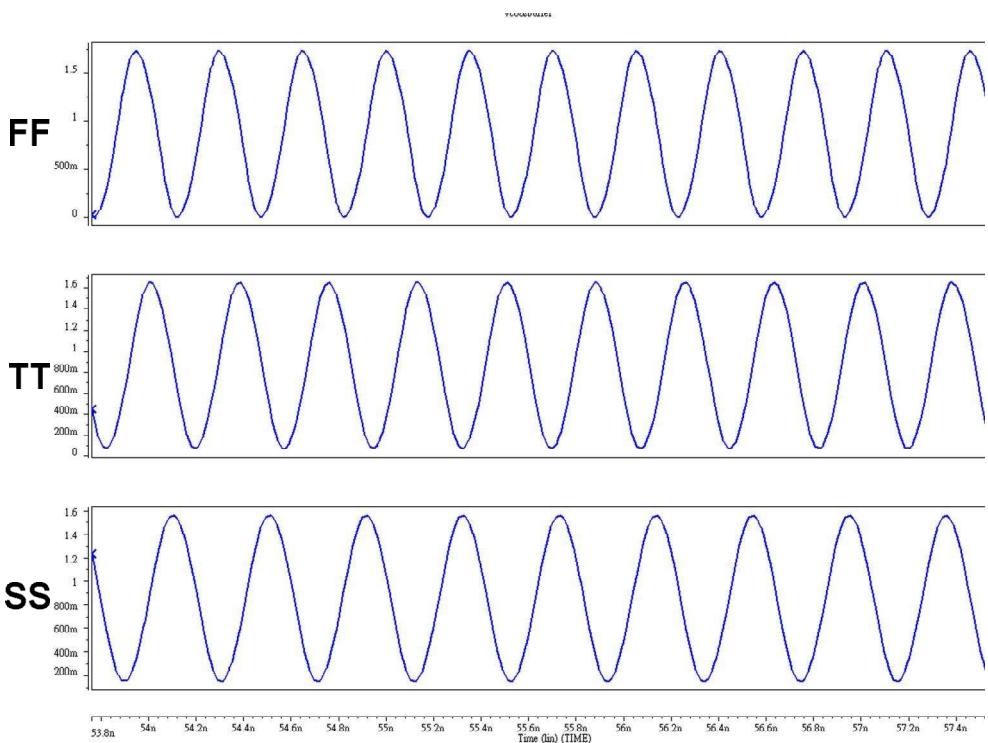

| 圖 4-26 各製程飄移下壓控振盪器的輸出波形                             | 43 |

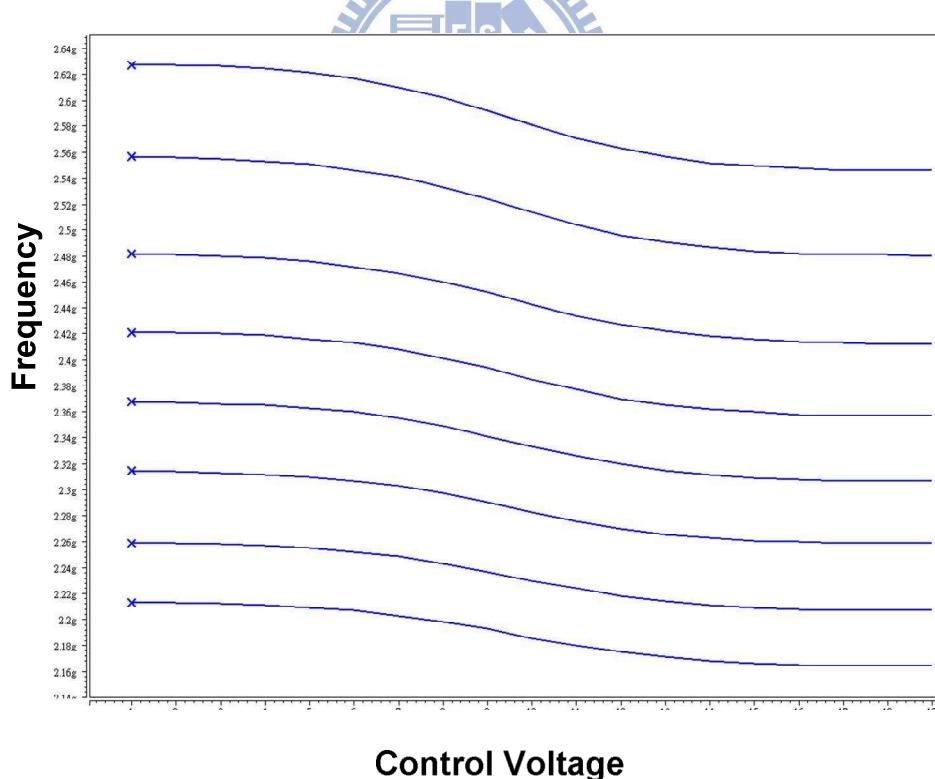

| 圖 4-27 壓控振盪器的頻率涵蓋範圍                                 | 43 |

| 圖 4-28 除頻器電路架構圖                                     | 45 |

| 圖 4-29 除 19 除頻器電路架構圖                                | 46 |

| 圖 4-30 內嵌 NAND 閘的 TSPC <sub>46</sub>                | 46 |

| 圖 4-31 除 8 除頻器電路架構圖                                 | 47 |

| 圖 4-32 除頻器在各製程變化下的模擬結果                              | 48 |

| 圖 4-33 (A)頻率檢知器的架構圖 (B)工作時序圖                        | 49 |

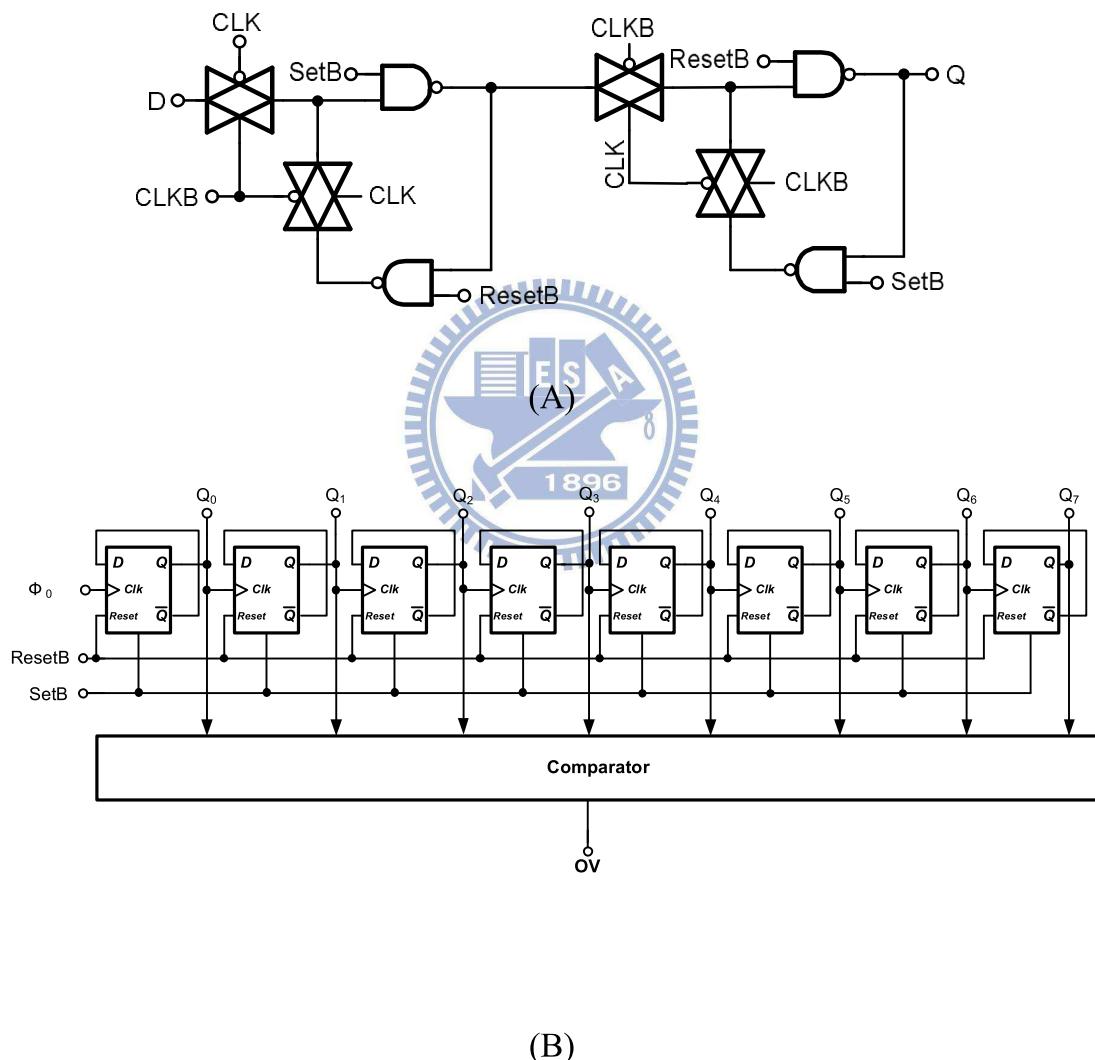

| 圖 4-34 (A)D 型靜態互補式正反器 (B)具有溢位偵測的 8 位元非同步計數器         | 50 |

## 第五章

|                                                      |    |

|------------------------------------------------------|----|

| 圖 5- 1 晶片照相圖與其腳位順序                                   | 53 |

| 圖 5- 2 儀器設置圖                                         | 54 |

| 圖 5- 3 壓控振盪器控制電壓對頻率的關係                               | 55 |

| 圖 5- 4 壓控振盪器輸出頻譜 (A)頻率取得模式 (B) 資料解調模式                | 56 |

| 圖 5- 5 壓控振盪器輸出之相位雜訊 (A)頻率取得模式(B)資料解調模式               | 57 |

| 圖 5- 6 頻率鎖定迴路濾波器的電壓變化                                | 58 |

| 圖 5- 7 鎖定後除頻器與中頻訊號的輸出波形                              | 58 |

| 圖 5- 8 (A)I/Q 輸出訊號之星座圖,QPSK 調變傳輸速率 1Mbps,(B) 輸出訊號之眼圖 | 59 |

圖 5-9 各電路功率消耗分佈圖 ..... 60

# 表目錄

## 第一章

表 1-1 各類振盪器特性比較[5] ..... 3

## 第二章

表 2-1 系統規格 ..... 9

## 第三章

表 3-1 系統規格 ..... 18

## 第四章

表 4-1 低雜訊放大器模擬結果 ..... 23

表 4-2 低雜訊放大器模擬結果 ..... 23

表 4-3 吉伯特混波器模擬結果(1) ..... 25

表 4-4 吉伯特混波器模擬結果(2) ..... 25

表 4-5 後級放大器規格表 ..... 32

表 4-6 在各製程變化下的模擬結果 ..... 44

表 4-7 除頻器在各製程變化功率消耗 ..... 48

## 第五章

表 5-1 晶片接腳配置表 ..... 53

表 5-2 各部分電路功率消耗分佈表 ..... 60

表 5-3 本晶片效能摘要表 ..... 61

# 第一章

## 簡介

### 1.1 相關背景與動機

近年來全球皆已邁入高齡化的時代，健康照顧將成為一個熱門的課題。以往對於病人身理訊號反應的監控，一般都是在病床邊使用數台昂貴的儀器，使用接線的方式，將病人的身理訊號呈現於儀器上，如此一來病患必須長時間待在醫院，增加了許多的醫療資源與費用的付出，且對於偏遠地區的居民的醫療資源也無法普及。

圖 1-1 無線近身網路的概念

由於近年來電路系統製程微小化、低功率與無線網路技術的進步，對於無線感測網路(Wireless Sensor Networks, WSN) [1][2]，在應用上提升了環境控制與自動監控的能力。將此技術整合於生物醫學上稱之為無線近身網路(Wireless Body Area Network, WBAN)，實現了遠距看護的目的。

無線近身網路的概念如圖 1-1 所示，人體上只需攜帶幾組微型感測

器，感測器會將身理訊號反應，透過無線近身網路使用 ZigBee (802.15.4)[3] 或 Bluetooth (802.15.1)[4]的通訊模式，傳到個人數位助理(PDA)、個人電腦 (PC)或是行動電話中，再透過乙太網路(Ethernet)或行動電話的第三代行動通訊技術(3<sup>rd</sup> Generation )，將擷取出的資訊送回醫院，醫生可在螢幕得知病患目前的狀況，藉由這些設備可以監控自身的身體狀況，並在緊急時通知醫療人員提供必要的協助。

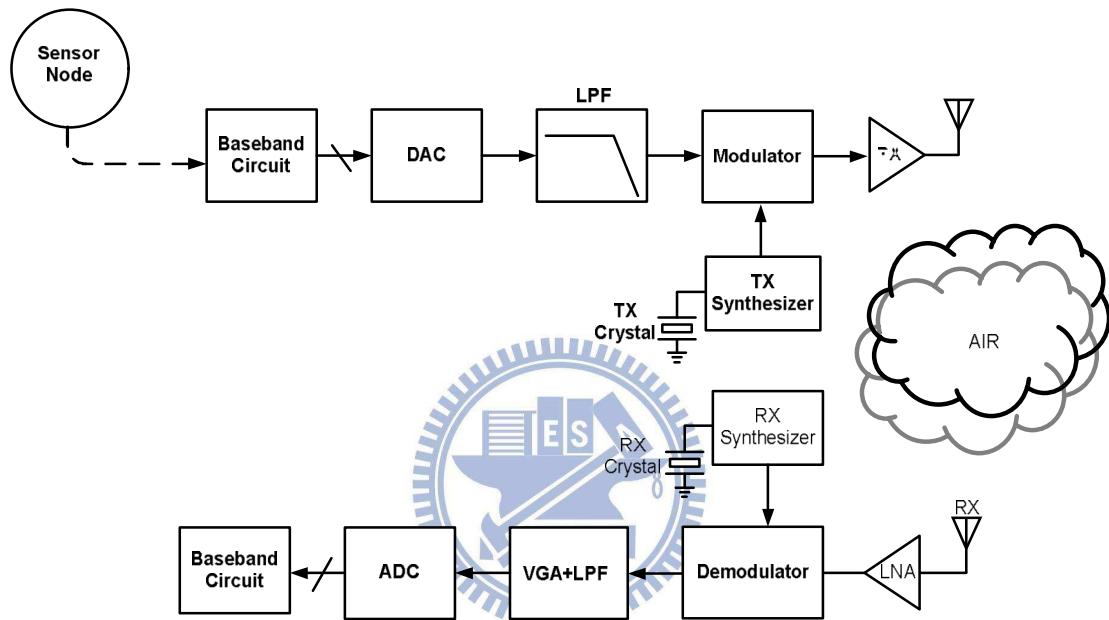

圖 1-2 典型之射頻無線傳輸系統

無線近身網路，利用射頻傳送接收器，透過無線傳送的機制連結感測器與監視主機，捨棄傳統接線傳輸的方式。一般典型的射頻通訊系統分為傳送端與接收端，如圖 1-2 所示，傳送端(TX)，由感測器節點(Sensor Node)截取出身理訊號，經由基頻電路(Baseband Circuit)做數位訊號處理，透過數位-類比轉換器(Digital-Analog Converter, DAC)轉換成類比訊號，經由低通濾波器(Low -Pass filter, LPF)濾除高頻的成份，訊號在調變器(Modulator)與傳送端之頻率合成器(TX -Synthesizer)作混波升頻，經由功率放大器(Power Amplify, PA)透過天線將訊號送出。接收端(RX)，由天線端接收到傳送端的微弱訊號，經由低雜訊放大器(Low Noise Amplifier，LNA)將訊號

放大，送入解調器(Demodulator)與接收端之頻率合成器(RX-Synthesizer)作混波降頻，透過低通濾波器與動態增益放大器(Variable Gain Amplifier, AGC)，將接收到的訊號放大至適當的位準與濾除高頻所帶來的雜訊，經由類比-數位轉換器(Analog-Digital Converter)將訊號轉換為數位訊號，傳送至基頻電路處理與還原出原始訊號。

頻率合成器在射頻收發器中扮演著關鍵的元件之一，主要的目的是產生多組且精確的頻率，以藉由調變器或解調器將射頻訊號上傳或下載至射頻頻帶，因此頻率合成器產生出的頻率穩定度對於射頻收發機而言是相當的重要的。頻率合成器在工作時必需要有一組參考訊號源，藉由此參考訊號，可讓頻率合成器的輸出訊號收斂至穩定的頻率，因此參考訊號源的選用對於射頻收發器上相當的關鍵。

|           | Crystal Oscillator              | MEMS Oscillator                  | Si Oscillator                   |

|-----------|---------------------------------|----------------------------------|---------------------------------|

| material  | Quartz                          | Si                               | Si                              |

| Power     | High                            | Medium                           | Medium                          |

| Size      | 2.5 x 2.0 x 0.8 mm <sup>3</sup> | 2.5 x 2.0 x 0.75 mm <sup>3</sup> | 2.0 x 1.6 x 0.5 mm <sup>3</sup> |

| Stability | <20ppm                          | <50ppm                           | <150ppm                         |

表 1-1 各類振盪器特性比較[5]

因此針對目前常用於頻率合成器之參考訊號源的元件介紹如下，如表 1-1 所示，目前最普遍使用的是石英晶體振盪器 (Crystal Oscillator)，其輸出頻率的精準度最高，但所消耗的功率也是最大，以一般市售的規格功率消耗約為 20mW 以上，由於石英晶體振盪器因材料的關係，使得在製程上無法與矽一樣可不斷的微小化。故若將此用於感測器電路板上，勢必無法將系統尺寸持續微小化，也無法做到低功率的目標。

## 1.2 組織架構

本論文主要分為六個章節，第一章，說明研究動機、應用情境與相關的系統規格介紹；第二章，介紹我們所提出的無參考訊號源之無線解調器，比較傳統架構的優缺點與系統分析；第三章，說明系統細部之工作原理；第四章，介紹組成本系統之詳細電路；第五章，實驗量測結果，第六章，結論。

## 第二章

### 系統架構

#### 2.1 頻率合成器簡介

圖 2-1 頻率合成器架構圖

頻率合成器在無線通訊系統、數位電路及資料傳輸介面中應用層面相當廣泛，更是佔有不可缺少的關鍵角色。然而鎖相迴路的概念已在半世紀前就已經開始發展，在現今電路系統中要求微小化、高整合度、低功率消耗和低成本已成現今積體電路的基本設計要求。在無線通訊應用上藉由頻率 (Frequency Modulation, FM)、相位 (Phase Modulation, PM) 與振幅 (Amplitude Modulation, AM) 的調變方式將信號與鎖相迴路產生的時脈信號混波再載入空氣中傳撥，接收端再經放大後經鎖相迴路產生解調時脈把

接收到的信號解調產生出原始的資料。在數位電路應用中，為了有更高效能的運算效率，在多級管路的運算單元內，時脈產生電路也是不可缺少之元件，同時資料傳輸中在電路串列/解串列的過程中，精準的時脈產生電路也是整個設計關鍵的一環。

如圖 2-1 所示，鎖相迴路 (Phase Locked Loop, PLL)，其中電壓控制振盪器 (Voltage Control Oscillator, VCO)，輸出端  $f_{OUT}$  會產生週期的輸出訊號，其頻率的快慢依據輸入端  $V_{Ctrl}$  控制。除頻器(Divider)，輸入端接收到  $f_{OUT}$  依據除頻器的除頻倍率(N)，輸出端會得到  $f_{FB}=f_{OUT}/N$ 。相位頻率偵測器(Phase Frequency Detector, PFD)，輸入端接收參考訊號  $f_{REF}$  與除頻器輸出的迴授訊號  $f_{FB}$ ，以  $f_{REF}$  為基準比較  $f_{FB}$  的相位差，輸出端產生相位領先 (up)與相位落後(dn)的訊號。充電泵(Charge Pump, CP)，依據相位頻率偵測器輸出的相位領先與落後的資訊，啟動充電泵上的開關，將相位誤差的時間轉換為電流訊號，再利用電容與電阻組成的低通濾波器將誤差電流量轉換為電壓並濾除一些由充電泵產生的高頻雜訊，調整  $V_{ctrl}$  的值，校正電壓控制振盪器的頻率。經由一連串的動作後當  $f_{FB}$  與  $f_{REF}$  相位差為零時，此時迴路鎖定，可提供一穩定的時脈訊號供後級使用。

圖 2-2 無線通訊系統示意圖

因此參考訊號的精準度與穩定度對與頻率合成器是非常重要的，如圖2-2 所示，頻率合成器應用於無線通訊系統中，需提供一個穩定的時脈訊號，使發射端能混波於正確的頻段，接收端接收到訊號從相同的頻段中解調出原始的訊號。由於傳送端與接收端的所使用參考訊號源，並不是同一組石英晶體振盪器，故傳送端與接收端的頻率合成器產生出的時脈訊號會有所差異，因此會造本地振盪頻率偏移的現象(LO Offset)，當誤差過大會導致接收端解調出的資料錯誤，我們將於下一節提出改善的方法。

## 2.2 無參考訊號源之無線接收器與資料解調器

系統晶片 (System on Chip, SoC)，為積體電路設計的主要的目標，系統晶片可以使產品降低製作成本，同時產品更輕薄具有競爭力，有鑑於前些章節所討論到的，傳統無線通訊有本地振盪的頻率誤差、整體系統的消耗過大等問題，故本論文將提出無參考訊號源之無線接收器與資料解調器，將針對高度整合度、低成本、低功率消耗與改善本地振盪頻率誤差為設計目標。

圖 2-3 無參考訊號源之無線接收器與資料解調器

如圖 2-3 所示，利用鎖相迴路為基礎，設計出的無線接收器，主要為追蹤發射端的載波頻率訓練接收器，使接收端與發射端頻率同步。電路初始時鎖向迴路內的電壓控制振盪器自振，當接收到傳送端的載波訊號時，接收端依據此訊號訓練鎖相迴路使系統達到收斂。

由於無線近身網路，使用藍芽或 ZigBee 系統的標準通訊協定，因此我們選用藍芽通訊系統規格為範本，設計我們所提出之短距離無線通訊傳輸系統，如表 2-1 所示，藍芽系統規格與本系統預計規格列表作一個整理。

| Item           | Bluetooth Spec.                                        | This Work                  |

|----------------|--------------------------------------------------------|----------------------------|

| Frequency Band | 2.4000GHz~2.4835GHz                                    | 2.416GHz                   |

| Data Rate      | 1Mb/s                                                  | 1Mb/s                      |

| Modulation     | GFSK                                                   | QPSK                       |

| Sensitivity    | -70dBm(for BER $10^{-3}$ )                             | -70dBm(for BER $10^{-3}$ ) |

| Locking Time   | <200us                                                 | <200us                     |

| Phase Noise    | <-80dBc/Hz@1MHz<br><-110dBc/Hz@2MHz<br><120dBc/Hz@3MHz | <-110dBc/Hz@1MHz           |

表 2-1 系統規格

依據通訊原理中的 M 位元 PSK 系統上定義的符號錯誤機率  $P_{S,MPSK}$

$$P_{S,MPSK} = erfc\left[\sqrt{\frac{\log_2(M)E_b}{N_0} \sin\left(\frac{\pi}{M}\right)}\right] \quad (M > 2) \quad (2-1)$$

其中

$erfc$  : 錯誤函數(error function)

$M$  : 為資料位元數目

由式(2-1)可描繪出圖 2-4，由圖 2-4 可知  $10^{-3}$  的符號錯誤機率對應到的 SNR 約為 8dB 依據藍芽系統歸範定義的資料錯誤率  $10^{-3}$  條件下接收靈敏度為 -70dBm，可由(2-2)

$$P_{in,min} = P_{RS}|_{dBm/Hz} + NF|_{dB} + 10\log BW + SNR_{min}|_{dB} \quad (2-2)$$

其中

$P_{in,min}$  : 輸入訊號的最小功率

$P_{RS}$  : 來源電阻雜訊功率

$NF$  : 雜訊因素

$BW$  : 資料頻寬，系統的中頻頻率為 16MHz

$SNR_{min}$  : 最小輸出的訊號雜訊比例

可得知系統的最低雜訊指數需小餘 24dB，因此可定義出我們的射頻前端電路所需的參數。

圖 2-4 QPSK 解調器的符號錯誤機率與訊號雜訊比的關係圖

我們針對 2.416GHz 頻段設計本系統，預估本系統的規格為資料傳輸率為 1Mb/s，調變訊號使用 QPSK 調變模式，資料錯誤率  $10^{-3}$  的條件下接收靈敏度為 -70dBm，系統鎖定時間須小於 200us，相位雜訊在 1MHz 時小於 -110dBc/Hz。

## 第三章

# 無參考訊號源之無線接收器與資料解調器系統設計

### 3.1 系統工作原理

圖 3-1 電路系統架構圖

整個詳細之無石英晶體振盪器之無線接收器與資料解調電路如圖3-1所示。其架構由一低雜訊放大器(LNA)，混波器(Mixer)，後級放大器(Post Amplifier)，低通濾波器(Low Pass Filter)，頻率還原器(LO Regenerator, LOR)，與資料解調器(Data Demodulator)整合於單一晶片中，其可應用在相位調變(BPSK，QPSK 等) 之無線接收機。其中虛線部分為頻率還原器。頻率還原過程將經歷兩個步驟，(1)頻率追蹤步驟 (2)相位頻率追蹤及資料解調。茲說明如下：

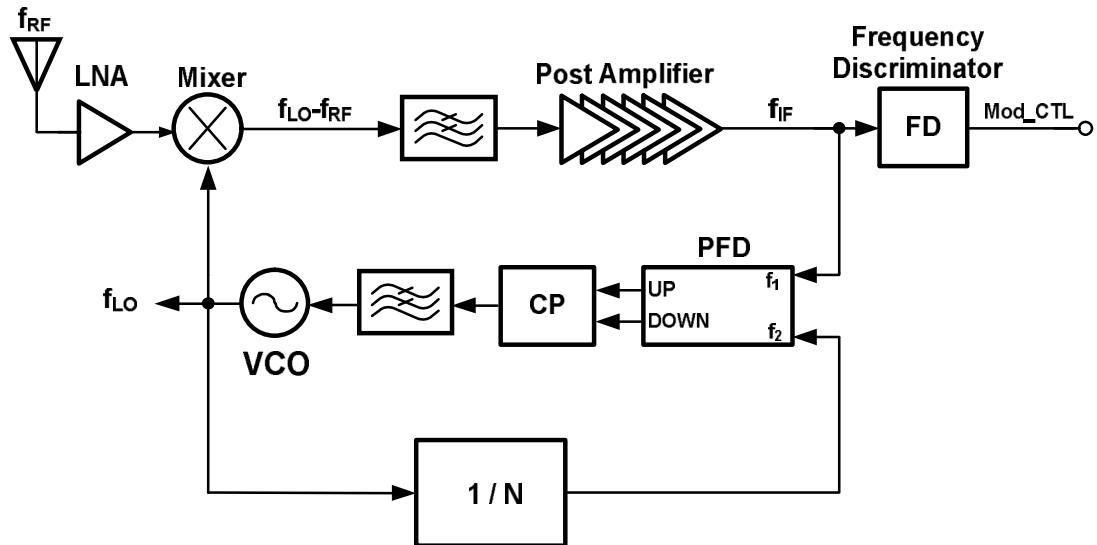

### 3.1.1 頻率追蹤步驟

圖 3-2 頻率追蹤模式

在系統初始狀態，令壓控振盪器之頻率為  $f_{LO}$ ，且  $f_{LO}$  預設為高於接收端之射頻信號( $f_{RF}$ )。此時發射端將傳送固定頻率導引信號  $f_{RF}$  (preamble) 進行通道連結。則接收端經降頻後之中頻信號為  $f_{IF}$ ，且

$$f_{IF} = f_{LO} - f_{RF} \quad (3-1)$$

此時，電壓控制振盪器經由除頻器 ( $1/N$ ) 產生多組相位輸出之除頻後信號 ( $\Phi_0 \dots \Phi_7$ )，其頻率皆為  $\frac{f_{LO}}{N}$ ，若將  $f_{IF}$  與固定相位之除頻器輸出信號 (如  $\Phi_0$ ) 進行相位頻率比較，且若

$$(f_{LO} - f_{RF}) > \frac{f_{LO}}{N} \quad (3-2)$$

則降低振盪器之輸出頻率。反之，若

$$(f_{LO} - f_{RF}) < \frac{f_{LO}}{N} \quad (3-3)$$

則提高振盪器之輸出頻率。如此一來壓控振盪器與相頻偵測器將構成負回授之鎖相迴路，當系統達到穩定狀態，則

$$f_{LO} = f_{RF} \frac{N}{N-1} \quad (3-4)$$

因此僅需藉由設定除頻器係數，同時經由天線接收之射頻導引信號(preamble)，即可達到初步之頻率追蹤。當頻率還原器透過射頻導引信號完成初步頻率鎖定，頻率檢知器(Frequency Discriminator)會偵測目前的中頻訊號，當中頻訊號滿足系統內設定的條件時(Mod\_CTL)會送出控制訊號，將系統由目前的頻率還原器切換至相位頻率追蹤及資料解調模式。

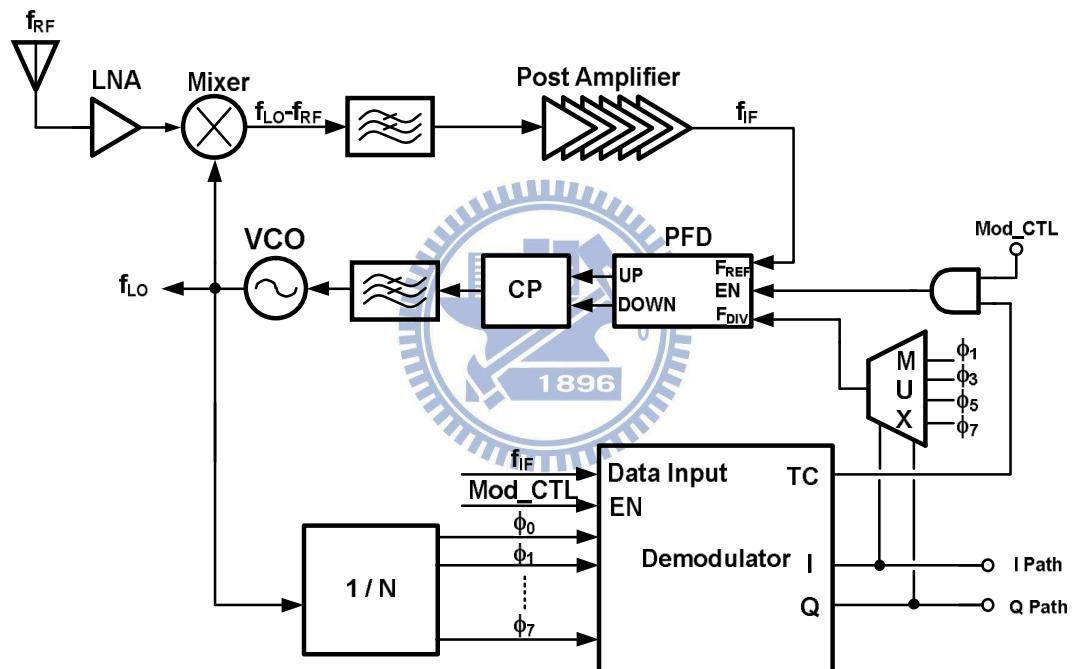

### 3.1.2 相位頻率追蹤及資料解調

圖 3-3 資料解調模式

當頻率檢知器切換系統模式於頻率追蹤及資料解調模式時，代表接收端的頻率與發射端的頻率同步，發射端即可開始傳送資料。本系統所使用的是 QPSK 的資料調變系統，是將資料載在相正交的兩個載波上傳輸，故也可以相位的變化來判定目前訊號的資料型態，因此我們在還原資料時可依據每一筆資料的相位的資訊，加以還原資料與修正接收端的頻率還原器所產生出訊號相位誤差。

當發射端資料為相位調變信號。亦即射頻信號 ( $f_{RF}$ ) 及降頻後之中頻信號 ( $f_{IF}$ ) 將在( $45^\circ, 135^\circ, 225^\circ, 315^\circ$ ) 之間進行相位切換。此時除頻器產生 8 個相位均勻分佈之信號( $\Phi_0 \dots \Phi_7$ )，其中( $\Phi_0, \Phi_2, \Phi_4, \Phi_6$ )將均分一個週期同時產生四個相位區(I, II, III, IV)，各自為  $90^\circ$  區間。此時令( $\Phi_1=45^\circ, \Phi_3=135^\circ, \Phi_5=225^\circ, \Phi_7=315^\circ$ ) 為鎖定時之目標相位。為達相位及頻率追蹤，其中中頻信號( $f_{IF}$ ) 將藉由相位選擇電路，如圖 3-4(A)所示，相位選擇器，判斷調變信號之相位區(I, II, III, IV)，並據此將目標相位( $\Phi_1=45^\circ, \Phi_3=135^\circ, \Phi_5=225^\circ, \Phi_7=315^\circ$ )透過多工器(MUX)導入至相位頻率偵測器，以持續進行相位及頻率追蹤。而此時相頻偵測器將進入調節模式 (Gating mode)，其在偵測到輸入參考相位切換過程如圖 3-6 所示，其中之  $C_{dm}$  為資料解碼時間， $C_{su}$  為下一筆資料的設定時間，在這兩段時間內將不進行相位比較，以避免迴路之誤動作，此一部份將藉由計時控制器 (Timing Controller, TC) 進行系統控制，在此同時，由於相位選擇電路已分辨出中頻信號 ( $f_{IF}$ ) 之相位區域，其座落區間即為相位解調變之結果。我們將細部分解相位選擇器內部之動作原理，如圖 3-4(B)(C)(D)所示，利用除頻器產生的相位均勻分布之信號( $\Phi_0 \dots \Phi_7$ )透過多組 D 型正反器檢測中頻調變信號之相位區域，經由邊緣偵測器(Edge Detector)偵測每筆資料的起始檔頭，依照資料的所在區域將資料歸納為( $I_0, I_2, I_4, I_6$ )對應於相位的(I, II, III, IV)，透過信心計數器(Confident Counter)確認資料所在之區域的正確性後編碼成 QPSK 之 I、Q 訊號，時間控制器依據解碼出的第一筆 I, Q 訊號，啟動內部計數器並在適當的時間內開啟相位頻率偵測器。

為了確保系統的穩定性，系統定義的資料速率為 1Mbps、中頻訊號為 16MHz，如圖 3-4(B)所示，每筆資料向量會在該資料相位區間內停留 16 次，且避免頻率偏移而導致資料向量滑出正確的相位區間，由上述的行為可計算出資料解調模式的迴路穩定條件，定義每筆資料必須在 1/2 的相位

區間內停留 16 次，則迴路穩定條件為中頻訊號偏移量( $\triangle IF$ )必須小餘 125KHz。

圖 3-4 (A) 相位選擇器，(B) 相域圖，資料向量落於  $\Phi_1$  與  $\Phi_2$ ，(C) 資料的起始狀態，(D) 解碼後對應到的調變資料相位。

圖 3-5 時間控制器內部架構

圖 3-6 時序圖

### 3.2 迴路頻寬設計

首先我們先決定鎖相迴路的閉迴路頻寬，由 2.1 節我們可以知道藍芽無線接收器對於相位雜訊的規範主要是在偏移中心載波頻率 1MHz 到 3MHz 的地方，而在這一個偏移頻率下，雜訊主要的來源會是從壓控振盪器，理由如下。由於充電汞與迴路濾波器雜訊所看到的轉移函數是低通函數，所以在該偏移頻率下的雜訊會被接收端內的鎖相迴路濾掉，但是壓控振盪器看到的是高通的轉移函數，所以其雜訊無法被濾掉；迴路頻寬以一般經驗法則約取參考頻率  $1/10 \sim 1/15$  倍以上，原因在於充電汞本身是屬於一個離散時間的系統當迴路的頻率遠小於參考訊號時可近似於一個連續的時間系統，且可濾除掉充電汞工作時所帶來的雜訊。在本系統由在解調變模式時，以圖 3-6 所示，相頻偵測器將進入調節模式，只會在特定的時間內啟動相位頻率的校正，以目前系統的定義，一筆資料歷經 16 個週期，取其中的 4 個週期作校正。依據經驗法則且使雜訊對系統的影響降低，我們取迴路頻寬約為參考訊號的  $1/50$  倍，再考慮相位頻率偵測器的工作週期則可計算出我們的迴路頻寬約為 80KHz。

### 3.3 系統模擬

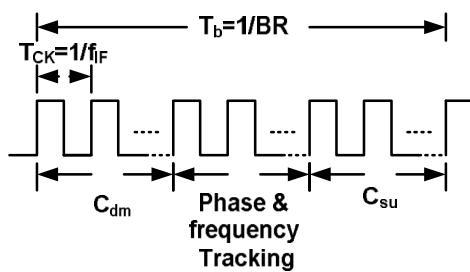

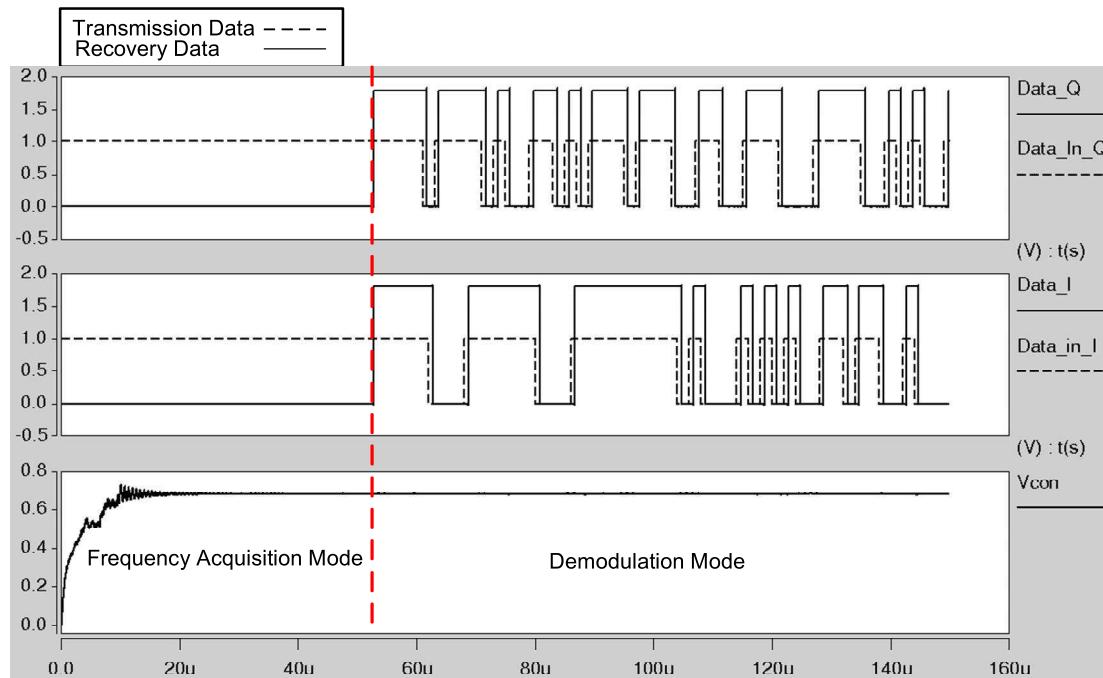

我們將以上的概念利用 Matlab 作系統驗證，設定本地振盪的起使頻率為 2.48GHz，經由發射端傳送出固定頻率導引信號，對接收端進行資料通道的連結，因訊號是透過天線在空氣中傳送，故接收到的訊號品質必須要將雜訊一起考慮，在模擬時加入了添加白高斯雜訊(Additive White Gaussian Noise, AWGN)，將訊號對雜訊品質(SNR)設定於 10dB，觀察本地振盪還原器的輸出頻率變化與解調出的資料 I/Q 訊號的資料錯誤率。由圖 3-7 所示頻率最後穩定於 2.432GHz，頻率檢知器於約 97us 時送出鎖定訊號，將系統切換至頻率追蹤及資料解調模式，於資料解調模式驗證出的資料錯誤率約為 0(BER  $\approx 0$ )。如圖 3-8 所示，由電晶體層級(Transistor Level) 是利用 Matlab 模擬傳送端並加入訊號品質考慮設定 SNR 為 10dB，將產生出的資料載入模擬軟體中，實現本系統之模擬結果，系統約於 55us 時切換為頻率追蹤與資料解調模式，I 與 Q 為資料解調器所解出的資料，與原始資料比對後的資料錯誤率約為 0(0/98)。在電晶體層級，由於模擬軟體的記憶體限制，無法載入太長的資料，故我們只驗證電路的可行性後，故其餘的驗證可由 Matlab 中觀察之。

圖 3-7 Matlab 系統模擬結果

圖 3-8 接收端本地振盪頻率穩定圖與資料解調

下表為系統目標規格

|                        |                         |

|------------------------|-------------------------|

| Process                | TSMC 0.18 um CMOS       |

| Supply Voltage         | 1.8V/3.3V(Buffer)       |

| Frequency Band         | 2416MHz                 |

| Intermediate Frequency | 16MHz                   |

| Moulation              | QPSK                    |

| Lock Time              | <200us (for Blue tooth) |

| Data Rate              | 1Mbit/s                 |

| Phase Noise            | < -110dBc/Hz @ 1MHz     |

表 3-1 系統規格

# 第四章

## 電路設計與實現

### 4.1 低雜訊放大器設計 (Low Noise Amplify)

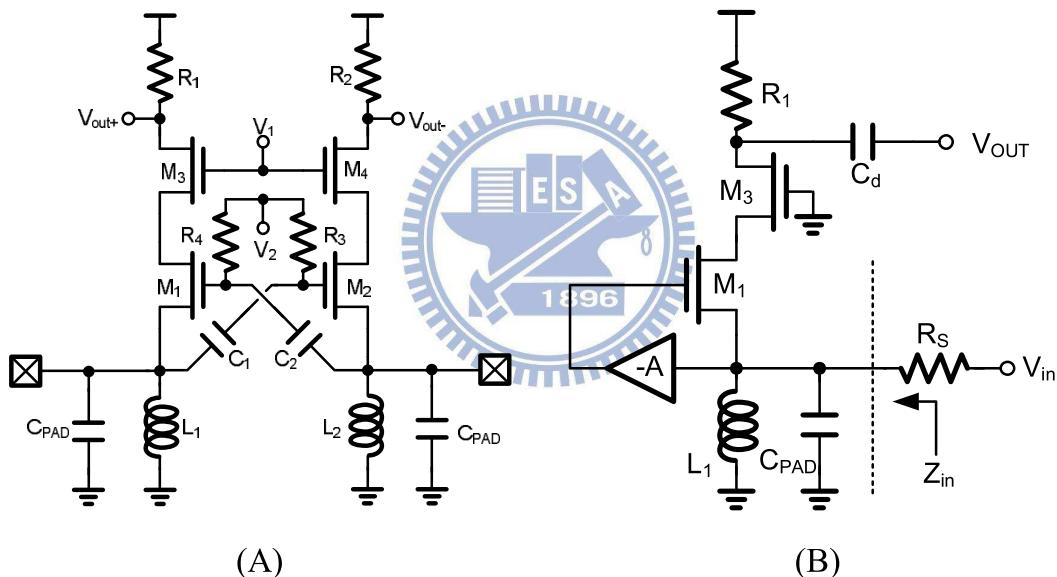

圖 4-1 (A)  $G_m$ -Boosted common-gate LNA (B)  $G_m$ -Boosted Common -gate 之等效電路圖

射頻前端電路主要由低雜訊放大器(Low Noise Amplify, LNA)[6]，與混波器(Mixer)所組成，由於射頻前端所接收到的訊號都是非常微弱的，在設計上必須注意到兩個設計時的要點，由天線端接收到射頻訊號能量是否能全部轉移到輸入端，不會因阻抗未匹配而造成訊號的衰減，其二，為了提高接收端的靈敏度，故雜訊對於放大器的影響，及如何降低雜訊是一個設

計的關鍵。由於一般的射頻天線與量測儀器都是  $50\Omega$  ( $R_s$ ) 輸出阻抗，為了要使輸入訊號的能量在最低的損失下，全部輸出至低雜訊放大器的輸入端，則必須將電路的輸入阻抗設計為  $50\Omega$ ，如圖 4-1 所示，為了要達到阻抗匹配的目的必須將  $Z_{in}$  設計成  $50\Omega$ ， $C_{PAD}$  為晶片針腳上的寄生電容，利用  $L_i$  與  $C_{PAD}$  形成共振的特性，將  $C_{PAD}$  消除。

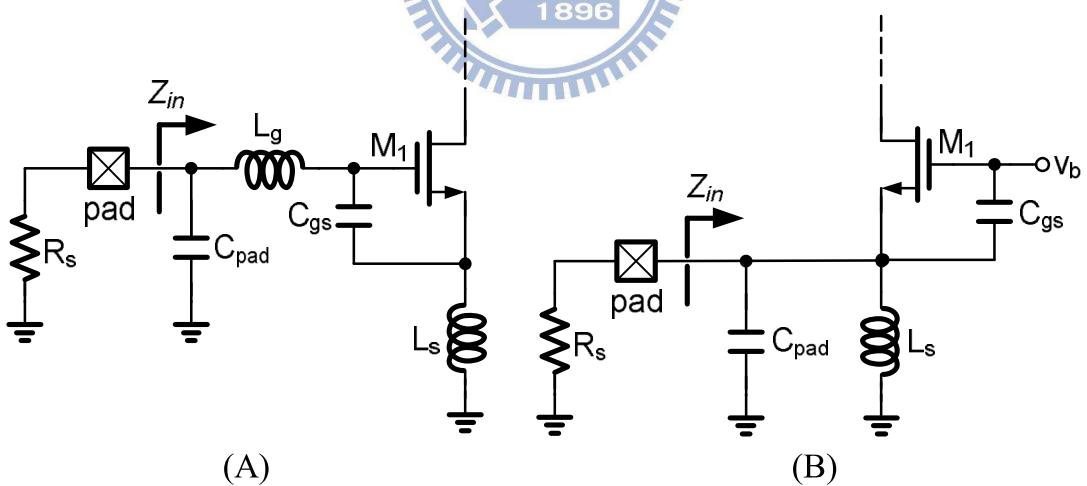

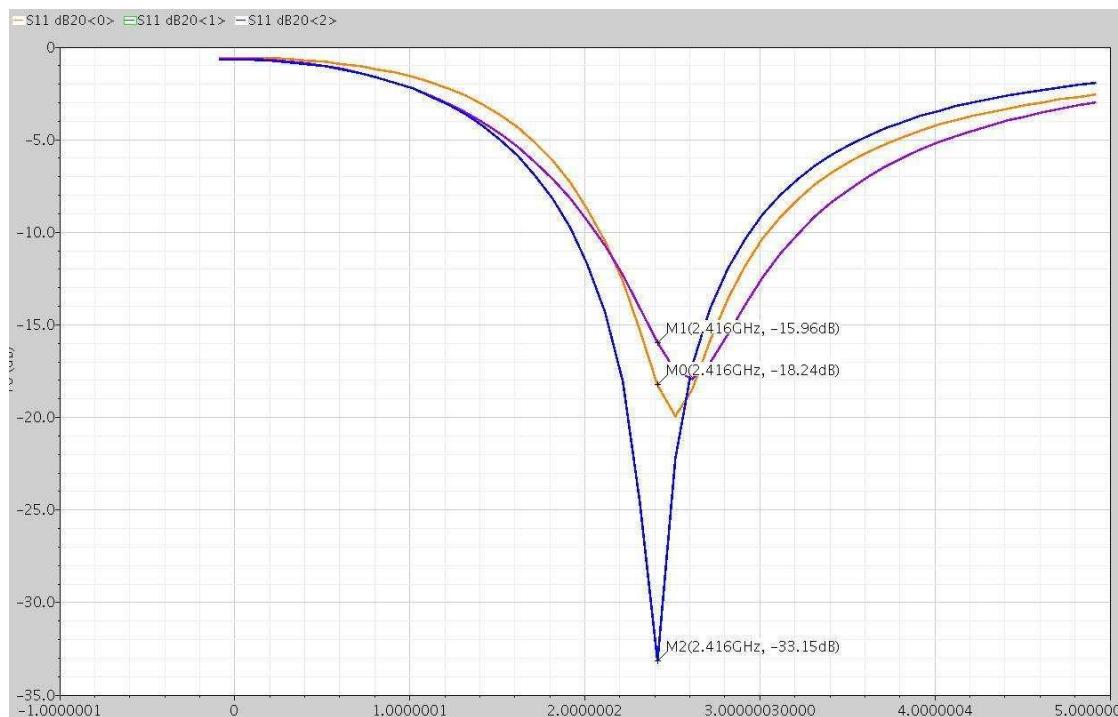

一般常用的低雜訊放大器架構通常為共源極(CSLNA)或共閘極(CGLNA)兩種組態，儘管在 2.4GHz 的操作頻段上 CSLNA 組態比 CGLNA 組態更有著較好的雜訊能力，但是在一般窄頻需要做到  $50\Omega$  的阻抗匹配在 CS LNA 組態中需要用到兩顆面積很大的電感  $L_s$  與  $L_g$ ，如圖 4-2(A)所示，對於晶片系統上是個非常大的負擔。從另一觀點在本系統中的射頻前端電路輸入的阻抗匹配必須涵蓋到壓控振盪器的自振頻率範圍，已確保系統在頻率追蹤模式中頻訊號有足夠的迴路增益。

圖 4-2 (A)電感退化組態的共源極低雜訊放大器 (B)共閘極低雜訊放大器

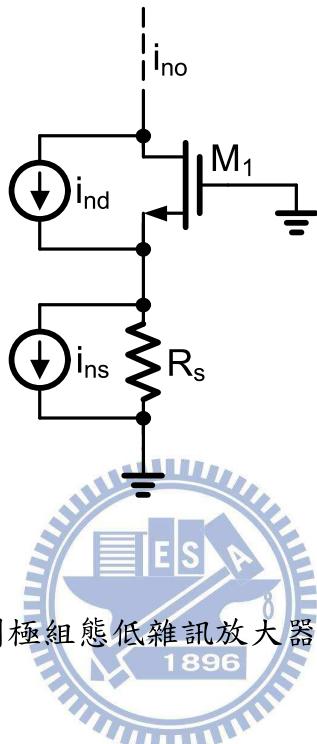

然而 CGLNA 是使用並聯共振網路  $L_s$  與  $C_{PAD}$  組成，使輸入阻抗( $1/gm$ )為  $50\Omega$ ，如圖 4-2(B)所示。因此共閘極組態 LNA 較適用於寬頻的架構，當輸入阻抗  $R_s$  等於  $1/gm$ ，則會得到最好的雜訊係數(noise figure)，如圖 4-3 所示，主要雜訊來源為  $i_{nd}$  與  $i_{ns}$  其結果為  $F$

$$F_{CGLNA} = 1 + \frac{\overline{i_{nd}^2} \left( \frac{1}{1 + g_m R_s} \right)^2}{\overline{i_{ns}^2} \left( \frac{g_m R_s}{1 + g_m R_s} \right)^2} = 1 + \frac{\gamma g_{d0}}{g_m^2 R_s} = 1 + \frac{\gamma}{\alpha} \Big|_{g_m R_s = 1} \quad (4-1)$$

圖 4-3 共閘極組態低雜訊放大器之雜訊貢獻

如圖 4-1 所示，具有提高轉導增益的共閘極的低雜訊放大器( $G_m$ -Boosted CG-LNA)，其目的在於利用提高轉導增益，抑制雜訊係數(Noise Figure)其雜訊係數為：

$$F_{CGLNA, gm\text{-boosted}} = 1 + \frac{\gamma}{\alpha} \frac{1}{(1 + A)} = 1 + \frac{\gamma}{\alpha} \frac{1}{1 + \frac{C_c}{(C_c + C_{gs})}} = 1 + \frac{\gamma}{\alpha} \left( \frac{C_{gs} + C_c}{C_{gs} + 2C_c} \right) \quad (4-2)$$

$A$  表示為迴授路徑的增益，當  $C_c \gg C_{gs}$  時  $A \approx 1$  則雜訊因數為

$$F_{CGLNA, gm\text{-boosted}} = 1 + \frac{\gamma}{2\alpha} \quad (4-3)$$

因此加入轉導增益的共閘極放大器，可在不消耗電流的情況下使雜訊因數下降。

圖 4-4 功率增益 (Power Gain)

圖 4-5 雜訊因數 (Noise Figure)

圖 4-6 輸入反射參數 (S11 Return Loss)

| Case | Power Gain | Noise Figure | Power Consumption |

|------|------------|--------------|-------------------|

| TT   | 16.63dB    | 3.33dB       | 5.66mW            |

| SS   | 16.57dB    | 3.75dB       | 2.98mW            |

| FF   | 16.63dB    | 3.67dB       | 8.17mW            |

表 4-1 低雜訊放大器模擬結果

| Parameter        | Value  |

|------------------|--------|

| S11 (@2GHz~3GHz) | <-10dB |

表 4-2 低雜訊放大器模擬結果

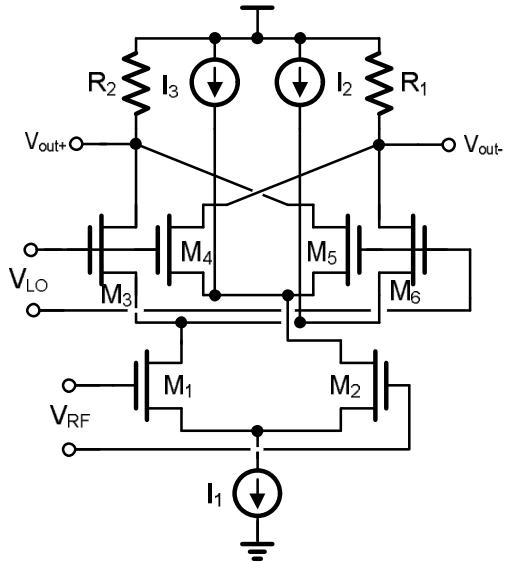

## 4.2 吉伯特雙旁帶混波器 (Double-balanced Gilbert-Type mixer)

由於互補式金屬氧化層半導體本身就是很高的閃爍雜訊(Flicker Noise)來源，又因電路設計的考量或是節省面積降低成本，會將電晶體的長度與寬度調的很小，這都是會照成閃爍雜訊上升的原因，為了增加訊號對雜訊的比例(Signal to Noise Ratio, SNR)與降低雜訊係數，必須降低閃爍雜訊。如圖 4-7 所示為加入流入的靜態電流機制(static current bleeding technique)的混波器完整電路[7]，利用  $M_3-M_6$  為本地振盪開關對(LO Switches)，在此所貢獻的輸出雜訊的端閃爍雜訊電流如下式(4-4)(4-5)所示，

$$i_{o,n} = \frac{(4I \times V_n)}{S \times T} \quad (4-4)$$

S 為本地振盪訊號的斜率

T 為本地振盪的週期

$V_n$  為  $M_3-M_6$  開關對的閃爍雜訊

$$V_n = \sqrt{2 \times \frac{K_f}{W_{eff} L_{eff} C_{ox} f}} \quad (4-5)$$

$K_f$  為製程參數

$f$  為頻率

$C_{ox}$  為氧化層電容

$W_{eff}, L_{eff}$  為有效的長、寬尺寸

透過式(4-4)(4-5)可得知為了減少輸出閃爍電流，可將流經本地振盪開關對的電流變小，與增加該開關對的有效長度( $L_{eff}$ )與寬度( $W_{eff}$ )的值，但由於將電晶體的尺寸增加，會導致混波器面積變大，若將射頻轉導的電流( $I_1$ )調小會影響到電路的輸出增益，為了要兼顧到較高的增益與節省面積，因此加入  $I_3$  與  $I_2$ ，減少本地振盪開關上所流過的偏壓電流，且不影響到射頻

轉導的電流大小，則輸出的閃爍雜訊也應此而降低。

圖 4-7 加入的靜態電流機制吉伯特雙旁帶混波器

| Case | Conversion Gain | Power Consumption |

|------|-----------------|-------------------|

| TT   | 6.67dB          | 3.57mW            |

| SS   | 5.08dB          | 3.51mW            |

| FF   | 7.47dB          | 3.63mW            |

表 4-3 吉伯特混波器模擬結果(1)

| Case | IIP3     | Noise Figure |

|------|----------|--------------|

| TT   | -1.54dB  | 17.45dB      |

| SS   | -1.635dB | 18.38dB      |

| FF   | -0.587dB | 16.61dB      |

表 4-4 吉伯特混波器模擬結果(2)

圖 4-8 輸入三階截止點(IIP3)

圖 4-9 雜訊因數(Noise Figure)

### 4.3 後級放大器之設計 (Post Amplifier)

在無線通訊傳輸路徑上的訊號強度，取決於發射機的輸出能量與訊號在傳輸路徑上的衰減，後級放大器的主要功能是在於回復信號之動態位準，以供解調器進行訊號解調。

本電路採用多級串接的方式來提高整體增益，每一級子電路將選用 Cherry-Hooper 架構來達到低功率高頻寬的需求，並且在輸出端加上消除直流偏移機制 (Offset cancellation)，其目的在於防止訊號經多級放大器後；造成輸出端的直流準位飄移，導致信號飽和與失真。其後級放大器包含兩個部分，第一是在於限制振幅(Limiting)[8]，將訊號放大或限制於系統電壓的準位，以供後級的數位電路能正常的使用，第二個功能是接收訊號強度指示(Received Signal Strength Indicator, RSSI)[9]，產生對應的訊號值，提供系統端能夠依據接收到的訊號品質，動態調整射頻前端電路的增益。圖 4-10 為後級放大器之示意圖。

後級放大器的架構圖，由輸入端(LA\_In+/ LA\_In-)輸入訊號經由各級子放大器(Sub-Cell)逐級放大，在輸出端(LA\_Out+/ LA\_Out-)會得到一組近似於全幅訊號(rail to rail)，其中在輸出端  $R_1, R_2, C_1, C_2$  與  $A_3$  所組成的主動式並並迴授機制(Active shunt-shunt feedback)，其目的在於防止各級放大器在製程上不匹配的因數，而造成輸出端的直流準位飄移，導致最後級輸出端的狀態錯誤，此外在各級放大器的輸出端接上一組全波整流器(Full-Wave Rectifiers, FWR)，可偵測出各級的輸出訊號品質，以下我們針對這兩部份分別說明其工作原理與內部的詳細電路。

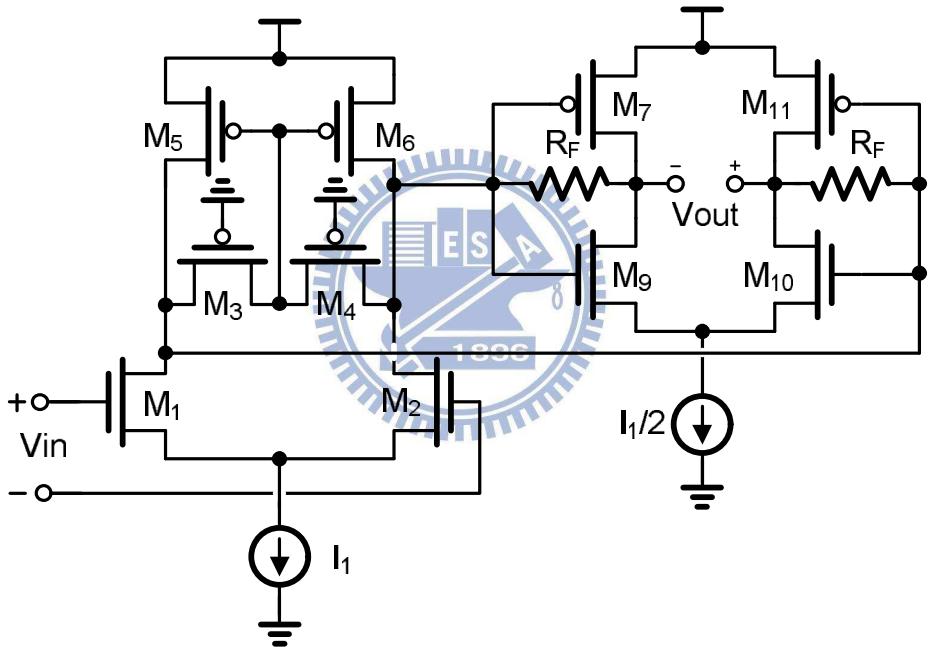

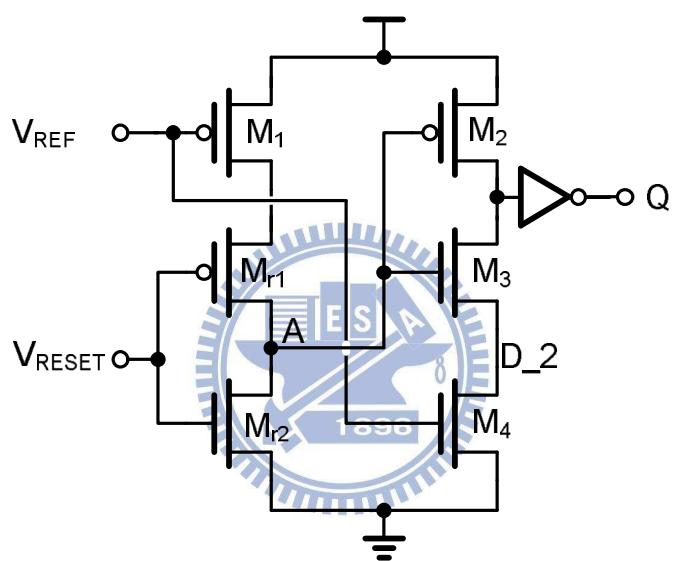

在架構圖中  $A_1$  與  $A_2$  其主要架構相同，差異在於  $A_1$  的輸入端多並連一組差動輸入對，以接收輸出端所迴授的資訊，如圖 4-11 所示為  $A_2$  單級的詳細電路，推導出下式，

$$\frac{V_{out}}{V_{in}} = \frac{A_{vo}\omega_n^2}{s^2 + 2\xi\omega_n^2 + \omega_n^2} \quad (4-6)$$

$$\frac{V_{Out(S)}}{V_{In(S)}} = \frac{\frac{g_{m1} \left[ (g_{m9} + g_{m7}) - \left( \frac{1}{R_F} + SC_{gd} \right) \right]}{(C_{gd} + C_Y)(C_{gd} + C_X) + C_{gd}^2}}{s^2 + s \left[ \frac{\frac{1}{R_F} (C_X + C_Y) + \frac{1}{R_O} (C_{gd} + C_Y) + (g_{m9} + g_{m7}) C_{gd}}{(C_{gd} + C_Y)(C_{gd} + C_X) + C_{gd}^2} \right] + \frac{\frac{1}{R_F} (g_{m9} + g_{m7} + \frac{1}{R_O})}{(C_{gd} + C_Y)(C_{gd} + C_X) + C_{gd}^2}}$$

$$A_{vo} = \left| \frac{V_{out}}{V_{in}} \right| = \frac{g_{m1} [(g_{m9} + g_{m7})R_F - 1]}{\frac{1}{R_o} + (g_{m9} + g_{m7})} \quad (4-8)$$

$$\omega_n^2 = \frac{\frac{1}{R_F} \left( g_{m9} + g_{m7} + \frac{1}{R_o} \right)}{\left( (C_{gd} + C_Y)(C_{gd} + C_X) + C_{gd}^2 \right)} \quad (4-9)$$

$$\xi^2 = \frac{\frac{1}{R_F} (C_X + C_Y) + \frac{1}{R_o} (C_{gd} + C_Y) + (g_{m9} + g_{m7}) C_{gd}}{2 \times \sqrt{\left[ (C_{gd} + C_Y)(C_{gd} + C_X) + C_{gd}^2 \right] \times \left[ \frac{1}{R_F} \left( g_{m7} + g_{m9} + \frac{1}{R_o} \right) \right]}} \quad (4-10)$$

圖 4-11 A<sub>2</sub> 放大器電路圖

其中  $A_{vo}$  為低頻增益， $\zeta$  為阻尼因子 (damping factor)， $\omega_n$  為自然頻率 (natural frequency)。兩階之轉導函數可得當  $\zeta$  為 0.707 時有最平坦 (maximally-flat) 之頻率響應  $\omega_n = \omega_{-3dB}$ 。此電路工作於中頻訊號，操作速度不快，故可將電路的功率消耗降至最低，在圖 4-11 中 M<sub>3</sub> 與 M<sub>4</sub> 在傳統架構中是利用電阻實現，但為縮小面積 M<sub>3</sub> 與 M<sub>4</sub> 使用 PMOS 實現，將其

操作於三極體區，使特性等效於一電阻的形式，也可穩定該級之輸出直流電壓位準，不會隨著製程變化而飄移。利用  $M_7$  與  $M_9$  形成轉阻放大器，在此放大級中可得到兩倍的  $g_m$  值，故可以節省一半的電源消耗。

圖 4-12 (A) 輸入訊號與各級的輸出結果 (B)輸出波形之眼圖

如圖 4-12(A)所示，輸入 QPSK 調變訊號，設定訊號品質 SNR 為 5dB，測試後級放大器的輸出波形，可看到 Stage 6 的輸出波形已將訊號放大至近似於全幅訊號(rail to rail)，經由一級反向器(inverter)將訊號推成 0V-V<sub>DD</sub>之位準，由圖 4-12(B)所示，我們將輸出波形成疊眼圖觀察電路的特性，可看到每級電路都有將訊號拉開，在眼圖的中央約 200ns 出現不規則波形，此為輸入相位調變訊號資料轉態的位置。

另一個功能為接收訊號強度指示(Received Signal Strength Indicator, RSSI)，利用全波整流器(Full Wave Rectification)接於第一級至第四級子放大器的輸出端，因第五級與第六級輸出端接近於大訊號操作，不易偵測出正確的訊號強度，故只接前四級。接收訊號強度指示器詳細電路如圖 4-13 所示，先將 M<sub>3</sub> 與 M<sub>8</sub> 偏壓於固定的工作電流，利用 M<sub>1</sub> 與 M<sub>2</sub> 將輸入電壓訊號轉換為電流訊號，將電流差值反應於 M<sub>4</sub> 與 M<sub>7</sub> 上且映射於 M<sub>5</sub> 與 M<sub>6</sub> 上作電流加總，透過電容電阻組成的低通率波器，可將偵測到的訊號反應於輸出電壓上。

圖 4-13 為接收訊號強度指示(RSSI)之電路圖

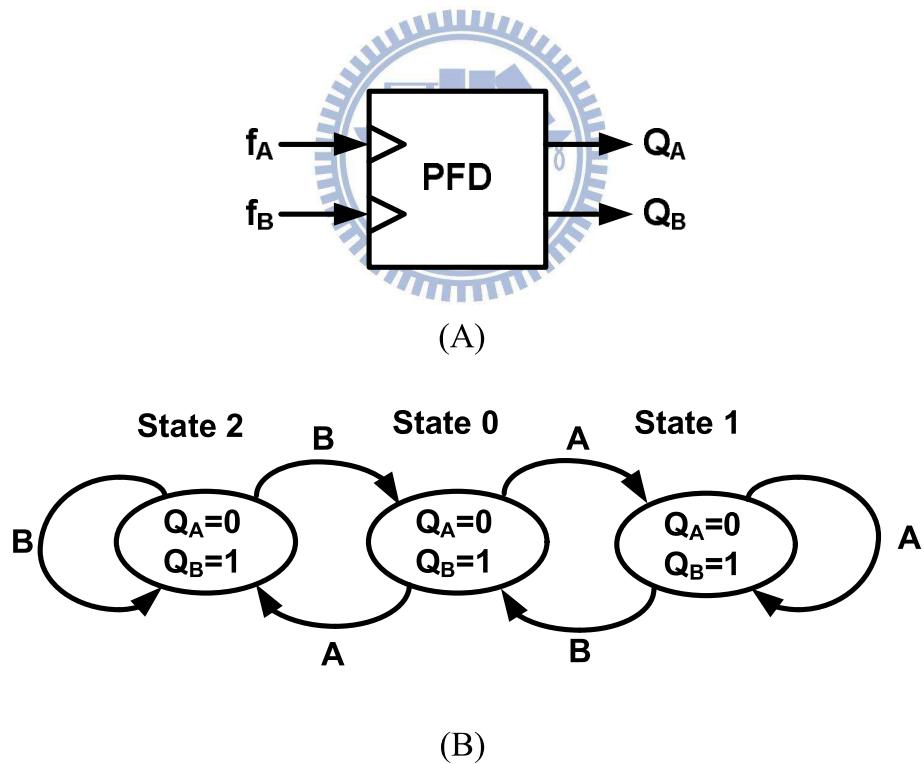

如圖 4-14 所示，在不同強度的輸入訊號下接收訊號強度指示器所偵測出的訊號強度結果。如表 4-5 所示，為後級放大器的模擬結果。

圖 4-14 接收訊號強度指示輸入與輸出的關係

| Parameter         | Value |

|-------------------|-------|

| Sensitivity       | -71dB |

| Gain              | 71dB  |

| Bandwidth         | 87MHz |

| Power Consumption | 0.6mW |

表 4-5 後級放大器規格表

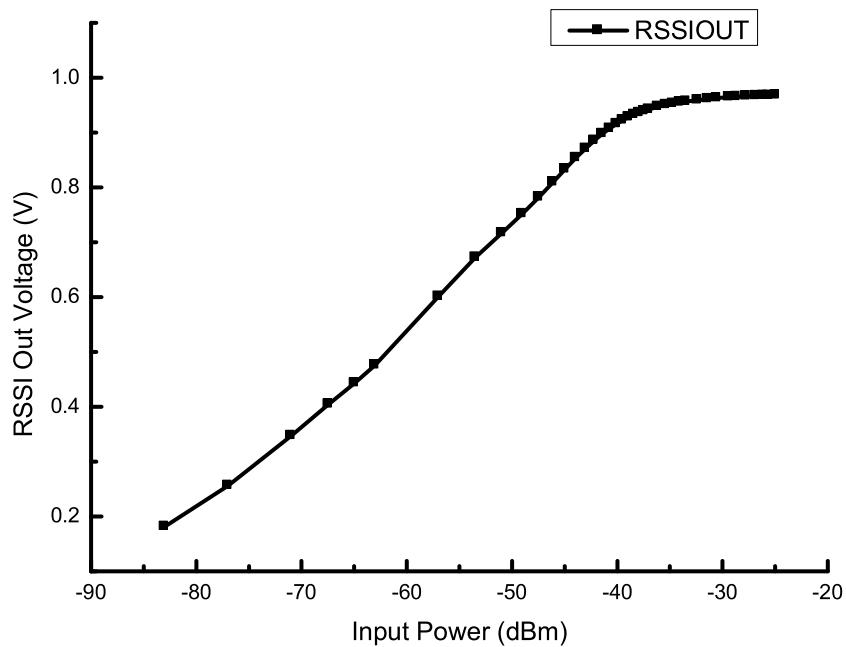

#### 4.4 相位頻率偵測器之設計(Phase and Frequency Detector)

相位頻率偵測器能夠偵測輸入端參考頻率和除頻頻率兩個訊號間的頻率和相位差，我所使用的相位頻率偵測器為傳統的三態相位頻率偵測器(Tri-state PFD)，其操作原理由圖 4-15 可知，當 A 輸入端的頻率比 B 端的頻率大的話，則  $Q_A$  端會拉起高電壓的訊號，但  $Q_B$  端則會保持在低電壓的位準，反之，若 B 輸入端的頻率若比 A 端的輸入頻率大的話，則  $Q_B$  端會拉起高電壓的訊號，但  $Q_A$  端則會保持在低電壓的位準，第三種情況是，當 A 端和 B 端兩邊的輸入頻率都一樣的話，此時會檢查 A、B 兩端的相位差是多少，如果有相位差的話，則  $Q_A$  或  $Q_B$  端會送出一個和相位差同寬度的訊號(是由  $Q_A$  或  $Q_B$  端送出則取決於到底是 A 領先 B，還是 A 落後 B)。

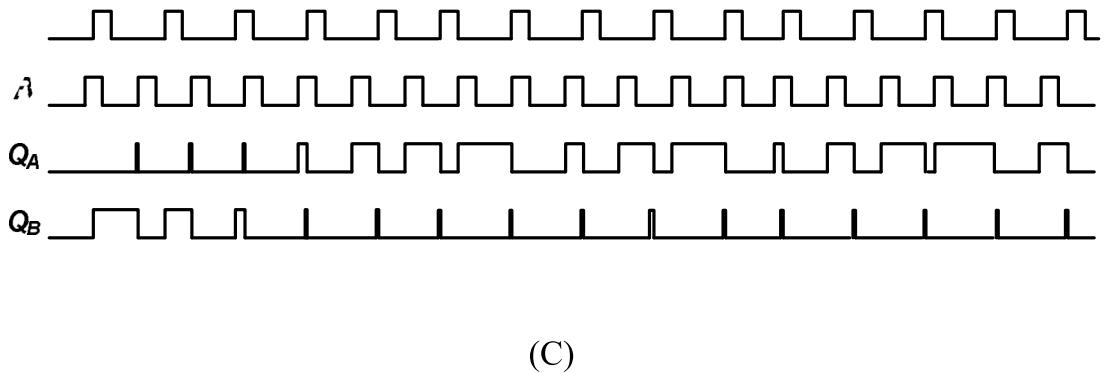

(C)

圖 4-15 (A) 相位頻率檢測器 (B) 相位和頻率檢測器的狀態圖(C) 相位和頻率檢測器的時序圖

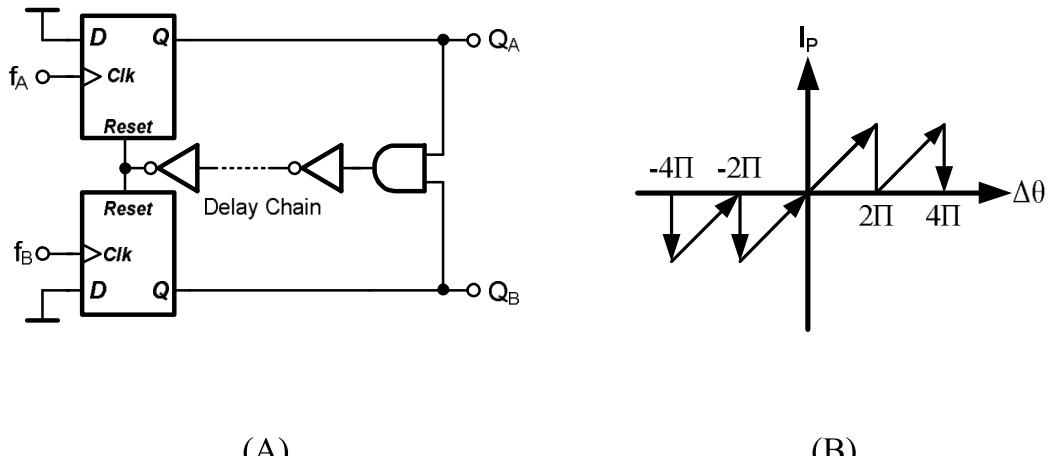

如圖 4-16(A)所示，為我們相位頻率偵測器的電路架構，其中包含了兩個具有可重置功能的 D 型正反器，還有一個 NAND 閘以及延遲串(Delay Chain)， $f_A$  和  $f_B$  兩輸入端各分別當作此兩個正反器的時脈，此兩個正反器的 D 輸入接至高電位，接下來分析相位頻率偵測器的運作過程，首先假設  $Q_A$  和  $Q_B$  一開始皆為零，若輸入端  $f_A$  變為 1，則  $Q_A$  會被設定為 1 而  $Q_B$  則維持 0，在回授路徑上經過一個 NAND 閘與奇數個反向器後，送 0 進入重設端，所以不會重設 D 型正反器。直到輸入端  $f_B$  也變為 1，此時  $Q_B$  變為 1，由於  $Q_A$  和  $Q_B$  都為 1，所以重設 D 型正反器，在經過延遲串的時間延遲後， $Q_A$  和  $Q_B$  會一起被重設為 0，回到初始的狀態。反之若輸入  $f_B$  先變為 1，則輸出  $Q_B$  會先變為 1 直到輸入端  $f_A$  也變為 1， $Q_A$  和  $Q_B$  才會一起被重設為 0。此種三態相位頻率偵測器的特徵圖如圖 4-16(B)所示。

相位頻率偵測器中的 D 型正反器電路架構如圖 4-17 所示，為單一相位 (True Single Phase Circuit) 的架構，此種架構的優點是電路簡單，且切換速度快，因此能夠增加線性度。

圖 4-16 (A)相位和頻率檢測器的內部電路，(B)相位和頻率檢測器的特徵圖

圖 4-17 相位頻率偵測器中的 D 型正反器

在相位頻率偵測器的設計中，死區(Dead Zone)是一個重要的非理想效應，所謂死區就是當輸入端  $f_A$  和輸入端  $f_B$  的相位差距小到一定的程度時，相位頻率偵測器的輸出無法具有足夠的時間來開啟充電汞，因此輸出的電流就無法與相位差有線性對映，如此會造成嚴重的參考突波(Reference Spur)。解決的方式就是在重設的回授路徑上加入延遲串，如此可以增加相位比較的結果顯現在輸出端的時間，而能讓充電汞有時間對此輸出結果做出反應，因此可以減少死區的效應。

## 4.5 充電汞與迴路率波器之設計(Charge Pump & Loop Filter)

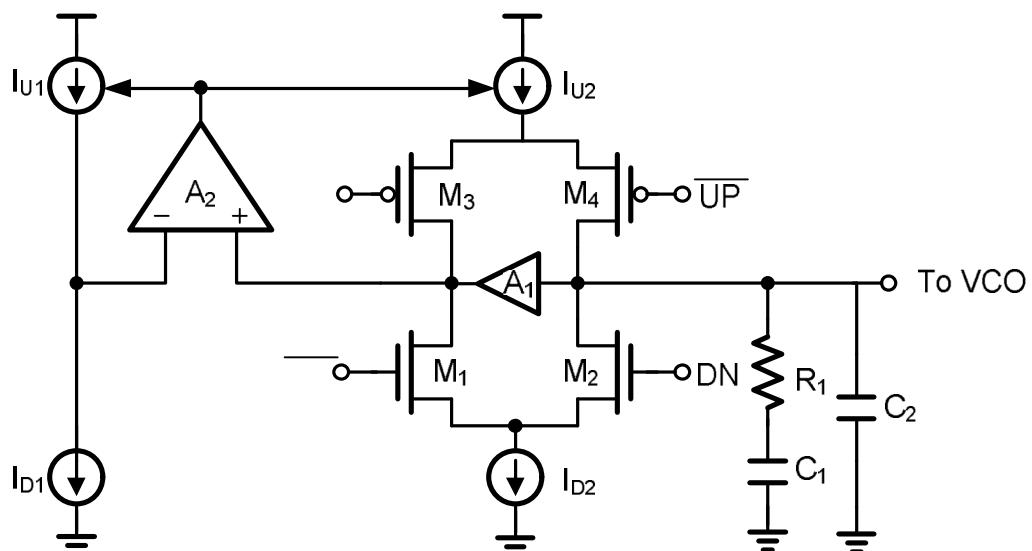

充電汞的功能是對迴路濾波器做充電或放電的動作，當相位頻率偵測器傳來充電訊號時，充電汞就要對迴路濾波器充電以增加壓控振盪器的控制電壓，反之則是放電以減小控制電壓。充電汞的電路設計最主要的重點在於如何增加充電電流與放電電流的匹配度。

充電泵之核心電路如圖 4-18 所示[10]，基本上由電流源  $I_{U2}$  和  $I_{D2}$  所組成。隨著迴路濾波器上的電壓在  $V_{DD}$  與 GND 之間擺動，充放電電流將會因為通道長度調變效應(channel length modulation effect)造成充放電電流不匹配現象。這將會造成在鎖定狀況時，充放電電流不一致而產生參考頻率突波上升。為了解決這問題，我們採用由  $A_2$ ,  $I_{U1}$  和  $I_{D1}$  組成之穩定電流迴授電路(regulated current feedback loop)。其中， $I_{U1}$  和  $I_{D1}$  為  $I_{U2}$  和  $I_{D2}$  之複製電路，而且充電電流可以藉著調整電流源之偏壓，即改變電流大小而互相追蹤。

進一步地，當 UP 和 DN 皆不動作時，單增益緩衝器(unity gain buffer)將被用來追蹤電流源輸出電壓與迴路濾波器上之電壓小，降低在充電泵歸零時之電荷分享(charge sharing)效應。

圖 4-18 充電汞電路架構

圖 4-19 充電汞充/放電的模擬結果

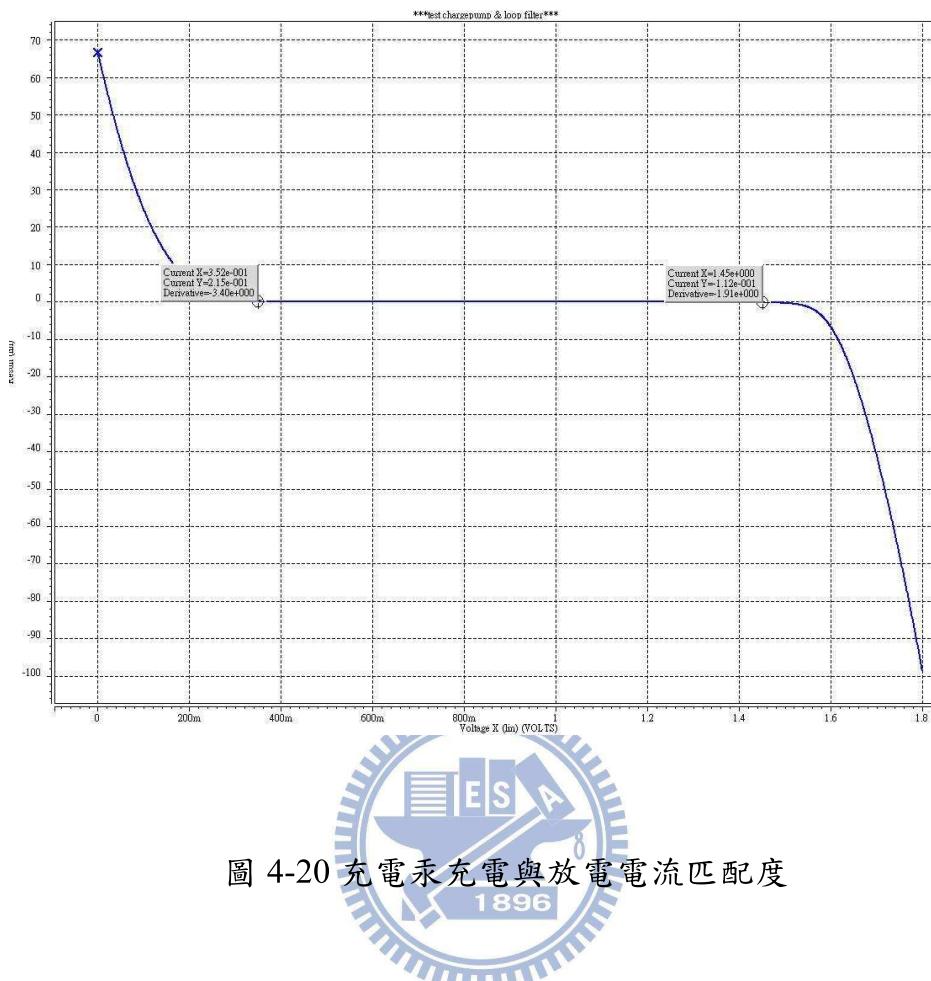

圖 4-20 充電汞充電與放電電流匹配度

圖4-20所示為在控制電壓的操作範圍內，上下電流源的匹配程度，可以知道在控制電壓變化從0.35v到1.45v之間，上下電流源的不匹配度可以壓制到百分之三以下。

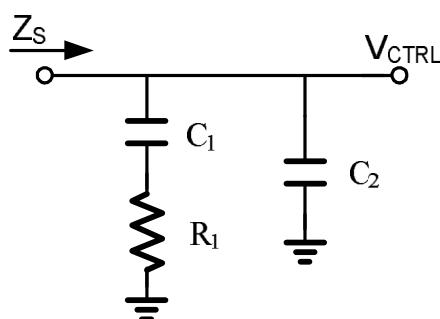

圖 4-21 二階迴路濾波器

低通率波器之設計，如圖 4-21 所示，為二接階迴路濾波器的架構圖 [11]，其輸入是充電汞的電流，輸出是控制電壓。濾波器的轉阻  $T(s)$ ，如下式所示：

$$T(s) = \frac{1+sC_1R_1}{s^2C_1C_2R_2 + s(C_1 + C_2)} \quad (4-11)$$

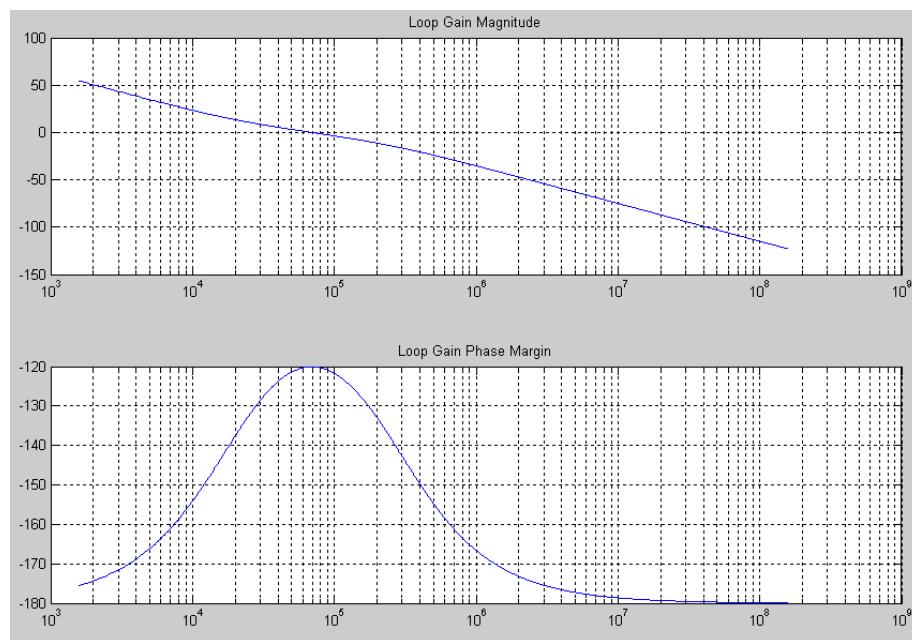

依據壓控振盪器與充電汞的條件，利用 Matlab 來檢證開迴路轉移函數所計算出的數值是否符合原先設定系統規劃的特性，如圖 4-22 所示，即為開迴路轉移函數波德圖。從圖中我們可以知道單位增益頻率如我們所設計的為 80KHz 與 60 度的相位邊限。

圖 4-22 開迴路轉移函數波德圖

## 4.6 壓控振盪器 (Voltage-Controller Oscillator)

壓控振盪器的功能是產生本地振盪還原器的輸出頻率，且其輸出頻率可以由控制電壓去做調整。壓控振盪器的設計中有兩個最主要的設計考量，一個是相位雜訊，另一個是功率損耗。

圖 4-23 互補式偶合壓控振盪器電路架構

圖 4-23 所示，是我們所使用的壓控振盪器架構，為一個 PMOS 與 NMOS 互補耦合式電感電容壓控振盪器(Complementary Cross Couple LC VCO)。使用電感電容壓控振盪器的原因是其所造成的相位雜訊較環型振盪器低。而電感電容振盪器又有分幾種架構，而選擇互補耦合式壓控振盪器的原因在於在相同的功率損耗下，互補耦合式壓控振盪器同時有上面的 PMOS 對與下面的 NMOS 對提供負阻抗，因此其負阻抗為只有單獨 NMOS 對架構的兩倍，換言之，在提供相同負阻抗的前提下，互補式耦合壓控振盪器會比較省功率。利用  $C_1, C_2, C_3$  電容與串接開關來決定要不要讓共振腔看到電容負載，以作切換頻帶的動作，而設計不同的電容值  $C_1, C_2$  與  $C_3$  可

以讓三位元的開關產生出八條頻帶，避免製程漂移照成壓控振盪器的輸出頻率無法包含我們所需要的範圍。另外為了降低相位雜訊，電流源(I)選擇由 PMOS 提供而非由 NMOS 提供，原因是 PMOS 的閃爍雜訊較 NMOS 低，因此產生較少的相位雜訊[12][13][14]。另外我們會在電流源端側通電容  $C_p$  (bypass capacitor)，加入這個電容的目的在於將雜訊側通到地，以避免雜訊偶合到電流源的閘級偏壓端，再藉由其電晶體轉導成雜訊電流，混波到我們的頻帶。另外為了減少電流源電晶體的閃爍雜訊，我們會盡量增加其尺寸，而增加尺寸的結果導致其電晶體會操作在三極管區，因此電流源的閘級電壓的穩定性就會非常的重要。

考慮壓控振盪器的相位雜訊與電感的關係[15]，由式子(4-12)可得知

$$L\{\Delta\omega\} = 10 \cdot \log \left[ \frac{1}{2} \cdot \frac{KT}{V_{\max}^2} \cdot \frac{1}{R_p (C\omega_{\text{osc}})^2} \cdot \left( \frac{\omega_{\text{osc}}}{\Delta\omega} \right)^2 \right] \quad (4-12)$$

Where  $R_p = Q \cdot L \cdot \omega_{\text{osc}}$

$Q$  為電感品質因數

$C$  為共振腔內的電容

$V_{\max}$  為最大的輸出電壓擺幅

電感的品質因數決定了壓控振盪器產生出的相位雜訊，進而影響整個系統的效能，我們由式子(4-13)可算出我們所需的電容值與電感值的比例，由製程廠商所提供的 PDK 文件，選取適當的電感與電容，並針對此電感模型掃出頻率對品質因數的關係，如圖 4-24 所示，在我們所需的頻率下的品質因數約為 9.4，由圖 4-25 可得壓控振盪器相位雜訊的模擬結果，在 1MHz 時的相位雜訊為-120dBc/Hz。

$$f_{\text{osc}} = \frac{1}{2\pi\sqrt{LC}} \quad (4-13)$$

圖 4-24 電感品質因數對頻率的關係

圖 4-25 壓控振盪器的相位雜訊模擬結果

圖 4-26 各製程飄移下壓控振盪器的輸出波形

圖 4-27 壓控振盪器的頻率涵蓋範圍

如圖 4-26 所示，壓控振盪器在各製程飄移下的輸出波形，輸出擺幅  $V_{P-P}$  均大於 1.4V，如圖 4-27 所示，為壓控振盪器能涵蓋的頻率範圍，防止 製程飄移使壓控振盪器無法工作於我們所設定的頻率值。

| Case | Power  | $f_{min}$ | $f_{max}$ |

|------|--------|-----------|-----------|

| TT   | 3.16mW | 2.16GHz   | 2.63GHz   |

| SS   | 2.87mW | 2.00GHz   | 2.46GHz   |

| FF   | 3.44mW | 2.37GHz   | 2.84GHz   |

表 4-6 在各製程變化下的模擬結果

## 4.7 除頻器之設計 (Divider)

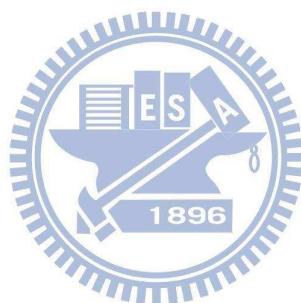

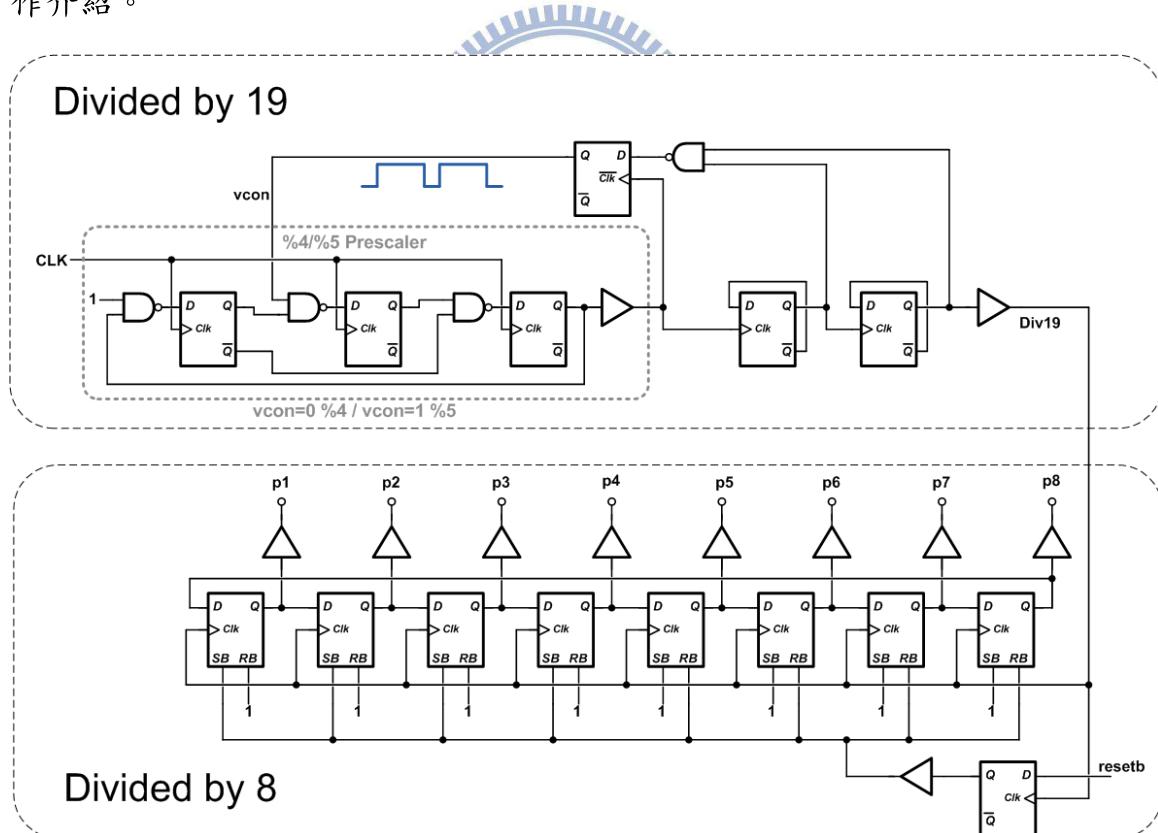

如圖 4-28 所示，為除頻器的架構，主要由一除 19 除頻器與一除 8 除頻器所組成。其中除 19 除頻器由除 4 除 5 預除器與兩級除 2 除頻器以及一除數控制電路所組成；而除 8 除頻器則是由 8 級移位器(Shift Register)所構成，在初始時先將其中 4 個暫存器存入 1，另外 4 個擇存入 0，則此 8 個暫存器輸出則為 8 個相位，並且除 8 的輸出。由於壓控振盪器的輸出為差動信號，為了使壓控振盪器兩端看到接近的電容量，因此電路中加入了一組 Dummy 電路，模擬除 19 除頻器的輸入端的寄生電容。壓控振盪器的一端連接此 Dummy 電路，另一端則連接到除 19 除頻器的輸入端，使壓控振盪器兩端電容量能接近。以下則分別針對除 19 除頻器以及除 8 除頻器作介紹。

圖 4-28 除頻器電路架構圖

圖 4-29 除 19 除頻器電路架構圖

如圖 4-29 所示，為除 19 除頻器由除 4 除 5 預除器與兩級除 2 除頻器以及一除數控制電路所組成。其中除 4 除 5 預除器其除數由三個 D 型正反器組成同步計數器的型式，並由一控制信號 vcon 控制其除數。當 vcon 為高電位時，除數為 5，當 vcon 為低電位時，除數為 4。由於輸入的信號頻率很高，因此這裡所使用的 D 型正反器採用 TSPC 的架構，並將邏輯閘 NAND 內嵌於其中，其電路圖如圖 4-30 所示。

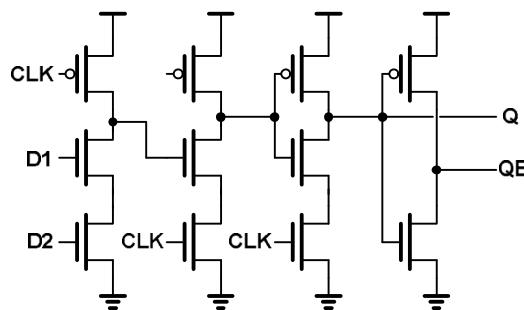

圖 4-30 內嵌 NAND 閘的 TSPC

透過一除數控制器，並搭配兩級的除 2 電路，使得每四個除 4 除 5 預除器之輸出週期中，有 3 個週期控制信號 vcon 為高電位，1 個週期中 vcon

為低電位，因此構成除數大小為  $5 \times 3 + 4 \times 1 = 19$ ，得到所需要的除頻數大小。

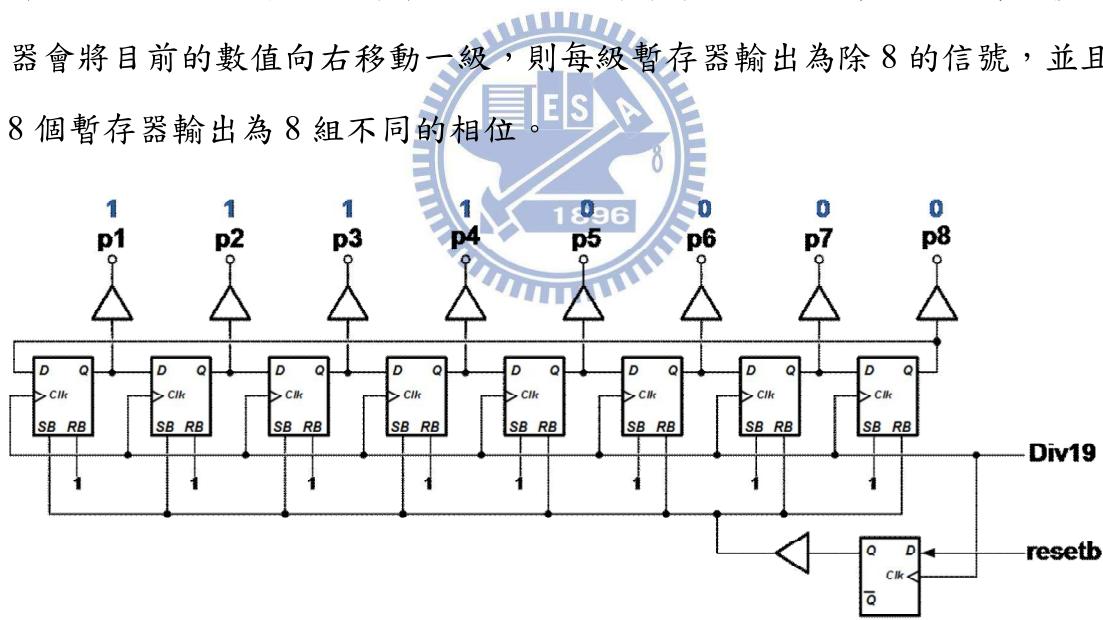

在前述 3.1 節提到，資料解調器必須使用八組相位均勻的輸入訊號，定位資料的相位基準點，但由於除 19 電路是利用三組除五週期與一組除四組週期所組成的，所產生的正負半週期不會為 50%，故我們除 8 除頻器是使用移位暫存器的架構。

除 8 除頻器主要的目的是要將除 19 除頻器的輸出結果再除 8，並且產生 8 組相位輸出。其電路架構如下圖所示，在此採用了 8 個暫存器組成移位器如圖 4-31 所示，並且在 **resetb** 信號為低電位時，先將其中四個站存器存入高電位，另外四個則存入低電位，則當每次 **Div19** 為高電位時，移位器會將目前的數值向右移動一級，則每級暫存器輸出為除 8 的信號，並且 8 個暫存器輸出為 8 組不同的相位。

圖 4-31 除 8 除頻器電路架構圖

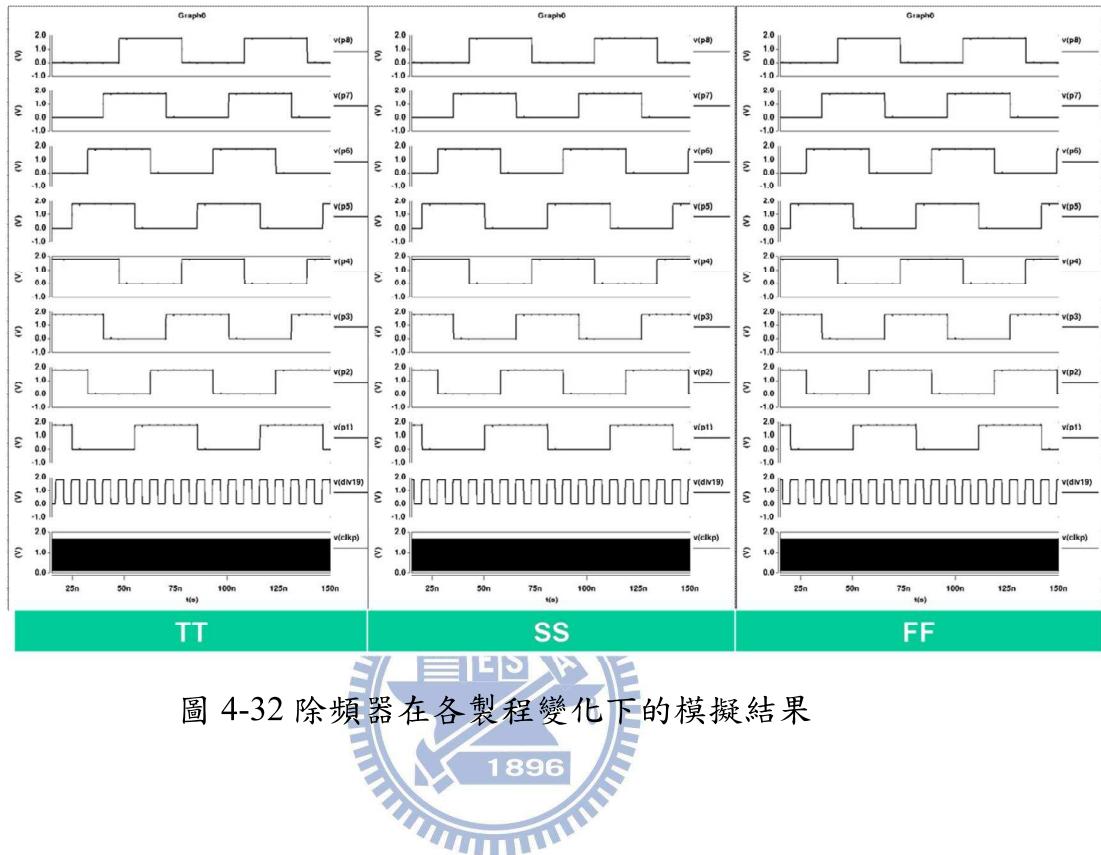

由圖 4-32 所示，由模擬結果可得知除頻器在各製程變化的情況下，都可產生八組各相差  $45^\circ$  的輸出波形。如表 4-7 所示，為除頻器在各製程變化下模擬出的功率消耗。

圖 4-32 除頻器在各製程變化下的模擬結果

| case | Power  |

|------|--------|

| TT   | 3.16mW |

| SS   | 2.87mW |

| FF   | 3.44mW |

表 4-7 除頻器在各製程變化功率消耗

## 4.8 頻率檢知器之設計 (Frequency Discriminator)

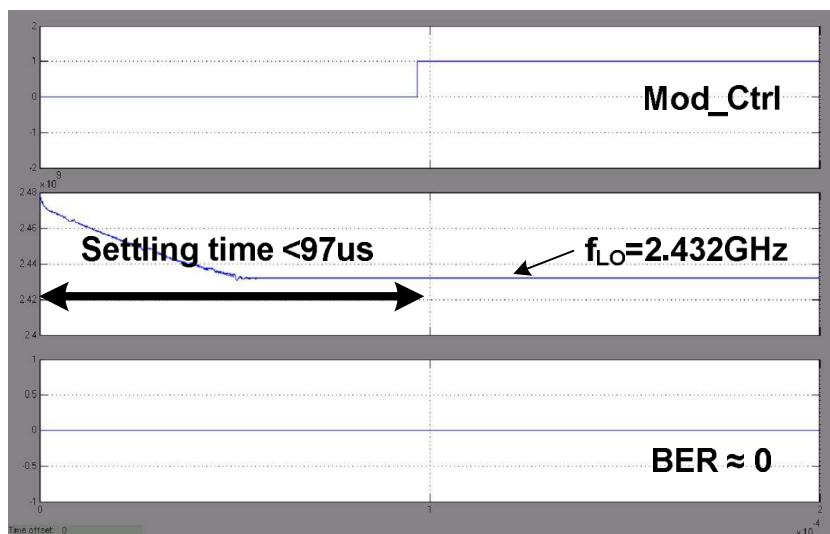

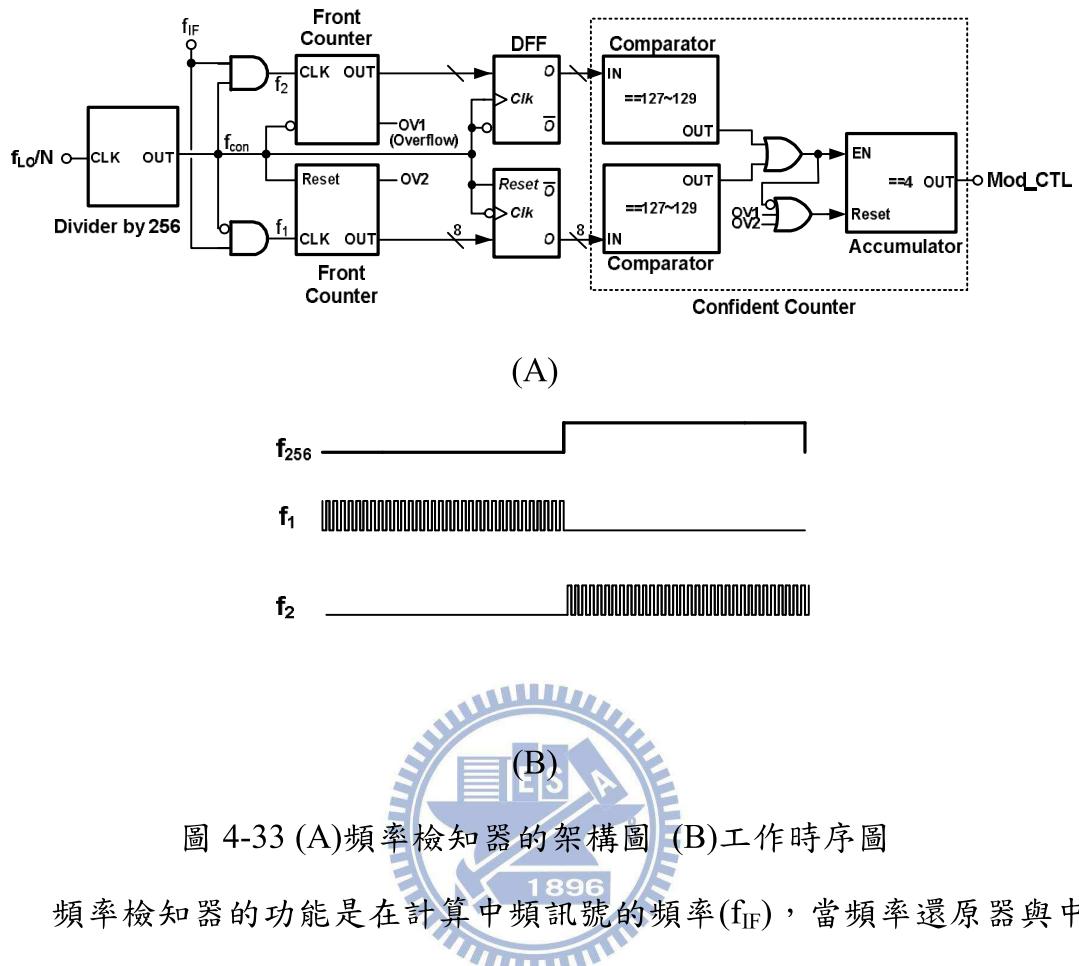

圖 4-33 (A) 頻率檢知器的架構圖 (B) 工作時序圖

頻率檢知器的功能是在計算中頻訊號的頻率( $f_{IF}$ )，當頻率還原器與中頻訊號鎖定時會送出 Mod\_CTL 的控制訊號，切換系統至相位頻率追蹤及資料解調模式。如圖 4-33(A)所示，其主要是由三組 8 個位元的計數器與數個比較器所構成，利用由壓控振盪器所除頻出的  $\Phi_0$  做為基準訊號，再利用 8 位元的控制計數器 (Control Counter) 對  $\Phi_0$  除 256，產生控制訊號  $f_{256}$ ，利用  $f_{256}$  控制前級計數器的狀態，經由前述的系統模擬可得知，當系統穩定時頻率誤差須小餘正/負 125 KHz，因此  $f_{IF}$  必須在  $f_{256}$  的半週內產生 127~129 次的脈波如圖 4-33(B)所示，我們將此條件設定為鎖定區間 (Locking Window)，若後級計數器(Post Counter)偵測出前級計數器(Front Counter)計數的脈波數目，已連續四次命中鎖定區間，則後級計數器會送出邏輯 1 的訊號(Mod\_CTL)，令系統狀態切換至相位頻率追蹤及資料解調模式。

當系統穩態時，在 $f_{256}$ 的半週內中頻訊號會產生127~129次的脈波，並重複四個半週，有鑑於此，利用現有電路的架構，在前級計數器上加入溢位偵測OV1(OV2)，當八位元計數器計數至255時，OV1(OV2)則會輸出邏輯1的控制訊號，清除後級計數器目前的狀態，因此可讓頻率檢知器可偵測的範圍更寬廣，解決傳統的頻率偵測器有偵測範圍的限制。以下則針對8位元計數器作介紹。

圖 4-34 (A)D 型靜態互補式正反器 (B)具有溢位偵測的 8 位元非同步計數器

8 位元計數器，由於輸入為中頻訊號並不是高速，為了節省功率，所用到的 D 型正反器皆是用靜態互補式架構，其電路架構如圖 4-34(A)所示，SetB 為設定訊號，ResetB 為重置訊號，可由外部設定該 D 型正反器的狀態，當 SetB 與 ResetB 都為邏輯 1 時，則為兩級反相器作串接，即可保持輸出端的邏輯準位，並利用時脈去控制傳送閘開關（Transmission Gate），圖 4-34(B)所示，利用八組一位元的 D 型正反器串接而成的八位元非同步計數器，由各級的輸出端( $Q_0 \dots Q_7$ )可得到計數的狀態。

# 第五章

---

---

## 佈局與量測結果

---

---

### 5.1. 晶片佈局 (Chip Layout)

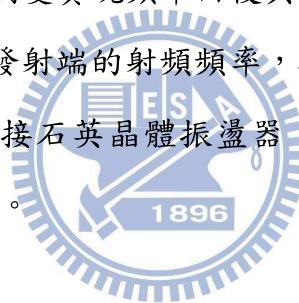

此晶片採用 TSMC 0.18- $\mu\text{m}$  CMOS 製程實現。圖 5-1 為晶片照相圖。晶片面積約  $1.8 \times 1.6 \text{ mm}^2$ 。共有 44pin，其各腳位定義如表 5-1 所示，此電路的主要功能，是以數位調變實現頻率回復與資料解調，其架構基於單一的頻率回復器，藉由追蹤發射端的射頻頻率，在接收端將射頻頻率還原與完成資料解調，而不需外接石英晶體振盪器，做為參考訊號源，適用於 QPSK，BPSK 等調變系統。

在電路佈局方面，因低雜訊放大器(LNA)，混波器(Mixer)與壓控振盪器(VCO)都為類比電路，所使用到的偏壓電源與輸入輸出腳位較多，且極易受干擾，另外考量到輸入輸出的差動訊號線必須要對稱的問題，因此將 LNA 與 Mixer 放置在本晶片左上方，則 VCO 需搭配低通濾波器(LF)，則將其放置於本晶片的下方，其餘的電路多半為數位電路或是工作於較低頻的類比電路，考量到走線的流暢度，故將其放置於正中央，因每個子電路所擺設的位子都非常的緊密，避免雜訊的相互干擾，在每個子電路上都利用雙層的保護環(Guard ring)包覆。

圖 5-1 晶片照相圖與其腳位順序

| PIN Number                       | Function           | PIN Number | Function               |

|----------------------------------|--------------------|------------|------------------------|

| 01,13,14,19,20,23,24,25,26,41,44 | Power Supply (1.8) | 15,11      | VCO BIAS               |

| 07,08                            | Power Supply (3.3) | 06,05      | VCO/IF Output          |

| 03,12,40                         | Mixer BIAS         | 09,10      | Buffer BIAS            |

| 02,04                            | LNA BIAS           | 22         | External Capacitance   |

| 38,39                            | LA BIAS            | 21         | Charge Pump BIAS       |

| 29                               | Reset              | 34,31      | $f_{DIV}/f_{REF}$      |

| 36,37,35                         | LA_C+/LA_C-/RSSI   | 30,32,33   | PFD/Encode EN/FD to PD |

| 16,17,18                         | VCO BAND Select    | 27,28      | I/Q Path               |

| 43,42                            | RF Input           |            |                        |

表 5-1 晶片接腳配置表

## 5.2. 量測環境 (Measurement Setup)

本晶片所需的輸入訊號(RF)為 2.416GHz 的 QPSK 調變訊號，而欲觀察頻率還原器在頻率鎖定時輸出 2.432GHz 的頻譜與資料解調器解調出的 I/Q 訊號所構成的星座圖(Constellation)。

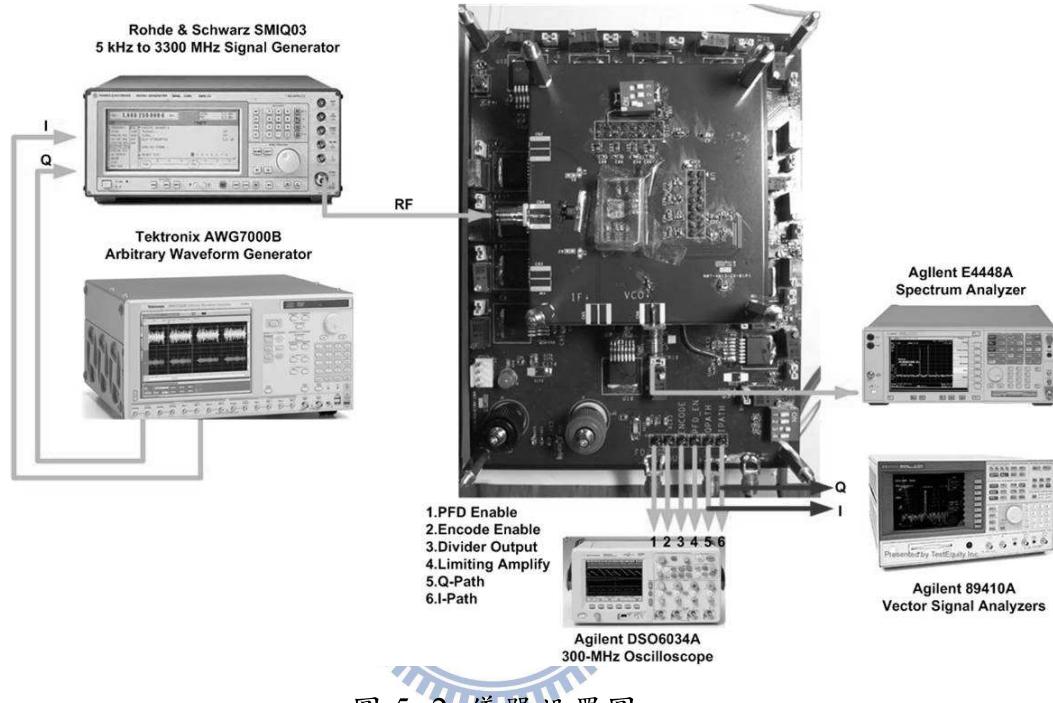

圖 5-2 儀器設置圖

儀器設置如圖 5-2 所示，晶片量測以裸晶片安置在 FR-4 材質之印刷電路板上進行量測，高頻輸出採用 3.5 mm SMA 接頭外接 cable 線至儀器。其發射端的射頻訊號是利用 Tektronix AWG7000B 任意波形產生器將編輯好的基頻資料向量，透過 Rohde & Schwarz SMIQ03 向量訊號產生器混頻於 2.416GHz 系統工作的頻段。輸出訊號方面，頻譜的觀察採用 Agilent E4448A 之頻譜分析儀，觀察時域行為則使用 Agilent DSO6034A 示波器觀察頻率鎖定時的輸出波形與鎖定行為，在資料解調的輸出端 I/Q 訊號，則使用 Agilent 89410A 的向量訊號分析儀，觀察解調變訊號的星座圖與眼圖。

### 5.3. 量測結果 (Measurement Results)

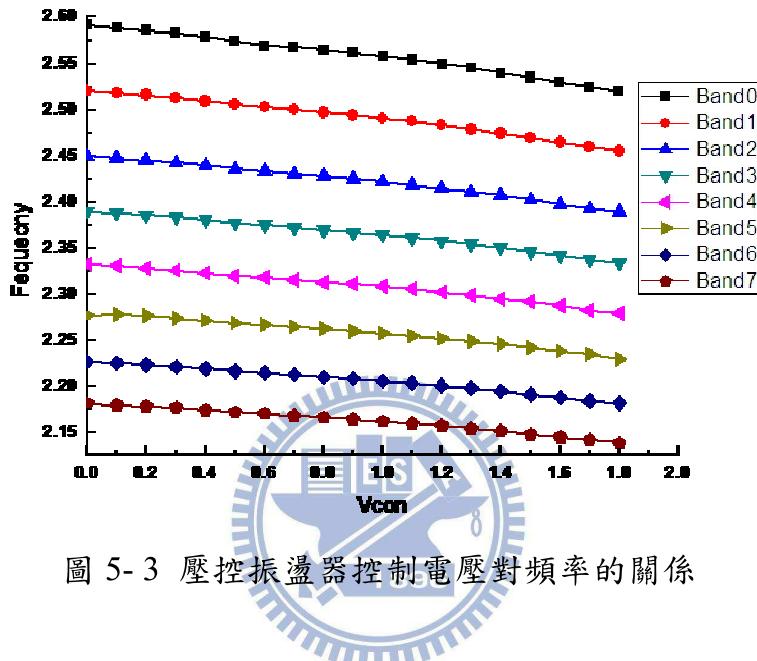

拿到晶片後，將 DC 板上的直流偏壓點設定好後，首先先測量壓控振盪器的工作頻率範圍，如圖 5-3 所示壓控振盪器控制電壓對頻率的關係，由圖可知在 Band2 的曲線上為系統的工作區域。

圖 5-3 壓控振盪器控制電壓對頻率的關係

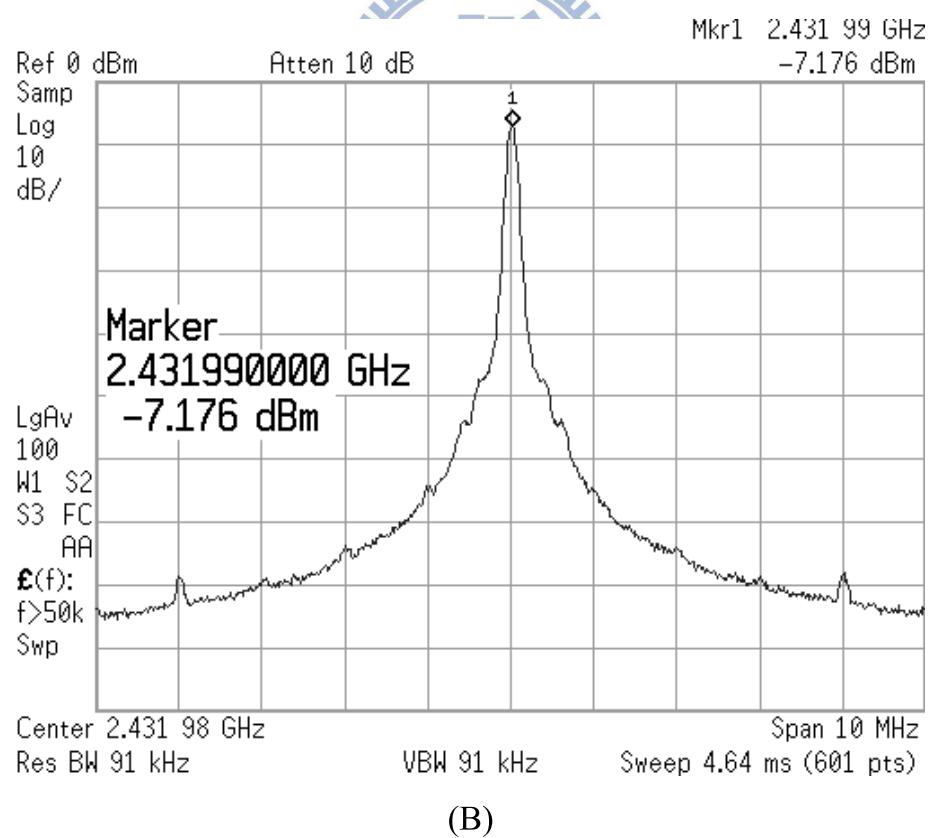

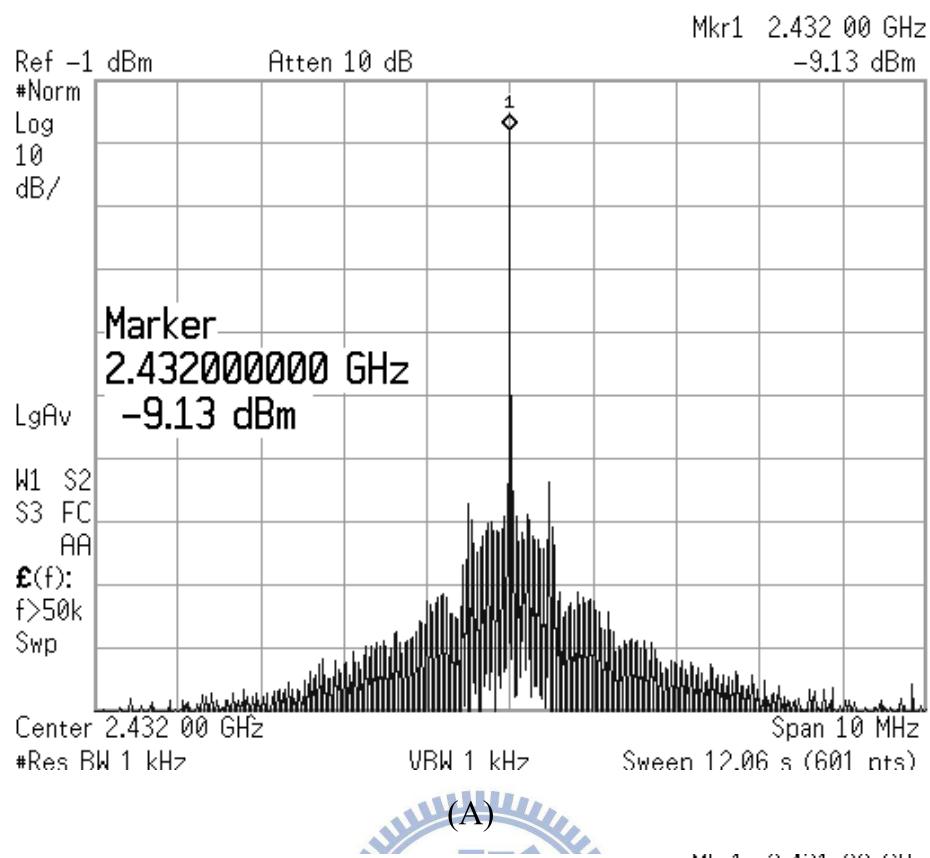

我們使用 SMA 接頭的銅軸電纜線連接傳送端與接收端，如圖 5-4 所示，為系統鎖定後壓控振盪器的輸出頻譜，圖 5-4(A)(B)所示分別為頻率取得模式與資料解調模式的輸出頻譜，鎖定於 2.432GHz。我們觀察到在資料解調模式中的輸出頻譜在主頻率偏移 4MHz 附近產生參考突波(Reference Spur)，此為系統工作於資料解調模式下相頻偵測器調節模式的工作週期。

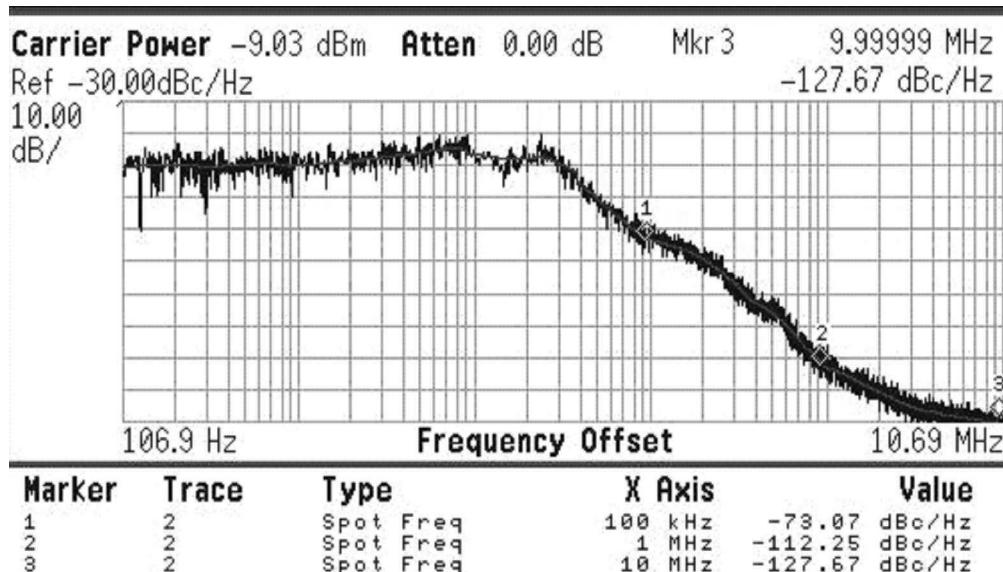

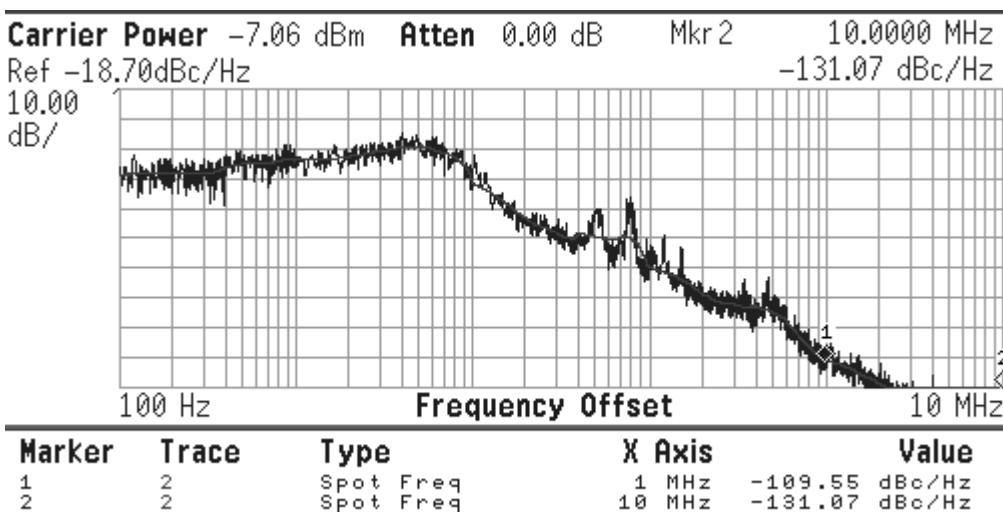

而在頻率取得模式下相位雜訊之表現如圖 5-5(A)所示，約為-112 dBc/Hz 於 1 MHz 偏移時，如圖 5-5(B)所示為資料解調模式的相位雜訊，約為-109dBc/Hz 於 1 MHz 偏移時，根據[16]已符合一般短距離通訊接收器的要求。

圖 5-4 壓控振盪器輸出頻譜 (A)頻率取得模式 (B) 資料解調模式

(A)

(B)

圖 5-5 壓控振盪器輸出之相位雜訊 (A)頻率取得模式(B)資料解調模式

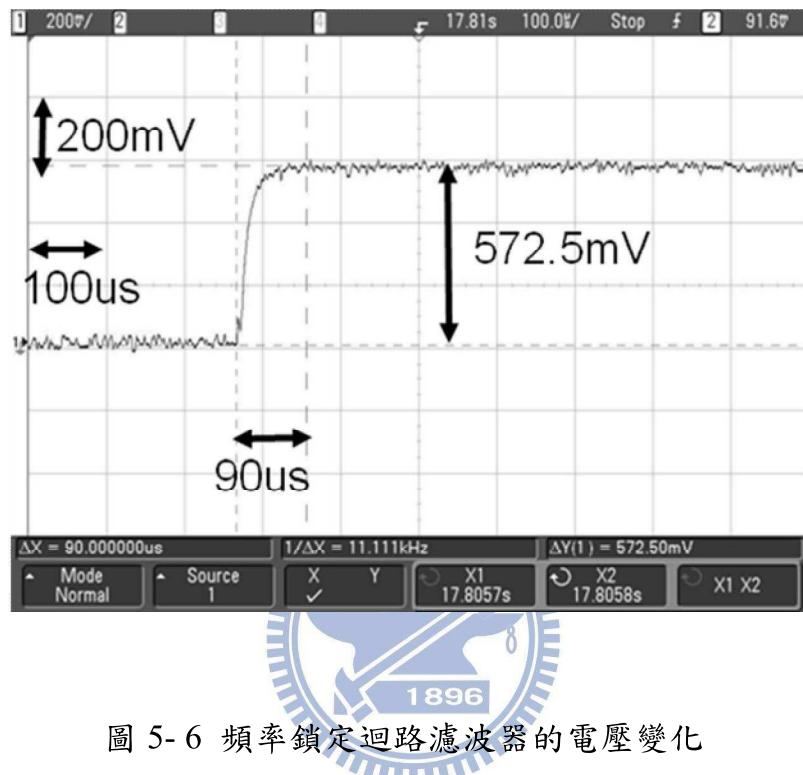

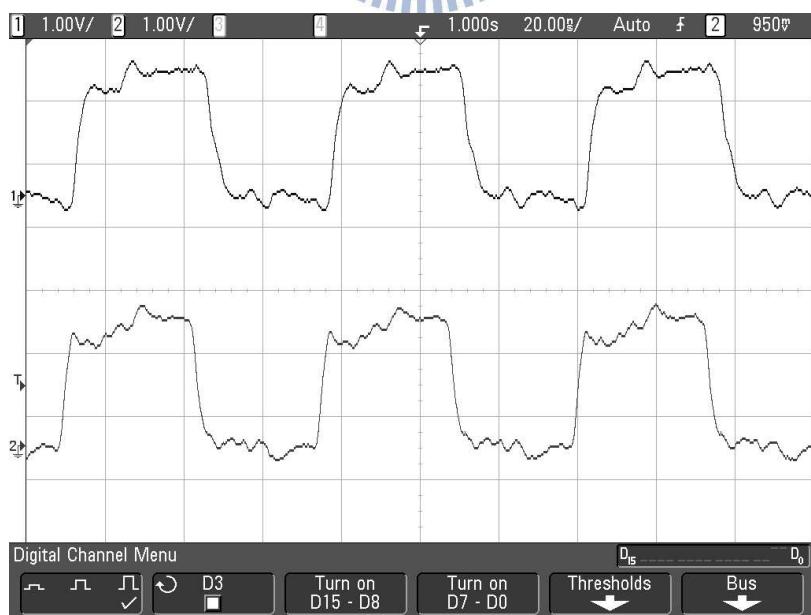

如圖 5-6 所示為頻率回復器鎖定所需的時間，利用示波器觀察迴路濾波器輸出端的電壓變化，由量測圖可得知，控制電壓由 0 伏特爬升到 0.57 伏特需要 90us，經由觀察壓控振盪器輸出頻譜，確認頻率已鎖定於我們所設定的頻率值，且觀察中頻訊號與除頻器輸出波形，兩訊號的上升緣在同一時間點是對齊的，如圖 5-7 所示。

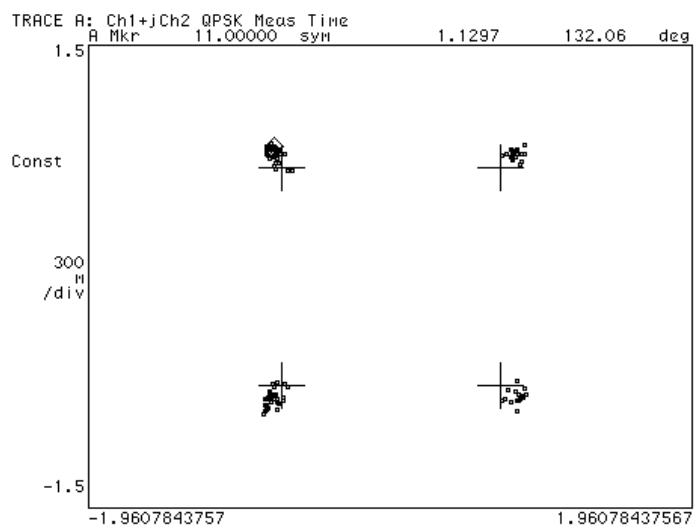

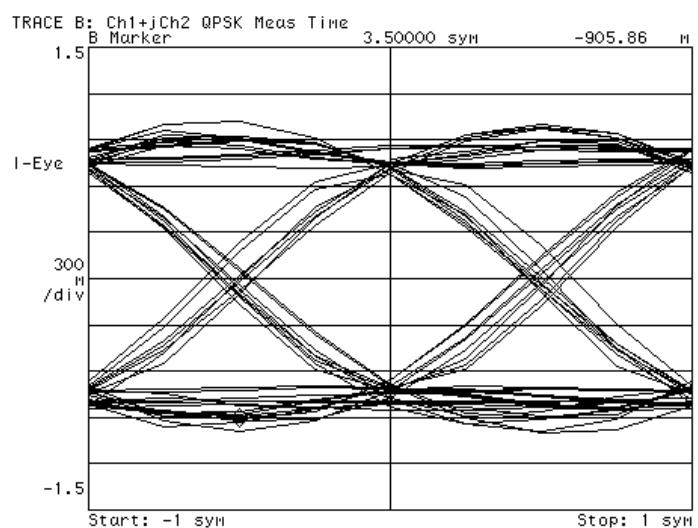

如圖 5-8(A)所示，為解調變後 I/Q 的輸出波形，經由向量訊號分析儀量測到的星座圖，由圖可觀察知，解調變後的訊號都有在調變系統所規範的四點上。如圖 5-8(B)所示，為 I/Q 輸出波形所疊出的眼圖，依照眼圖最高準位與最低準位所交疊的開口寬度與高度均於所規範內。

圖 5-6 頻率鎖定迴路濾波器的電壓變化

圖 5-7 鎖定後除頻器與中頻訊號的輸出波形

Date: 01-11-09 Time: 08:27 PM

Date: 01-11-09 Time: 08:08 PM

圖 5-8 (A)I/Q 輸出訊號之星座圖，QPSK 調變傳輸速率 1Mbps，(B)輸出訊號之眼圖

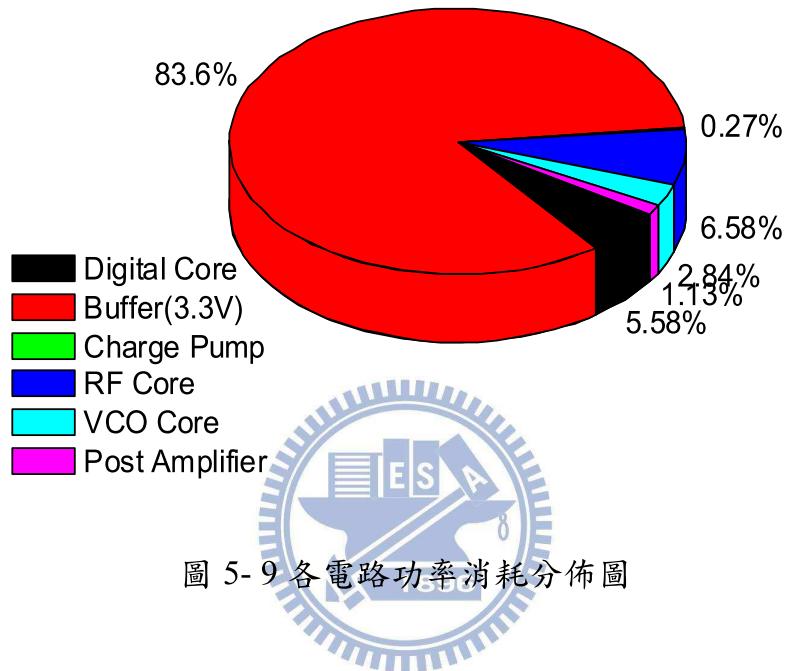

最後整個無線接收器，其功率消耗核心電路操作在 1.8 V 之電壓下，總共消耗約 21mW，其輸出緩衝級工作於 3.3V，功率消耗約為 103.9mW，如表所示為本晶片量測出的效能摘要表，如表 5-3 所示。

| Part           | Power Consumption                                   |

|----------------|-----------------------------------------------------|

| Digital Core   | 6.94mW                                              |

| Buffer(3.3V)   | 103.98mW                                            |

| Charge Pump    | 0.34mW                                              |

| RF Core        | 8.19mW                                              |

| VCO Core       | 3.53mW                                              |

| Post Amplifier | 1.4mW                                               |

| Total Power    | 20.4mW+34.5mW(Buffer for Core)+70mW(Buffer for PAD) |

表 5-2 各部分電路功率消耗分佈表

| Parameter              | Value                                        |

|------------------------|----------------------------------------------|

| Process                | TSMC 0.18 $\mu$ m CMOS                       |

| Core Supply            | 1.8V                                         |

| Buffer Supply          | 3.3V                                         |

| Phase Noise<br>(@1MHz) | FA Mode : -112dBc/Hz<br>DM Mode : -109dBc/Hz |

| Locking Time           | 90 us                                        |

| Power Consumption      | 20.8mW@1.8v(Core)<br>34.3mW@3.3v(Buffer)     |

| Chip Area              | 1750 um x 1550 um                            |

表 5-3 本晶片效能摘要表

# 第六章

---

---

## 結論

---

---

本論文提出一個操作於 2.4GHz 無晶體振盪器之單晶片無線接收器使用 1Mbps 的 QPSK 解調器 (A 2.4 GHz Crystal-less Single-Chip Wireless Receiver for 1Mbps QPSK Demodulation)，其電路由低雜訊放大器，混波器，後級放大器，低通濾波器，頻率還原器，與資料解調器整合於單一晶片中，本無線接收器電路可自發射端信號直接還原頻率信號，無須仰賴石英晶體振盪器等參考信號源，使系統達到完全單晶片化，免除石英晶體振盪器之額外功率消耗，在電路板系統層級可做到低功耗及低成本，因系統可自發射端信號直接還原頻率信號，降低無線發射器與接收器兩端之頻率誤差問題。此外頻率還原電路可同時進行發射信號之資料解調變 (BPSK，或 QPSK)，無須仰賴傳統之類比數位轉換器及解調變器，大幅降低系統複雜度及成本。

## 參考文獻

- [1] B. Gyselinckx, et al, "Human++: autonomous wireless sensors for body area networks," *Proc. of IEEE Custom Integrated Circuits Conference*, Sept. 2005, pp.13-19.

- [2] D. Han and Y. Zheng, "An ultra low power GFSK demodulator for wireless body area network," *Proc. of IEEE ESSCIRC*, Sep. 2008, pp.434–437.

- [3] IEEE 802.15.4 WPAN-LR Task Group

“<http://www.ieee802.org/15/pub/TG4.html>”

- [4] IEEE 802.15.1, “<http://www.ieee802.org/15/pub/TG1.html>”

- [5] 王智弘/林苑晴 “矽/MEMS 振盪器下戰帖石英晶體振盪器嚴陣以待”

新電子期刊 2009 年 3 月號

- [6] D.J. Allstot, et al., "Design considerations for CMOS low-noise amplifiers" *IEEE RFIC Symp.*, pp. 97-100, June 2004

- [7] J. Park, C-H. Lee, B. Kim, and J. Laskar, "Design and Analysis of Low Flicker-Noise CMOS Mixers for Direct-Conversion Receivers" *IEEE Trans. Microw. Theory Tech.*, vol. 54, no.12 pp.4372 - 4380 Dec. 2006.

- [8] S. Galal and B. Razavi, "10-Gb/s Limiting Amplifier and Laser/Modulator Driver in 0.18- $\mu$ m CMOS Technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 12, pp. 2138–2146, Dec. 2003.

- [9] Y.-C. Chen, Y.-C. Wu and P.-C. Huang, "A 1.2-V CMOS Limiter/RSSI/Demodulator for Low-IF FSK Receiver" *IEEE Custom Integrated Circuits Conference (CICC)*, San Jose, California, Sep. 2007

- [10] Wei-Zen Chen and Dai-Yuan Yu, "A Dual-band Four-mode Delta Sigma Frequency Synthesizer" *Radio Frequency Integrated Circuit Symposium*, pp. 206-207, June. 2006.

- [11] National Semiconductor.

- [12] B. Razavi, "A study of phase noise in CMOS oscillators," *IEEE Journal of Solid State Circuits*, Vol. 31, pp. 331-343, Mar. 1996.

- [13] D. A. Hitok and C. G. Sodini, "Adaptive biasing of a 5.8GHz CMOS oscillator," *IEEE Int. Solid State Circuits Conf. Dig. Tech. Papers*, pp. 292-293, Feb. 2002.

- [14] E. Hegazi, et al., "A filtering technique to lower oscillator phase noise," *IEEE Int. Solid State Circuits Conf. Dig. Tech. Papers*, pp. 292-293, Feb. 2001.

- [15] Ali Hajimiri, Thomas H. Lee, "A General Theory of Phase Noise in Electrical Oscillators" *IEEE Journal of Solid State Circuits*, Vol. 33, No2, pp. 179-194, February 1998.

- [16] D. M. W. Leenaerts, et al., "A 15-mW fully integrated I/Q synthesizer for Bluetooth in 0.18- $\mu$ m CMOS" *IEEE Journal of Solid State Circuits*, Vol. 38, pp. 1155-1162, July 2003.