國立交通大學

電機學院 IC 設計產業研發碩士班

碩士論文

具二區段式溫度計編碼架構的

12 位元 500 百萬赫芝電流式互補式

金氧半導體數位類比轉換器

12-bit 500MSample/s Current-Steering CMOS D/A Converter

with Dual-Segment Thermometer-Code Architecture

研究 生：張維欣

指導教授：洪崇智 教授

中華民國九十七年九月

具二區段式溫度計編碼架構的

12 位元 500 百萬赫芝電流式互補式

金氧半導體數位類比轉換器

12-bit 500MSample/s Current-Steering CMOS D/A Converter

with Dual-Segment Thermometer-Code Architecture

研究 生：張維欣

Student : Wei-Shin Chang

指 導 教 授：洪 崇 智

Advisor : Chung-Chih Hung

A Thesis

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Industrial Technology R & D Master Program

on IC Design

September 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年九月

具有二區段式溫度計編碼架構的

12 位元 500 百萬赫芝電流式互補式

金氧半導體數位類比轉換器

學生：張維欣

指導教授：洪崇智博士

國立交通大學電機學院產業研發碩士班

摘要

本論文設計實現一個 12 位元 500MHz 的數位類比轉換器，選取電流式架構讓數位-類比轉換器輸出級的設計上不需要設計額外放大器來做電流電壓轉換，降低功率消耗並符合高速與高解析度的應用。

電流式數位類比轉換器設計需考量因製程造成電流源不匹配效應，對電流源電晶體大小進行最佳化後來降低對靜態特性 DNL 與 INL 上的不理想性。進而針對因電路造成的輸出突波的非理想性加以改善所以加入二元順序判別電路的機制讓數位-類比轉換器電路一次只打開一個電流源，降低突波效應，得到較佳的動態特性表現，並配合選擇順序最佳化與四象限對稱佈局安排來降低階梯誤差與系統誤差。

電流式數位類比轉換器由 4 + 8 位元用二區段式溫度計編碼架構組成。採用 TSMC 0.18  $\mu\text{m}$  1P6M mixed-signal CMOS 製程來實現，整體晶片面積為  $1.8648\text{mm}^2$ 。

# 12-bit 500MSample/s Current-Steering CMOS D/A Converter with Dual-Segment Thermometer-Code Architecture

Student : Wei-Shin Chang

Advisor : Dr. Chung-Chih Hung

Industrial Technology R & D Master Program of

Electrical and Computer Engineering College

National Chiao Tung University

## ABSTRACT

The thesis presents a 12bit 500MHz digital-to-analog-converter (DAC) by using a current-steering architecture. The output of the DAC does not require an extra output buffer to convert I to V so as to achieve lower power consumption, and to suit for high speed and high resolution application.

The current steering DAC needs to deal with the issue of the current source mismatch due to process fabrication. Therefore current sources are first optimized by transistor size to reduce no-ideal integral nonlinearity (INL) and differential nonlinearity (DNL) effects on static performance. To reduce non-ideal glitch effects, binary order decision circuits are implemented in the current-steering DAC to allow only one current source opened every time for getting better performance. Combined with optimized switching sequence and symmetric current source array arranged as a two-dimensional common centroid floor plan, gradient effects and symmetric errors can be further decreased.

The 12bit digital-to-analog converter was fabricated in a TSMC 0.18 $\mu$ m CMOS technology. It is based on a current steering dual segment with both thermometer coded 4+8 architecture.

# 誌謝

首先感謝指導老師洪崇智老師在這兩年多的研究與學習生涯裡，提供舒適的學習環境與自由探索學問的空間。以及研究領域上對我的指導與照顧，學生銘記於心並由衷感謝老師您有教無類的辛勞。感謝李育民教授及羅天佑學長撥冗蒞臨並榮幸承蒙您對此論文寶貴的指導與建議，使其更趨完備。

其次感謝天佑、文弘、德文、旭右、嘉泰、家敏學長們在這兩年多裡專業知識上教導與傳承，並宗諺與阿白學長們將研究領域上的經驗傾囊相授與耐心教導，還有同窗們楓翔、介仁、智龍、竹緯、文霖、永洲、威文、俊彥在學業上的扶持和研究生活上的關照，與學弟們阿龜、聖文、兆良、新傑的關懷，感謝大家。

再者感謝這些年來一路相伴的朋友們，雅筑、季慧、儼矜、振益、文亮、嘉雯、東山、豐鏞、維修、伯堂、政學、秋華與真綾，亦師亦友的關懷與幫忙。

最要感謝我的爹娘，感謝他們勞心且勞力栽培，完全的支持是我勇於努力加油往前走的動力，讓我能全心投入研究之中，無後顧之憂的完成我的學業與論文。在此致上最高的敬意，願及祈福您們永遠身體健康與快樂。

深覺得之於人者多，出之於己者少，在此將感謝獻給所有幫助過我的貴人們。

張維欣

國立交通大學

中華民國九十七年九月

# 目錄

|                           |     |

|---------------------------|-----|

| 中文摘要                      | I   |

| <b>Abstract (English)</b> | II  |

| 誌謝                        | III |

| 目錄                        | IV  |

| 圖目錄                       | VII |

| 表目錄                       | X   |

| <br>                      |     |

| <b>第一章. 緒論</b>            |     |

| 1.1 研究動機                  | 1   |

| 1.2 論文組織                  | 2   |

| <b>第二章. 數位-類比轉換器基本架構</b>  | 3   |

| 2.1 理想數位-類比轉換器            | 3   |

| 2.2 類比-數位轉換器規格            | 4   |

| 2.2.1 靜態特性                | 4   |

| 2.2.2 動態特性                | 8   |

| 2.2.3 動態範圍                | 10  |

| 2.3 二進位加權式數位-類比轉換器架構      | 12  |

| 2.3.1 R-2R 階梯式數位-類比轉換器    | 12  |

| 2.3.2 切換電容式電荷重分配數位-類比轉換器  | 13  |

| 2.3.3 二進位碼加權電流式數位-類比轉換器   | 15  |

| 2.4 溫度計碼數位-類比轉換器架構        | 16  |

| 2.5 混合型數位-類比轉換器架構         | 17  |

| 2.6 總結                    | 18  |

|                               |           |

|-------------------------------|-----------|

| <b>第三章. 電流式數位-類比轉換器的非理想效應</b> | <b>19</b> |

| 3.1 電流源電晶體的不匹配性               | 19        |

| 3.2 電流源的有限輸出阻抗                | 23        |

| 3.3 電流源陣列的不匹配性                | 25        |

| 3.4 電流源開關電晶體組的非理想效應           | 28        |

| 3.5 位元偏移與突波                   | 31        |

| 3.6 總結                        | 32        |

| <b>第四章. 數位-類比轉換器電路設計</b>      | <b>33</b> |

| 4.1 數位-類比轉換器的架構               | 33        |

| 4.1.1 區段式溫度計碼數位-類比轉換器         | 34        |

| 4.1.2 12 位元數位-類比轉換器架構圖        | 36        |

| 4.2 數位電路                      | 37        |

| 4.2.1 溫度計解碼器                  | 37        |

| 4.2.2 二元順序判別電路                | 39        |

| 4.2.3 高速門閂電路                  | 42        |

| 4.3 類比電路                      | 43        |

| 4.3.1 切換單位電流源設計               | 44        |

| 4.3.2 參考偏壓電流源電路               | 45        |

| 4.4 選擇序列最佳化                   | 46        |

| 4.5 佈局                        | 49        |

| 4.6 總結                        | 51        |

| <b>第五章. 模擬與測試電路</b>           | <b>52</b> |

| 5.1 模擬結果                      | 52        |

| 5.2 測試電路                      | 55        |

第六章. 結論與未來工作展望 58

參考文獻 59

# 圖目錄

## Chapter 2

|                                      |    |

|--------------------------------------|----|

| Fig. 2.1 數位-類比轉換器介面                  | 3  |

| Fig. 2.2 N 位元的數位-類比轉換器區塊圖            | 4  |

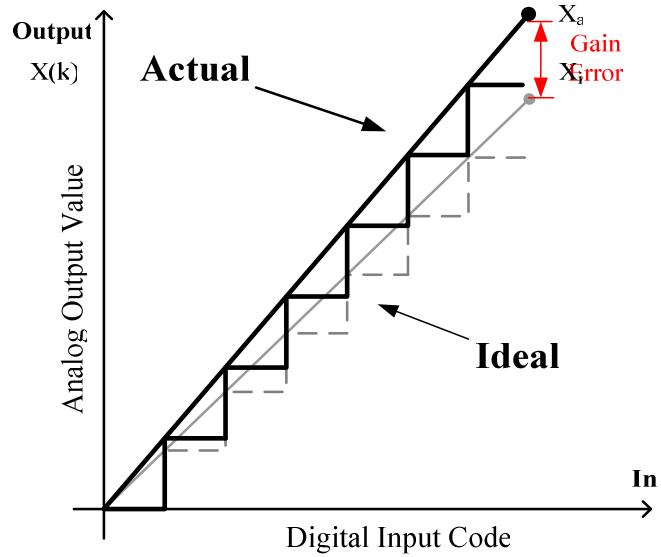

| Fig. 2.3 有偏移誤差量的非理想轉換曲線              | 5  |

| Fig. 2.4 有增益誤差量的非理想轉換曲線              | 6  |

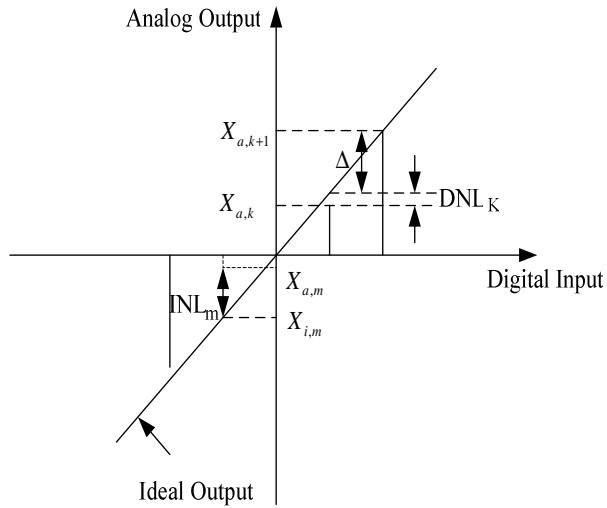

| Fig. 2.5 換器的 INL 與 DNL 非線性誤差         | 7  |

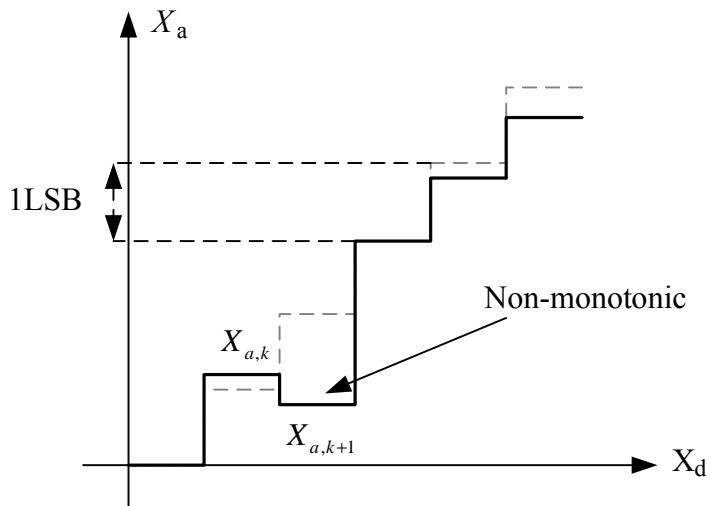

| Fig. 2.6 非單調線性的數位-類比轉換器              | 7  |

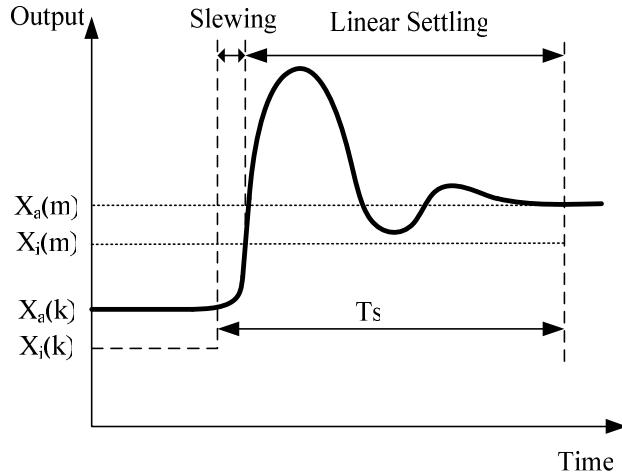

| Fig. 2.7 實際輸出信號與理想輸出信號(黑色破折號)        | 9  |

| Fig. 2.8 輸出有突波                       | 10 |

| Fig. 2.9 數位-類比轉換器輸出頻譜圖               | 10 |

| Fig. 2.10 N 位元 R-2R 階梯式數位-類比轉換器      | 13 |

| Fig. 2.11 N 位元切換電容式電荷重分配數位-類比轉換器     | 14 |

| Fig. 2.12 N 位元二進位碼加權電流切換式數位類比轉換器     | 15 |

| Fig. 2.13 溫度計碼電流式數位-類比轉換器            | 17 |

| Fig. 2.14 以 M 位元溫度解碼的 N 位元區段數位-類比轉換器 | 18 |

## 第三章

|                                                                                           |    |

|-------------------------------------------------------------------------------------------|----|

| Fig. 3.1 $INL_{yield}$ 與 $\left(\frac{\sigma_I}{I}\right) Unit Current Std Deviation$ 的關係 | 20 |

| Fig. 3.2 理想的 MOS 電流源與製程中發生隨機不匹配性                                                          | 21 |

| Fig. 3.3 單位電流源所需最小的閘極面積與過驅電壓關係                                                            | 23 |

| Fig. 3.4 有限輸出阻抗的電流源                                                                       | 24 |

| Fig. 3.5 12 位元數位-類比轉換器有限輸出阻抗與 INL 關係                                                      | 25 |

| Fig. 3.6 電流源陣列與外圍等效相彷電流源                                                                  | 25 |

## 第四章

|                                                                                                                     |    |

|---------------------------------------------------------------------------------------------------------------------|----|

| Fig. 4.1 溫度計碼架構, 二進位加權架構下數位-類比轉換器摘要                                                                                 | 33 |

| Fig. 4.2 常態分佈電流源面積與區段的百分比                                                                                           | 35 |

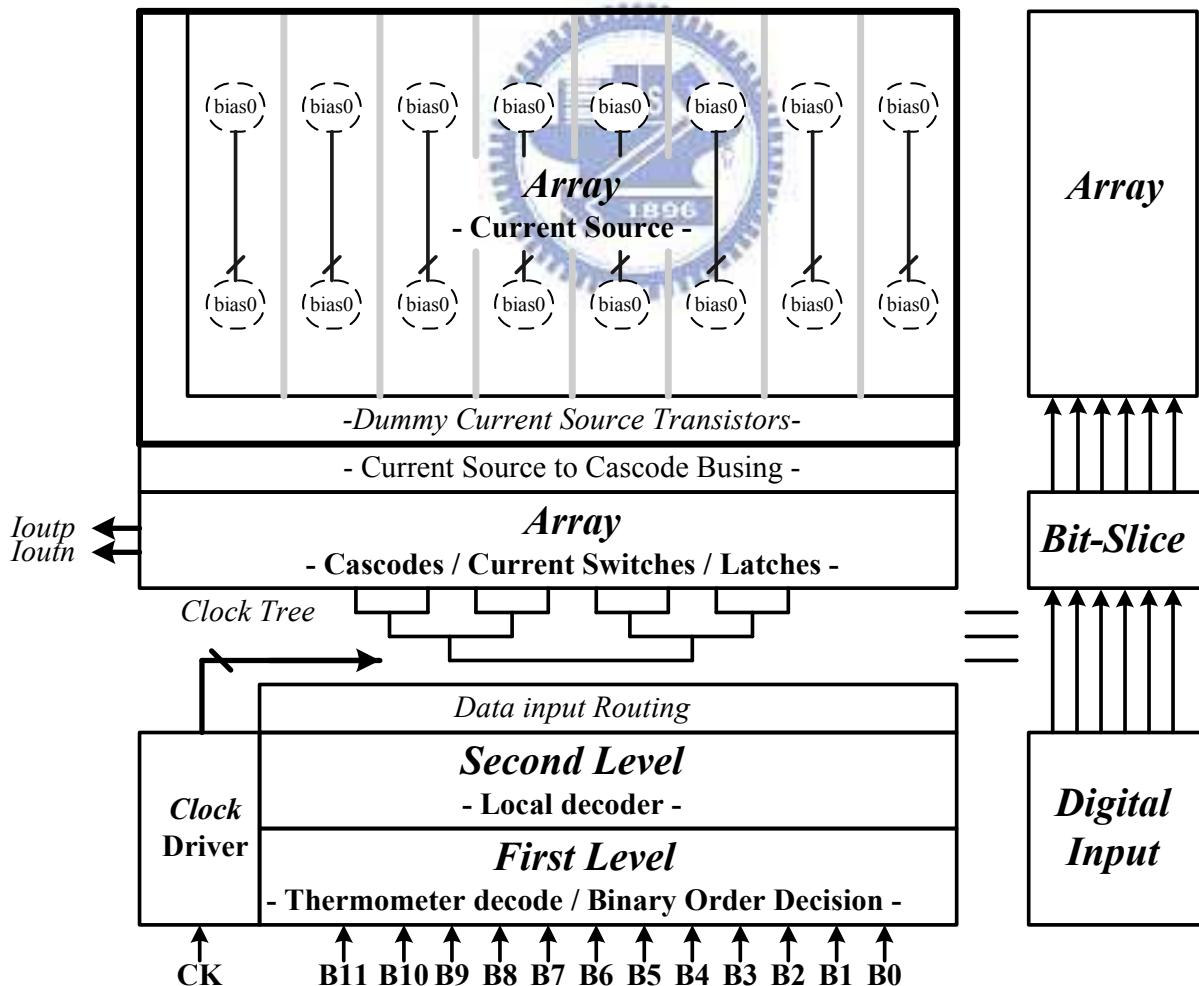

| Fig. 4.3 12 位元數位-類比轉換器架構示意圖.                                                                                        | 36 |

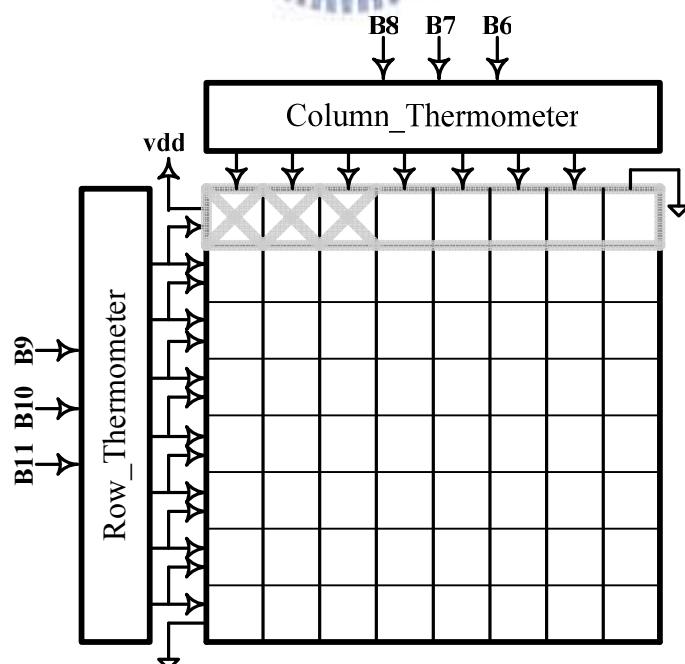

| Fig. 4.4 8*8矩陣式門閂器排列與一對3-to-8溫度計解碼器關係圖                                                                              | 37 |

| Fig. 4.5 溫度計解碼器                                                                                                     | 38 |

| Fig. 4.6 MSB電流源和LSB電流源打開的配合關係圖                                                                                      | 39 |

| Fig. 4.7 相比較於(a) 12bit DAC(6bit-溫度計碼)+(2bit-BOD電路)與<br>(b) 12bit DAC(6bit-溫度計碼)+(2bit-二進位碼)-Ref[6]<br>在輸出端造成突波大小示意圖 | 40 |

| Fig. 4.8 二元順序判別(BOD)規則                                                                                              | 40 |

| Fig. 4.9 二元順序判別(BOD)電路與方塊示意圖.                                                                                       | 41 |

|                                                                      |    |

|----------------------------------------------------------------------|----|

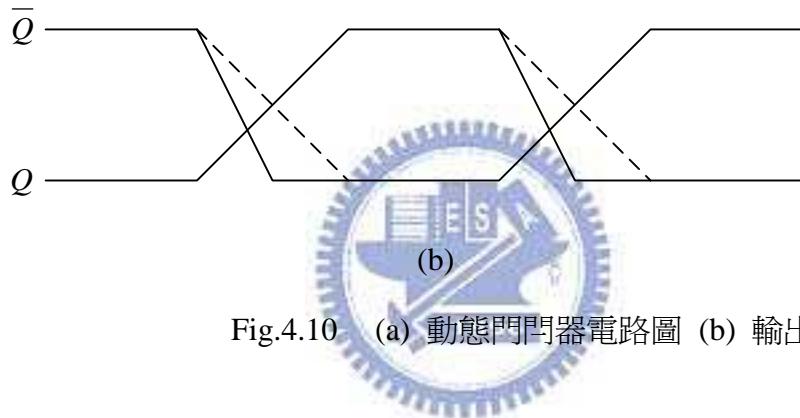

| Fig. 4.10 (a) 動態門閂器電路圖                                               |    |

| (b) 輸出訊號                                                             | 43 |

| Fig. 4.11 叠接式和開關電晶體組成的電流源                                            | 44 |

| Fig. 4.12 電流源的設計流程                                                   | 45 |

| Fig. 4.13 偏壓電路圖                                                      | 46 |

| Fig. 4.14 圖示 A 為(8 個組週期)x(8 個行單位電流源)的矩陣                              | 46 |

| Fig. 4.15 圖示 B 為兩個圖示 A 以 $y_{axis}$ 為中心做鏡像對稱                         | 47 |

| Fig. 4.16 四組 8*8 矩陣以 $x_{axis} - y_{axis}$ 中心呈對稱且做 common central 排列 | 48 |

| Fig. 4.17 電流源 1*8 矩陣共兩組以 $y_{axis}$ 的佈局                              | 49 |

| Fig. 4.18 數位-類比轉換器佈局對稱平面配置圖                                          | 49 |

| Fig. 4.19 晶片佈局圖                                                      | 50 |

## 第五章

|                                                             |    |

|-------------------------------------------------------------|----|

| Fig. 5.1 SIN波頻譜 $F_s = 500$ MHz and $F_{sig} = 1.46$ MHz    | 53 |

| Fig. 5.2 SIN波頻譜 $F_s = 500$ MHz and $F_{sig} = 171.4$ MHz   | 53 |

| Fig. 5.3 SIN 波頻譜(SFDR)輸入信號 1.46 MHz 到 171.4MHz 而取樣頻率 500MHz | 54 |

| Fig. 5.4 差動非線性(DNL)和累積非線性(INL)                              | 54 |

| Fig. 5.5 測試環境建立                                             | 56 |

| Fig. 5.6 電源調整器                                              | 57 |

# 表目錄

## 第二章

|                             |    |

|-----------------------------|----|

| Table 2.1 十進位碼，二進位碼，溫度計碼對應表 | 16 |

|-----------------------------|----|

## 第四章

|                                  |    |

|----------------------------------|----|

| Table 4.1 二進位碼與溫度計碼數位-類比轉換器面積的比較 | 34 |

| Table 4.2 3-to-8 溫度計碼真值表         | 38 |

| Table 4.3 布林函數表示式                | 38 |

| Table 4.4 2-to-4 溫度計碼真值表         | 41 |

## 第五章

|                  |    |

|------------------|----|

| Table 5-1 模擬結果列表 | 55 |

|------------------|----|

現代通訊應用電腦系統、數位電視、高畫質電視等上，高速數位-類比轉換器是通訊系統上重要的一個區塊[2]，它利用數位訊號技術將信號數位化處理後，更能有效率的利用數位-轉類比的界面將信號做傳輸，所以數位-類比介面的正確性與動態性能上的極限掌控了整個轉換器的表現。

### 1.1 研究動機

高速數位類比轉換器使用CMOS製程來做的電路設計，實現的電路設計的方法有很多，如較早期的作法用被動元件的方式有電阻式(Resistor strings)，切換電容式(Switched-capacitor)需耗費大片面積與消耗掉大量功率，現在的作法用主動元件的電流源式(Current-Steering)其速度不會受到輸出緩衝器的限制[2]可以達到高速的需求。

電流源式數位類比轉換器性能上受限於CMOS製程，如電流源電晶體因製程上如參雜濃度或氧化層厚度…梯度影響下所造成的靜態非線性失誤，可利用設計上加大電流源的面積[3]、隨機佈局的方式[8]、[10]、[12]、加入有校準機制[15]或微調的電路[18]，增加元件的匹配特性來改善靜態特性上的線性度[3]-[18]。

在論文中此數位類比轉換器使用0.18um TSMC CMOS 製程，採用的是溫度計碼架構型的電流源數位類比轉換器，用8位元的溫度計碼(MSB)與4位元的溫度計碼 (LSB)所組成來實現符合具有高速、高解析度、突波最小化等特點的操作。

## 1.2 論文組織

此論文有六個章節所組成 .

第一章 緒論

第二章 數位-類比轉換器架構

第三章 電流式數位-類比轉換器的非理想效應

第四章 數位-類比轉換器電路設計

第五章 數位-類比轉換器電路模擬結果與量測

第六章 結論與未來工作展望

### 數位-類比轉換器基本架構

本章介紹數位-類比轉換器在應用系統中所扮演的角色，與數位-類比轉換實作上有不同的基本架構與其規格參數代表的定義。

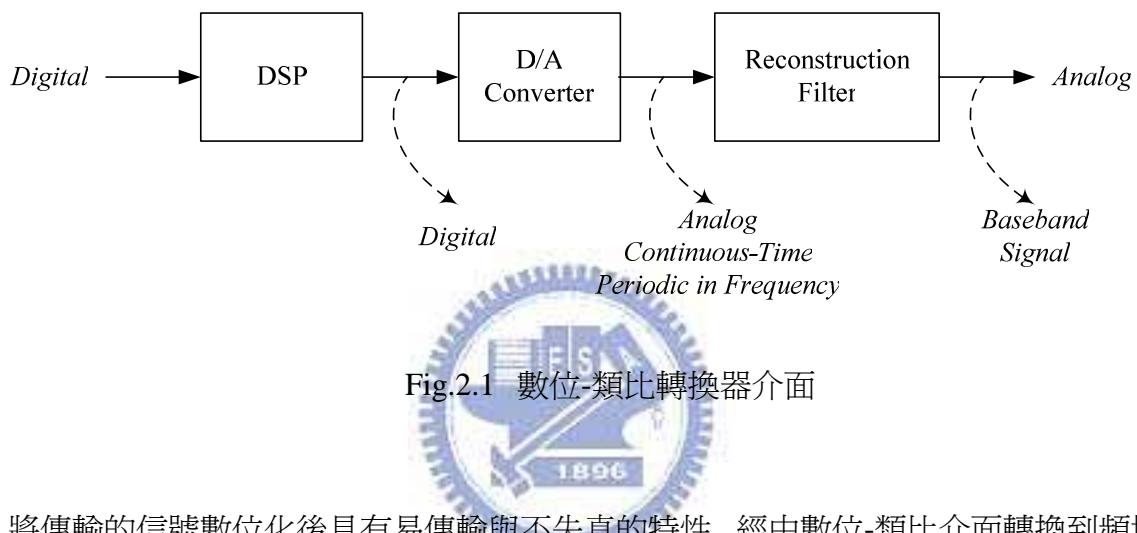

將傳輸的信號數位化後具有易傳輸與不失真的特性，經由數位-類比界面轉換到頻域變成類比連續信號後，經過重建濾波器移除掉高頻的雜訊取出基頻的訊號。

#### 2.1 理想的數位-類比轉換器

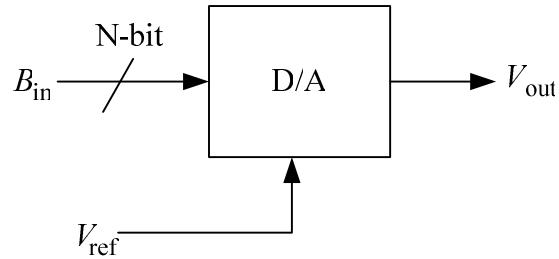

經數位-類比轉換器轉換後產生的類比電壓  $V_{out}$  值正比於數位輸入信號  $B_{in}$ 。

如一  $N$  位元的數位-類比轉換器如圖 Fig.2.2，其輸出電壓值  $V_{out}$  表示如：

$$V_{out} = V_{ref} * (B_0 * 2^{-1} + B_1 * 2^{-2} + B_2 * 2^{-3} + \dots + B_{N-1} * 2^{-N}) \quad (2.1)$$

$B_i$ : 代表1或0.

$B_{N-1}$ : 定義最高位元(Most Significant Bit)MSB

$B_0$  : 定義最低位元(Least significant bit)LSB

Fig.2.2 N位元的數位-類比轉換器區塊圖

## 2.2 數位-類比轉換器規格

數位-類比轉換器的設計上要瞭解其重要的特性並將這些特性分成兩類，其一為靜態特性，其二為動態特性與範圍[1].

### 2.2.1 靜態特性

有五種參數來描述靜態的特性，依序為

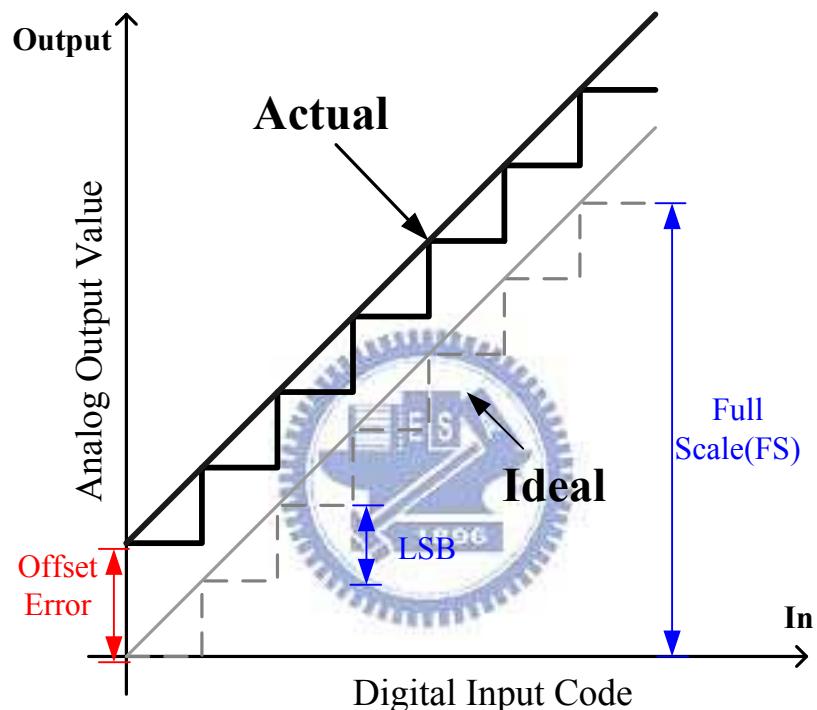

偏移誤差(Offset Error)

增益誤差(Gain Error)

差分非線性誤差(DNL)

累積非線性誤差(INL)

與單調性(Monotonic)

## 偏移量誤差 ( Offset Error )

數位信號輸入為零時，類比輸出理想上為零電壓輸出，但實際上有偏移量的類比電壓輸出。

$$E_{off} \equiv \frac{V_{out}}{V_{LSB}}|_{0.....0} \text{ (L S B)} \quad (2.2)$$

Fig.2.3 帶有偏移誤差量的非理想轉換曲線

## 增益誤差 ( Gain Error )

數位-類比轉換器滿刻度轉換完畢後，計算理想與實際的轉換下的增益誤差量，此時已經將實際的轉換曲線特性偏移誤差量先移除到0，並定義如下：

$$E_{gain}(DAC) \equiv \left[ \frac{V_{out}}{V_{LSB}}|1....1 - \frac{V_{out}}{V_{LSB}}|0....0 \right] - 2^N - 1 \quad (2.3)$$

Fig.2.4 帶有增益誤差量的非理想轉換曲線

### 差分非線性誤差 (Differential Non-Linearity - DNL)

DNL 為實際設計的轉換器相臨輸出變化量差值，除上理想轉換器相臨變化量差值，即予以正規化後並減去理想值 1LSB 即得到相對應之間的差距。

$$DNL_k = \frac{X_{a,k+1} - X_{a,k}}{\Delta} - 1 \quad (2.4)$$

### 積分非線性誤差 (Integral Non-Linearity - INL )

整體的非線性誤差量為實際設計轉換器的每一筆類比輸出轉換距理想轉換之間的差分線性誤差量(DNL)的總合。

$$INL_k = \sum_{i=1}^k DNL_i \quad (2.5)$$

非線性誤差使用低頻的輸入信號來量測將出現在高頻時的動態錯誤顯示出來. 所以DNL與INL經常用來看靜態特性的參數或是工具. Fig.2.5與Fig.2.6中 $X_a$ 代表實際情況下類比輸出值,  $X_i$ 代表理想狀況的類比輸出值,  $\Delta$ 是理想數位-類比轉換器的步階大小.

Fig.2.5 轉換器的 INL 與 DNL 非線性誤差

**單調性 (Monotonic)**

隨著數位輸入的增加, 轉換器的類比輸出值也隨著增加, 所以DNL小於1便具有單調性.

舉個非單調性的數位-類比轉換器例子如 Fig.2.6.

Fig.2.6 非單調線性的數位-類比轉換器

單調性 (Monotonicity) 能確保偏差量可以距最佳化曲線少於半個LSB內,

$$|INL_k| \leq \frac{1}{2} LSB \text{ for all } k \quad (2.6)$$

所以DNL的誤差量也必然小於1 LSB以內,

$$|DNL_k| \leq 1 LSB \text{ for all } k \quad (2.7)$$

一般而言需要同時滿足以上兩項條件才能確保有單調性, 仍有架構本身的設計即可以擁

有單調性如溫度解碼式數位-類比轉換器.

## 2.2.2 動態特性

數位-類比轉換器除了靜態錯誤所引起的不匹配性外, 尚有輸入信號快速轉換下所引起其

他失誤的類型. 動態錯誤與輸入信號的頻率有相依性並且隨著輸入信號的頻率與振幅增加而

上升, 而此現象是決定數位-類比轉換器性能的關鍵[2].

### 穩定時間 (Settling Time)

穩定時間是定義轉換器所需要轉換到特定值時所需花費的時間. 數位-類比轉換器主要動

態特性是看轉換速度, 而穩定時間就是定義了數位-類比轉換器的運作速度. 而數位-類比轉

換器的運轉速度受到增益頻寬、運算放大器的旋轉率與寄生電容等影響. 輸出端的轉換速度

關係圖示於Fig.2.7.

Fig.2.7 實際輸出信號與理想輸出信號(黑色破折號)

$X_i(k)$ : 理想狀態下的起始值 ;  $X_i(m)$ : 理想狀態下的最終值.

$X_a(k)$ : 實際狀態下的起始值 ;  $X_a(m)$ : 實際狀態下的最終值.

穩定的狀態由非線性的旋轉階段(Slewing)和現性的穩定階段(Setting)兩種狀態所組成.

由於實際的數位-類比轉換器無法因輸入信號改變而立刻在反應在輸出狀態上. 需要時間讓最後的輸出值穩定於合理的變動範圍內, 如最後輸出值的0.1%變動範圍所需要的穩定時間為 $T_s$ , 此值決定了此電路能運作在多快的速度. 而旋轉階段的狀態則能越小越好, 才不至拉長穩定時間引起類比波形上的失真. 而這種旋轉階段的狀態通常是由電路的輸出端從小電流增加成大電流時發生的現象.

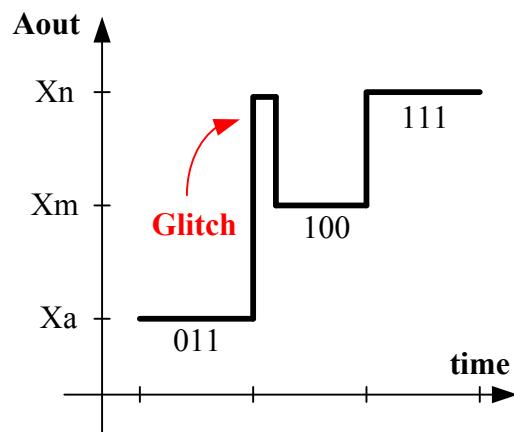

## 突波 (Glitch)

以二進位加權數位-類比轉換器為例, 進行不同位元的切換, 電晶體開與關的時間如果無法匹配則會有突波產生. 如下圖Fig.2.8, 當數位-類比轉換器進行數位碼011到100的轉換, 發生有111數位碼的暫存現象, 代表著一個極大值的存在而且會有很大的突波在輸出端出現, 而突波與信號會產生相依性會影響輸出信號的表現.

Fig.2.8 輸出突波

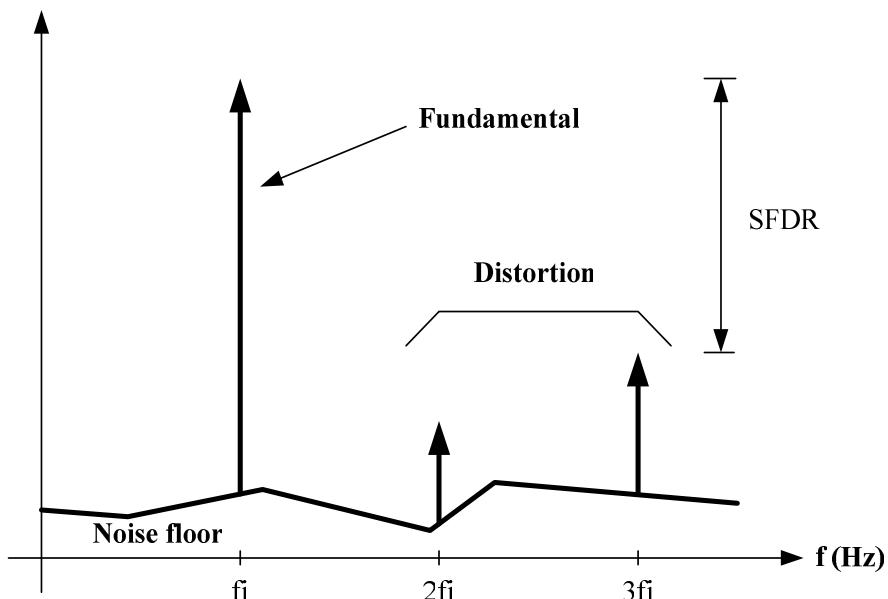

### 2.2.3 動態範圍

在通訊應用上，數位-類比轉換器在頻域上來描述其特性相當方便，可經由訊號雜訊比(Signal-to-Noise Ratio)或無雜波動態範圍(Spurious-Free Dynamic Range)的方式來量測得到。圖示如下

Fig.2.9 數位-類比轉換器輸出頻譜圖

## 訊號雜訊比 (Signal-to-Noise Ratio - SNR)

Signal-to-Noise Ratio (SNR) 就是訊號強度除以總雜訊強度，在一定的頻帶範圍內.

$$\text{SNR}(dB) = 10 * \log \left( \frac{\text{Signal Power}}{\text{Total Noise Power}} \right) \quad (2.8)$$

## 無雜波動態範圍 (Spurious Free Dynamic Range - SFDR)

Spurious Free Dynamic Range (SFDR) 是訊號強度除以最大的突波雜訊強度，在一定頻帶範圍內.

$$\text{SFDR}(dBc) = 10 * \log \left( \frac{\text{Signal Power}}{\text{Largest Spurious Power}} \right) \quad (2.9)$$

## 總諧波失真 (Total Harmonic Distortion - THD)

Total Harmonic Distortion (THD) 是總諧波失真強度除上基頻訊號強度，在一定頻帶範圍內.

$$\text{THD} = 10 * \log \left( \frac{\text{Total Harmonic Distortion Power}}{\text{Signal Power}} \right) \quad (2.10)$$

## 信號對雜訊及諧波失真比 (Signal-to-Noise and Distortion Ratio - SNDR)

Signal-to-Noise and Distortion ratio (SNDR) 是信號強度除上雜訊與諧波失真的總合強度相加，在一定頻帶範圍內.

$$\text{SNDR} = 10 * \log \left( \frac{\text{Signal Power}}{\text{Noise and Distortion Power}} \right) \quad (2.11)$$

## 2.3 二進位加權式數位-類比轉換器架構

### (Binary Weighted DAC Architecture)

利用一些具有某基準的元件組成具有二進位加權特性的數位-類比轉換器，其輸出信號可寫如下：

$$X_a(nT) = A_0 [b_0(nT) + 2 \cdot b_1(nT) + \cdots + 2^{N-1} \cdot b_{N-1}(nT)] + Aos \quad (2.12)$$

A0: 某基準元件值, T: 數位-類比轉換器的單位週期, Aos: 偏移量

此架構最大的優點是所使用到的數位解碼電路與切換器的數目是最少，而元件是以相加與乘法來運作，可以用電流源電晶體或電阻或電容來當其基本元件。

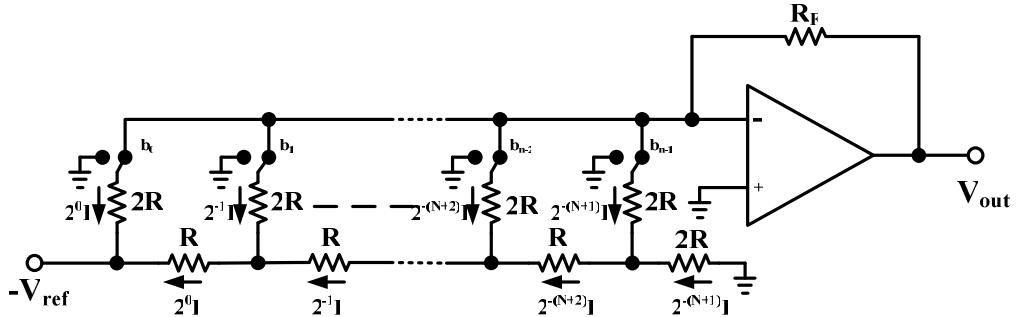

#### 2.3.1 R-2R 階梯式數位類比轉換器

##### (R-2R Ladder DAC)

使用階梯型的架構來只需用到一些少量不同大小的元件，如兩種電阻元件的大小  $R$  與  $2R$ ，相同的電流大小  $I$ ，單一大小的切換器，就可實現二進位加權的電流，與多少位元數  $N$  無關。

R-2R階梯型中的 $2R$ 是用兩等值的電阻  $R$ 來達到更好的元件匹配的特性，所以R-2R用較小的元件尺寸來達到較佳的準確度的特性。

$N$ 位元R-2R階梯型數位-類比轉換器如圖Fig.2.10，單看R-2R這部份的電路，

可看出

$$I = \frac{V_{ref}}{2R} \quad (2.13)$$

與

$$V_{out} = R_F \sum_{i=1}^N \frac{b_{i-1} I}{2^{i-1}} = V_{ref} \left( \frac{R_F}{R} \right) \sum_{i=1}^N \frac{b_{i-1}}{2^i} \quad (2.14)$$

此架構的缺點在於功率使用上效率不佳，因為電流經過電阻網路會損耗，而在製程上電阻非線性會引起的訊號失真，而且切換上的時間差易產生突波，內部節點的電壓AC變化會影響電流源，讓電流源的端點電壓會產生擾動。

Fig.2.10 N位元 R-2R 階梯式數位-類比轉換器

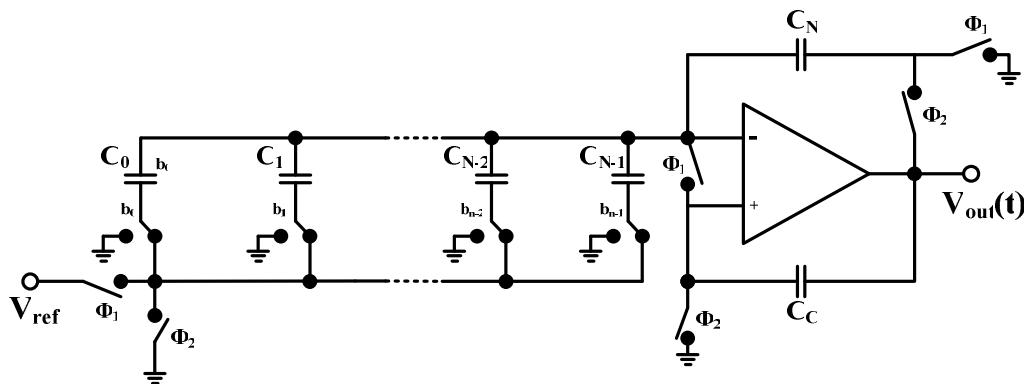

### 2.3.2 切換電容式電荷重分配數位-類比轉換器

(Charge Redistribution DAC)

切換電容式電荷重分配數位-類比轉換器電路是將電荷儲存在具有二進位權重的電容內來完成轉換。圖Fig.2.11是N位元轉換器的例子。權重的電容是以一群具有基本準位的單位電容所組成。

時間  $nT$  ( $\phi_1$ 時期)，位元  $b_i$  決定是那個二進位權重的電容需要從參考電壓充電。在此時期內電容  $C_N$  中的一邊金屬接腳連到地，而虛接地則是在運算放大器的輸入端，相當於沒有電荷存在  $C_N$  和  $q_N(nT) = 0$ 。電容  $C_C$  是用來補償偏移量。

時間  $nT$  二進位權重電容所得到的總電量如下，

$$q_T(nT) = V_{ref} \sum_{l=0}^{N-1} C_l \cdot b_l = V_{ref} \sum_{l=0}^{N-1} 2^l \cdot C \cdot b_l = V_{ref} \cdot C \cdot k(nT) \quad (2.15)$$

時間  $nT + T/2$ , ( $\phi_2$ 時期), 二進位權重電容電路放電, 所以電容兩端接腳一邊接直流端一邊虛接地, 所以電荷在地與  $C_N$  之間進行重分佈.  $C_N$  電荷重分佈所需要的穩定時間如下,

$$q_N(nT + \frac{1}{2}T) = C_N \cdot V_{out}(nt + T/2) \quad (2.16)$$

電荷轉換如下

$$q_N(nT + \frac{1}{2}T) = -q_T(nT) \quad (2.17)$$

使用 (2.15) and (2.16) in (2.17) 可得到

$$V_{out}(nt + T/2) = \frac{C}{C_N} \cdot k(nT) \cdot V_{ref} \quad (2.18)$$

此架構主要的好處在於對於偏移量的電壓值和有限增益的運算放大器不敏感. 此轉換器最大的限制會在電容匹配問題, 切換打開時的電阻值, 與運算放大器有限的頻寬.

Fig.2.11 N位元切換電容式電荷重分配數位-類比轉換器

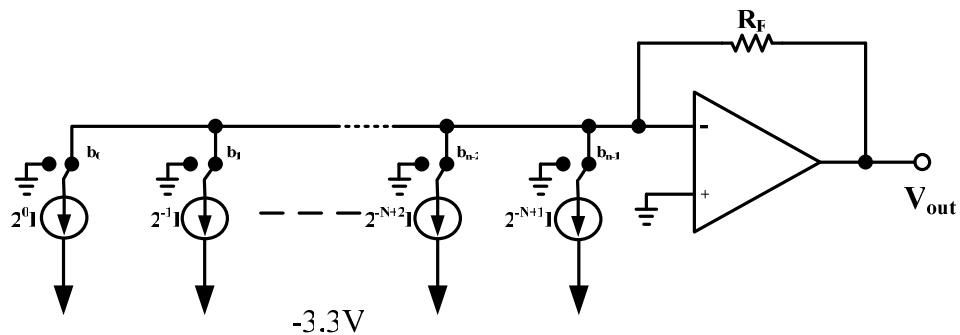

### 2.3.3 二進位碼加權電流式數位-類比轉換器

#### (Binary-Weighted Current-Mode DAC)

電流式數位-類比轉換器與電阻所組成的轉換器電路相似，而電流式數位-類比轉換器適用於高速應用上，而基本概念就是將電流切到地或是輸出端的方式來實現，圖示如下

Fig.2.12 N位元二進位碼加權電流切換式數位類比轉換器

將輸出電流經由  $R_f$  轉換成電壓，所以部份未使用的電流源電壓是維持在接地狀態。

切換電流的技術適合使用CMOS製程，因參考與總合的元件與切換器可以一併實現。電流源型式的數位-類比轉換器主要優勢在於10位元以下的電路可以有好的精確度與高速運作的目地，而其功率是集中在輸出端來轉換，所以功率效益可以有效提升。最主要不利的影響因素在於電流源電晶體之元件匹配的敏感度，突波和高位元下的電流源之輸出阻抗等處理。所以電流切換式數位-類比轉換器適用於高速與高解析度而其匹配度的改善需特別注意。

數位-類比轉換器設計上會採用混合型，設計電流源將權重高的部份使用溫度計碼而權重低的部份使用二進位碼來減少不匹配度的敏感性進而降低突波的影響度，以保有轉換器的單調性。

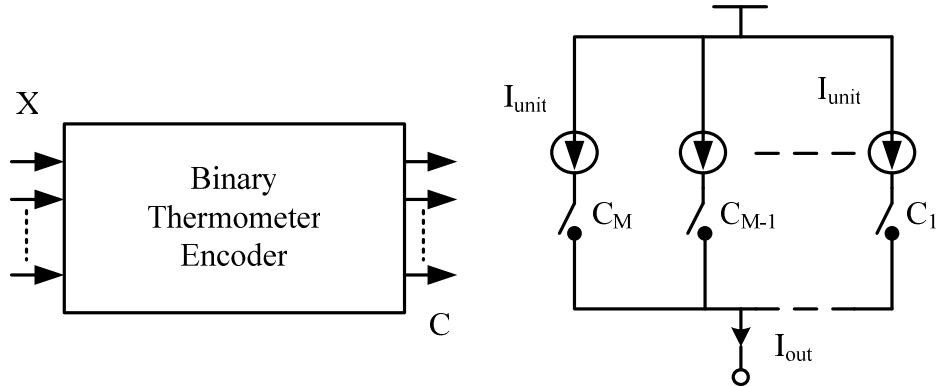

## 2.4 溫度計碼數位-類比轉換器架構

### (Thermometer Coded DAC Architecture)

溫度計碼數位-類比轉換器是使用相同權重的元件所組成. 而二進位的輸入碼會轉碼成溫度計碼, 以三位元的輸入碼為例, 列表於Table.2.1 通常N位元的二進位碼會有 $M = 2^N - 1$ 個溫度計碼.

時間  $nT$  時的類比輸出如下:

$$X_a = A_0 \cdot \sum_{i=1}^M C_i(nT) \quad (2.19)$$

$C_i = (nT) \in \{0,1\}, 1 \leq i \leq M$  代表溫度計碼所在的碼數.

| Decimal | Binary |       |       | Thermometer Code |       |       |       |       |       |       |   |

|---------|--------|-------|-------|------------------|-------|-------|-------|-------|-------|-------|---|

|         | $b_2$  | $b_1$ | $b_0$ | $c_7$            | $c_6$ | $c_5$ | $c_4$ | $c_3$ | $c_2$ | $c_1$ |   |

| 0       | 0      | 0     | 0     | 0                | 0     | 0     | 0     | 0     | 0     | 0     | 0 |

| 1       | 0      | 0     | 1     | 0                | 0     | 0     | 0     | 0     | 0     | 1     |   |

| 2       | 0      | 1     | 0     | 0                | 0     | 0     | 0     | 0     | 1     | 1     |   |

| 3       | 0      | 1     | 1     | 0                | 0     | 0     | 0     | 1     | 1     | 1     |   |

| 4       | 1      | 0     | 0     | 0                | 0     | 0     | 1     | 1     | 1     | 1     |   |

| 5       | 1      | 0     | 1     | 0                | 0     | 1     | 1     | 1     | 1     | 1     |   |

| 6       | 1      | 1     | 0     | 0                | 1     | 1     | 1     | 1     | 1     | 1     |   |

| 7       | 1      | 1     | 1     | 1                | 1     | 1     | 1     | 1     | 1     | 1     |   |

Table 2-1 十進位碼 , 二進位碼 , 溫度計碼對應表

用溫度計碼的數位-類比轉換器其基本準位元件全部是相同的權重，所以各別元件的匹配狀況相較於二進位加權式數位-類比轉換器而言簡單。全部的權重總合是 $2^N-1$ ，而溫度計碼的數位-類比轉換器轉換具有單調性，而DNL與INL相較於二進位加權式數位-類比轉換器有改善的效果。

Fig. 2.13 溫度計碼電流式數位-類比轉換器

Fig.2.13是溫度計碼電流式數位-類比轉換器中附帶二進位碼對溫度計碼的編碼器，數位電路將二進位碼 (X) 編碼成溫度計碼 (C)，而內部連接線的數目會非常龐大，而輸出的個數會成指數成長。意謂內部電路的佈局會更複雜。而編碼電路可用管線式組成，經由編碼器來控制其傳輸時間。

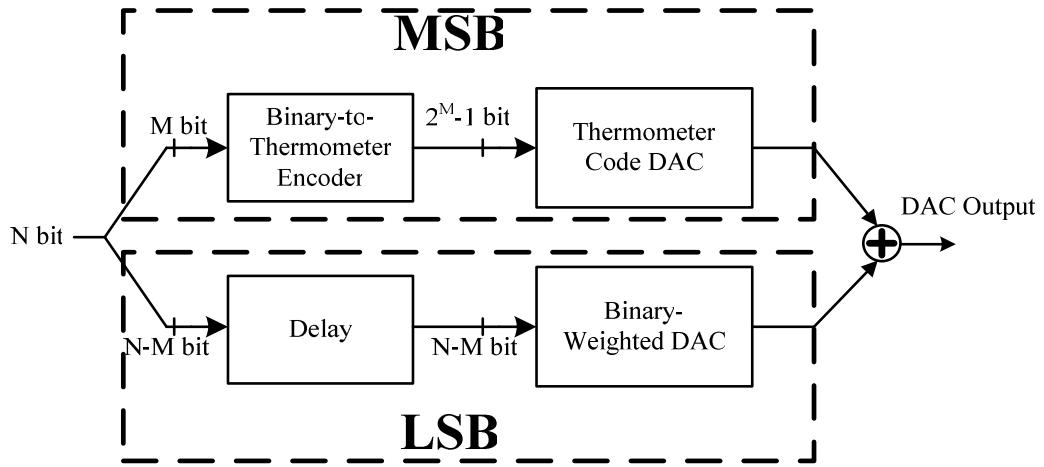

## 2.5 混合型數位-類比轉換器架構

### ( Hybrid DAC Architecture )

使用合併的技巧圖示如Fig.2.14在混合型的數位-類比轉換器的設計產生了不同結果。現在數位-類比轉換器普遍使用了混合型的設計因為它可以兼具二進位加權碼與溫度計碼兩種架構的優點。舉例而言，將權重高的前幾個MSB使用溫度計碼方法而權重低的幾個LSB使用二進位比例的技巧來完成。此設計可降低在MSB部份的突波並有更好的精確度，而在LSB部份的突波與精確度上的需求上可以降低，因LSB部份使用二進位碼加權式方法可節省下電路

的設計面積.

Fig.2.14 以M位元溫度解碼的N位元區段數位-類比轉換器

## 2.6 總結

本章節討論了數位-類比轉換器的基本原則，與其特性參數可用來描述數位-類比轉換器的規格。也介紹了不同種類的奈奎斯特率的數位-類比轉換器。

前面討論了不同種類的奈奎斯特率的數位-類比轉換器的優缺點，我們可以依據需求上的應用比如功率，速度，晶片大小等來選擇適合的架構。

### 電流式數位-類比轉換器的非理想效應

電流源式數位-類比轉換器是一種應用於高速與高解析度的普遍架構，它可直接驅動輸出電阻負載且不需要在輸出端放置高速運算放大器來做 I 轉 V 的角色。使用具有差動輸出型式的電流源數位-類比轉換器其因具有較低共模輸出雜訊並可消除二階諧波失真的好處。

本章第一節到第三節討論數位-類比轉換器第一類錯誤稱為靜態錯誤(Static Error)，它在靜態操作時存在，與數位-類比轉換器所操作的頻帶無關。第四節到地六節討論第二類錯誤稱為動態錯誤( Dynamic Error)，當數位-類比轉換器的操作頻率越來越高時，這類的錯誤將使轉換器的表現比在低頻操作時來的差[1][19]。

#### 3.1 電流源電晶體的不匹配性

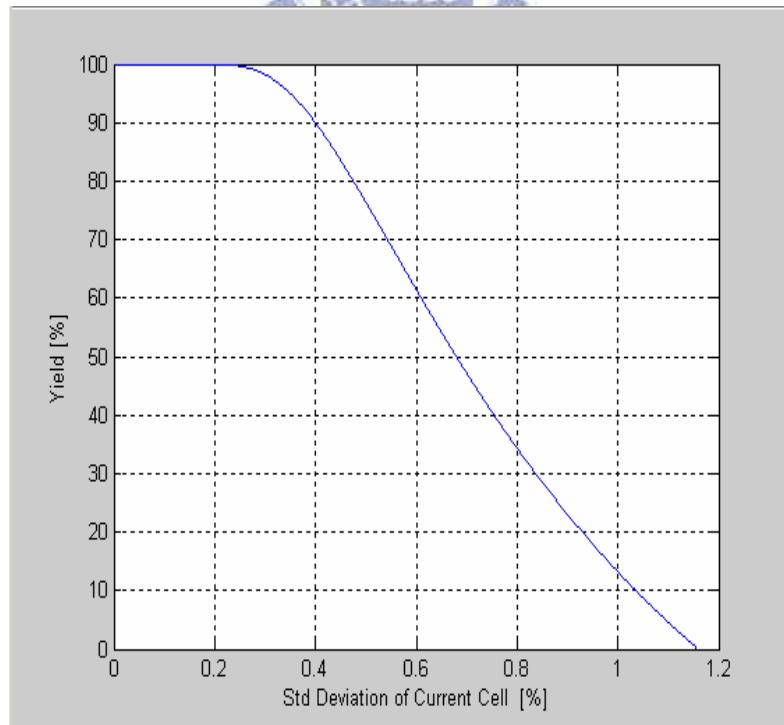

12 位元數位-類比轉換器準確性需求是數位輸入信號所控制的全部電流源 ( INL ) 積分非線性誤差量需低於 0.5LSB，依據此規格可得電流源相對準確性[6]。

$$\frac{\Delta I_{MSB}}{I_{MSB}} \leq \frac{0.5LSB}{2^{N-1} LSB} \quad (3-1)$$

N: 代表數位-類比轉換器的準確性。

當最高位元電流源 **MSB** 是由  $2^{N-1}$  個單位電流源 **I** 所並聯組成，可得到數位-類比轉換器積分非線性函數(INL)近似於是單位電流源具有隨機微量擾動特性下，讓  $2^{N-1}$  個電流源產生變化量的函數。

$$INL \approx \sqrt{2^{N-1}} \left( \frac{\sigma_I}{I} \right) LSB \quad (3-2)$$

在此  $\left( \frac{\sigma_I}{I} \right)$ ：單位電流源標準相對誤差

假設單位電流源是常態分佈，則INL-yield的設計即是伴隨電路  $INL < 1/2LSB$  所發生的機率  $\rho(INL < 1/2LSB)$ 。它變成了一項重要的規格[10]。

$$C = \text{inv\_norm}_{(0,1)}\left(0.75 + \left( \frac{INL\_yield}{4} \right)\right) \quad (3-3)$$

$$\left( \frac{\sigma_I}{I} \right) \leq \frac{1}{\sqrt{2^{N+2}} * C} \quad (3-4)$$

由上兩式可知  $INL\_yield$  與  $\left( \frac{\sigma_I}{I} \right)$  Unit Current Std Deviation 的關係圖如下：

Fig.3.1  $INL\_yield$  與  $\left( \frac{\sigma_I}{I} \right)$  Unit Current Std Deviation 的關係

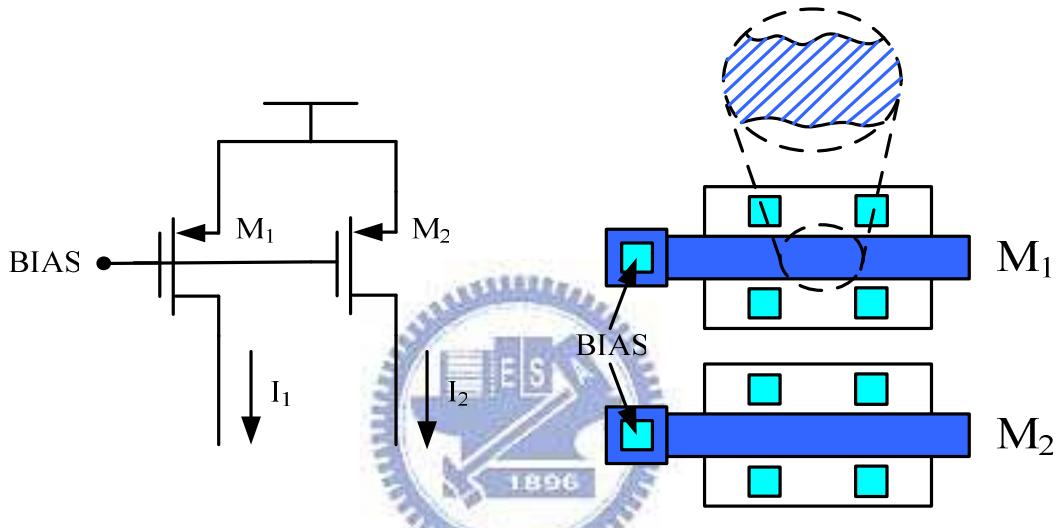

## 隨機錯誤 ( Random Error )

電流源隨機錯誤產生決定在於MOS電晶體的匹配的性質. 考慮兩個理想上完全相同的電流源如圖Fig.3.2 而這兩者電流源電晶體  $M_1$  與  $M_2$  幾何大小在每道步驟的製造過程中發生不確定性的有限隨機不匹配性, 造成電晶體  $M_1$  與  $M_2$  的輸出電流  $I_1$  和  $I_2$  有不匹配成份存在. 舉例來說, MOSFETs的閘極幾何大小經過製程處理後, 伴隨著隨機現象產生, 由顯微鏡觀察出在長度與寬度上發現有微小的變化量 [20].

Fig.3.2 理想的 MOS 電流源與製程中發生隨機不匹配性

Fig.3.2 假設理想狀況下  $M_1$  和  $M_2$  電晶體大小相同, 所以會有相等的 I-V 平方特性:

$$I_D = \frac{1}{2} \mu C_{ox} \frac{W}{L} (V_{GS} - V_T)^2 \quad (3-5)$$

我們微幅增加其寬度, 長度與  $V_{GS}$  來降低因不匹配性對於汲極電流的影響. 然而增大寬度會增加汲極對基板, 閘極對汲極電容和面積. 而加大長度需要更高的  $V_{GS}-V_T$  以得到相同的汲極電流, 但增加  $V_{GS}-V_T$  却限制了電流源電晶體  $M_1$  和  $M_2$  汲極端可用的汲極電壓空間. 所以需依據準確度、速度與輸出電壓擺幅等妥善考量後得到合理結果.

12 位元數位-類比轉換器準確性需求是數位輸入信號所控制下的全部電流源所造成的

(INL)積分非線性誤差量需低於 0.5LSB, 依據此規格可估算出電流源相對準確性[6].

$$\frac{\Delta I_{MSB}}{I_{MSB}} \leq \frac{0.5LSB}{2^{N-1} LSB} \quad (3-6)$$

N 代表數位-類比轉換器的準確性

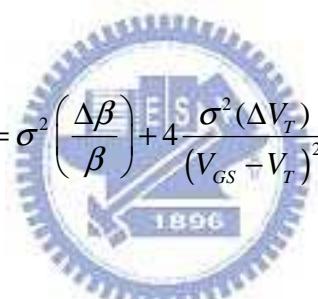

為了降低電流源不匹配性的影響，必需選出適合的電晶體大小。依據電晶體通道面積最小化與不匹配性參數估算方式如下[13]:

$$I_D = \frac{1}{2} \beta (V_{GS} - V_T)^2 \quad (3.7)$$

$\beta = \mu C_{ox} (W/L)$ , 相對應的電流源不匹配性如下:

$$\sigma^2 \left( \frac{\Delta I}{I} \right) = \sigma^2 \left( \frac{\Delta \beta}{\beta} \right) + 4 \frac{\sigma^2 (\Delta V_T)}{(V_{GS} - V_T)^2} \quad (3.8)$$

根據文獻[14], 可最小化的電流源尺寸相等於

$$(WL)_{\min} = \frac{\frac{1}{2} \left[ A_\beta^2 + \frac{4 A_{VT}^2}{(V_{GS} - V_T)^2} \right]}{\left( \frac{\sigma_I}{I} \right)^2} \quad (3.9)$$

在這裡:

$$\sigma^2 \left( \frac{\Delta \beta}{\beta} \right) = \frac{A_\beta}{WL} \quad (3.10)$$

$$\sigma^2 (\Delta V_T) = \frac{A_{VT}}{WL} \quad (3.11)$$

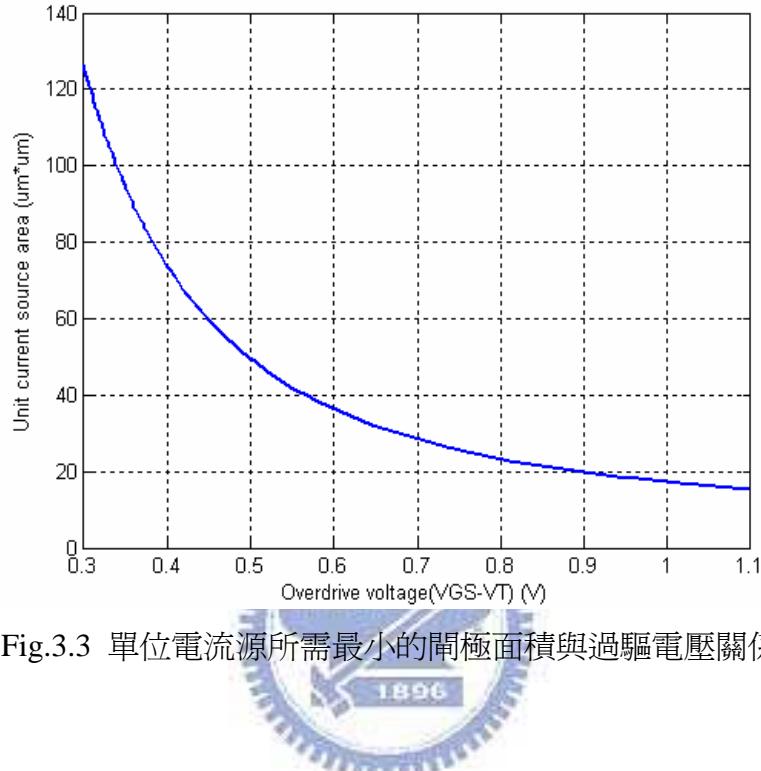

參數  $A_{VT}$  和  $A_\beta$  是製程參數，與製程有相依性，根據 (3-9)式可知所需要的電流源最小面積  $(WL)_{min}$  是過驅電壓  $(V_{GS}-V_T)$  和電流不匹配標準變化量  $(\sigma_1/I)$  的函數。故增加過驅電壓  $(V_{GS}-V_T)$  和電流不匹配標準變化量  $(\sigma_1/I)$  可降低所需電流源面積。

Fig.3.3 單位電流源所需最小的閘極面積與過驅電壓關係

### 3.2 電流源的有限輸出阻抗 (Finite Output Impedance of Current Source)

#### 系統錯誤 (Systematic Error)

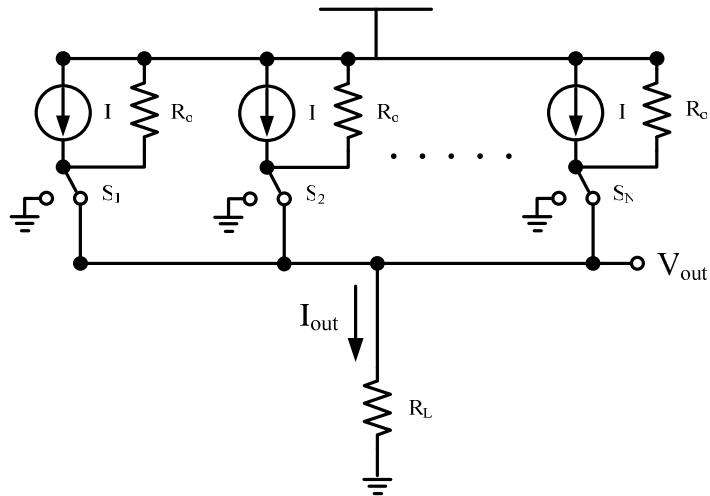

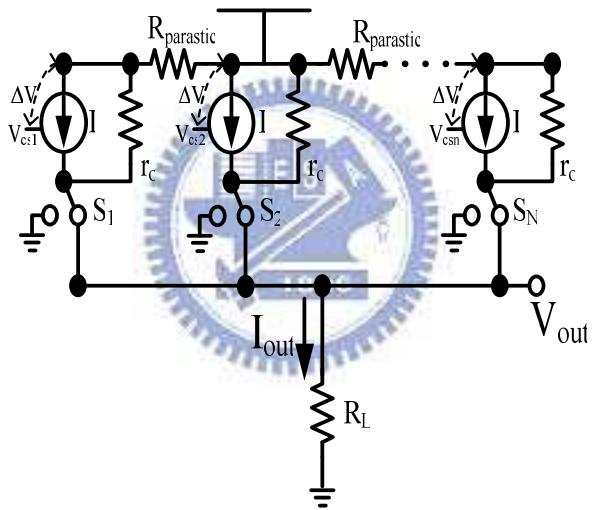

電流式數位-類比轉換器的電流源輸出阻抗，內部金屬連線與切換器的寄生阻抗都會影響其特性。而一個非理想的電流源具有一個有限的輸出阻抗，可被做出的模型是[23]如下。圖 Fig.3.4 是一組電流源陣列並包含有其電流源的輸出阻抗。以溫度計碼的結構為例，

Fig.3.4 有限輸出阻抗的電流源

$R_o$  代表每單一電流源的輸出阻抗，共有  $N$  個溫度計碼，其實際上的輸出電壓為：

$$V_{out,N} = NI \left( R_L \parallel \frac{R_o}{N} \right) \quad (3-12)$$

對於共有  $j$  個理想輸出電壓值為：

$$V_{out,j} = jI \left( R_L \parallel \frac{R_o}{N} \right) \quad (3-13)$$

而理想電壓與實際電壓差的結果就是 INL 的錯誤.

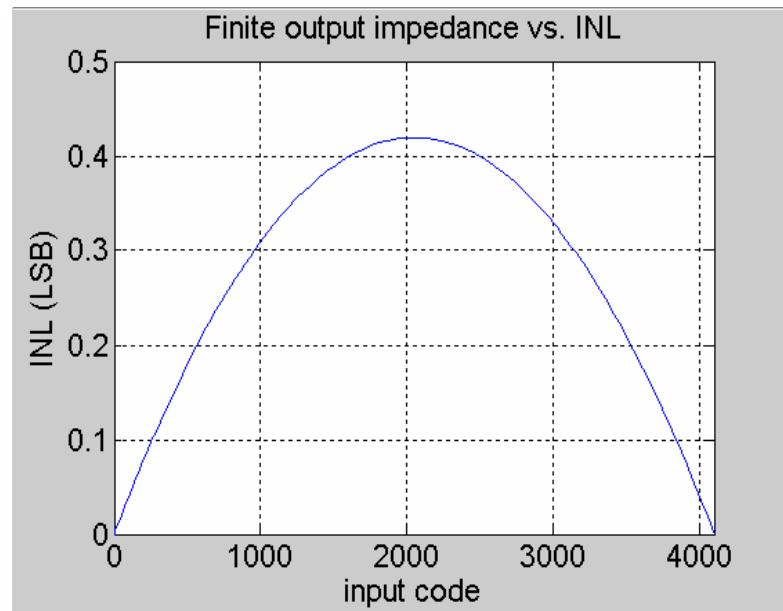

$$INL_j = jI \left( \frac{R_L R_o}{R_o + jR_L} - \frac{R_L R_o}{R_o + N R_L} \right) = \frac{IR_L^2}{R_o} j(N-j) \quad (3-14)$$

由上述的推導可得知隨著電流源輸出電阻上升可降低 INL 且 INL 最大值發生在數位輸入信號切到最高權重(MSB)時.

Fig.3.5 12 位元數位-類比轉換器有限輸出阻抗與 INL 關係

### 3.3 電流源陣列的不匹配性 ( Current Source Array Mismatch )

#### 梯度誤差 ( Graded Error )

- 邊界效應 ( Edge Effect )

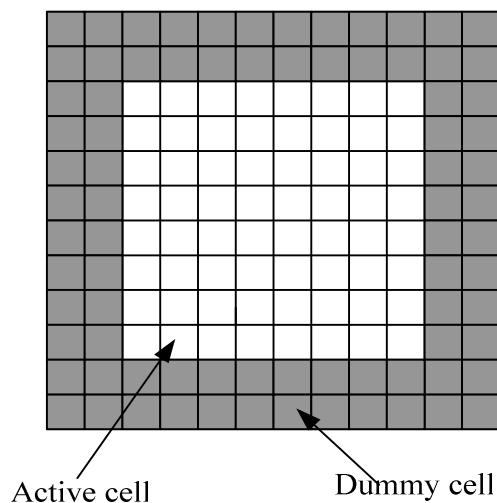

電流源電晶體陣列中，為了避免邊界的電流源電晶體因製成所造成的不匹配，會在電流源陣列的周圍，加入相仿但不具電流源作用的電晶體達到佈局上的匹配性。

Fig.3.6 電流源陣列與外圍等效相仿電流源

- 溫度梯度 ( Thermal Gradient )

- 製程相依性的錯誤 ( Technology Gradient ): 如參雜濃度梯度, 氧化層厚度梯度等.

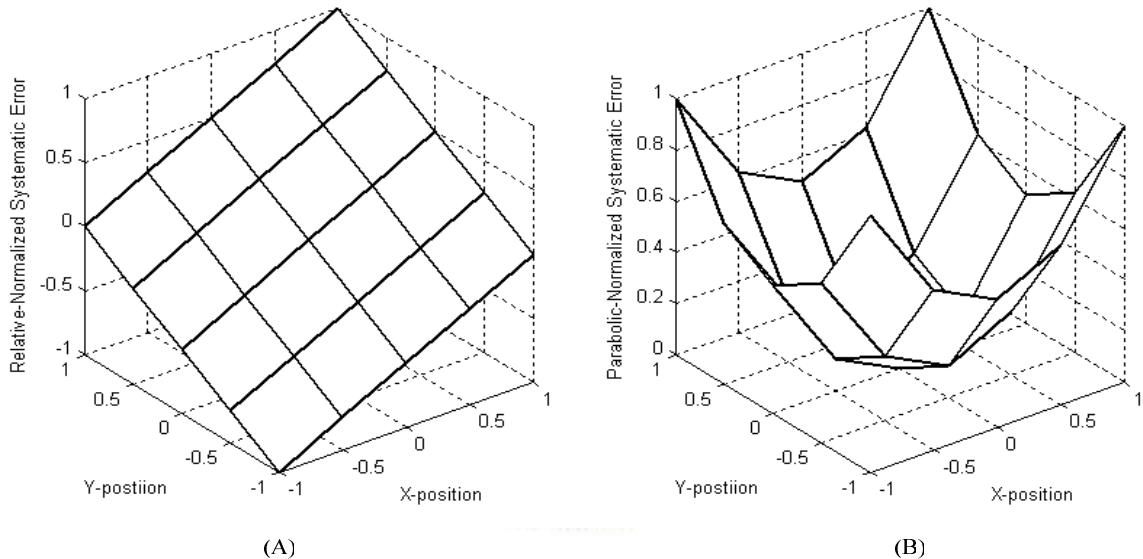

以上三者的梯度誤差在電流源陣列中使用泰勒級數展開來表示[8].

$$i_{\text{thermal,technology},\dots}(x, y) = b_0 + b_1 x + b_2 y + b_3 xy + b_4 x^2 + b_5 y^2 + \dots \quad (3.15)$$

- 電壓降 ( Voltage Drop )

Fig.3.7 金屬接地線存在寄生有限電阻.

金屬接地線存在有限寄生電阻情況下, 電流源電流流過時會造成電壓下降[8],

$$i_{\text{voltage drop}}(x) = \sqrt{g_m R_{\text{gnd}}} \frac{\cosh(\sqrt{g_m R_{\text{gnd}}} x)}{\sinh(\sqrt{g_m R_{\text{gnd}}})} \approx a_0 + a_1 x^2 + \dots \quad (3.16)$$

在此 \$x\$ 代表電流源沿著接地線的座標位置.

在高速高解析度的數位類比轉換器的應用上，梯度誤差會影響其線性度上的表現。

由(3.15) 與(3.16) 式中將整個電流源陣列看成一個單位且集中在同一區域內，則非理想效應的梯度誤差(First Order)與拋物線(Second Order)類型分佈在電流源陣列空間中，可得此區域內剩餘總誤差相當於是空間總誤差量如下式[6][8]：

$$\mathcal{E}_{\text{res}}(x, y) = \mathcal{E}_{\text{res}}^{(1)}(x, y) + \mathcal{E}_{\text{res}}^{(2)}(x, y) \quad (3.17)$$

Fig.3.8 (a) 線性誤差 (First Order) (b) 系統誤差 (Second Order) 在電流源陣列。

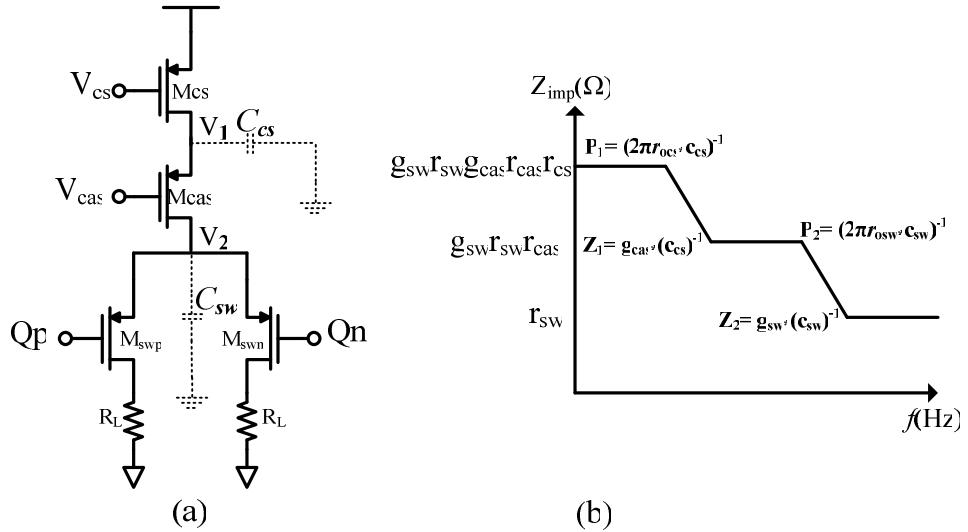

### 3.4 電流源開關電晶體組的非理想效應

Fig.3.9 (a)電流源開關閘極驅動器輸出波型 (b)高準位交錯點(c)低準位交錯點.

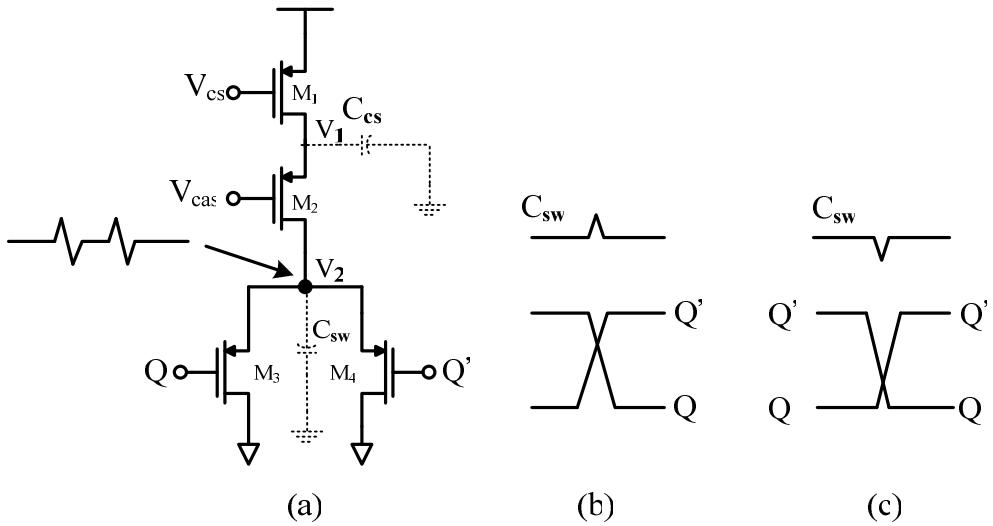

電流源切換的動態非理想性會影響到數位-類比轉換器的動態特性表現.

電流源內部其開關電晶體組其閘極端差動控制信號的交錯點為高準位，造成控制差動電流的開關電晶體組同時被關閉，則開關電晶體組其汲極端電壓  $V_2$  往  $VDD$  端拉升，造成輸出電流有瞬間被擾動現象，而  $V_2$  點電壓的擾動造成部份電流經由該點對基板的寄生電容中流出，影響到數位-類比轉換器的動態特性[19].

PMOS 電流源中開關電晶體組其閘極端的差動控制信號的交錯點電壓設計在低準位較為適合，保持開關電晶體組維持必定有其中之一在打開的狀態，讓寄生的電容  $C_{sw}$  不會產生放電效應[19].

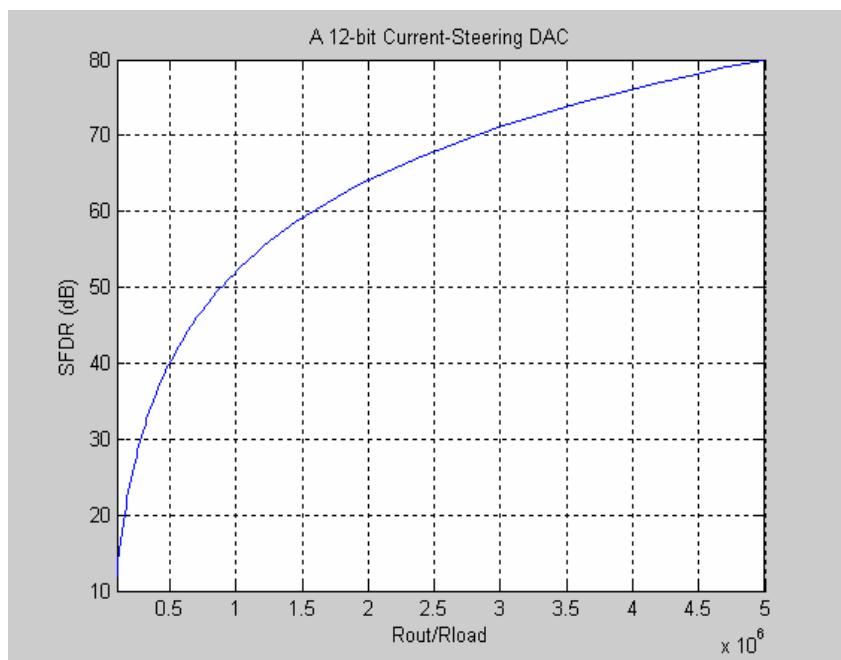

電流源的有限輸出阻抗除了影響到轉換器的靜態特性外，也影響了動態特性的表現. 參考前面圖 Fig.3.5 由動態特性的參數 SFDR 來看電流源有限輸出阻抗對於轉換器的影響.

經由 SFDR 式子計算得[1]

$$SFDR = \left\{ \frac{1+\rho \cdot K_{dc}}{\rho \cdot K_{ac}} + \left[ \sqrt{\left( \frac{1+\rho \cdot K_{dc}}{\rho \cdot K_{ac}} \right)} - 1 \right] \right\}^2 \quad (3-17)$$

而

$$K_{ac} = K_{dc} = \frac{2^N - 1}{2}, \quad \rho = \frac{R_{Load}}{R_o} \quad (3-18)$$

一般而言，差動輸入切換訊號可以消除掉二階諧波失真，且電流源輸出阻抗遠大於輸出負載的阻抗，所以  $\rho$  值非常大，則上式可以近似：

$$SFDR \approx 40 \log \left( \frac{1}{\rho} \right) - 12(N-2) \text{ dBc} \quad (3-19)$$

Fig.3.10, 在差動輸入訊號與差動輸出訊號的情況中，顯示輸出阻抗對於 SFDR 的影響。

電流源輸出阻抗下降時 SFDR 會降低，轉換器的動態特性也變差。

Fig. 3.10 不同的輸出阻抗下的 SFDR 動態特性

Fig.3.11 (a) 疊接式電流源電晶體 (b) 疊接式電流源在頻域阻抗特性

由Fig.3.11可得高頻時電流源阻抗不夠，數位-類比轉換器SFDR動態表現會失真。高頻操作下，尾端節點( $V_2$ )加堆疊電流源電晶體(Mcas)將零點與極點推向高頻，改善高頻輸出阻抗而增加頻域可操作範圍。佈局上將電流源電晶體(Mcs)與堆疊電流源電晶體(Mcas)分開並對其加入對中心對稱的技巧並不會大幅增加尾端寄生電容 $C_{sw}$ [16]。

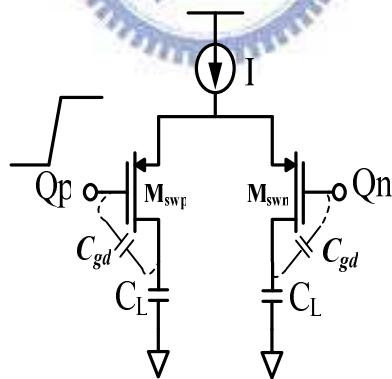

Fig.3.12 數位訊號電容耦合效應

電流源開關電晶體組閘極“控制訊號”切換時會經由該電晶體的寄生電容 $C_{gd}$ 直接耦合到輸出端，造成輸出端電壓會有跳動現象，而這些跳動會造成數位-類比轉換器動態特性下降。所以降低“控制訊號”擺幅電壓可縮小經由 $C_{gd}$ 耦合到輸出端之切換訊號所造成的雜訊量[19]。

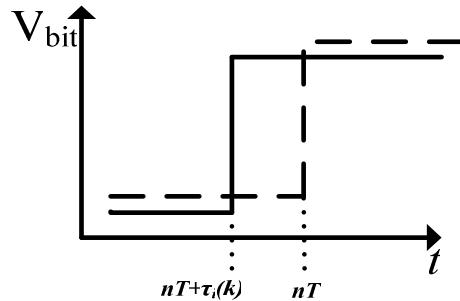

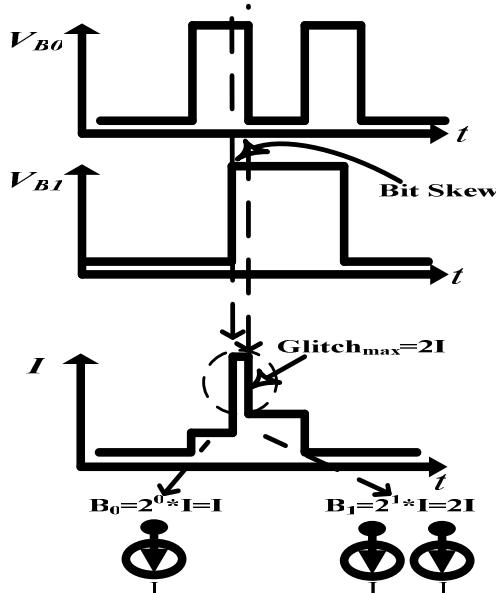

### 3.5 位元偏移與突波 ( Bit Skew and Glitches )

Fig.3.13 位元偏移非穩定時間錯誤

高速數位-類比轉換器的特性並非單考慮電流源最後的輸出值，尚需考量到每位元送達數位-類比轉換器後經數位電路轉換成數位碼Sample後經過時間的差異性。數位碼Sample對穩定時間有非常嚴格的要求，因穩定時間延遲會直接在輸出端造成電壓或是電流的突波後產生錯誤出現在動態特性上，所以必需保持各位元其切換時間的正確性[1]。

以二進位加權數位-類比轉換器為例：位元碼由01→10。而B0位元“01”發生偏移導致與B1位元“10”切換時間上有重疊，造成B2位元碼“11”短暫出現，造成電流源開關電晶體對的穩定時間發生錯誤，輸出端就有振幅2I大小的突波出現，影響數位-類比轉換器動態特性。圖示於Fig.3.14，所以採用適當比例區段的混合模式數位-類比轉換器設計縮小區段突波能量或脈衝。

Fig.3.14 位元偏移造成輸出端有突波現象

### 3.6 總結

設計高速與高解析度的數位-類比轉換器需注意因製程所產生的非理想效應，考量靜態特性與動態特性表現後決定出適合的電流源輸出阻抗，電流源電晶體面積，電流源開關電晶體組大小，數位控制訊號電壓擺幅。並注意數位輸入訊號到達電流源電晶體切換時間是否同步與突波等問題。

## 數位-類比轉換器電路設計

此章節先介紹所設計的 12 位元 500MHz 電流式數位-類比轉換器的架構，接著討論數位-類比轉換器的各區塊的電路設計。設計高速與高解析度數位-類比轉換器將靜態與動態特性和電路耗費的功率，面積與複雜度上做合理的評估後選擇出適合的架構。最後使用選取序列技巧與佈局方式來平衡之前第三章所提過系統和梯度誤差

## 4.1 數位-類比轉換器的架構

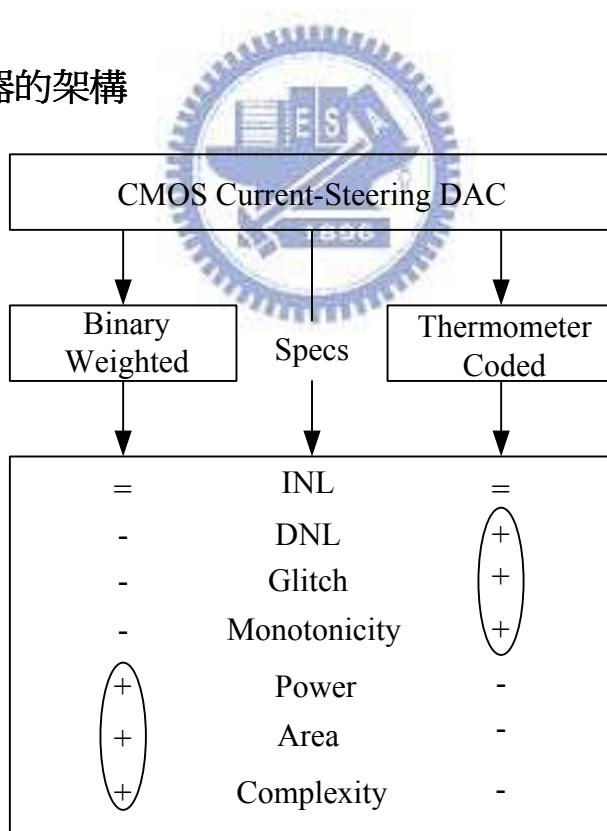

Fig.4.1 溫度計碼架構，二進位加權架構下數位-類比轉換器摘要[10]。

基於討論過不同架構的數位-類比轉換器，此研究選擇全溫度計碼架構的數位-類比轉換器，其架構上最大的優點在於沒有二進位加權碼的突波與無法確保單調性的問題。

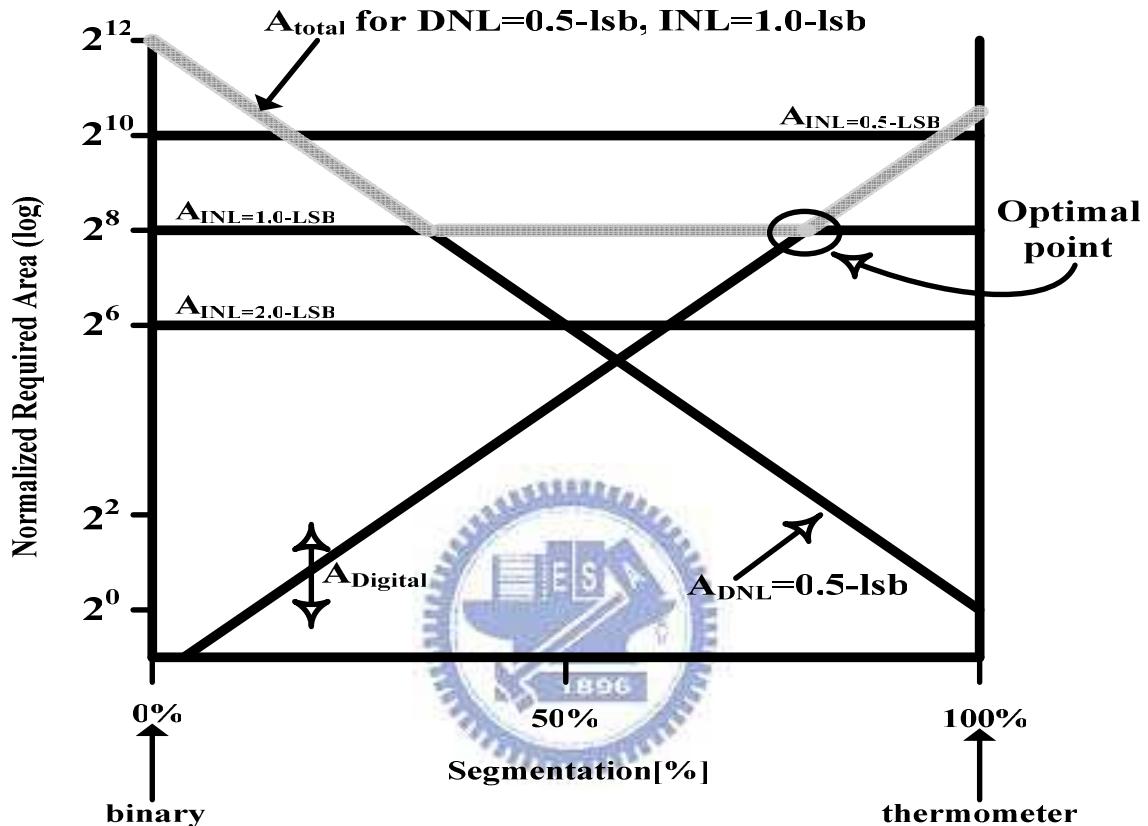

#### 4.1.1 區段式溫度計碼數位-類比轉換器

如何在 12 位元數位-類比轉換器取出分段，使佈局面積、突波問題、差動非線性誤差量、單調增加的特性上有最佳化的取捨，分析如下。參考[5]作者的方式將二進位加權碼與溫度計碼兩種數位-類比轉換器在相同的 DNL 與 INL 的條件做推算。

以 12 位元數位-類比轉換器為例，首先產生  $2^{12}$  個平均值為 1LSB，標準差為  $\sigma$  的電流源，做二進位碼與溫度計碼數位-類比轉換器模擬可得列表 Table4.1 如下：

| 需求               | 二進位加權碼                           | 溫度計碼                             |

|------------------|----------------------------------|----------------------------------|

| INL              | $0.5 * (\sqrt{2^{12}} * \sigma)$ | $0.5 * (\sqrt{2^{12}} * \sigma)$ |

| DNL              | $\sqrt{2^{12}} * \sigma$         | $\sigma$                         |

| Area(INL=0.5LSB) | $1024 * A_{unit}$                | $1024 * A_{unit}$                |

| Area(INL=1LSB)   | $256 * A_{unit}$                 | $256 * A_{unit}$                 |

| Area(DNL=0.5LSB) | $2^{12} * A_{unit}$              | $A_{unit}$                       |

Table 4.1 二進位碼與溫度計碼數位-類比轉換器面積的比較[5]

理論分析上來看在二進位加權碼與溫度計碼的 INL 值近似，而二進位加權碼的中間數位碼會造成很大的突波，所以在 DNL 特性上遠不及溫度計碼來的好。

所需 “類比面積  $\alpha \frac{1}{\sigma^2}$  ”，故定義  $A_{unit}$  是要達到 DNL=0.5LSB 時溫度計碼架構下所需要的最小面積，而二進位加權碼架構下所需類比面積為  $2^{12} * A_{unit}$ 。要達到 INL=0.5LSB 而言，兩種架構所需最小類比面積為  $1024 * A_{unit}$ 。綜合以上討論可知會把數位-類比轉換器劃分出兩個子部份並依溫度計碼的優點與最小面積特性下選擇出所需要區段的比例。Fig.4.2 常態分佈電流源面積與區段的百分比

要符合數位-類比轉換器靜態規格要求 DNL=0.5-lsb 與 INL=1-lsb 的條件，所以 MSB 部份的溫度計碼架構下的數位-類比轉換器選取 8 位元，LSB 部份的溫度計碼架構是 4 位元。

雖然 12 位元的數位-類比轉換器全部用溫度計碼架構設計有最好的 DNL，最佳化的單調性與將突波問題最小化，佈局的複雜度成指數上升，所需耗費的晶片面積太大，所以才會採用區段式溫度計碼架構的數位類比轉換器。

Fig.4.2 常態分佈電流源面積與區段的百分比[5]

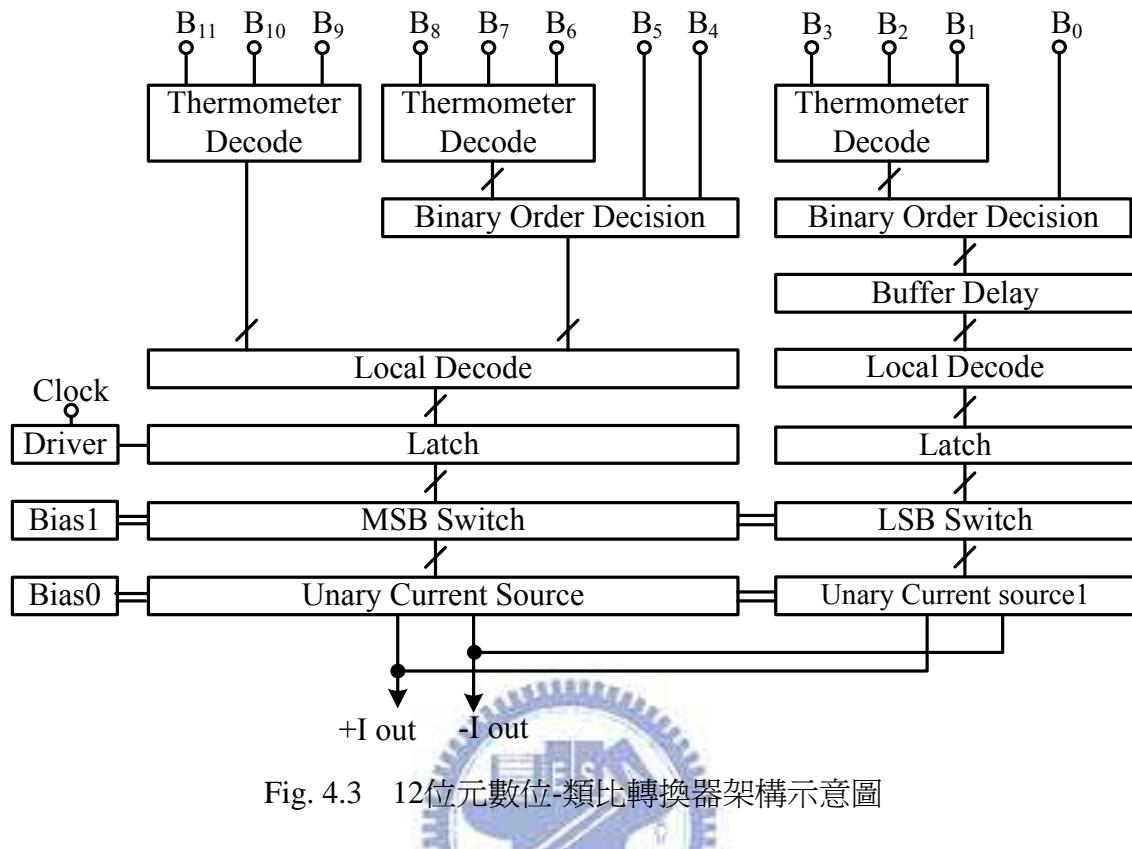

#### 4.1.2 12位元數位-類比轉換器架構圖

Fig. 4.3 12位元數位-類比轉換器架構示意圖

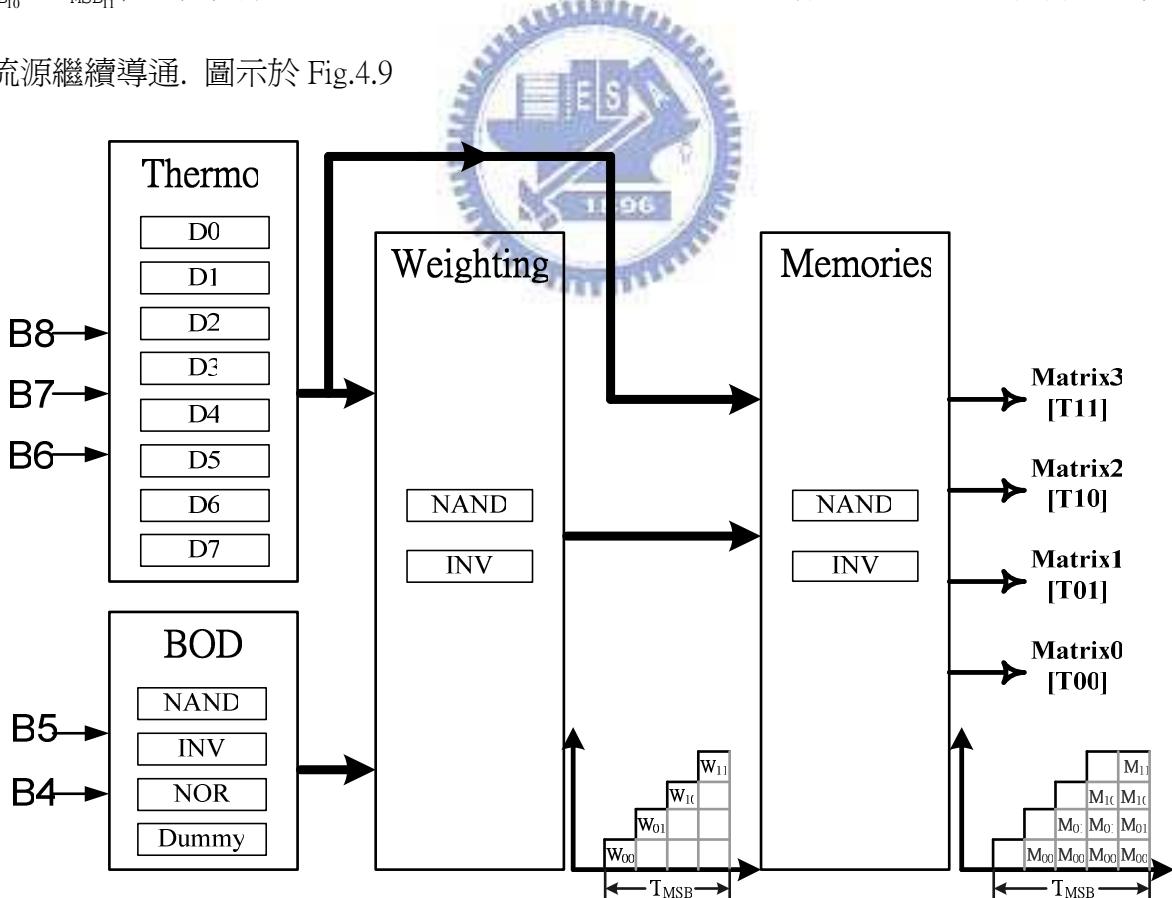

12位元500MHz電流式數位-類比轉換器此論文中所使用的架構如Fig.4.3, 此數位-類比轉換器電路使用以下一些電路方塊圖如下: 包含數位電路, 門閂器, 電流源和偏壓電路. 二位元輸入信號MSB部份 (B11~B9 & B8~B6)與LSB部份(B3~B1)經過第一層數位電路 (Thermometer decoder)轉碼為溫度計碼 D0~D7, 再與二元輸入信號MSB部份 (B5, B4) 與 LSB部份 (B0) 同步進入第二層數位電路(BODD) (Binary Order Decision Decode)做編碼後, 這些編碼過後的數位訊號會透過門閂器的控制, 驅動電流源內開關電晶體組同步化, 並且降低在電流源開關電晶體組汲極端電壓擾動量, 所以減少突波的效應. 電流源開關電晶體組的控制單位電流源電晶體矩陣產生差動電流到輸出端.

此數位-類比轉換器的子電路區塊功能會在下面章節做討論.

## 4.2 數位電路

在區段電流式數位-類比轉換器中，數位電路提供了將二位元數位輸入訊號轉碼為溫度計碼。設計數位電路的部份有以下問題要注意：

- 高速操作

- 電路複雜度

- 總消耗功率

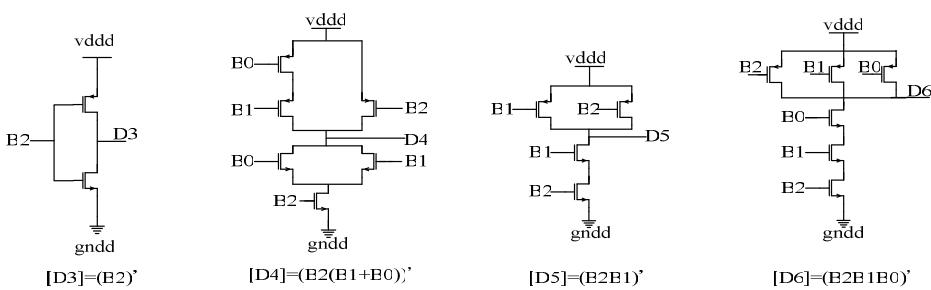

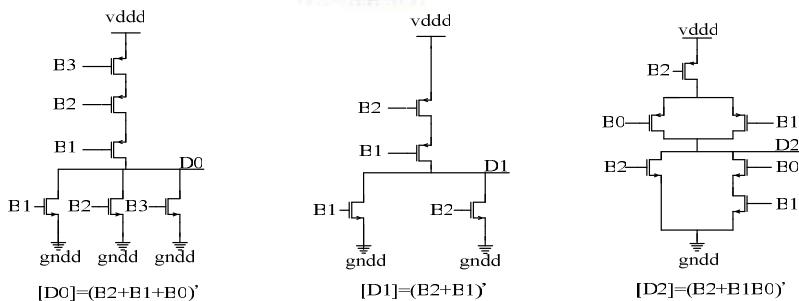

### 4.2.1 溫度計解碼器

高速應用上數位-類比轉換器會因所選擇編碼器的種類而限制其轉換速率。而矩陣行列式選取碼的方法是簡單且可實現於高速轉換中。

而實現矩陣行列式選取碼的方法可用四組每組一對的3-to-8溫度計解碼器來實現控制4組8\*8矩陣共255個電流源電晶體。其中控制列的3-to-8的溫度計解碼器決定了那一列要導通(Fig.4.4 圖-灰階外框示意圖)，而控制行的3-to-8的溫度計碼器決定了該列內那個行的電流源電流要打開。(Fig.4.4 圖-叉叉示意圖)

Fig.4.4 8\*8矩陣式門門器排列與一對3-to-8溫度計解碼器關係圖

而數位電路部份是用反溫度計碼的方式控制電流源輸出. 真值表列於Table 4.2, 而布林函數來表示於Table 4.3, 並用組合電路來實現如Fig.4.5圖示.

| Decimal | B2 | B1 | B0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

|---------|----|----|----|----|----|----|----|----|----|----|

| 0       | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 1       | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  |

| 2       | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 0  |

| 3       | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  |

| 4       | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| 5       | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  |

| 6       | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 7       | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Table 4.2 3-to-8 溫度計碼真值表

|    |                         |    |                      |    |                        |    |                   |

|----|-------------------------|----|----------------------|----|------------------------|----|-------------------|

| D1 | $(\overline{B2+B1+B0})$ | D2 | $(\overline{B2+B1})$ | D3 | $(\overline{B2+B1B0})$ | D4 | $(\overline{B2})$ |

| D5 | $\overline{B2(B1+B0)}$  | D6 | $(\overline{B2B1})$  | D7 | $(\overline{B2B1B0})$  |    |                   |

Table 4.3 布林函數表示式

Fig.4.5 溫度計解碼器

#### 4.2.2 二元順序判別電路(Binary Order Decision Circuit)

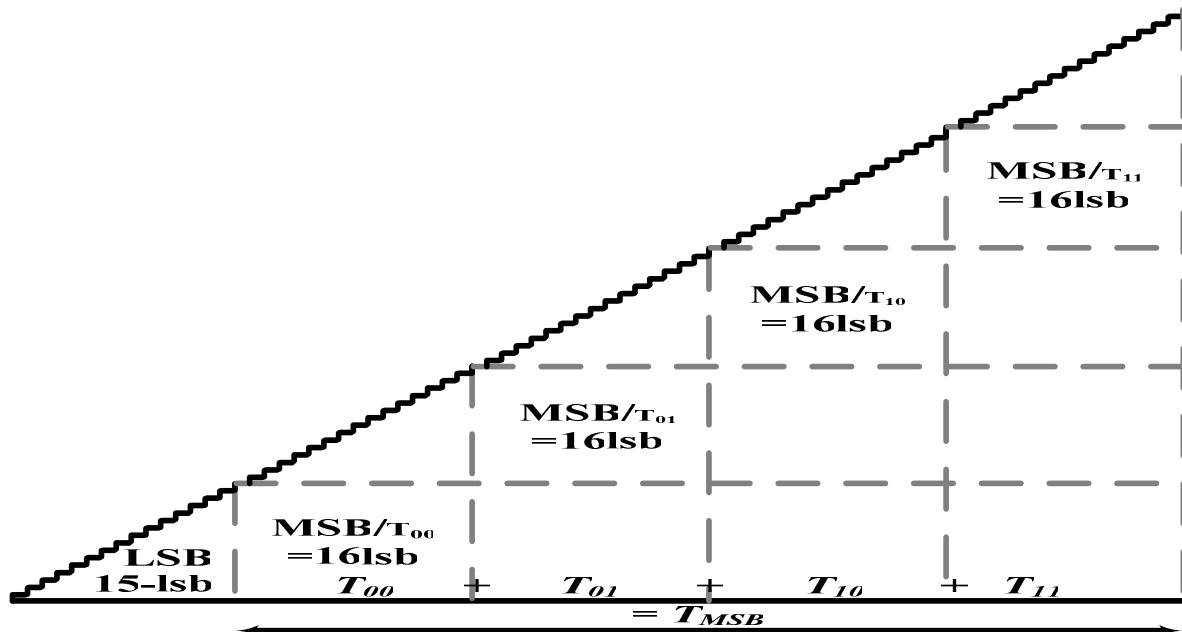

兩個子電路是全溫度計碼電流式數位-類比轉換器, 其 MSB 部份的數位-類比轉換器由四組相同的行與列 3-to-8 溫度計解碼器會同步解碼出 64 個數位信號, 意謂有 64 個 MSB 電流源, 其電流源有四個基本單位電流源分散在四個電流源矩陣內, 以  $x_{axis} - y_{axis}$  為中心做鏡像對稱的 common central 排列. 設計一個 MSB 電流源為 64-lsb 而 LSB 電流源為 1-lsb. LSB 部份的電流源總合為 15-lsb, 而一個 MSB 電流源的基本單位電流源為 16-lsb.

MSB 部份和 LSB 部份這兩個子數位-類比轉換器的電流源配合方式如下:

$$[(16*4)*64 - 16 = 4080\text{-lsb}] + 15\text{-lsb} = 4095\text{-lsb}$$

Fig.4.6 MSB 電流源和 LSB 電流源打開的配合關係圖. 其中

(16\*4)的意義: 16-lsb 為 MSB 的基本單位電流源 x 把該 MSB 電流源週期經過加權後,

由四個不同權重的子週期所組合而成

64 的意義: 64 組 MSB 電流源

-16-lsb 的意義: 有一個 MSB 電流源只包含有三個基本單位電流源

15-lsb 的意義: 15 組 LSB 電流源

Fig.4.6 MSB 電流源和 LSB 電流源打開的配合關係圖

此二元順序判別(BOD)電路設計的目地在於因 MSB 電流源切割為四個基本單位電流源放在四個象限內形成四組  $8 \times 8$  矩陣，具有讓一個 MSB 電流源的四個基本單位電流源於一個 MSB 電流源週期內有依序打開的功能。而且依照行與列 3-to-8 溫度計解碼器所形成的 64 個數位碼的順序輸入到門閂電路依序打開 MSB 的基本單位電流源完成數位-到類比的轉換。特點是一次只打開 MSB 電流源中的一個基本單位電流源 16-lsb，所產生的突波能量不大，對數位-類比轉換器的在輸出端的動態特性不會產生影響。

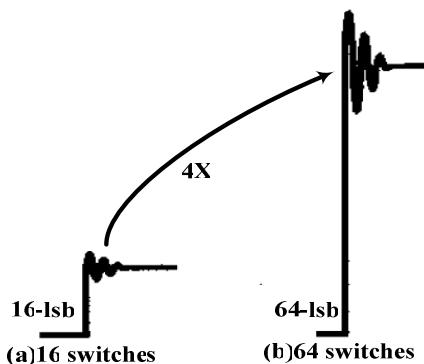

避免像[6]內將 12 位元電流式數位-類比轉換器中 8bit 拆成(B11~B6)-溫度計碼型式 MSB 部份與(B5~B4)二進位碼型式 ULSB 的部份做(6+2)位元組合，由 ULSB 部份 B5B4 位元由 11->00 其最大電流源是 48-lsb 關閉而 B11~B6 打開 MSB 電流源 64-lsb，進行大電流切換會造成很大的突波，而影響到數位-類比轉換器輸出端動態特性。圖示 Fig4.7 參考[5]

Fig.4.7 相比較於(a)12bit DAC(6bit-溫度計碼)+(2bit-BOD 電路)與

(b)12bit DAC(6bit-溫度計碼)+(2bit-二進位碼)-Ref[6]在輸出端造成突波大小示意圖

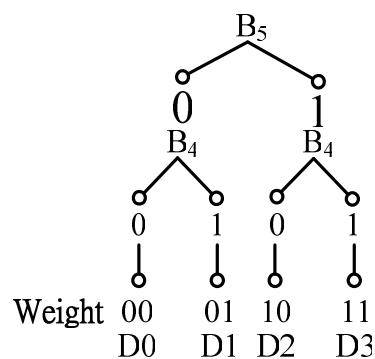

Fig. 4.8 二元順序判別(BOD)規則

取 B5~B4 來做二元順序判別(BOD)電路的輸入，用反溫度計碼方式實現.在 Table 4.4

| Wight | B5 | B4 | D4 | D3 | D2 | D1 |

|-------|----|----|----|----|----|----|

| 0     | 0  | 0  | 1  | 1  | 1  | 1  |

| 1     | 0  | 1  | 1  | 1  | 1  | 0  |

| 2     | 1  | 0  | 1  | 1  | 0  | 0  |

| 3     | 1  | 1  | 1  | 0  | 0  | 0  |

Table 4.4 2-to-4 溫度計碼真值表

所以二元順序判別(BOD)電路，其動作一是(BOD): 把打開一個 MSB 電流源所進行的時間當作基本週期  $T_{MSB}$ ，由二元順序判別(BOD)電路分別產生四權重  $D_{00}$ 、 $D_{01}$ 、 $D_{10}$  &  $D_{11}$ . 動作二 Weighting: 即是對該 MSB 電流源的基本週期做加權動作後形成四個子週期  $T_{MSB_{00}}$ 、 $T_{MSB_{01}}$ 、 $T_{MSB_{10}}$  &  $T_{MSB_{11}}$ ，然後依序 MSB 電流源的四基本單位電流源. 動作三 Memories: 維持打開後 MSB 電流源繼續導通. 圖示於 Fig.4.9

$W_{00}$ 代表:英文字母-Weight/下標-子週期

$M_{00}$ 代表:英文字母-Momery/下標-子週期

Fig.4.9 二元順序判別(BOD)電路與方塊示意圖

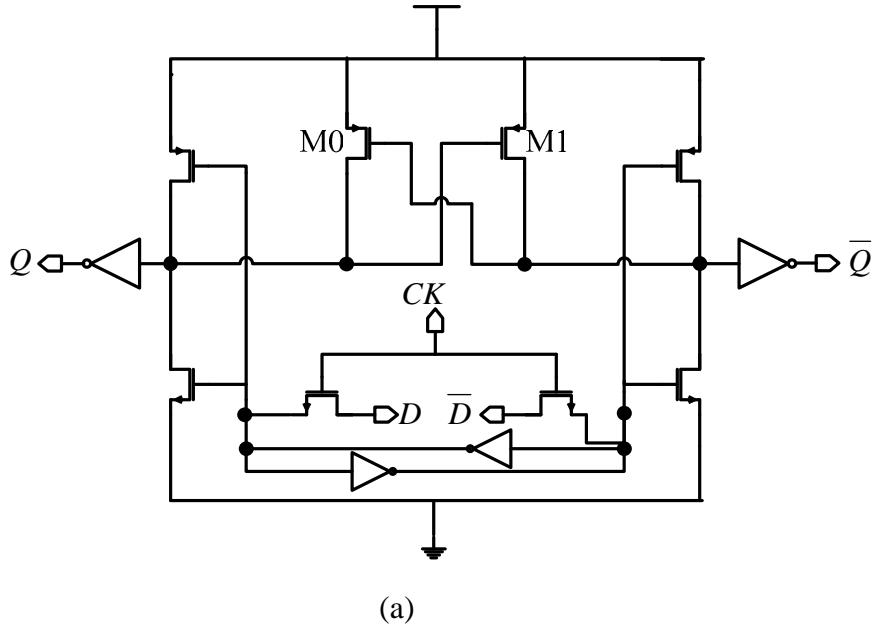

### 4.2.3 高速門閂電路(High speed latch)

電流式數位-類比轉換器的動態特性下降，由以下與電流源切換相關因素所造成。這些重要因素會造成動態特性上限制如下：

- 電流源開關電晶體組的控制訊號有不理想非同步的情況。

- 電流源開關電晶體組同時瞬間關閉造成電流源電晶體的汲極端偏壓擾動。

- 控制信號經過電流源開關電晶體組的寄生電容 $C_{gd}$ 耦合影響到輸出端。

爲了降低以上三種效應，需用使具有設計同步化的門閂驅動器。高速低突波的門閂驅動器圖示於Fig.4.10(a)。它能提供兩個具有互補性質的訊號給電流源開關電晶體對使用。

爲了解決傳統型門閂驅動器造成電流源開關電晶體對瞬間同時關閉，讓電流源疊接電晶體端的寄生電容被充電。而電流源開關電晶體組要回到正常操作則要經過線性區才能回到飽合區。不只造成電流源的操作速度下降也在輸出端造成突波[19]。

爲了解決這個問題，此門閂驅動器是用具有上升/下降的時間特性。爲了使輸入端下降訊號進來時輸出端可瞬間改變，額外增加PMOS電晶體M0與M1並聯且各自與電路的最上層交錯相接。把( $\mu_n / \mu_p$ )拿來找到設計這PMOS電晶體M0與M1與回授路徑中一對反相器內的PMOS電晶體達到適當的比例，則上升時間速度低於下降時間速度，就可提供輸出控制訊號的具低交錯點的特性，如圖示Fig.4.10(b)。

取樣時間信號CK可提供當地的電流源開關電晶體組同步化的閘極控制訊號。數位電路的電壓源vdd可低於類比電路的電壓源vdda 來降低其輸出閘極控制訊號擺幅。而回授路徑上一對反相器可以移除取樣時間造成的穿透效應並且對同步的輸入訊號有穩定的功用[10]。

(a)

Fig.4.10 (a) 動態門閂器電路圖 (b) 輸出訊號

### 4.3 類比電路

產生準確的電流有以下幾點的考量. 首先要注意不同電流源因製程所造成不匹配性, 所以要設計適當的電流源電晶體大小來降低此效應. 其次需要足夠大的電流源輸出阻抗以得到好的靜特性表現. 最後需設計一個提供電流源有穩定偏壓的偏壓電路. 電路上的設計與考量會在以下小節描述

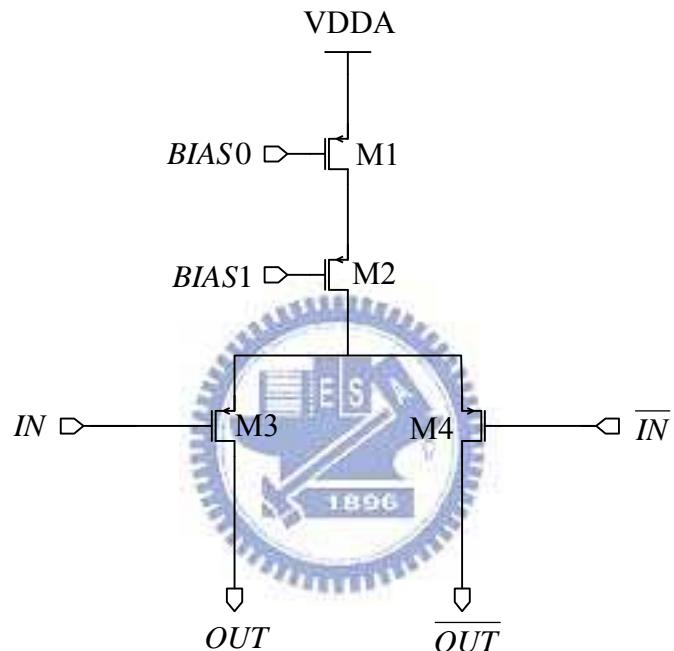

### 4.3.1 切換單位電流源設計

使用PMOS電晶體當電流源有兩大好處：其一為PMOS元件坐落在Nwell井內有效隔絕由基板而來的雜訊。其二是PMOS比NMOS有較少的閃爍雜訊。電路用疊接和開關電晶體組成的電流源圖示於Fig.4.11. 其電流源的輸出阻抗  $r_{sw_{M3}} g_{sw_{M3}} r_{cas_{M2}} g_{cas_{M2}} r_{cs_{M1}}$  足夠大到來維持數位-類比轉換器的靜態與動態特性。

Fig.4.11 疊接式和開關電晶體組成的電流源

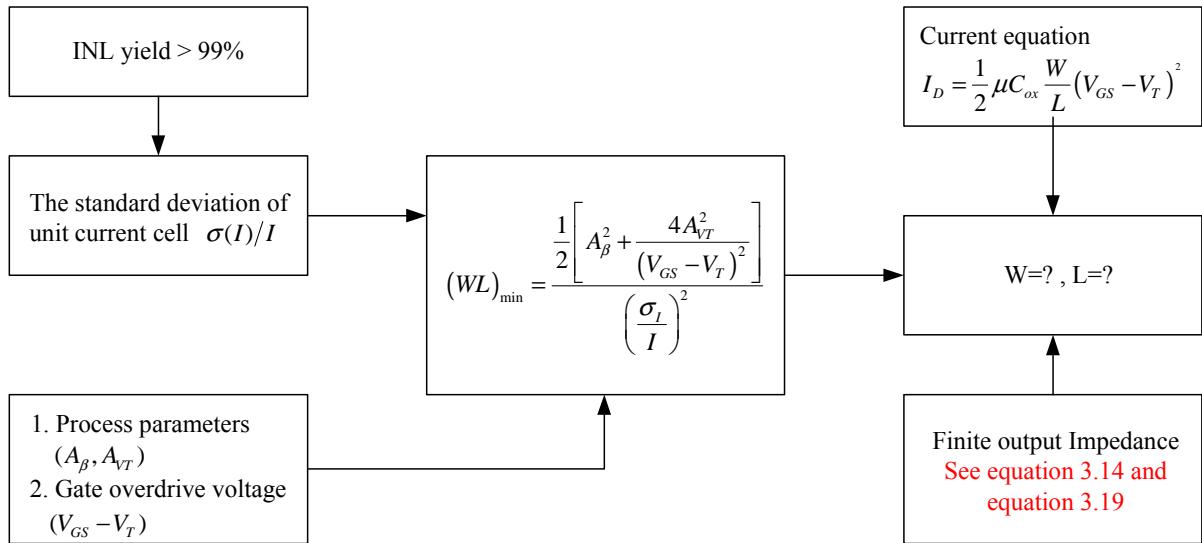

接下來看如何設計合適的電流源電晶體大小，設計流程如在圖Fig.4.12. 決定適合的電流源電晶體大小需要有INL\_yield, 製程參數( $A_\beta$  and  $A_{VT}$ ),與閘極過驅電壓( $V_{GS}-V_T$ ). 而數位-類比轉換器其INL與DNL的規格參數需一併列入考量。

Fig.4.12 電流源的設計流程[24]

前面Ch4.1 提到經過最佳化後的區段成8-4的電流式數位-類比轉換器電路，由兩個子數位-類比全溫度計碼轉換器組合而成。所以使用到兩種不同的單位電流源。MSB部份的單位電流源是 $2^4 = 16$ -lsb而LSB部份的單位電流源則使用 $2^0 = 1$ -lsb。

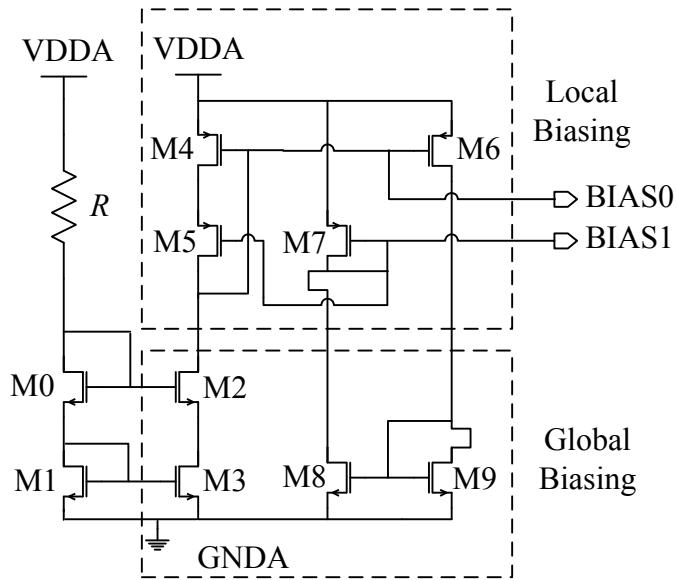

#### 4.3.2 參考偏壓電流源電路 ( Reference Current Generation )

Fig.4.13圖此電路用來提供電流源電晶體的偏壓，需外接電阻R來產生參考電流。NMOS的偏壓部份標記為“提供全部偏壓(global biasing)”，而PMOS的偏壓部份則提供了“局部偏壓(local biasing)”。疊接鏡像電流源用來降低短通道效應與增加輸出端的阻抗，但卻限制了訊號的擺幅。所以“局部偏壓-(local biasing)”使用寬擺幅疊接鏡像電流源來減少限制[24]。

Fig.4.13 偏壓電路圖

#### 4.4 選擇序列最佳化 (Selecting Sequence)

參考[12], Fig.4.14 圖示看 MSB 部份 6 位元 B11~B6 輸入於 3-to-8 行與列溫度計解碼器,

在經過由 B5~B4 所控制的 BOD 編碼器後產生 64 個數位碼共有四組. 每組內其 64 個數位碼控制下面的電流源  $8 \times 8$  矩陣的佈局. 以每列為一個組(定義為列週期), 其內有八個行為單位(定義為有八個行為單位電流源), 所以  $8 \times 8$  矩陣內共有八個組. 而以  $y_{axis}$  為中心做鏡像對稱的這兩列週期算成一個群圖示於 Fig.4.15. 所以行與列的角色互換仍可相等.

|           |           |           |           |           |           |           |           |           |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| <b>Y8</b> | 1         | 7         | 5         | 3         | 0         | 6         | 4         | 2         |

| <b>Y7</b> | 7         | 0         | 2         | 4         | 6         | 1         | 3         | 5         |

| <b>Y6</b> | 5         | 3         | 1         | 6         | 4         | 2         | 0         | 7         |

| <b>Y5</b> | 2         | 4         | 6         | 0         | 3         | 5         | 7         | 1         |

| <b>Y4</b> | 0         | 6         | 4         | 2         | 1         | 7         | 5         | 3         |

| <b>Y3</b> | 6         | 1         | 3         | 5         | 7         | 0         | 2         | 4         |

| <b>Y2</b> | 4         | 2         | 0         | 7         | 5         | 3         | 1         | 6         |

| <b>Y1</b> | 3         | 5         | 7         | 1         | 2         | 4         | 6         | 0         |

|           | <b>X1</b> | <b>X2</b> | <b>X3</b> | <b>X4</b> | <b>X5</b> | <b>X6</b> | <b>X7</b> | <b>X8</b> |

Fig.4.14 圖示 A 為(8 個組週期)  $\times$  (8 個行為單位電流源)的矩陣

參考[12], Fig.4.15 圖示以兩個  $8 \times 8$  矩陣且以  $y_{axis}$  為中心呈對稱且做 common central 排列, 優點一可消除一階線性梯度誤差. 因為一列 “Y8” 此列週期內, 會有 “-X6” 與 “X6” 這兩行單位電流源皆對稱於  $y_{axis}$  且同時被打開, 他們所造成的梯度誤差量總合就是 0. Fig.4.16 圖內將兩相同組週期以  $x_{axis} - y_{axis}$  為中心呈對稱且做 common central 排列, 所以任意一階線性誤差均可拆解為對  $x_{axis}$  與對  $y_{axis}$  的梯度誤差量做線性相加, 其總合為 0.

Fig.4.15 圖示 B 為兩個圖示 A 以  $y_{axis}$  為中心做鏡像對稱

優點二可以消除二階曲線非線性誤差: 參看圖 Fig.4.15

其一為系統誤差為:

$$\epsilon_{unit} = \sum_{i=1}^{16} (a_{x\_coordinate\_i}^2 + b_{y\_coordinate\_i}^2) \quad 4.1)$$

單位電流源的系統誤差量可以拆解為在行與列這兩種成份的誤差量, 所以

對  $y_{axis}$  對稱的兩個群而言其誤差量總合在重寫為:

$$\epsilon_{unit} = a_{x-8}^2 + \dots + a_{x-1}^2 + \dots + a_{x8}^2 + 2b_{y1}^2 + \dots + 2b_{y8}^2 \quad 4.2)$$

對於全部的單位電流源而言為其常數補償量, 並不影響線性度, 所以二次誤差消除.

其二為若二次誤差量發生在矩陣陣列對  $x_{axis} - y_{axis}$  發生旋轉現象時,

$$\epsilon(x', y') = a_{x'}^2 + b_{y'}^2. \quad (4.3)$$

$$x' = x \cos(\alpha) + y \sin(\alpha) \quad (4.4)$$

$$y' = -x \sin(\alpha) + y \cos(\alpha) \quad (4.5)$$

經過轉換後可得

$$\begin{aligned}\varepsilon(x, y) = & a(x^2 \cos^2(\alpha) + y^2 \sin^2(\alpha) + 2xy \cos(\alpha) \sin(\alpha)) \\ & + b(x^2 \sin^2(\alpha) + y^2 \cos^2(\alpha) - 2xy \sin(\alpha) \cos(\alpha))\end{aligned}\quad (4.6)$$

$x^2$  &  $y^2$  的項同式子(4.2)其總合為常數補償量不影響線性度, 而  $xy$  的項基於鏡像對稱的特性, 一個群內相同列週期的兩個組會貢獻出  $-xy$  與  $xy$  誤差量, 則二次誤差量相互抵消.

所以總結用圖示 A 的特性來消除  $x, y, x^2, y^2$  這些誤差項, 而圖示 B 的特性則是將兩個圖示 A 用鏡像以  $y_{axis}$  對稱的方式對來消除  $xy$  的誤差項後, 並延伸圖示 A 加上圖示 B 的功能使用於 4 組 8\*8 矩陣共 255 個 MSB 的電流源, 以  $x_{axis} - y_{axis}$  為中心呈對稱且 common central 排列如 Fig.4.16 , Fig.4.16 圖無色區代表每組的列週期內, 第一個行單位電流源打開所在矩陣內的相對應位置.

|            |            |            |            |            |            |            |            |            |           |           |           |           |           |           |           |           |

|------------|------------|------------|------------|------------|------------|------------|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| <b>Y8</b>  | 1          | 7          | 5          | 3          | 0          | 6          | 4          | 2          | 2         | 4         | 6         | 0         | 3         | 5         | 7         | 1         |

| <b>Y7</b>  | 15         | 8          | 10         | 12         | 14         | 9          | 11         | 13         | 13        | 11        | 9         | 14        | 12        | 10        | 8         | 15        |

| <b>Y6</b>  | 21         | 19         | 17         | 22         | 20         | 18         | 16         | 23         | 23        | 16        | 18        | 20        | 22        | 17        | 19        | 21        |

| <b>Y5</b>  | 26         | 28         | 30         | 24         | 27         | 29         | 31         | 25         | 25        | 31        | 29        | 27        | 24        | 30        | 28        | 26        |

| <b>Y4</b>  | 32         | 38         | 36         | 34         | 33         | 39         | 37         | 35         | 35        | 37        | 39        | 33        | 34        | 36        | 38        | 32        |

| <b>Y3</b>  | 46         | 41         | 43         | 45         | 47         | 40         | 42         | 44         | 44        | 42        | 40        | 47        | 45        | 43        | 41        | 46        |

| <b>Y2</b>  | 52         | 50         | 48         | 55         | 53         | 51         | 49         | 54         | 54        | 49        | 51        | 53        | 55        | 48        | 50        | 52        |

| <b>Y1</b>  | 59         | 61         | 57         | 58         | 60         | 62         | 56         |            | 56        | 62        | 60        | 58        | 57        | 63        | 61        | 59        |

| <b>-Y1</b> | 59         | 61         | 63         | 57         | 58         | 60         | 62         | 56         | 56        | 62        | 60        | 58        | 57        | 63        | 61        | 59        |

| <b>-Y2</b> | 52         | 50         | 48         | 55         | 53         | 51         | 49         | 54         | 54        | 49        | 51        | 53        | 55        | 48        | 50        | 52        |

| <b>-Y3</b> | 46         | 41         | 43         | 45         | 47         | 40         | 42         | 44         | 44        | 42        | 40        | 47        | 45        | 43        | 41        | 46        |

| <b>-Y4</b> | 32         | 38         | 36         | 34         | 33         | 39         | 37         | 35         | 35        | 37        | 39        | 33        | 34        | 36        | 38        | 32        |

| <b>-Y5</b> | 26         | 28         | 30         | 24         | 27         | 29         | 31         | 25         | 25        | 31        | 29        | 27        | 24        | 30        | 28        | 26        |

| <b>-Y6</b> | 21         | 19         | 17         | 22         | 20         | 18         | 16         | 23         | 23        | 16        | 18        | 20        | 22        | 17        | 19        | 21        |

| <b>-Y7</b> | 15         | 8          | 10         | 12         | 14         | 9          | 11         | 13         | 13        | 11        | 9         | 14        | 12        | 10        | 8         | 15        |

| <b>-Y8</b> | 1          | 7          | 5          | 3          | 0          | 6          | 4          | 2          | 2         | 4         | 6         | 0         | 3         | 5         | 7         | 1         |

|            | <b>-X8</b> | <b>-X7</b> | <b>-X6</b> | <b>-X5</b> | <b>-X4</b> | <b>-X3</b> | <b>-X2</b> | <b>-X1</b> | <b>X1</b> | <b>X2</b> | <b>X3</b> | <b>X4</b> | <b>X5</b> | <b>X6</b> | <b>X7</b> | <b>X8</b> |

Fig.4.16 四組 8\*8 矩陣以  $x_{axis} - y_{axis}$  中心呈對稱且做 common central 排列

同理, LSB 部份由 3 位元 B3~B1 輸入於 3-to-8 行與列溫度計解碼器, 再經過由 B0 所控制的 BOD 編碼器後產生 8 個數位碼. 控制下面的電流源  $1*8$  矩陣共兩組的佈局.

|    |     |     |     |     |     |     |     |     |    |    |    |    |    |    |    |    |

|----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

| Y1 | 1   | 7   | 5   | 3   | 0   | 6   | 4   | 2   | 2  | 4  | 6  | 0  | 3  | 5  | 7  | 1  |

|    | -X8 | -X7 | -X6 | -X5 | -X4 | -X3 | -X2 | -X1 | X1 | X2 | X3 | X4 | X5 | X6 | X7 | X8 |

Fig.4.17 電流源  $1*8$  矩陣共兩組以  $y_{axis}$  對稱的排列

以上討論是將選擇序列經過最佳化安排後, 做來因溫度或是製程等造成其非線性因素如第三章所介紹的梯度誤差與系統誤差…等的消除或補償.

## 4.5 佈局 (Layout)

整個電流式數位-類比轉換器以  $x_{axis} - y_{axis}$  中心呈對稱且做 common central 排列, 分佈於  $x_{axis} - y_{axis}$  四象限呈完全對稱, 佈局平面配置圖只需看其一象限即可, 圖示於 Fig.4.18.

Fig.4.18 數位-類比轉換器佈局對稱平面配置圖

參考[11]-用Bit Slice方式作來此數位-類比轉換器的佈局平面配置，它在佈局中有好的均勻度與低的梯度誤差的效應，提供數位-類比轉換器有好的特性表現。以下來討論各區塊配置上的考量。

第一階層(First Level)、第二階層(Second Level)和取樣時間驅動器(Clock driver)等數位電路集中放置，降低因數位訊號引起雜訊干擾到旁邊的類比電路。

電流源內部的疊接電晶體(Cascodes)與開關電晶體組(Switches)和門閂器(Latch)以陣列型式配置，減少數位輸入訊號進入門閂器(Latches)後將送出到達電流源內開關電晶體(Switches)的控制閂極之數位訊號所需走的路徑，降低控制閂極數位訊號的時間延遲與寄生效應。

將取樣時間驅動器(Clock Driver)送入的訊號用樹狀分佈架構進入陣列[電流源內疊接電晶體(Cascodes)、開關電晶體組(Switches)與門閂器(Latch)]中，降低取樣時間(Clock)的跳動量(jitter)，減少門閂器的控制閂極數位訊號輸出的時間誤差(time skew)量，讓數位-類比轉換器能有較佳的線性。

電流源陣列(Current Source Array)集中放置電流源電晶體的面積比傳統Row-column型[6]將Local解碼器放入電流源陣列中來的小，使得電流源電晶體匹配程度較佳，而且排除了數位與類比訊號混合交錯的可能，則數位訊號的雜訊就不會耦合到類比訊號或是電路中[19]。而PMOS型電流源電晶體集中坐在Nwell內，避免來自基板的雜訊干擾。

參考[5]作法，將偏壓電路打散在四象限的電流源陣列內，降低DNL與INL因梯度效應所引起的誤差量，每象限內的電流源陣列中其列有八個行單位電流源(MSB電流源中的一個基本單位電流源)放置兩個偏壓電路來降低送到電流源電晶體閂極控制電壓的電壓下降效應。

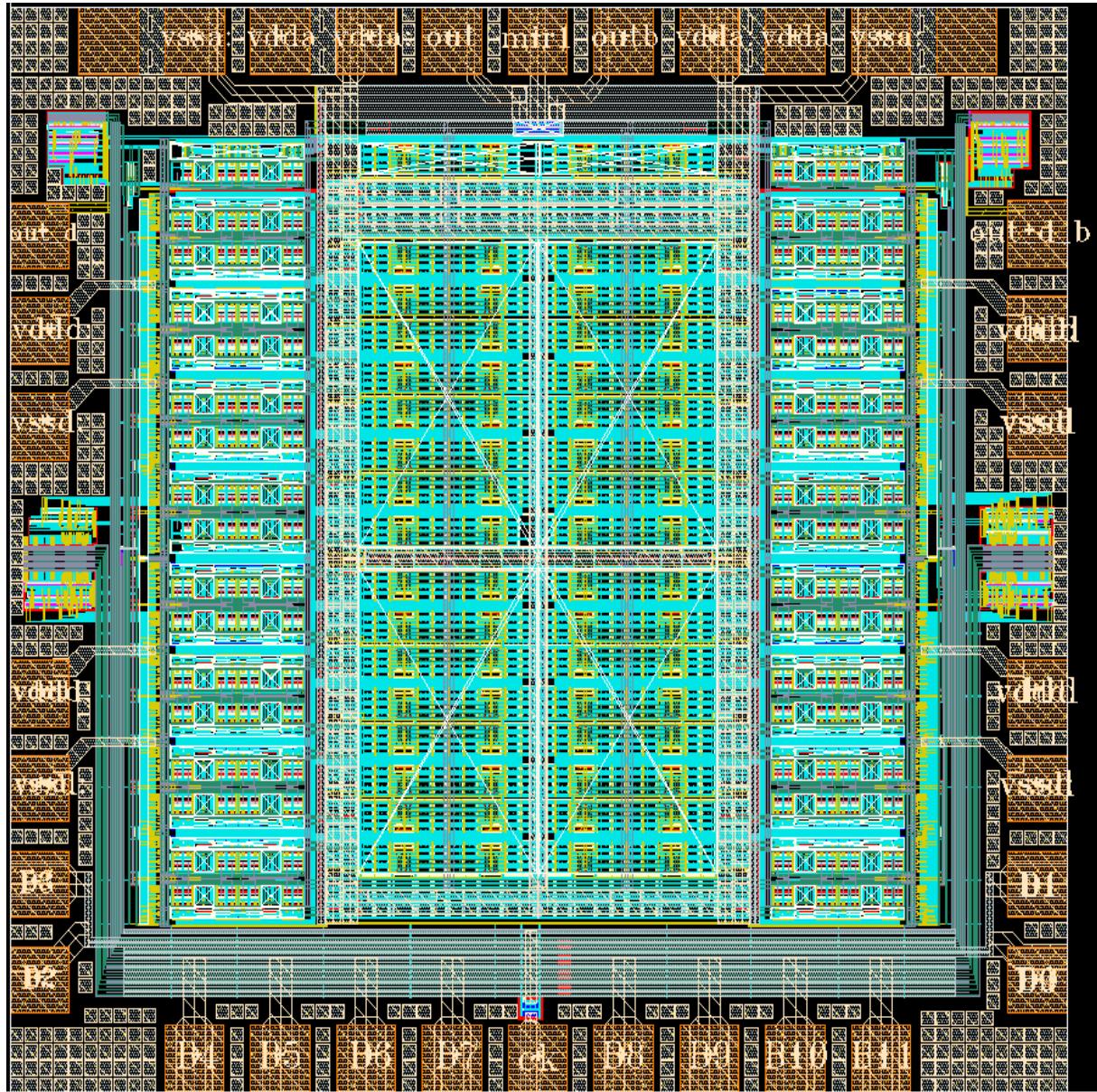

此晶片是用TSMC 0.18  $\mu\text{m}$  1P6M CMOS混合信號1.8 & 3.3V製程, 最後佈局圖於Fig.4.19

Fig.4.19 晶片佈局圖

## 4.6 總結( Summary)

此章節討論12位元500MHz電流式數位-類比轉換器電路設計. 首先架構區段化的考量, 系統中的每個子區塊電路的設計, 電流源陣列的選擇序列最佳化, 最後佈局考量. 整個數位-類比轉換器的電路模擬結果與量測電路設計將放在下章節.

### 模擬與測試電路

此研究的電流式數位-類比轉換器設計與佈局用台灣積體電路公司  $0.18\text{ }\mu\text{m }1\text{P6M CMOS}$  混合信號製程. 本章是模擬結果、量測環境的建立.

#### 5.1 模擬結果

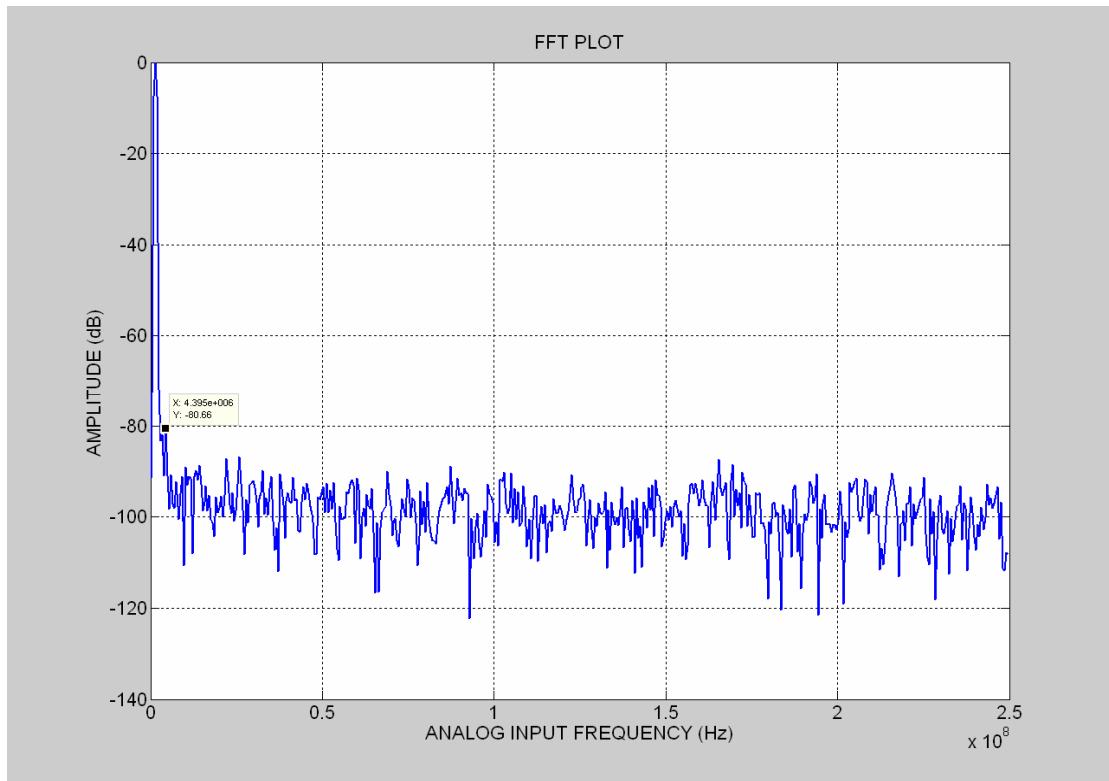

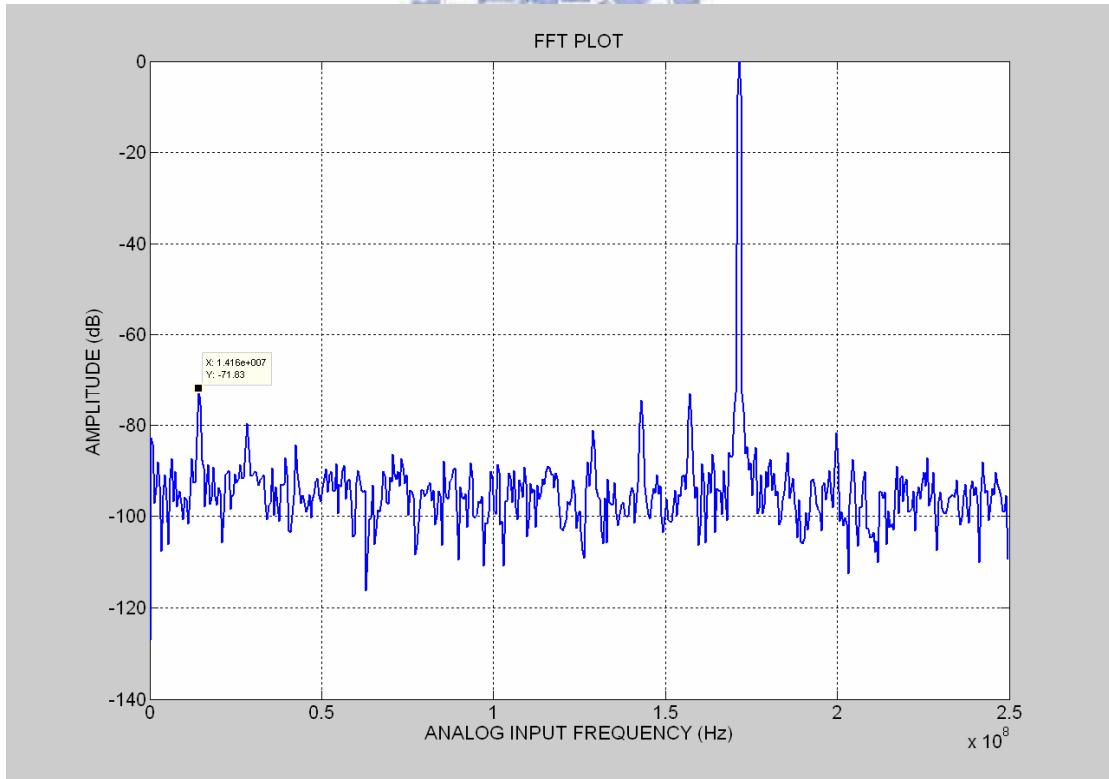

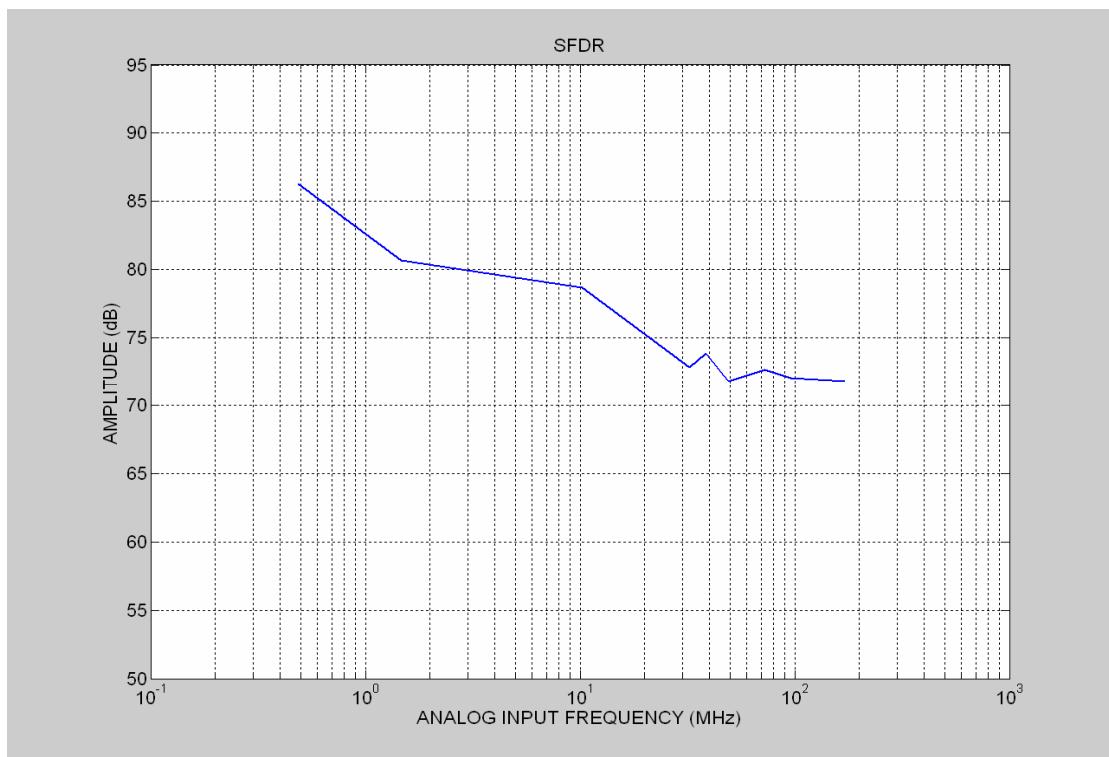

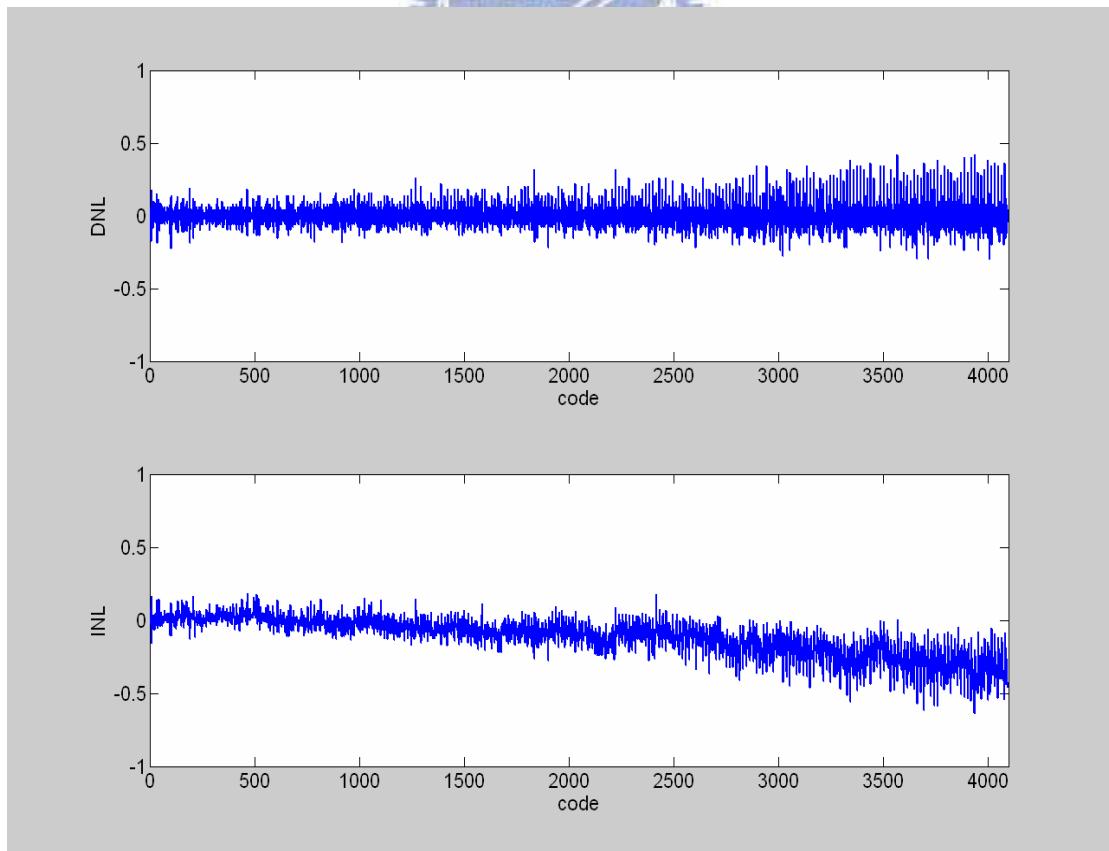

此研究上, 最主要的參數規格 SFDR 在信號頻率到達  $171.4\text{MHz}$  時有  $71.2\text{dB}$ .先進研發就是以達到它最大的效益為設計的目地.

取樣速率  $500\text{MHz}$  時, 輸入信號為  $1.46\text{MHz}, 10.25\text{MHz}, 32.22\text{MHz}, 38.57\text{MHz}, 49.31\text{MHz}, 72.75\text{MHz}, 96.19\text{MHz}, 110.83\text{MHz}, 171.39\text{MHz}$ . 而 Fig.5.1 為 SIN 波頻譜在取樣時間為  $500\text{MHz}$ , 輸入信號為  $1.46\text{MHz}$  下的模擬結果. Fig.5.2 為 SIN 波頻譜在取樣時間為  $500\text{MHz}$ , 輸入信號為  $171.39\text{MHz}$  下的模擬結果. Fig.5.3 為輸入信號由  $1.46\text{MHz}$  至  $171.39\text{MHz}$  的 SFDR 之 SIN 波頻譜. Fig.5.4 為差動非線性誤差與累積非線性誤差. 此電流式數位-類比轉換器的模擬結果列於表 Table 5.1

Fig.5.1 SIN波頻譜  $F_s = 500$  MHz and  $F_{sig} = 1.46$  MHz

Fig.5.2 SIN波頻譜  $F_s = 500$  MHz and  $F_{sig} = 171.4$  MHz

Fig.5.3 SIN波頻譜(SFDR)輸入信號1.46 MHz到171.4MHz而取樣頻率500MHz

Fig.5.4 差動非線性(DNL)和累積非線性(INL)

Table 5.1 模擬結果列表

|                    |                                             |

|--------------------|---------------------------------------------|

| Process            | TSMC 0.18 $\mu$ m CMOS<br>Mixed-Signal      |

| Supply Voltage     | Digital supply 1.8 V<br>Analog supply 3.3 V |

| Sampling Frequency | 500 MHz                                     |

| DNL                | < 0.5 LSB                                   |

| INL                | < 0.7 LSB                                   |

| SFDR (Fin=171MHz)  | 71.83dB@CLK=500 MHz                         |

| Power Dissipation  | 139 mW                                      |

| Active Area        | 1.8648mm <sup>2</sup>                       |

## 5.2 測試電路(Test Circuits)

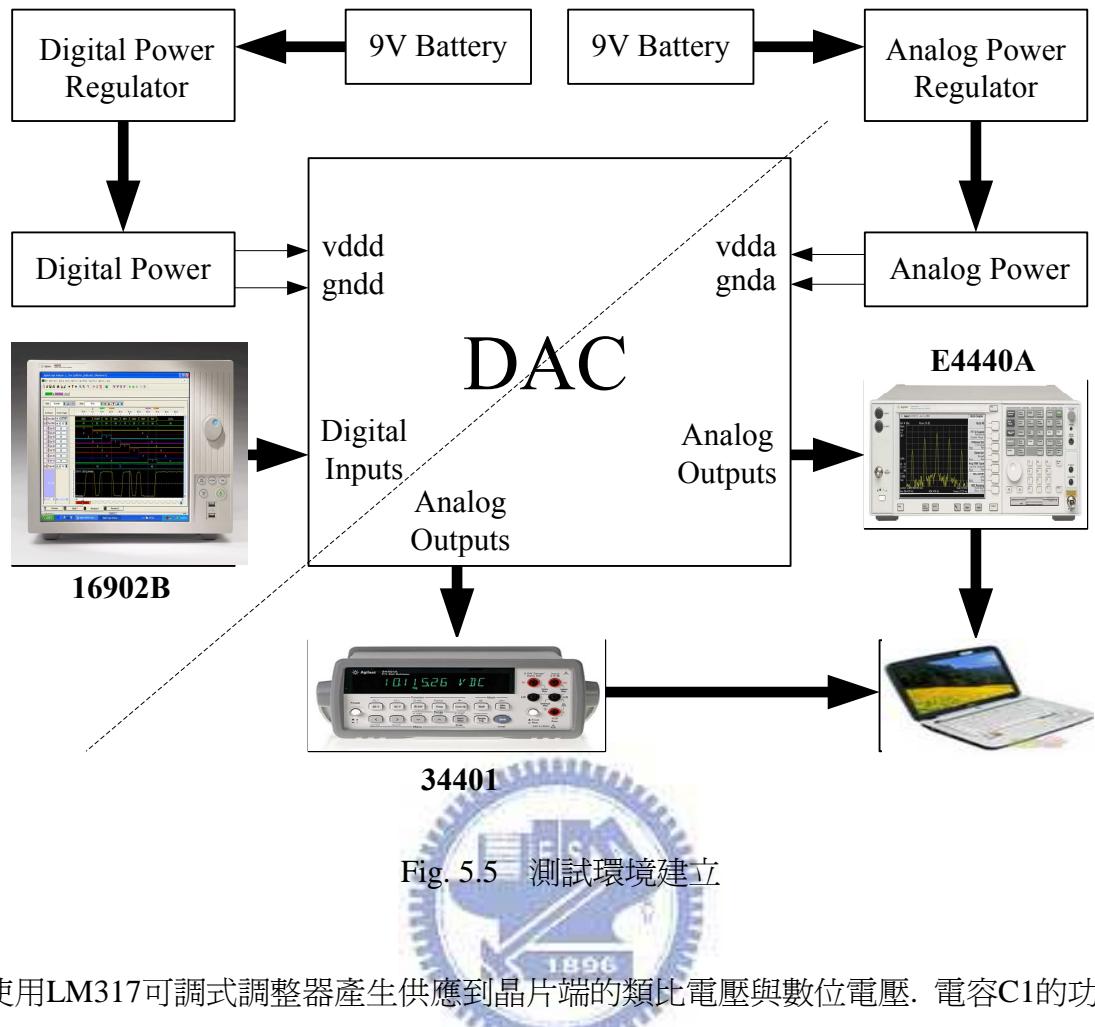

Fig.5.5 是整個數位-類比轉換器的量測環境建立, 建立環境中, Agilent 16902B Logic analysis System是用來產生數位輸入信號. 使用主動式探針將數位-類比轉換器的差動輸出信號轉成單端輸出信號用來消除共模雜訊和二階失真. Agilent E4440A 3 Hz-26 GHz PSA Series Spectrum Analyzer來量測其單端輸出結果. Agilent 34401 Digital Multi-meter來量測電壓暫態信號. 兩台precise power supplies來產生類比電壓源與數位電壓源.

Fig. 5.5 測試環境建立

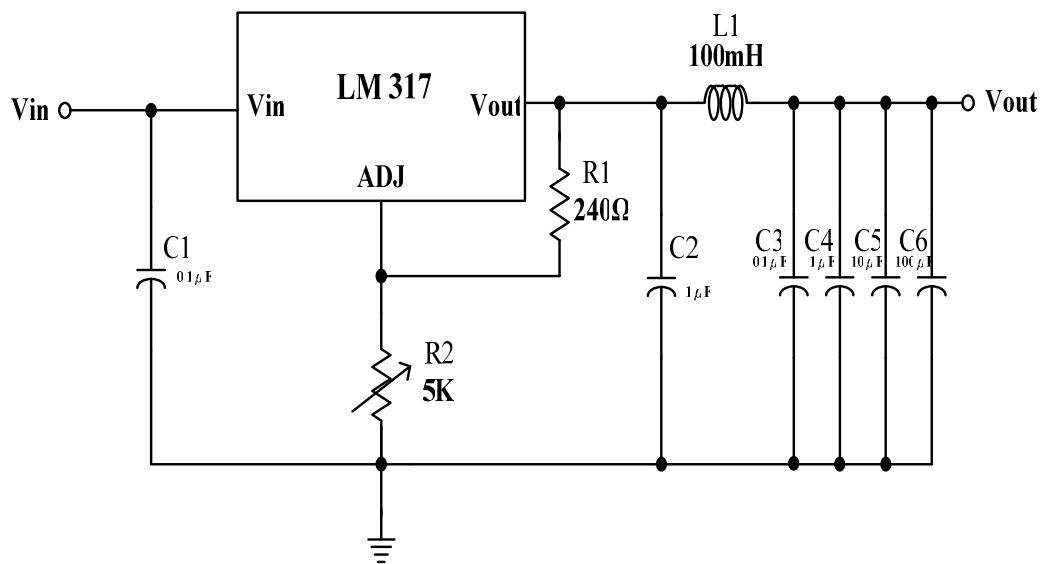

使用LM317可調式調整器產生供應到晶片端的類比電壓與數位電壓. 電容C1的功用在改善漣波排斥效應(ripple rejection), 而電容C2是旁路電容. 電阻R1是固定式電阻, 而電阻R2是精確可調式電阻. 電感L1和電容C3,C4,C5,C6組成低通濾波器. Fig.5.6的輸出電壓表示式:

$$V_{out} = 1.25V \cdot \left(1 + \frac{R_2}{R_1}\right) \cdot I_{ADJ} \cdot R_2 \quad (5.1)$$

其中 $I_{ADJ}$  is 是直流電流流過可調式調整器的ADJ端.

順便一提電阻R1使用低溫度係數的金屬薄膜型電阻用來得到穩定的輸出電壓.

Fig.5.6 電源調整器

### 結論與工作未來展望

---

12 位元電流式類比-數位轉換器使用 TSMC 0.18um 1P6M CMOS Mixed-Signal 的製程.

為了降低梯度效應影響到數位-類比轉換器的靜態特性 DNL 與 INL 誤差量而在類比電路內電流源陣列與疊接及切換電晶體陣列內使用大量的偏壓電路, 所以模擬結果造成 139mW 高功率消耗. 應朝降低類比電壓源與數位電壓源的方向進行研究解決功率耗費的問題.

因電流式數位-類比積體電路的電流源所在晶片的位置在打開電流時所引起梯度效應與系統誤差量大小有直接的關聯性. 可朝著電流源陣列佈局的均勻度是否有更佳的選擇序列方式來消除梯度誤差量與系統誤差量的方向來研究.

此研究的電流式數位-類比轉換器是用二區段 4 + 8 全溫度計碼式架構. 所以兩個子電流式數位-類比轉換器的切換電流上仍然有輸出端突波的現象, 影響數位-類比的轉換的動態特性 SFDR, 可朝此不理想性是否有其它方法可降低卻能讓數位-類比轉換器維持在高速與高解析度上使用的方向繼續研究.

## 參考文獻

- [1] Mikael Gustavsson, J Jacob Wikner and Nianziong Nick Tan, “CMOS Data Converters for communications,” Kluwer Academic Publishers, Boston,2000.

- [2] Farzen K., Johns D.A., “A power-efficient architecture for high-speed D/A Converters,” *Circuits and System, 2003. ISCAS '03. Proceedings of the 2003 International Symposium on, Volume*”1,25-28 May 2003 Pages: I-897 – I-900 vol.1.

- [3] J. Bastos, M. Steyaert, and W. Sansen, “A high yield 12-bit 250-MS/s CMOS D/A converter,” in *Proc. IEEE 1996 CICC*, May 1996, pp. 431-434.

- [4] A. R. Bugeja, B.-S. Song, P. L. Rakers, and S. F. Gilling, “A 14b 100 MSample/s CMOS DAC designed for spectral performance,” in *Proc. IEEE1999 ISSCC*, Feb. 1999, pp. 148-149.

- [5] C-H. Lin and K. Bult, “A 10b 500MSamples/s CMOS DAC in  $0.6\text{mm}^2$ ,” *IEEE J. Solid-State Circuits*, vol. 33, pp. 1948-1958, Dec. 1998.

- [6] J. Bastos, A. Marques, M. Steyaert and W. Sansen, “A 12-bit intrinsic accuracy high-speed CMOS DAC,” *IEEE J.Solid-State Circuits*, vol. 33, pp. 1959-1968, Dec. 1998.

- [7] A. Van den Bosch, M. Borremans, M. Steyaert, and W. Sansen, “A 12b 500 MSamples/s current-steering CMOS D/A converter,” in *IEEE Int. Solid-State Circuits Dig. Tech. Papers*, Feb. 2001, pp. 366-367.

- [8] G. Van Der Plas, J. Vandenbussche, W. Sansen, M. Steyaert, and G. Gielen, “A 14-bit intrinsic accuracy  $Q^2$  random walk CMOS DAC,” *IEEE J. Solid-State Circuits*, vol. 34, pp. 1708–1717, Dec. 1999.

- [9] J. Hyde, T. Humes, C. Diorio, M. Thomas, and M. Figueroa, “A 300-MS/s 14-bit digital-to-analog converter in logic CMOS,” *IEEE J. Solid-State Circuits*, vol. 38, pp. 734–740, May 2003.

- [10] A. Van den Bosch, M. A. F. Borremans, M. Steyaert, and W. Sansen, “A 10-bit 1-GSamples/s Nyquist Current-Steering CMOS D/A converter,” *IEEE J. Solid-State circuits*, VOL. 36, NO. 3, pp. 315-324, MAR. 2001

- [11] Kevin O’Sullivan, Chris Gorman, Michael Hennessy, and Vincent Callaghan, “A 12-bit 320-MSample/s Current-Steering CMOS D/A Converter in  $0.44\text{ mm}^2$ ,” *IEEE J. Solid-State Circuits*, vol. 39, no. 7, JULY 2004.

- [12] Jurgen Deveugele, Geert Van der Plas, Michiel Steyaert,Georges Gielen, and Willy Sansen, “A Gradient-Error and Edge-Effect Tolerant Switching Scheme for a High-Accuracy DAC,” *IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS*, vol. 51, no. 1, JANUARY 2004.

- [13] K. Lakshmikumar, R. Hadaway, ad M. Copeland, “Characterization and modeling of mismatch in MOS transistors for precision analog design,” *IEEE J. Solid-State Circuits*, vol. SC-21, pp. 1057-1066, Dec. 1986.

- [14] M. J. M. Pelgrom, A.C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," *IEEE J. Solid-State Circuits*, vol. 24, pp. 1433-1439, Oct.1989.

- [15] Yonghua Cong and Randall L. Geiger, "A 1.5-V 14-Bit 100-MS/s Self-Calibrated DAC , " *IEEE J. Solid-State Circuits*, vol. 38,no. 12, Dec. 2003.

- [16] A. Van den Bosch, M. Steyaert, and W. Sansen, "SFDR-bandwidth limitations for high-speed high-resolution current-steering CMOS D/A converters," in *Proc. IEEE Int. Conf. Electronics, Circuits and Systems (ICECS)*, Sept. 1999, pp. 1193-1196.

- [17] Mika P. Tiilikainen, "A 14-bit 1.8-V 20-mW 1-mm<sup>2</sup> CMOS DAC," *IEEE J. Solid-State Circuits*, vol. 36, no. 7, JULY 2001.

- [18] Alex R. Bugeja, and Bang-Sup Song, "A Self-Trimming 14-b 100-MS/s CMOS DAC," *IEEE J. Solid-State circuits*, vol. 35, pp. 1841-1852, Dec. 2000.

- [19] 劉沛潔 “通訊系統中數位類比轉換器之電路設計,” 晶片系統002期

- [20] Behzad Razavi, "Design of Analog CMOS Integrated Circuit Design," McGraw-Hill,2001.

- [21] John W. Harris and Horst Stocker. , "Handbook of mathematics and computational science," New York ,Springer,1998.

- [22] J Ronald L. Graham, Donald E. Knuth and Oren Patashnik. , "Concrete mathematics /a foundation for computer science," Addison-Wesley,1994.

- [23] Behzad Razavi, "Principles of Data Conversion System Design," NJ:IEEE Press,1995.

- [24] 蔡宗彥 “A 12-bit 500-MSamples/s Current-Steering CMOS D/A Converter,” 交通大學碩士論文，中華民國九十五年十月

- [25] 白逸維 “12 bit 250MSamples/s Current-Steering CMOS Converters with Partial Random Element Matching” 交通大學碩士論文，中華民國九十六年十二月