## 國立交通大學

電機與控制工程學系

碩士論文

### 生醫應用系統單晶片之 FPGA 實現

FPGA Implementation of Biomedical Application SoC

研究生:楊寓鈞

指導教授:林進燈 博士

中華民國九十八 年 一 月

### 生醫應用系統單晶片之 FPGA 實現

# FPGA Implementation of Biomedical Application SoC

研究生:楊寓鈞 Student: Yu-Chun Yang

指導教授:林進燈 Advisor: Dr. Chin-Teng Lin

國立交通大學

電機與控制工程學系

碩士論文

A Thesis

Submitted to Department of Electrical and Control Engineering

College of Electrical Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master

in

Electrical and Control Engineering

September 2008

Hsinchu, Taiwan, Republic of China

中華民國 九十八 年 一 月

### 生醫應用系統單晶片之 FPGA 實現

學生:楊寓鈞 指導教授:林進燈 博士

#### 國立交通大學電機與控制工程研究所

#### 中文摘要

在目前生醫電子領域研究中,如何能夠即時處理與分析大量的生理訊號是一個重要的討論問題。以往電子醫療和分析儀器都相當龐大且價格貴,因此可攜式 與嵌入式的生醫電子產品,需求日益增加。基於這兩個原因,本論文提出生醫應 用系統單晶片的設計,以提供資源整合性的使用。

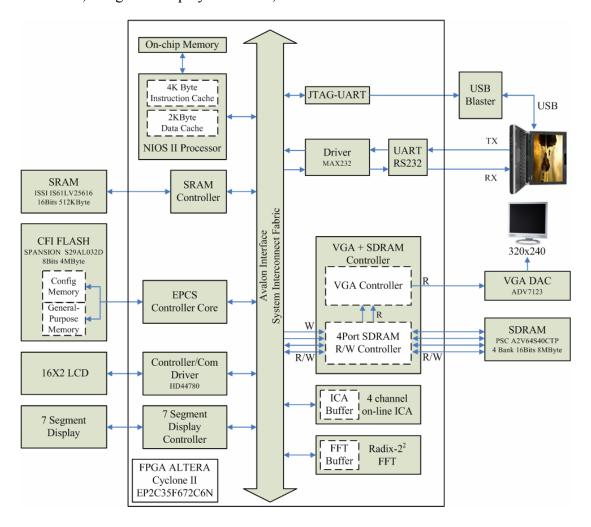

本論文提出一個生醫訊號處理的系統單晶片設計,具有(1)可程式化的監控與分析生理訊號能力及(2)整合性硬體擴充的空間:只要配置好暫存器存取位址,便能將客製化硬體設計透過系統匯流排整合進系統中。此系統單晶片架構包含可程式化的中央處理器、生醫訊號處理單元、系統匯流排、通訊和顯示介面。可程式化的中央處理器負責系統程序的排程和輸出入控制;生醫訊號處理單元能對生理訊號做訊號分離與分析的數位訊號處理核心;系統匯流排的設計能夠方便數位訊號處理 IP 的加入與移除。

經由實驗的結果顯示,本論文所提出生醫系統單晶片架構能在 FPGA 的平台上以 100 MHz 執行頻率達到訊號即時分析與顯示解析波形的效果。因為透過硬體執行與其他高速 DSP 的使用有很大的節省空間,如較少執行的週期、較低的功率消耗、減少 PCB 設計的面積等。最後,本論文所提出的架構透過 FPGA 實現並在 Altera DE2 發展板展示,共使用 29,640 邏輯單元。

**FPGA Implementation of Biomedical**

**Application SoC**

Student: Yu-Chun Yang

Advisor: Dr. Chin-Teng Lin

Department of Electrical and Control Engineering

National Chiao Tung University

**Abstract**

In the study of biomedical electronics nowadays, processing and analyzing

masses of physiological signals in time is a critical issue in real world. In the past,

electronic treatment and analysis instruments are very expansive and large. Therefore,

the requirement of portable and embedded biomedical electronic product is growing

rapidly. Based on these two reasons, this thesis presents a system-on-chip (SoC)

design for biomedical applications to provide the integration of systematic resources.

In this thesis, the SOC design for biomedical signal processing is presented. It

has the following features. (1) The ability of programmable monitoring and analyzing

biomedical signals. (2) The flexibility for further hardware extension. The SoC design

is composed of a programmable CPU, biomedical signal processing (BSP) units,

system bus, communication, and display interface. The programmable CPU manages

the process schedule and I/O control. The BSP unit is treated as digital signal

processing (DSP) cores which can separate and analyze physiological signals. The

system bus makes it flexible to add or to remove DSP IPs.

iii

By experimental results, the proposed design implemented on FPGA can achieve real-time analysis and waveform displays under at 100 MHz. Comparison with other high-speed DSP processors, the system presents some optimization such as less execution cycles, lower power consumption, use of fewer PCB area. Finally, the SoC design is demonstrated in this thesis with the Altera DE2 development board. The whole design is consisted of 29,640 logic elements.

#### 誌謝

兩年的研究所生涯隨著論文的完成劃上了句號,這兩年間,要感謝許多人 的鼓勵和幫忙,使我獲得充實的專業能力並順利完成研究所的學業。

首先要感謝的是我的指導教授-林進燈老師。感謝老師提供了很理想的研究環境、豐富的資源及正確的引導,使我在研究上非常順利。在老師悉心的指導下,讓我學習到解決問題的能力及做研究應有的態度,使我獲益良多。感謝范倫達教授時常關心我學業上的研究,時常與我討論論文方向及進度。

另外也感謝實驗室的麻吉們,感謝經翔學長開啟我雙主修之路的大門,還有在專業上跟生活上給予我許多的建議。感謝訓緯在生活上很照顧我。德瑋、俊傑、靜瑩及智文等學長姐們謝謝你們。還有我的同學們:煒忠,心情好或壞總是有人互相支持。儀晟,我們是706閃靈二人組喔。孟修,是不是一輩子的好兄弟,陽台時間總是很開心。福雄,謝謝你的照顧啦。建昇、俊彦,最後這段時間有你們一起衝刺真的很好。依伶,感謝一姐給我一流的建議跟幫助。毓廷、孟哲,有你們的生活真的是歡樂不斷。

我也要謝謝實驗室的學弟妹: 昕展,你跟我都走一樣的路,一樣辛苦,要加油!也謝謝你了!哲睿,真的很高興能跟你玩在一起耶,很高興我們時常能互相討論耶,是不是陽台四人組!介恩,謝謝你在半夜心情不好時的義氣相挺,加油,跟你在一起的陽台時間總是特別白爛!家欣、有德,謝謝你們在研究上及生活上的互相扶持及鼓勵。志賢,很謝謝你的陪伴,能玩在一起真是太開心了。雞蛋瑄,是不是生活上,運動上,心情上大家都是很好的咖,很高興有你這個好友喔。阿航,跟你瘋癲哈啦還真是快樂。文文,感謝你這麼挺我這個學長,讓我很感動。Frank,謝謝你這個半夜咖加早餐咖。聖祥,謹譽、敬婷、凱能,你們真是太可愛的一群人了。蘋果鈴,謝謝你這個早餐咖常在半夜義氣相挺,有你的生活真的是歡樂不斷,小~黑,有些話真的是盡在不言中啦,感謝感謝。

Thanks Kevin, you are really my buddy, I enjoy small break with you all the time. Thanks Clare, you make me grow up to be who I am now.孟宏,謝謝你這個摯友,總是挺我挺到底,有你這好友真好。

感謝教會的好朋友們, 郁翔, 真的是換帖的。仲石、孟蓉, 你們真真正正是自己人, 太感謝你們的照顧了。還有C團的大家、社青團契還有關心我的人, 謝謝。Cindy, thanks for your prayer and tears, I'll keep the word I promised you.

最後要感謝家人:老爸,你真的是我的偶像,是我很大的靠山,謝謝你全力的支持跟呵護,我都收到啦。感謝老媽的支持,你真的真的從頭挺到尾耶,有沒有這麼可愛的媽媽呀,愛妳喔。還有老姊跟姊夫,你們真的是太照顧我了,讓我感受到很溫暖的關心,謝謝你們。我也要謝謝上帝,賞賜的是耶和華,收取的也是耶和華,Thanks god!

#### **Contents**

| 中文摘要      | £       |                                                | ii   |

|-----------|---------|------------------------------------------------|------|

| Abstract  | t       |                                                | iii  |

| 誌謝        | •••••   |                                                | v    |

| List of F | igures  |                                                | ix   |

| List of T | ables   |                                                | xiii |

| Chapter   | 1 Intro | ductionduction                                 | 1    |

| 1-1       | M       | otivation                                      | 1    |

| 1-2       | Ol      | ojectives                                      | 3    |

| 1-3       | Or      | rganization of the Thesis                      | 4    |

| Chapter   | 2 Biome | edical SoC Architecture                        | 5    |

| 2-1       | Sy      | stem Architecture                              | 5    |

|           | 2-1-1   | Hardware Configuration                         | 6    |

|           | 2-1-2   | Systematic Data Flow                           | 10   |

| 2-2       | M       | icroprocessor Core                             | 11   |

|           | 2-2-1   | Introduction of Nios II Processor              | 11   |

|           | 2-2-2   | Hardware Architecture of Nios II Processor     | 12   |

|           | 2-2-3   | Memory & I/O Organization of Nios II Processor | 13   |

| 2-3       | Bi      | omedical Signal Processing Units               | 15   |

|           | 2-3-1   | Introduction of on-line ICA                    |      |

|           | 2-3-2   | Structure of on-line ICA                       |      |

|           | 2-3-3   | Implementation of on-line ICA                  | 21   |

|           | 2-3-4   | Introduction of FFT                            | 27   |

|           | 2-3-5   | Different Structure of FFT Nowadays            | 33   |

|           | 2-3-6   | Implementation of Radix-2 <sup>2</sup> FFT     | 35   |

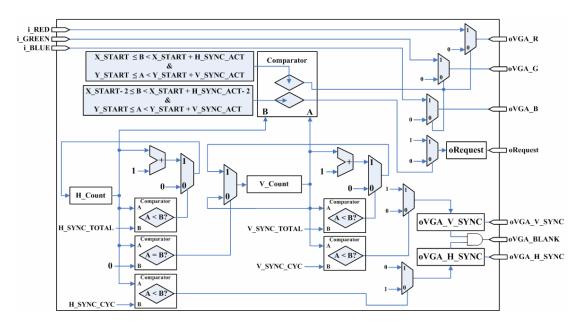

| 2-4       | V       | GA Controller                                  | 42   |

|           | 2-4-1   | Introduction VGA Controller                    | 42   |

|           | 2-4-2   | Implementation of VGA Controller               | 45   |

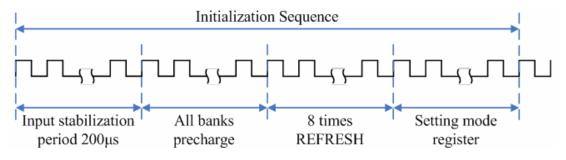

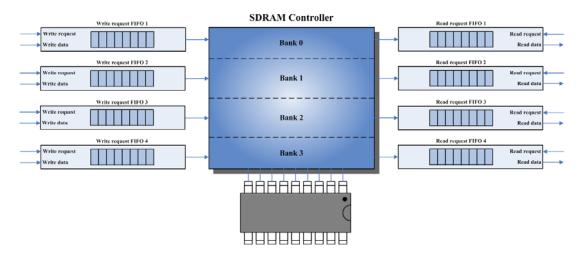

| 2-5       | SI      | DRAM Controller                                | 47   |

|           | 2-5-1   | Introduction of SDRAM                          | 47   |

|           | 2-5-2   | Pin Description of SDRAM of PSC A2V64S40CTP    | 49   |

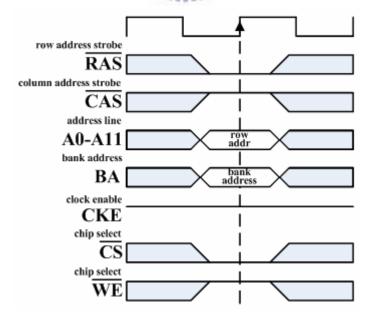

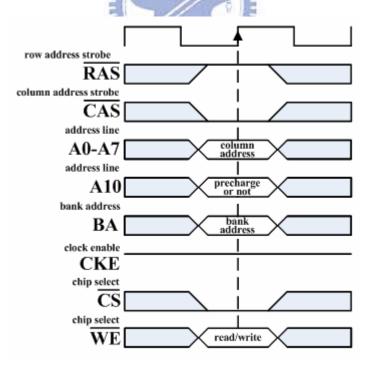

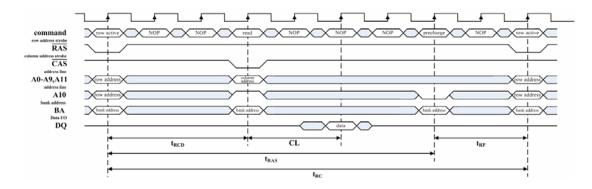

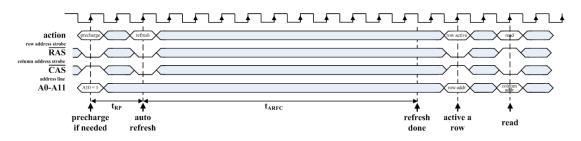

|           | 2-5-3   | The Principle of Internal Operation and Timing | 49   |

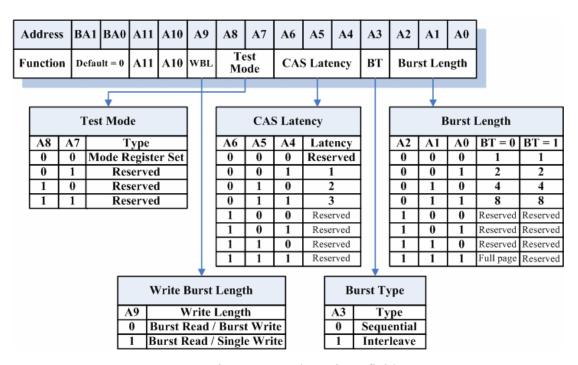

|           | 2-5-4   | Mode Register in SDRAM                         | 57   |

|           | 2-5-5   | Timing Parameters                              | 57   |

|           | 2-5-6   | Implementation of SDRAM Controller             | 58   |

| 2-6       | Bl      | ock level simulation result                    | 64   |

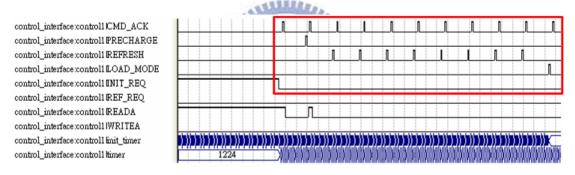

|           | 2-6-1   | Simulation Result of VGA Controller            | 64   |

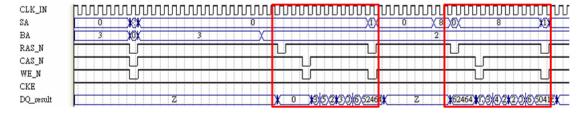

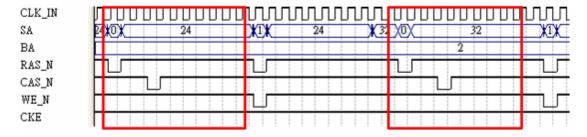

|     |       | 2-6-2    | Simulation Result of SDRAM Controller               | 66  |

|-----|-------|----------|-----------------------------------------------------|-----|

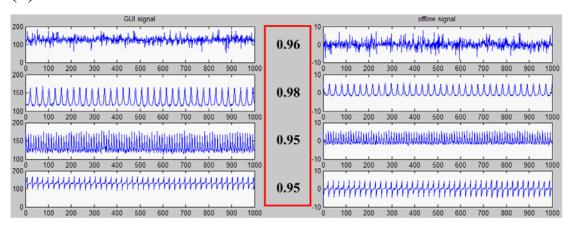

|     |       | 2-6-3    | Simulation result of on-line ICA                    | 69  |

|     |       | 2-6-4    | Simulation result of FFT                            | 74  |

| Cha | apter | 3 FPG    | A Implementation                                    | 77  |

|     | 3-1   | Iı       | ntroduction of Implementation Platform              | 77  |

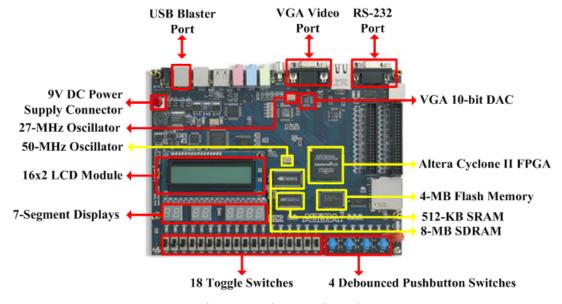

|     |       | 3-1-1    | Features of Altera DE2 Board                        | 77  |

|     | 3-2   | Iı       | ntroduction of SOPC                                 | 78  |

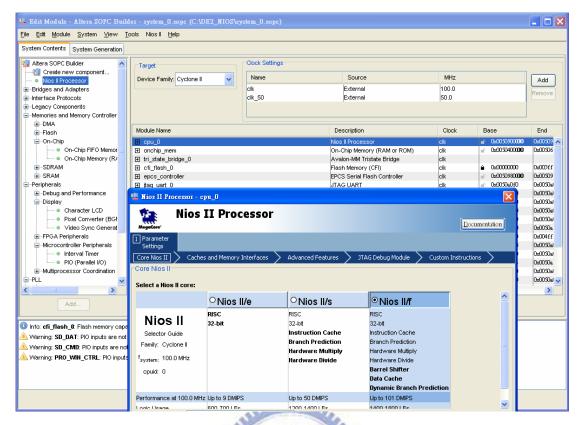

|     |       | 3-2-1    | SOPC                                                | 79  |

|     |       | 3-2-2    | SOPC Builder                                        | 80  |

|     | 3-3   | Iı       | ntroduction of Avalon BUS Interface                 | 81  |

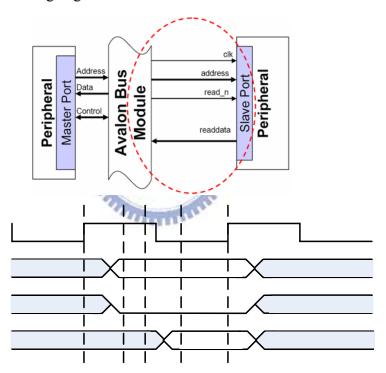

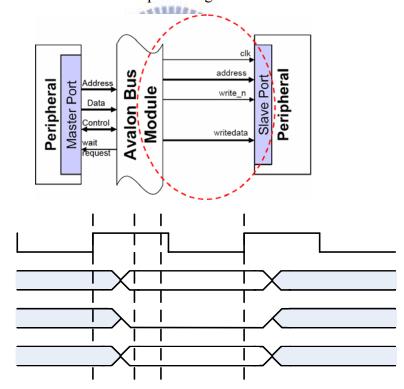

|     |       | 3-3-1    | SOPC Builder and Generation of the Avalon Bus       | 81  |

|     |       | 3-3-2    | Avalon Peripherals                                  | 82  |

|     |       | 3-3-3    | Avalon Bus Signals                                  | 83  |

|     |       | 3-3-4    | Slave Read Transfers on the Avalon Bus              | 83  |

|     |       | 3-3-5    | Slave Write Transfers on the Avalon Bus             | 85  |

|     | 3-4   | Iı       | ntegration of Customized IP into Avalon BUS         | 86  |

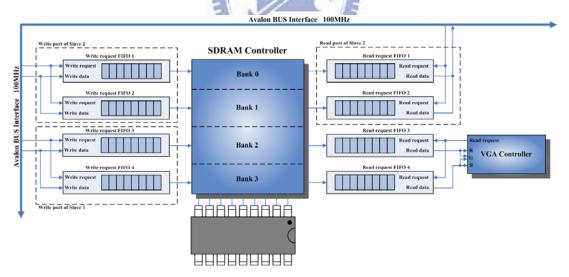

|     |       | 3-4-1    | Integration of VGA/SDRAM Controller into Avalon BUS | 86  |

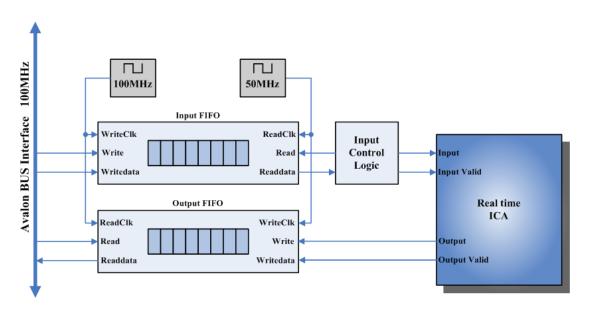

|     |       | 3-4-2    | Integration of ICA into Avalon BUS                  | 88  |

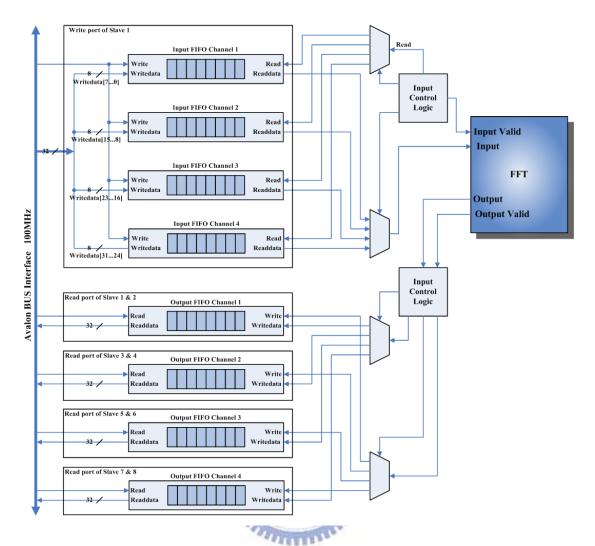

|     |       | 3-4-3    | Integration of FFT into Avalon BUS                  | 89  |

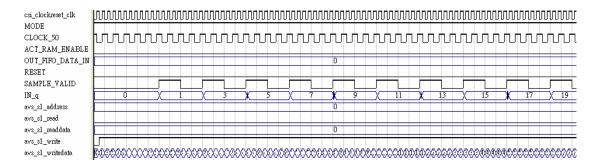

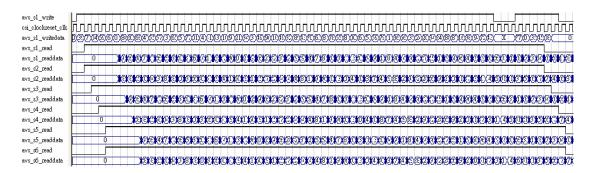

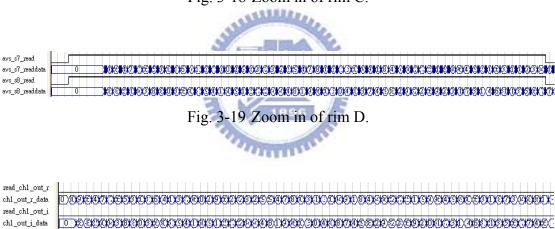

|     | 3-5   | S        | imulation Result of Wrappers                        | 90  |

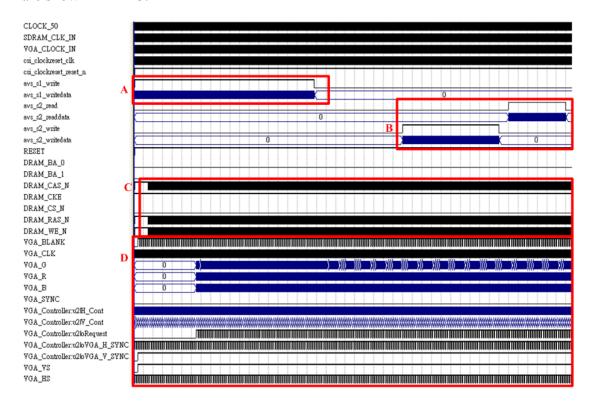

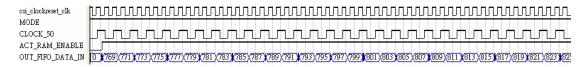

|     |       | 3-5-1    | Simulation Result of VGA/SDRAM Controller Wrapper   | 90  |

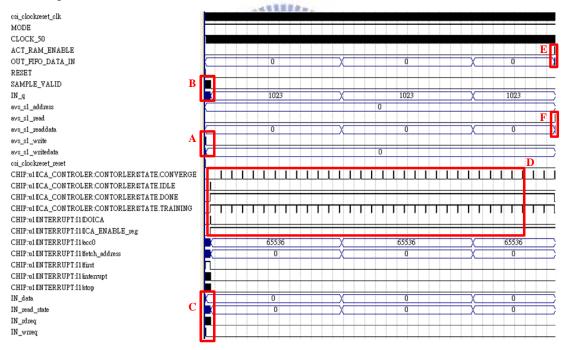

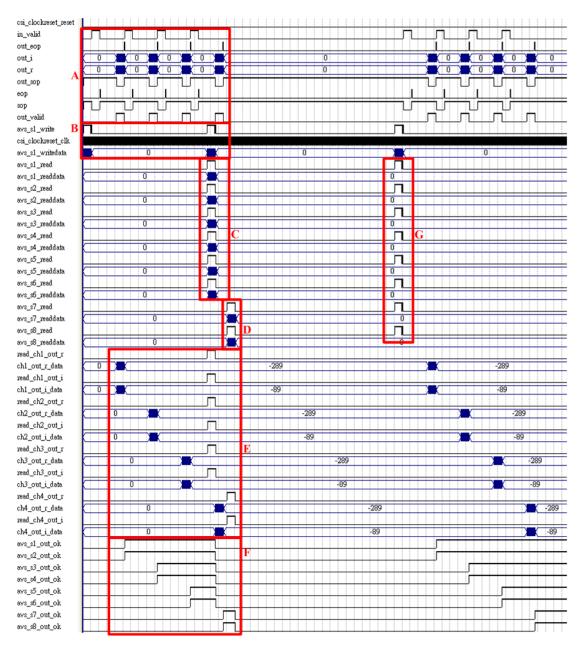

|     |       | 3-5-2    | Simulation Result of ICA Wrapper                    | 91  |

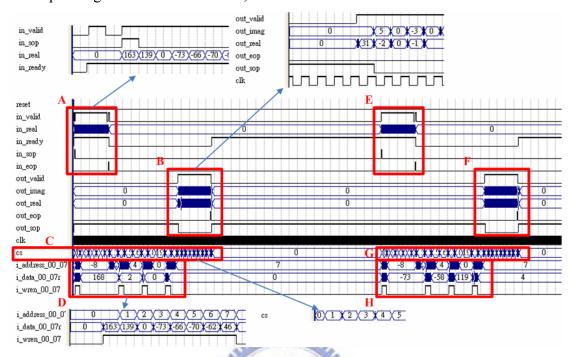

|     |       | 3-5-3    | Simulation Result of FFT Wrapper                    | 93  |

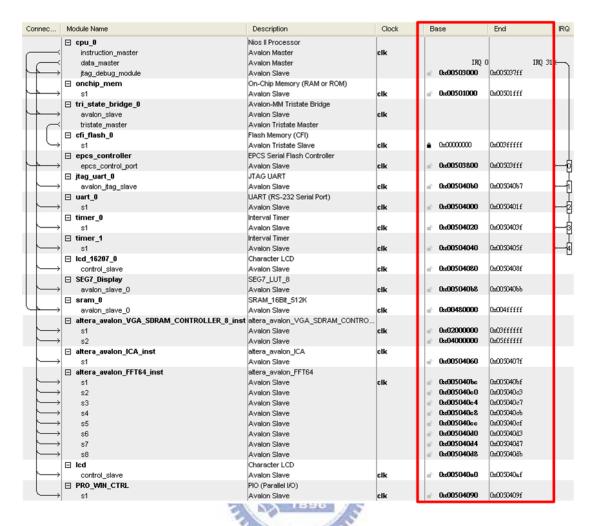

|     |       | 3-5-4    | Base Address Definition of System Components        | 95  |

|     | 3-6   | S        | ummary of Hardware Resources after Synthesis        | 96  |

|     |       | 3-6-1    | Synthesis Result of VGA/SDRAM Controller Wrapper    | 96  |

|     |       | 3-6-2    | Synthesis Result of ICA Wrapper                     | 97  |

|     |       | 3-6-3    | Synthesis Result of FFT Wrapper                     | 98  |

|     | 3-7   | S        | oftware Development                                 | 99  |

|     |       | 3-7-1    | Main Program Procedural Flow                        | 99  |

|     |       | 3-7-2    | Flash Programmer and Zipped File System             | 100 |

|     |       | 3-7-3    | GUI Implementation                                  | 100 |

| Cha | apter | 4 Expe   | erimental Results                                   | 103 |

|     | 4-1   | S        | ynthesis Result of the System                       | 103 |

|     | 4-2   | P        | ower Analysis of the System                         | 104 |

|     | 4-3   | $\Gamma$ | Device for Demonstration                            | 105 |

|     | 4-4   | E        | Experimental Result of EEG Signal                   | 105 |

|     | 4-5   | C        | Comparison with other System                        | 112 |

| Chapter 5 Conclusions and Future Works |              | 114 |

|----------------------------------------|--------------|-----|

| 5-1                                    | Conclusions  | 114 |

| 5-2                                    | Future Works | 115 |

| References                             | S            | 116 |

## **List of Figures**

| Fig. 2-1  | System architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

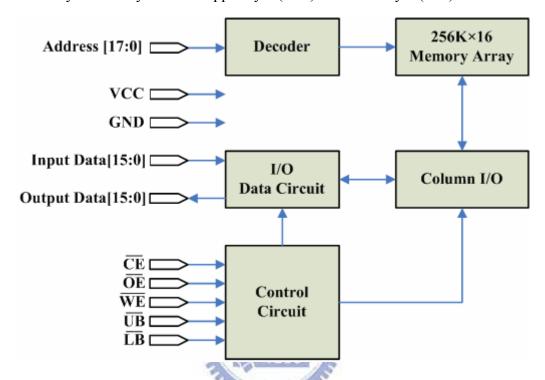

| Fig. 2-2  | Functional block diagram of SRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7  |

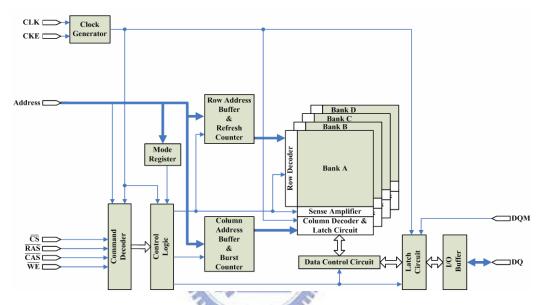

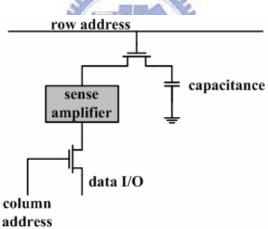

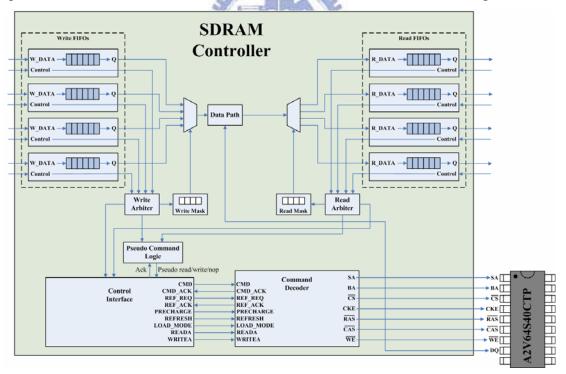

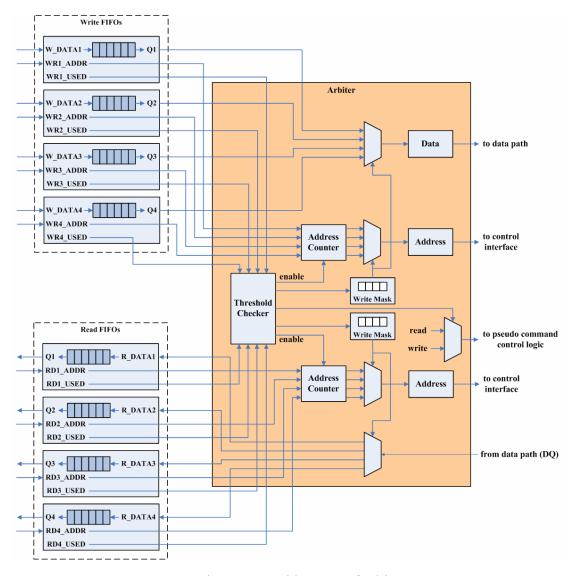

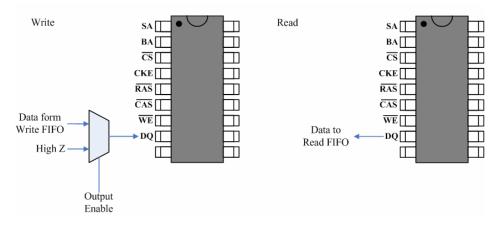

| Fig. 2-3  | Functional block diagram of SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8  |

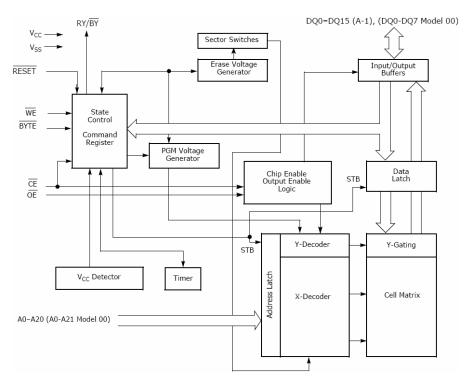

| Fig. 2-4  | Block Diagram of Flash memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9  |

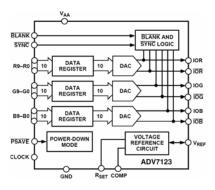

| Fig. 2-5  | Functional block diagram of VGA DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 |

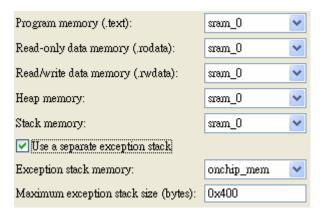

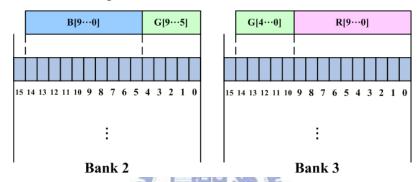

| Fig. 2-6  | Detail memory configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10 |

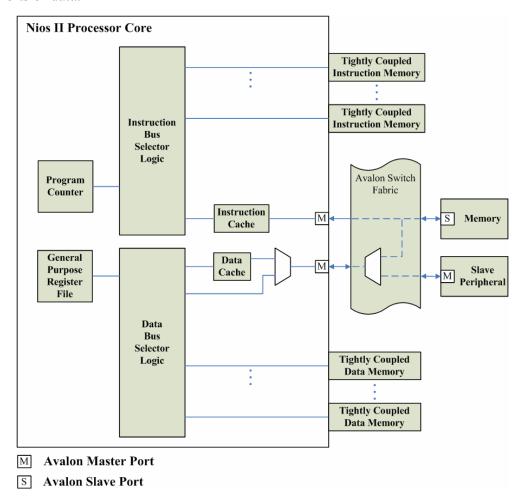

| Fig. 2-7  | Nios II processor core block diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12 |

| Fig. 2-8  | Nios II Memory & I/O Organization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14 |

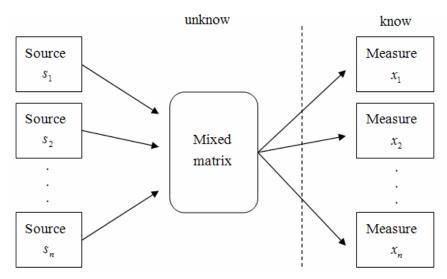

| Fig. 2-9  | Illustration of the BSS problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

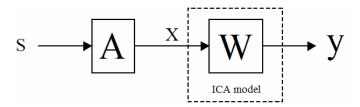

| Fig. 2-10 | Illustration of ICA formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17 |

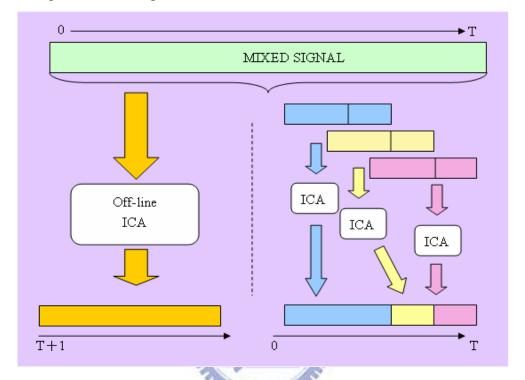

| Fig. 2-11 | Illustration of off-line and on-line algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 |

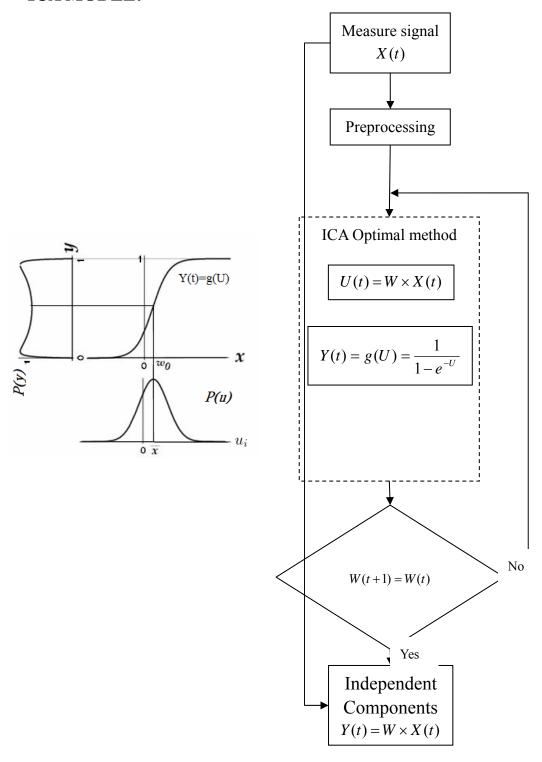

| Fig. 2-12 | Diagram flow of the computation of implementation of on-line ICA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|           | learning algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19 |

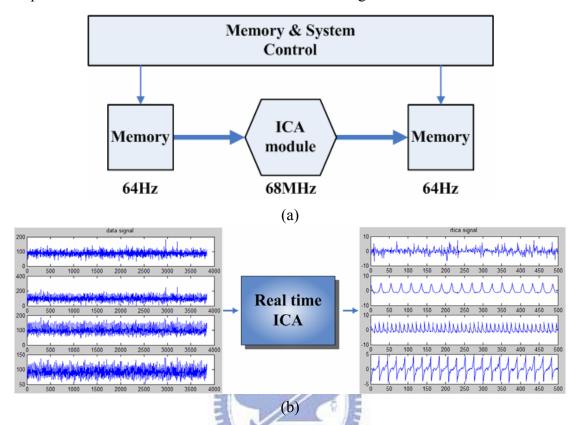

| Fig. 2-13 | (a) Top level hardware architecture and (b) Illustration of real-time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|           | systems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Fig. 2-14 | And a second control of the second control o |    |

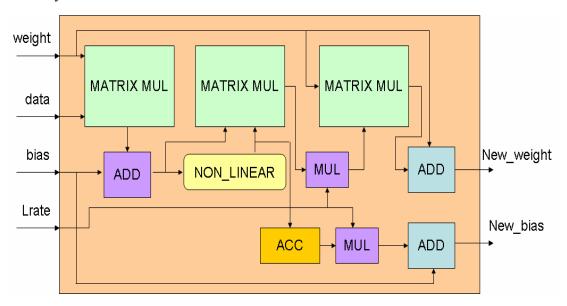

| Fig. 2-15 | Integrated computing unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21 |

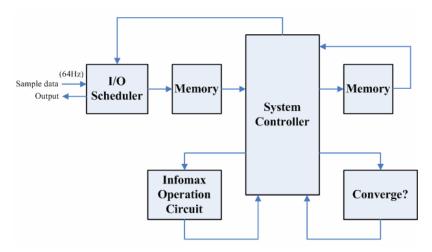

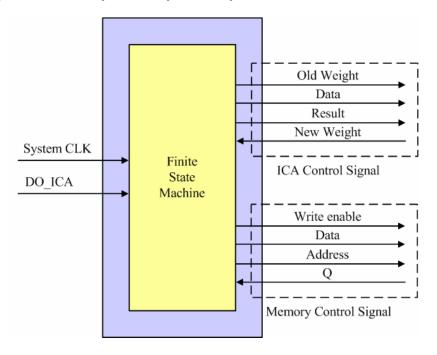

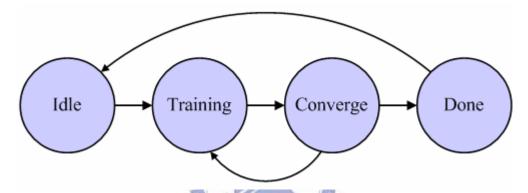

| Fig. 2-16 | Main controller architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22 |

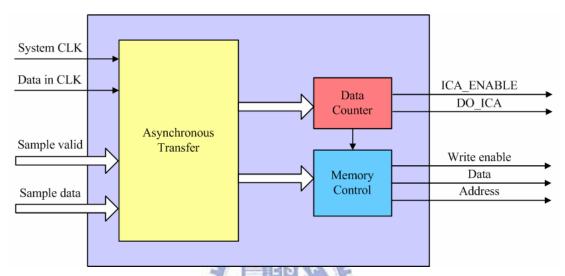

| Fig. 2-17 | Asynchronous memory controller circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23 |

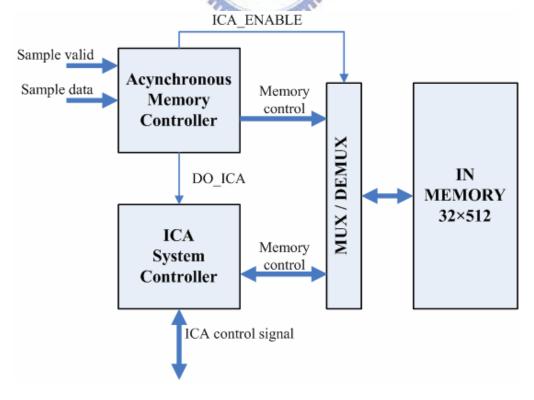

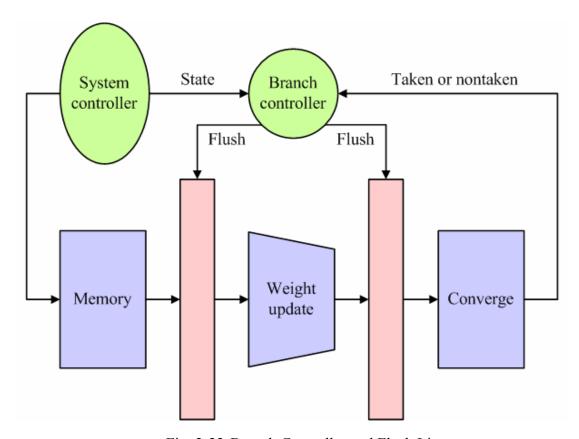

| Fig. 2-18 | System controller circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24 |

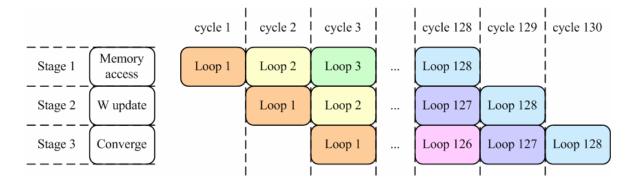

| Fig. 2-19 | System pipeline flow.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 |

| Fig. 2-20 | Illustration of micro-controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25 |

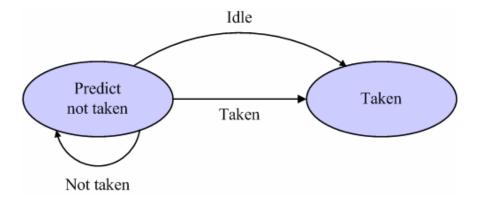

| Fig. 2-21 | Dynamic Branch Prediction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26 |

| Fig. 2-22 | Branch Controller and Flush Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26 |

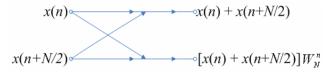

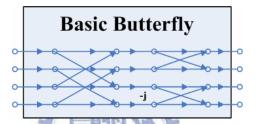

| Fig. 2-23 | Butterfly flow graph of Radix-2 algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28 |

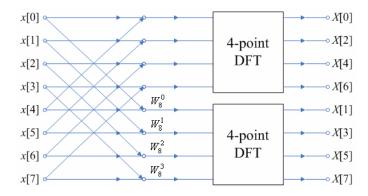

| Fig. 2-24 | Flow graph of 8-point DFT computation into two 4-point DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|           | computations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29 |

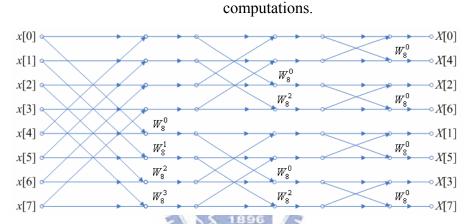

| Fig. 2-25 | Flow graph of complete decimation-in-frequency decomposition of an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|           | 8-point DFT computation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29 |

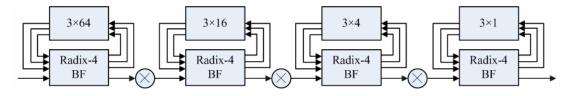

| Fig. 2-26 | Basic butterfly flow graph of a Radix-4 FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30 |

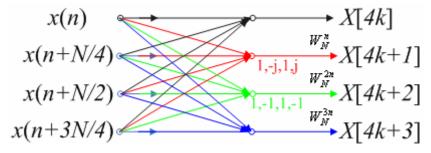

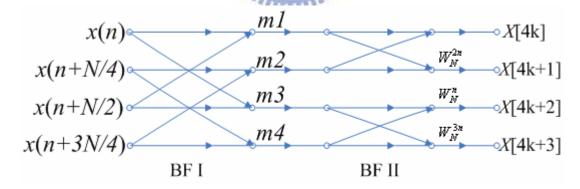

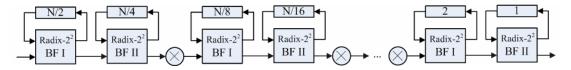

| Fig. 2-27 | Basic butterfly flow graph of a Radix-2 <sup>2</sup> FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32 |

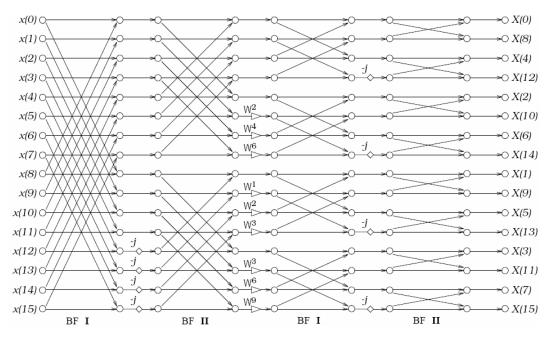

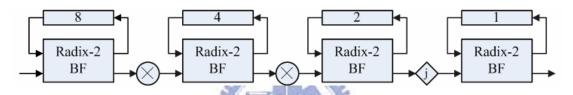

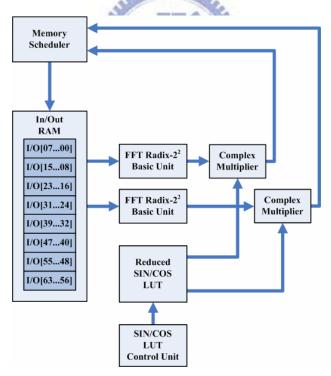

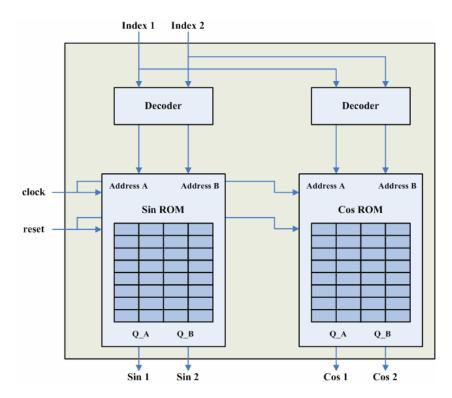

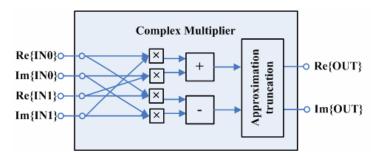

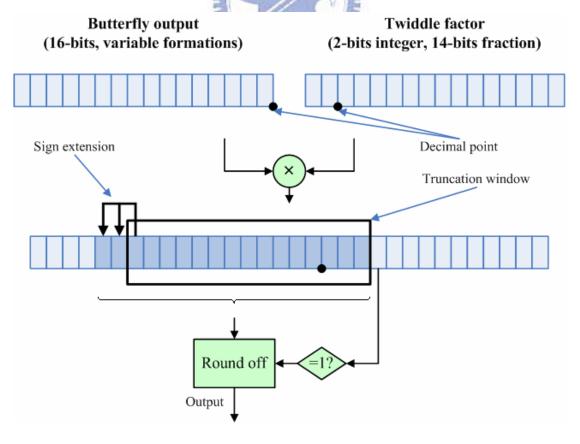

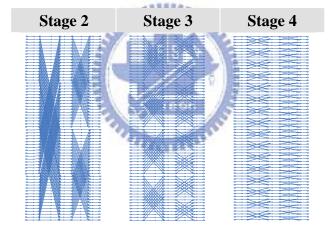

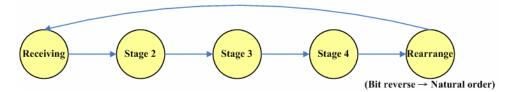

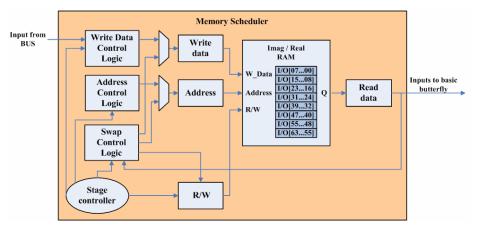

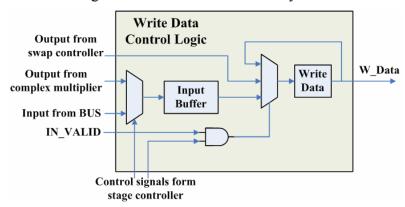

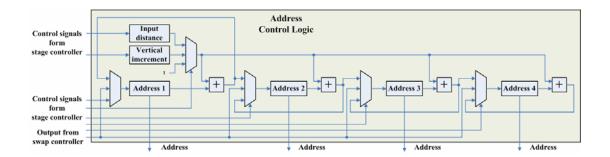

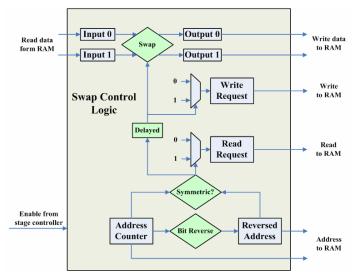

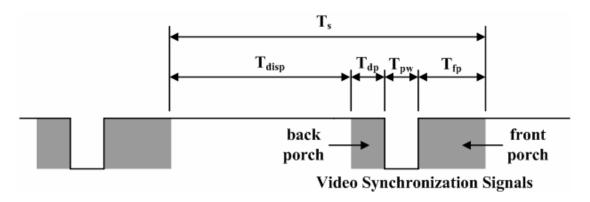

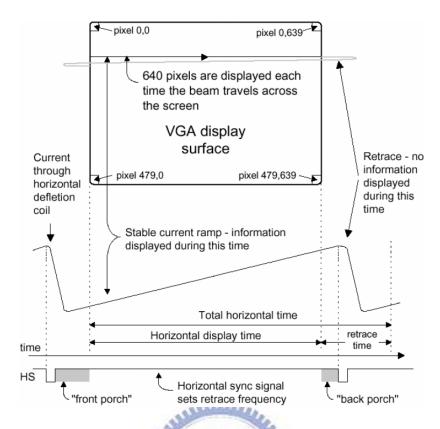

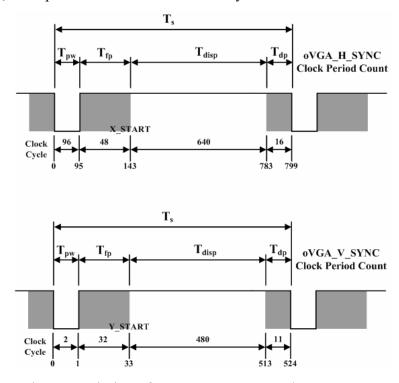

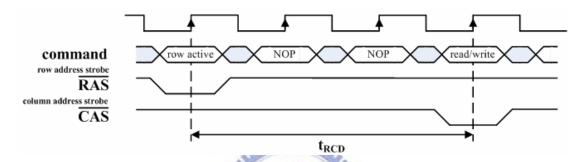

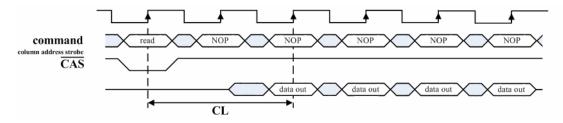

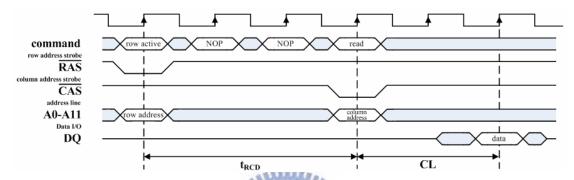

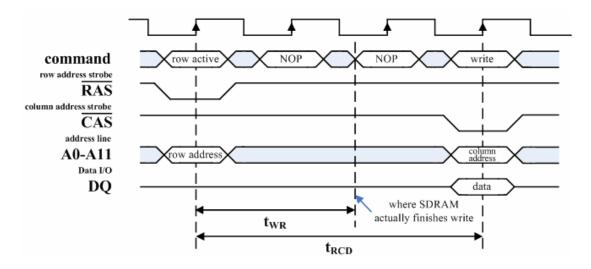

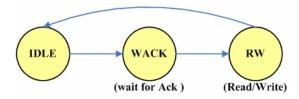

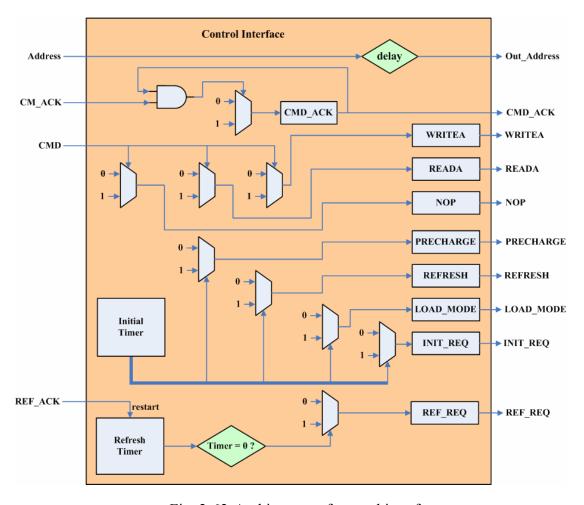

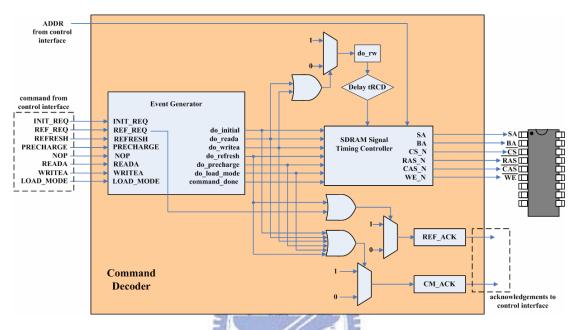

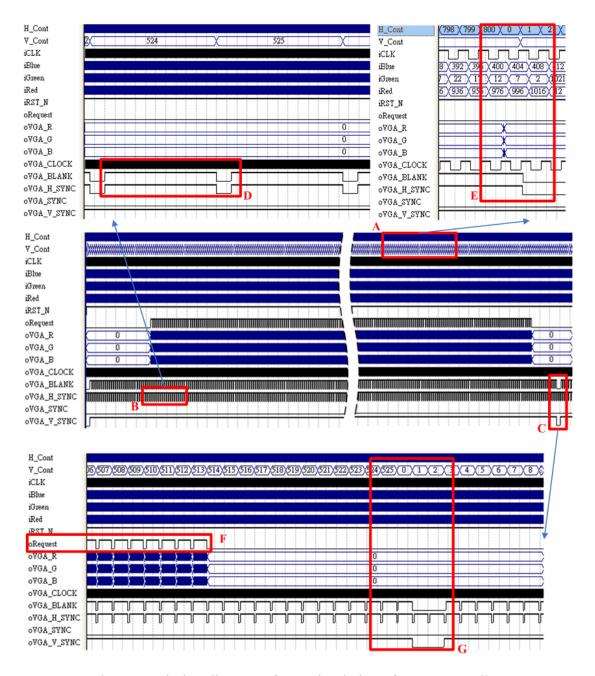

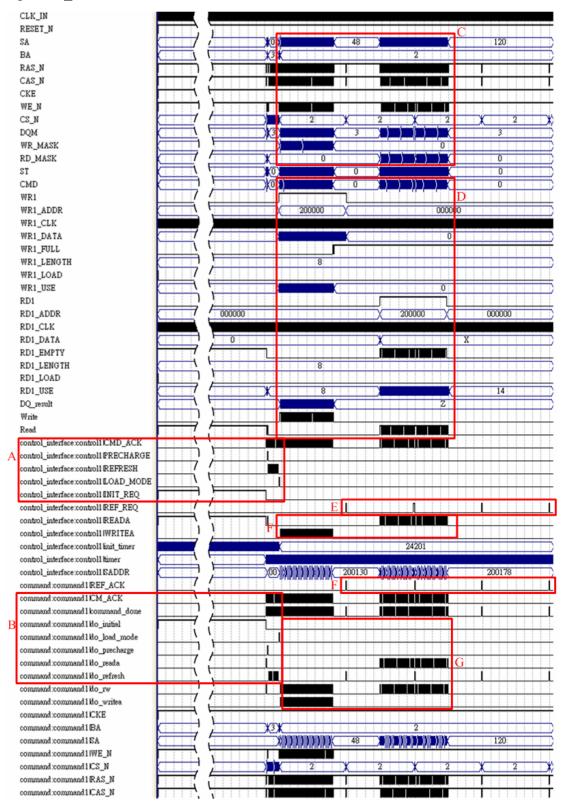

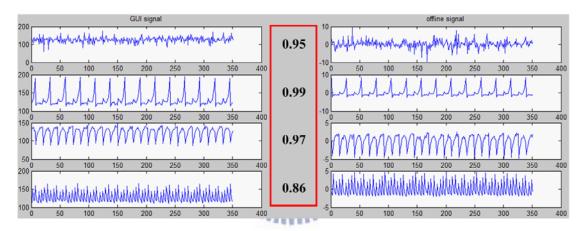

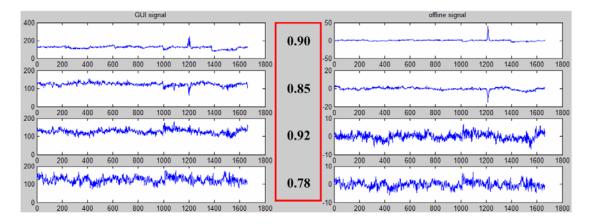

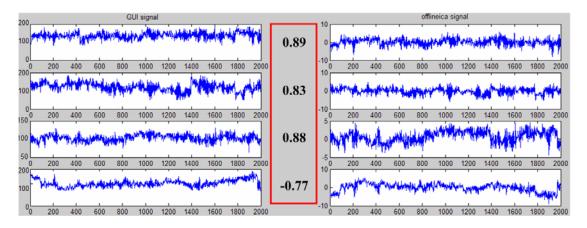

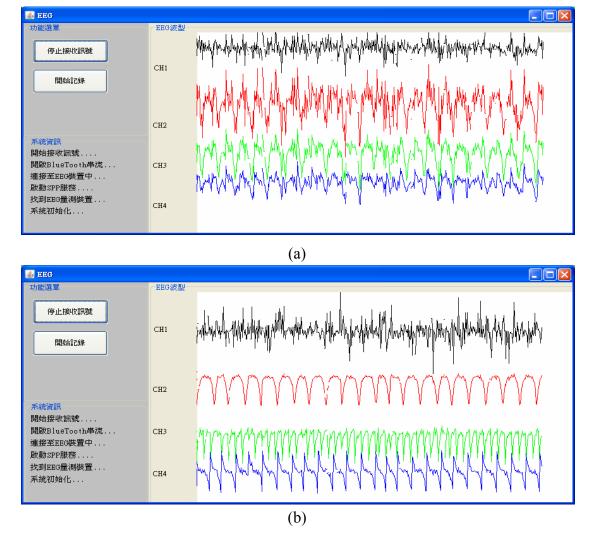

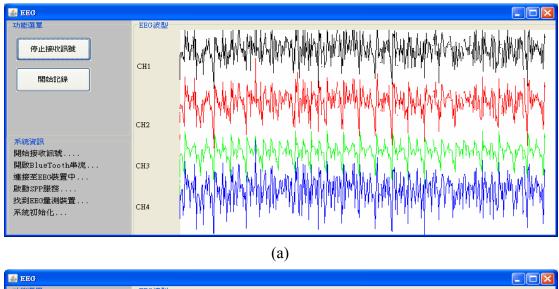

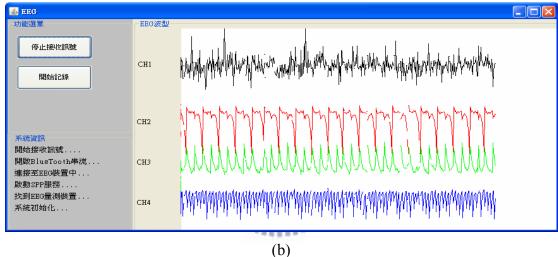

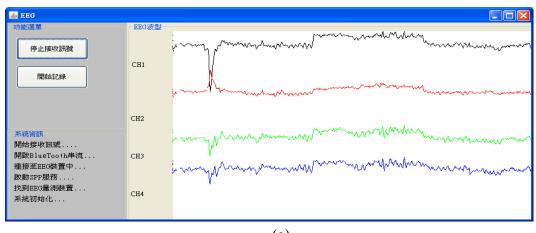

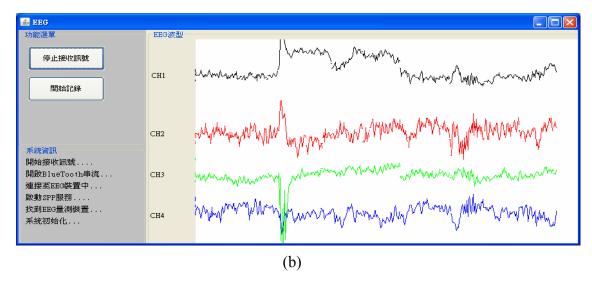

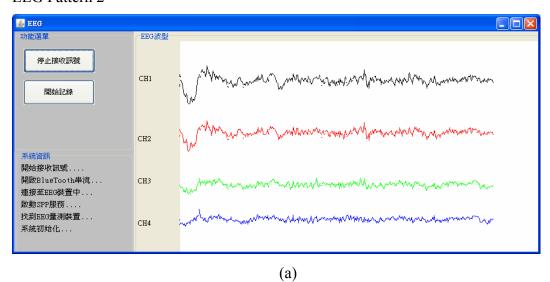

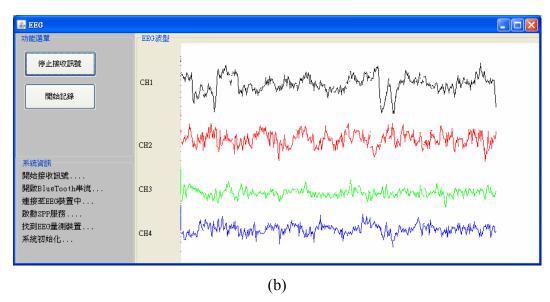

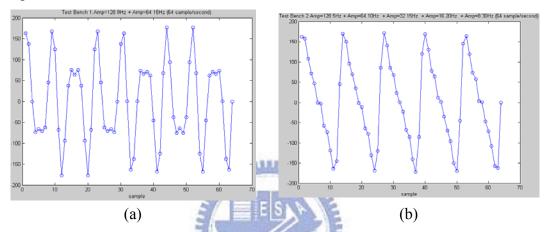

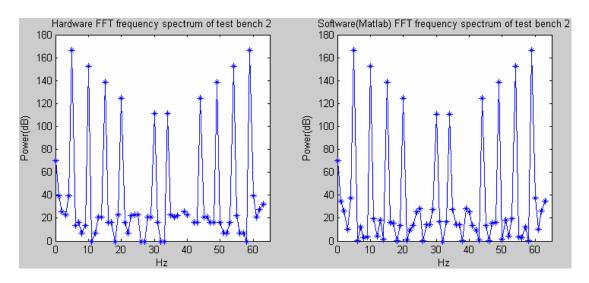

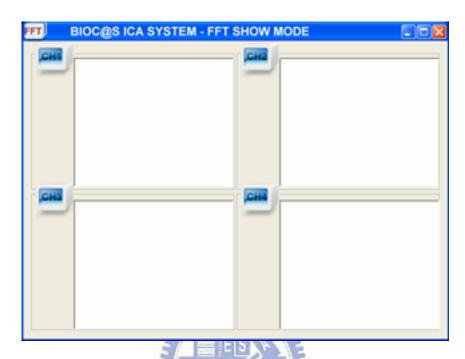

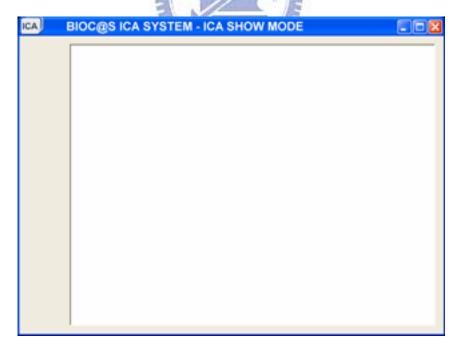

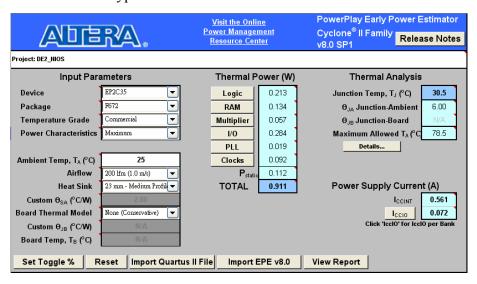

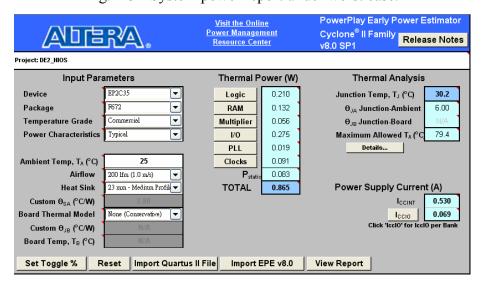

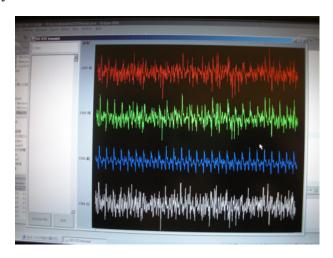

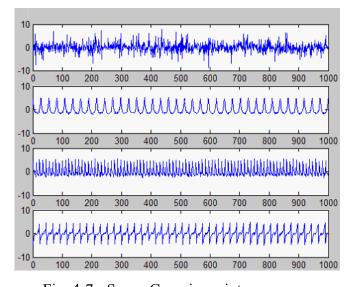

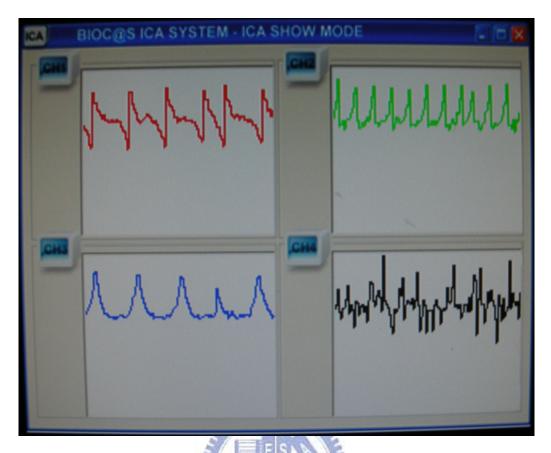

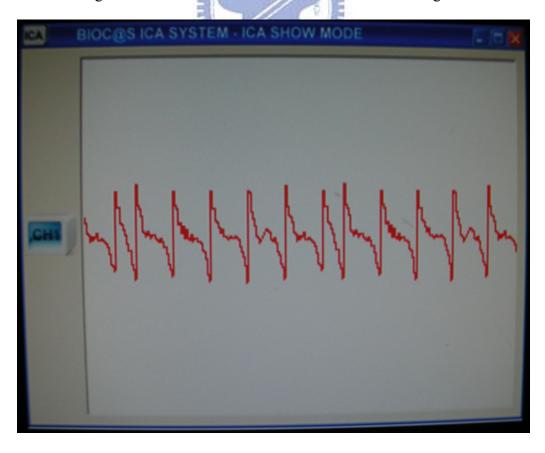

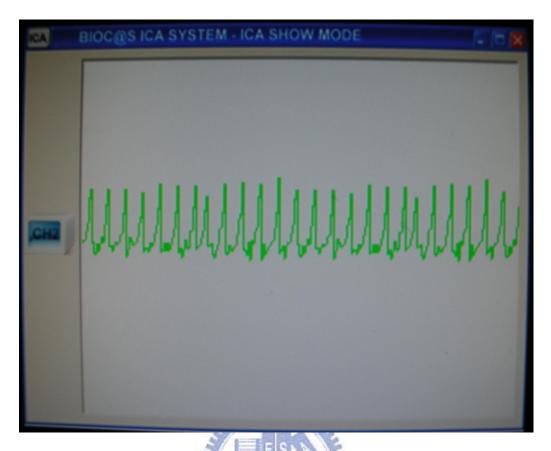

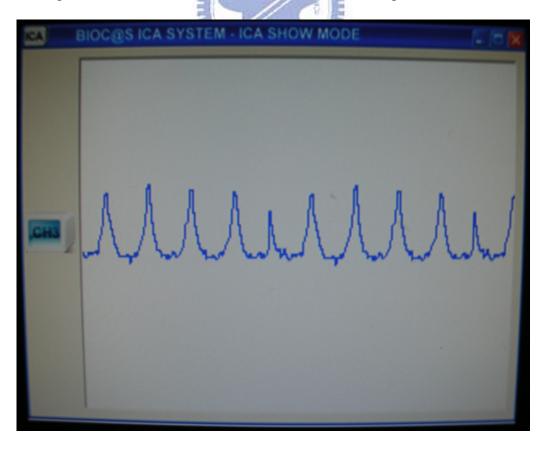

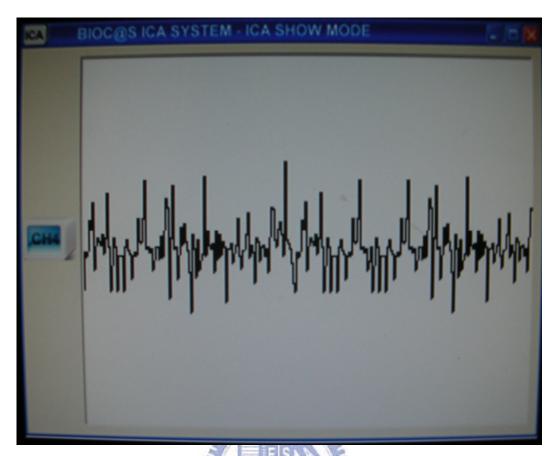

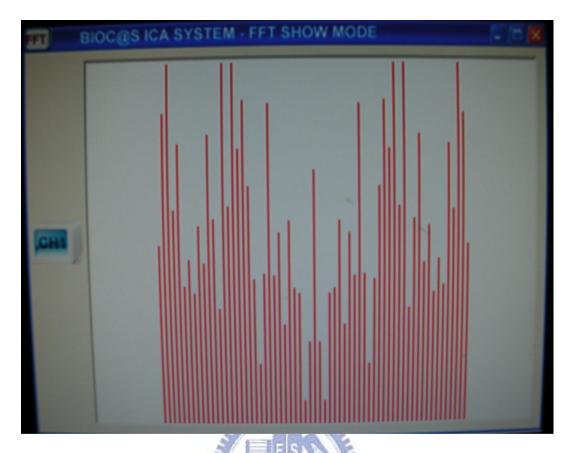

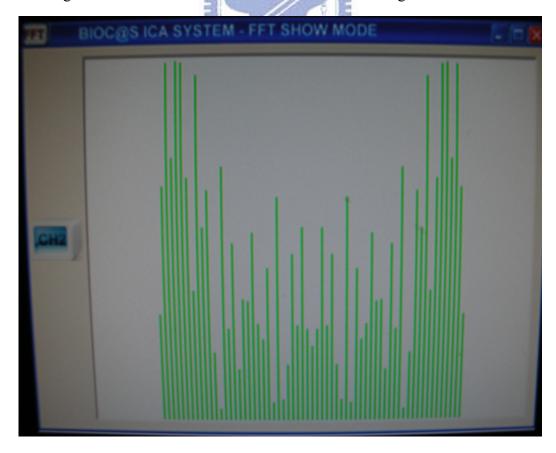

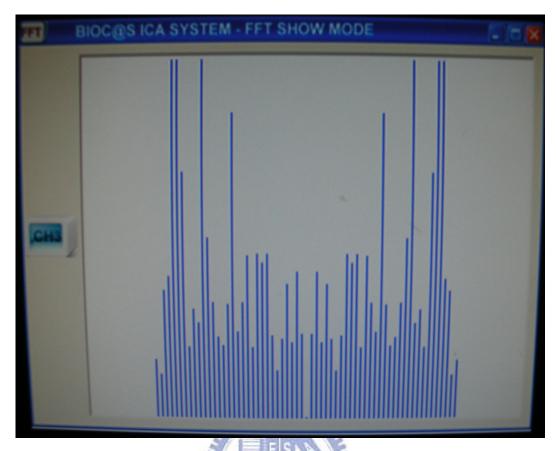

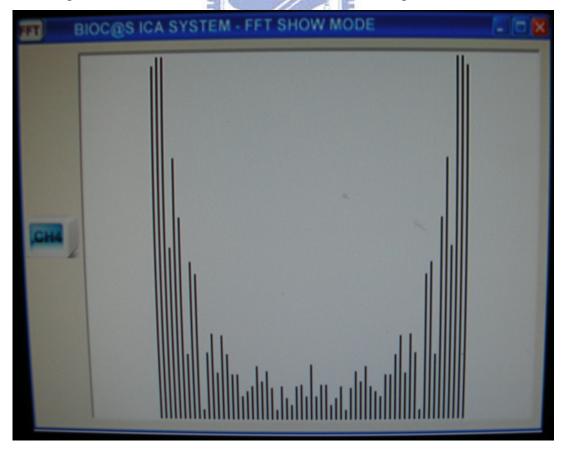

| Fig. 2-28 | Flow graph of complete decimation-in-frequency decomposition using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |