## 國立交通大學

電子工程學系 電子研究所

博士論文

新穎矽奈米線元件之研製與應用

Fabrication and Analysis of Novel Silicon Nanowire

Devices and Their Applications

研究生:蘇俊榮

指導教授:林鴻志博士

黄調 元博士

中華民國九十七年十二月

## 新穎矽奈米線元件之研製與應用

# Fabrication and Analysis of Novel Silicon Nanowire Devices and Their Applications

研究生:蘇俊榮 Student: Chun-Jung Su

指導教授:林鴻志 博士 Advisors: Dr. Horng-Chih Lin

黄調元 博士 Dr. Tiao-Yuan Huang

國立交通大學

電子工程學系 電子研究所

博士論文

A Dissertation

Submitted to Department of Electronics Engineering &

Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in

Electronics Engineering

December 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年十二月

## 新穎矽奈米線元件之研製與應用

研究生: 蘇俊榮 指導教授: 林鴻志 博士

黄調元 博士

國立交通大學電子工程學系電子研究所

#### 摘要

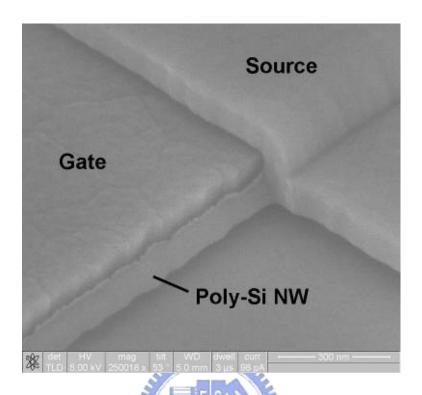

本文提出一新穎多晶矽奈米線電晶體之結構與製作。其製備之特點為利用一般製作側壁邊襯(sidewall spacer)之概念,來形成多晶矽邊襯,此邊襯之直徑可以準確地控制至 20 nm ~ 90 nm,故可巧妙地將之作為多晶矽奈米線通道。此外,相較於一般奈米線製備方式(top-down 和 bottom-up),本文所提出新結構的主要優越之處在於不需昂貴的設備和高門檻的技術,便可以簡易製程步驟來達到:(1)直接控制奈米線直徑和長度,(2)精準定義奈米線位置,(3)定義汲極和源極之同時,可自我對準形成奈米線通道,(4)再現性及可靠度高之多晶矽奈米線電子元件。

首先,藉由基本電性之探討結果,發現此多晶矽奈米線元件之開狀態(on-state)性能受到某種程度之限制,以及關狀態(off-state)時展現特殊的漏電流現象。這些

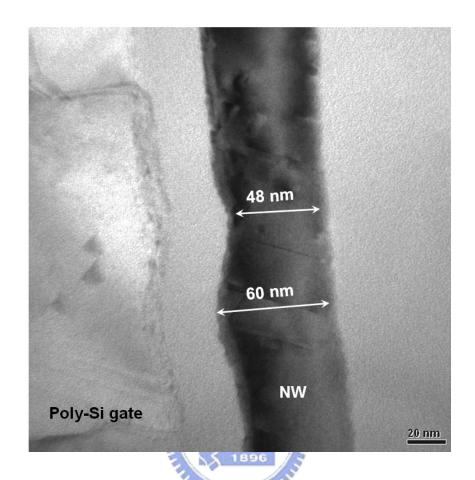

問題主要來自於固相結晶所形成之多晶矽具有相當多之缺陷,並且原本所設計之製程和結構有所缺失,而造成此獨特之漏電機制。此漏電流表現,可藉由本研究所提出之結構和製程修正方式明顯得到改善。此外,為了改善多晶矽之結晶品質,本研究使用電漿氫化處理來修補不完整鍵結之缺陷,以及利用金屬誘發側向結晶(MILC)或/和快速熱退火(RTA)的方式來增益奈米線本身的結晶特性。使用MILC 製程的過程中,我們發現奈米線的長度、寬度以及結晶引洞的排列,對所形成的薄膜結晶品質有很大之影響。再者,經由結合 MILC 和 RTA 處理之多晶矽奈米線,可以得到非常優異之元件性能。由 TEM 圖分析得知,在此條件下可以獲得具有單晶品質之矽奈米線,此良好結晶性質之矽奈米線可顯著地反映至元件的性能表現上。值得注意的是,在本研究中,元件可以得到高達 550 cm²/V-sec之電子遷移率和 230 cm²/V-s 之電洞遷移率,這些特性為目前奈米線相關文獻中的最佳成果。

除了改善薄膜結晶品質外,本研究更採用多重閘極結構來提升對奈米線通道之控制能力,進而增進元件性能表現。基於本研究電晶體巧妙之架構,多晶矽奈米線可精準地與側、下和上閘極排列。由於奈米線本身體積小,因此可以增強多重閘極之間的偶合作用,故在多重閘極的操控下,元件的性能可以大幅提升。傳統以雜質摻雜調整臨界電壓的方式,易導致奈米線中雜質分佈不均,而本結構的多重閘極可單獨施壓以調控通道之臨界電壓,此調控方式相當可靠且穩定,能避免雜質分佈不均之問題,因此本研究之多重閘極奈米線結構相當具有實用性。

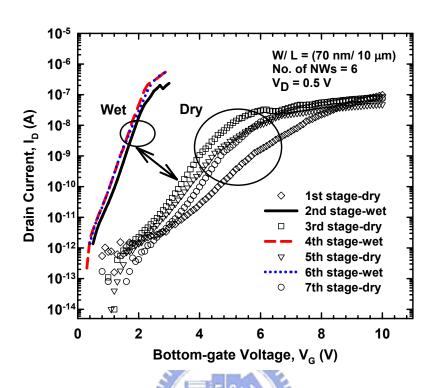

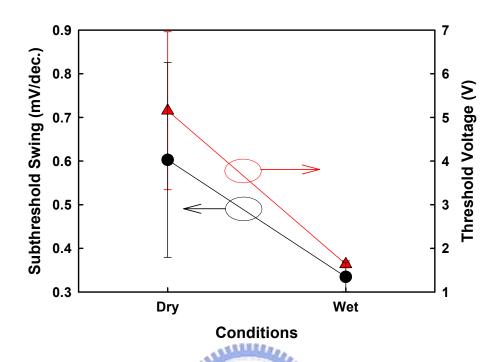

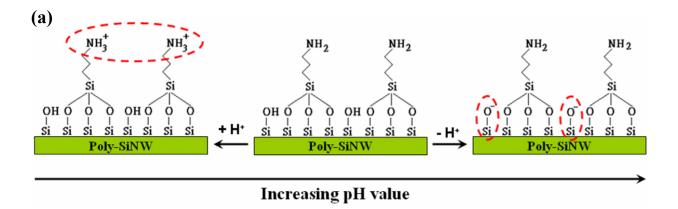

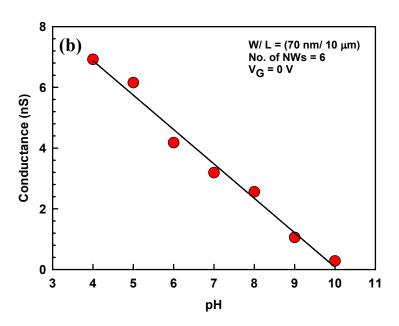

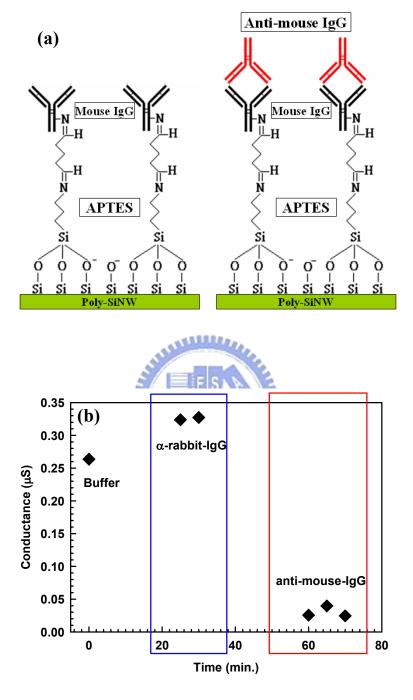

最後,本研究探討多晶矽奈米線用於感測應用方面之可行性。當今大部份的生化感測反應皆於水溶液中進行。而本研究發現,在水溶液中,此多晶矽奈米線元件之表現可以提升至與單晶矽相當,所以其感測靈敏度也會隨之升高。其可能的原因來自於水中的氫 $(H^{+})$ 或/和氫氧離子 $(OH^{-})$ 對於奈米線內的晶體缺陷,具有明顯且完整之修補作用,並且此修補作用具有再現性。因此,我們將表面具有特定接受器(receptor)之奈米線,進行pH值和生化分子之感測實驗,此奈米線展現相當不錯之感測能力和選擇性。

關鍵字:金屬誘發側向結晶,多重閘極,奈米線,電漿修補處理,多晶矽,快速

熱退火,感測器,側壁邊襯,固相結晶,薄膜電晶體

**Fabrication and Analysis of Novel Silicon**

Nanowire Devices and Their Applications

Student: Chun-Jung Su

Advisors: Dr. Horng-Chih Lin

Dr. Tiao-Yuan Huang

Department of Electronics Engineering & Institute of Electronics

National Chiao Tung University

A novel field-effect transistor (FET) using sidewall-spacer polycrystalline silicon

nanowire (poly-Si NW) channels is disclosed and investigated. This scheme features

well-controlled dimension, accurate positioning and alignment of NWs as well as

reliable source/drain (S/D) contacts. In addition, the approach is reproducible and

suitable for low-cost manufacturing.

From the examination of the basic electrical properties, an anomalous leakage

behavior and suppressed on-state performance are found. These issues are identified

to be due to a deficiency in the original device design and the inherent defective

crystallinity of solid-phase crystallized (SPC) poly-Si. With the structural and process

modifications proposed in this study, the unsatisfactory off-state characteristics could

iv

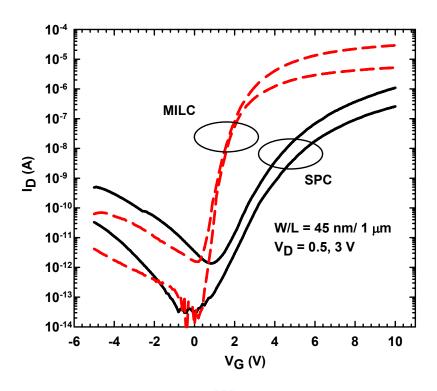

be effectively eliminated. To improve the poly-Si crystal property, plasma hydrogenation, metal-induced lateral crystallization (MILC) and/or rapid thermal annealing (RTA) techniques are employed to passivate the microstructural defects and enhance the crystallinity of the NWs, respectively. In the implementation of MILC process, it is shown that the arrangement of seeding window and the dimension of the NWs play an important role in affecting the resulting film quality. Furthermore, MILC coupled with RTA results in excellent device performance. With the TEM analyses, it is found that single-crystal-like NWs are achieved, leading to significant performance improvement. It is noteworthy that superior field-effect motilities up to 550 cm<sup>2</sup>/V-sec for electrons and 230 cm<sup>2</sup>/V-s for holes recorded in this study are among the best reported results for NW devices in the literature.

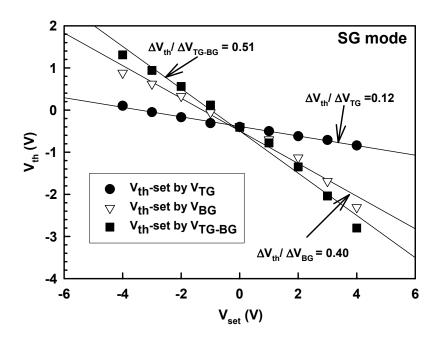

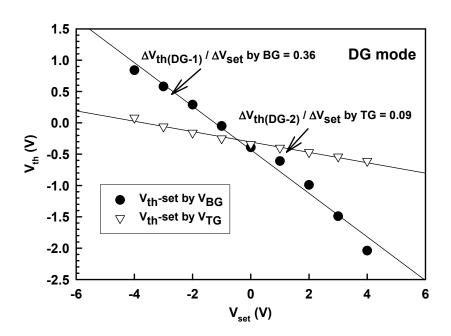

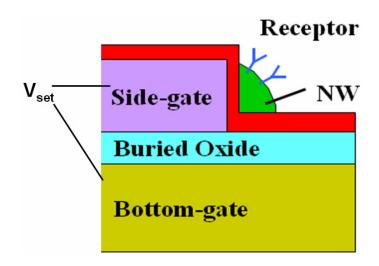

In addition to improving the film crystal property, an alternative strategy is to uplift the gate controllability over the channel with the adoption of multiple-gated (MG) configuration. Based on the proposed device structure, poly-Si NWs can be precisely positioned with respect to the side-gate, bottom-gate and top-gate. The strong gate coupling effect of the MG operation, which is ascribed to the tiny body of NW channels, thus dramatically promotes the device performance. Moreover, another great benefit of such scheme is that the independently applied gate bias can be employed to regularly adjust the threshold voltage ( $V_{th}$ ) of NW channels in a reliable

manner. The experimental results indicate that the  $V_{th}$  could be modulated by the gates with both positive and negative biases, making it suitable for practical applications.

Finally, the capability and feasibility of poly-Si NWs for sensing applications are investigated. In this work, the device performance is dramatically improved to a level comparable to the monocrystalline-Si counterparts, as poly-Si NW channels are exposed to the aqueous environment. Passivation of defects in the poly-Si NW by H<sup>+</sup> and/or OH contained in the aqueous solution is proposed to explain the phenomenon. Moreover, this passivation effect is stable and reproducible. This finding is especially important as it implies that poly-Si NWs can be cleverly operated in aqueous solutions to take advantage of the performance improvement. Consequently, by functionalizing specified receptors on their surface, poly-Si NWs exhibit good sensibility and selectivity for pH-value and biomolecules detections.

Keywords: Metal-induced Lateral Crystallization (MILC), Multiple Gate (MG),

Nanowire, Plasma Passivation, Polycrystalline Silicon (Poly-Si),

Rapid-thermal Annealing (RTA), Sensor, Sidewall Spacer, Solid-phase

Crystallization (SPC), Thin-film Transistor (TFT)

## 誌謝

由衷地感謝指導教授林鴻志博士和黃調元博士,博學多聞且無私的指導,以 及嚴謹的研究態度,著實為學習之典範,讓我受用一生。老師們對學生於獨立思 考能力之要求甚鉅,並總能適時地指點和鞭策,讓我在這些年中成長許多,對於 老師們的感激之情,著實難以用言語形容,僅能銘記在心。

特別感謝美國休士頓大學陳永松教授對於工程科學上之啟蒙指導,幫我開啟 了浩瀚學術領域之大門。謝謝交大材料系吳耀銓教授於大學專題時之指導,當時 所學之知識和實作經驗對於本論文助益匪淺。另外也感謝胡振國教授、賴朝松教 授、蔡銘進博士、陳明哲教授和崔秉鉞教授對於論文給予的實貴意見和指導。

本論文之完成另外得感謝共同參與奈米國家型計畫的楊裕雄教授和柯富祥 教授,以及李政哲、蕭程允和吳佳典等同學們,藉由此堅強團隊之腦力激盪和創 意開發,構築了本論文主要之架構,並開啟了許多新穎且值得深入探討之主題。

在此感謝先進元件技術實驗室所有同學們的相互鼓勵學習。感謝嘉裕學長耐心且詳盡地教導儀器之操作和經驗之分享,也謝謝宏年和明賢學長於實驗上之帶領和訓練。同時也感謝耀仁、文泰、冠麟、百宏學長和景森於研究上之討論和建議;感謝一起打拼、共同經歷爆肝生活的夥伴們:銑泓、行徽、凱翔、健銘、育峯、子銘、子儀、政雄、威臣、冠樟和漢仲等,謝謝你們於實驗上之協助和陪伴。另外,感謝國立交通大學和國家奈米元件實驗室提供良好的環境和完善的儀器設備,使研究之進行皆得以順利完成。

此外,感謝在德國期間共同於 RWTH Aachen 大學進行訪問研究的莊傑、宛 邵和凌珠,在異鄉生活有你們的陪伴和互相激勵,讓我擁有許多美好回憶。

最後,特別感謝我的父母:蘇文慶先生和黃玉燕女士,由於您們無私的付出,才能讓我無後顧之憂地不斷往前邁進;感謝姐姐、姐夫和最可愛的外甥們,讓我在求學的路途上,隨時感受到最溫暖的親情慰藉。感謝岳父母:汪建民博士、陳幼雪女士和妹妹一直以來的關心、鼓勵與支持;更要感謝在求學路途和生活上長久以來互相扶持的汪砡華小姐,與我分享度過無數個人生高低潮,一起於世界上各個角落留下我們的足跡,有了妳的陪伴是我最大的福分。

謹以此論文獻給我摯愛的家人、敬重的師長和所有的朋友。

蘇 俊 榮 誌於風城交大 戊子年甲子月

## **Contents**

| Abstract (Chinese)                                                                 | i    |

|------------------------------------------------------------------------------------|------|

| Abstract (English)                                                                 | iv   |

| Acknowledgement                                                                    | vii  |

| Contents                                                                           | viii |

| Table Captions                                                                     | xi   |

| Figure Captions                                                                    | xii  |

| Chapter 1 Introduction                                                             | 1    |

| 1.1 An Overview of Nanowires                                                       | 1    |

| 1.1.1 Top-down Approach                                                            | 2    |

| 1.1.2 Bottom-up Approach                                                           | 3    |

| 1.2 Low-temperature Crystallization Techniques                                     | 5    |

| 1.2.1 Solid-phase Crystallization                                                  | 5    |

| 1.2.2 Metal-induced Lateral Crystallization                                        | 7    |

| 1.3 Nanowire Sensor Devices                                                        | 9    |

| 1.4 Motivations of this Study                                                      | 10   |

| 1.5 Organizations of the Thesis                                                    | 12   |

| References                                                                         | 16   |

| Chapter 2 Novel Thin-Film Transistors Featuring Sidewall-Poly-Si Nanowire Channels | _    |

| 2.1 Introduction                                                                   | 28   |

| 2.2 Experimental                                                                   |      |

| 2.2.1 Solid-phase Crystallized Poly-Si NW TFTs                                     |      |

| 2.2.2 Metal-induced Lateral Crystallized Poly-Si NW TFTs                           | 32   |

| 2.2.3 Electrical Characterization Methods                                          | 35   |

| 2.3 Results and Discussions                                                        | 37   |

| 2.3.1 Fabricated Device Structure                                                  | 37   |

| 2.3.2 Basic Electrical Characteristics of SPC Poly-Si NW TFTs                      | 37   |

| 2.3.3 Impacts of Recrystallization and NW Formation Sequence                       | 38   |

| 2.3.4 Leakage Reduction in Poly-Si NW TFTs                                         | 41   |

| 2.3.5 Performance Enhancement of Poly-Si NW TFTs                                   | 43   |

| 2.4 Summary                                                                        | 50   |

| References                                                                                                  | 53      |

|-------------------------------------------------------------------------------------------------------------|---------|

| Chapter 3 Analyses of Silicon Nanowire Thin-Film Trans<br>Enhanced by Metal-Induced Lateral Crystallization |         |

| 3.1 Introduction                                                                                            | 92      |

| 3.2 Device Structure and Fabrication                                                                        | 94      |

| 3.3 Material Characterization                                                                               | 96      |

| 3.4 Electrical Characteristics of the Fabricated Devices                                                    | 99      |

| 3.4.1 Effects of Seeding Window Arrangement                                                                 | 99      |

| 3.4.2 Impacts of RTA on Device Performance                                                                  | 101     |

| 3.4.3 Forward and Reverse Modes of Operation in ASW Devices                                                 | 103     |

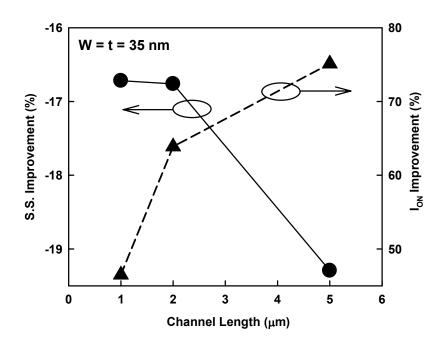

| 3.4.4 Length Effects on MILC Si NWs                                                                         | 105     |

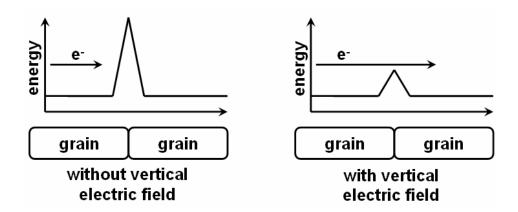

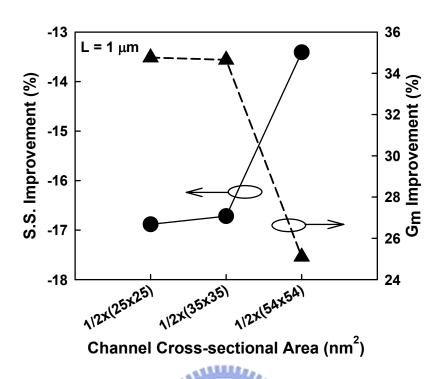

| 3.4.5 Width Effects on MILC Si NWs                                                                          | 107     |

| 3.5 Summary                                                                                                 |         |

| References                                                                                                  | 110     |

| Chapter 4 Poly-Si Nanowire Thin-Film Transistors                                                            | with    |

| Multiple-Gated Configuration                                                                                |         |

| 4.1 Introduction                                                                                            | 133     |

| 4.2 Device Structure and Fabrication.                                                                       | 135     |

| 4.2.1 Fabrication Process                                                                                   |         |

| 4.2.2 Device Structure and Operation Modes of NW TFTs                                                       |         |

| 4.3 Results and Discussion                                                                                  | 138     |

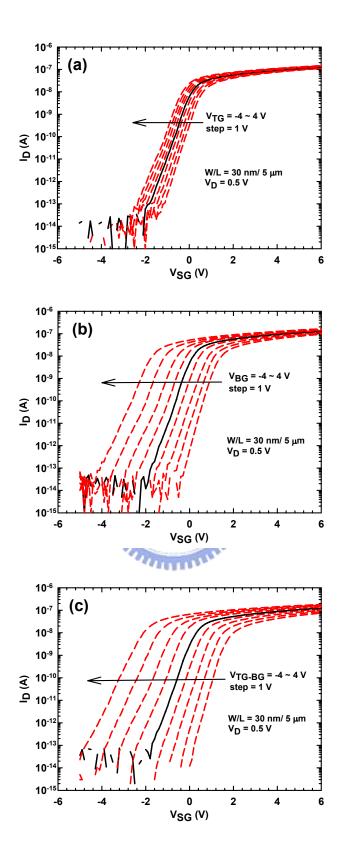

| 4.3.1 Multiple-gated Operation of NW TFTs                                                                   |         |

| 4.3.2 Effects of NW Channel Dimension                                                                       |         |

| 4.3.3 Tunable Threshold Voltage of MG NW TFTs                                                               | 142     |

| 4.4 Summary                                                                                                 | 145     |

| References                                                                                                  | 147     |

| Chapter 5 Sensing Devices Based on Poly-Si Nanowire Field-                                                  | -Effect |

| Transistors                                                                                                 |         |

| 5.1 Introduction                                                                                            | 173     |

| 5.2 Fabrications of Poly-Si NW Sensors                                                                      | 174     |

| 5.2.1 Fabrications of Poly-Si NW Sensing FETs                                                               | 174     |

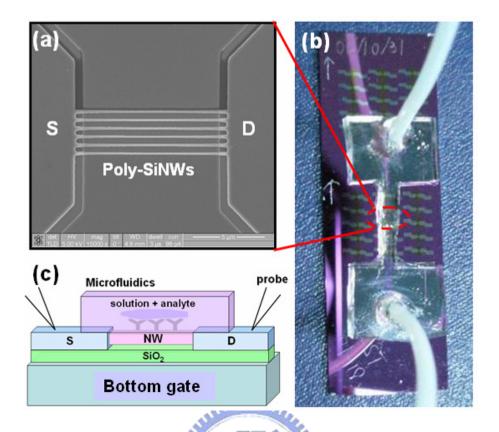

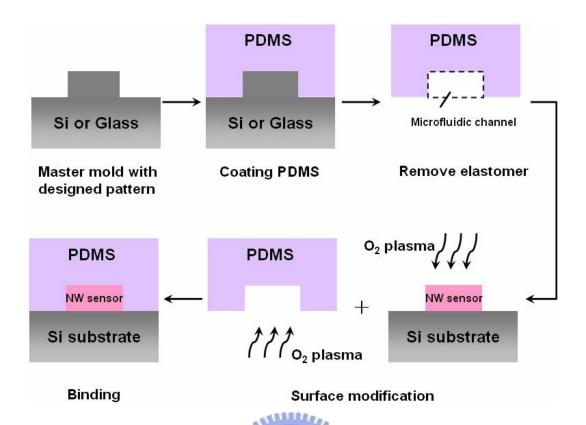

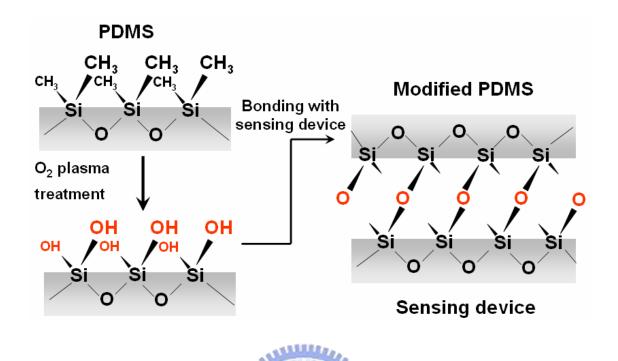

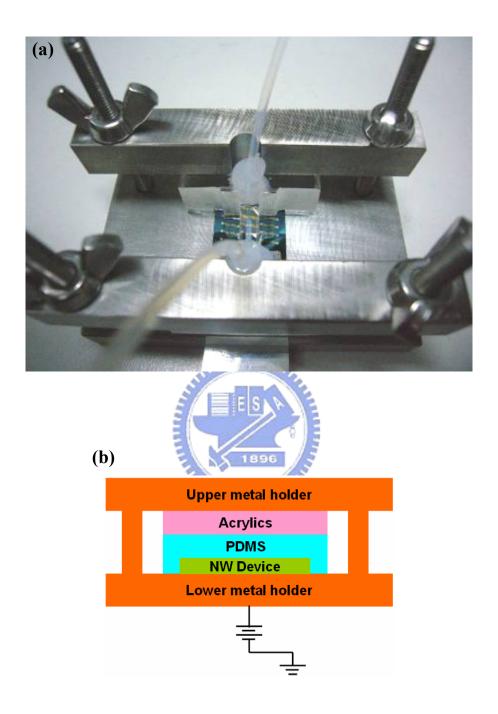

| 5.2.2 Preparations of Microfluidic Systems                                                                  | 175     |

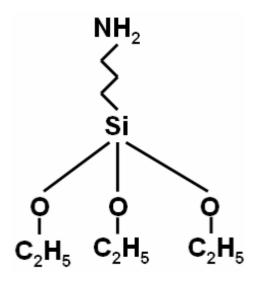

| 5.2.3 Immobilization of Biomolecules on Poly-Si NWs                                                         | 177     |

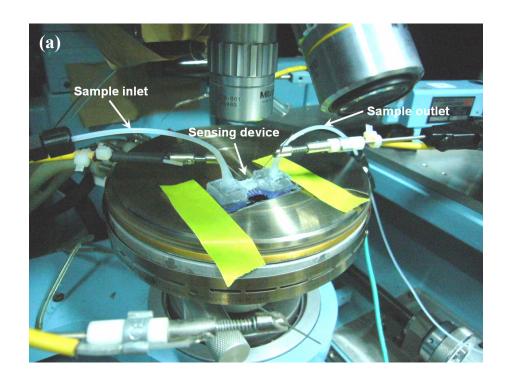

| 5.3 Experimental Setup                                                                                      | 178     |

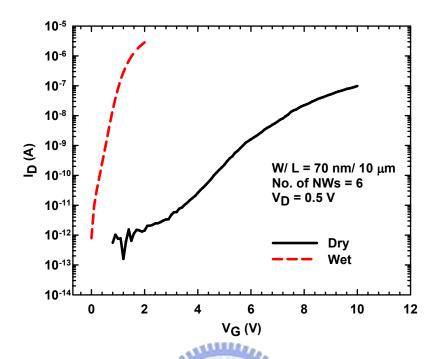

| 5.4 Analyses of Poly-Si NW Behaviors in De-ionized Water                                                    | 179     |

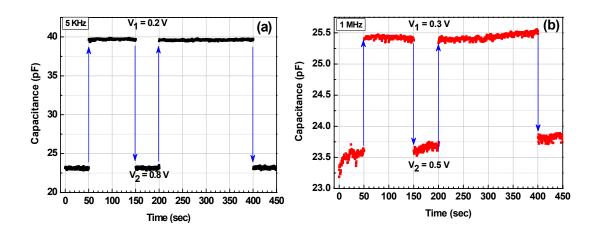

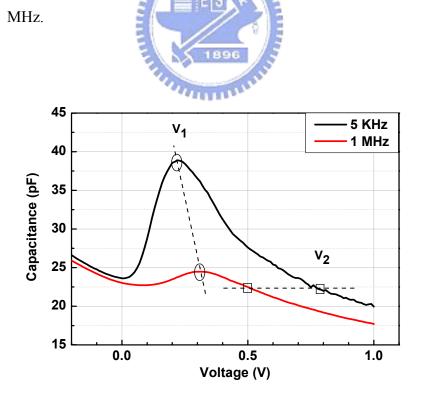

| 5.4.2 Mechanisms of Water Passivation Effects       181         5.4.3 Reproducibility of Water Passivation Effects       182         5.5. Poly-Si NW Sensing Devices       183         5.5.1 pH Sensing       183         5.5.2 Biomolecule Detection       184         5.6 Summary       185         References       187         Chapter 6 Conclusions and Future Works       201         6.1 Conclusions       201         6.2 Future Works       203         6.2.1 Morphology of the Poly-Si NWs       204         6.2.2 Smart Microfluidic System       204         6.2.3 Nano-electro-mechanical System       205         References       206         Appendix Capacitance-Voltage Characterizations of Silicon Nanodots Embedded in SiO2 Double-Barrier Structure       212         A.1 Introduction       212         A.2 Device Structure and Fabrication       215         A.3 Results and Discussions       217         A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes       217         A.3.2 Frequency-dependent Properties of the Capacitance Peaks       221         A.3.3 Stability of Resonant Tunneling Behaviors       226         A.4 Summary       228         A.5 Acknowledgment       228         References | 5.4.1 Electrical Characteristics                         | 179     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------|

| 5.5 Poly-Si NW Sensing Devices       183         5.5.1 pH Sensing       183         5.5.2 Biomolecule Detection       184         5.6 Summary       185         References       187         Chapter 6 Conclusions and Future Works       201         6.1 Conclusions       201         6.2 Future Works       203         6.2.1 Morphology of the Poly-Si NWs       204         6.2.2 Smart Microfluidic System       205         References       206         Appendix Capacitance-Voltage Characterizations of Silicon Nanodots Embedded in SiO2 Double-Barrier Structure       212         A.1 Introduction       212         A.2 Device Structure and Fabrication       215         A.3 Results and Discussions       217         A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes       217         A.3.2 Frequency-dependent Properties of the Capacitance Peaks       221         A.3.3 Stability of Resonant Tunneling Behaviors       226         A.4 Summary       228         A.5 Acknowledgment       228         References       230         Vita       233                                                                                                                                                             | 5.4.2 Mechanisms of Water Passivation Effects            | 181     |

| 5.5.1 pH Sensing       183         5.5.2 Biomolecule Detection       184         5.6 Summary       185         References       187         Chapter 6 Conclusions and Future Works       201         6.1 Conclusions       201         6.2 Future Works       203         6.2.1 Morphology of the Poly-Si NWs       204         6.2.2 Smart Microfluidic System       204         6.2.3 Nano-electro-mechanical System       205         References       206         Appendix Capacitance-Voltage Characterizations of Silicon Nanodots Embedded in SiO2 Double-Barrier Structure       212         A.1 Introduction       212         A.2 Device Structure and Fabrication       215         A.3 Results and Discussions       217         A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes       217         A.3.2 Frequency-dependent Properties of the Capacitance Peaks       221         A.3.3 Stability of Resonant Tunneling Behaviors       226         A.4 Summary       228         A.5 Acknowledgment       228         References       230         Vita       233                                                                                                                                                       | 5.4.3 Reproducibility of Water Passivation Effects       | 182     |

| 5.5.2 Biomolecule Detection       184         5.6 Summary       185         References       187         Chapter 6 Conclusions and Future Works       201         6.1 Conclusions       201         6.2 Future Works       203         6.2.1 Morphology of the Poly-Si NWs       204         6.2.2 Smart Microfluidic System       204         6.2.3 Nano-electro-mechanical System       205         References       206         Appendix Capacitance-Voltage Characterizations of Nanodots Embedded in SiO2 Double-Barrier Structure       212         A.1 Introduction       212         A.2 Device Structure and Fabrication       215         A.3 Results and Discussions       217         A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes       217         A.3.2 Frequency-dependent Properties of the Capacitance Peaks       221         A.3.3 Stability of Resonant Tunneling Behaviors       226         A.4 Summary       228         A.5 Acknowledgment       228         References       230         Vita       233                                                                                                                                                                                                  | 5.5 Poly-Si NW Sensing Devices                           | 183     |

| 5.6 Summary       185         References       187         Chapter 6 Conclusions and Future Works       201         6.1 Conclusions       201         6.2 Future Works       203         6.2.1 Morphology of the Poly-Si NWs       204         6.2.2 Smart Microfluidic System       205         6.2.3 Nano-electro-mechanical System       205         References       206         Appendix Capacitance-Voltage Characterizations of Nanodots Embedded in SiO2 Double-Barrier Structure       212         A.1 Introduction       212         A.2 Device Structure and Fabrication       215         A.3 Results and Discussions       217         A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes       217         A.3.2 Frequency-dependent Properties of the Capacitance Peaks       221         A.4 Summary       228         A.5 Acknowledgment       228         References       230         Vita       233                                                                                                                                                                                                                                                                                                                  | 5.5.1 pH Sensing                                         | 183     |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5.5.2 Biomolecule Detection                              | 184     |

| Chapter 6 Conclusions and Future Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.6 Summary                                              | 185     |

| 6.1 Conclusions       201         6.2 Future Works       203         6.2.1 Morphology of the Poly-Si NWs       204         6.2.2 Smart Microfluidic System       205         6.2.3 Nano-electro-mechanical System       205         References       206         Appendix Capacitance-Voltage Characterizations of Nanodots Embedded in SiO2 Double-Barrier Structure       212         A.1 Introduction       212         A.2 Device Structure and Fabrication       215         A.3 Results and Discussions       217         A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes       217         A.3.2 Frequency-dependent Properties of the Capacitance Peaks       221         A.3.3 Stability of Resonant Tunneling Behaviors       226         A.4 Summary       228         A.5 Acknowledgment       228         References       230         Vita       233                                                                                                                                                                                                                                                                                                                                                                    | References                                               | 187     |

| 6.2 Future Works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chapter 6 Conclusions and Future Works                   | 201     |

| 6.2.1 Morphology of the Poly-Si NWs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6.1 Conclusions                                          | 201     |

| 6.2.2 Smart Microfluidic System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6.2 Future Works                                         | 203     |

| Appendix Capacitance-Voltage Characterizations of Silicon Nanodots Embedded in SiO <sub>2</sub> Double-Barrier Structure 212  A.1 Introduction 215  A.2 Device Structure and Fabrication 215  A.3 Results and Discussions 217  A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes 217  A.3.2 Frequency-dependent Properties of the Capacitance Peaks 221  A.3.3 Stability of Resonant Tunneling Behaviors 226  A.4 Summary 228  A.5 Acknowledgment 228  References 230  Vita 233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.2.1 Morphology of the Poly-Si NWs                      | 204     |

| Appendix Capacitance-Voltage Characterizations of Silicon Nanodots Embedded in SiO <sub>2</sub> Double-Barrier Structure 212  A.1 Introduction 215  A.2 Device Structure and Fabrication 215  A.3 Results and Discussions 217  A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes 217  A.3.2 Frequency-dependent Properties of the Capacitance Peaks 221  A.3.3 Stability of Resonant Tunneling Behaviors 226  A.4 Summary 228  A.5 Acknowledgment 228  References 230  Vita 233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.2.2 Smart Microfluidic System                          | 204     |

| Appendix Capacitance-Voltage Characterizations of Silicon Nanodots Embedded in SiO <sub>2</sub> Double-Barrier Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6.2.3 Nano-electro-mechanical System                     | 205     |

| Nanodots Embedded in SiO <sub>2</sub> Double-Barrier Structure 212  A.1 Introduction 215  A.2 Device Structure and Fabrication 215  A.3 Results and Discussions 217  A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes 217  A.3.2 Frequency-dependent Properties of the Capacitance Peaks 221  A.3.3 Stability of Resonant Tunneling Behaviors 226  A.4 Summary 228  A.5 Acknowledgment 228  References 230  Vita 233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | References                                               | 206     |

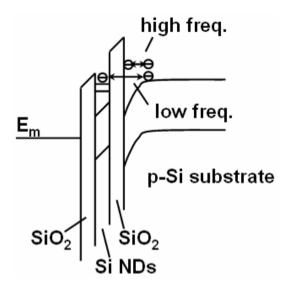

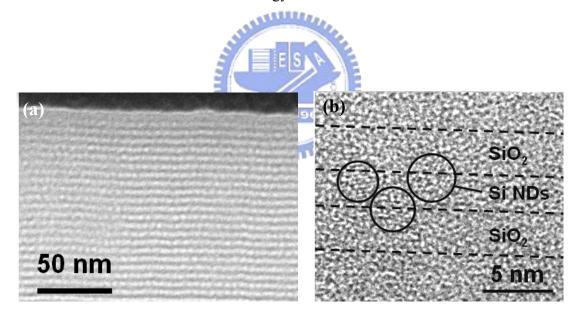

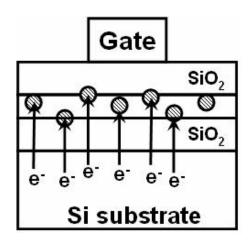

| A.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Nanodots Embedded in SiO <sub>2</sub> Double-Barrier Sta | ructure |

| A.2 Device Structure and Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          | 212     |

| A.2 Device Structure and Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A.1 Introduction                                         | 212     |

| A.3 Results and Discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |         |

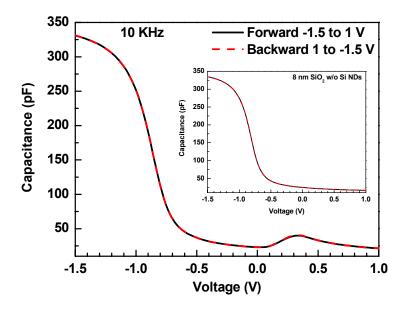

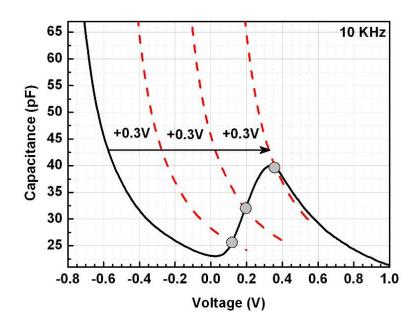

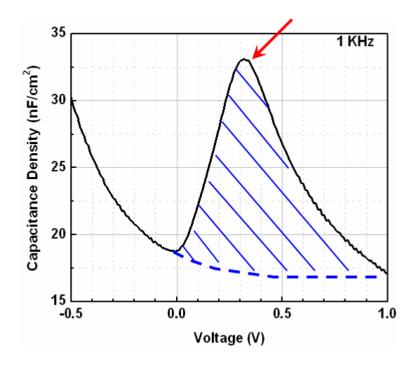

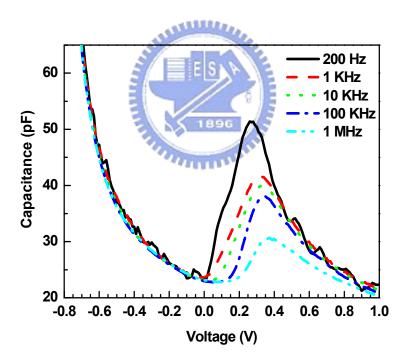

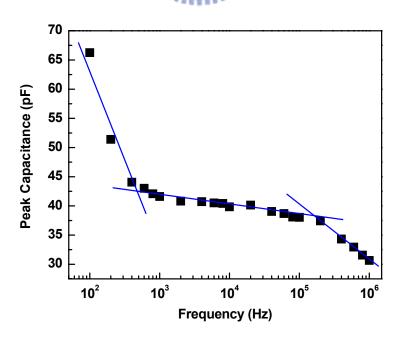

| A.3.1 Capacitance-voltage Characteristics of the Si ND Diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A.3 Results and Discussions                              | 217     |

| A.3.2 Frequency-dependent Properties of the Capacitance Peaks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |         |

| A.3.3 Stability of Resonant Tunneling Behaviors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                                        |         |

| A.4 Summary       228         A.5 Acknowledgment       228         References       230         Vita       233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |         |

| A.5 Acknowledgment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Ş                                                        |         |

| Vita233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                                        |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Vita                                                     | 233     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                          |         |

## **Table Captions**

| Chapter     | 2                                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2-I F | Parameters of plasma hydrogenation treatment                                                                                                                     |

| Table 2-II  | Summary of electrical parameters for poly-Si NW devices with various treatments.                                                                                 |

| Table 2-III | Summary of the device characteristics obtained in this work. Data reported in several previous publications in the literature are also included for comparisons. |

| Chapter     | 3                                                                                                                                                                |

| Table 3-I   | Comparisons of device parameters for ASW MILC and SSW MILC TFTs.                                                                                                 |

| Chapter     | 4                                                                                                                                                                |

|             | Active operating gates used in multiple-gated modes                                                                                                              |

| Chapter     |                                                                                                                                                                  |

|             | Comparisons of device performance parameters measured in dry and wet (DI water) ambients                                                                         |

| Chapter     | 6                                                                                                                                                                |

|             | Comparisons of Si NW formation between top-down, bottom-up and our approach                                                                                      |

## **Figure Captions**

| Chapter | 1 |

|---------|---|

| ~       |   |

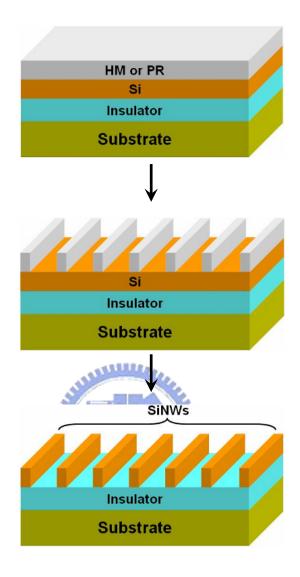

| Fig. 1-1 | Schematic illustration of Si NWs fabrication on SOI substrate by advanced lithography technique                                                                                                                                                                                                                                       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

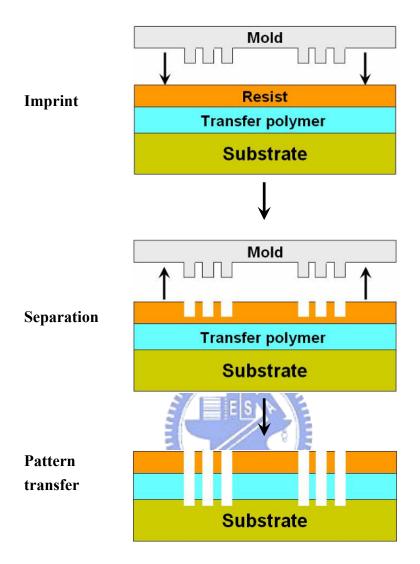

| Fig. 1-2 | Principle of imprint lithography: 1) mold with nano features is used to physically deform thin layer of resist; 2) mold is separated from the resist after curing; 3) nano patterns in resist are transferred into substrate22                                                                                                        |

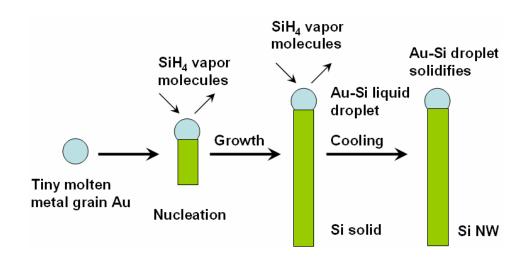

| Fig. 1-3 | Growth mechanism of nanowire by VLS method                                                                                                                                                                                                                                                                                            |

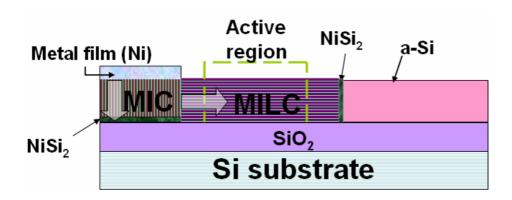

| Fig. 1-4 | Schematic illustration of the metal-induced crystallization (MIC) and metal-induced lateral crystallization (MILC). The arrows indicate the crystallization direction for each mechanism                                                                                                                                              |

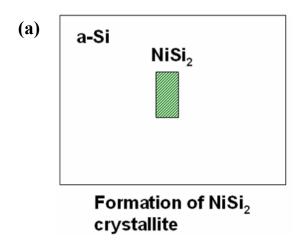

| Fig. 1-5 | Schematic representation of the formation of (a) NiSi <sub>2</sub> precipitate in a-Si network, and (b) c-Si crystallite after the migration of NiSi <sub>2</sub>                                                                                                                                                                     |

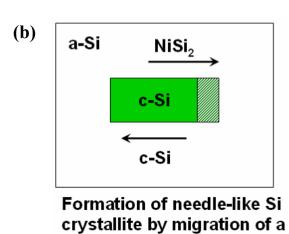

| Fig. 1-6 | Schematic equilibrium free energy diagram for NiSi <sub>2</sub> in contact with a-Si and c-Si.                                                                                                                                                                                                                                        |

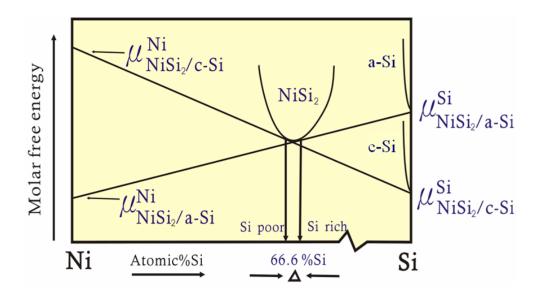

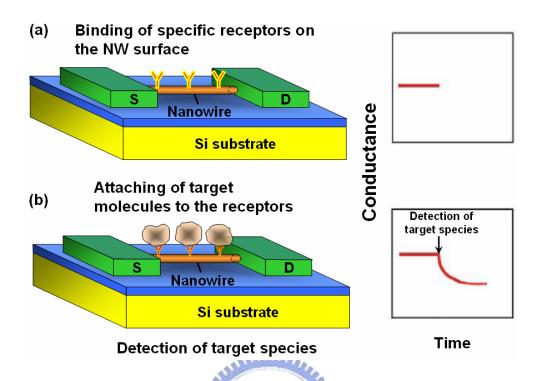

| Fig. 1-7 | Illustrations of sensing process for a Si NW device. (a) NW's surface is modified with specific receptors and the conductance is recorded. (b) Target species are introduced and attached to the receptors. If the NW device is n-type and the target molecules are negatively charged, then the corresponding conductance is reduced |

| Chapte   | er 2                                                                                                                                                                                                                                                                                                                                  |

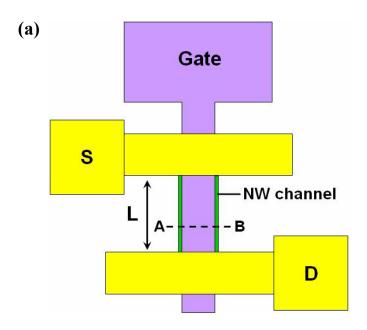

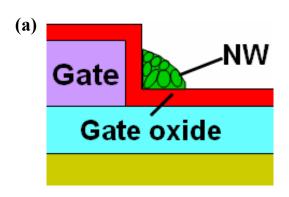

| Fig. 2-1 | (a) Top view of the proposed NW device, where channel length is defined as the spacing between source and drain, (b) cross-sectional view of the device along A-B direction in (a), featuring the NWs with sidewall spacer structure. Definitions of NW width and thickness are also illustrated                                      |

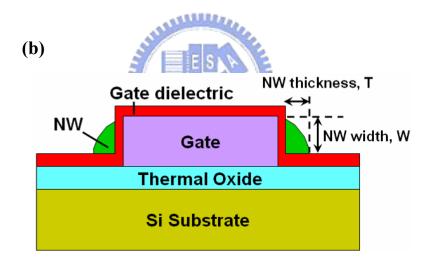

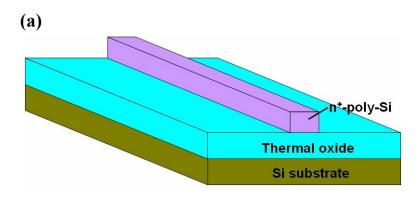

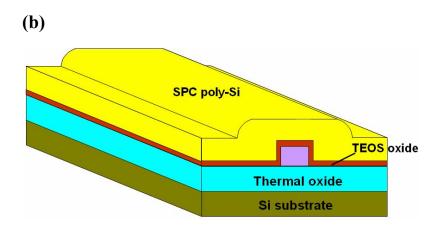

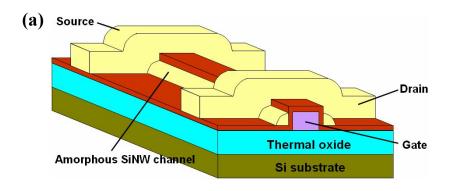

| Fig. 2-2 | Diagrams of major fabrication steps of the SPC poly-Si NW TFT. (a) Formation of n <sup>+</sup> -poly-Si gate on an oxidized Si substrate. (b) Deposition of the gate oxide, followed by solid-phase crystallized (SPC) poly-Si layer. (Continued)                                                                                     |

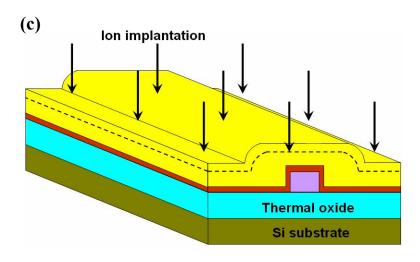

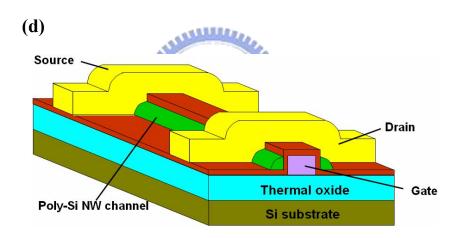

| Fig. 2-2 | (c) Low-energy S/D ion implantation into the poly-Si layer. The dashed contour indicates the projected range of ion implantation, which is located in the top portion of Si layer. (d) Schematic structure of the fabricated poly-Si NW TFT.                                                                                          |

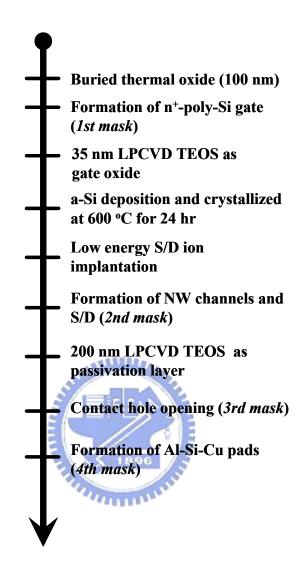

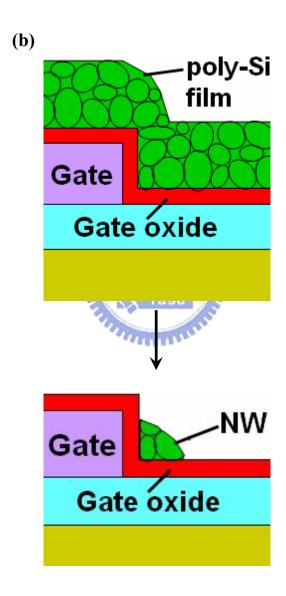

| Fig. 2-3 | Key fabrication flow of the poly-Si NW TFT. Only four masks are required in the whole process.                                                                                                                                                                               |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

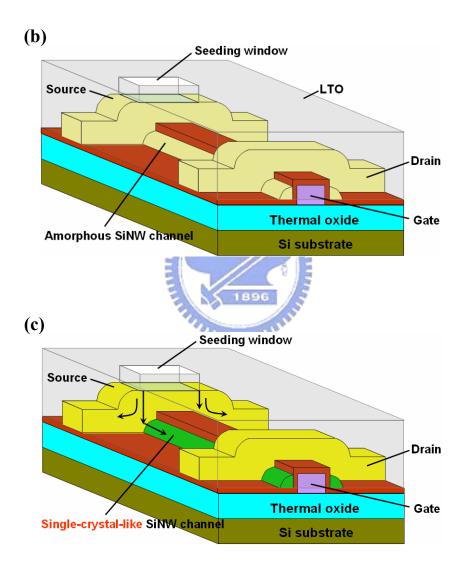

| Fig. 2-4 | 4 Diagrams of major fabrication steps of the MILC poly-Si NW TFT. (a) Formation of a basic amorphous Si NW TFT. (b) Deposition of LTO and patterning the seeding window. (c) Schematic device structure after MILC annealing. The arrows indicate crystallization directions |

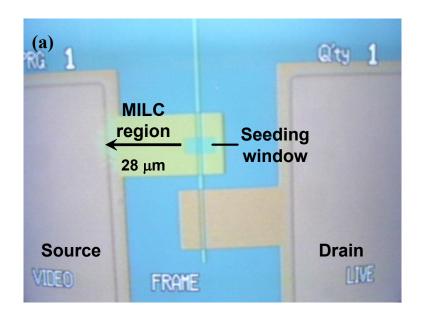

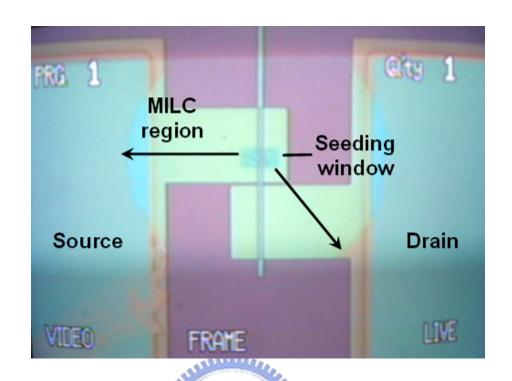

| Fig. 2-5 | 6 Optical micrograph (OM) photos of (a) n-type and (b) p-type MILC samples annealing at 550 °C for 16 hours                                                                                                                                                                  |

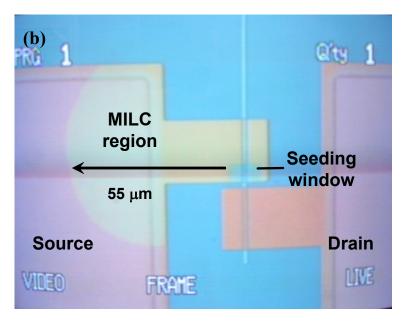

| Fig. 2-6 | MILC rate for n- and p-type doped poly-Si films.                                                                                                                                                                                                                             |

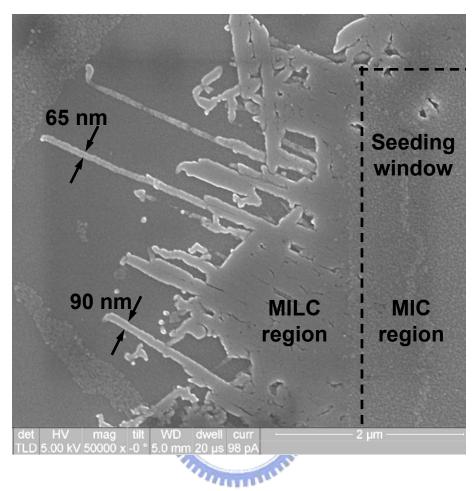

| Fig. 2-7 | 7 SEM image of MILC sample near the seeding window. Secco etching was used to remove most of amorphous Si                                                                                                                                                                    |

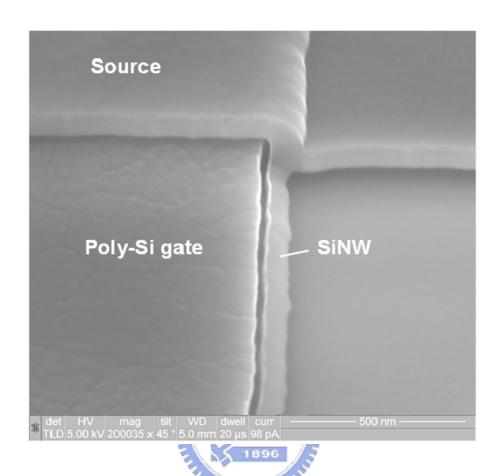

| Fig. 2-8 | SEM image shows the accurate alignment of NW channel with gate and reliable contact with source region.                                                                                                                                                                      |

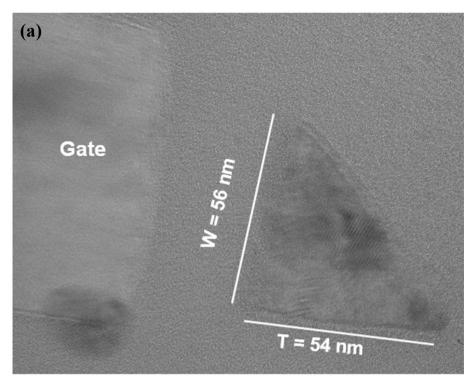

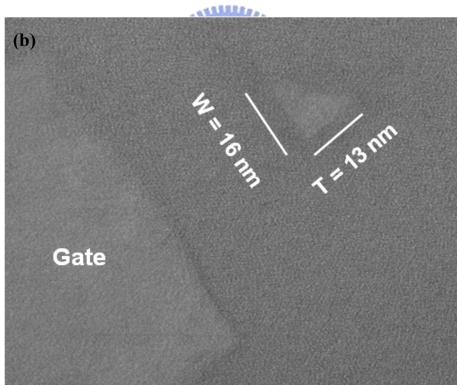

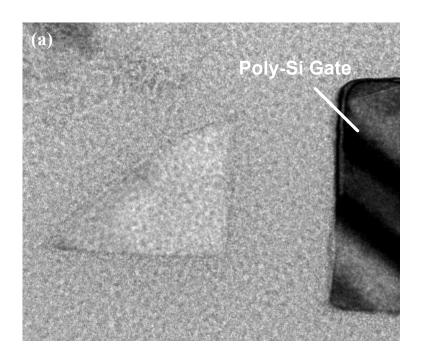

| Fig. 2-9 | TEM images of fabricated poly-Si NW TFTs. (a) NW size is 56 nm by 54 nm (b) NW dimension is 16 nm by 13 nm                                                                                                                                                                   |

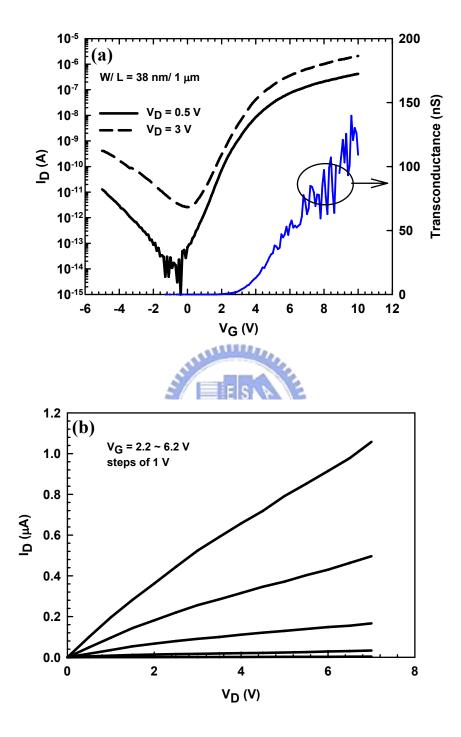

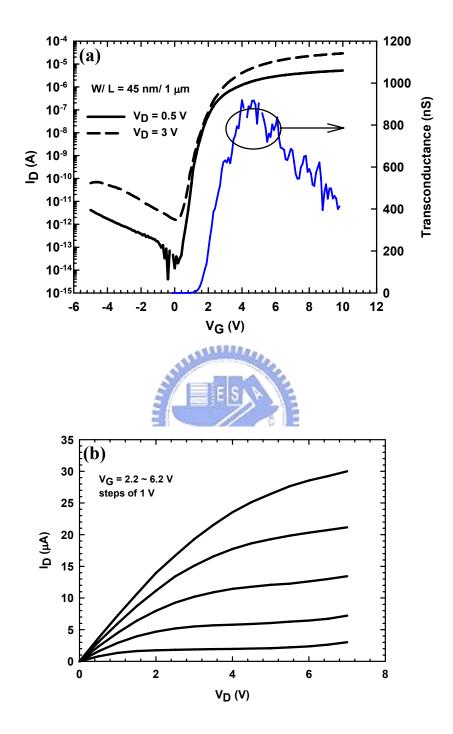

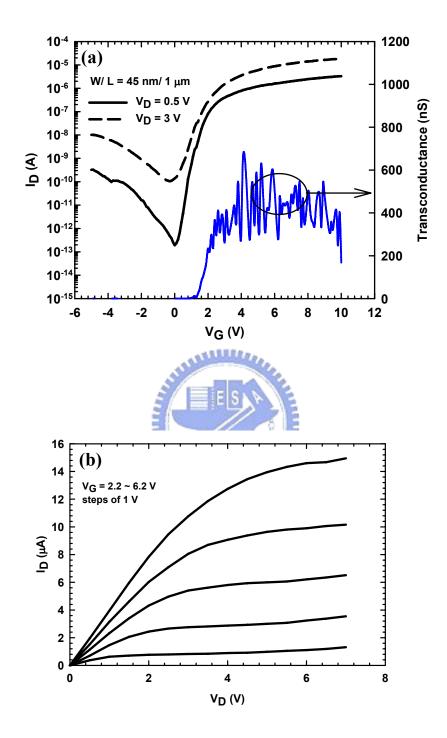

| Fig. 2-1 | 10 (a) Typical transfer and (b) output characteristics of the SPC poly-Si NW TFT67                                                                                                                                                                                           |

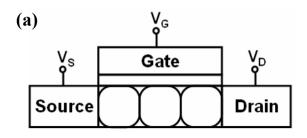

| Fig. 2-1 | 1 (a) Cross-sectional view of a poly-Si TFT, and potential distribution around the grain boundary (b) without and (c) with lateral electric field68                                                                                                                          |

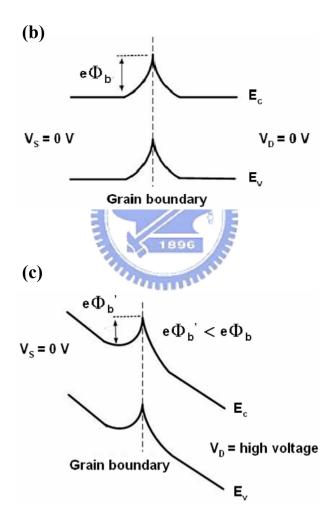

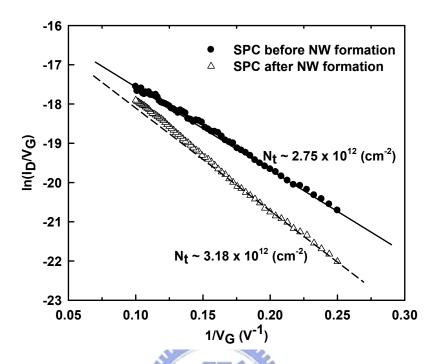

| Fig. 2-1 | 12 Transfer characteristics of poly-Si NW devices for SPC before/after NW formation                                                                                                                                                                                          |

| Fig. 2-  | 13 Schematic correlation between poly-Si NW crystal property and SPC process for SPC performed (a) after NW formation, and (b) before NW formation                                                                                                                           |

| Fig. 2-1 | 4 Plot of $ln(I_D/V_G)$ vs. $(1/V_G)$ and the extracted effective trap density of SPC poly-Si NW TFT. $I_D$ was measured at $V_D = 0.5$ V                                                                                                                                    |

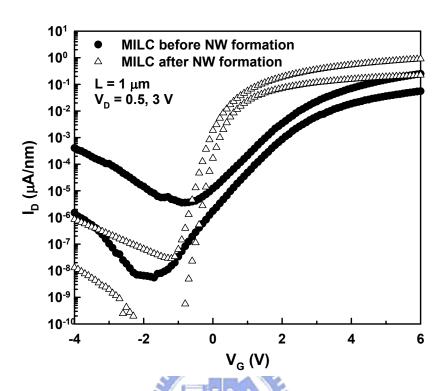

| Fig. 2-1 | 15 Transfer characteristics of poly-Si NW devices for MILC before and after NW formation                                                                                                                                                                                     |

| Fig. 2-1 | 6 OM photo of the MILC sample for MILC before NW formation                                                                                                                                                                                                                   |

| Fig. 2-  | 17 Top-view layout of the NW device showing gate-to-drain (GD) overlap region                                                                                                                                                                                                |

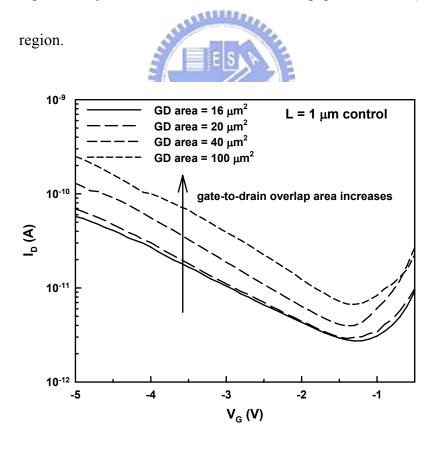

| Fig. 2-  | 18 Dependence of off-state current for poly-Si NW TFTs with various                                                                                                                                                                                                          |

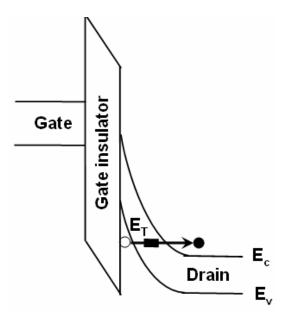

| showing (trap assisted) band-to-band tunneling                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

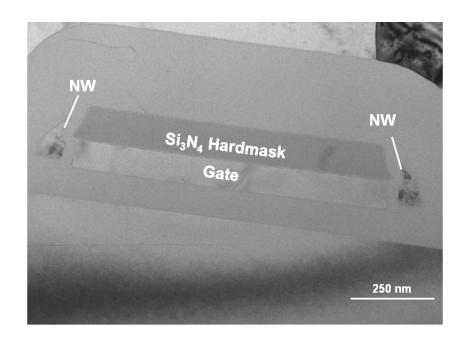

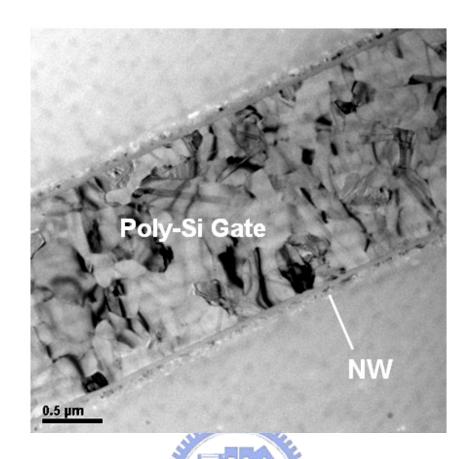

| Fig. 2-20 Cross-sectional-view TEM of the poly-Si NW TFT with hardmask structure                                                                                                                                                                      |

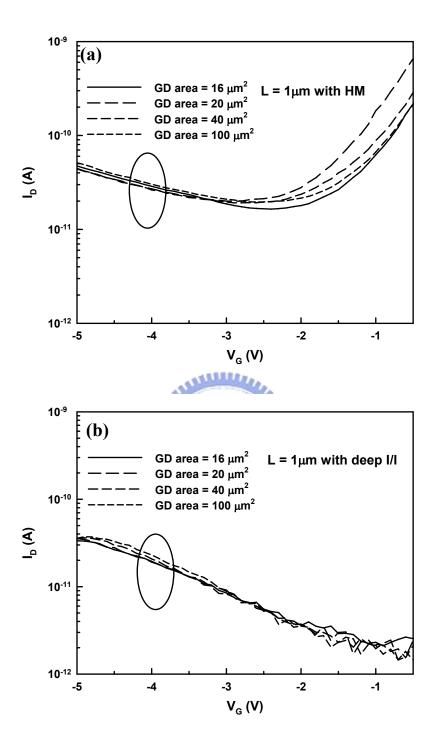

| Fig. 2-21 Off-state behaviors of the poly-Si NW TFTs with (a) hardmask and (b) deep ion implantation                                                                                                                                                  |

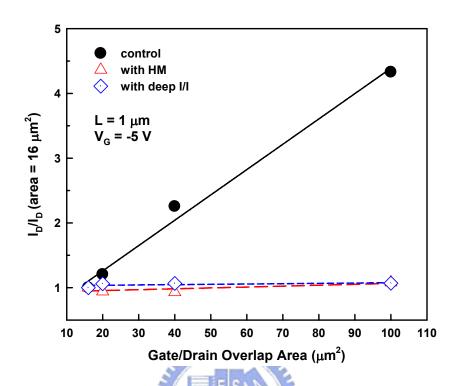

| Fig. 2-22 Normalized off-currents of the devices with different modification approaches                                                                                                                                                               |

| Fig. 2-23 Comparisons of transfer properties for the devices without and with plasma treatment.                                                                                                                                                       |

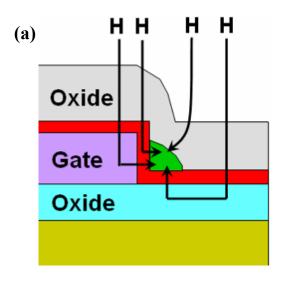

| Fig. 2-24 Diagrams illustrating possible pathways for hydrogen migration from the gas source to (a) poly-Si NW TFT and (b) planar TFT                                                                                                                 |

| Fig. 2-25 Comparisons of transfer characteristics for SPC and MILC poly-Si NW TFTs with NW channels.                                                                                                                                                  |

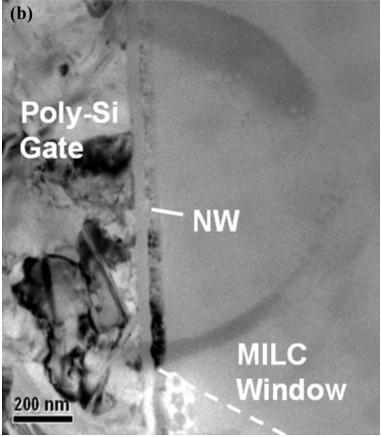

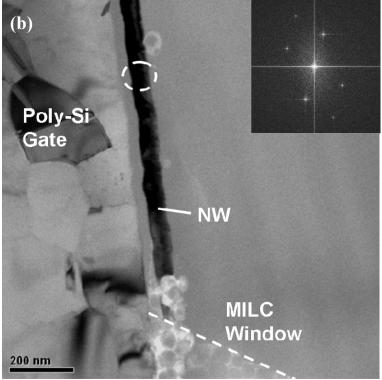

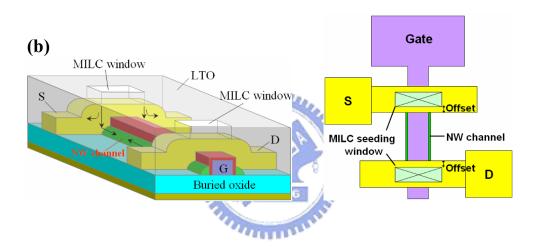

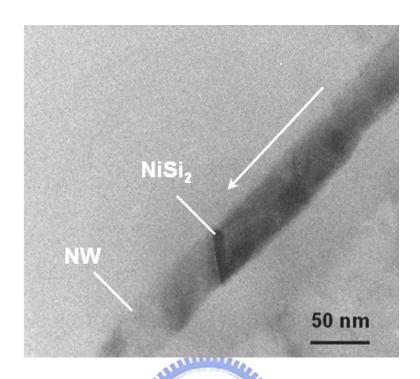

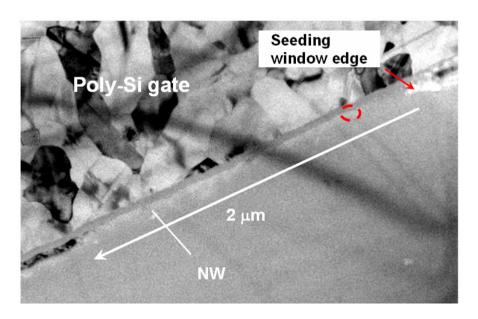

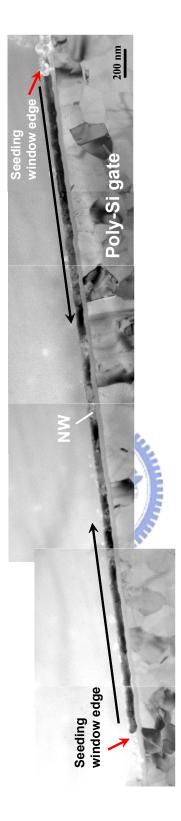

| Fig. 2-26 TEM images of MILC poly-Si NW device (a) cross-sectional view and (b plane-view near the MILC seeding window                                                                                                                                |

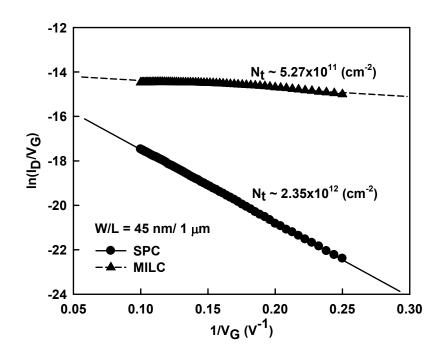

| Fig. 2-27 Plot of $ln(I_D/V_G)$ vs. $(1/V_G)$ and the extracted effective trap density of SPC and MILC poly-Si NW TFTs. $I_D$ were measured at $V_D = 0.5$ V                                                                                          |

| Fig. 2-28 Transfer characteristics of SPC NW devices before and after RTA treatment                                                                                                                                                                   |

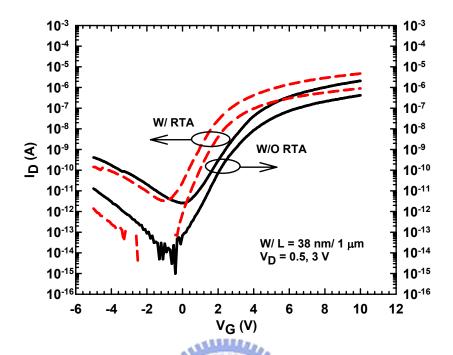

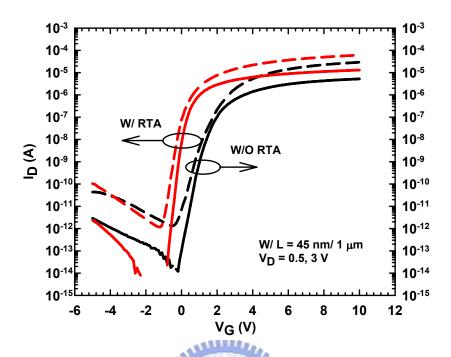

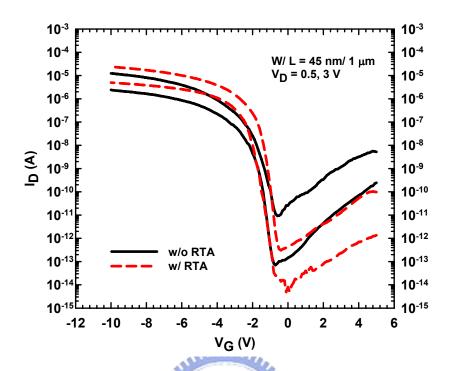

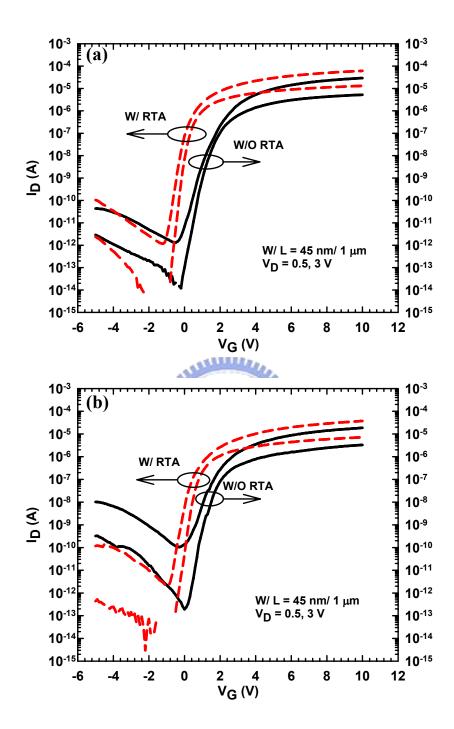

| Fig. 2-29 Transfer characteristics of MILC NW devices before and after RTA treatment                                                                                                                                                                  |

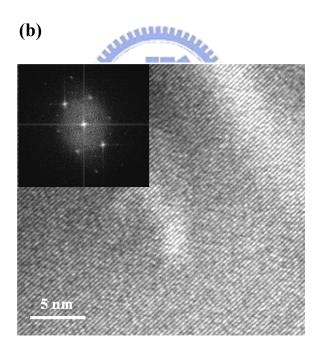

| Fig. 2-30 (a) Cross-sectional TEM and (b) plane-view TEM images of MILC device with RTA treatment. The selective diffraction pattern was taken from the circled region in (b), implying single-crystalline property87                                 |

| Fig. 2-31 Top-view TEM picture of SPC device with RTA treatment                                                                                                                                                                                       |

| Fig. 2-32 Transfer characteristics of MILC NW p-TFTs devices without and with RTA treatment                                                                                                                                                           |

| Chapter 3                                                                                                                                                                                                                                             |

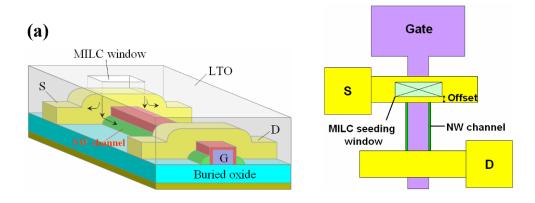

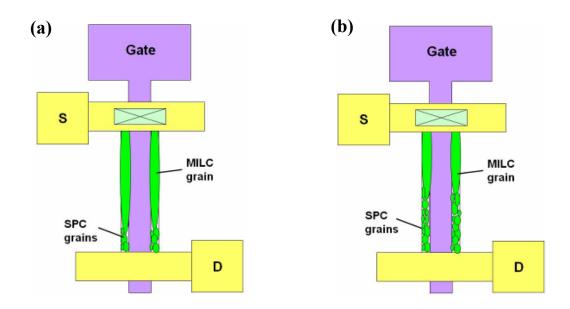

| Fig. 3-1 Top and side views of the MILC devices with (a) ASW and (b) SSW configurations. Note that NW spacers actually remain on the sidewall of the gate pad and gate-end regions, but are not shown in the top views of the devices for simplicity. |

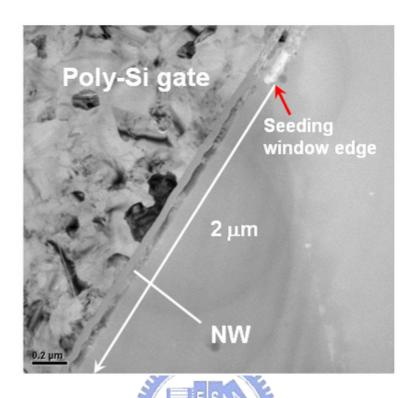

| The arrow indicates the crystallite proceeding direction                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3-3 Top-view TEM image of an MILC Si NW.                                                                                                                                                                                                                                                                                                                                |

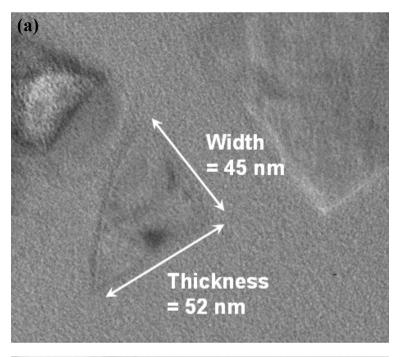

| Fig. 3-4 (a) TEM image of an MILC Si NW with RTA treatment. (b) A high-resolution view of the NW channel (the circled region in (a)) and the associated diffraction patterns.                                                                                                                                                                                                |

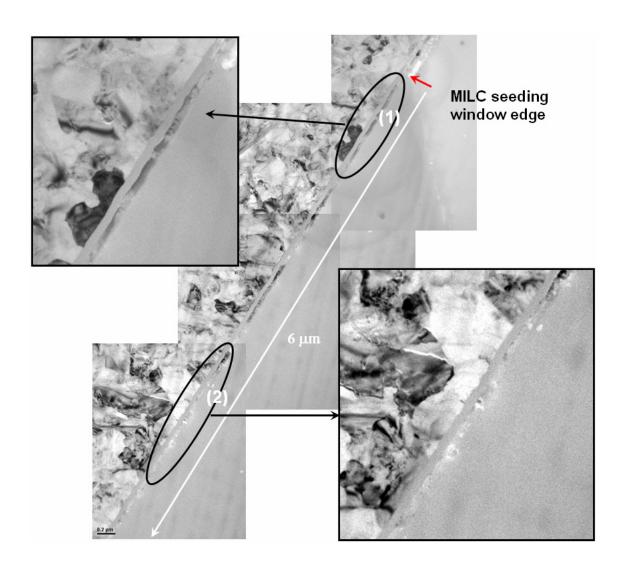

| Fig. 3-5 An overview on the crystallization region of an MILC Si NW. The inserpictures are enlarged view of region 1 (close to the seeding window) and region 2 (about 5 μm away from the seeding window) in the characterization region. Due to the distance effect, SPC mechanism also proceeds in region and leads to a smaller grain structure as compared with region 1 |

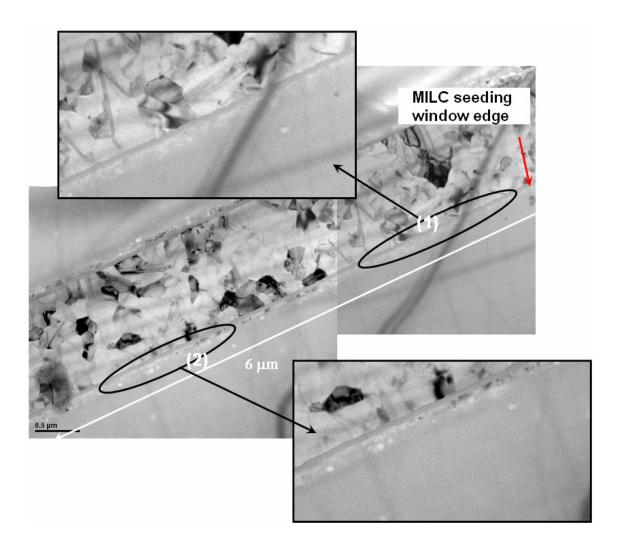

| Fig. 3-6 An overview on the crystallization region of an MILC Si NW with RTA treatment. The inset pictures are enlarged view of regions 1 and 2 in the characterization region. Note that the grain structure in region 2 is no significantly affected by the RTA treatment                                                                                                  |

| Fig. 3-7 (a) Transfer and (b) output characteristics of an MILC device with ASV configuration.                                                                                                                                                                                                                                                                               |

| Fig. 3-8 (a) Transfer and (b) output characteristics of an MILC device with SSW configuration.                                                                                                                                                                                                                                                                               |

| Fig. 3-9 Transfer characteristics of MILC devices with (a) ASW and (b) SSW configuration with and without RTA treatment                                                                                                                                                                                                                                                      |

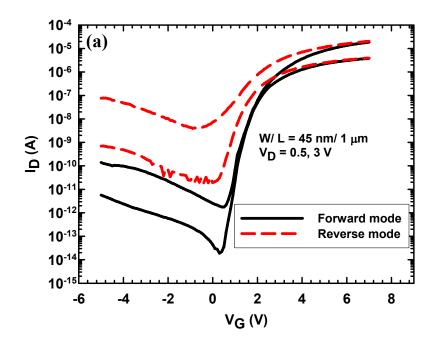

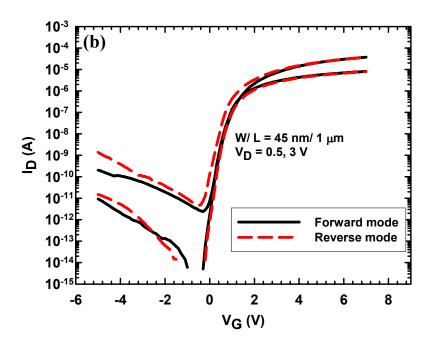

| Fig. 3-10 Transfer characteristics of ASW MILC devices (a) without and (b) with RTA treatment under forward and reverse modes of operation                                                                                                                                                                                                                                   |

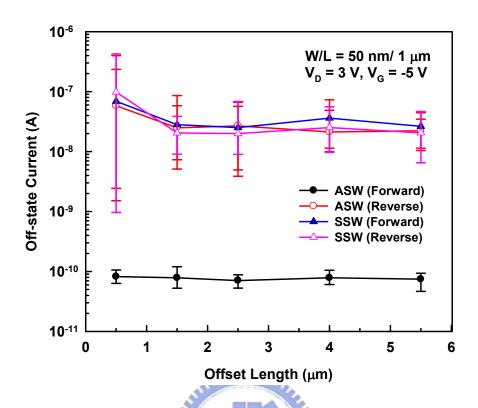

| Fig. 3-11 Off-state leakage current as a function of the offset length for ASW and SSW devices operated in forward and reverse modes, respectively. The number of devices characterized for each condition is 20                                                                                                                                                             |

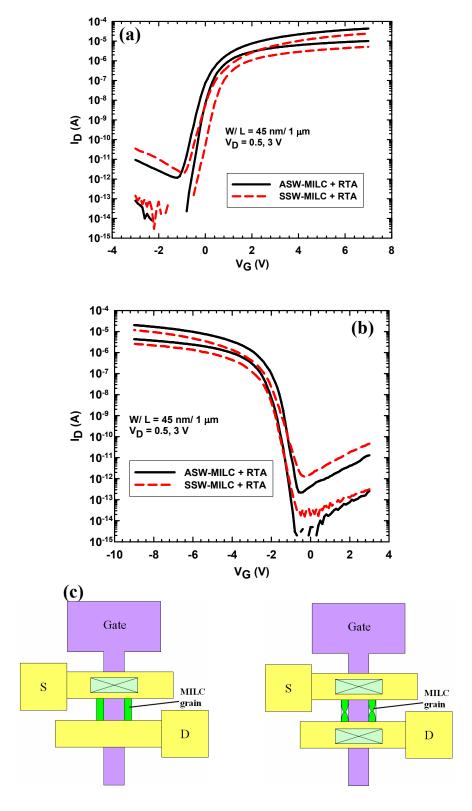

| Fig. 3-12 Comparisons of transfer characteristics for ASW and SSW structures with I = $1\mu m$ in (a) n-TFTs and (b) p-TFTs. (c) Schematic grain distribution in NW channels for ASW and SSW configurations.                                                                                                                                                                 |

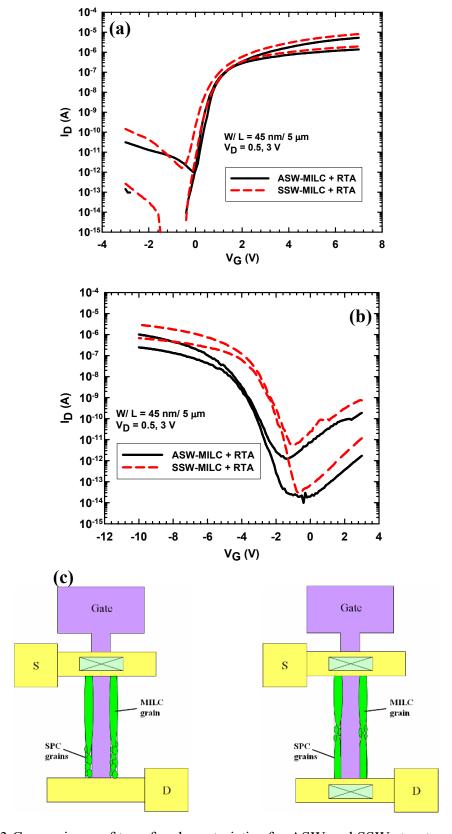

| Fig. 3-13 Comparisons of transfer characteristics for ASW and SSW structures with I = $5 \mu m$ in (a) n-TFTs and (b) p-TFTs. (c) Schematic grain distribution in NW channels for ASW and SSW configurations.                                                                                                                                                                |

| Fig. 3-14 Successive TEM pictures taken in the two adjacent seeding windows128                                                                                                                                                                                                                                                                                               |

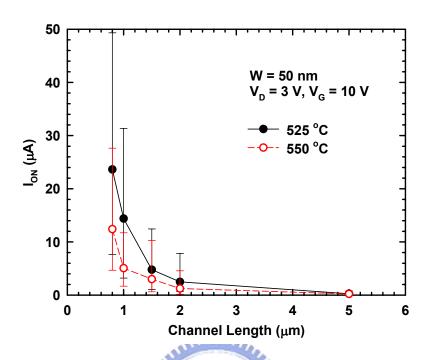

| Fig. 3-15 On-current as a function of the channel length for devices re-crystallized a                                                                                                                                                                                                                                                                                       |

| 525 °C and 550 °C, respectively. The number of devices characterized for each condition is 20.                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3-16 Schematic illustration for the crystallinity of NW channels performed at (a lower and (b) higher annealing temperatures during MILC process130                                                                                                                                                                                                                                                                                                      |

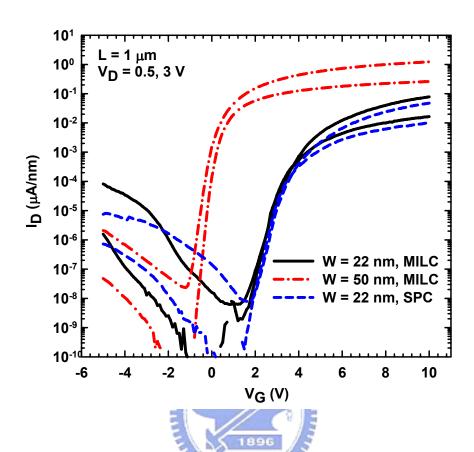

| Fig. 3-17 Transfer characteristics of NW devices with various NW widths an crystallization approaches. All samples received RTA post-treatment. Not that the SPC sample was performed at 550 °C for 16 hours                                                                                                                                                                                                                                                  |

| Chapter 4                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

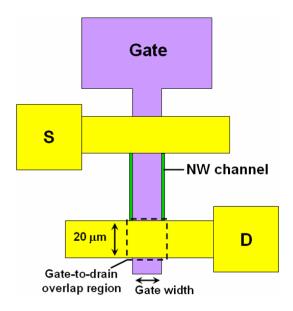

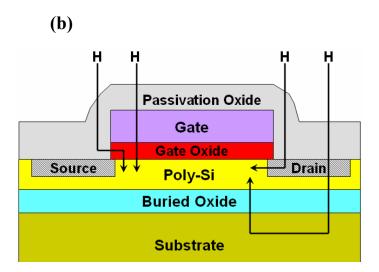

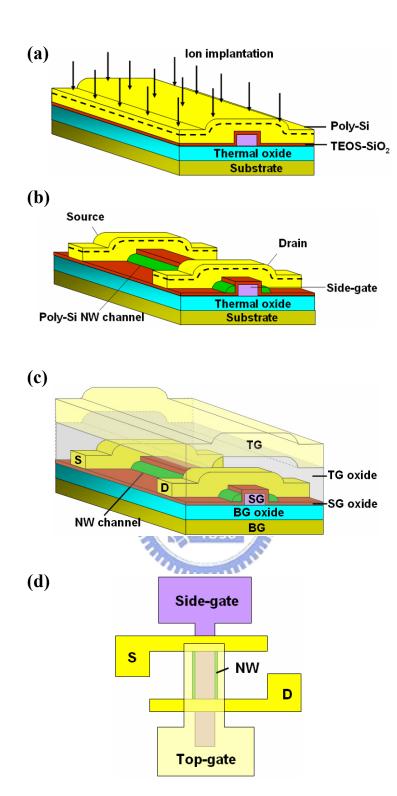

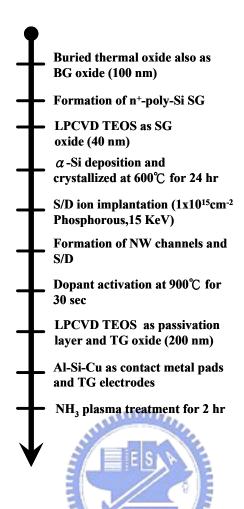

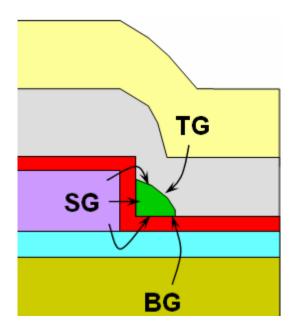

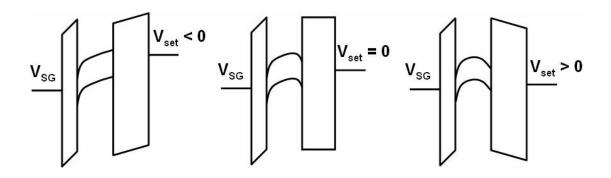

| Fig. 4-1 Key fabrication steps of the MG NW TFT. (a) Source/drain ion implantation The dashed line represents the projected range which is near the top surfac due to the low implant energy used. (b) Formation of source, drain and NV channels. The NW channels remain undoped due to the low implant energ used. (c) Stereo-view of the fabricated NW TFT. Top-, side-, an bottom-gates are formed in the structure. (d) Top-view of the fabricate device |

| Fig. 4-2 Process flow for the fabrication of MG NW TFTs                                                                                                                                                                                                                                                                                                                                                                                                       |

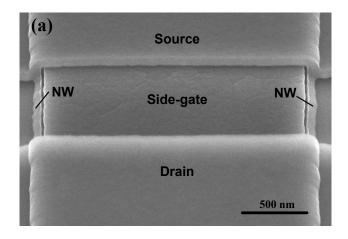

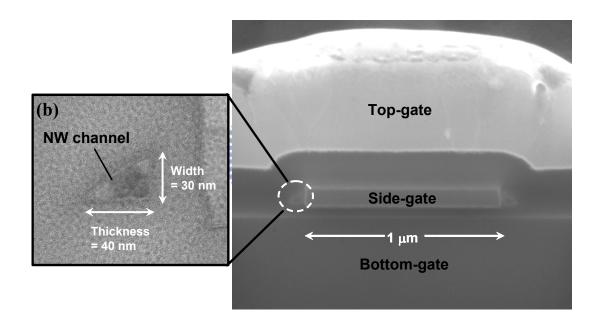

| TEM image of a NW channel specifying the width and thickness                                                                                                                                                                                                                                                                                                                                                                                                  |

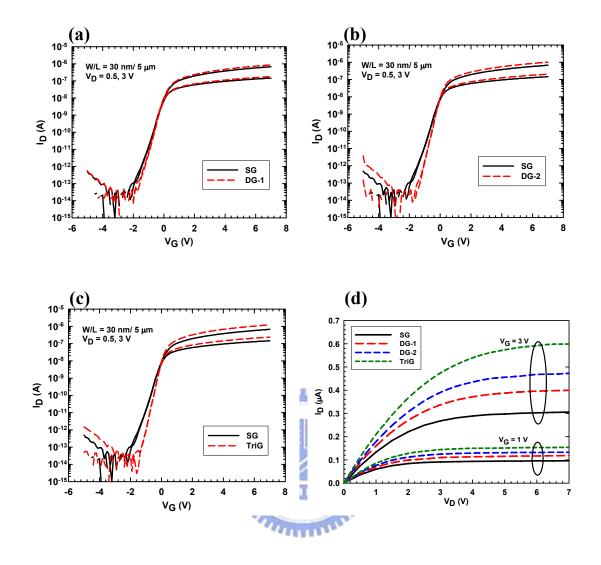

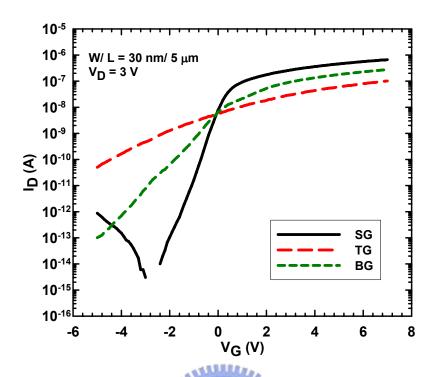

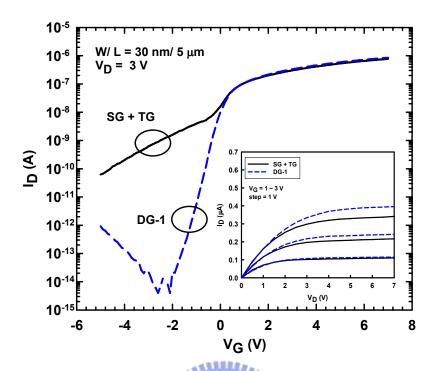

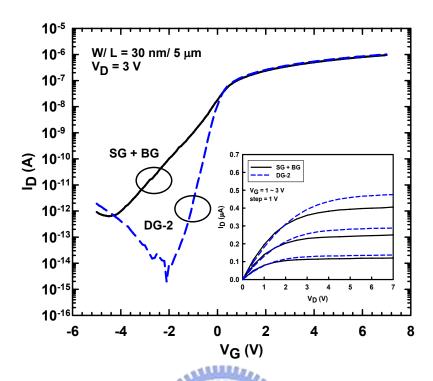

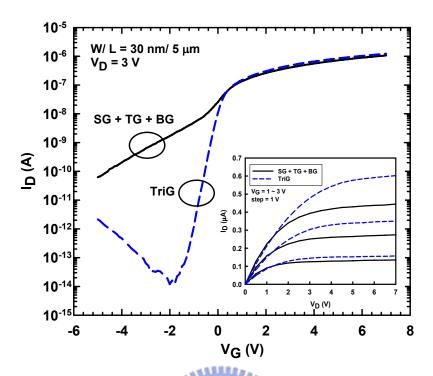

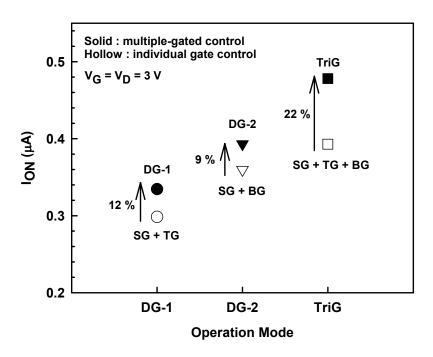

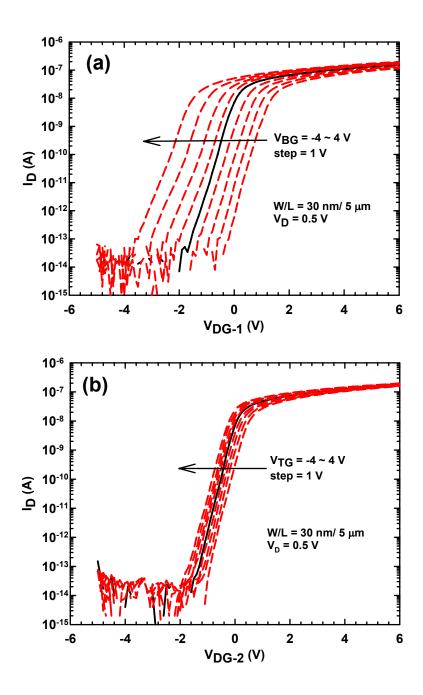

| Fig. 4-5 Typical transfer characteristics of a NW TFT under (a) DG-1, (b) DG-2 and (c) TriG modes of operations compared with SG mode, respectively. (d) Comparisons of output characteristics between MG and SG modes of operations                                                                                                                                                                                                                          |

| Fig. 4-6 Transconductance characteristics of a NW device under various modes of operation.                                                                                                                                                                                                                                                                                                                                                                    |

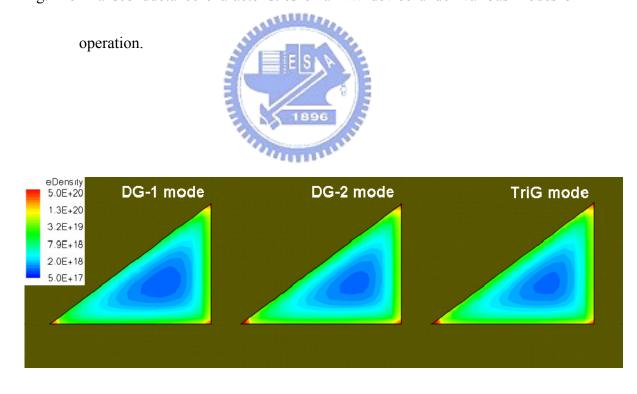

| Fig. 4-7 2-dimensional simulation of electron density (eDensity) in NWs under DG-1 DG-2 and TriG modes of operation. The applied gate voltage is 5 V156                                                                                                                                                                                                                                                                                                       |

| Fig. 4-8 I-V curves of single-gated mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                        |

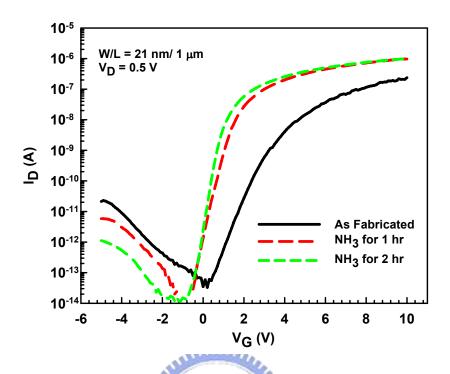

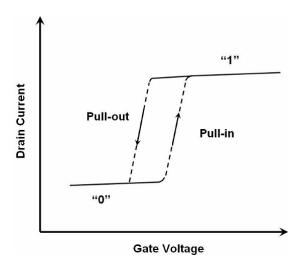

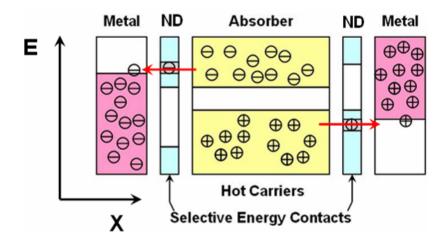

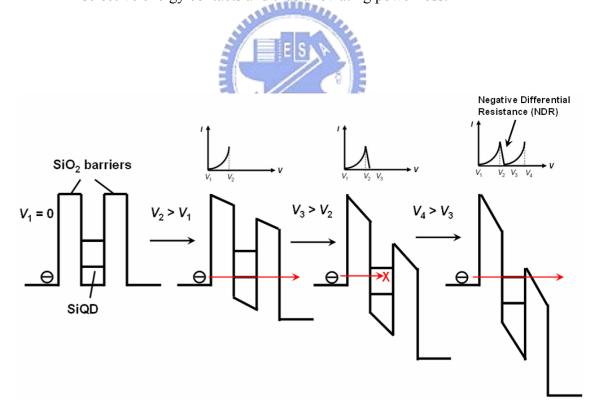

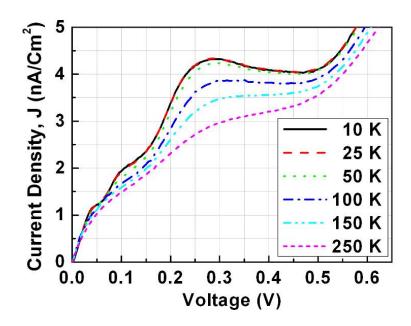

| Fig. 4-9 Transfer and output (inset) characteristics for DG-1 operation as compare with the sum of the current of two individual single-gated operations15                                                                                                                                                                                                                                                                                                    |