國 立 交 通 大 學

奈米科技研究所

碩 士 論 文

環繞式閘極多晶矽奈米線薄膜電晶體於非揮發性

Study of Gate-All-Around Poly-Si Nanowire TFTs as

Nonvolatile Memory

研 究 生：陳履安

指 導 教 授：許 錦 宗 博 士

中 華 民 國 九 十 八 年 七 月

環繞式閘極多晶矽奈米線薄膜電晶體於非揮發性記憶體研究

Study of Gate-All-Around Poly-Si Nanowire TFTs as Nonvolatile Memory

研究 生：陳履安

Student : Lu-An Chen

指 導 教 授：許 錚 宗

Advisor : Jeng-Tzong Sheu

國 立 交 通 大 學

奈 米 科 技 研 究 所

碩 士 論 文

Submitted to Department of Institute Nanotechnology

College of Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of Master

in

Nanotechnology

June 2009

Hsinchu, Taiwan, Republic of China

中 華 民 國 九 十 八 年 七 月

# 環繞式閘極多晶矽奈米線薄膜電晶體於非揮發性記憶體研究

學生：陳履安

指導教授：許鉢宗 博士

國立交通大學

奈米科技研究所

## 摘要

近年多重閘極結構被廣泛的研究，目的是為了增加閘極控制能力，解決電晶體微小化後的問題。本實驗室之前已經利用環繞式的閘極結構，成功地應用於多晶矽奈米線薄膜電晶體，利用其優越的閘極掌控能力，抑制短通道效應，成功的提升電晶體的轉換特性。而本研究建立於之前的基礎上，將環繞式閘極結構的多晶矽奈米線電晶體與非揮發性記憶體結合，除了利用環繞式閘極結構提昇電晶體轉換特性，同時也利用其包覆奈米線通道時產生的角落效應，增加非揮發性記憶體的寫入抹除速度，抑制閘極注入的效率，改善傳統平面薄膜電晶體應用於非揮發性記憶體難以寫入抹除的現象。

元件完成後，同時比較環繞式閘極結構與三閘極結構的元件轉換特性，發現環繞式閘極元件擁有較大的驅動電流、較低臨界擺幅、較高開關電流比與較低的汲極引發能位障下降。但由於環繞式閘極優越的閘極掌控能力，也同時擁有較大的閘極引發汲極漏電流。在記憶體元件特性上，環繞式閘極結構因為較多的角落效應，在記憶體寫入抹除特性上優越於三閘極結構。另外也量測此新穎元件的可靠度特性，發現其元件電荷儲存能力與元件耐久性都擁有優異的特性。

# **Study of Gate-All-Around Poly-Si Nanowire TFTs as Nonvolatile Memory**

Student : L. A. Chen

Advisor : Dr. J. T. Sheu

Department (Institute) of Nanotechnology

National Chiao Tung University

## **ABSTRACT**

Recently, multiple gate structures has been widely studied to increase channel controllability and to overcome limitations in device scaling down. In past study, Gate-All-Around structure in TFT has been proposed to improve channel controllability, to suppress short channel effect (SCE), and to increase device performance due to corner effect. In this thesis, gate-all-around (GAA) poly-Si nanowire (NW) TFTs with SONOS-type memory was demonstrated. The GAA structure is being used to not only increase the device performance but also create corner effect around the nanowire channel. It raises the P/E speed of SONOS-type memory, restrains the gate injection efficiency, and improves the fact of “hard-to-erase” in planer devices as flash memory.

A comparison of device performance between GAA deviec and TriGate device was also presented. It shows that the GAA device has a high driving current, a steep subthreshold swing, an absence of drain induced barrier lowering (DIBL), and a high on/off current ratio, but gate induced drain leakage (GIDL) was larger than that of TriGate device. The memory program and erase efficiency in the GAA device is better than those of TriGate device due to the increase of corners number. Furthermore, the device endurance and data retention measurement have also been demonstrated.

## 誌謝

首先感謝指導老師 許鉅宗 博士給我很大的研究自由，讓我可以自由發揮，並提供學生良好的研究環境與資源，讓我可以很順利的完成碩士學位。也很感謝老師在碩士生涯中給我的諄諄教誨，沒有老師一路叮嚀和指導，碩士學位很難如此順利的拿到，再次感謝。

感謝實驗室的學長，柏鈞學長不僅常常跟我在 NDL 日夜顛倒的做實驗，在研究上也給我許多建議及方向，分享許多寶貴的經驗，讓我受益良多。另外，振嘉學長也常常教我許多知識，例如元件量測技巧與 LABVIEW 等，讓我學習到很多東西。而皓恆學長常常在實驗室一起度過，跟學弟妹感情很好，平時也提供我們許多戶外活動可以參加。

感謝實驗室所有的學長、同學與學弟妹，振嘉、家豪、柏鈞、皓恆、子訓、奕貞、昶龍、欣霖、伯勳、治廷、昭睿、盈傑、珊聿、明莉、以倫、朝俊。這些日子以來，不論在實驗上或是在日常生活中，有辛苦也有歡樂，感謝有你們的陪伴，讓我有個難忘的碩士生涯。

最後要感謝我的父母親，從小到大從不給我壓力，讓我走自己想走的路，訓練我獨立自主的能力。當我在心情低落時，總是不停地給我鼓勵，並在身後默默地支持我。雖然你們是最不起眼，但也是最重要，沒有你們我也無法達到今天的成就，謝謝你們。

## 目錄

|                                          |     |

|------------------------------------------|-----|

| 中文摘要 .....                               | I   |

| 英文摘要 .....                               | II  |

| 致謝 .....                                 | III |

| 圖目錄 .....                                | IV  |

| 表目錄 .....                                | X   |

| 第一章 緒論 .....                             | 1   |

| 1.1 多晶矽薄膜電晶體回顧 .....                     | 1   |

| 1.2 環繞式閘極技術回顧 .....                      | 1   |

| 1.3 非揮發性記憶體回顧 .....                      | 3   |

| 1.4 文獻回顧 .....                           | 4   |

| 1.5 實驗動機 .....                           | 9   |

| 1.6 論文架構 .....                           | 9   |

| 第二章 元件製作流程與基本電性量測 .....                  | 10  |

| 2.1 三維結構元件電性模擬 .....                     | 10  |

| 2.2 元件製作流程 .....                         | 13  |

| 2.3 元件 TEM 圖 .....                       | 19  |

| 2.4 參數萃取方法 .....                         | 21  |

| 2.4.1 臨限電壓定義 .....                       | 21  |

| 2.4.2 次臨界斜率定義 .....                      | 22  |

| 2.4.3 沖極引發位能下降 .....                     | 22  |

| 2.5 電性基本量測與討論 .....                      | 24  |

| 2.5.1 不同的多重閘極結構對於電晶體轉換特性的影響 .....        | 24  |

| 2.5.2 多重奈米線通道薄膜電晶體與傳統平面式薄膜電晶體的電性比較 ..... | 25  |

| 2.5.3 奈米線通道的多寡，對於電晶體轉換特性上的變異 .....       | 26  |

|                                             |    |

|---------------------------------------------|----|

| 第三章 元件記憶體特性 .....                           | 29 |

| 3.1 基本穿隧機制介紹 .....                          | 29 |

| 3.1.1 Channel-Hot-Electron Injection .....  | 29 |

| 3.1.2 Fowler-Nordheim Tunneling .....       | 29 |

| 3.2 元件電場模擬 .....                            | 32 |

| 3.3 元件記憶體特性量測 .....                         | 38 |

| 3.3.1 FN Tunneling Program/Erase 特性量測 ..... | 38 |

| 3.3.2 Retention Time 量測 .....               | 43 |

| 3.3.3 Endurance 量測 .....                    | 44 |

| 3.4 降低等效氧化層厚度的記憶體特性表現 .....                 | 45 |

| 3.4.1 降低等效氧化層厚度的元件 TEM 圖 .....              | 45 |

| 3.4.2 薄膜電晶體元件轉換特性 .....                     | 46 |

| 3.4.3 Program/Erase 特性量測 .....              | 48 |

| 3.4.4 Endurance 量測 .....                    | 49 |

| 3.4.5 Retention Time 量測 .....               | 50 |

| 第四章 結論與未來展望 .....                           | 52 |

| 參考文獻 .....                                  | 58 |

## 圖 目 錄

|                                                                       |    |

|-----------------------------------------------------------------------|----|

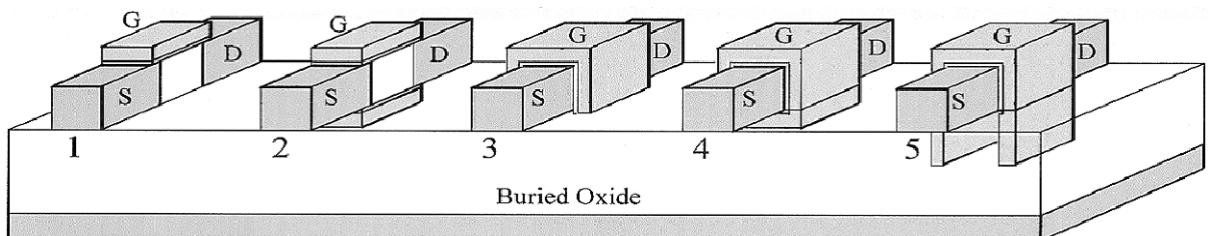

| 圖 1-1、各種多重閘極結構示意圖(1)單一閘極、(2)雙重閘極、(3)三面閘極、(4)四面閘極和(5)II 型閘極[28]。 ..... | 4  |

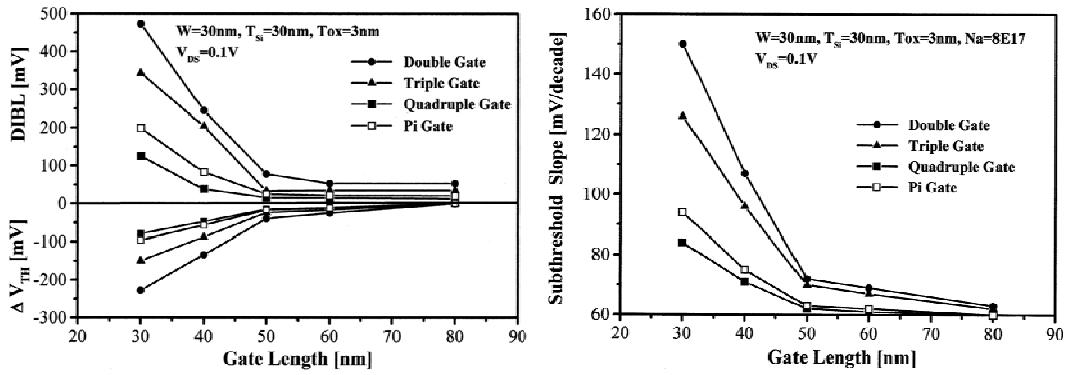

| 圖 1-2、模擬各種多重閘極結構對於 Short Channel Effect 的影響[28]。 .....                | 5  |

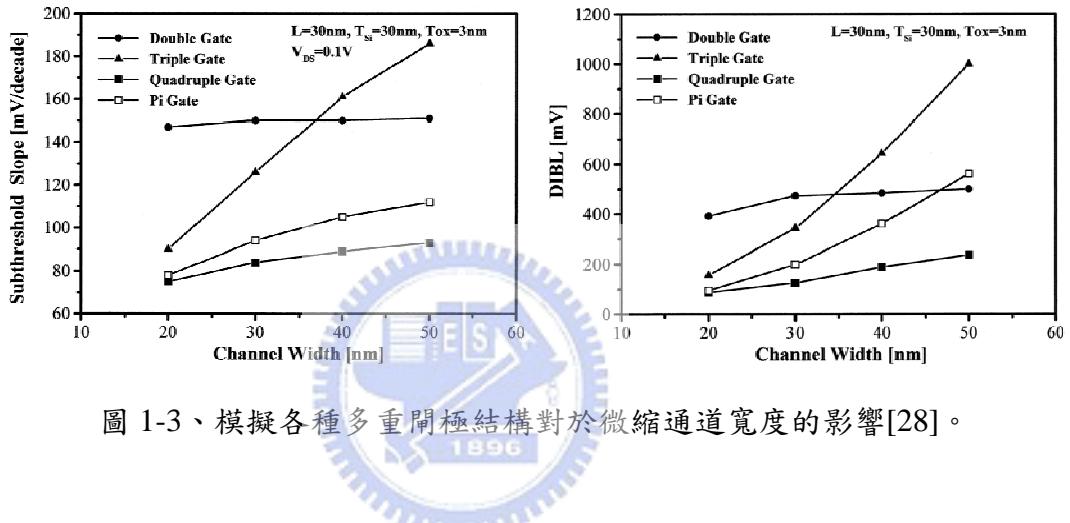

| 圖 1-3、模擬各種多重閘極結構對於微縮通道寬度的影響[28]。 .....                                | 5  |

| 圖 1-4、GAA 結構奈米線通道薄膜電晶體的通道 TEM 圖[29]。 .....                            | 6  |

| 圖 1-5、電漿處理前後的 Id-Vg 特性比較圖[29]。 .....                                  | 6  |

| 圖 1-6、TriGate 結構奈米線通道薄膜電晶體的通道 TEM 圖與 Id-Vg 圖[30]。 .....               | 7  |

| 圖 1-7、TriGate 結構與傳統平面結構的寫入抹除特性比較圖[30]。 .....                          | 8  |

| 圖 1-8、模擬通道表面與通道角落在同個閘極電壓下的電場強度圖[30]。 .....                            | 8  |

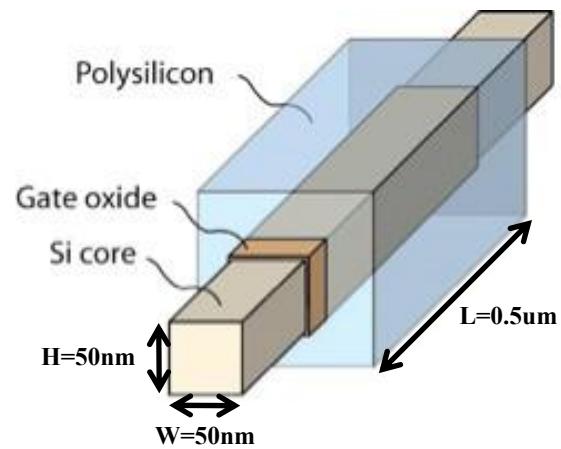

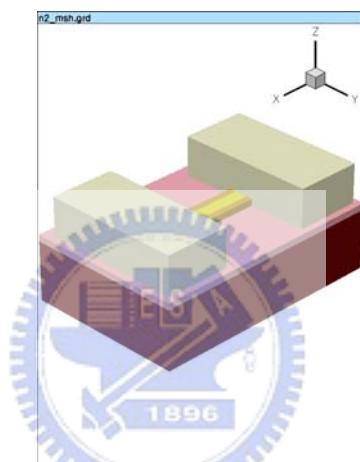

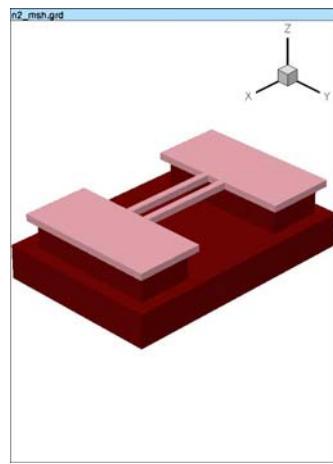

| 圖 2-1、模擬元件結構示意圖。 .....                                                | 11 |

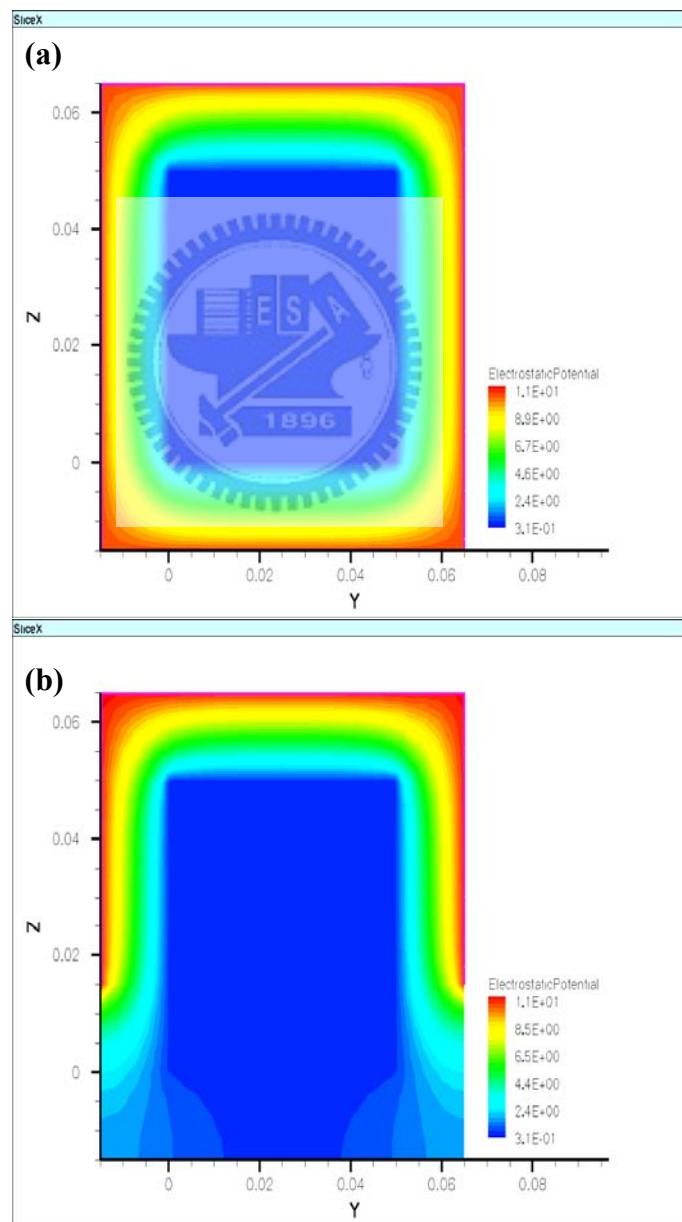

| 圖 2-2、閘極電壓為 10 伏下的電位圖(a)GAA 結構，(b)TriGate 結構。 .....                   | 11 |

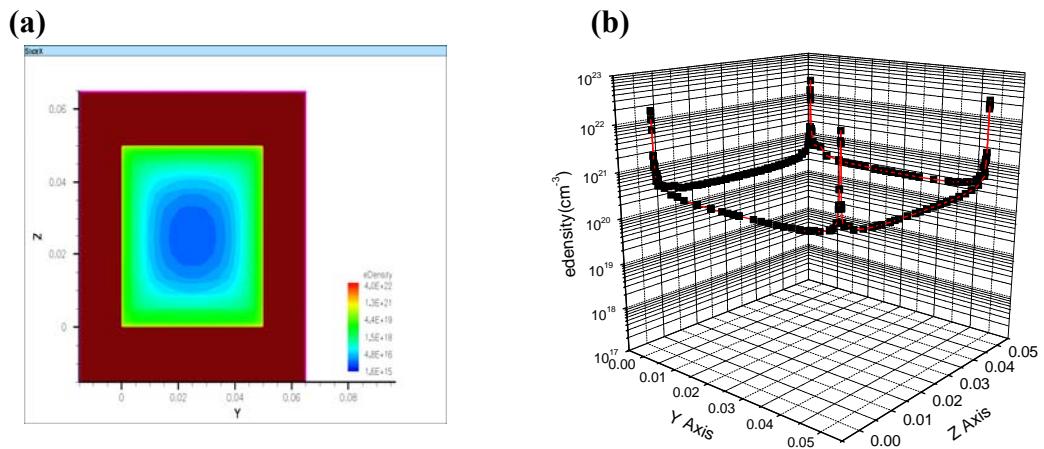

| 圖 2-3、閘極電壓為 10V 時 GAA 結構 (a)電子密度圖，(b)通道表面電子密度圖。 ....                  | 12 |

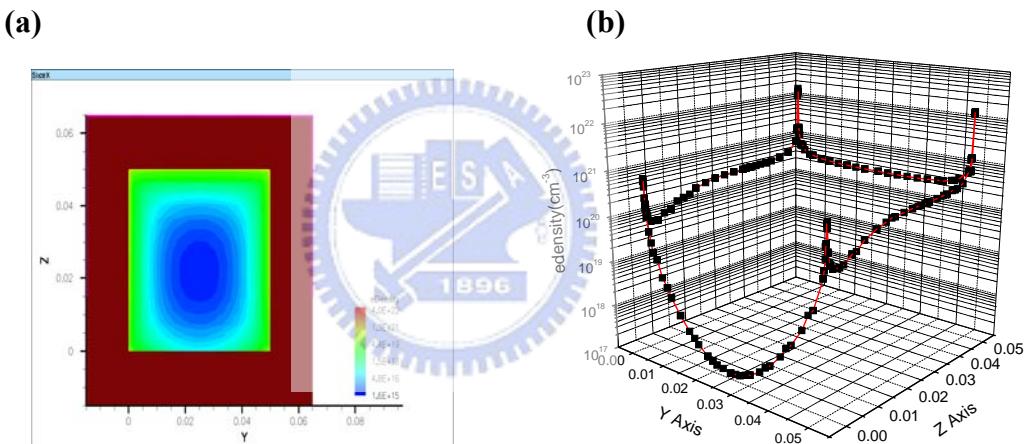

| 圖 2-4、閘極電壓為 10V 時 TriGate 結構(a)電子密度圖，(b)通道表面電子密度圖。 ...                | 12 |

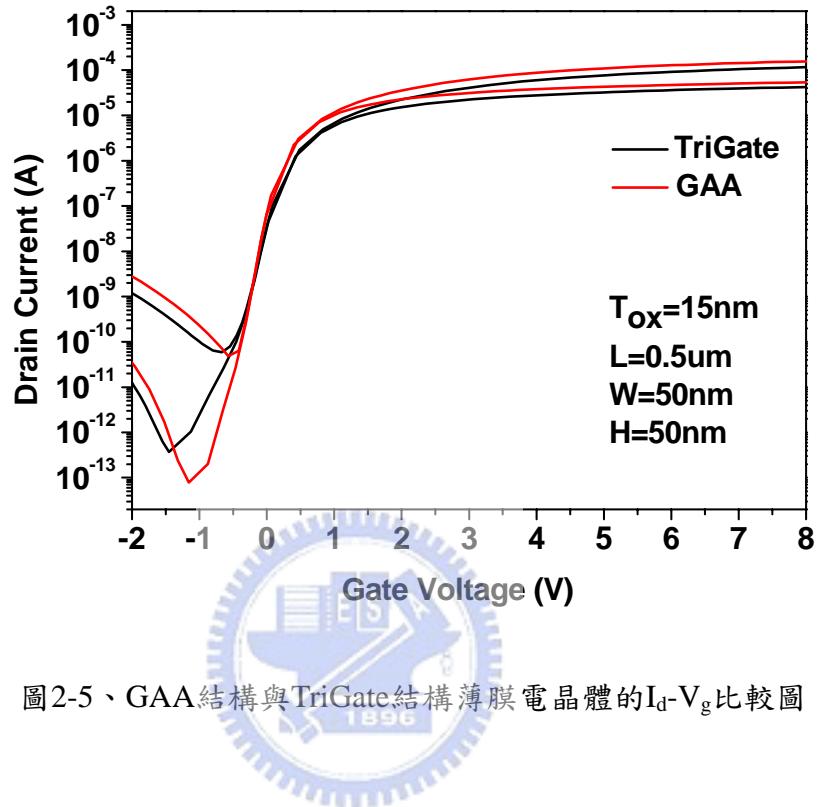

| 圖 2-5、GAA 結構與 TriGate 結構薄膜電晶體的 Id-Vg 比較圖。 .....                       | 13 |

| 圖 2-6、在 wet oxide 上面沉積非晶矽。 .....                                      | 15 |

| 圖 2-7、在非晶矽上面沉積 TEOS。 .....                                            | 15 |

| 圖 2-8、以光阻當作 Mask 蝕刻出 TEOS Block。 .....                                | 15 |

| 圖 2-9、利用乾蝕刻技術，蝕刻出 Nitride Spacer。 .....                               | 16 |

|                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 圖 2-10、利用微影技術 Pattern 出 Source/Drain 形狀。 .....                                                                                                         | 16 |

| 圖 2-11、利用 BOE 把 TEOS Block 去除。 .....                                                                                                                   | 16 |

| 圖 2-12、垂直性乾蝕刻非晶矽。 .....                                                                                                                                | 17 |

| 圖 2-13、把 Source/Drain 上面的光阻去除。 .....                                                                                                                   | 17 |

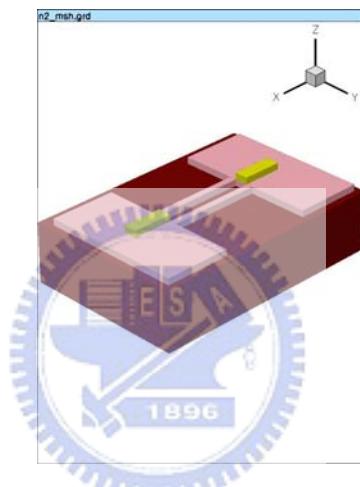

| 圖 2-14、利用 DHF 蝕刻 wet oxide 使奈米線通道懸空。 .....                                                                                                             | 17 |

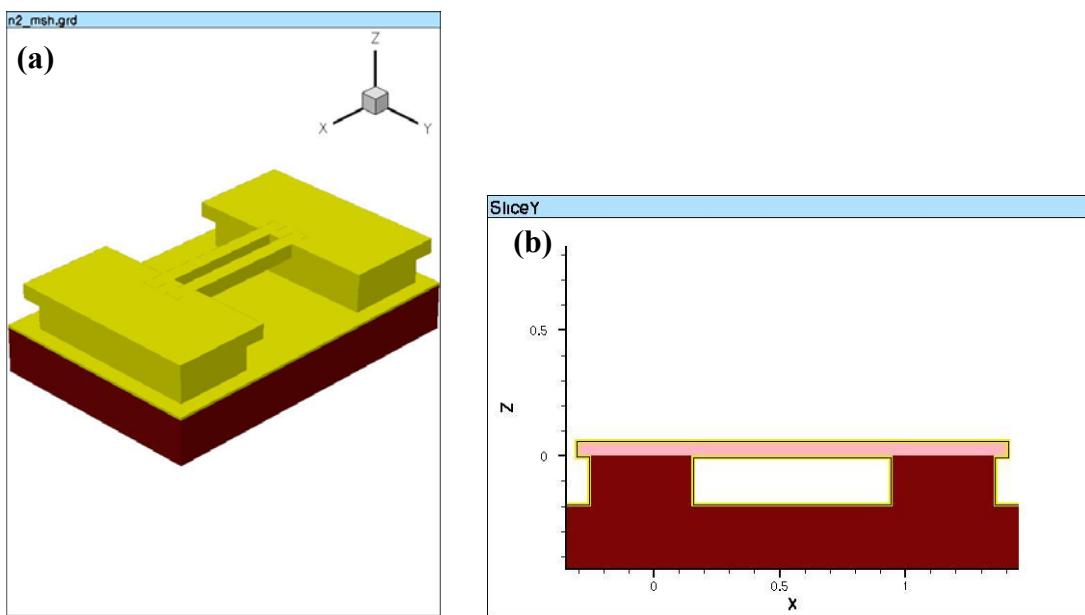

| 圖 2-15、(a)利用 LPCVD 環繞式沉積 O/N/O 閘極氧化層，(b)通道縱切面圖。 .....                                                                                                  | 18 |

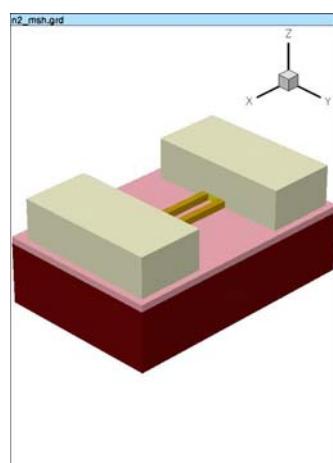

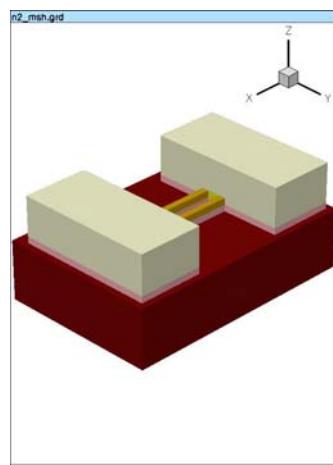

| 圖 2-16、(a)利用 LPCVD 沉積 Poly Gate 並微影蝕刻出 Poly Gate 的形狀，(b)通道橫切面圖，(c)通道縱切面圖。 .....                                                                        | 18 |

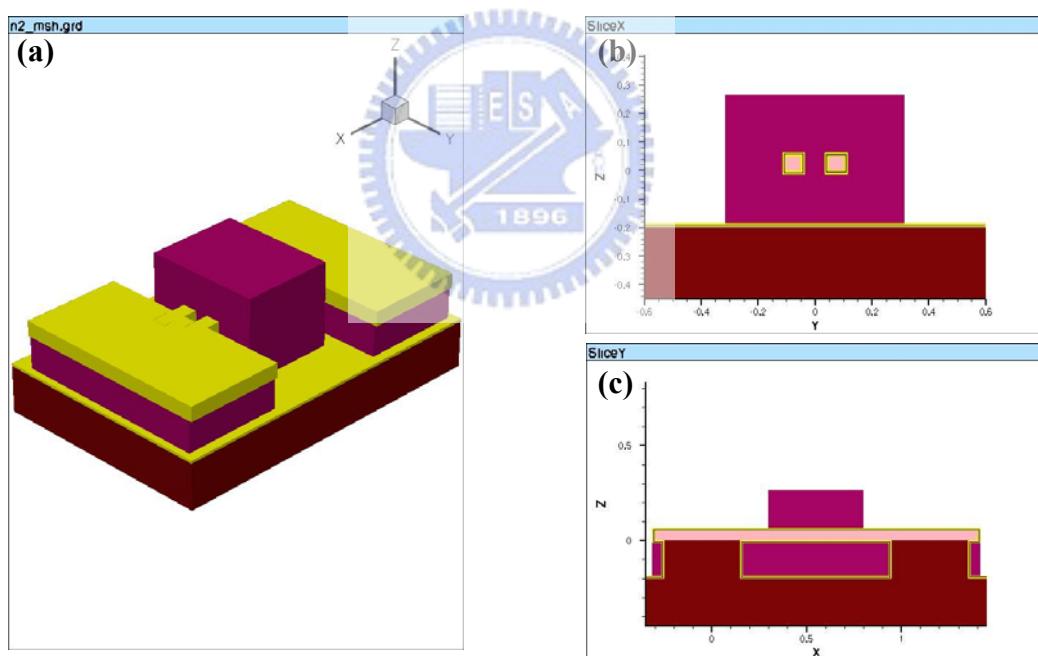

| 圖 2-17、奈米線通道的 TEM 圖 (a)GAA 結構，(b)TriGate 結構，其中 $W_{ch}/T_{ch}=62\text{-nm}/44\text{-nm}$ ， $O/N/O=10.5\text{-nm}/5.5\text{-nm}/15.3\text{-nm}$ 。 ..... | 20 |

| 圖 2-18、定電流 $V_{th}$ 定義方法。 .....                                                                                                                        | 21 |

| 圖 2-19、Subthreshold Swing 定義方法。 .....                                                                                                                  | 22 |

| 圖 2-20、DIBL 能帶示意圖。 .....                                                                                                                               | 23 |

| 圖 2-21、DIBL 定義方法。 .....                                                                                                                                | 23 |

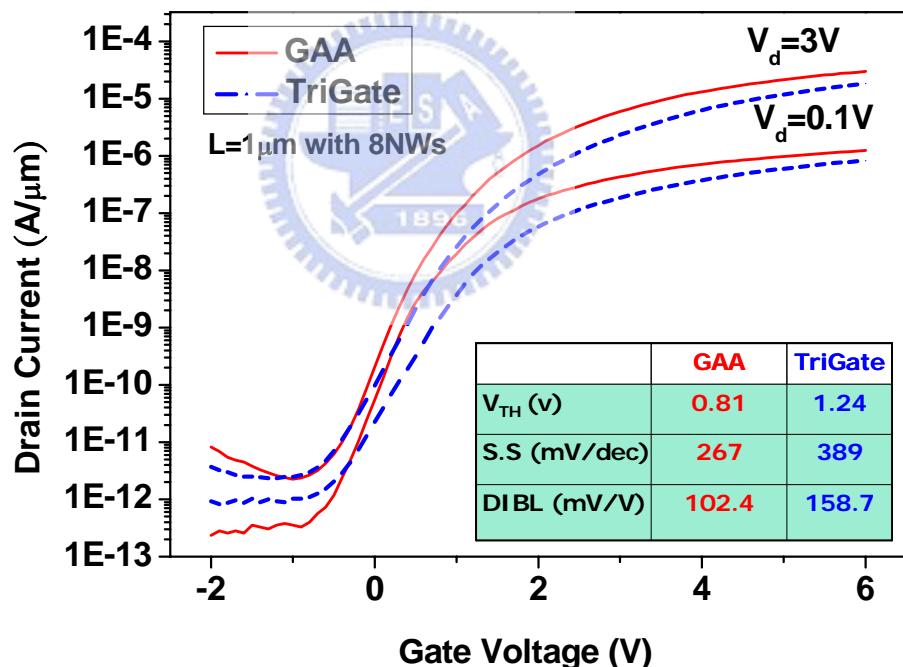

| 圖 2-22、GAA 結構與 TriGate 結構的 $Id$ - $V_g$ 圖。 .....                                                                                                       | 24 |

| 圖 2-23、(a)Planar 結構，(b)Multiple NWs 結構的示意圖。 .....                                                                                                      | 25 |

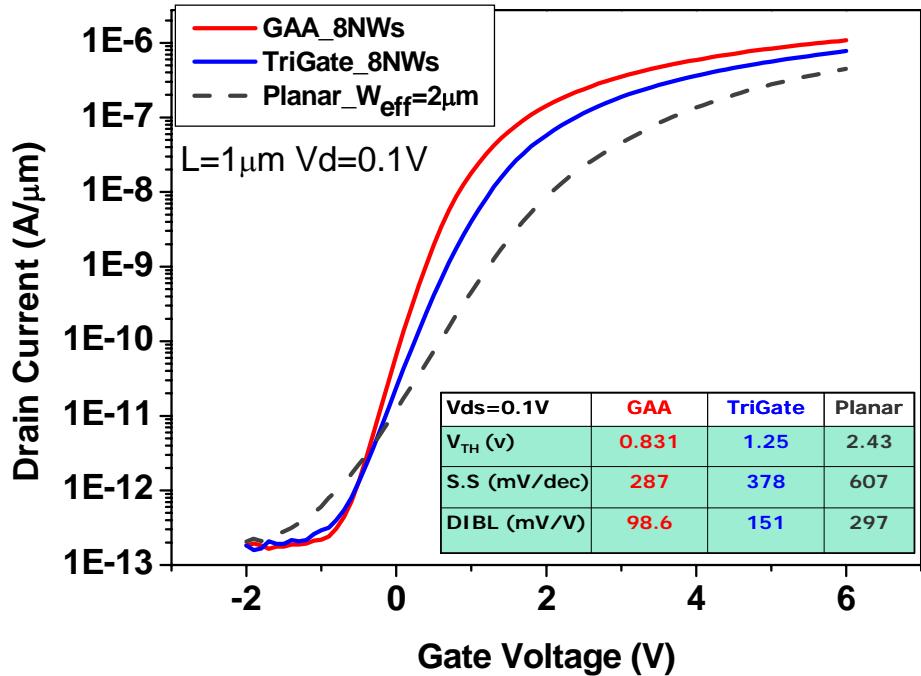

| 圖 2-24、8 個奈米線通道的 GAA 和 TriGate 結構薄膜電晶體與 $W_{eff}=2\mu\text{m}$ 的 Planar device 的 $Id$ - $V_g$ 比較圖。 .....                                               | 26 |

| 圖 2-25、不同的通道數目的 $Id$ - $V_g$ 圖，縱軸為並未規一化的汲極電流。 .....                                                                                                    | 27 |

| 圖 2-26、不同的通道數目的 $Id$ - $V_g$ 圖，縱軸為規一化後的汲極電流。 .....                                                                                                     | 27 |

|                                                                      |    |

|----------------------------------------------------------------------|----|

| 圖 2-27、不同的通道數目的(a)Vth 與 SS , (b) DIBL Variation 比較。 .....            | 28 |

| 圖 3-1、Channel-Hot-Electron Injection 機制示意圖。 .....                    | 30 |

| 圖 3-2、Fowler-Nordheim Tunneling 機制能帶示意圖。 .....                       | 31 |

| 圖 3-3、Direct Tunneling 機制能帶示意圖。 .....                                | 31 |

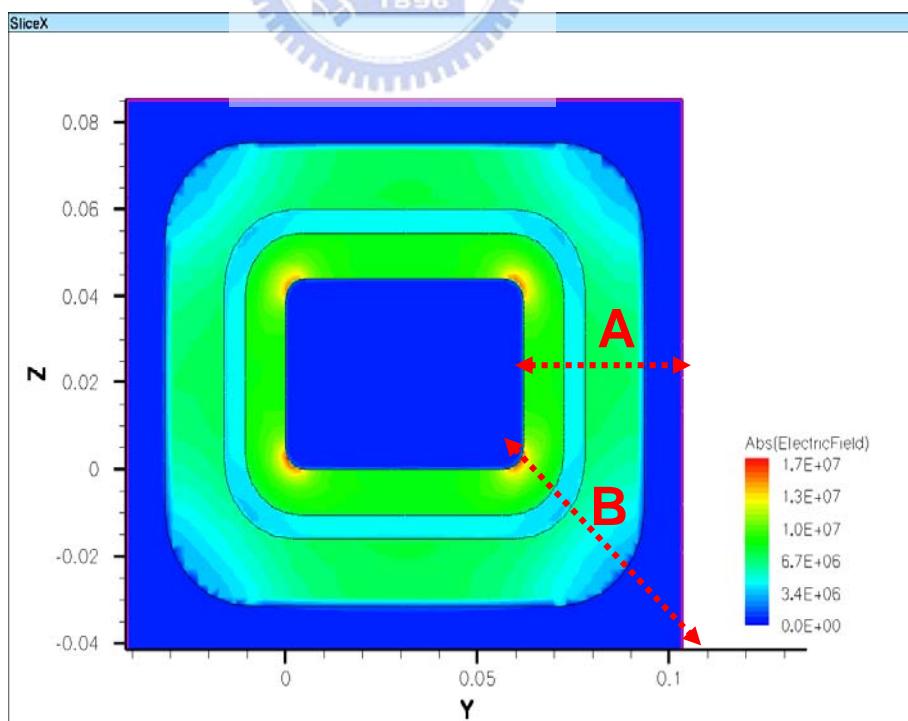

| 圖 3-4、當閘極電壓為 22V 時，GAA 結構的電場分布模擬圖，其中切線 A 為平邊區域，切線 B 為角落區域。 .....     | 32 |

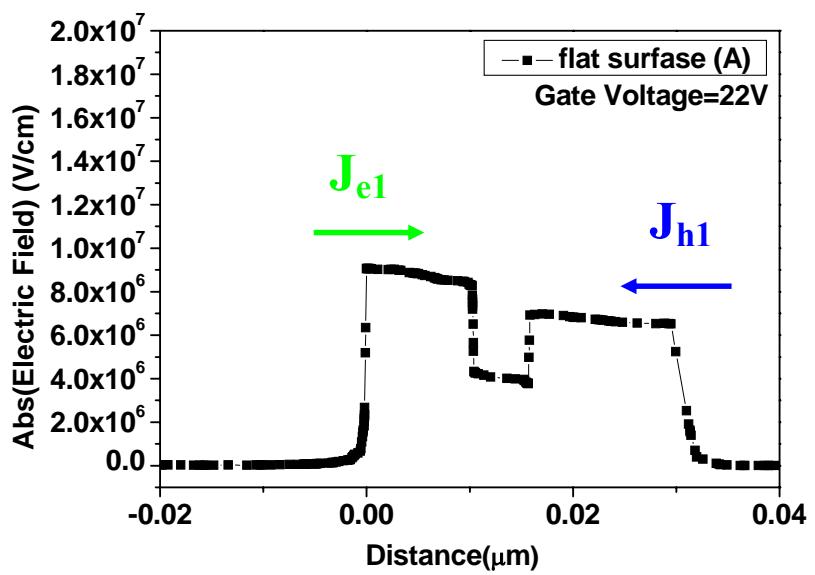

| 圖 3-5、當閘極電壓為 22V 時，平邊區域(切線 A)的電場絕對值分布圖。 .....                        | 33 |

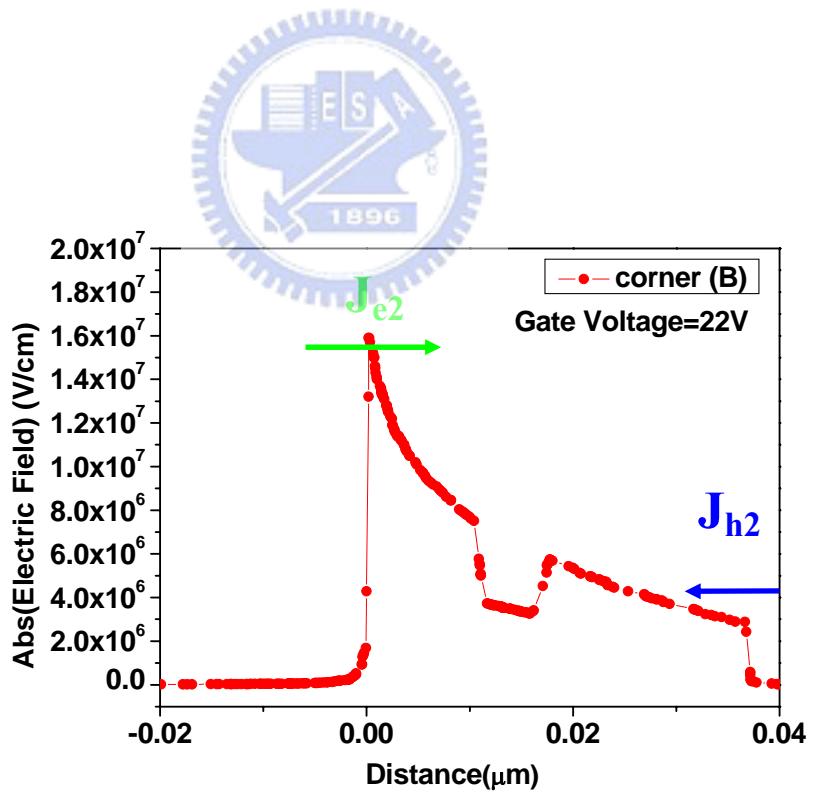

| 圖 3-6、當閘極電壓為 22V 時，角落區域(切線 B)的電場絕對值分布圖。 .....                        | 33 |

| 圖 3-7、FNT 公式的能障高度示意圖。 .....                                          | 34 |

| 圖 3-8、當閘極電壓為-24V 時，GAA 結構的電場絕對值分布模擬圖，其中切線 C 為平邊區域，切線 D 為角落區域。 .....  | 36 |

| 圖 3-9、當閘極電壓為-24V 時，平邊區域(切線 C)的電場絕對值分布圖。 .....                        | 37 |

| 圖 3-10、當閘極電壓為-24V 時，角落區域(切線 D)的電場絕對值分布圖。 .....                       | 37 |

| 圖 3-11、GAA 結構的元件經過 FNT 操作 Program/Erase 後的 Id-Vg 曲線。 .....           | 39 |

| 圖 3-12、GAA 結構的元件對於 FNT 寫入抹除的特性圖。 .....                               | 40 |

| 圖 3-13、GAA 與 TriGate 結構的元件對於 FNT 寫入的特性比較圖。 .....                     | 42 |

| 圖 3-14、GAA 與 TriGate 結構的元件對於 FNT 抹除的特性比較圖。 .....                     | 42 |

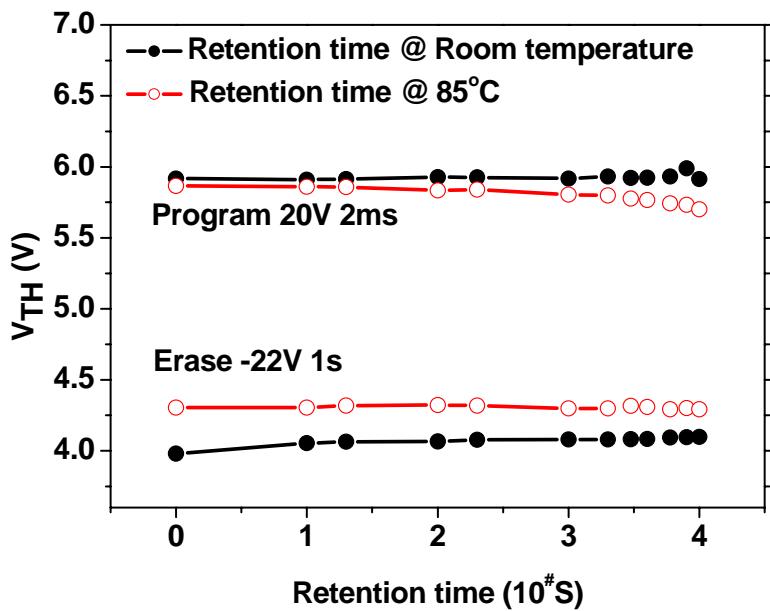

| 圖 3-15、GAA 結構的元件分別在室溫與 85°C 中 Retention Time 的比較圖。 .....             | 44 |

| 圖 3-16、GAA 結構的元件對於 Endurance 的表現。 .....                              | 45 |

| 圖 3-17、GAA 結構的 Nanowire Channel 剖面圖，其中 O/N/O=(5-nm/4.3-nm/7.7-nm) ，圖 |    |

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

| 中通道的寬度( $W_{ch}$ )約為 40 nm，高度( $T_{ch}$ )約為 65 nm。 .....                           | 46 |

| 圖 3-18、不同有效氧化層厚度(EOT)的 GAA 結構元件，對於 Id-Vg 的影響。 .....                                | 47 |

| 圖 3-19、不同有效氧化層厚度(EOT)的 GAA 結構元件，對於 Id-Vd 的影響。 .....                                | 47 |

| 圖 3-20、有效氧化層厚度(EOT)下降後的 GAA 元件， Program 效率的量測。 .....                               | 48 |

| 圖 3-21、有效氧化層厚度(EOT)下降後的 GAA 元件，對於 Erase 效率的量測。 .....                               | 49 |

| 圖 3-22、有效氧化層厚度(EOT)下降後的 GAA 元件，其 Endurance 的表現。 .....                              | 50 |

| 圖 3-23、有效氧化層厚度(EOT)下降後的 GAA 元件，經過 10000 次 Stress 後，其在室溫下 Retention Time 的表現。 ..... | 51 |

| 圖 4-1、元件結構的結構示意圖，並對照右下角的參雜濃度表，(a)非對稱閘極結構，(b)環繞式閘極結構。 .....                         | 53 |

| 圖 4-2、模擬非對稱結構與環繞式閘極結構的 Id-Vg 曲線圖。 .....                                            | 54 |

| 圖 4-3、模擬非對稱結構與環繞式閘極結構的通道電場圖。 .....                                                 | 55 |

| 圖 4-4、模擬非對稱結構與 GAA 結構通道表面電場圖。 .....                                                | 55 |

| 圖 4-5、 $\Omega$ 閘極結構與 GAA 結構的奈米線通道 TEM 圖。 .....                                    | 56 |

| 圖 4-6、 $\Omega$ 閘極結構與 GAA 結構的 Id-Vg 比較圖。 .....                                     | 57 |

## 表目錄

|                                                  |    |

|--------------------------------------------------|----|

| 表 1-1、電漿處理前後的 Id-Vg 特性的整理表格[29]。 .....           | 7  |

| 表 2-1、GAA 結構與 TriGate 結構薄膜電晶體的 Id-Vg 比較表格。 ..... | 13 |

| 表 3-1、FNT 公式的參數整理。 .....                         | 35 |

# 第一章

## 緒論

### 1.1 多晶矽薄膜電晶體回顧

近年來，多晶矽薄膜電晶體(Poly-Si TFTs)已被廣泛使用於主動式陣列液晶顯示器(AMOLCD)[1]。比起傳統的非晶矽薄膜電晶體(Amorphous-Si TFTs)，Poly-Si TFTs 擁有更高的載子遷移率(Mobility)。其優越的驅動電流(Drain Driving Current)、高顯示亮度、高解析度、消耗功率，適合應用於手機、筆記型電腦、高解析度液晶面板…等電子產品。

但是多晶矽有許多缺陷(Traps)在晶體邊界(Grain Boundary)上，多晶矽薄膜電晶體轉換特性會受到這些缺陷影響而降低。因此許多團隊希望能降低缺陷密度與增加多晶矽晶體的體積，來抑制多晶矽中晶體邊界對於元件特性的影響，例如準分子雷射退火(Excimer Laser Anneal)[2]、金屬誘發側向結晶(Metal Induce Lateral crystallization)[3,4]、固相結晶法(Solid phase crystallization)...等方法[5,6]，都是利用再次結晶的步驟提升多晶矽的品質，改善多晶矽受到缺陷影響的問題，並提升電晶體轉換特性。

而本實驗利用固相結晶法，讓多晶矽的晶體變大，來提升電晶體特性。除此之外，使用多重閘極結構，可降低臨限電壓(Threshold Voltage)的變動，降低背閘極對通道的影響，並提升開關速度[7]。由於液晶顯示面板所使用的基板材料為玻璃，因此低溫多晶矽的薄膜電晶體[8]也受到廣泛的應用，強調製程溫度不能超過 600°C 或是更低溫，目前本實驗的元件仍需高溫活化，尚無法以玻璃基板取代，這方面製程條件還需要改善。另外本實驗所使用的閘極為經過摻雜的  $N^+$ 多晶矽閘極，早期多直接以金屬當閘極，省去許多製程步驟，但從自我對準的離子佈植發明後，因金屬不適合高溫製程，多晶矽和氧化層的介面特性良好，且能忍受高溫的製程，因此改為  $N^+$ 多晶矽閘極以利後續之高溫離子活化。

### 1.2 環繞式閘極技術回顧

根據摩爾定律(Moore's Law)，一顆晶片上的電晶體數目會每 18 個月成長一倍，元件大小也會隨之微縮，到目前為止半導體業已經進入 CMOS 45 奈米量產的階段，並繼續往下發展。當金氧半場效電晶體元件越小，通道的長度將隨之縮短，因此電晶體的操

作速度將加快。但是電晶體的通道長度並不能無限制的縮減，當其長度縮短到某一定的程度後，金氧半場效電晶體在操作時於源極和汲極所產生的空乏區寬度就越接近，將與通道產生重疊，造成部份通道被源極及汲極的空乏區共享，次啟始電流(Subthreshold Current)將上升，使得金氧半場效電晶體的臨限電壓下降，甚至使得閘極電壓無法對MOS的汲極電流做控制的情形出現。而因通道長度變小所衍生的各種問題，稱為短通道效應(Short Channel Effects)[9,10]，因此許多研究試圖另闢新路，找出解決之道。

研究發現可以從另一個維度的開發，以改善平面電晶體的微縮瓶頸，之後發展出了三維結構電晶體，藉由增加閘極對通道的控制面積，使得漏電得以控制，抑止短通道效應，也為下一個世代的半導體產業找到新的方向。當電晶體微縮到奈米尺下，有效的閘極控制能力是必須的，因此許多改善方法被發展出來，包括通道以奈米線方式呈現，配合多閘極、三閘極(TriGate)、Ω閘極或環繞式閘極(Gate All Around, GAA)都是目前用來改善短通道效應的方法一路被開發出來[11-14]。

在各種多閘極結構中，以環繞式閘極結構最引人注目，因為其閘極包覆面積最大，閘極控制能力最好，擁有高驅動電流，與更好的電晶體特性。加上假如通道是方型結構，最大的電場會落在通道四個角落(Corner Effect)[15]，造成電子密度提高，但也造成漏電流(GIDL)[16]增加的現象。為了抑制漏電流增加的現象，許多團隊提出了許多方法去抑制汲極電場，例如採用低汲極摻雜(LDD)方式，使整個通道電場降低，避免表面高漏電[17]，或者使用汲極遠離閘極結構(Offset)，讓汲極離閘極遠一點，如同增加串聯電阻讓電場降低[18,19]。

目前許多團隊使用 SOI 晶圓當做基板，SOI 的好處在於沒有基底效應並且抑止軟性錯誤(Soft Error)，擁有完全空乏的能力，通常奈米線電晶體元件均使用 SOI 晶圓[20]，但單晶 SOI 製造成本高，所以價格高昂，是其缺點。而本研究以 Poly-Silicon on Insulator 作為研究的基本材料，並無使用 SOI 晶圓，可以大大降低製造成本。雖然薄膜電晶體受限於本身晶粒邊界的缺陷，漏電流大及載子遷移率低，但本實驗使用環繞式閘極電晶體，來提升閘極對奈米線通道的控制能力，兼具高驅動電流及高開關電流比，改善載子遷移率，並有很陡的次臨界擺幅。

### 1.3 非揮發性記憶體回顧

在積體電路(Integrated Circuit)的領域中，記憶體(Memory)是相當重要的一個分支；近年來在相關技術的帶領之下，新的應用不斷地被開發，對記憶體的需求亦有增無減。為了爭取商機，世界各記憶體大廠均卯足全力，相繼推出高密度(High Density)，高性能的產品(High Performance)，以提升市場佔有率。此現象除了出現在動態隨機存取記憶體之外(Dynamic Random Access Memory, DRAM)，非揮發性記憶體(Nonvolatile Memory)也受到可攜帶式的電子產品影響，例如：MP3 播放器、數位相機、手機或是隨身碟…等，近年來受到矚目。

目前非揮發性記憶體在工業上成熟的技術是懸浮閘結構(Floating Gate)的記憶體，其原理為利用中間的導電層儲存電荷而造成臨限電壓的漂移，因而可有記憶“0”或是“1”兩種狀態(State)的記憶體功能，且裡面的電荷不會隨著電源關閉而流失，因而稱為非揮發性記憶體。

隨著摩爾定律的推展，懸浮閘結構記憶體面臨無法繼續微縮的窘境，穿隧氧化層(Tunneling Oxide)隨著尺寸微縮而減薄，可能會因為穿隧氧化層上面的一個缺陷，造成儲存電荷層(Trapping Layer)的漏電問題，或是整個儲存電荷流失。目前有兩類改良式的結構在研究中，一種是奈米晶體(Nanocrystal)記憶體，其利用直徑是奈米級的顆粒替換浮閘記憶體的導電層[21,22]。另一種是 SONOS 結構，將氮化矽(Nitride)替換原本懸浮閘記憶體的導電層，利用氮化矽裡的缺陷(Traps)當作儲存電荷層，由於每個缺陷都是獨立的儲存層，所以假使穿隧氧化層上有一個缺陷造成漏電，也不會造成整個儲存電荷層的漏電。並且因為氮化矽因為其製成簡單、材料取得方便、不易受元件形狀影響，比起奈米晶體記憶體更適合通道長度的微縮，也更適合三維結構記憶體的應用。

近年來許多研究單位為了追求更高效能、更高可靠度的 SONOS 記憶體而提出了取多方法，例如將二氧化矽的阻隔氧化層(Blocking Oxide)換成 High- $\kappa$  材料，可以增加閘極吸引電荷的能力，提升寫入與抹除(Program/Erase, P/E)的效率。此外也有團隊改善穿隧氧化層的材料或是換成堆疊結構，除了可以提升 P/E 效率也可以增加記憶體元件可靠度。或是利用高缺陷密度的材料取代矽化氮，可以提升 Window 的大小[23-26]。而本論文將利用三維結構的薄膜電晶體與 SONOS 記憶體結合，利用三維結構的 Corner Effect 提升表面電場，增加 P/E 的效率，改善平面式結構難以寫入或是難以抹除的現象[27]。

## 1.4 文獻回顧

此節將討論三篇近幾年其他團隊的期刊論文，第一篇是 2002 IEEE[28]，此篇模擬五種不同的多重閘極結構，包括單一閘極(Single gate)、雙重閘極(Double gate)、三面閘極(Triple gate)、四面閘極(Quadruple gate)和π型閘極(Pi-gate)，如圖 1-1，調變不同閘極長度(Gate Length)與通道寬度(Channel Width)等條件，討論不同的多重閘極對於電晶體非理想效應的影響。文中固定的元件參數如下，元件材料為單晶矽，閘極氧化層為 3-nm 的二氧化矽，並使用功函數為 4.63 電子伏特(eV)的鎢(tungsten)做為閘極材料。

隨著 MOS 場效電晶體元件微縮，短通道效應越來越明顯，導致臨限電壓下降、汲極引發位能障(DIBL)上升、次臨界斜率(Subthreshold Swing)上升。如圖 1-2，文中討論不同的閘極對於短通道效應的影響。本實驗可以明顯發現閘極包覆的面積越多，閘極掌控能力越好，越能抑制短通道效應，其中以四面閘極(Quadruple gate)結構抑制短通道效應的能力最好。此外，此論文也調變不同的通道寬度(Channel Width)，並討論各種多重閘極結構對於元件的影響力，其中也是以 Quadruple gate 結構的效果最為顯著，如圖 1-3。此外，由於雙重閘極結構電晶體的閘極是包覆於通道的上下兩邊，所以電晶體轉換特性對於通道寬度的變異並無太大的改變。

圖 1-1、各種多重閘極結構示意圖(1)單一閘極、(2)雙重閘極、(3)三面閘極、(4)四面閘極和(5)π型閘極[28]。

圖 1-2、模擬各種多重閘極結構對於 Short Channel Effect 的影響[28]。

圖 1-3、模擬各種多重閘極結構對於微縮通道寬度的影響[28]。

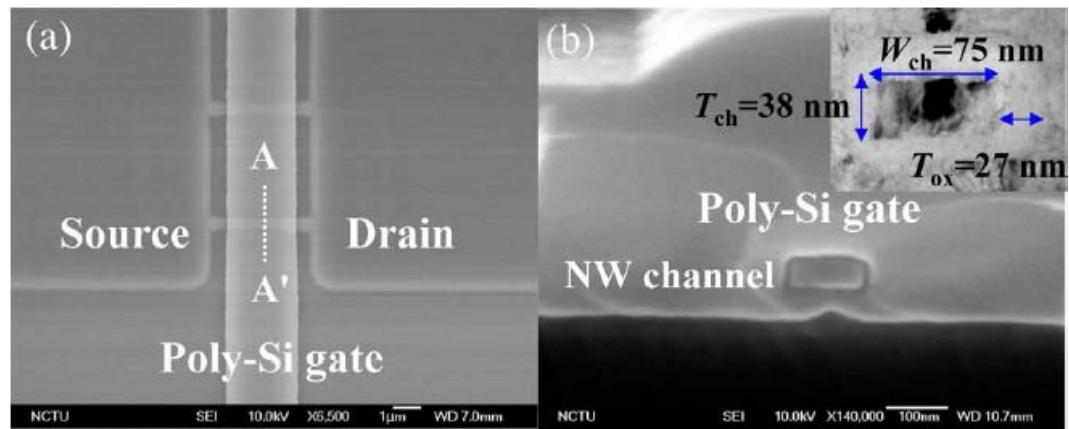

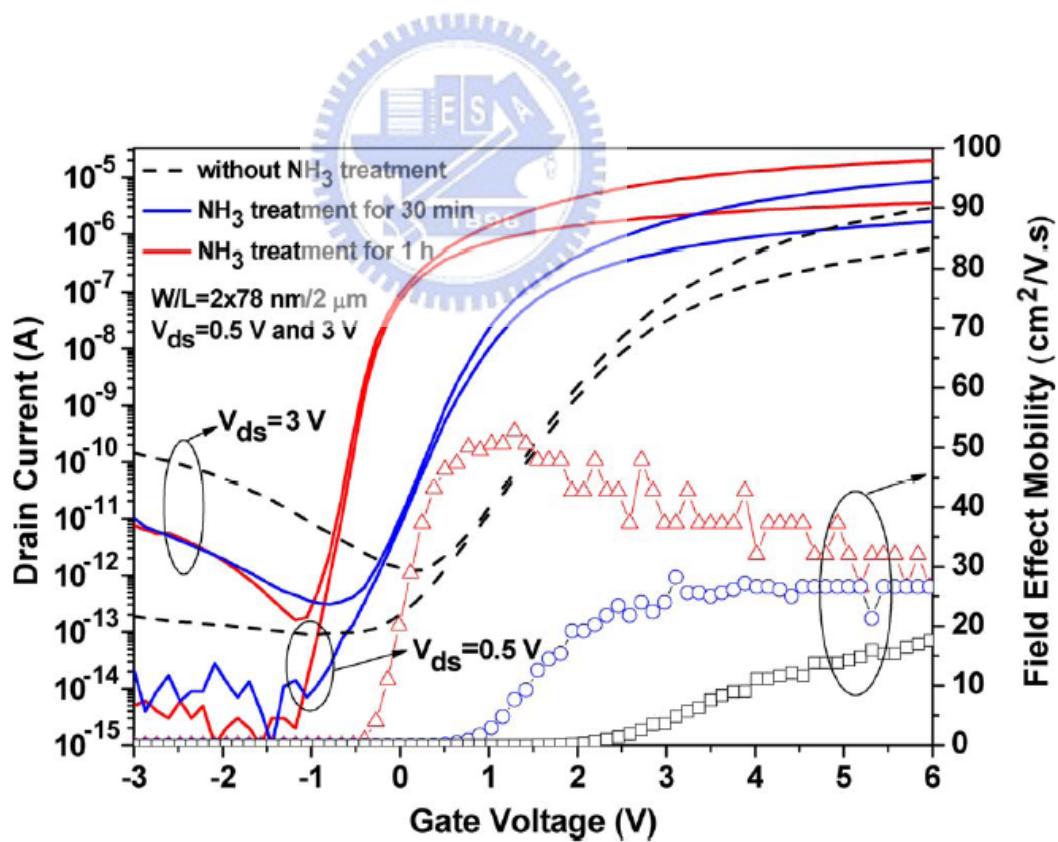

第二篇論文發表於 2009 IEEE EDL[29]，此篇論文利用側壁 Spacer 奈米線技術製作出環繞式閘極多晶矽薄膜電晶體，利用經過 24 小時退火的多晶矽奈米線，將其下面的底部氧化層濕式蝕刻移除後，使奈米線呈懸梁臂的懸空狀態，再將薄氧化層沉積上去當閘極絕緣層，之後蓋  $N^+$  多晶矽薄膜，此層須將整個空隙填滿，包住整個通道，如圖 1-4，來提升閘極對通道的控制能力，改善短通道效應。元件完成後，經過氮電漿處理，發現它整個電性有非常明顯的改善，包括極高驅動電流，低次臨界擺幅達到 114 mV/dec、載子遷移率亦獲改善、幾乎零汲極引發位能障下降、高開關電流比  $> 10^8$ ，如圖 1-5。此外，文中也比較傳統的平面多晶矽薄膜電晶體與環繞式閘極多晶矽薄膜電晶體在電性上的差異，並將重要參數整理於表 1-1，很明顯環繞式閘極多晶矽薄膜電晶體擁有較好的轉換特性。

圖 1-4、GAA 結構奈米線通道薄膜電晶體的通道 TEM 圖[29]。

圖 1-5、電漿處理前後的  $I_d$ - $V_g$  特性比較圖[29]。

表 1-1、電漿處理前後的  $I_d$ - $V_g$  特性的整理表格[29]。

| Structure ( $W_{eff}/L$ )                    | $V_{th}$ (V)      | $I_{on}/I_{off}$  | SS (mV/dec) | DIBL (mV/V) |

|----------------------------------------------|-------------------|-------------------|-------------|-------------|

| GAA (0.452 $\mu m/2 \mu m$ , $NH_3$ 1h)      | $-0.38 \pm 0.177$ | $1.2 \times 10^8$ | 114         | 13          |

| GAA (0.452 $\mu m/2 \mu m$ , $NH_3$ 30 min)  | $0.73 \pm 0.317$  | $2.9 \times 10^7$ | 125         | 14          |

| GAA (0.452 $\mu m/2 \mu m$ , as fabricated)  | $2.2 \pm 0.361$   | $2.5 \times 10^6$ | 466         | 24          |

| Planar (0.5 $\mu m/2 \mu m$ , $NH_3$ 1h)     | 0.9               | $2.1 \times 10^7$ | 402         | 15          |

| Planar (0.5 $\mu m/2 \mu m$ , as fabricated) | 1.12              | $3.3 \times 10^6$ | 611         | 96          |

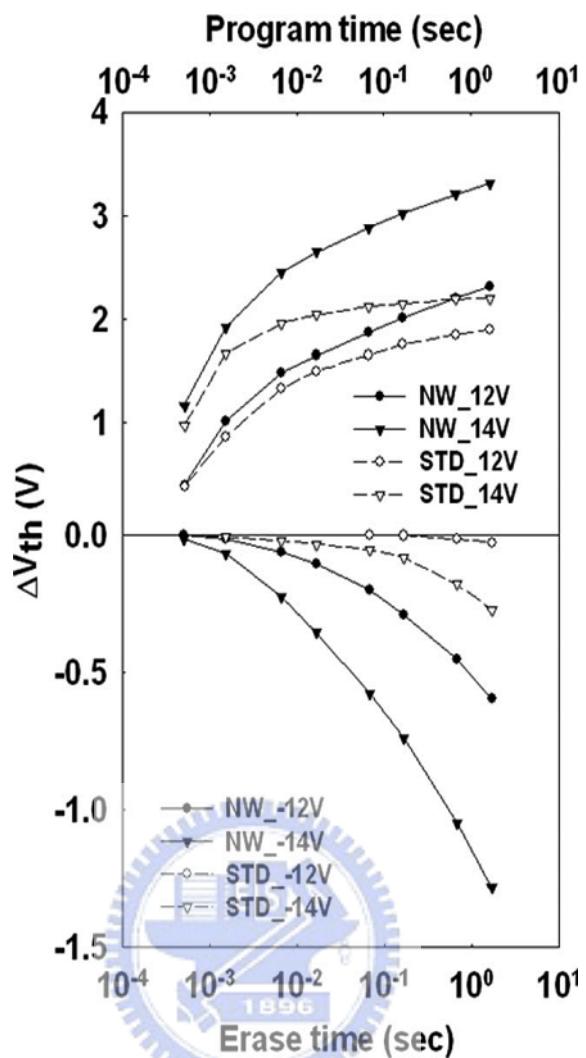

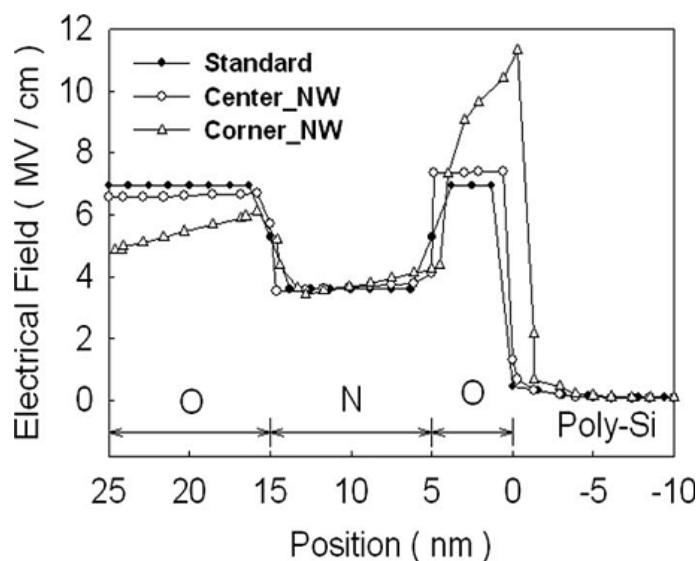

最後一篇發表於 2007 IEEE EDL[30]，首先利用 E-beam 微影技術定義出長方形的奈米線通道，再連續沉積閘極氧化層(TEOS/Nitride/TEOS=5-nm/10-nm/10-nm)與  $N^+$ 多晶矽閘極。利用多重閘極的概念，將奈米線多晶矽薄膜電晶體(Poly-Si Nanowire TFTs)與三面式閘極(TriGate)結合，提升薄膜電晶體的轉換特性，如圖 1-6。另外也成功地與 SONOS 快閃記憶體結合，並且強調當閘極施加正電壓，會使通道角落產生強大的電場(Corner effect)，奈米線通道表面反轉產生的電子會有 FN 穿隧現象，並注入捕捉電荷層，使臨限電壓的變化量增加。反之施加足夠的負電壓，奈米線通道表面的電洞也會穿隧至捕捉電荷層。但是傳統平面式薄膜電晶體並沒有 Corner effect 的現象，所以施加同樣的閘極電壓與相同的時間， $V_{th}$  的變化量會明顯下降，如圖 1-7。並且利用半導體元件模擬軟體證明施加同樣的閘極電壓時，通道角落的電場會遠大於通道平邊的電場，如圖 1-8。

圖 1-6、TriGate 結構奈米線通道薄膜電晶體的通道 TEM 圖與  $I_d$ - $V_g$  圖[30]。

圖 1-7、TriGate 結構與傳統平面結構的寫入抹除特性比較圖[30]。

圖 1-8、模擬通道表面與通道角落同個閘極電壓下的電場強度圖[30]。

## 1.5 實驗動機

近年來越來越多研究投入Poly-Si TFTs與SONOS Memory的整合應用，將Control device與Memory device一起製作整合在同個LCD面板，目的是為了縮小產品面積、降低製作成本、減少可靠度的問題，並稱此技術為System On Panel(SOP)。但是多晶矽薄膜電晶體應用於SOP時，由於多晶矽有許多晶體邊界(Grain Boundary)，因此造成電晶體轉換特性差、記憶體寫入抹除特性不佳等問題。為了克服此問題，本實驗提出一種新穎的薄膜電晶體結構，將傳統平面式薄膜電晶體改成三維結構的薄膜電晶體。其結合多晶矽奈米線通道與環繞式閘極，利用環繞式閘極包覆住多晶矽奈米線通道，增加閘極掌控能力，提昇電晶體轉換特性，並且利用角落效應(Corner Effect)增加記憶體寫入與抹除的效率。

## 1.6 論文架構

本論文將以環繞式閘極結構(GAA)多晶矽奈米線薄膜電晶體為主軸，將此結構與非揮發性記憶體結合，探討其轉換特性與記憶體特性的表現，並且與傳統平面式結構和三閘極結構(TriGate)比較。希望證明此結合薄膜電晶體與非揮發性記憶體的新穎元件，可以利用環繞式閘極結構提昇薄膜電晶體的轉換特性，同時增加非揮發性記憶體的寫入抹除效率，並且相信此高效能的元件可以成功的適用在未來SOP的應用上。

在論文架構上，首先介紹 GAA 結構的元件製作流程與電晶體轉換換性的量測，其中為了證明 GAA 結構其優越的閘極能力與四個角落的 Corner Effect，本研究利用 ISE-TCAD 模擬環繞式閘極結構結合奈米線薄膜電晶體後的電晶體特性，並與三閘極(TriGate)結構比較 Corner Effect 的大小與轉換電性上的差異。除此之外，本研究也實作出 GAA 結構、TriGate 結構的奈米線薄膜電晶體與傳統平面式薄膜電晶體(Planar device)，實際量測三者在電晶體轉換電性上的差異，並與模擬結果比較。

接著將介紹 GAA 結構的元件與非揮發性記憶體結合後，其記憶體特性上的表現。本實驗針對 GAA 結構與 TriGate 結構進行記憶體寫入抹除效率的量測，討論 Corner Effect 對於記憶體寫入抹除效率的影響。並且量測此新穎結構的元件在可靠度上面的表現，包括 Retention Time 與 Endurance 量測。最後，本研究也提出一些方法，希望可以提升 GAA 結構的特性並解決在應用上的問題。

## 第二章

### 元件製作流程與基本電性量測

#### 2.1 三維結構元件電性模擬

本節將利用ISE-TCAD模擬軟體，分別探討GAA結構與TriGate結構於奈米線通道的閘極控制能力比較，和應用於薄膜電晶體後， $I_d$ - $V_g$ 電性上的比較。首先介紹元件結構，如圖 2-1，奈米線長度為1000-nm，而受到閘極控制的通道長度(L)只有 500-nm，奈米線通道高度(H)與通道寬度(W)各為 50-nm，閘極氧化層厚度( $Tox$ )為 15-nm。

接下來介紹參數定義，奈米線通道的材料為Poly-Si，假設其材料擁有缺陷密度(Trap Density)。未受到閘極控制的奈米線通道，本實驗定義其離子佈值濃度為 磷  $1 \times 10^{20}$  ( $1/cm^3$ )，分別當作源極與汲極區域(S/D Region)，而受到閘極控制的通道並無離子佈值。閘極氧化層的材料為 $SiO_2$ ，假設它是完美的閘極氧化層，在此並未定義其缺陷密度。閘極電極材料與S/D電極材料都設定其功函數(Work function)為 4.1eV。

由於此元件的尺寸並未很小，量子效應(Quantum Effect)並不明顯，所以在此並未加入量子效應的物理機制，而是利用 Poisson Equation 與 DD model。並且考慮 Poly-Si TFTs 的閘極引發的汲極漏電流 Gate Induced Drain Leakage, GIDL) 現象，所以在此本實驗不使用 SHR 復合機制[31]，反而加入 Band to Band Tunneling 的復合機制[32]，加以探討 GAA 結構的 GIDL 現象。

以下將介紹模擬結果，首先本實驗將閘極電壓( $V_g$ )設定於10伏，源汲極電壓都接地，單純的觀察GAA結構與TriGate結構的閘極控制能力。圖 2-2，閘極電壓為10伏時的電位分布圖，本實驗可以藉由此電位分布圖，很明顯的觀察到兩種結構的閘極控制面積，是由GAA結構佔了優勢。而不一樣的電位分布，會直接影響到電子密度的分布。圖 2-3(a)，閘極電壓為10伏GAA結構的電子密度圖，其電子密度平均的集中於四個表面與四個角落。圖 2-3(b)，是只取圖通道表面的電子密度值做成的圖表，可以很明顯的發現四個角落的電子密度比四個表面高出許多，此為Corner Effect。

圖 2-1、模擬元件結構示意圖。

圖2-2、閘極電壓為10伏下的電位圖(a)GAA結構，(b)TriGate結構。

圖2-3、閘極電壓為10V時GAA結構(a)電子密度圖，(b)通道表面電子密度圖。

圖2-4、閘極電壓為10V時TriGate結構(a)電子密度圖，(b)通道表面電子密度圖。

圖 2-4為TriGate結構的電子密度圖，由於閘極控制面積的減少，電子密度僅集中於三個表面與四個角落，但是其中兩個角落Corner Effect也明顯減弱。圖 2-5為此兩種結構的TFT在 $I_d$ - $V_g$ 的電性比較，並將轉換特性整理於表 2-1。由於GAA結構的閘極控制能力較強，所以有高驅動電流、較小的 $V_{th}$ 、較優越的次臨界斜率、較小的DIBL等優點。但是本實驗在圖 2-5中可以觀察到GAA結構的GIDL比TriGate結構還要明顯。GIDL現象會發生於閘極給負電壓時，與汲極端的正電壓產生很大的電場導致Band to Band Tunneling，使漏電流增加。雖然GAA結構會增加閘極控制面積，但是也同時增加閘極與

汲極端的面積，導致漏電面積增加，使GIDL現象更明顯。而抑制GIDL現象的方法有很多種，例如使用LDD結構的製程技術或是使用Offset的結構的製程技術，目的都是要降低開極與汲極端的電場，抑制GIDL的現象。

圖2-5、GAA結構與TriGate結構薄膜電晶體的 $I_d$ - $V_g$ 比較圖。

表2-1、GAA結構與TriGate結構薄膜電晶體的 $I_d$ - $V_g$ 比較表格。

|                    | TriGate                       | GAA                           |

|--------------------|-------------------------------|-------------------------------|

| $V_{th}$ (V)       | <b>0.370</b>                  | <b>0.286</b>                  |

| S.S. (mV/V)        | <b>157</b>                    | <b>125</b>                    |

| $G_m$ MAX(S)       | <b>1.04e-5</b>                | <b>1.66e-5</b>                |

| DIBL(mV/V)         | <b>284</b>                    | <b>265</b>                    |

| $I_{ON} / I_{OFF}$ | <b><math>1.27*10^8</math></b> | <b><math>7.51*10^8</math></b> |

| GIDL@ $V_g=-2V$    | <b><math>1.22e-11</math></b>  | <b><math>3.42e-11</math></b>  |

Note:  $V_D=0.5V$   $T_{ox}=20nm$   $L=0.5um$   $W=50nm$   $T_{Poly}=50nm$

## 2.2 元件製作流程

首先利用高溫常壓水平爐管在六吋矽晶圓基板上濕氧化(Wet Oxidation)，產生450 nm的二氧化矽( $\text{SiO}_2$ )，之後再用低壓水平爐管沉積50-nm的Amorphous-Si( $\alpha$ -Si)當做主動層，如圖 2-6所示。

在此本實驗利用Spacer的技術定義本實驗的奈米線通道(Nanowire Channel)[33]，先在50-nm的 $\alpha$ -Si上沉積80-nm的TEOS (Tetraethoxysilane，四乙氧基矽烷，化學式： $\text{Si}(\text{OC}_2\text{H}_5)_4$ )，如圖 2-7，經過微影(Lithography)和乾蝕刻(Dry Etch)定義出方形的圖形，如圖 2-8所示。再利用LPCVD沉積80-nm的氮化矽(Nitride)並乾蝕刻氮化矽 80-nm。此時上一步的TEOS方形圖案周圍會殘存氮化矽，本實驗將利用之當作定義奈米線通道的Hard Mask，如圖 2-9所示。製作出氮化矽的殘留物Spacer後，經過微影系統定義出源極/汲極區(S/D Region)光阻的圖案，如圖 2-10，利用B.O.E(1：7)濕蝕刻去除TEOS，此時主動層的Mask已經大致完成，如圖 2-11。接著進行乾蝕刻 $\alpha$ -Si 50-nm，如圖 2-12，並用Ozone Asher去除光阻，包括S/D Region和奈米線通道的主動層即完成，如圖 2-13所示。

為了將 $\alpha$ -Si奈米線通道轉換成Poly-Si奈米線通道，本實驗將元件在氮氣中進行600 °C 24hr的退火。之後是環繞式閘極最重要的一個步驟，先將元件進行RCA清洗，利用DHF(1：50)去除 $\alpha$ -Si下面的二氧化矽200-nm，此時的奈米線通道將會懸空(Suspended)，如圖 2-14。接著馬上進行多層閘極氧化層沉積，本實驗將懸空的元件，利用LPCVD先後沉積TEOS/Nitride/TEOS=(10.5-nm/5.5-nm/15.3-nm)，如圖 2-15，並沉積 $\text{N}^+$ 多晶矽200-nm當作閘極，將懸空的奈米線通道環繞式的包覆，製作出環繞式閘極的結構。之後利用微影與乾蝕刻技術，定義出閘極的圖案並蝕刻 $\text{N}^+$ 多晶矽，如圖 2-16。此時S/D上面仍有多層閘極氧化層，本實驗用乾蝕刻去除TEOS 15.3-nm和Nitride 5.5-nm，但是仍留下TEOS約10-nm尚未去除，是為了當作犧牲氧化層(Pad Oxide)，避免接下來的離子佈值(Ion Implantation)造成S/D的結構破壞，使表面粗操度增加，增加金屬的接觸電阻。此時，多晶矽閘極上的光阻尚未去除，本實驗利用它達成自我對準(Self-alignment)的S/D Implantation。之後的製程步驟和標準製程大致相同，去除閘極光阻後，利用LPCVD疊上300-nm的TEOS當作隔絕水氣層(Passivation layer)，再經過600°C 6小時的活化，降低S/D的接觸阻抗。利用微影與乾蝕刻技術，蝕刻出接觸孔(Contact Hole)，並以熱蒸鍍的方式鍍鋁200-nm，並再次利用微影與蝕刻技術，蝕刻出金屬層圖案。最後，本實驗將元件進行30分鐘的H<sub>2</sub> Sinter，修補鋁電極與S/D和多晶矽閘極的缺陷，降低接觸電阻。

圖2-6、在wet oxide上面沉積非晶矽。

圖2-7、在非晶矽上面沉積TEOS。

圖2-8、以光阻當作Mask蝕刻出TEOS Block。

圖2-9、利用乾蝕刻技術，蝕刻出Nitride Spacer。

圖2-10、利用微影技術Pattern出Source/Drain形狀。

圖2-11、利用BOE把TEOS Block去除。

圖2-12、垂直性乾蝕刻非晶矽。

圖2-13、把Source/Drain上面的光阻去除。

圖2-14、利用DHF蝕刻wet oxide使奈米線通道懸空。

圖2-15、(a)利用LPCVD環繞式沉積O/N/O閘極氧化層，(b)通道縱切面圖。

圖2-16、(a)利用LPCVD沉積Poly Gate並微影蝕刻出Poly Gate的形狀，(b)通道橫切面圖，(c)通道縱切面圖。

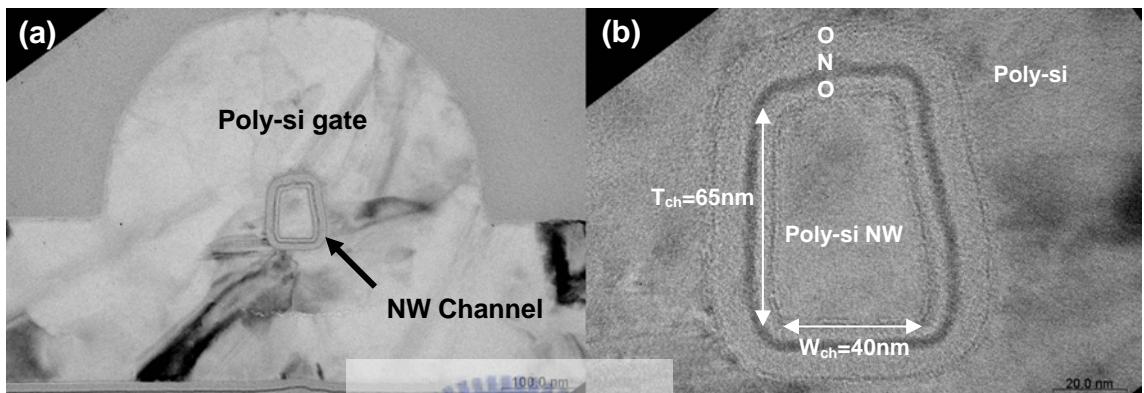

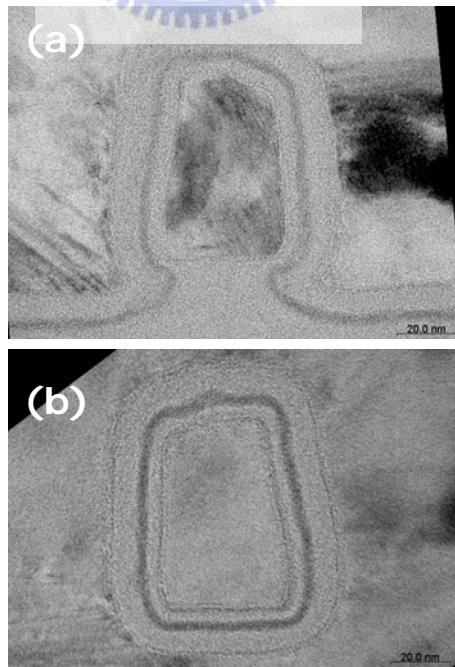

## 2.3 元件TEM圖

以上是介紹元件的製程流程，元件完成後，本實驗進行 TEM Image 的確認。圖 2-17(a)(b)分別為 GAA 與 TriGate 兩種結構的 Nanowire Channel 剖面圖，可以清楚看到奈米線通道為方形的結構，圖中通道的寬度( $W_{ch}$ )約為 62-nm，高度( $T_{ch}$ )約為 44-nm。NW 的寬度取決於 Nitride Spacer 的寬度，假如希望擁有較小線寬的奈米線，可以降低 TEOS Block 的高度，或是增加蝕刻 Nitride Spacer 時 Over Etch 的時間。然而，NW 的厚度主要取決於沉積  $\alpha$ -Si 的厚度，但也需注意蝕刻 TEOS Block 時，過大的 TEOS Over Etch 也會同時造成  $\alpha$ -Si 厚度的下降。

同時比較圖 2-17(a)(b)，可以明顯發現 GAA 結構的通道被 TEOS/Nitride/TEOS=(10.5-nm/5.5-nm/15.3-nm)和  $N^+$  Poly Gate 環繞式均勻地包覆，然而方形的通道結合 GAA 的結構，本實驗可以初步看到 GAA 結構比起 TriGate 結構，更能使閘極控制面積有效的增加，並且通道的 Corner 數量也同時增加。由於三維結構閘極的演變，使得閘極控制面積增加，本實驗定義一個參數：有效的通道寬度( $W_{eff}$ )，GAA 結構的  $W_{eff}$  為通道數目乘上  $2(W_{ch}+T_{ch})$ ，而 TriGate 結構的  $W_{eff}$  為通道數目乘上  $(W_{ch}+T_{ch}+T_{ch})$ ，這個定義將在接下來的章節廣泛的應用。

圖 2-17、奈米線通道的 TEM 圖(a)GAA 結構，(b)TriGate 結構，其中

$W_{ch}/T_{ch}=62\text{-nm}/44\text{-nm}$ ， $O/N/O=10.5\text{-nm}/5.5\text{-nm}/15.3\text{-nm}$ 。

## 2.4 參數萃取方法

本節將介紹量測的參數萃取，包括臨限電壓(Threshold Voltage)、次臨界斜率(Subthreshold Swing, SS)、汲極引發位能障下降(DIBL)等特性。將量到的參數比較分析，而電性的量測機台主要以 HP 4156 半導體分析儀量測，軟體則為 ICS 操作系統，GPIB 為連接兩硬軟體的溝通介面。

### 2.4.1 臨限電壓定義(Threshold Voltage)

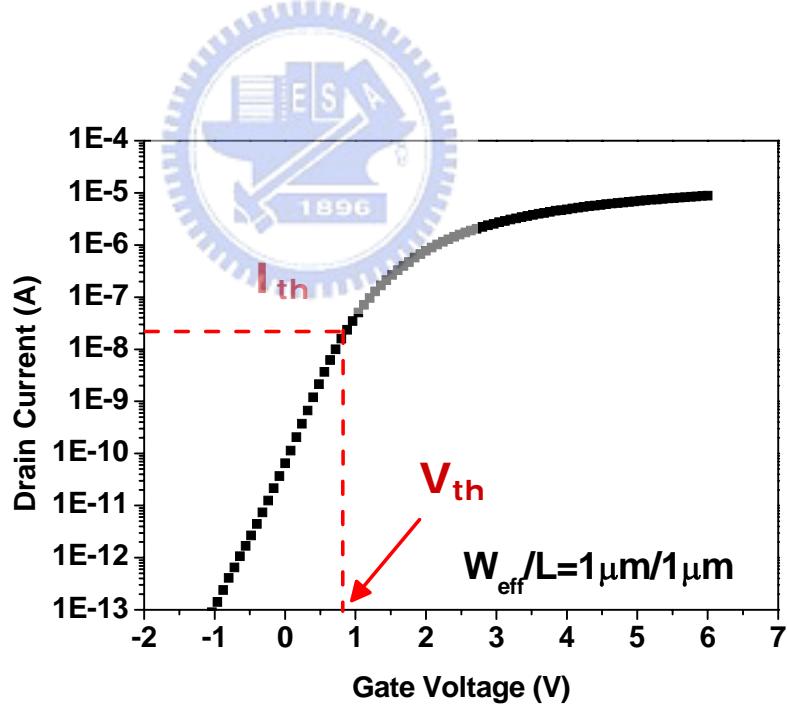

$V_{th}$ 為MOSFET元件中最基本且重要的參數，它的定義方法為將量到的  $I_d$ - $V_g$  圖，在固定的  $V_d$  下，取  $G_m$ (Transconductance)最大值對應到  $I_d$ - $V_g$  下的  $V_g$  且fit出一條直線與X軸的切點  $V_g$ ，在扣掉二分之一  $V_d$ (線性區電流等於零時)，即為  $V_{th}$ 。而本實驗是利用定電流法估計，在  $I_d = (W_{eff} / L) \times 10^{-8} A = I_{th}$  時的  $V_g$  即為  $V_{th}$ ，如圖 2-18。

圖2-18、定電流  $V_{th}$  定義方法。

## 2.4.2 次臨界斜率定義(Subthreshold Swing)

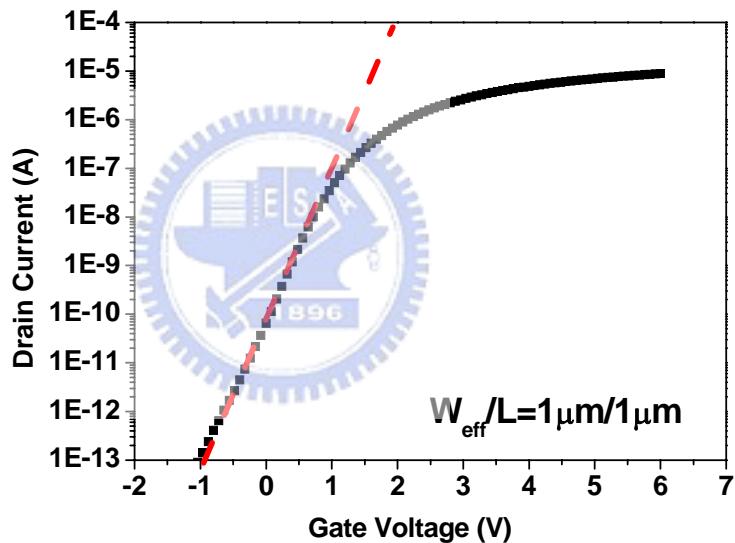

次臨界斜率的定義方法為在弱反轉區的次臨界電流，取對數除以 $V_g$ 的倒數。

$$S = \left[ \frac{\partial \log_{10}(I_d)}{\partial V_g} \right]^{-1} \quad (2-1)$$

如圖2-19，首先元件操作在線性區，外加 $V_d$ 為0.1 V，量測  $\log_{10}(I_d)$ -  $V_g$ 圖。接下來求出在弱反轉區的最大斜率，並取之倒數，即為次臨界斜率(S)的求法。次臨界斜率的單位為mV/dec，越小的次臨界斜率即代表此元件閘極控制能力佳，可以操作很小的 $V_g$ 變化，即可取得很大的電流變化。

圖2-19、Subthreshold Swing定義方法。

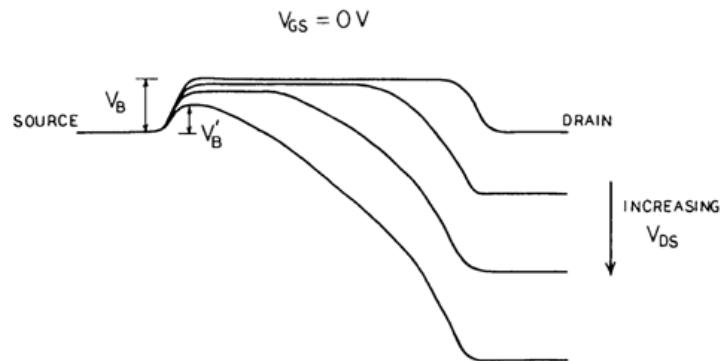

## 2.4.3 沖極引發位能障下降定義(Drain Induced Barrier Lowing)

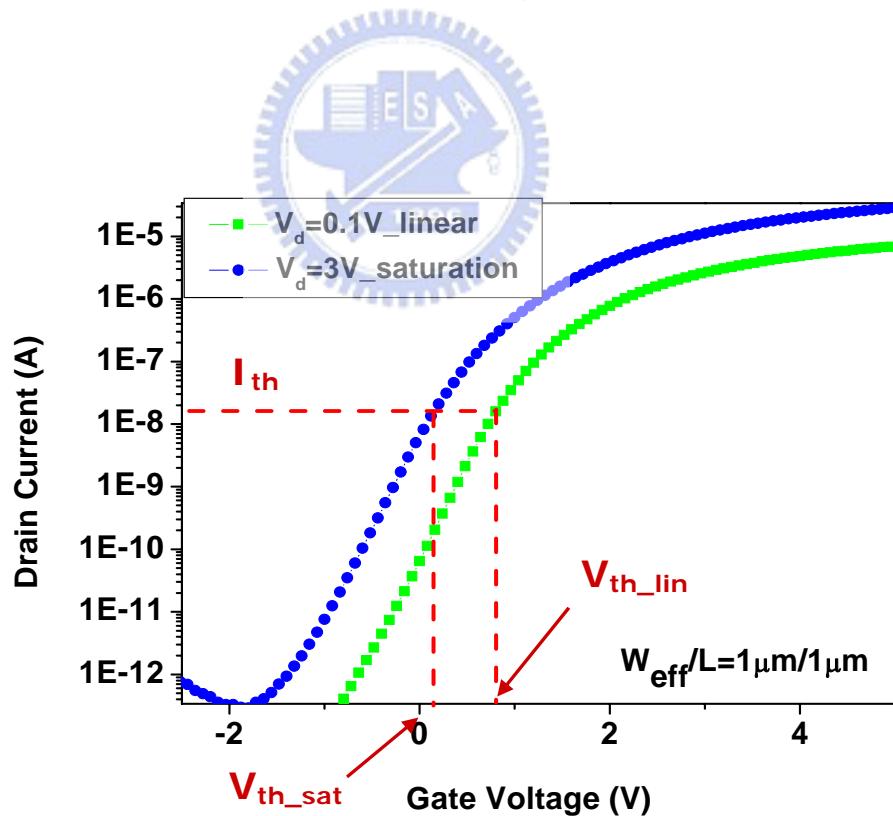

沖極引發位能障下降(DIBL)的原因是由於沖極端的電壓( $V_d$ )增加，沖極端的位能下降，連帶源極端的能位帳( $V_B$ )也隨之下降，而 $V_{th}$ 下降，使元件容易導通，如圖2-20。當元件越做越小，通道長度也隨之下降，DIBL的現象也會越來越明顯，越小的DIBL值表示元件閘極控制能力強，源極端的能位障( $V_B$ )不容易被沖極端的電壓影響( $V_d$ )，是判斷元件閘極控制能力的重要指標。在此本實驗定義DIBL(mV/V)的公式如下：

$$DIBL(\frac{mV}{V}) = \frac{V_{TH\_lin} - V_{TH\_sat}}{|Vd\_lin - Vd\_sat|} \quad (2-2)$$

先用定電流  $V_{th}$  定義法，分別在  $V_d$  為 0.1 V 與 3 V 下所量到的  $V_{th}$ ，兩者的差除以  $V_d$  的差，即為 DIBL 的值，如圖 2-21。

圖 2-20、DIBL 能帶示意圖。

圖 2-21、DIBL 定義方法。

## 2.5 電性基本量測與討論

在此章節將介紹元件的基本量測結果，主要包含不同的多重閘極結構，對於電晶體轉換特性的影響、多重奈米線通道薄膜電晶體與傳統平面式薄膜電晶體的電性比較、奈米線通道的多寡對於電性上的變異。

### 2.5.1 不同的多重閘極結構對於電晶體轉換特性的影響

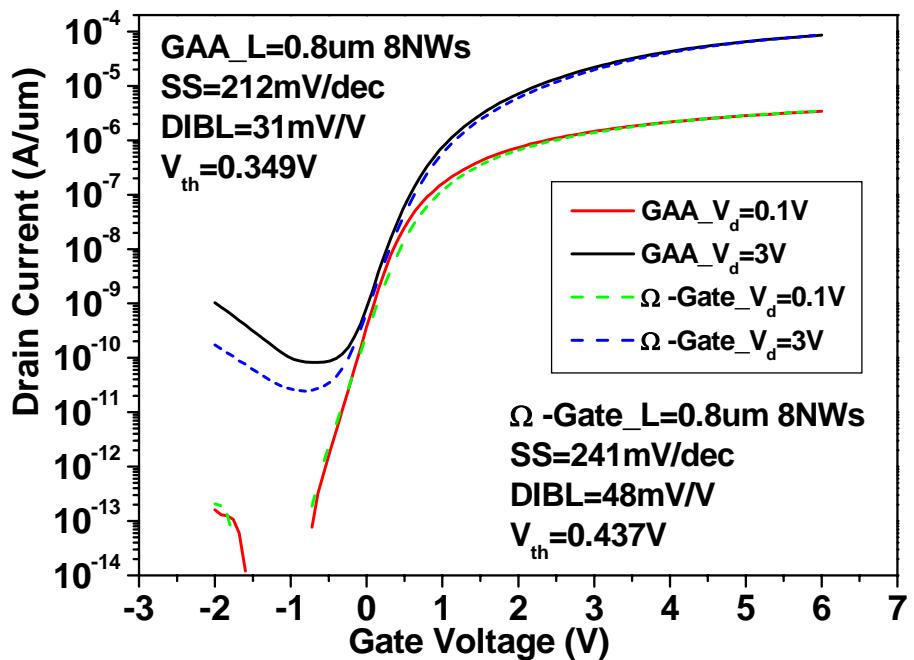

在之前的章節介紹了GAA與TriGate結構的差異，在此本實驗實際做出元件，量測其基本電晶體轉換特性，並加以討論。圖 2-22 為GAA與TriGate結構在 $I_d$ - $V_g$ 上的比較，並將其電性參數整理於圖的右下角。在此注意圖中的縱軸為規一化(Normalize)後的Drain Current，是將Drain Current除以 $W_{eff}$ ，其單位為A/ $\mu m$ 。規一化的目的是為了表達單位通道寬度的電流，可以客觀的比較出元件優劣。

圖 2-22、GAA結構與TriGate結構的 $I_d$ - $V_g$ 圖。

在圖 2-22 中，本實驗可以印證模擬的結果，GAA 結構由於閘極的控制面積變大，使得閘極的控制能力變好，因此有較大的驅動電流、較小的 DIBL、較小的次臨界斜率...等優點，但是也同時造成 GIDL 變大。但是模擬的電性與實際量測的電性有點不同，可能有以下的原因

- (1) 模擬元件結構與實際結構不同。

- (2) 模擬時的 Gate oxide 為完美的  $\text{SiO}_2$ ，但實際上是 TEOS。

- (3) Poly-Si 裡的 Grain Boundary 並未考慮。

- (4) Poly-Si 的 Trap density 模擬參數不正確。

雖然，模擬的數據與實際量測的數據有差異，不過可以看出大致上的趨勢。也發現 GAA 結構的 GIDL 過大的問題。在這邊我提出幾個方法來改善 GAA 的漏電問題，這些方式都是降低汲極端的電場，來改善漏電，例如：LDD 結構或是 off-set 結構。

### 2.5.2 多重奈米線通道薄膜電晶體與傳統平面式薄膜電晶體的轉換電性

#### 比較

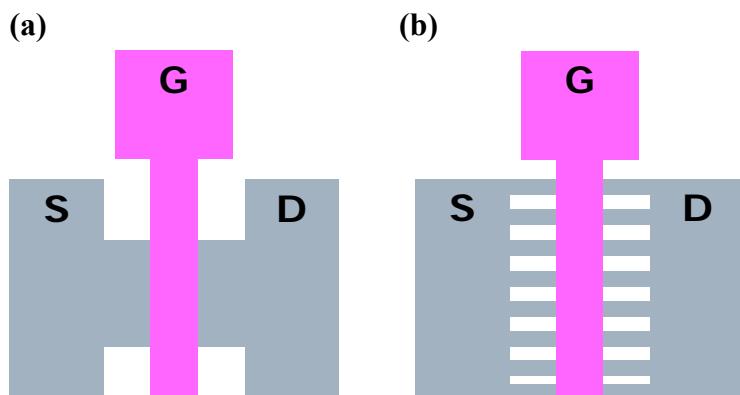

在這節將先討論多重奈米線通道結構(Multiple NWs)與傳統平面式結構(Planar)的結構差異，再近而討論他們對於薄膜電晶體的電性影響。圖 2-23，本實驗可看到這兩種結構的差別，多重奈米線通道是由很多的奈米線組成，配合 GAA 閘極結構，可以增加閘極掌控的面積，增加 Corner 的數量，提升 Corner Effect 的效應，讓元件擁有很多的閘極掌控能力。為了比較出多重奈米線通道結構的優勢，本實驗比較兩者的  $I_d$ - $V_g$ ，如圖 2-24。圖中本實驗可以看到無論是 GAA 或是 TriGate 結構的多通道閘極薄膜電晶體，在  $I_d$ - $V_g$  電性上都比傳統平面式的薄膜電晶體還要優越。

圖 2-23、(a)Planar 結構，(b)Multiple NWs 結構的示意圖。

圖 2-24、8 個奈米線通道的 GAA 和 TriGate 結構薄膜電晶體與  $W_{eff}=2 \mu m$  的 Planar device 的  $I_d$ - $V_g$  比較圖。

### 2.5.3 奈米線通道的多寡，對於電晶體轉換特性上的變異

隨著莫爾定律的演進，當元件尺寸也同時越做越小，元件特性的變異(Fluctuation)也越來越受到重視[34]。Poly-Si雖然擁有很多的Grain Boundary，但是傳統的薄膜電晶體由於尺寸很大，相對而言Grain Boundary對其電性影響較小，所以較少人討論其Fluctuation等議題。但是隨著Poly-Si薄膜電晶體越做越小時，Grain Boundary在元件上位置的變異，會強烈影響電性的表現[35]。本節將討論奈米線通道的多寡，對於電性上的變異影響。

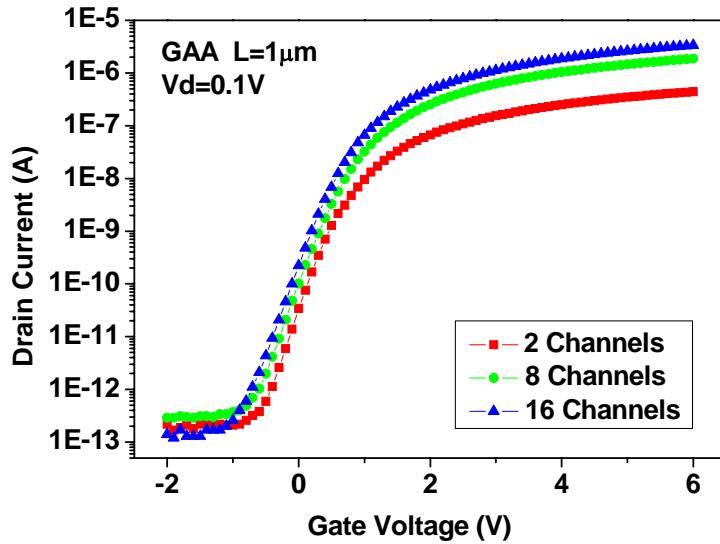

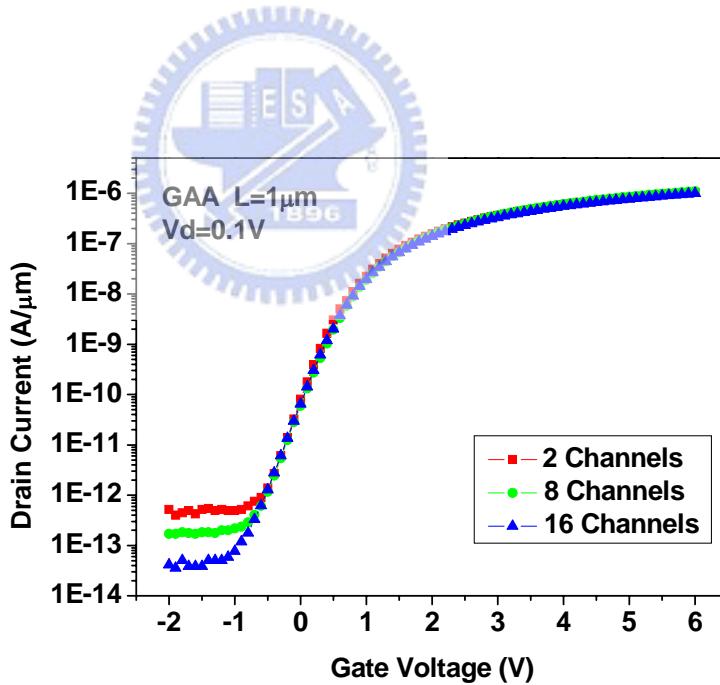

圖 2-25為不同的通道數目的 $I_d$ - $V_g$ 圖，圖中本實驗比較2個NWs、8個NWs與16個NWs這三種不同的尺寸，並在縱軸不使用規一化(Normalize)後的汲極電流，而圖2-26的縱軸是使用規一化後的汲極電流。本實驗可以由圖 2-25、2-26的兩張圖發現，由於通道數目越多，元件的驅動電流也隨之增加，但是經過規一化後，其實不同元件的 $I_d$ - $V_g$ 圖形會重疊在一起。這表示奈米線通道的增加或減少，電性也會線性

的增加或減小，而且不影響 $V_{th}$ 、次臨界斜率、DIBL等元件參數。

圖 2-25、不同的通道數目的 $I_d$ - $V_g$ 圖，縱軸為並未規一化的汲極電流。

圖 2-26、不同的通道數目的 $I_d$ - $V_g$ 圖，縱軸為規一化後的汲極電流。

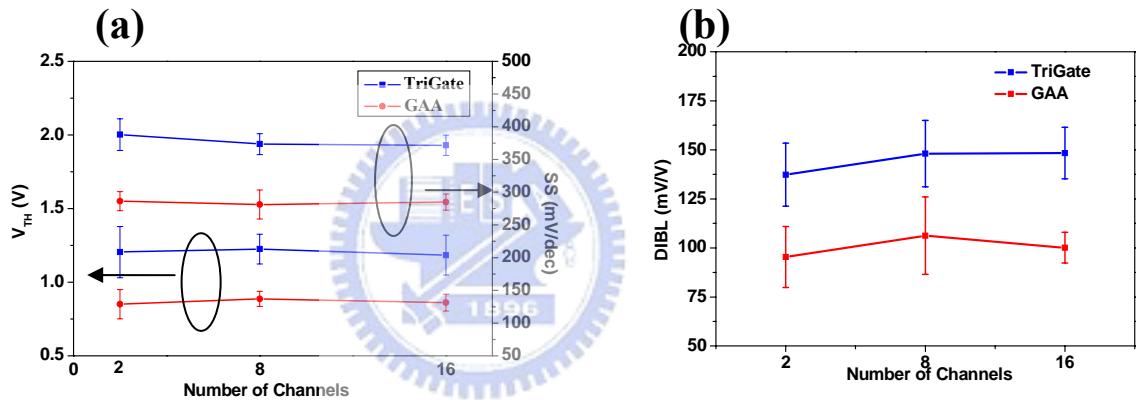

圖 2-27(a)與(b)是把2NWs、8NWs與16NWs這三種不同通道數目的元件各量22組，並取出全部的參數整理而成的元件特性變異圖。圖中本實驗比較 $V_{th}$ 、次臨界斜率、DIBL這三種參數，並取其Error Bar。本實驗可以看到這三種參數的平均值，其

實並不會隨著通道數目的多寡而改變，但是參數的變異量會隨著通道數目的減小而增加。由於奈米線通道數量的變少，Grain Boundary對於元件的影響相對變大，反而通道數目大於8NWs後，其平均了Grain Boundary對元件的影響，降低了參數變異性。由於取樣數目不是很多，圖中有幾個點不是依照此原則，但多奈米線通道擁有較小的參數變異是個趨勢。此外，目前有很多種方法可以減少Grain Boundary對電性上的影響，例如準分子雷射退火(Excimer Laser Anneal)、金屬誘發側向結晶(Metal Induce Lateral crystallization)、固相結晶法(Solid phase crystallization)或是氮電漿( $\text{NH}_3$  plasma)處理...等方法。這些方法都可以減少Grain Boundary和修補Trap Density，提升元件的驅動電流，並且減少電性上的變異[36,37]，但此論文並無著重於這些方法。

圖2-27、不同的通道數目的(a)  $V_{th}$ 與SS，(b) DIBL Variation比較。

## 第三章

### 元件記憶體特性

#### 3.1 基本穿隧機制介紹

近年來，許多團隊致力於快閃記憶體元件的研究，並且已經廣泛的應用在各種產品。其操作原理很簡單，利用注入或是抹除電荷儲存層的電荷量，調整臨限電壓的變化，來判別“0”或是“1”。目前寫入或是抹除的物理機制有很多種，普遍為以下兩種機制，第一個為通道熱電子注入 (channel-hot-electron injection，CHEI)，第二種為 Fowler-Nordheim Tunneling (FNT)，並在以下的章節加以討論。

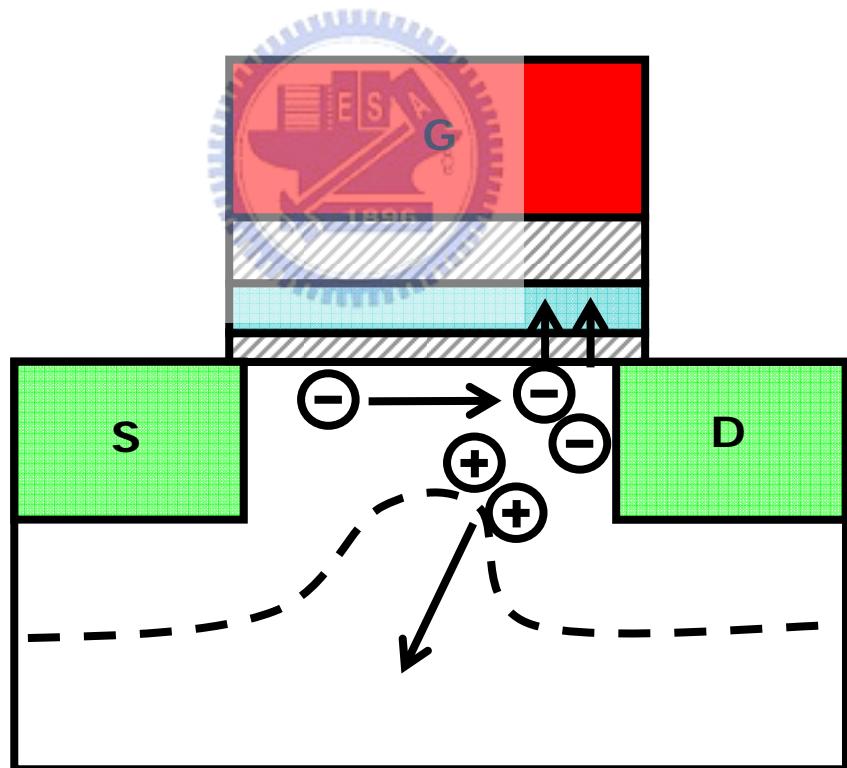

##### 3.1.1 Channel-Hot-Electron Injection

從1970年代，MOSFET的熱載子效應(Hot Carrier Effect)已經廣泛的被討論，以N型MOSFET為例，當通道反轉為導通的狀態下，且汲極端偏壓落在飽和區範圍( $V_{ds} > V_{dssat}$ )，受到橫向電場的作用下，此時產生大量的電子向汲極端移動，當元件進入夾止區時(Pinch-off Region)，電子在電場加速後擁有很多的能量會碰撞出大量的電子電洞對，此時受到閘極垂直電場的作用下，電子被吸引往閘極方向流動，閘極電流便由此產生，不然則大部分的電子可能流向汲極，電洞則可能往基極的方向流動，因而造成功率的消耗[38]，如圖3-1。相較之下快閃記憶體元件，由於比N型MOSFET多了一層浮接閘極，往上走的電子便可以儲存在此電極上，達成了記憶體寫入的目的，然而這些往上走的熱電子中集中在一個很小的區域射入，可以想見的，在經過多次的寫入之後，一些電子可能陷入氧化層中，可能陷入浮接閘極中，如此造成電子不容易射入，因而使得元件的可靠度降低。

##### 3.1.2 Fowler-Nordheim Tunneling

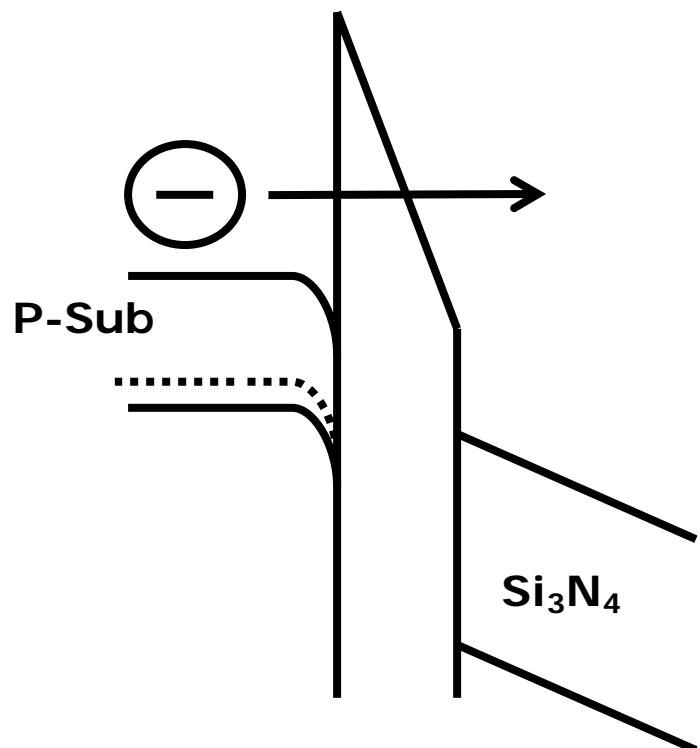

量子穿隧效應有分成兩種，一個為Direct Tunneling (DT)，另一個為Fowler-Nordheim Tunneling (FNT)，兩者都是利用跨在氧化層上的電場，使電子發生穿隧現象。其中Fowler-Nordheim Tunneling (FNT)是利用跨在氧化層上的電場，使氧化層的能帶圖彎曲，氧化層能帶厚度變薄，讓電子(電洞)的穿隧機率增加，而產生量子穿隧的現象，如圖 3-2。FNT所產生的穿隧電流，決定於跨在氧化層的電

場強度，當電場越強，能帶彎曲更劇烈，穿隧電流將會越大，其所需要的電場至少約 6 MV/cm以上。而Direct Tunneling(DT)通常發生於極薄氧化層厚度(約3-nm)的元件，由於氧化層厚度越薄，其量子穿隧效應越大，所以DT只需要較小的電場即可發生，如圖 3-3。而SONOS元件可以利用閘極施加的電壓，產生正向或是負向的電場，讓電子或是電洞發生FNT或是DT的現象，產生穿隧電流注入捕捉電荷層，使臨限電壓改變。其中FNT的穿隧電流密度公式如下，

$$J = \left[ \frac{q^3}{16\pi^2 \cdot h \cdot \text{bar} \cdot m_{ox} \cdot \Phi_B} \right] E^2 \exp \left[ \frac{-4(2m_0 m_{ox})^{1/2} \Phi_B^{3/2}}{3 \cdot h \cdot \text{bar} \cdot q \cdot E} \right] \quad (3-1)$$

公式 3-1 中的  $\Phi_B$  為 FNT 的能障高度， $m_0$  為單位有效質量， $m_{ox}$  為穿隧的有效質量比， $h \cdot \text{bar}$  為普郎克常數除以兩倍的圓周率，即  $h/2\pi = 1.054 \times 10^{-34}$  J-S，單電子的電荷量  $q$  為  $1.6 \times 10^{-19}$  C， $E$  為電場強度。

圖 3-1、Channel-Hot-Electron Injection 機制示意圖。

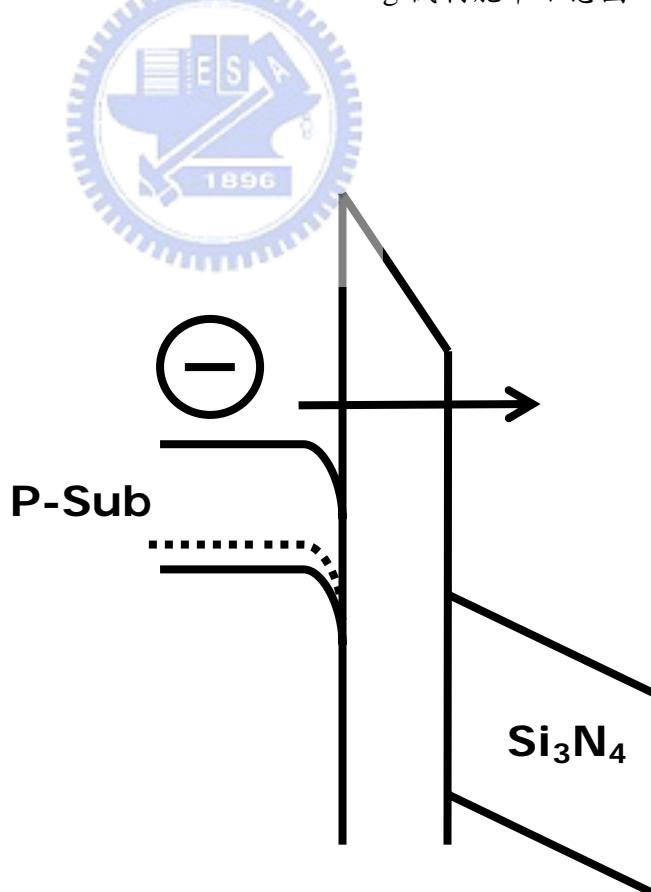

圖 3-2、Fowler-Nordheim Tunneling 機制能帶示意圖。

圖 3-3、Direct Tunneling 機制能帶示意圖。

### 3.2 元件電場模擬

之前的章節已經探討 Corner Effect 對於轉換特性的影響，例如可以降低次臨界斜率、增加驅動電流、抑制短通道效應…等優點，本節將繼續討論 Corner Effect 對於 FNT 的影響。首先利用 ISE TCAD 模擬環繞式閘極元件的電場分布，並把模擬出來的角落電場代入 FNT 的公式，加以探討穿隧電流大小。模擬的元件依照實際元件的大小設計，閘極電壓也按照實際操作寫入抹除時所施加的電壓，並假設沒有任何的電荷儲存於閘極氧化層(Gate Oxide)與捕捉電荷層(Trapping Layer)。在此假設任何的電荷注入電荷捕捉層都會被困住，電荷沒有任何的機率可以從缺陷中釋放。

首先模擬寫入(Program)時的電場分布，此時閘極電壓施加 22V，如圖 3-4。為了探討平邊區域(flat surface)與角落區域(corner region)兩者電場的差異，本實驗將圖 3-4 做兩個切線，取出平邊區域(切線 A)與角落區域(切線 B)的電場絕對值，如圖 3-5, 3-6。可以發現平邊區域因為沒受到 Corner Effect 影響，電場大約  $9.1 \times 10^6 \text{ V/cm}$ ，而角落區域因為 Corner Effect 的影響，擁有最大的電場約  $1.6 \times 10^7 \text{ V/cm}$ 。

圖 3-4、當閘極電壓為 22V 時，GAA 結構的電場分布模擬圖，其中切線 A 為平邊區域，切線 B 為角落區域。

圖 3-5、當閘極電壓為 22V 時，平邊區域(切線 A)的電場絕對值分布圖。

圖 3-6、當閘極電壓為 22V 時，角落區域(切線 B)的電場絕對值分布圖。

元件操作在寫入(Program)時，閘極施加正電壓，在通道表面與穿隧氧化層(Tunneling Oxide)產生電場，讓能帶圖彎曲，發生 FNT，使通道表面的電子注入捕捉電荷層(Trapping Layer)，讓  $V_{th}$  變更。同時，閘極與 Blocking Oxide 的表面也有個電場，使閘極的電洞發生 FNT 注入捕捉電荷層。因此注入的有效穿隧電流為兩者的總和，這兩個穿隧電流一正一負，同時注入捕捉電荷層會互相抵消。接下來將把模擬的電場絕對值代入 FN 穿隧電流密度公式 3-1，加以討論有效的穿隧電流密度。

$$J = \left[ \frac{q^3}{16\pi^2 \cdot h \cdot \text{bar} \cdot m_{ox} \cdot \Phi_B} \right] E^2 \exp \left[ \frac{-4(2m_0 m_{ox})^{1/2} \Phi_B^{3/2}}{3 \cdot h \cdot \text{bar} \cdot q \cdot E} \right] \quad (3-1)$$

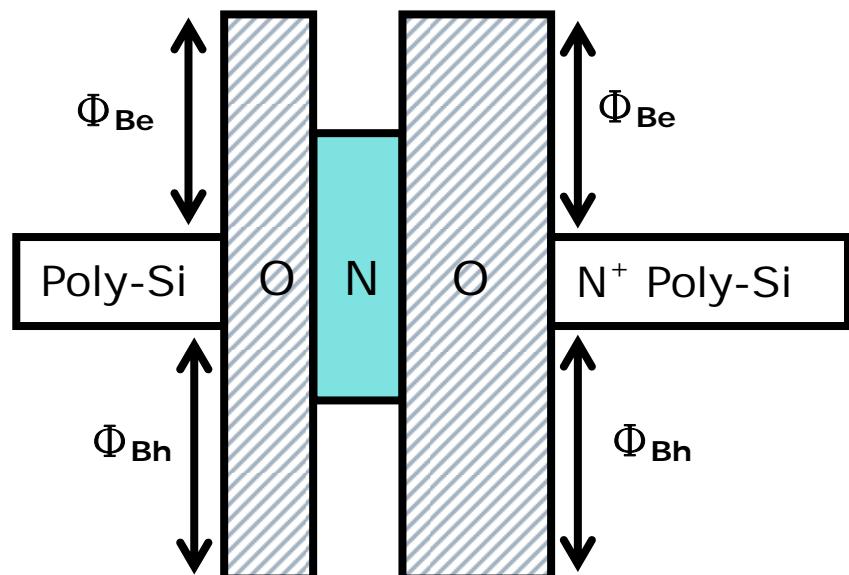

公式 3-1 中的  $\Phi_B$  為 FNT 的能障高度，在此案例，電子欲從 Poly-Si 通道表面穿隧  $\text{SiO}_2$  至 Nitride， $\Phi_{Be}$  即為 Poly-Si 與  $\text{SiO}_2$  的 conduction band 能障高度差， $\Phi_{Be}$  約  $3.15\text{eV}$ 。反之電洞欲從 Poly-Si 閘極穿隧  $\text{SiO}_2$  至 Nitride， $\Phi_{Bh}$  即為 Poly-Si 與  $\text{SiO}_2$  的 valance band 能障高度差， $\Phi_{Bh}$  約  $4.3\text{eV}$ ，如圖 3-7。另外， $m_0$  為單位有效質量， $m_{ox}$  為穿隧的有效質量比，其中電子的穿隧有效質量比( $m_{eox}$ )為  $0.5$ ，電洞的穿隧有效質量比( $m_{hox}$ )為  $0.77$ 。 $\text{h-bar}$  為普郎克常數除以兩倍的圓周率，即  $h/2\pi = 1.054 \times 10^{-34} \text{ J-S}$ ，單電子的電荷量  $q$  為  $1.6 \times 10^{-19} \text{ C}$ 。以上的參數整理於表 3-1。

圖 3-7、FNT 公式的能障高度示意圖。

表 3-1、FNT 公式的參數整理。

| 參數名稱        | 參數值      | 單位   |

|-------------|----------|------|

| $\Phi_{Be}$ | 3.15     | eV   |

| $\Phi_{Bh}$ | 4.3      | eV   |

| q           | 1.6E-19  | C    |

| $h_{bar}$   | 6.6E-16  | eV-S |

| $M_0$       | 9.11E-31 | Kg   |

| $M_{eox}$   | 0.5      |      |

| $M_{hox}$   | 0.77     |      |

| $\Pi$       | 3.14     |      |

接下來本實驗將圖 3-5 中，通道與 Tunneling Oxide 的接面電場絕對值代入公式 3-1，求出電子穿隧電流密度  $J_{e1}=1.05\times10^{-5} \text{ A/cm}^2$ ，將閘極與 Control Oxide 的接面電場絕對值代入公式 3-1，求出電洞穿隧電流密度  $J_{h1}=2.71\times10^{-28} \text{ A/cm}^2$ 。可以發現平邊區域(切線 A)在閘極電壓為 22V 的時候，電洞由閘極注入(Gate Injection)的現象並不明顯，電子注入的電流密度  $J_{e1}$  遠大於電洞注入的電流密度  $J_{h1}$ 。利用圖 3-6，也可以取得角落區域(切線 B)在閘極電壓為 22V 時的電子穿隧電流密度  $J_{e2}=1.17\times10^1 \text{ A/cm}^2$  和電洞穿隧電流密度  $J_{h2}=1.66\times10^{-73} \text{ A/cm}^2$ 。本實驗發現不管是角落區域(切線 B)或是平邊區域(切線 A)，有效的穿隧電流密度都是由通道表面注入的穿隧電流主導，而且角落區域(切線 B)的電子穿隧電流密度  $J_{e2}$  遠大於平邊區域(切線 A)的  $J_{e1}$  約 6 個次方，因此模擬結果証實，受到 Corner Effect 影響的區域可以增加穿隧電流密度，提升 Program 的效率。

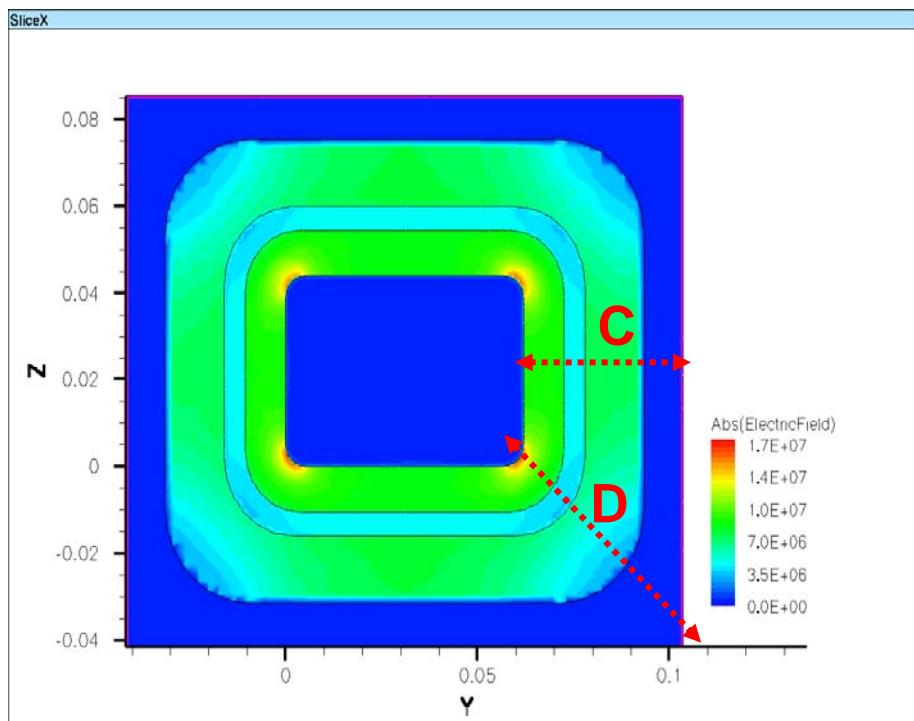

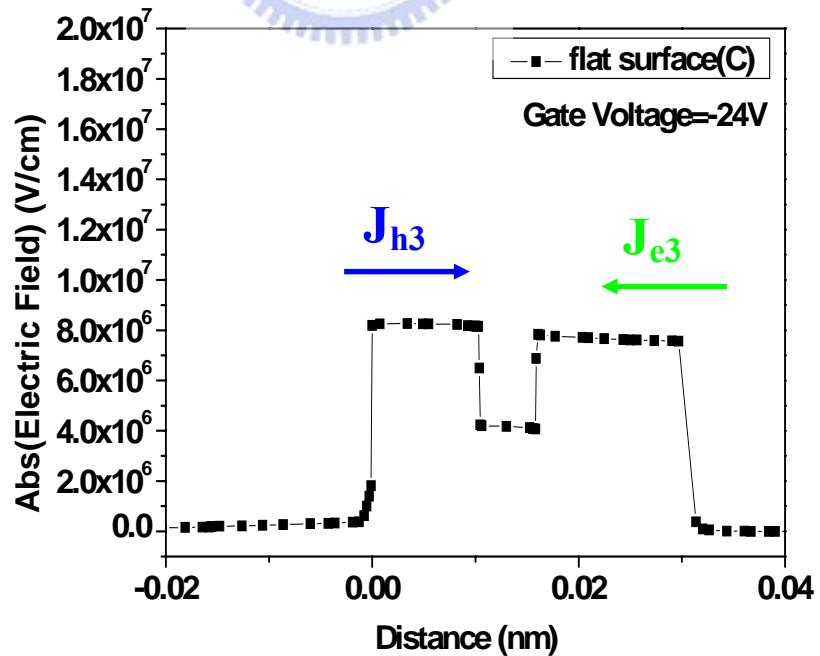

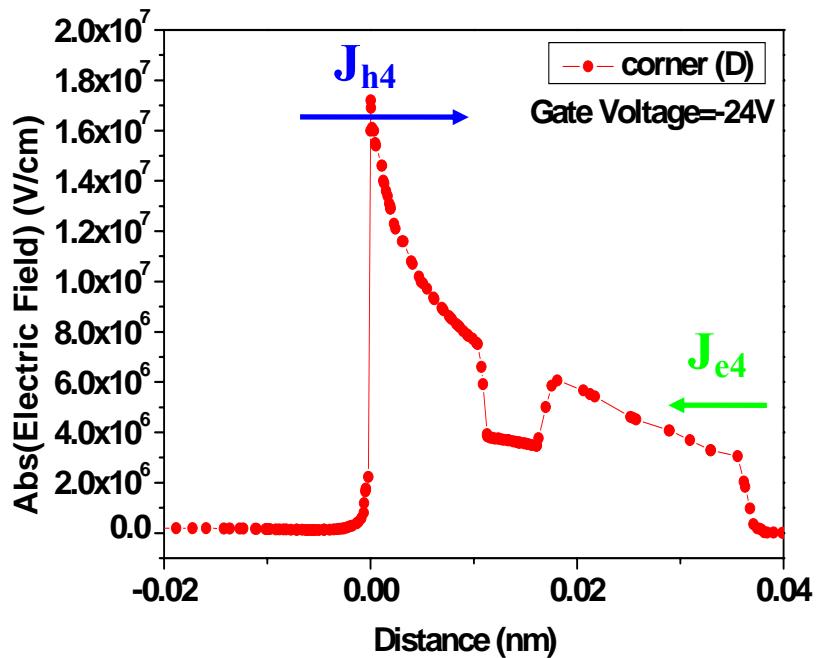

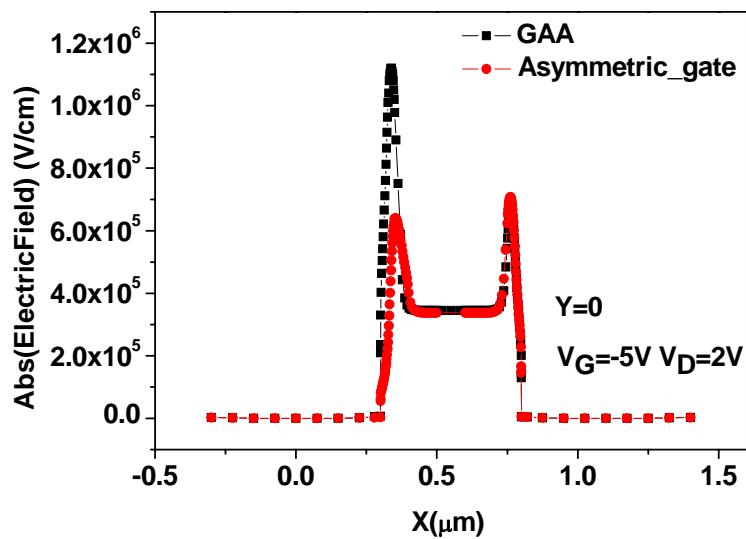

以上本實驗模擬閘極施加 22V 的情形，接下來本實驗模擬閘極電壓為-24V 的電場分布，如圖 3-8。也同時在圖 3-8 中做兩條切線，其中切線(C)代表平邊區域(flat surface)，而切線(D)代表角落區域(corner)，並將兩者的電場絕對值取出，分別用圖 3-9 與圖 3-10 表示。可以發現角落區域因為 Corner Effect 的影響，擁有較大的電場約  $1.7\times10^7 \text{ V/cm}$ 。

圖 3-8、當閘極電壓為-24V 時，GAA 結構的電場絕對值分布模擬圖，其中切線 C 為平邊區域，切線 D 為角落區域。

圖 3-9、當閘極電壓為-24V 時，平邊區域(切線 C)的電場絕對值分布圖。

圖 3-10、當閘極電壓為-24V 時，角落區域(切線 D)的電場絕對值分布圖。

此外元件操作在抹除(Erase)的時候，閘極施加負電壓，也會同時產生兩個穿隧電流，一個是電洞穿隧電流，經由通道表面穿隧至補捉電荷層，另一個是電子穿隧電流，經由閘極穿隧至補捉電荷層。本實驗利用圖 3-9 的電場絕對值代入公式 3-1，求出平邊區域(切線 C)的電洞穿隧電流密度  $J_{h3}=2.26 \times 10^{-21} \text{ A/cm}^2$  和電子穿隧電流密度  $J_{e3}=1.81 \times 10^{-8} \text{ A/cm}^2$ 。在此意外發現，當閘極電壓操作在-24V 的時候，平邊區域的閘極電子穿隧的效率大於通道電洞穿隧的效率，產生 Gate Injection 的現象 [39,40]。會產生 Gate Injection 的現象並不是本實驗所希望見到的，原本操作在 Erase 時， $\Delta V_{th}$  應該會小於 0，但是元件的設計不良等因素，可能產生 Gate Injection 使  $\Delta V_{th}$  大於 0，讓元件操作狀態不正常。另外本實驗也利用圖 3-10，求出角落區域(切線 D)的電洞穿隧電流密度  $J_{h4}=3.88 \times 10^{-6} \text{ A/cm}^2$  和電子穿隧電流密度  $J_{e4}=7.21 \times 10^{-33} \text{ A/cm}^2$ 。本實驗發現由於 Corner Effect，使角落區域的電洞穿隧電流密度  $J_{h4}$  比平邊區域的  $J_{h3}$  還要大很多，並且角落區域的電子穿隧電流密度  $J_{e4}$  也被 Corner effect 抑制。因此元件操作在 ERASE 時，利用 corner effect 除了可以提升電場，增加電洞的穿隧效率之外，也可以抑制 Gate Injection 的現象。

### 3.3 元件計憶體特性量測

上一節模擬出 GAA 結構的電場，並且代入 FNT 的公式，求得有效的穿隧電流密度。由模擬結果得知，經由 Corner Effect 影響的區域，可以有效增加穿隧電流密度，並且抑制 Gate Injection 現象。本章節將實際量測 GAA 結構和 TriGate 結構 Poly-Si NWs TFTs 的 Program/Erase 特性，並探討是否會因為 Corner Effect 的影響多寡，而造成兩者在 Program/Erase 的特性差異。另外，本實驗量測 Retention Time 與 Endurance 等記憶體特性，探討元件可靠度的優劣。

#### 3.3.1 FN Tunneling Program/Erase 特性量測

延續著之前的章節，接下來探討 GAA Poly-Si NWs SONOS-TFTs 在 Program/Erase 上的表現，並與 TriGate 結構比較 Window 大小。在此本實驗使用 FN tunneling 的操作機制，在閘極施加電壓並且 S/D 端接地，利用閘極產生垂直於通道的電場，使載子發生 FN tunneling，讓  $V_{th}$  變更。以下量測，都是使用通道長度為 1um 的八通道奈米線元件。

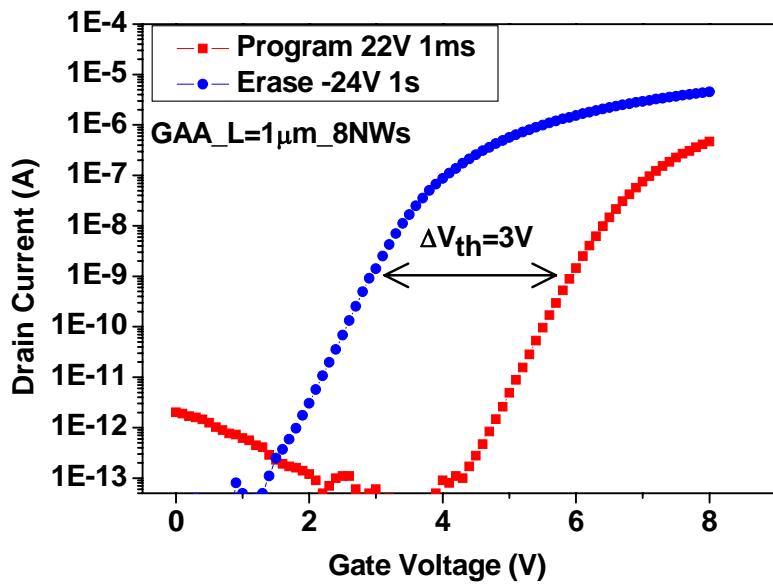

如圖 3-11，GAA 結構的元件經過閘極 22V 1mS 的 Program 後， $I_d-V_g$  曲線向右平移， $V_{th}$  約為 6.5V。經過閘極-24V 1S 的 Erase 後， $I_d-V_g$  曲線向左平移， $V_{th}$  約 3.5V。經過 FN tunneling 操作 Program/Erase 後的  $I_d-V_g$  曲線， $V_{th}$  的差值約 3V，並且次臨界斜率沒有改變，表示元件在此操作條件下可以運作，不會對元件產生破壞。

圖 3-11、GAA 結構的元件經過 FNT 操作 Program/Erase 後的  $I_d$ - $V_g$  曲線。

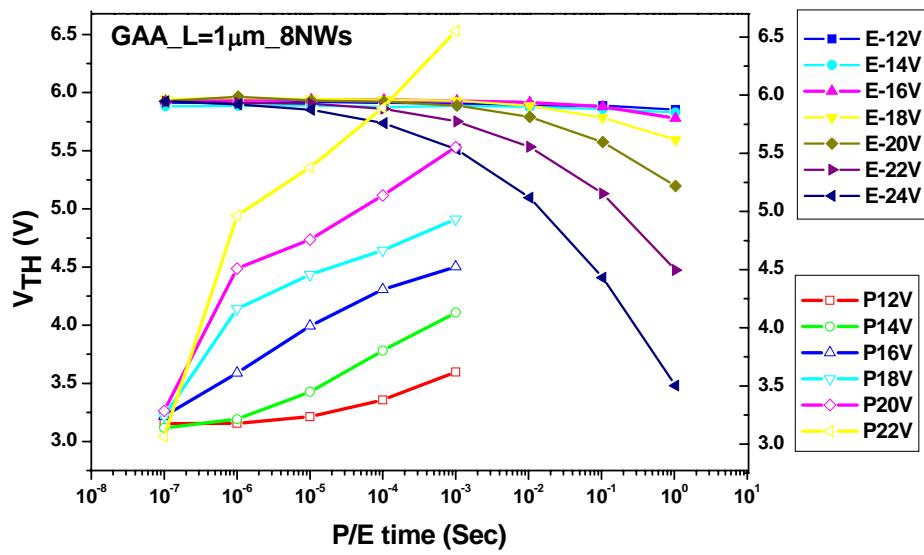

為了更仔細的探討 GAA 結構的元件 Program/Erase 特性表現，本實驗做了陣列式的量測。首先將元件操作在固定的  $V_{th}$  狀態，固定 Program Voltage，改變 Program Time，觀察  $V_{th}$  在同個閘極電壓下， $V_{th}$  對 Program Time 的變化。例如圖 3-12 左下角紅色的線，本實驗先將元件  $V_{th}$  操作約在 3.2V 的狀態，當作初始的  $V_{th}$ ，依序閘極施加 12V 為期  $1\mu\text{S}$  到  $1\text{mS}$  的 Program Time，並紀錄每次 Program 完的  $V_{th}$ 。可以發現在 Program Voltage 為 12V 時， $V_{th}$  隨著時間的增加而慢慢的增加，不過由於閘極氧化層太厚，Program Voltage 為 12V 時， $V_{th}$  並沒有很大的改變。此外本實驗也將 Program Voltage 依序增加至 22V，如圖 3-12 中左下角的黃線，可發現 Program Time 只要  $1\mu\text{S}$  就可以使  $V_{th}$  從 3.1V 增加至 4.9V，當 Program Time 增加至  $1\text{mS}$  時， $V_{th}$  可以增加至 6.5V。

圖 3-12、GAA 結構的元件對於 FNT 寫入抹除的特性圖。

由圖 3-12 左下角的資料，發現 Program Voltage 與 Program Time 深深的影響元件  $V_{th}$  的變化，越大的 Program Voltage 可以增加載子注入的效率，降低 Program 所需要的時間，即可達到想要的  $V_{th}$  變化量。此外由於元件的閘極氧化層太厚，TEOS/Nitride/TEOS=10-nm/5.5-nm/15-nm，造成需要增加更大的 Program Voltage 才能產生足夠的電場，所以此元件操作電壓必須操作大約 20V 以上。為了解決 P/E 操作電壓過大的問題，本實驗之後的實驗將使閘極氧化層的厚度下降，除了可以提升電場，增加 P/E 效率，也同時可以增加元件的閘極控制能力，提升元件轉換特性，此議題將在之後的章節介紹。

除了針對元件 Program 特性探討，本實驗也以同樣的方法量測元件對於 Erase 的特性表現。首先將元件操作在  $V_{th}=5.9V$ ，並進行調變 Erase Voltage 與 Erase Time 的陣列量測，如圖 3-12 右上部份。本實驗可以發現 Erase 的效率比 Program 還要差，如閘極電壓為-22V 時，Erase Time 要增加 1mS 以上才有微小的  $V_{th}$  變化量，甚至要增加到 1 秒才有 1V 以上的變化量。由於在同樣電場下，電洞的有效質量與 Barrier High( $\Phi_B$ )都大於電子，對於 FNT 有很大的影響，如公式 3-1。因此並不意外 Program 與 Erase 效率會產生如此大的差異，並且根據之前的模擬結果，當閘極電壓為 22V 時，corner region 的電子穿隧電流密度約

$1.17 \times 10^1$  A/cm，而當閘極電壓為-24V 時，corner region 的電洞穿隧電流密度約  $3.88 \times 10^{-6}$  A/cm，兩者相差快  $10^7$  倍，因此可以驗證實際元件難以抹除(Hard to Erase)的現象。

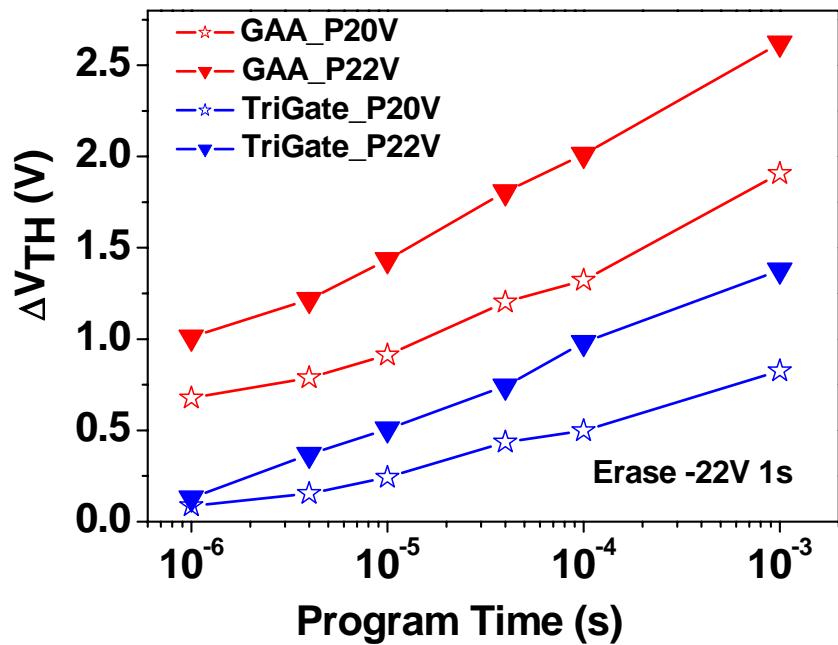

接下來要比較 GAA 結構與 TriGate 結構的 P/E 效率，進而討論 Corner 數量多寡對於 P/E 效率的影響。以下量測，都是使用通道長度為 1um 的八通道奈米線元件。為了強調兩種結構在同樣的操作條件下的  $\Delta V_{th}$  多寡，在此量測的手法與圖 3-12 有些不同。首先在進行 Program 以前，都會進行一次固定條件的 Erase。目的是為了確保上一次 Program 後的電荷不要影響下一次 Program 的正確性，因此 Erase 的條件要足夠大。反之，在進行 Erase 之前，都會進行一次固定條件的 Program。而  $\Delta V_{th}$  就是 P/E 後的  $V_{th}$  減 P/E 前的  $V_{th}$ ，通常 Program 的時候  $\Delta V_{th} > 0$ ，反之 Erase 的時候  $\Delta V_{th} < 0$ 。

如圖 3-13，本實驗在每次 Program 以前，都會進行閘極電壓-22V 為期 1s 的 Erase 動作，以確保上次 Program 後的電荷都能去除，不影響下次 Program 的正確性。此外本實驗調變 Program 的條件，Program Voltage 有 20V 與 22V，而 Program Time 從  $1\mu\text{s}$  調變至 1ms。首先看到圖 3-13 中，GAA 結構在閘極電壓 22V 為期 1ms 的 Program 條件下， $\Delta V_{th}$  約為 2.6V，但是 TriGate 結構的  $\Delta V_{th}$  才只有 1.4V。並且在任何同樣 Program 條件下，GAA 結構的  $\Delta V_{th}$  大約是 TriGate 結構的兩倍多，這可以證明 Corner Effect 對於 Program 效率的重要性。

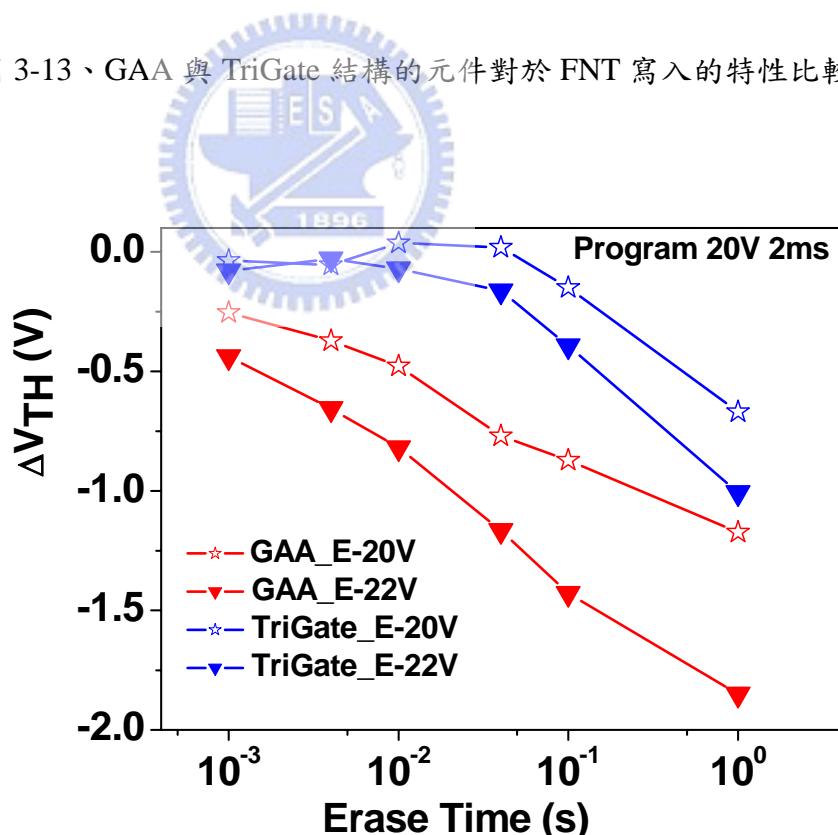

此外本實驗調變 Erase 的條件，Erase Voltage 有 -20V 與 -22V，Erase Time 從 1ms 調變至 1s，而 Program 的條件固定為 20V 為期 2ms，如圖 3-14。圖中任何同樣條件下，GAA 結構的 Erase 效率都高於 TriGate 結構，例如 GAA 結構在閘極電壓 -22V 為期 1s 的條件下， $\Delta V_{th}$  約為 -1.9V，但是 TriGate 結構的  $\Delta V_{th}$  才只有 1V。這也可以證明 Corner Effect 對於 Erase 效率的重要性。

圖 3-13、GAA 與 TriGate 結構的元件對於 FNT 寫入的特性比較圖。

圖 3-14、GAA 與 TriGate 結構的元件對於 FNT 抹除的特性比較圖。

### 3.3.2 電荷儲存時間(Retention Time)量測

電荷儲存時間(Retention Time)是判斷快閃記憶體可靠度優劣的重要參數之一。Retention Time 越長，代表記憶體元件儲存能力越好，元件儲存的電荷經過長時間也不會發生漏電。反之 Retention Time 越短，代表記憶體元件儲存能力很差，元件儲存的電荷易發生漏電，導致讀取資料時的錯誤。通常 Retention Time 的優劣取決於閘極氧化層的品質，假如閘極氧化層太薄或是品質不好都會容易漏電，影響快閃記憶體元件的 Retention Time。

本節將使用 FN Tunneling 的操作方法，量測  $1\mu\text{m}$  GAA Poly-Si 8NWs SONOS-TFT 在 Retention Time 的表現。為了避面 Grain Boundary 對於記憶體特性的影響，本實驗使用八個奈米線通道的元件，使元件變異性降低。

接下來要介紹量測 Retention Time 的手法，首先本實驗將元件操作在室溫(Room Temperature)，然後操作一次 Program 並且紀錄經過 Program 的元件  $V_{th}$  對於時間的變化。接著再操作一次 Erase，同樣的紀錄元件  $V_{th}$  對於時間的變化。利用這兩條線來判斷元件在室溫下的 Retention Time 表現。如圖 3-15，元件操作 Program 的條件為閘極電壓  $20\text{V}$  為期  $2\text{ms}$  的 Stress，而操作 Erase 的條件為閘極電壓  $-22\text{V}$  為期  $1\text{秒}$  的 Stress，本實驗可以發現元件在室溫下的電荷儲存能力很好，Program 後  $1\text{秒}$  的  $V_{th} \approx 5.92\text{V}$ ，而經過  $1\text{萬秒}$  之後的  $V_{th} \approx 5.91\text{V}$ ，Erase 後  $1\text{秒}$  的  $V_{th} \approx 3.99\text{V}$ ，而經過  $1\text{萬秒}$  之後的  $V_{th} \approx 4.09\text{V}$ ，兩者  $V_{th}$  幾乎都沒什麼改變。

此外本實驗將元件升溫至  $85^\circ\text{C}$ ，探討在高溫中元件電荷儲存能力會受到高溫而下降。如圖 3-15，圖中的紅線為升溫至  $85^\circ\text{C}$  的 Retention Time，此時 Program 與 Erase 的操作條件與室溫時的條件相同，本實驗可以發現升溫之後，元件保存電子的能力會下降。例如 Program 後  $1\text{秒}$  的  $V_{th} \approx 5.87\text{V}$ ，而經過  $1\text{萬秒}$  之後的  $V_{th} \approx 5.70\text{V}$ ， $V_{th}$  下降了  $0.17\text{V}$ ，比起室溫下的  $V_{th}$  下降幅度還大。但是 Erase 後  $1\text{秒}$  的  $V_{th} \approx 4.30\text{V}$ ，而經過  $1\text{萬秒}$  之後的  $V_{th} \approx 3.29\text{V}$ ，跟室溫時一樣，其  $V_{th}$  幾乎沒什麼改變。因此可以判定元件在升溫之後，電子漏電的情況會比電洞還嚴重。此外，本實驗推算此元件在室溫下經過十年後，window 還維持約有  $1.7\text{V}$ 。而元件在  $85^\circ\text{C}$  下經過十年後，由於漏電情況較為嚴重，使 window 僅維持約  $0.7\text{V}$ ，雖然不能說 Retention Time 的特性很好，但是還可以接受。

圖 3-15、GAA 結構的元件分別在室溫與 85°C 中 Retention Time 的比較圖。

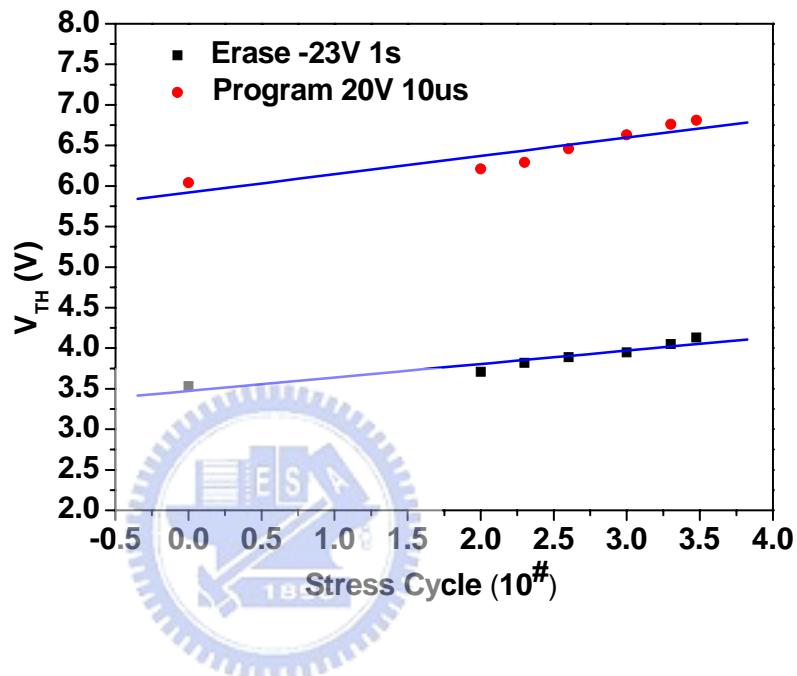

### 3.3.3 耐久度(Endurance)量測

除了 Retention Time 之外，Endurance(耐久度)也是判斷快閃記憶體可靠度優劣的重要參數。然而快閃記憶體的 Endurance 好壞，是由元件可以重複寫入抹除操作的次數來判定。要是元件擁有好的 Endurance，即代表元件經過很多次的 P/E 操作，元件還維持在正常的工作範圍裏面，不會受到多次的 Stress 使元件 P/E 效率下降。反之，差的 Endurance 即代表元件經過多次 P/E 操作後，元件可能發生閘極氧化層劣化、漏電增加、轉換曲線變差、P/E 效率變差...等無法恢復的現象。

本節將使用 FN Tunneling 的操作方法，量測  $1\mu\text{m}$  GAA Poly-Si 8NWs SONOS-TFT 在 Endurance 的表現。為了避面 Grain Boundary 對於記憶體特性影響，本實驗使用八個奈米線通道的元件，使元件變異性降低。

在此本實驗介紹量測手法，首先認定 1 次 Program 與 1 次 Erase 稱為 1 個迴圈(Cycle)，並且紀錄元件經過多次迴圈後的  $V_{th}$  變化。如圖 3-16，操作 8000 次迴圈後的元件，Window 的大小沒有太大改變，可以維持 2.7V 左右。另外可

以發現元件經過多次的 Stress 後，閘極氧化層會困住一些電子，造成  $V_{th}$  有些微變大的現象。雖然在此案例， $V_{th}$  僅變大 0.4V 左右，但是本實驗並不樂見此現象的發生，因為  $V_{th}$  的平移會造成讀取上的誤判。之後可以改善閘極氧化層的品質，如：改變氧化層材料、降低缺陷密度、提升氧化層的耐操度…等，改善元件經過多次 Stress 後  $V_{th}$  平移的現象。

圖 3-16、GAA 結構的元件對於 Endurance 的表現。

### 3-4 降低等效氧化層厚度的記憶體特性表現

在上一節量測實做出來的元件，並且證明 GAA 結構比 TriGate 結構擁有更好的閘極掌控能力，更快速的 Program/Erase 速度。但是由於實驗機台的誤差，導致閘極氧化層太厚，TEOS/Nitride/TEOS=10.5-nm/5.5-nm/15.3nm，所以 P/E 的操作電壓必須提昇至 20V 以上，才有足夠的電場讓記憶體元件有效的寫入或是抹除。因此本實驗重新做了一組元件，目的是為了降低閘極氧化層厚度，同時增加閘極掌控能力和 Program/Erase 的效率。

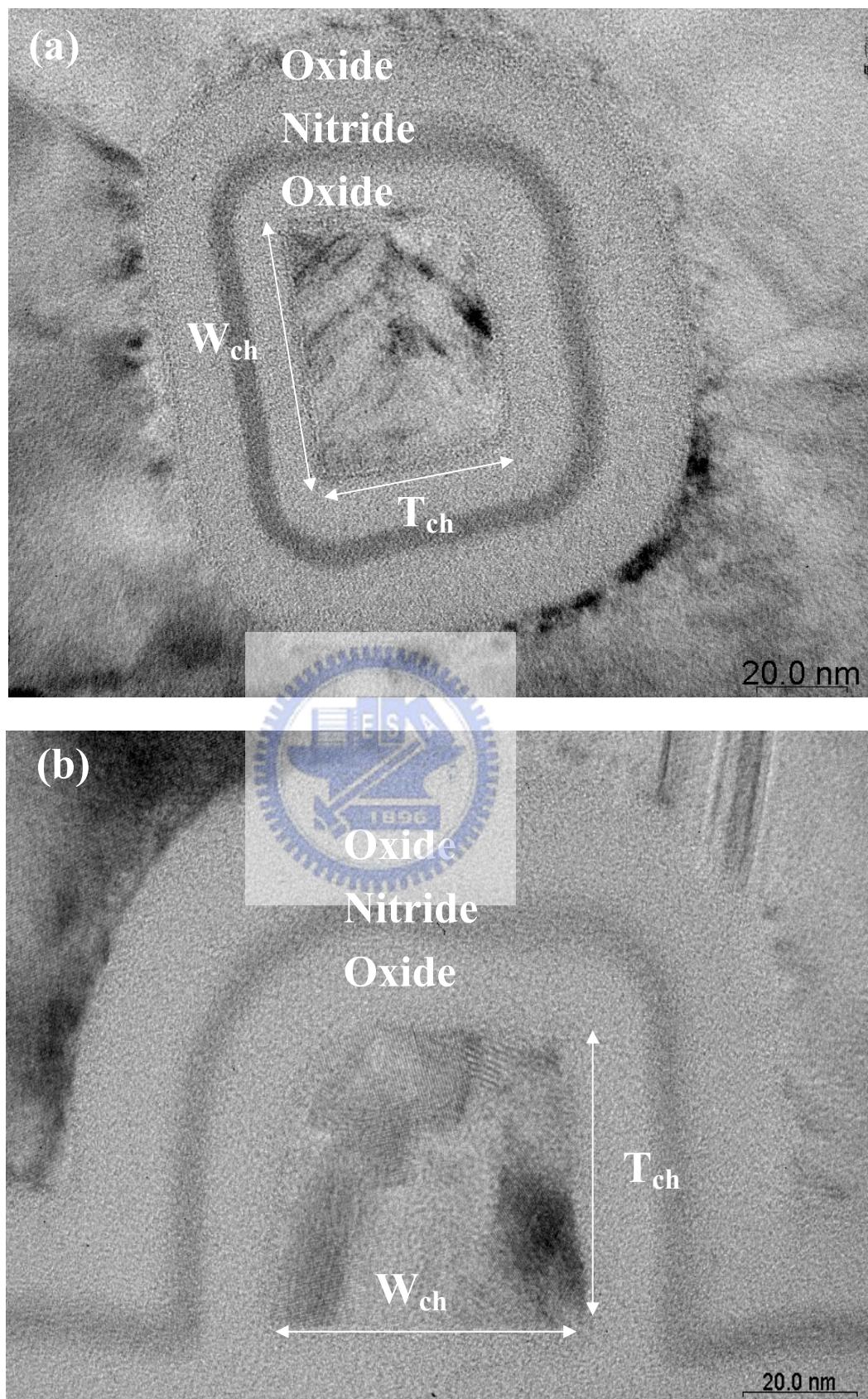

### 3.4.1 降低等效氧化層厚度的元件 TEM 圖

而這組元件同樣利用 Spacer 技術定義元件的奈米線通道，除了閘極氧化層厚度降低之外，其餘製程流程與之前介紹的一模一樣。圖 3-17 為 GAA 結構的 Nanowire Channel 剖面圖，可以清楚看到 NW Channel 被 TEOS/Nitride/TEOS=(5-nm/4.3-nm/7.7-nm)和 N<sup>+</sup> Poly Gate 環繞式均勻地包覆，圖中通道的寬度(W<sub>ch</sub>)約為 40 nm，高度(T<sub>ch</sub>)約為 65nm。

圖 3-17、GAA 結構的 Nanowire Channel 剖面圖，其中 O/N/O=(5-nm/4.3-nm/7.7-nm)，圖中通道的寬度(W<sub>ch</sub>)約為 40 nm，高度(T<sub>ch</sub>)約為 65 nm。

同時比較圖 2-17 與圖 3-17，可以發現兩者的奈米線通道形狀不一樣，前者的通道寬度(W<sub>ch</sub>)約為 62 nm，高度(T<sub>ch</sub>)約為 44nm。然而主要造成 NW 形狀不同的原因，是因為製程機台穩定度問題，導致兩批元件的 Nitride Spacer 寬度與沉積  $\alpha$ -Si 的厚度不一樣。慶幸地兩者通道長度與通道寬度剛好一個約 60-nm 一個約 40-nm，導致有效通道寬度很接近，如圖 2-17 單一通道有效的通道寬度(W<sub>eff</sub>)為 212-nm，而圖 3-17 單一通道有效的通道寬度為 210-nm。所以在此案例中，閘極氧化層的厚度是決定兩者電性差異的主因，反而通道形狀的不同對於電性影響不大。

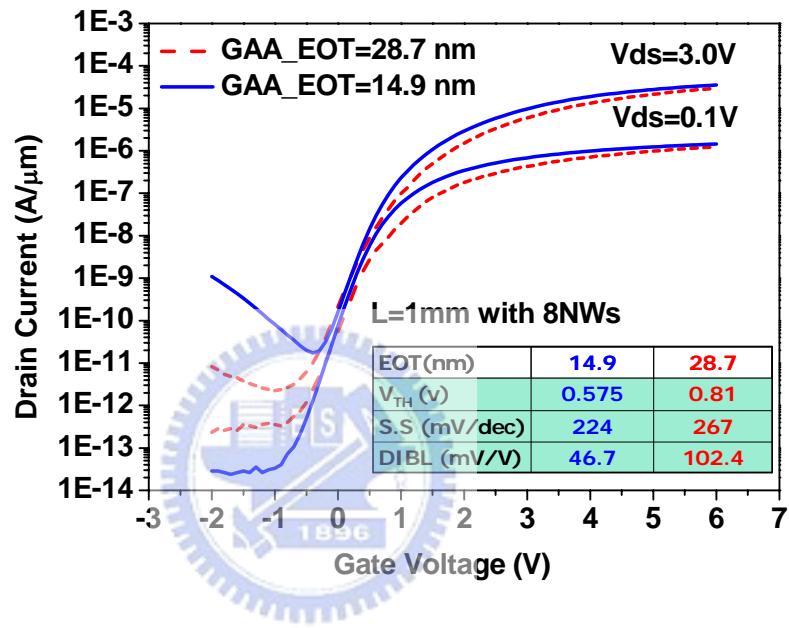

### 3.4.2 薄膜電晶體元件轉換特性

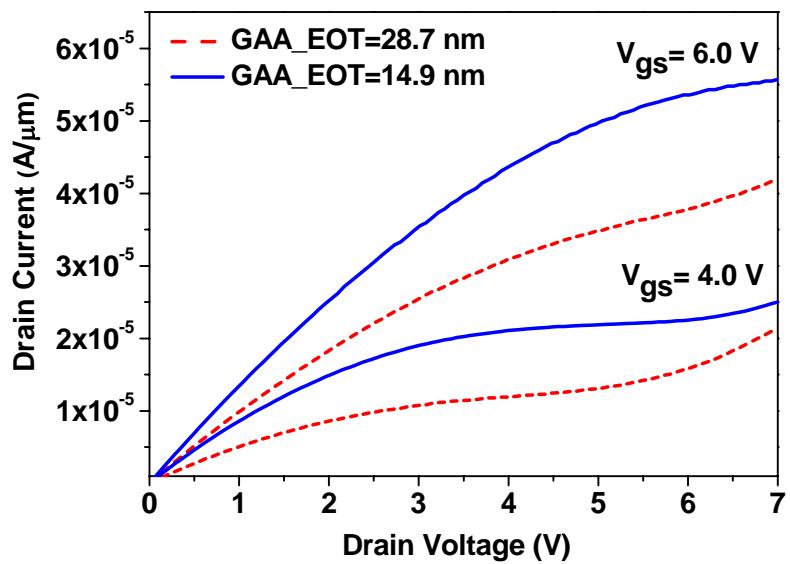

接下來為了探討閘極氧化層厚度對於元件特性的影響，本實驗將圖 2-17 中的閘極氧化層，TEOS/Nitride/TEOS=(10.5-nm/5.5-nm/15.3-nm)，換算成有效

氧化層厚度(EOT)約為 28.7-nm，而圖 3-14 的有效氧化層厚度(EOT)約為 14.9-nm，並量測兩者的  $I_d$ - $V_g$  圖與  $I_d$ - $V_d$  圖，比較兩者對於薄膜電晶體特性的影響，如圖 3-18、圖 3-19。如預期的，由於有效氧化層厚度越薄，閘極掌控能力越好，所以  $EOT=14.9$ -nm 的 GAA 元件擁有較大的驅動電流、較小的 SS 與較小的 DIBL... 等優點。但是也由於  $EOT$  下降，在閘極與汲極產生更大的電場，導致 GIDL 的現象更明顯。

圖 3-18、不同有效氧化層厚度(EOT)的 GAA 結構元件，對於  $I_d$ - $V_g$  的影響。

圖 3-19、不同有效氧化層厚度(EOT)的 GAA 結構元件，對於  $I_d$ - $V_d$  的影響。

### 3.4.3 Program/Erase 特性量測

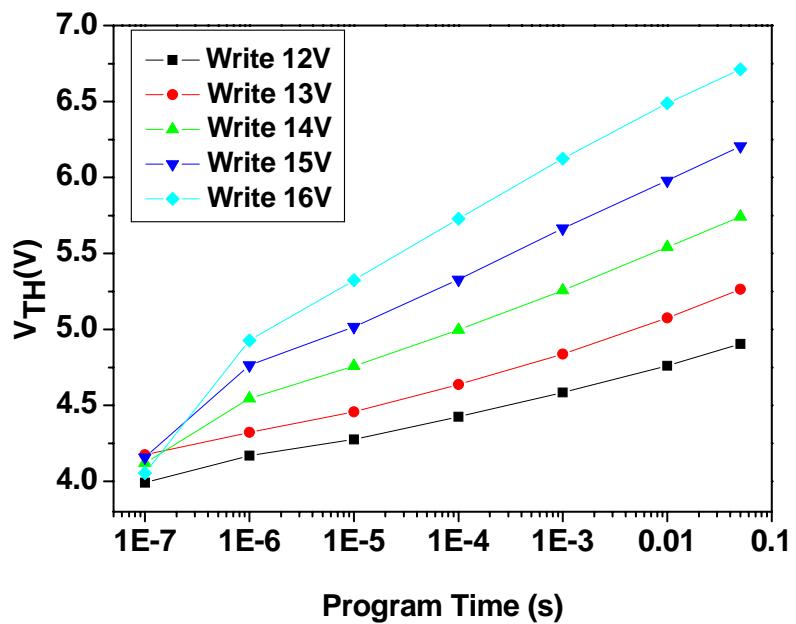

另外，本實驗也針對有效氧化層厚度下降後的元件進行 Program/Erase 效率的量測，如圖 3-20 與圖 3-21。圖 3-20 是說明 Program 的效率，操作的方法如之前所說的，首先把元件初始  $V_{th}$  固定於 4.2V 左右，接下來調變 Program Voltage 與 Program Time，並觀察其  $V_{th}$  的變化。

本實驗可以發現有效氧化層厚度下降後的元件，其穿隧氧化層只有 5-nm，可以增加電場強度並提升 Program 效率，不需要施加 20 幾伏的電壓讓元件產生 Window，例如閘極電壓為 16V 為期  $1 \mu\text{S}$  的 Program，可以使初始  $V_{th}=4.05\text{V}$  增加至 6.12V，產生將近 2V 的 Window。

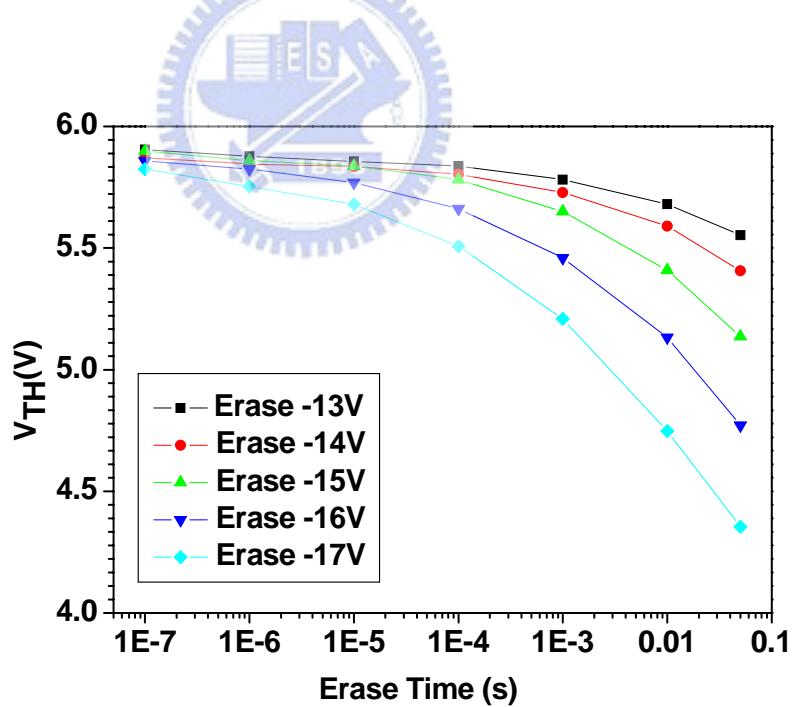

除此之外，本實驗也量測其 Erase 效率，如圖 3-21。同樣由於穿隧氧化層厚度下降的原因，增加電場並提升 Erase 的效率，例如閘極電壓為 -17V 為期 50mS 的 Erase，可以使初始  $V_{th}=5.82\text{V}$  降低至 4.35V，產生將近 1.5V 的 Window。雖然 Erase 的效率還是比 Program 的效率差，但是本實驗降低閘極氧化層整體的厚度，成功的提升 Erase 的效率，除了 Erase 的電壓不需要再施加到 -20 幾伏，並且 Stress 的秒數也不必超過 1 秒，這是本實驗所預期的結果。

圖 3-20、有效氧化層厚度(EOT)下降後的 GAA 元件，Program 效率的量測。

圖 3-21、有效氧化層厚度(EOT)下降後的 GAA 元件，對於 Erase 效率的量測。

### 3.4.4 Endurance 特性量測

上一節本實驗已經針對等效氧化層厚度下降的元件進行 Program 與 Erase 效率的量測，本實驗發現降低 EOT 的元件可以成功地提升 P/E 效率。但是 EOT 降低的元件是否會提升 P/E 效率，反而降低元件的可靠度，是接下來本實驗討論的重點。

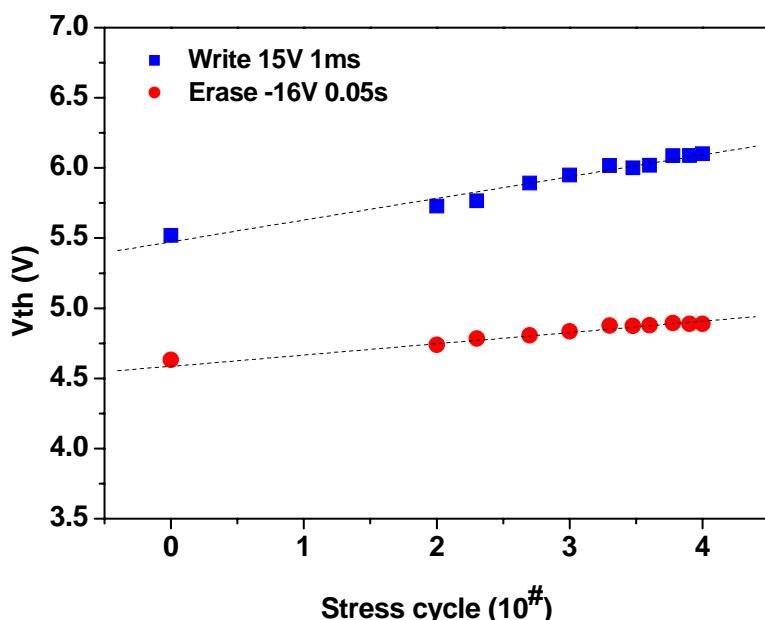

首先本實驗將量測  $1\mu\text{m}$  GAA Poly-Si 20NWs SONOS-TFT 在 Endurance 的表現，而操作手法如同 3-3.3 節所介紹的，只是由於 EOT 下降，所以 Program 與 Erase 操作的條件有所不同，其餘手法都一樣。每次 Program 的閘極電壓為 15V 為期 1mS，而每次 Erase 的閘極電壓為 -16V 為期 0.05S，window 大約控制在 1V 左右，並記錄 10000 次迴圈的  $V_{th}$  變化，如圖 3-22。

可以發現 EOT 下降後的元件可以操作 10000 次迴圈，雖然 window 的大小有隨著 Stress 次數增加而變大，從一開始 Window 約 0.9V 左右，慢慢增加至 1.2V，但是還算在可以接受的範圍。另外本實驗也發現整體的  $V_{th}$  經過 Stress 後有慢慢增加的趨勢，這也是因為閘極氧化層有受到 Stress 而受到破壞，閘極氧化層會困住一些電子，造成  $V_{th}$  有些微變大的現象。

圖 3-22、有效氧化層厚度(EOT)下降後的 GAA 元件，其 Endurance 的表現。

### 3.4.5 Retention Time 特性量測

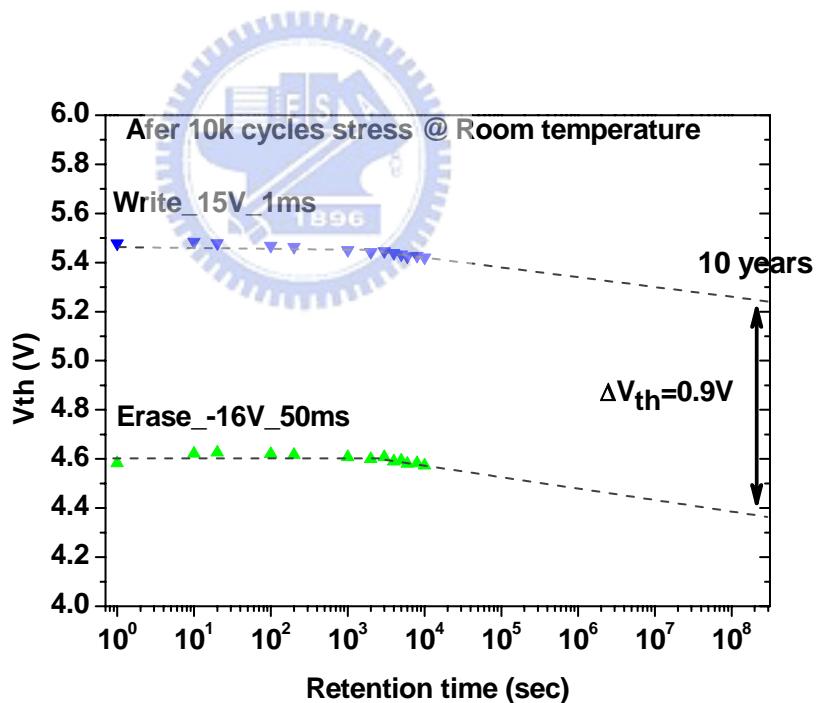

接下來要量測 Retention Time，討論 EOT 降低後的元件是否 Retention Time 會變差。首先本實驗將上一節操作過 10000 次迴圈的元件操作在室溫(Room Temperature)，然後操作一次 Program 並且紀錄經過 Program 的元件  $V_{th}$  對於時間的變化。接著再操作一次 Erase，同樣的紀錄元件  $V_{th}$  對於時間的變化。利用這兩條線來判斷元件在室溫下的 Retention Time 表現。如圖 3-23，元件操作 Program 的條件為閘極電壓 15V 為期 1ms 的 Stress，而操作 Erase 的條件為閘極電壓-16V 為期 50mS 的 Stress，本實驗可以發現元件在室溫下的電荷儲存能力很好，Program 後 1 秒的  $V_{th} \approx 5.48V$ ，而經過 1 萬秒之後的  $V_{th} \approx 5.42V$ ，Erase 後 1 秒的  $V_{th} \approx 4.58V$ ，而經過 1 萬秒之後的  $V_{th} \approx 4.57V$ ，兩者  $V_{th}$  幾乎都沒什麼改變。此外，本實驗推算此元件在室溫下經過十年後，window 還維持約有 0.9V。雖然不能說 Retention Time 的特性很好，但是還可以接受。

圖 3-23、有效氧化層厚度(EOT)下降後的 GAA 元件，經過 10000 次 Stress 後，其在室溫下 Retention Time 的表現。

# 第四章

## 結論與未來展望

### (Summary and Future Work)

本實驗利用側壁 Spacer 及光微影製程技術，成功製作出環繞式閘極(Gate-All-Around)結構的多晶矽奈米線薄膜電晶體，並與 SONOS 記憶體(SONOS-type memory)結合。利用側壁 Spacer 的技術，不須使用先進的微影技術即可簡易地製作出奈米線結構電晶體，可以大量減少微影製程成本。由 TCAD 半導體數值模擬結果顯示，環繞式閘極包覆住方型的奈米線通道時，其四個通道角落會因角落效應(Corner effect)而產生極大的電場。因此環繞式閘極結構不僅可以增加閘極對通道的掌控能力，應用在非揮發性記憶體時，可以利用其包覆方型奈米線通道所產生的角落效應，提升寫入抹除的速度，抑制閘極注入的效率。

本研究實際做出環繞式閘極多晶矽奈米線薄膜電晶體，並與三閘極結構與傳統平面式結構的薄膜電晶體比較。由實驗結果顯示，由於環繞式閘極結構其閘極包覆通道面積大、閘極掌控能力最強，因此不論在電晶體驅動電流、次臨限斜率、汲極引發能位障下降...等電晶體轉換特性，環繞式閘極結構都優越於其他閘極結構。實驗結果顯示，將環繞式閘極結構應用於 SONOS 記憶體，其記憶體寫入抹除的效率上也優越於三閘極結構的 SONOS 記憶體，可以證明 Corner Effect 對於記憶體寫入抹除效率上的影響性。最後本實驗量測環繞式閘極結構的 SONOS 記憶體，顯示其擁有優越的 Retention Time 與 Endurance，並且期盼此元件可以應用在未來 System On Panel(SOP)的技術。

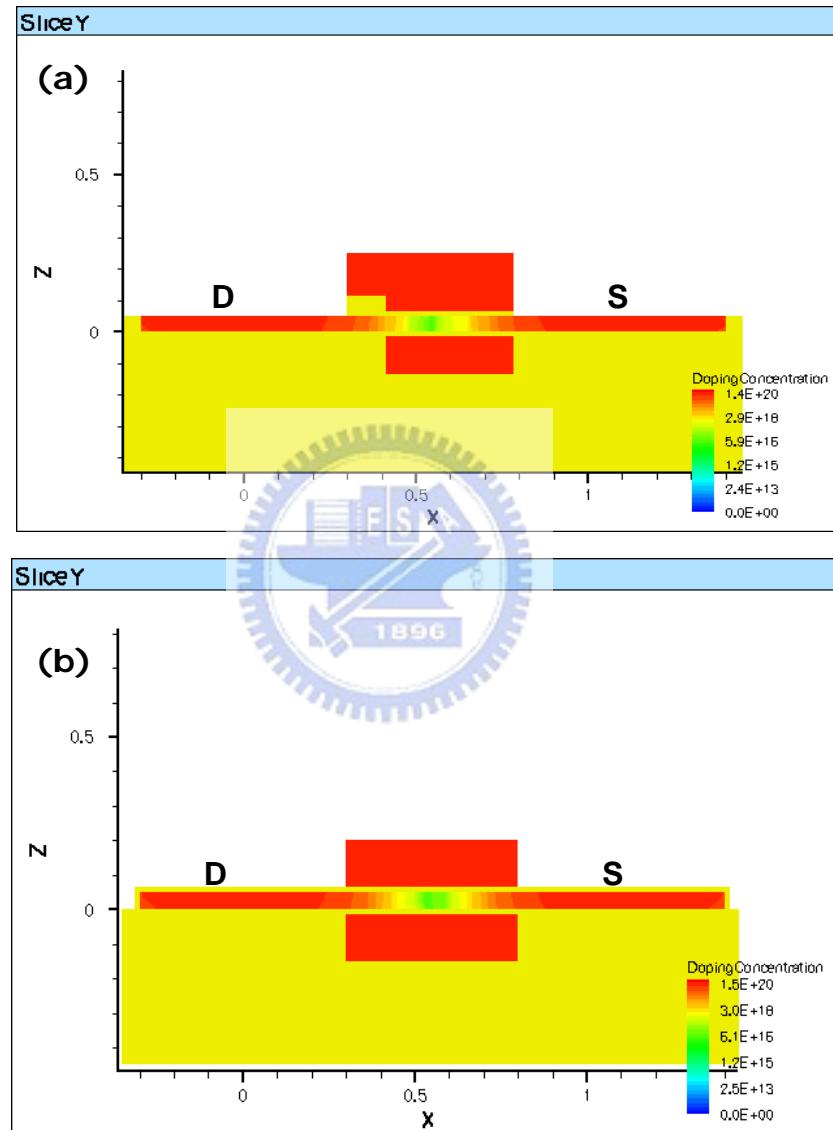

本實驗成功地利用環繞式閘極結構提昇薄膜電晶體的特性，但由於環繞式閘極結構包覆通道的面積增加，其閘極引發漏電流(GIDL)也很明顯。抑制 GIDL 的製程技術有很多種，最常見的就是輕汲極參雜(LDD)，在此將介紹一種新穎的非對稱閘極結構並且應用於環繞式閘極，雖然此論文並無使用此製程技術，但希望在未來此新穎的概念能實際應用在元件上。

非對稱閘極結構的概念其實很簡單，就是一個環繞式閘極結構的電晶體，其汲極端使用三閘極結構，並且搭配較厚的閘極氧化層，目的是降低汲極端的電場，使 GIDL 的現象降低。雖然增加汲極端的氧化層厚度會降低驅動電流，但是只要元件設計得當，就可以損失很少的驅動電流，卻可以大大的降低 GIDL 的現象。以下將用 TCAD 模擬非對

稱結構的電晶體電性，探討此結構是否可以降低閘極引發的漏電流。首先介紹非對稱結構元件的設計，其中通道高與寬各為 50-nm，閘極控制的通道長度為 500-nm，閘極氧化層厚度為 15-nm，然而汲極有 100-nm 區域為三閘極結構，其閘極氧化層厚度為 65-nm，閘極與源汲極為  $N^+$  高摻雜區域約為  $1 \times 10^{20} (1/cm^3)$ ，其通道剖面圖如圖 4-1(a)所示。另外環繞式閘極結構的閘極氧化層都為 15-nm，如圖 4-1(b)。

圖 4-1 元件結構的結構示意圖，並對照右下角的參雜濃度表，(a)非對稱閘極結構，(b) 環繞式閘極結構。

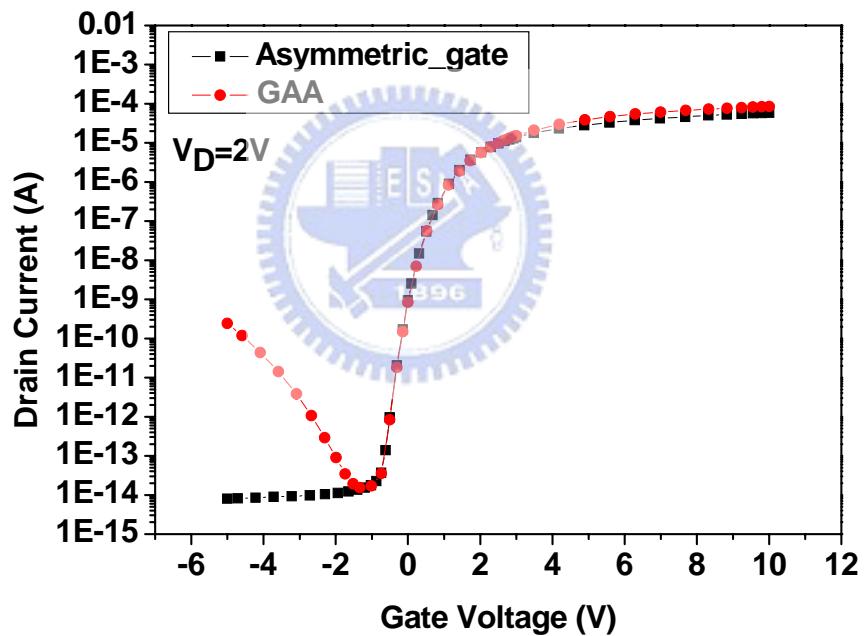

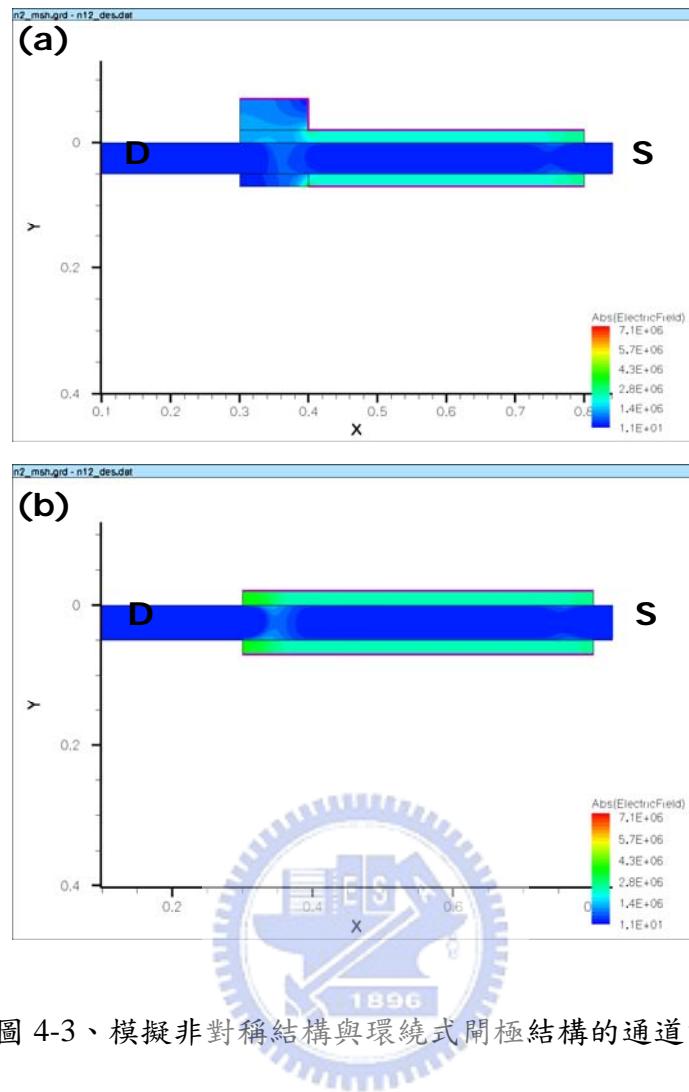

接著模擬這兩種結構在  $I_d$ - $V_g$  圖的表現，根據模擬結果顯示，使用非對稱結構時，雖然降低了驅動電流，但在閘極電壓為-5V 的時候，非對稱結構可以降低漏電流近 5 個 order，明顯地抑制 GIDL 的現象，如圖 4-2。為了證明非對稱結構可以降低汲極端的電場，本實驗將兩種元件操作在元件關閉的狀態(Gate Voltage=-5V，Drain Voltage=2V，Source Voltage=0V)，探討兩者的通道電場大小，如圖 4-3，本實驗可以發現兩者在汲極端的電場明顯的不同，非對稱結構明顯降低了汲極端電場。另外將通道表面的電場絕對值取出來做比較，使用非對稱結構後，可以將表面電場原本約 1.1 MV/cm 下降至 0.7 MV/cm，如圖 4-4。經由以上的模擬可以證明非對稱結構可以有效的降低汲極端的電場，因而降低閘極引發的漏電流效應，但是這只是簡略性的模擬，實際上製作元件時，如何有效的降低漏電流卻不會損失太多的驅動電流是一個重要的設計議題。

圖 4-2、模擬非對稱結構與環繞式閘極結構的  $I_d$ - $V_g$  曲線圖。

圖 4-3、模擬非對稱結構與環繞式閘極結構的通道電場圖。

圖 4-4、模擬非對稱結構與 GAA 結構通道表面電場圖。

另外此論文中有實際做出環繞式閘極與三閘極結構，並且比較兩者對於元件的影響。不論是模擬結果或是實際量測的結果顯示，環繞式閘極都是優越於三閘極結構，其中一個主要原因是環繞式閘極包覆住方型奈米線通道時，四個角落所產生的角落效應，優越於三閘極結構只會在兩個角落產生角落效應，因此電性有明顯的差異。但是假如是環繞式閘極與  $\Omega$  閘極比較，環繞式閘極會包覆四個通道表面與四個通道角落，而  $\Omega$  閘極會包覆三個通道表面與四個通道角落，兩者同樣是包覆四個通道角落，因此猜測兩者少了角落效應的差異，兩者電性應該會非常的接近，因此本實驗實際製作出兩種結構的元件，並且將介紹初步的量測比較結果。

首先是兩者元件的 TEM 圖，如圖 4-5，其中圖 4-5(a)為  $\Omega$  閘極的結構，而圖 4-5(b)為環繞式閘極的結構，兩者通道高度約為 65-nm，通道寬度為 40-nm，其堆疊式閘極氧化層為(TEOS=5-nm/Nitride=4.3-nm/TEOS=6.7-nm)。接著針對通道長度為 800-nm 的兩種結構元件進行  $I_d$ - $V_g$  的比較，如圖 4-6，並在圖內顯示兩者的  $V_{th}$ 、DIBL 與 SS。可以發現環繞式閘極結構在  $I_d$ - $V_g$  的表現上雖然優越於  $\Omega$  閘極的結構，但是兩者差異很小，甚至幾乎沒有。這也如本實驗預期的一樣，少了角落效應的差異，其元件特性上差異會很相近。但在這裡只是初步的比較，詳細的探討與研究兩者結構對於元件的影響是本實驗往後的目標，包括兩者在電晶體上的轉換特性比較、製程的良率(Yield)上的比較、電性變異性(Fluctuation)的比較、記憶體特性上的比較...等議題。

圖 4-5、 $\Omega$  閘極結構與 GAA 結構的奈米線通道 TEM 圖。

圖 4-6、 $\Omega$  閘極結構與 GAA 結構的  $I_d$ - $V_g$  比較圖。

除了以上兩個本實驗提出的目標，由於目前本實驗只實做出單位元的快閃記憶體元件，未來可以朝著多位元的快閃記憶體方面進行，或者氧化層更換高介電係數(High- $\kappa$ )材料與金屬閘極(Metal Gate)配合，可以增加閘極掌控能力，或者利用金屬奈米點(Nano-dot)埋藏在捕捉電荷層中，增加儲存的電荷量。目前有許多團隊都投入環繞式閘極結構的相關研究，目的都是想利用其優越的閘極掌控能力，抑制短通道效應，但是此三維結構與實際產品結合還是有許多議題必須克服，但是相信未來環繞式閘極結構可以解決微小化的問題。

## 参考文献(References)

- [1] T. Aoyama, K. Ogawa, Y. Mochizuki, and N. Konishi, "Inverse staggered poly-Si and amorphous Si double structure TFT's for LCD panels with peripheral driver circuits integration," *IEEE Trans. Electron Devices*, vol. 43, no. 5, pp. 701-705, May 1996.

- [2] C. W. Lin, L. J. Cheng, Y. L. Lu, Y. S. Lee, and H. C. Cheng, "High-performance low-temperature poly-Si TFTs crystallized by excimer laser irradiation with recessed-channel structure," *IEEE Electron Device Lett.*, vol. 22, no. 6, pp. 269-271, Jun 2001.

- [3] S. W. Lee and S. K. Joo, "Low temperature poly-Si thin-film transistor fabrication by metal-induced lateral crystallization," *IEEE Electron Device Lett.*, vol. 17, no. 4, pp. 160-162, Apr 1996.

- [4] C. J. Su, H. C. Lin, and T. Y. Huang, "High-performance TFTs with Si nanowire channels enhanced by metal-induced lateral crystallization," *IEEE Electron Device Lett.*, vol. 27, no. 7, pp. 582-584, Jul 2006.

- [5] H. C. Lin, M. H. Lee, C. J. Su, and S. W. Shen, "Fabrication and characterization of nanowire transistors with solid-phase crystallized poly-Si channels," *IEEE Trans. Electron Devices*, vol. 53, no. 10, pp. 2471-2477, Oct 2006.

- [6] M. K. Hatalis, and D. W. Greve, "Large grain polycrystalline silicon by low-temperature annealing of low-pressure chemical vapor deposited amorphous silicon films," *J. Appl. Phys.*, vol. 63, no. 7, pp. 2260-2266, Apr 1988.

- [7] Z. B. Xiong, H. T. Liu, C. X. Zhu, and J. K. O. Sin, "A new polysilicon CMOS self-aligned double-gate TFT technology," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2629-2633, Dec 2005.

- [8] T. Serikawa, S. Shirai, A. Okamoto, and S. Suyama, "Low-temperature fabrication of high-mobility poly-Si TFT's for large-area LCD's," *IEEE Trans. Electron Devices*, vol. 36, no. 9, pp. 1929-1933, Sep 1989.

- [9] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S. H. Lo, G. A. SaiHalasz, R. G. Viswanathan, H. J. C. Wann, S. J. Wind, and H. S. Wong, "CMOS scaling into the nanometer regime," *Proc. IEEE*, vol. 85, no. 4, pp. 486-504, Apr 1997.

- [10] D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur, and H. S. P. Wong, "Device scaling limits of Si MOSFETs and their application dependencies," *Proc. IEEE*, vol. 89, no. 3, pp. 259-288, Mar 2001.

- [11] D. Hisamoto, W. C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.

- J. King, J. Bokor, and C. M. Hu, "FinFET - A self-aligned double-gate MOSFET scalable to 20 nm," *IEEE Trans. Electron Devices*, vol. 47, no. 12, pp. 2320-2325, Dec 2000.

- [12] T. Saito, T. Saraya, T. Inukai, H. Majima, T. Nagumo, and T. Hiramoto, "Suppression of short channel effect in triangular parallel wire channel MOSFETs," *IEICE Trans. Electron.*, vol. E85C, no. 5, pp. 1073-1078, May 2002.

- [13] J. Y. Song, W. Y. Choi, J. H. Park, J. D. Lee, and B. G. Park, "Design optimization of gate-all-around (GAA) MOSFETs," in *10th Silicon Nanoelectronics Workshop*, Kyoto, JAPAN, 2005, pp. 186-191.

- [14] N. Singh, A. Agarwal, L. K. Bera, T. Y. Liow, R. Yang, S. C. Rustagi, C. H. Tung, R. Kumar, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, "High-performance fully depleted silicon-nanowire (diameter  $\leq$  5 nm) gate-all-around CMOS devices," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 383-386, May 2006.

- [15] A. Burenkov and J. Lorenz, "Corner effect in double and triple gate FinFETs," in *33rd European Solid-State Device Research Conference*, Estoril, Portugal, 2003, pp. 135-138.

- [16] Y. K. Choi, D. Ha, T. J. King, and J. Bokor, "Investigation of gate-induced drain leakage (GIDL) current in thin body devices: Single-gate ultra-thin body, symmetrical double-gate, and asymmetrical double-gate MOSFETs," in *International Conference on Solid State Devices and Materials (SSDM 2002)*, Nagoya, Japan, 2002, pp. 2073-2076.

- [17] S. Miyamoto, S. Maegawa, S. Maeda, T. Ipposhi, H. Kuriyama, T. Nishimura, and N. Tsubouchi, "Effect of LDD structure and channel poly-Si thinning on a gate-all-around TFT (GAT) for SRAM's," *IEEE Trans. Electron Devices*, vol. 46, no. 8, pp. 1693-1698, Aug 1999.

- [18] Z. B. Xiong, H. T. Liu, C. X. Zhu, and J. K. O. Sin, "A novel self-aligned offset-gated polysilicon TFT using high-kappa, dielectric spacers," *IEEE Electron Device Lett.*, vol. 25, no. 4, pp. 194-195, Apr 2004.

- [19] S. Seki, O. Kogure, and B. Tsujiyama, "Leakage current characteristics of offset-gate-structure polycrystalline-silicon MOSFET's," *IEEE Electron Device Lett.*, vol. 8, no. 9, pp. 434-436, Sep 1987.

- [20] S. Cristoloveanu, "Future trends in SOI technologies," in *10th Seoul International Symposium on the Physics of Semiconductors and Applications*, Cheju, South Korea, 2000, pp. S52-S55.

- [21] J. De Blauwe, "Nanocrystal nonvolatile memory devices," *IEEE Trans. Nanotechnol.*, vol. 1, no. 1, pp. 72-77, Mar 2002.

- [22] M. L. Ostraat, J. W. De Blauwe, M. L. Green, L. D. Bell, M. L. Brongersma, J. Casperson, R. C. Flagan, and H. A. Atwater, "Synthesis and characterization of aerosol silicon nanocrystal nonvolatile floating-gate memory devices," *Applied Physics Letters*, vol. 79, no. 3, pp. 433-435, Jul 2001.

- [23] C. H. Lee, S. H. Hur, Y. C. Shin, J. H. Choi, D. G. Park, and K. Kim, "Charge-trapping device structure of SiO<sub>2</sub>/SiN/high-k dielectric Al<sub>2</sub>O<sub>3</sub> for high-density flash memory," *Applied Physics Letters*, vol. 86, no. 152005.

- [24] V. A. Gritsenko, K. A. Nasyrov, Y. N. Novikov, A. L. Aseev, S. Y. Yoon, J. W. Lee, E. H. Lee, and C. W. Kim, "A new low voltage fast SONOS memory with high-k dielectric," in *12th Workshop on Dielectrics in Microelectronics (WoDiM 2002)*, Grenoble, France, 2002, pp. 1651-1656.

- [25] M. H. White, D. A. Adams, and J. K. Bu, "On the go with SONOS," *IEEE Circuits Devices*, vol. 16, no. 4, pp. 22-31, Jul 2000.

- [26] Y. N. Tan, W. K. Chim, W. K. Choi, M. S. Joo, T. H. Ng, B. J. Cho, and ieee, "High-K HfAlO charge trapping layer in SONOS-type nonvolatile memory device for high speed operation," in *50th IEEE International Electron Devices Meeting*, San Francisco, CA, 2004, pp. 889-892.

- [27] Y. H. Shih, H. T. Lue, K. Y. Hsieh, R. Liu, and C. Y. Lu, "A novel 2-bit/cell nitride storage flash memory with greater than 1M P/E-cycle endurance," *Ieee International Electron Devices Meeting 2004, Technical Digest*, pp. 881-884, 2004.

- [28] J. T. Park and J. P. Colinge, "Multiple-gate SOI MOSFETs: Device design guidelines," *IEEE Trans. Electron Devices*, vol. 49, no. 12, pp. 2222-2229, Dec 2002.

- [29] J. T. Sheu, P. C. Huang, T. S. Sheu, C. C. Chen, and L. A. Chen, "Characteristics of Gate-All-Around Twin Poly-Si Nanowire Thin-Film Transistors," *IEEE Electron Device Lett.*, vol. 30, no. 2, pp. 139-141, Feb 2009.

- [30] S. C. Chen, T. C. Chang, P. T. Liu, Y. C. Wu, P. S. Lin, B. H. Tseng, J. H. Shy, S. M. Sze, C. Y. Chang, and C. H. Lien, "A novel nanowire channel poly-Si TFT functioning as transistor and nonvolatile SONOS memory," *IEEE Electron Device Lett.*, vol. 28, no. 9, pp. 809-811, Sep 2007.

- [31] W. Shockley and W. T. Read, "Statistics of the Recombinations of Holes and Electrons," *Physical Review*, vol. 87, no. 5, p. 835, April 1952.

- [32] A. Schenk, "Rigorous theory and simplified model of the band-to-band tunneling in silicon," *Solid-State Electron.*, vol. 36, no. 1, pp. 19-34, Jan 1993.

- [33] Y.-K. Choi, T.-J. King, and C. Hu, "Spacer FinFET: nanoscale double-gate CMOS technology for the terabit era," *Solid-State Electron.*, vol. 46, no. 10, pp. 1595-1601, October 2002.

- [34] H. H. Hsu, H. C. Lin, L. Chan, and T. Y. Huang, "Threshold-Voltage Fluctuation of Double-Gated Poly-Si Nanowire Field-Effect Transistor," *IEEE Electron Device Lett.*, vol. 30, no. 3, pp. 243-245, Mar 2009.

- [35] A. Bolognesi, M. Berliocchi, M. Manenti, A. Di Carlo, P. Lugli, K. Lmimouni, and C. Dufour, "Effects of grain boundaries, field-dependent mobility, and interface trap states on the electrical characteristics of pentacene TFT," *IEEE Trans. Electron Devices*, vol. 51, no. 12, pp. 1997-2003, DEC 2004.

- [36] H. C. Cheng, F. S. Wang, and C. Y. Huang, "Effects of NH<sub>3</sub> plasma passivation on N-channel polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 44, no. 1, pp. 64-68, Jan 1997.

- [37] S. Uchikoga and N. Ibaraki, "Low temperature poly-Si TFT-LCD by excimer laser anneal," in *3rd Symposium O on Thin Film Materials for Large Area Electronics of the E-MRS 2000 Spring Meeting*, Strasbourg, France, 2000, pp. 19-24.

- [38] S. Tam, P. K. Ko, and C. M. Hu, "Lucky-electron model of channel hot-electron injection in MOSFET's," *IEEE Trans. Electron Devices*, vol. 31, no. 9, pp. 1116-1125, SEP 1984.

- [39] S. Yen-Hao, L. Hang-Ting, H. Kuang-Yeu, L. Rich, and L. Chih-Yuan, "A novel 2-bit/cell nitride storage flash memory with greater than 1M P/E-cycle endurance," in *2004 International Electron Devices Meeting*, San Francisco, CA, 2005, pp. 881-884.

- [40] D. K. Wu, R. Huang, P. F. Wang, P. R. Tang, and Y. Y. Wang, "A low-voltage flash memory cell utilizing the gate-injection program/erase method with a recessed channel structure," *Semicond. Sci. Technol.*, vol. 23, no. 7, p. 5, Jul 2008.