國 立 交 通 大 學

電控工程研究所

碩 士 論 文

**可程式化車用功率積體電路**

**Programmable Power Driving Circuit for**

**Automobile Applications**

研 究 生：盧泓瑋

指 導 教 授：蘇朝琴 陳鴻祺 教授

中 華 民 國 九 十 九 年 十 一 月

# 可程式化車用功率積體電路

## Programmable Power Driving Circuit for Automobile Applications

研究 生：盧泓瑋

Student : Hung-Wei Lu

指導 教授：蘇朝琴 教授

Advisor : Chau-Chin Su

陳鴻祺 教授

Hung-Chi Chen

Submitted to Institute of Electrical Control Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Electrical Control Engineering

November 2010

Hsinchu, Taiwan, Republic of China

中 華 民 國 九 十 九 年 十 一 月

# 可程式化車用功率積體電路

研究生：盧泓瑋

指導教授：蘇朝琴 教授

陳鴻祺 教授

國立交通大學電控工程研究所

## 摘要

本論文提出一個使用於汽車上之泛用型功率驅動電路，它可以根據指令提供多樣化的電壓或電流的驅動曲線 (Voltage/Current Driving Profile)。主要的目的在於以單一電壓 (12V) 提供多樣化汽車電器所需之驅動功率。初步以提供2A 的電流為目標驗證可行性。本論文的特色在於可程式的功率積體電路，根據所接受的指令，產生所需要的驅動信號，來驅動被控制的元件。舉凡車用燈具所需的閃爍頻率或亮暗程度、馬達驅動的電流大小與驅動曲線、或電子組件的直流電壓，均可以由此一電路提供。如此則能大大的簡化所需之零件，並降低零件的成本。本論文所產出的可程式功率驅動積體電路預計可以達到以下之輸出，一、電壓可程式的直流電源以提供電子組件電源，二、頻率、電壓可程式的交流信號以控制燈具的閃爍與亮度，三、功率曲線可程式之馬達驅動電流以驅動馬達。俱備了以上三種功能，多數的汽車電器裝備將可以由此一積體電路驅動。

關鍵字：功率積體電路、系統晶片、車用電子、馬達驅動、直流電壓轉換

# Programmable Power Driving Circuit For Automobile Applications

Student: Hung-Wei Lu

Advisor: Chau-Chin Su

Hung-Chi Chen

Institute of Electrical Control Engineering

National Chiao Tung University

## Abstract

This thesis proposes an universal power driving circuit for automobile applications. It can produce the desired voltage or current driving profile, according to the command. The main purpose is to provide multiple driving needs from a single DC power source. The tentative goal is to provide 2A of driving current for the feasibility study purposes. The distinguishing feature is the programmability. According to the command, it can produce the driving signal to driver the driven devices. Not only the flickering frequency and brightness of the light but also the motor driving power profile can be controlled by the circuit. As a result, the cost of the device can be reduced significantly. The proposed programmable power driving circuit is able to produce the following outputs. The first one is the voltage programmable DC power source for electronic equipment, The second one is frequency and voltage programmable for light control. The third one is the power driving profile programmable motor driver. With the above three functions, the majority of the electrical parts in an automobile can be driven by this circuitry.

Keyword: Power IC, SoC, Automobile Electronics, Motor Driver, DC Converter

# 誌謝

在這兩年多的研究生活首先要感謝的是我的指導教授，在一開始研究還沒方向時總是給了我們許多的建議及指導，讓我們能在錯誤的研究中找到正確的方向，也常常告訴我們研究必須了解它背後的物理意義，不要只是一昧的靠模擬來研究，使我們在研究上獲益良多。

在研究上要感謝仁乾學長及陳契霖學長在 Power IC 上面給了我許多的指導以及建議，讓我在研究上所遇到的問題能迎刃而解。這邊也感謝庭佑學長及長官在硬體方面給了我們許多協助，使我們能專心的研究。也感謝于昇、鈞藝、哲瑋、博祥、群育、修明及盈杰學長再這兩年的研究生活一起討論學術一起成長。最後要感謝 918 lab 的學弟軍團：璟伊、澤勝、昶志、弘宇、順裕、佳容、Mark、阿 Mon、嘉哲、蔡倫、可謙在研究之時往往是枯燥的，但是有你們的陪伴使 918 lab 更加溫馨歡樂，雖然現在即將畢業理當興奮期待，但要離開你們卻非常不捨，希望將來大家畢業邁入工作，為自己的人生打拼之時，都能闖出自己的一片天空。

最後則是感謝我的家人，媽媽、爸爸、奶奶、姐姐及妹妹，雖然父親在我高中時過世，但我在他身上學到了負責兩個字，對家人對事業對自己。而母親在父親過世之後則是負起家裡得重擔，使我們三個孩子能在學業上專心的學習。在這兩年的研究生活中母親總是無時無刻的關心我，讓我在研究時能提起精神。也感謝奶奶、姐姐及妹妹能在背後支持我。

# 目錄

|                                             |          |

|---------------------------------------------|----------|

| 摘要 .....                                    | i        |

| Abstract .....                              | ii       |

| 誌謝 .....                                    | iii      |

| 目錄 .....                                    | iv       |

| 圖目錄 .....                                   | vii      |

| 表目錄 .....                                   | x        |

| <b>第一章 .....</b>                            | <b>1</b> |

| <b>緒論 .....</b>                             | <b>1</b> |

| 1.1 簡介 .....                                | 1        |

| 1.2 研究動機 .....                              | 2        |

| 1.3 論文結構 .....                              | 5        |

| <b>第二章 .....</b>                            | <b>6</b> |

| <b>數位控制直流-直流切換式電源供應、LED 及直流馬達基本原理 .....</b> | <b>6</b> |

| 2.1 直流-直流降壓電路基本原理 .....                     | 6        |

| 2.1.1 類比直流-直流降壓電路操作原理 .....                 | 7        |

| 2.1.2 輸出濾波器設計 .....                         | 9        |

| 2.1.3 數位直流-直流降壓電路基本架構及操作原理 .....            | 11       |

| 2.1.4 類比數位轉換器 .....                         | 12       |

| 2.1.5 數位正比積分微分控制器 (PID) 補償器 .....           | 14       |

| 2.1.6 數位脈波寬度調變(DPWM) .....                  | 16       |

|                                                      |           |

|------------------------------------------------------|-----------|

| 2.2 LED 及馬達基本操作原理 .....                              | 22        |

| <b>第三章 .....</b>                                     | <b>25</b> |

| <b>可程式車用功率積體電路設計.....25</b>                          |           |

| 3.1 驅動晶片系統設計及規格制定 .....                              | 25        |

| 3.1.1 可程式車用功率積體電路系統設計 .....                          | 25        |

| 3.1.2 規格制定 .....                                     | 27        |

| 3.2 $\Sigma\Delta$ 數位脈波寬度調變電路.....                   | 29        |

| 3.2.1 數位脈波寬度調變電路基於雜訊整形概念 .....                       | 29        |

| 3.2.2 一階 $\Sigma\Delta$ 雜訊整型數位脈波寬度調變電路 .....         | 32        |

| 3.2.3 二階 $\Sigma\Delta$ 雜訊整型數位脈波寬度調變電路 .....         | 40        |

| 3.3 誤差類比數位轉換器 .....                                  | 43        |

| 3.4 數位正比積分微分補償器 .....                                | 45        |

| <b>第四章 .....</b>                                     | <b>51</b> |

| <b>模擬結果 .....</b>                                    |           |

| 4.1 計數模式數位脈波寬度調變數位降壓電路模擬驗證 .....                     | 51        |

| 4.2 二階 $\Sigma\Delta$ 雜訊整形迴路數位脈波寬度調變數位降壓電路模擬驗證 ..... | 55        |

| <b>第五章 .....</b>                                     | <b>58</b> |

| <b>FPGA 驗證結果 .....</b>                               |           |

| 5.1 車用電子測試環境及硬體架構 .....                              | 58        |

| 5.2 直流-直流降壓電路驗證.....                                 | 61        |

| 5.3 馬達及 LED 驗證 .....                                 | 68        |

| <b>第六章 .....</b>                                     | <b>71</b> |

|            |    |

|------------|----|

| 結論 .....   | 71 |

| 參考文獻 ..... | 72 |

# 圖 目 錄

|                                                      |    |

|------------------------------------------------------|----|

| 圖 1. 汽車電路導線佈局示意圖 .....                               | 2  |

| 圖 2. 電源線通訊汽車電路導線佈局示意圖 .....                          | 3  |

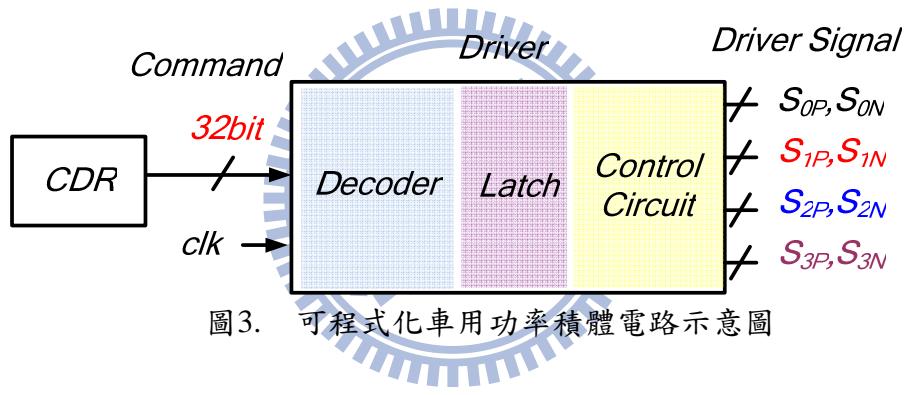

| 圖 3. 可程式化車用功率積體電路示意圖 .....                           | 3  |

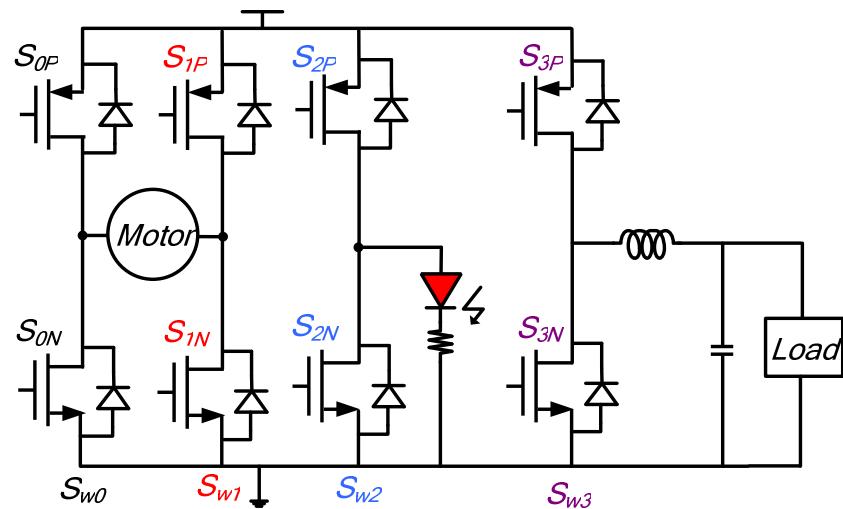

| 圖 4. 四組開關推動馬達、LED 及降壓電路 .....                        | 3  |

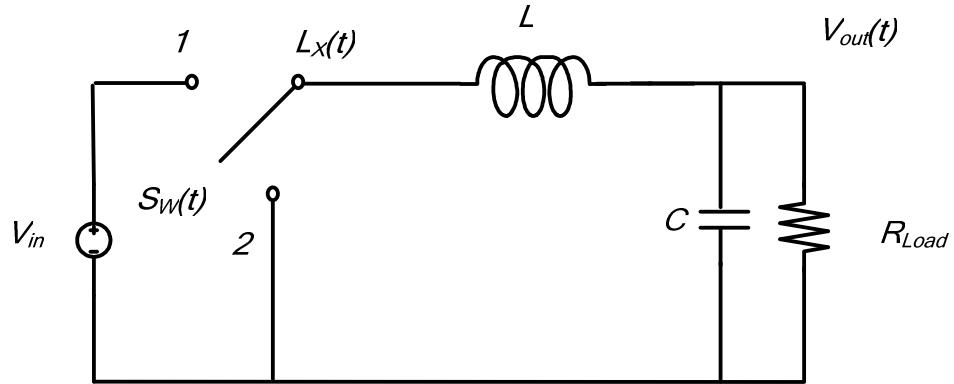

| 圖 5. 直流-直流降壓電路基本架構[1] .....                          | 7  |

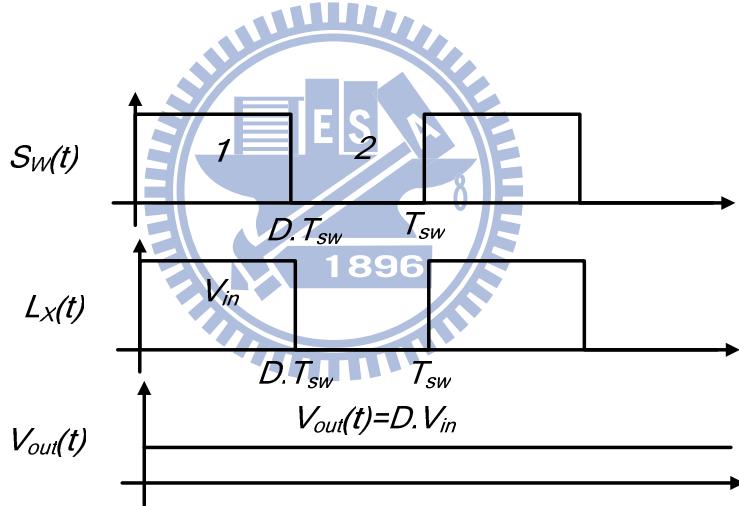

| 圖 6. $S_w(t)$ , $L_x(t)$ 及 $V_{out}(t)$ 波形圖[1] ..... | 7  |

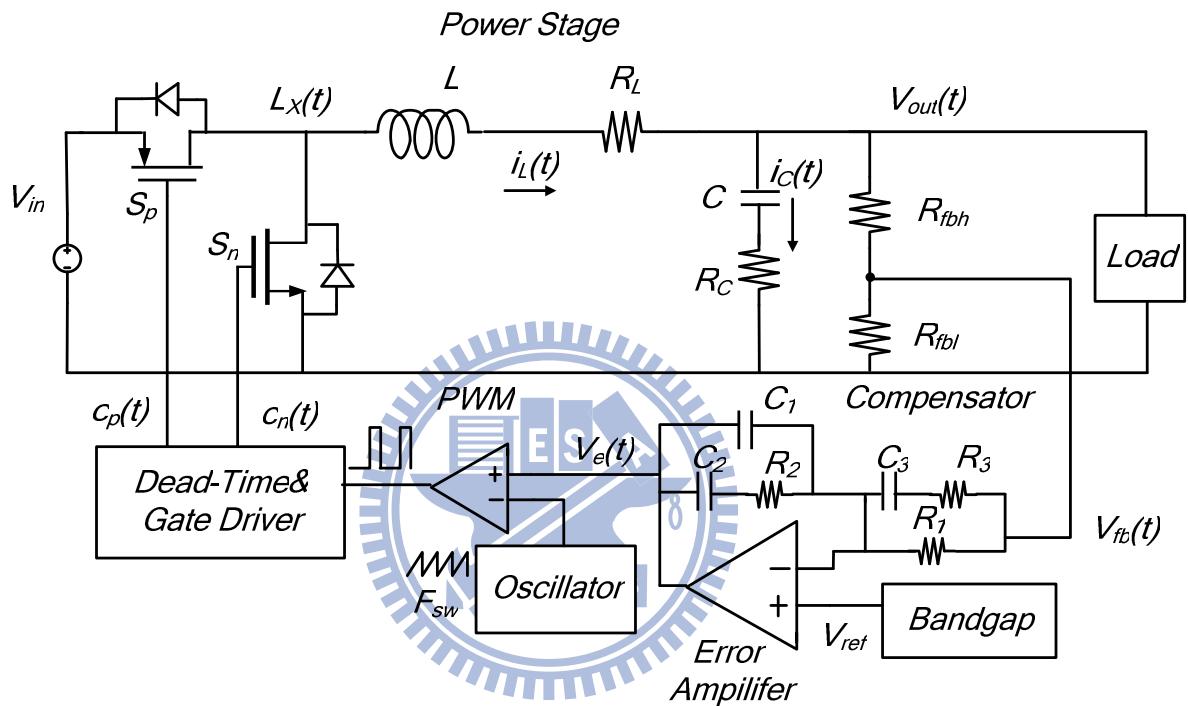

| 圖 7. 直流-直流降壓電路[6] .....                              | 8  |

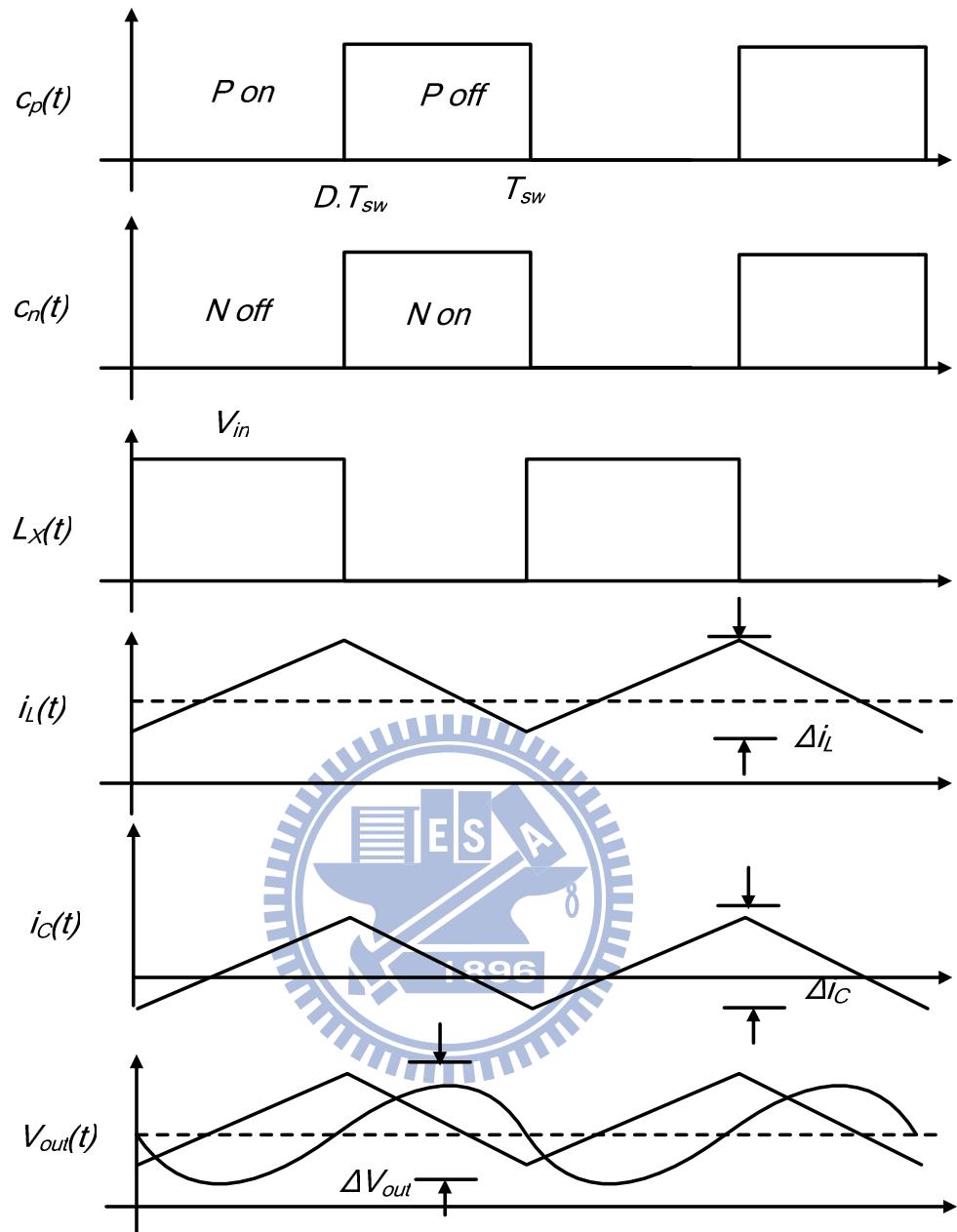

| 圖 8. 直流-直流降壓電路穩態波形圖[6] .....                         | 9  |

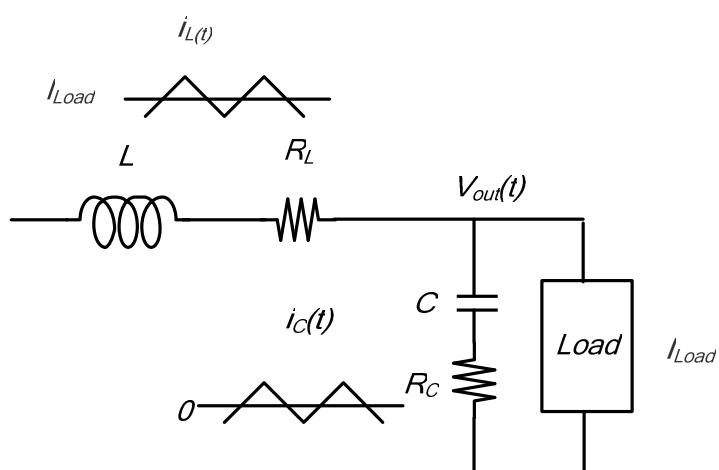

| 圖 9. 輸出濾波器[2] .....                                  | 10 |

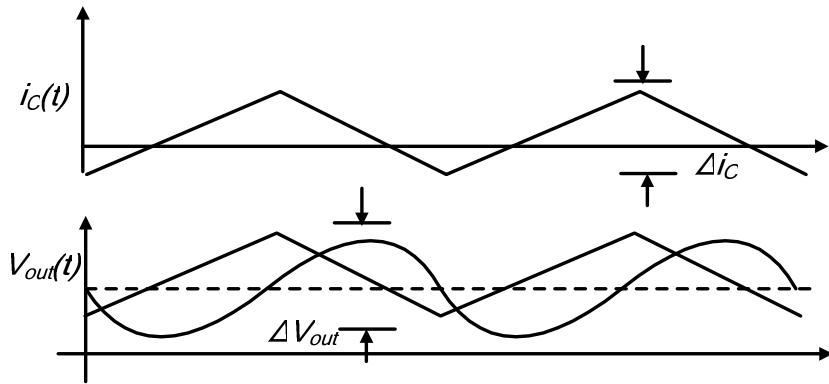

| 圖 10. $i_c(t)$ 及 $V_{out}(t)$ 波形圖[2] .....           | 11 |

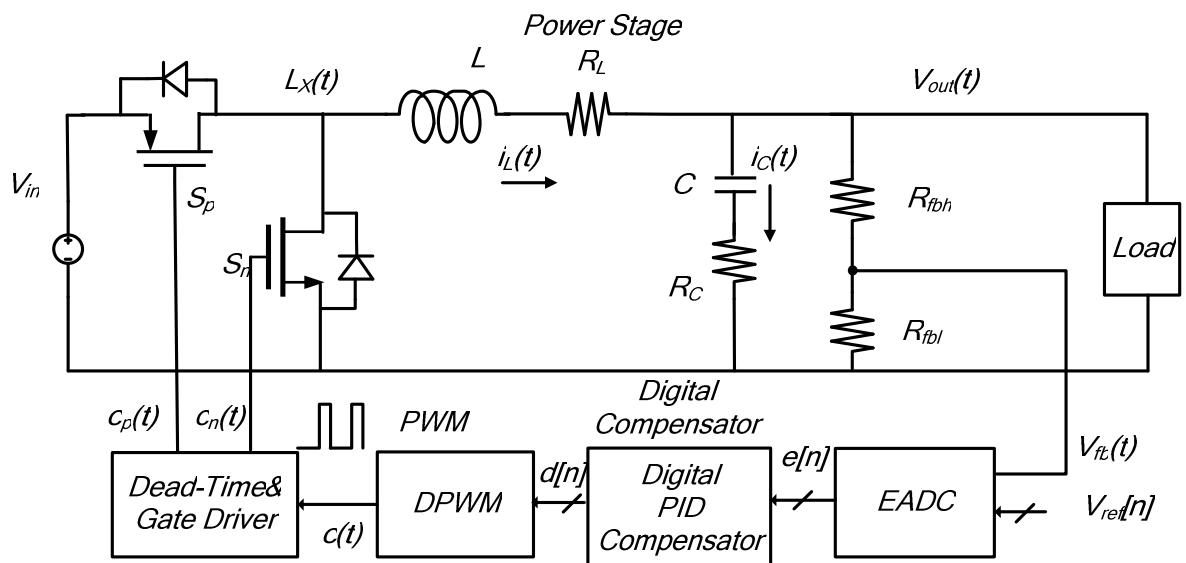

| 圖 11. 數位直流-直流降壓電路方塊圖[7] .....                        | 11 |

| 圖 12. 誤差類比數位轉換器、數位補償器及數位脈波寬度[7] .....                | 12 |

| 圖 13. 開關切換時所造成的切換雜訊[6] .....                         | 13 |

| 圖 14. 窗型類比數位轉換器輸入及輸出轉換圖[6] .....                     | 14 |

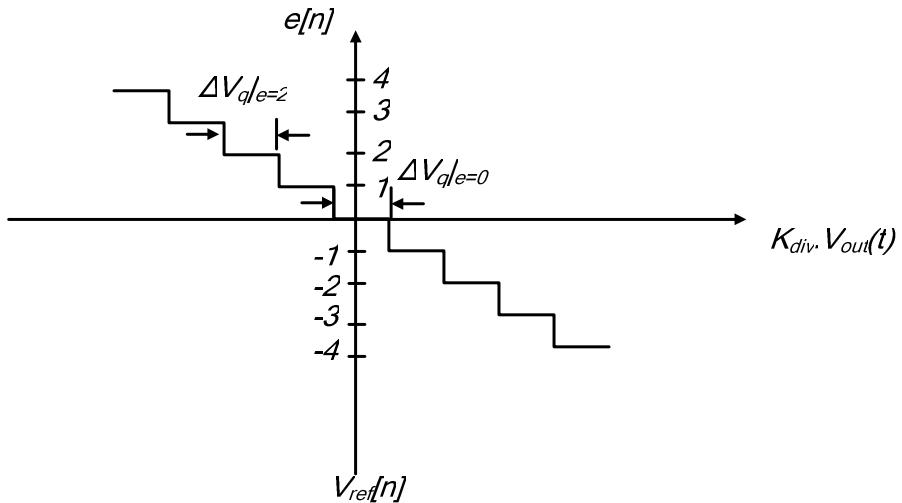

| 圖 15. 數位補償器方塊圖[6] .....                              | 15 |

| 圖 16. 數位補償器方塊圖基於查表法[6] .....                         | 16 |

| 圖 17. 數位類比轉換圖 .....                                  | 17 |

| 圖 18. 脈波工作週期解析度與輸出電壓關係圖[6] .....                     | 18 |

| 圖 19. 計數器模式數位脈波寬度調變[6] .....                         | 19 |

| 圖 20. 延遲線模式數位脈波寬度調變[6] .....                         | 20 |

| 圖 21. 混合計數延遲線模式數位脈波寬度調變電路[6] .....                   | 21 |

| 圖 22. $\Delta\Sigma$ 數位脈波寬度調變電路[6] .....             | 22 |

| 圖 23. LED 操作電路圖 .....                                | 22 |

| 圖 24. 馬達等效模型[18] .....                               | 23 |

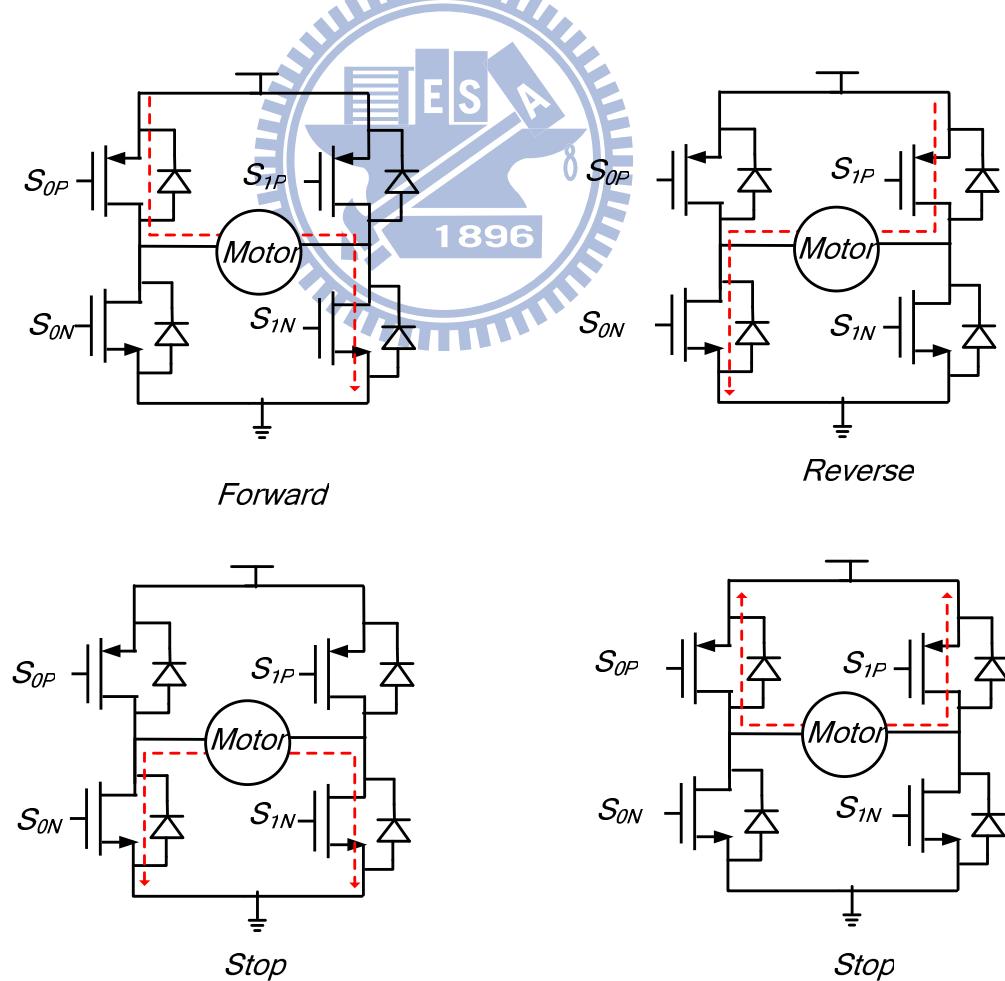

| 圖 25. 馬達轉向示意圖 .....                                  | 24 |

| 圖 26. H 橋驅動馬達[18] .....                              | 24 |

| 圖 27. 整合馬達、LED 及降壓電路 .....                           | 26 |

| 圖 28. 數位脈波寬度調變電路採用 $\Delta\Sigma$ 調變[9] .....        | 26 |

| 圖 29. 可程式車用功率積體電路系統 .....                            | 27 |

| 圖 30. 可程式車用功率積體電路系統時間流程圖 .....                       | 27 |

| 圖 31. 直流-直流降壓電路系統方塊圖[6] .....                        | 28 |

| 圖 32. 基本 $\Sigma\Delta$ 雜訊整形迴路架構[6] .....            | 29 |

| 圖 33. $\Sigma\Delta$ 雜訊整形迴路架構-加了雜訊[6] .....          | 30 |

| 圖 34. $\Sigma\Delta$ 雜訊整形迴路數位脈波寬度調變頻譜分析[6] .....     | 32 |

| 圖 35. 基本一階雜訊整形迴路數位脈波寬度調變[3] .....                    | 33 |

| 圖 36. 一階誤差回授 $\Sigma\Delta$ 雜訊整型數位脈波寬度調變電路[6] .....  | 35 |

|                                                                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

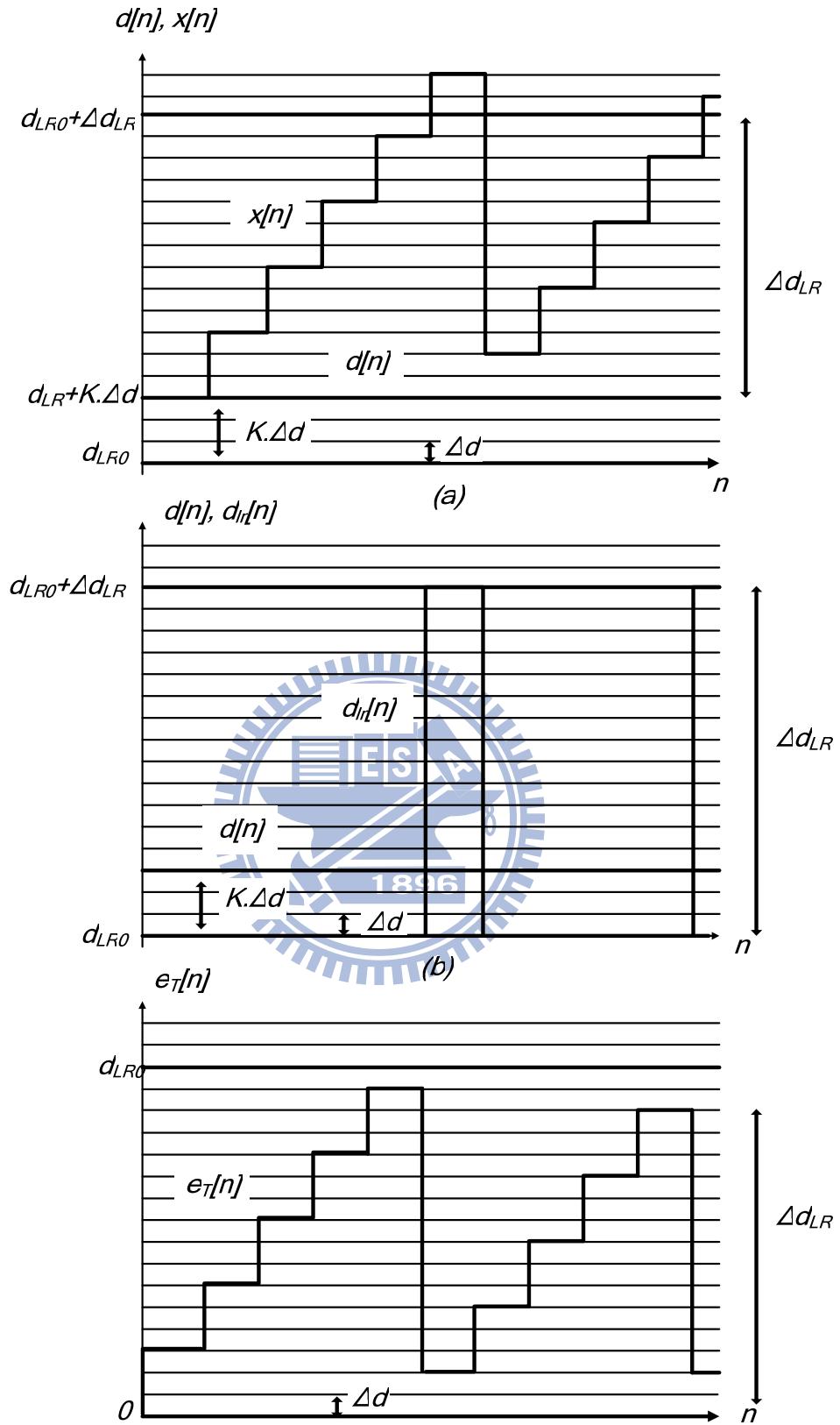

| 圖 37. 一階 $\Sigma\Delta$ 雜訊整型迴路訊號圖(a)高解析度 $d[n]$ 及內部 $x[n](b)$ 低解析度<br>$d[n](c)$ 誤差值 $e_T[n][6]$ .....                                                                                                      | 37 |

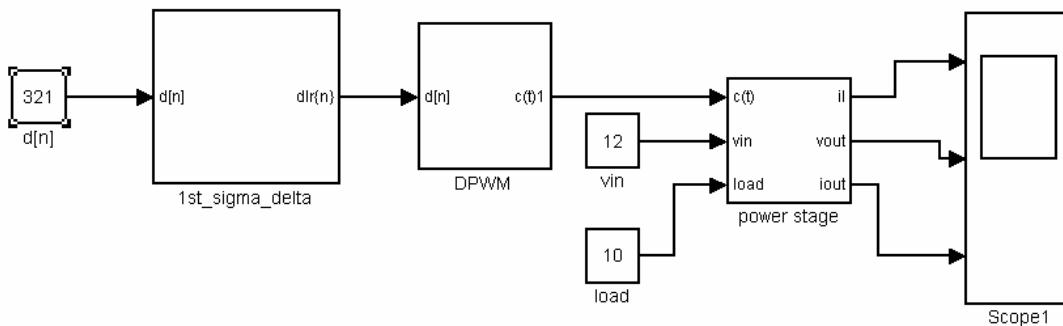

| 圖 38. 一階 $\Sigma\Delta$ 雜訊整型數位脈波寬度調變電路 Simulink 模型圖[19] .....                                                                                                                                              | 38 |

| 圖 39. 一階 $\Sigma\Delta$ 雜訊整型數位脈波寬度調變電路模擬結果 .....                                                                                                                                                           | 39 |

| 圖 40. 二階誤差回授 $\Sigma\Delta$ 雜訊整形迴路數位脈波寬度調變[6] .....                                                                                                                                                        | 40 |

| 圖 41. 二階 $\Sigma\Delta$ 誤差回授雜訊整型迴路訊號圖(a)高解析度 $d[n]$ 及內部 $x[n](b)$ 低解<br>析度 $d[n](c)$ 誤差值 $e_T[n][6]$ .....                                                                                                 | 41 |

| 圖 42. 二階 $\Sigma\Delta$ 誤差回授雜訊整型數位脈波寬度調變電路 Simulink 模型圖[19] .....                                                                                                                                          | 42 |

| 圖 43. 二階 $\Sigma\Delta$ 誤差回授雜訊整型數位脈波寬度調變電路模擬結果 .....                                                                                                                                                       | 42 |

| 圖 44. (a)誤差類比數位轉換器編碼(b) 誤差類比數位轉換器輸入與輸出對應圖 .....                                                                                                                                                            | 44 |

| 圖 45. (a)數位降壓電路系統方塊圖(b)降壓電路系統轉移函式圖[22] .....                                                                                                                                                               | 45 |

| 圖 46. $G_c(s)$ 輕載及重載的頻率響應圖 .....                                                                                                                                                                           | 47 |

| 圖 47. 系統 $T(s)$ 頻率響應圖 .....                                                                                                                                                                                | 48 |

| 圖 48. 連續訊號 $T(s)$ 及尤拉和雙線性開迴路 $T(z)$ 的頻率響應圖 .....                                                                                                                                                           | 49 |

| 圖 49. 正比積分微分補償器基於查表法 .....                                                                                                                                                                                 | 50 |

| 圖 50. (a)計數器模式數位脈波寬度調變降壓電路系統模型(b)數位脈波寬度調變<br>電路模型(c)功率區塊模型(d)數位正比積分微分補償器 .....                                                                                                                             | 52 |

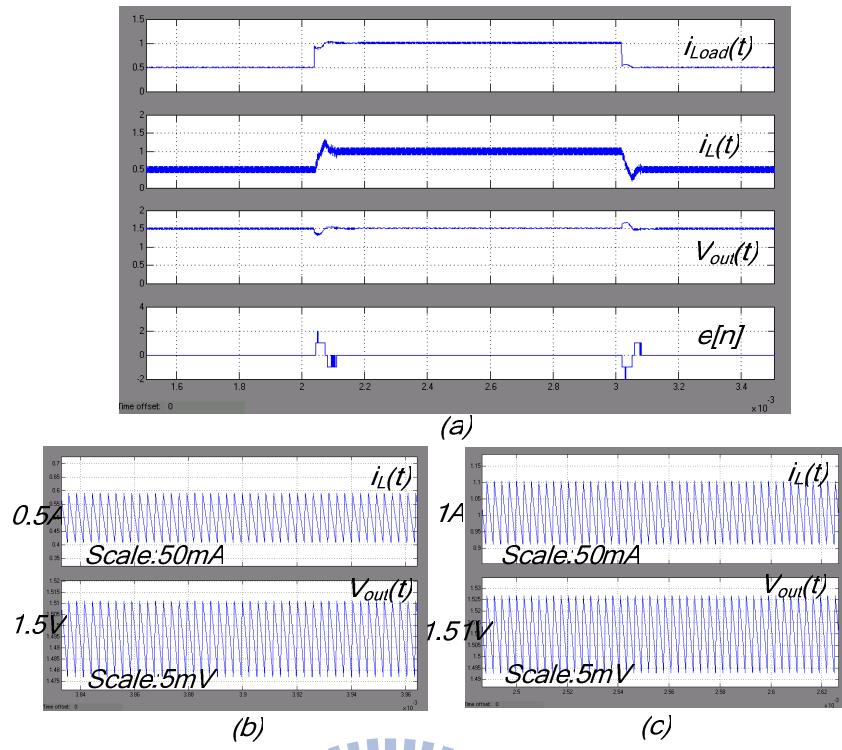

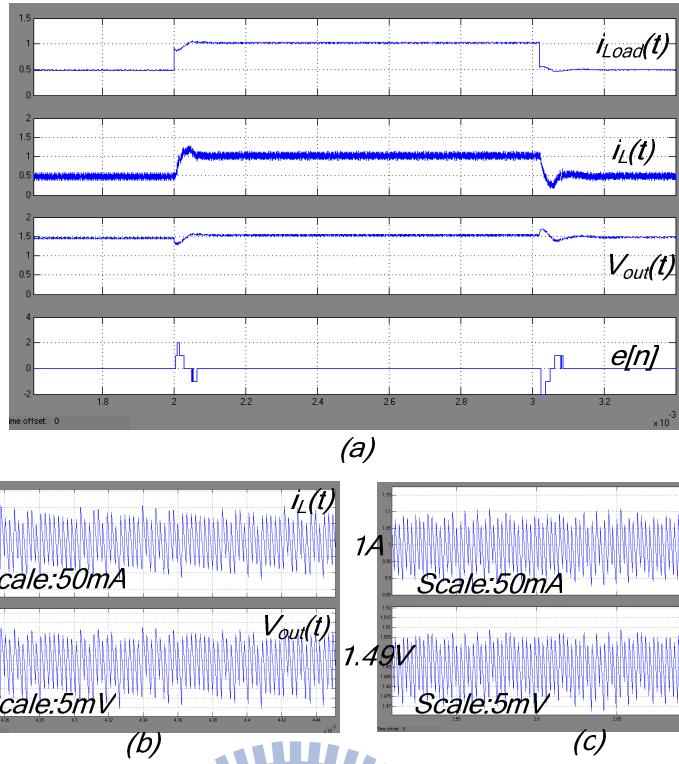

| 圖 51. 計數器模式數位脈波寬度調變負載抽載輸出電壓 1.5V 模擬圖 (a)輸出負載<br>$i_{load}(t)$ 、電感電流 $i_L(t)$ 、輸出電壓 $V_{out}(t)$ 及誤差值 $e[n]$ (b)負載 500mA 時 $i_L(t)$<br>及 $V_{out}(t)$ (c)負載 1A 時 $i_L(t)$ 及 $V_{out}(t)$ .....              | 53 |

| 圖 52. 計數器模式數位脈波寬度調變負載抽載輸出電壓 3V 模擬圖 (a)輸出負載<br>$i_{load}(t)$ 、電感電流 $i_L(t)$ 、輸出電壓 $V_{out}(t)$ 及誤差值 $e[n]$ (b)負載 500mA 時 $i_L(t)$<br>及 $V_{out}(t)$ (c)負載 1A 時 $i_L(t)$ 及 $V_{out}(t)$ .....                | 53 |

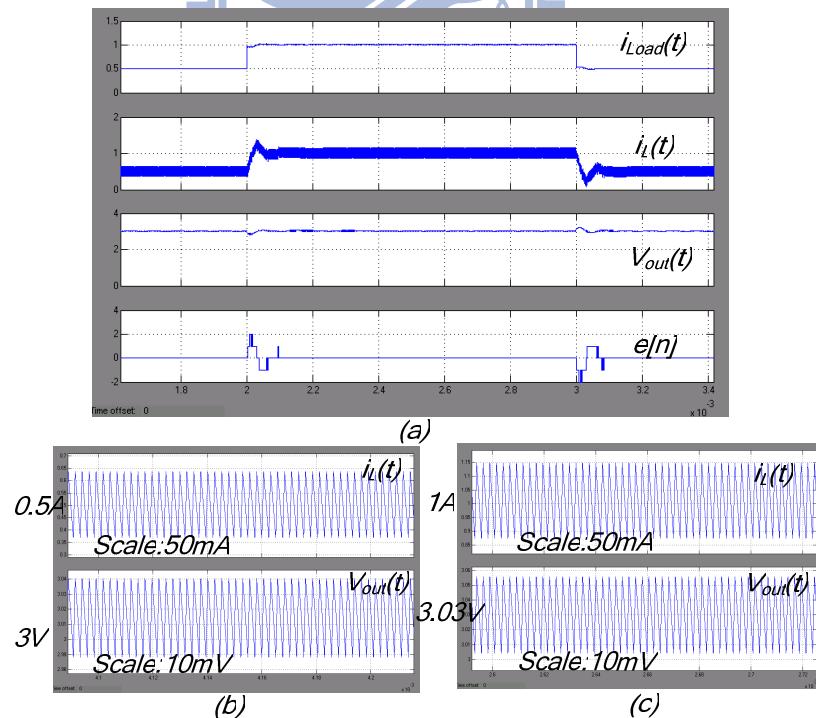

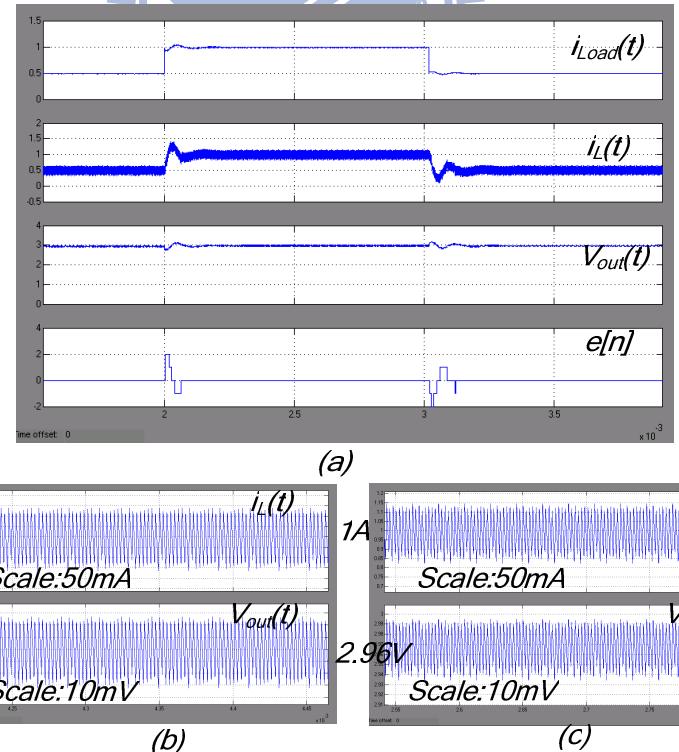

| 圖 53. 計數器模式數位脈波寬度調變負載抽載輸出電壓 5V 模擬圖 (a)輸出負載<br>$i_{load}(t)$ 、電感電流 $i_L(t)$ 、輸出電壓 $V_{out}(t)$ 及誤差值 $e[n]$ (b)負載 500mA 時 $i_L(t)$<br>及 $V_{out}(t)$ (c)負載 1A 時 $i_L(t)$ 及 $V_{out}(t)$ .....                | 54 |

| 圖 54. 計數器模式數位脈波寬度調變負載抽載輸出電壓 9V 模擬圖 (a)輸出負載<br>$i_{load}(t)$ 、電感電流 $i_L(t)$ 、輸出電壓 $V_{out}(t)$ 及誤差值 $e[n]$ (b)負載 500mA 時 $i_L(t)$<br>及 $V_{out}(t)$ (c)負載 1A 時 $i_L(t)$ 及 $V_{out}(t)$ .....                | 54 |

| 圖 55. (a)二階 $\Sigma\Delta$ 雜訊整形迴路數位脈波寬度調降壓電路系統模型(b) 二階 $\Sigma\Delta$<br>雜訊整形迴路調變 .....                                                                                                                    | 55 |

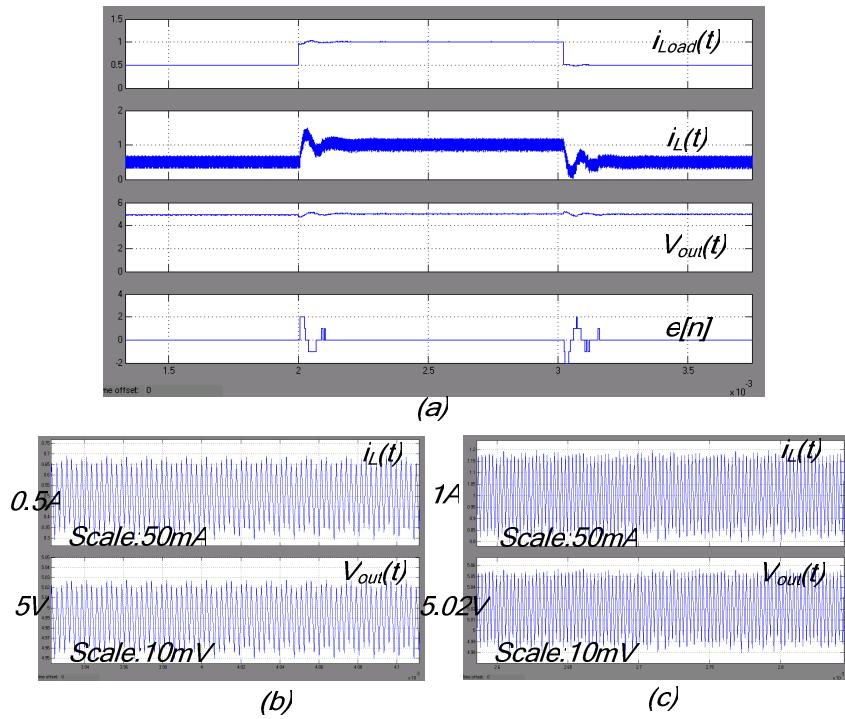

| 圖 56. 二階 $\Sigma\Delta$ 數位脈波寬度調變負載抽載輸出電壓 1.5V 模擬圖 (a)輸出負載<br>$i_{load}(t)$ 、電感電流 $i_L(t)$ 、輸出電壓 $V_{out}(t)$ 及誤差值 $e[n]$ (b)負載 500mA 時 $i_L(t)$<br>及 $V_{out}(t)$ (c)負載 1A 時 $i_L(t)$ 及 $V_{out}(t)$ ..... | 56 |

| 圖 57. 二階 $\Sigma\Delta$ 數位脈波寬度調變負載抽載輸出電壓 3V 模擬圖 (a)輸出負載<br>$i_{load}(t)$ 、電感電流 $i_L(t)$ 、輸出電壓 $V_{out}(t)$ 及誤差值 $e[n]$ (b)負載 500mA 時 $i_L(t)$<br>及 $V_{out}(t)$ (c)負載 1A 時 $i_L(t)$ 及 $V_{out}(t)$ .....   | 56 |

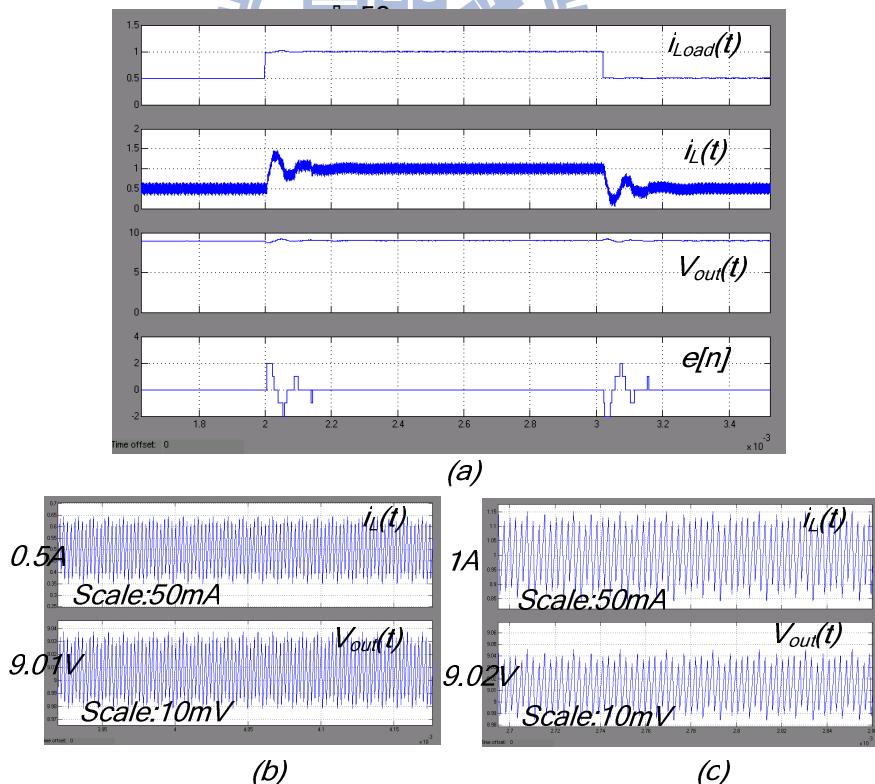

| 圖 58. 二階 $\Sigma\Delta$ 數位脈波寬度調變負載抽載輸出電壓 5V 模擬圖 (a)輸出負載                                                                                                                                                    |    |

|                                                                                                                                                                                                                                                                 |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| i <sub>load</sub> (t)、電感電流 i <sub>L</sub> (t)、輸出電壓 V <sub>out</sub> (t)及誤差值 e[n] (b)負載 500mA 時 i <sub>L</sub> (t)<br>及 V <sub>out</sub> (t) (c)負載 1A 時 i <sub>L</sub> (t)及 V <sub>out</sub> (t).....                                                            | 57 |

| 圖 59. 二階 $\Sigma\Delta$ 數位脈波寬度調變負載抽載輸出電壓 9V 模擬圖 (a)輸出負載<br>i <sub>load</sub> (t)、電感電流 i <sub>L</sub> (t)、輸出電壓 V <sub>out</sub> (t)及誤差值 e[n] (b)負載 500mA 時 i <sub>L</sub> (t)<br>及 V <sub>out</sub> (t) (c)負載 1A 時 i <sub>L</sub> (t)及 V <sub>out</sub> (t)..... | 57 |

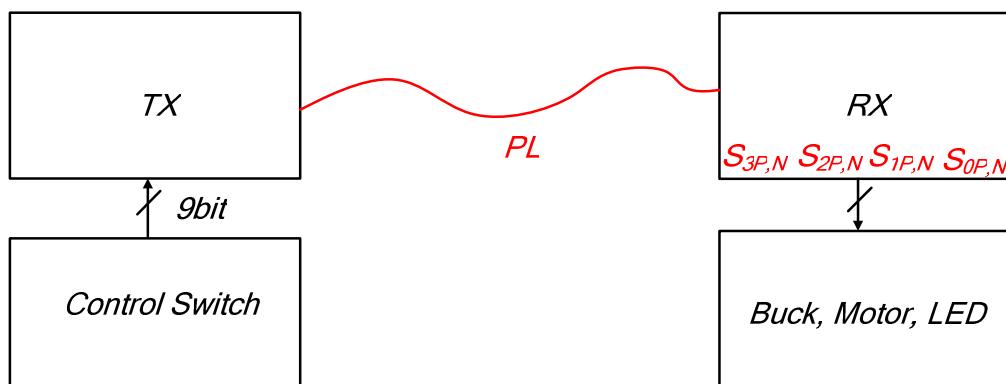

| 圖 60. 車用電子電源線通訊及可程式車用功率積體電路示意圖.....                                                                                                                                                                                                                             | 58 |

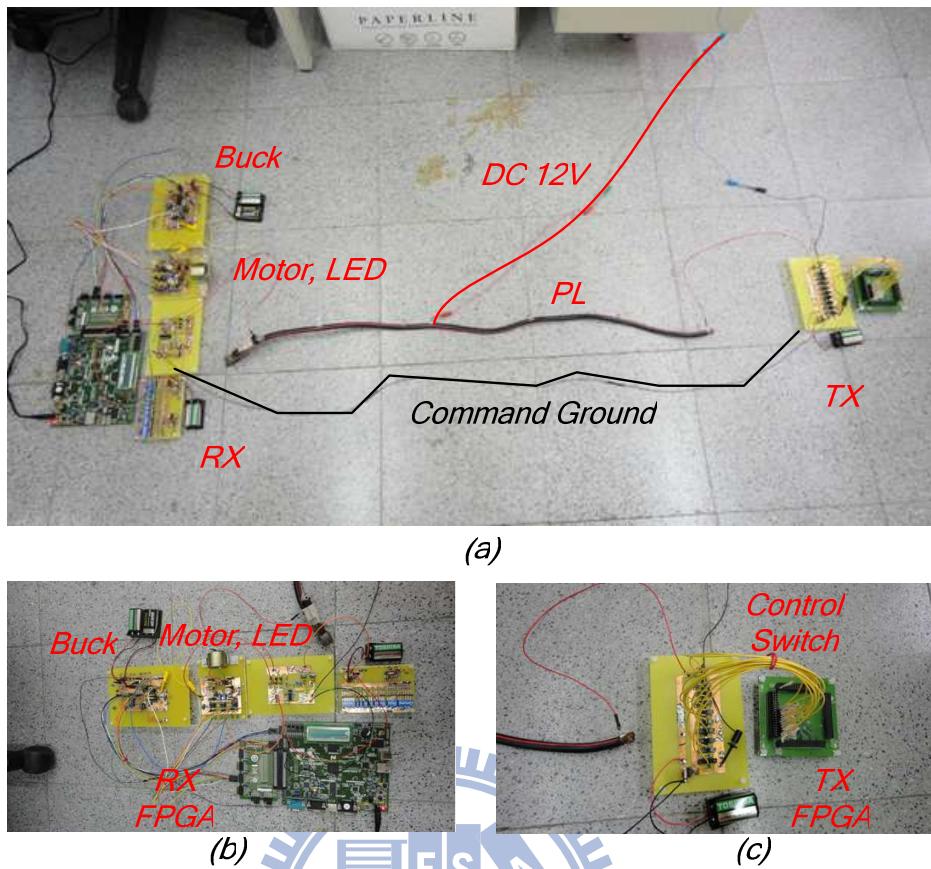

| 圖 61. (a)車用電子電源線通訊及可程式車用功率積體電路實際圖(b)接收端<br>(RX)、馬達、LED 及降壓電路(c)傳輸端(TX)及開關 .....                                                                                                                                                                                 | 59 |

| 圖 62. 直流-直流降壓印刷電路板子元件佈局圖.....                                                                                                                                                                                                                                   | 60 |

| 圖 63. (a)直流-直流降壓印刷電路板子實際圖(b)馬達及 LED 印刷電路板子實際圖 .....                                                                                                                                                                                                             | 60 |

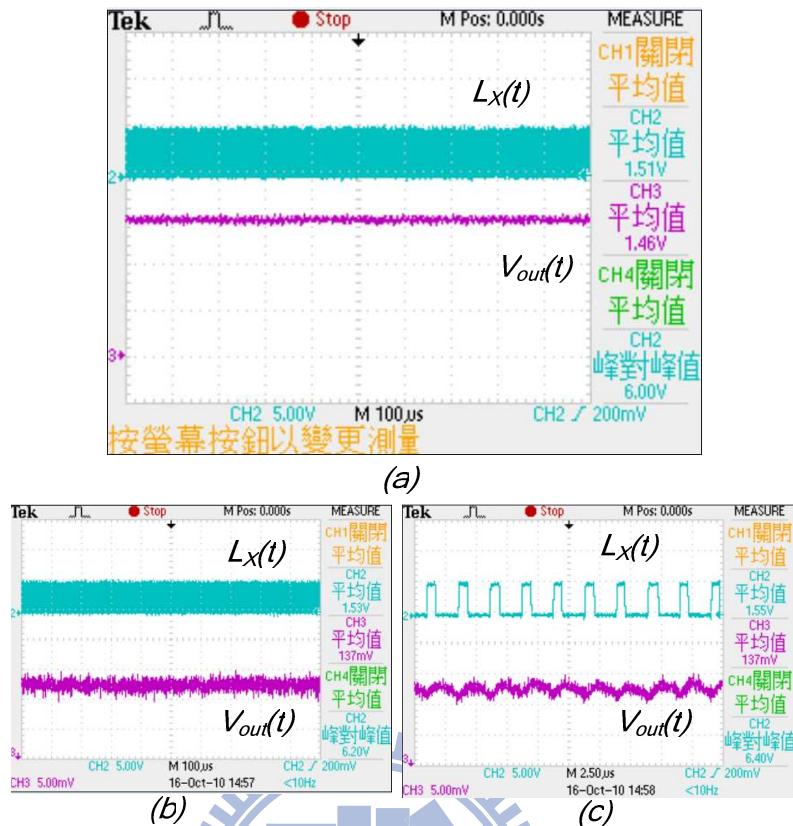

| 圖 64. 輸出 1.5V(no load) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                                    | 61 |

| 圖 65. 輸出 1.5V(load=500mA) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                                 | 62 |

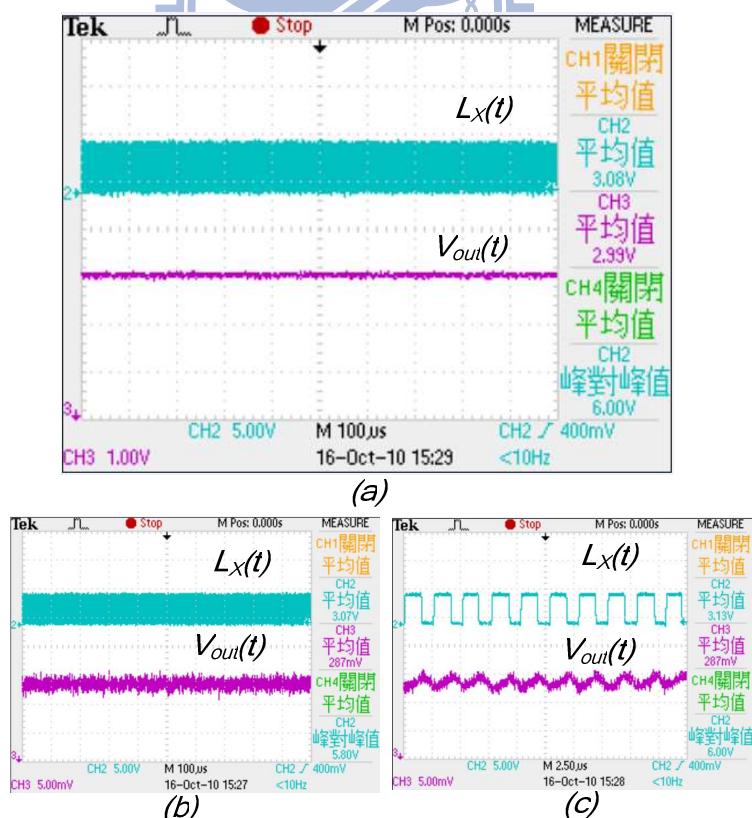

| 圖 66. 輸出 3V(no load) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                                      | 62 |

| 圖 67. 輸出 3V(load=600mA) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                                   | 63 |

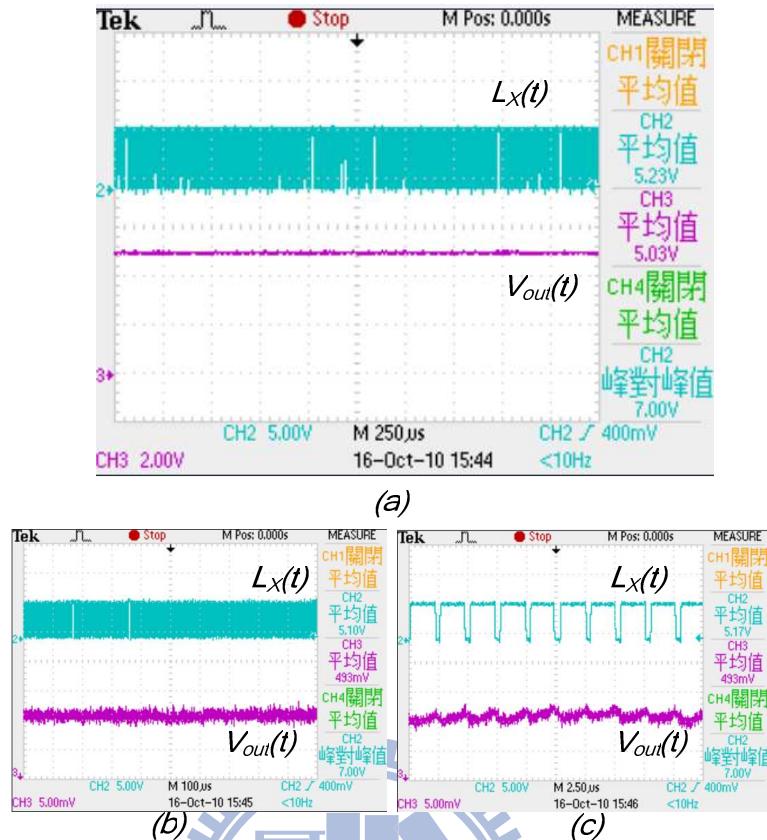

| 圖 68. 輸出 5V(no load) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                                      | 63 |

| 圖 69. 輸出 5V(load=500mA) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                                   | 64 |

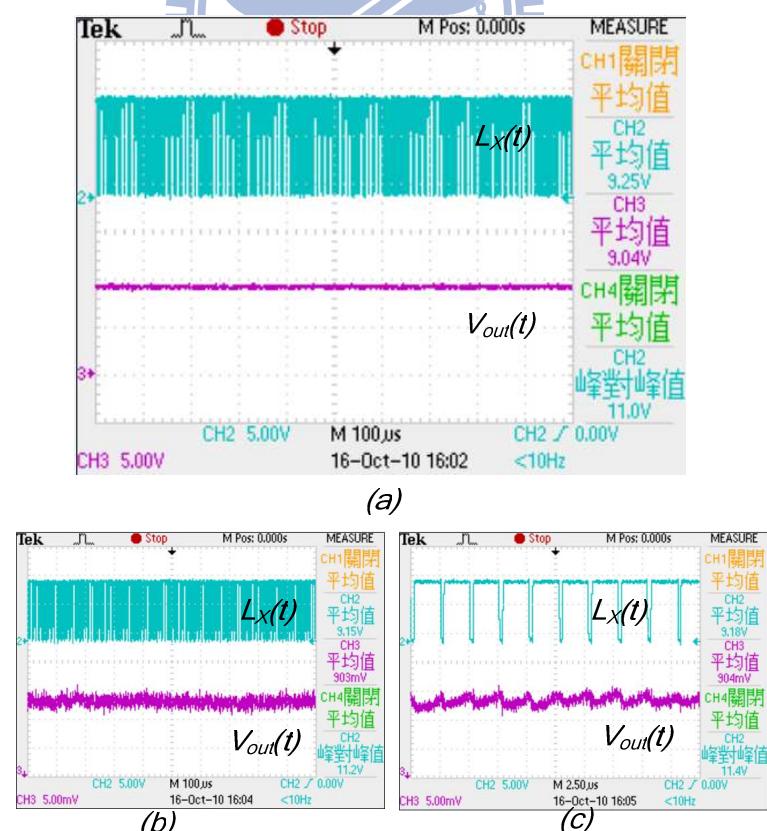

| 圖 70. 輸出 9V(no load) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                                      | 64 |

| 圖 71. 輸出 9V(load=600mA) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                                   | 65 |

| 圖 72. 輸出 1.5V(V <sub>in</sub> =5V) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                        | 66 |

| 圖 73. 輸出 3V(V <sub>in</sub> =5V) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                          | 66 |

| 圖 74. 輸出 5V(V <sub>in</sub> =6V) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                          | 67 |

| 圖 75. 輸出 9V(V <sub>in</sub> =10V) , V <sub>out</sub> (t) (a)平均值 (b)漣波大小 (c)每週期充放電 .....                                                                                                                                                                         | 67 |

| 圖 76. 馬達轉速(a)轉速 20%(b)轉速 50%(c)轉速 80% .....                                                                                                                                                                                                                     | 68 |

| 圖 77. LED 亮度的調控(a)亮度 20% (b)亮度 50% (c)亮度 80%.....                                                                                                                                                                                                               | 69 |

| 圖 78. LED 頻率的調控(a)頻率 6Hz(b)頻率 3Hz(c)頻率 1.5Hz(d)頻率 0.75Hz .....                                                                                                                                                                                                  | 69 |

| 圖 79. LED 亮度時間的調控，這邊設定頻率為 0.75Hz，亮度為 50%(a)亮度時間<br>20%(b)亮度時間 50%(c)亮度時間 80% .....                                                                                                                                                                              | 70 |

# 表目錄

|                                                                        |    |

|------------------------------------------------------------------------|----|

| 表 1. 32 位元控制指令及功能說明 .....                                              | 5  |

| 表 2. 數位降壓電路的規格如表所示 .....                                               | 28 |

| 表 3. $d[n]$ 為 50 經由一階 $\Sigma\Delta$ 雜訊整形迴路所觀察到輸出 $d_{lr}[n][9]$ ..... | 34 |

| 表 4. 誤差類比數位轉換器編碼 .....                                                 | 44 |

| 表 5. 計數器模式數位脈波寬度調變降壓電路負載變化下輸出電壓性能表現 .....                              | 52 |

| 表 6. 二階 $\Sigma\Delta$ 雜訊整形迴路數位脈波寬度調變降壓電路負載變化下輸出電壓性能表現 .....           | 55 |

| 表 7. 5 位元控制指令表 .....                                                   | 59 |

| 表 8. 輸入電壓為 12V，輸出電壓在不同的負載的性能表現 .....                                   | 61 |

| 表 9. 在無負載狀態下，輸出電壓在不同輸入電壓的性能表現 .....                                    | 65 |

# 第一章

## 緒論

### 1.1 簡介

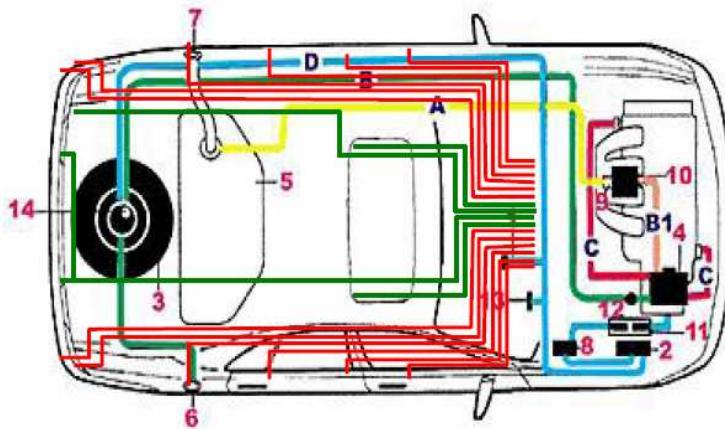

由於科技的進步，汽車的結構日益複雜，越來越多的電子產品被使用在汽車上面。複雜的如DVD影像播放器、GPS 導航系統、汽車前後防撞雷達、恆溫獨立空調等等，簡單的如LED 尾燈、迎賓車門燈、電動天窗、電動窗、電動座椅等等，都可以看到電的影子。平價的車子，電子所佔的汽車成本比重約為15~25%，而高級車可以佔到超過50% 的汽車成本。這顯示汽車電子的重要性逐年攀升。更有甚之全球的石油供給量越來越吃緊，預估在2050 年將耗盡所有的石油，能源危機的不僅不會疏解，反而會越來越重。油電混合車只是過渡時期的產品，氫燃料車又還不成熟，未來的車可能還是比較可能採用全電動方式。如之前在美國加州發表的 Tesla 就是一台全電動的跑車，售價十萬美元，其中的馬達與電源總成由台灣製作。到了電動車的年代，電器設備的使用就會更高，將會達80%以上。下圖1所示為一個電相關的基本系統，每一個開關、燈具、驅動點，都有一條特定的導線或匯流排，將指令由開關處傳送至儀表板，然後再將動作指令傳到受驅動點。據統計汽車的總共有超過300 條以上長短不一的導線，複雜的高級轎車甚至有超過500 條的導線，總長度超過1000 公尺。以電動窗為例，它就有一條線拉到電動窗的開關處，將開關的指令傳至儀表板後方，再把指令由另一條專線傳至該電動窗，方向燈與車頭燈亦有相同的機制。這些來來回回的線路，使得汽車的繞線非常的複雜。不僅造成維修的困難，也是可靠度一個非常大的威脅。下圖所示為汽車電路線的示意圖，實際的複雜度遠超過此一圖示。複雜的繞線，除了提高生產成本與增加維修困難外，也嚴重的影響汽車的可靠度。

圖1. 汽車電路導線佈局示意圖

## 1.2 研究動機

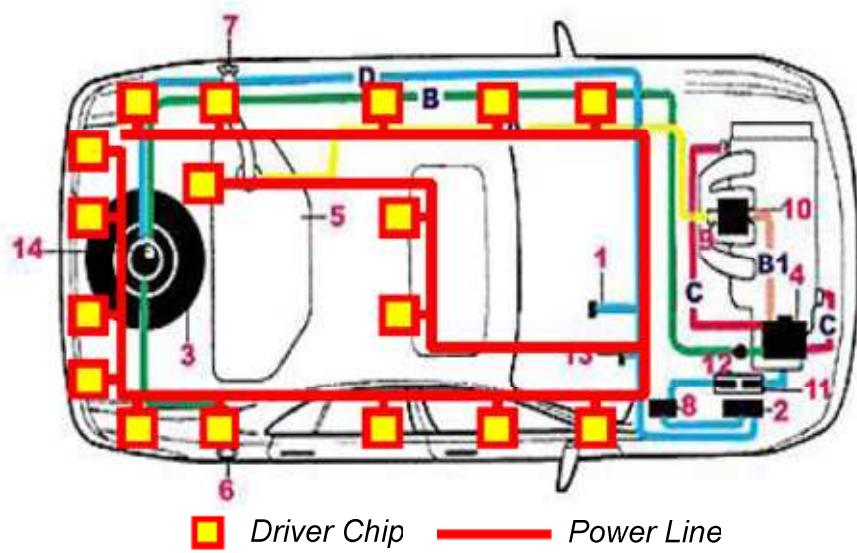

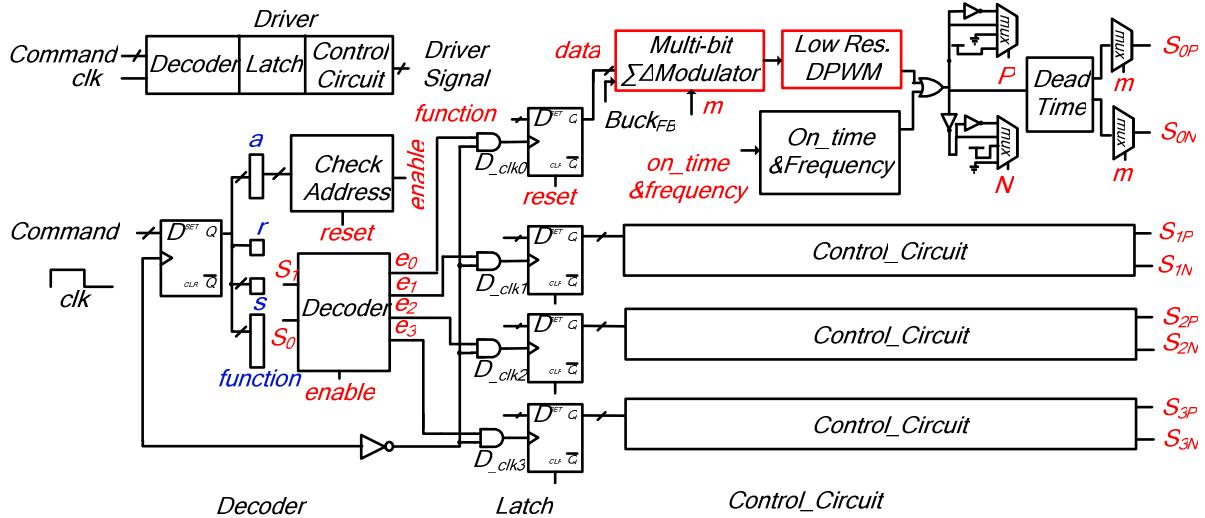

本計畫提出一個汽車專用的電源線通訊技術，並結合可程式的功率積體電路，根據所接受的指令，產生所需要的驅動信號，來驅動被控制的元件。以燈具控制而言，方向燈、煞車燈、車內燈、倒車燈、緊急燈等，均有不同亮度與閃爍頻率的需求，LED 與傳統燈泡亦有不同之驅動電壓與模式。以馬達驅動而言，自動車窗馬達、電動座椅、天窗馬達、天線馬達、甚至汽車驅動馬達等，亦有不同的驅動能力與模式。本計畫提出的汽車功率SoC，能夠經由電源線來傳送指令，並且根據所接收到的指令，調整輸出的電壓電流大小、閃爍頻率、甚至到馬達驅動的電壓電流曲線 (Voltage/Current Profile)。如此，多數的車上電器裝備，都可使用此一晶片進行驅動，而汽車也只有一條電源線，更有甚之，此電源線為單一條串聯線，不需要向傳統的平行佈線方式。如此則能大大的減少佈線的使用，也能夠提昇汽車的可靠度，降低汽車的生產成本。下圖2所示為一個利用本技術所產出的汽車佈線示意圖。在這邊我們可以看到電源線上面會有許多的驅動晶片，而每顆驅動晶片內部的方塊圖如下圖3所示包含了解碼、拴鎖，以及控制電路。車用電子電源線通訊顧名思義則是訊號是由電源上傳遞，在這邊傳送的訊號為每次32位元。每顆晶片在電源線上都有自己的位址，所以每次收到資料時都必須做一次解碼的動作，看看是否要動作。我們可以看到驅動晶片的輸出有四組訊號，每一組訊號分別給P及N型的功率電晶體來推動馬達，LED或降壓電路如圖4所示。

圖2. 電源線通訊汽車電路導線佈局示意圖

圖3. 可程式化車用功率積體電路示意圖

圖4. 四組開關推動馬達、LED 及降壓電路

如圖4所示這邊定義每一組開關由P及N型功率電晶體所組成，圖4所示共有四組的開關。在可程式化車用功率積體電路晶片如圖3所示有32位元的輸入、一時脈以及四組的輸出訊號，而每組的輸出訊號分別給一組開關，也就是P及N型的功率電晶體。在整個計畫裡面我們希望能藉由32位元的輸入指令，使得每一組的輸出訊號可以達到控制馬達、LED及降壓電路。表1所示為驅動晶片的輸入指令共32位元，這邊分別來解釋這32位元的功能：

Address : 共有8位元，可以選擇電源線上的驅動晶片

Reset : 清除開關

Mode : 選擇開迴路模式(LED、馬達)或閉迴路模式(降壓電路[1, 2])

Switch : 選擇要使用哪一組開關(每顆驅動晶片有4組輸出訊號)

PMOS : 選擇開關上P功率晶體要全關、全開、由控制器決定或控制器的反向決定

NMOS : 選擇開關上N功率晶體要全關、全開、由控制器決定或控制器的反向決定

Frequency : 選擇頻率((LED、馬達))

on\_time : 在 LED 閃爍時可以選擇它亮的時間長短(0%~100%)

data : 在 LED 、馬達使用下控制它的亮度或轉速，在降壓電路使用下可以當作輸出電壓的調整。

由於功率驅動晶片共有4組的輸出控制訊號，每一組分別為控制P功率晶體及N功率晶體，在此篇論文每一組的控制訊號皆能控制馬達、LED及降壓電路。接下來分別了解馬達、LED及降壓電路的基本控制原理，可觀察到它們有共通的電路則是數位脈波寬度調變。此篇論文採用的則是二階的 $\Sigma\Delta$ 整形雜訊(Noise-Shaping)迴路[3, 4]數位脈波寬度調變電路，它有許多優點，分別為低功率消耗、可操作在高速，在這邊最主要是能將馬達、LED及降壓電路結合在一起，節省面積及功率消耗。

表1. 32位元控制指令及功能說明

| Command   | Number of Bit | Symbol | Function                                                          |

|-----------|---------------|--------|-------------------------------------------------------------------|

| Address   | b24~b31       | a0~~a7 | select chip                                                       |

| Reset     | b23           | r      | reset switch                                                      |

| Mode      | b22           | m      | close or open loop                                                |

| Switch    | b20~b21       | s0~s1  | select switch                                                     |

| Pmos      | b18~b19       | P0~P1  | 00=off, 01=on,<br>10=control, 11=control_bar                      |

| Nmos      | b16~b17       | N0~N1  | 00=off, 01=on,<br>10=control, 11=control_bar                      |

| Frequency | b13~b15       | f0~f2  | 000=24kHz, 001=190Hz<br>010=6hz, 011=3Hz<br>100=1.5Hz, 101=0.75Hz |

| On_time   | b8~b12        | t0~t4  | on time control                                                   |

| Data      | b0~b7         | d0~d7  | PWM control                                                       |

## 1.3 論文結構

本論文內容分成五個章節。第一章為緒論，簡介發展現況、研究動機以及論文結構。第二章為數位直流-直流切換式電源供應、馬達及 LED 基本原理，一開始先介紹降壓電路的基本操作原理，接下來進入類比降壓電路基本架構，最後則是進入數位降壓電路。第三章節則是介紹可程式車用功率積體電路設計的規格制定及設計流程。第四章節則是使用 Matlab/Simulink 模擬數位降壓電路在不同數位脈波寬度調變電路負載變化時所看到輸出的狀態。第五章節則是使用 FPGA 驗證整體電源線通訊(PLC)可程式車用功率積體電路，利用兩塊 FPGA 分別當傳送端(TX)及接收端(RX)和可程式車用功率積體電路，訊號藉由 DC12V 的電源線傳送達到控制馬達、LED 及降壓電路。

## 第二章

# 數位控制直流-直流切換式電源供應、 LED 及直流馬達基本原理

在這一章節主要是介紹數位控制直流-直流切換式電源供應、LED 及直流馬達的基本原理。一開始先從基本的直流-直流降壓電路每週期的充放電看起，可得到輸出電壓跟輸入電壓的關係式，接下來進入類比直流-直流降壓電路系統面的分析，裡面包含類比的補償電路、脈波寬度調變電路及輸入濾波器的設計。當類比直流-直流降壓電路分析完之後再進入數位直流-直流降壓電路，數位直流-直流降壓電路則是將輸出類比訊號經由類比數位轉換器轉為數位碼之後進入數位補償電路、數位脈波寬度調變電路產生脈波寬度調變達到與類比直流-直流降壓電路相同的功能。最後則是介紹 LED 及馬達的驅動原理。

## 2.1 直流-直流降壓電路基本原理

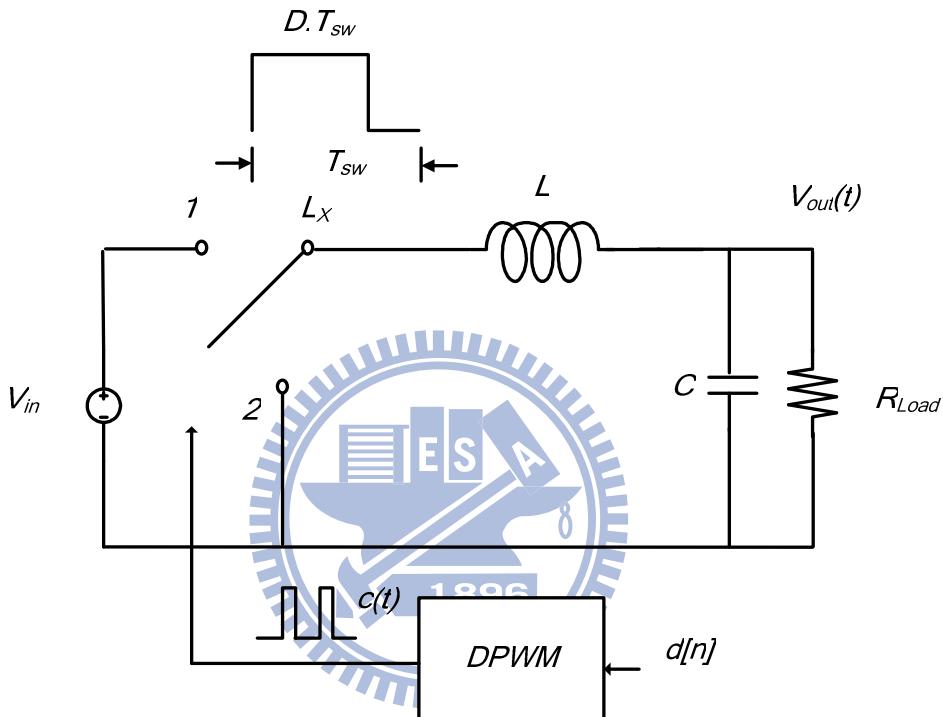

如下圖 5 所示我們可以看到為直流-直流降壓電路的基本的操作原理[1, 2]。當  $S_W(t)$  切到 1 時，此時  $L_X(t)$  的電位為  $V_{in}$ ，電感上產生一電位差進而產生電流流向輸出電容充電，當  $S_W(t)$  切到 2 時， $L_X(t)$  的電位降為地，由於電感電流為持續性的，電感上的電位差為反方向，故在電感上的電流會像三角波隨著切換週期而充放電，最後到達穩態狀態，這邊可以得到輸出電壓與輸入電壓關係式，如式(2.1)所示，D 為工作週期， $T_{on}$  為充電時間， $T_{sw}$  為切換週期。

$$V_{out}(t) = D \cdot V_{in} \quad (2.1)$$

$$D = \frac{T_{on}}{T_{sw}} \quad (2.2)$$

圖5. 直流-直流降壓電路基本架構[1]

圖6.  $S_W(t)$ ,  $L_X(t)$  及  $V_{out}(t)$  波形圖[1]

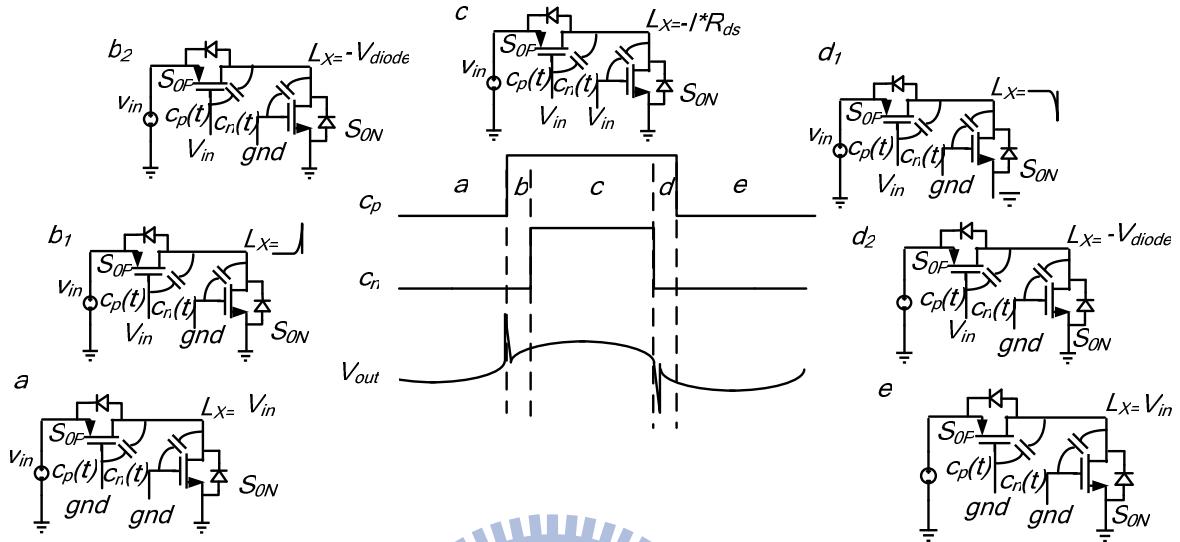

### 2.1.1 類比直流-直流降壓電路操作原理

如下圖 7 所示可以看到整體類比直流-直流降壓電路共包含了三個部份，分別為功率區塊(Power Stage)、補償電路[5] (Compensator) 及脈波寬度調變(PWM)。在功率區塊裡面包含了 P 及 N 型功率電晶體、輸出電感及電容。而補償電路部分則是由比較器、補償電阻及電容所組成的，最後脈波寬度調變電路則是由補償電路的輸出和鋸齒波產生器經由比較產生脈波寬度調變。整體系統行為模式則是一開始輸出電壓  $V_{out}(t)$  初始值為

0V，此時代參電壓(Bandgap Reference)會做緩啟動，輸出電壓  $V_{out}(t)$  經由衰減器  $R_{fbh}$  及  $R_{tbl}$  產生回授電壓  $V_{fb}(t)$ ，此回授電壓會一直鎖著代參電壓，這兩點電壓的誤差值經由補償電路所產生的  $V_e(t)$ ，再經由比較器和鋸齒波作比較，所產生的脈波寬度調變來控制電晶體開啟多一點或少一點，使得  $V_{out}(t)$  鎖住  $V_{ref}$ 。上述所提到的緩啟動主要用來避免脈波寬度調變電路一開始為全開狀態，造成電感上電流及輸出電壓暴衝而損毀電路及元件，

圖7. 直流-直流降壓電路[6]

如下圖 8 所示，此波型圖是在穩態狀態下分析。一開始由 P 電晶體開啟 N 電晶體關閉，可觀察到  $L_X(t)$  上的電壓會等於  $V_{in}$  的電壓，此時在電感上的跨壓會是  $V_{in} - V_{out}(t)$ ，電感上的電流  $i_L(t)$  會隨著時間而線性上升，電感電流  $i_L(t)$  會流入兩條路徑，第一條路徑則是輸出負載，此負載電流趨進於直流電流，第二條路徑則是流入輸出電容，由於直流電流已流入輸出負載，故在輸出電容上的電流則為  $i_L(t)$  的充電電流，此電流會造成輸出電壓上升。當 P 電晶體所關閉 N 電晶體開啟， $L_X(t)$  上的電壓會等於地的電壓，此時在電感上跨壓為  $-V_{out}(t)$ ，電感上的電流會持續的流，但由於電感上的壓降已變為反向，故電感上的電流  $i_L(t)$  會隨著時間而線性下降，由於輸出負載維持直流電流，輸出電容會吐出電荷給輸出負載，進而造成輸出電壓放電。

圖8. 直流-直流降壓電路穩態波形圖[6]

### 2.1.2 輸出濾波器設計

在這邊討論一下輸出濾波器的設計，輸出濾波器由下圖 9 所示由電感、電容及一負載電阻所組成，要如何決定這一些被動的元件的大小，對整個系統的穩定度及輸出電壓上的漣波(Ripple)有很大的影響。這邊知道電感上的電流在每一週期的充放電如式(2.3)， $T_{sw}$  為每一切換頻率的之週期。

$$\Delta i_L = \frac{V_{in} - V_{out}}{L} \cdot D \cdot T_{sw} \quad (2.3)$$

經由下圖 9 所示，電感上的電流可以拆為兩部分來看，第一部分為直流部份會等於負載所抽的電流  $I_{Load}$ ，第二部份則是經由每週期的充放電在直流上面的漣波  $\Delta i_L$ ，會等效於電容上面的電流  $\Delta i_C$ 。輸出電壓上的漣波大小則是  $\Delta i_C$  在輸出電容及輸出電容上面的寄生電阻(ESR)所影響造成的， $R_C$  為電容上的等效串聯電阻(ESR)， $R_L$  為電感上的直流電阻(DCR)。

在輸出電容上寄生電阻上所造成的輸出漣波影響為：

$$\Delta i_L = \Delta i_C \quad (2.4)$$

$$\Delta V_{out} = \Delta i_L \cdot R_C \quad (2.5)$$

而在輸出電容的影響則為：

$$Q = I \cdot T = C \cdot V \quad (2.6)$$

$$\frac{\Delta i_L}{2} \cdot \frac{T_{sw}}{2} \cdot \frac{1}{2} = C \cdot \Delta V_{out} \quad (2.7)$$

$$\Delta V_{out} = \frac{T_{sw} \cdot \Delta i_L}{8C} \quad (2.8)$$

故輸出電壓漣波的大小或電感上的電流漣波的大小，都可以參考這些式子來設計出這些被動元件。另外一方面我們知道這邊的 LC 再整個系統的裡面會產生一組共軛的雙極點，在這邊我們會設計  $LC >> \omega_{sw}^{-2}$ ，使得切換頻率的雜訊在這系統裡面可以被濾掉。

圖9. 輸出濾波器[2]

圖 10.  $i_C(t)$  及  $V_{out}(t)$  波形圖 [2]

### 2.1.3 數位直流-直流降壓電路基本架構及操作原理

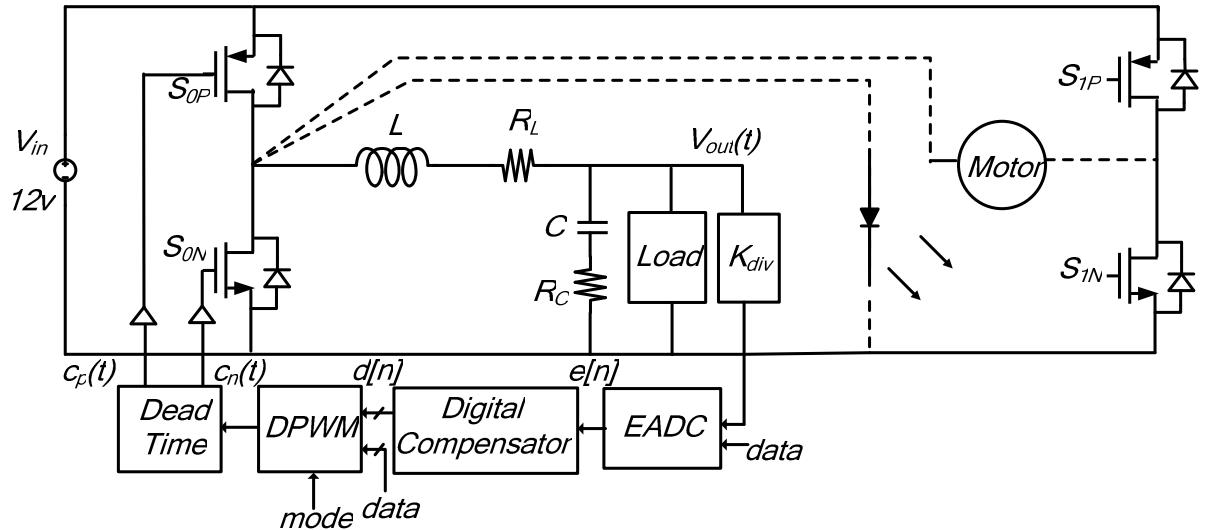

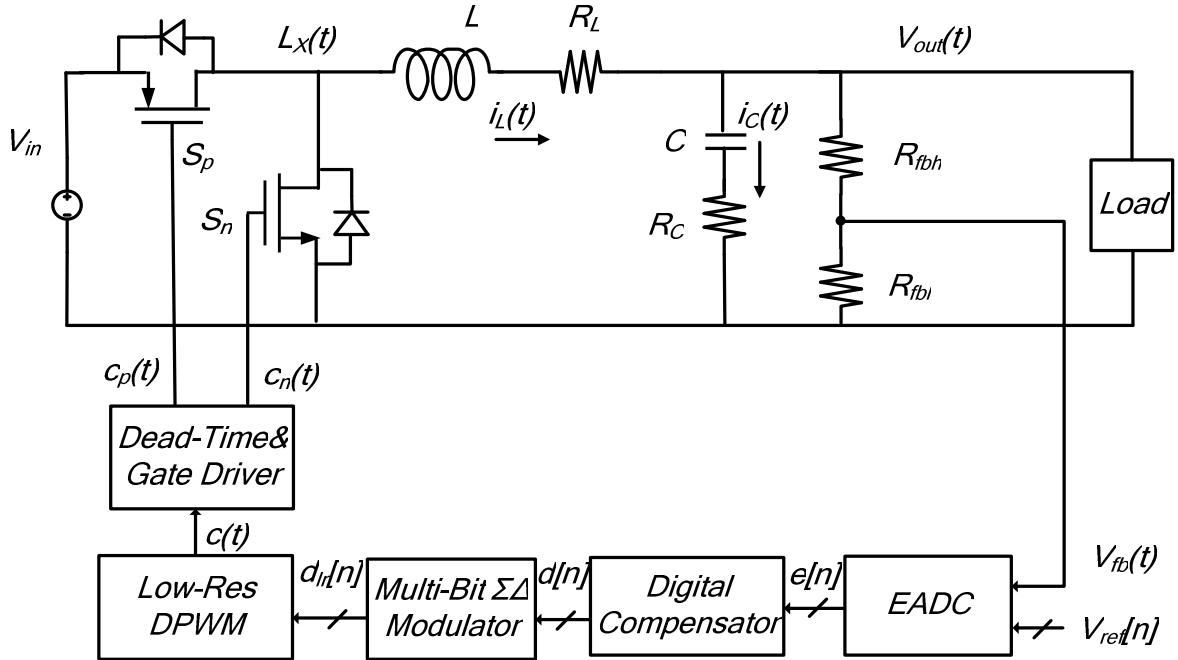

在這邊介紹一下數位直流-直流降壓電路基本架構及操作原理[6, 7]，如下圖 11 所示數位降壓電路跟類比降壓電路的動作原理其實是一樣的，經由鎖住參考電壓，達到所需要的輸出電壓。在這邊可以看到數位降壓電路所包含的方塊電路有功率區塊、類比數位轉換器、數位控制補償器以及數位脈波寬度調變。整個系統的動作為輸出電壓經由一衰減器，所得到的回授電壓經由類比數位轉換器得到數位碼，將會和參考碼  $V_{ref}[n]$  作相減的動作，所得到的誤差信號  $e[n]$  將會進入數位補償電路，此數位補償電路在類比補償電路當中則為放大器、補償電阻及電容所組成的。在數位補償電路當中可以使用正反器及其邏輯閘來合成。經由數位補償電路所出來的值為  $d[n]$ ，則是脈波寬度調變的工作週期比值(duty-ratio)，最後則是產生  $c_p(t)$  及  $c_n(t)$  脈波寬度調變進入功率區塊對電感電容充放電進而達到降壓的效果。

圖 11. 數位直流-直流降壓電路方塊圖 [7]

### 2.1.4 類比數位轉換器

在整個數位降壓電路當中，類比數位轉換器[7]所扮演的角色則是它們的溝通介面，可以由下圖 12 觀察，在每一次類比數位轉換器取樣輸出電壓經由衰減器  $K_{div}$  的值轉換為數位的碼之後，將和我們的參考電壓碼作相減動作，所得到的誤差值  $e[n]$  將是我們進入補償器重要的資訊。

圖12. 誤差類比數位轉換器、數位補償器及數位脈波寬度[7]

類比數位轉換器的輸入動態範圍對整個系統則是相當重要，它的輸入動態範圍必須要能容忍輸出電壓經由衰減器後的電壓值，當輸出在鎖定參考電壓或負載被抽載時才能有效的將輸出電壓的取樣回授到系統當中。另外一議題則是如何決定類比數位轉換器的解析度[8]，我們可以觀察式子(2.9)， $n_{A/D}$  表示類比數位轉換器的位元數， $\Delta V_q$  則是類比數位轉換器的最低位元解析度。整體數位降壓電路必須滿足此式子， $K_{div}$  則是輸出的衰減器， $\Delta V_{out}$  則是輸出上能容忍的漣波大小。

$$n_{A/D} = \log_2 \left( \frac{V_{A/D\_max} - V_{A/D\_min}}{\Delta V_q} \right) \quad (2.9)$$

$$\Delta V_q \geq K_{div} \cdot \Delta V_{out} \quad (2.10)$$

接下來討論切換雜訊對類比數位轉換器的影響，我們可以知道類比數位轉換器是在對輸出電壓作取樣，前面討論到的都是在穩態當中將輸出電壓當作是直流電壓取樣，但在實際當中如圖 13 所示，可以發現在每一週期切換時，都會有切換的雜訊所產生，此

切換雜訊則是由寄生的電容在開關切換時經由耦合所產生的尖波(Spike)。當類比數位轉換器取樣到切換雜訊，此時回授到數位補償器的誤差值將會變動的很激烈，進而影響到整個系統的鎖定狀況。

圖13. 開關切換時所造成的切換雜訊[6]

在此數位降壓電路系統可以採用窗型類比數位轉換器(Window ADC)[6, 7, 9, 10]下

1896

圖 14 為窗型類比數位轉換器輸入及輸出的轉換圖，它在數位直流-直流降壓電路有三個優點，第一優點由於它的作法是將誤差類比數位轉換器(EADC)後面再加個編碼，編碼過後的誤差  $e[n]$  將會限制在  $-4 \sim +4$  之間，也就是當誤差類比數位轉換器輸出的值超過  $+4$  或  $-4$  時將它會飽和掉，由於誤差類比數位轉換器的輸出只有  $-4 \sim +4$ ，故後面那一級的數位補償器可以減少很大的面積成本及計算的功率消耗。第二優點則是在數位直流-直流降壓電路可以省去緩啟動(Soft Start)電路，在類比直流-直流轉換器中會在代差參考電壓(Bandgap)做緩啟動，使代差參考電壓慢慢的上升，因此脈波寬度調變才不會一開始就是全開狀態使得電感上的電流及輸出電壓暴衝，窗型類比數位轉換器也等同於這一原理，在電路剛啟動時誤差量  $e[n]$  為  $+4$  經由數位補償器之後所產生的脈波寬度則是慢慢增大其功能等效於緩啟動。第三優點則是可以減少切換頻率雜訊對系統的影響，在這邊將每一誤差的量化  $\Delta V_q$  設計不等距離，當取樣到有切換頻率雜訊時，誤差可以由之前的非常大到現在設計的  $-1$  或  $+1$ ，對數位補償器來說雜訊的敏感度降低了。

圖14. 窗型類比數位轉換器輸入及輸出轉換圖[6]

### 2.1.5 數位正比積分微分控制器（PID）補償器

數位補償器[11]在整體數位降壓電路其功能等同於類比的補償器，但兩者的設計方式不一樣。類比的作法是將輸出電壓經由衰減器後和參考電壓經由放大器和補償電容及電阻出來的連續  $e(t)$  訊號，經由和鋸齒波比較產生脈波。而數位補償器的作法則時將誤差類比數位轉換器的輸出  $e[n]$  經由數位補償器計算出  $d[n]$ 。

在這邊將使用離散的控制法[12]藉由類比的補償轉移函式轉換為數位的正比積分微分控制器。首先設計時我們會將類比直流-直流降壓電路整個系統還沒加上類比補償電路的轉移函式導出來，先評估整個系統在開迴路想達到的單位頻寬增益(Unit Gain Bandwidth)及相位邊界(Phase Margin)。式子(2.11)可看到使用正比積分微分控制器，在低頻加入一個極點使系統的穩態誤差變小，而零點可以補償系統的相位邊界。

$$G_c(s) = \frac{D(s)}{E(s)} = \frac{1 + \frac{s}{Q_c \omega_z} + \frac{s^2}{\omega_z^2}}{s} \quad (2.11)$$

當類比的補償轉移函式  $G_c(s)$  導出來之後，將  $s$  平面轉到  $z$  平面上。在數位的控制系統[12]或數位訊號處理[13]的書上有提到我們可以利用尤拉規則(Eular's Rule)、雙線性轉移(Bilinear Transform)或零極點映射(ZPM)，即可達到  $z$  平面上轉移函式，如下式(2.12)是由  $G_c(s)$  轉為  $G_c(z)$ 。

$$G_c(z) = \frac{D(z)}{E(z)} = \frac{a + bz^{-1} + cz^{-2}}{1 - z^{-1}} \quad (2.12)$$

當設計出在  $z$  平面上的轉移函式，可知道在  $z$  平面上對應到時間平面上它是離的訊號。接下來則是將  $G_c(z)$  轉為到離散時間如下式(2.13)所表示。可觀察到  $e[n]$  為誤差類比數位轉換器的誤差值，而  $e[n-1]$  及  $e[n-2]$  則是  $e[n]$  上一個及上上一個狀態值。 $d[n]$  則是我們系統脈波寬度工作週期比值，而  $d[n-1]$  則是上一個狀態值。

$$d[n] = d[n-1] + a \cdot e[n] + b \cdot e[n-1] + c \cdot e[n-2] \quad (2.13)$$

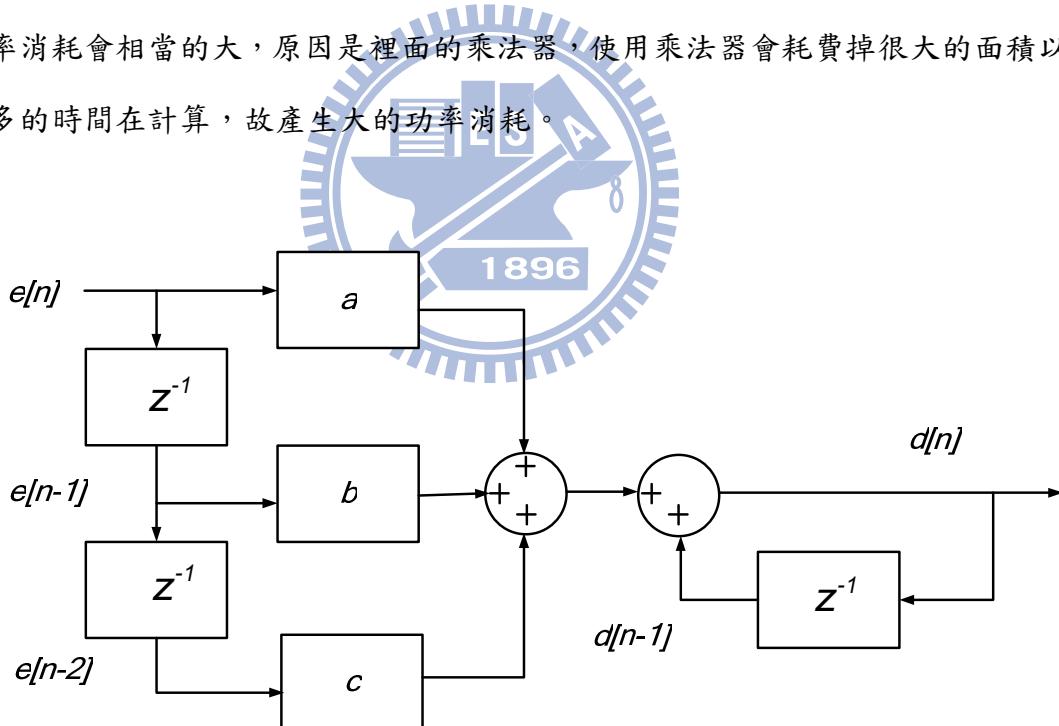

當設計出直接形式(Direct Form)，接下來就是將它實現為電路，可以發現在式子(2.13)當中需要的數位元件當中有 D 型正反器、乘法器及加法器。我們可以將式子(2.13)由圖 15 所表示。可以看到圖當中需要三個乘法器達到  $a \cdot e[n]$ 、 $b \cdot e[n-1]$  及  $c \cdot e[n-2]$ ，三個 D 型正反器達到儲存上一個狀態值，最後則是加法器。這邊可以看到一個相當嚴重的問題則是功率消耗會相當的大，原因是裡面的乘法器，使用乘法器會耗費掉很大的面積以及耗費很多的時間在計算，故產生大的功率消耗。

圖 15. 數位補償器方塊圖[6]

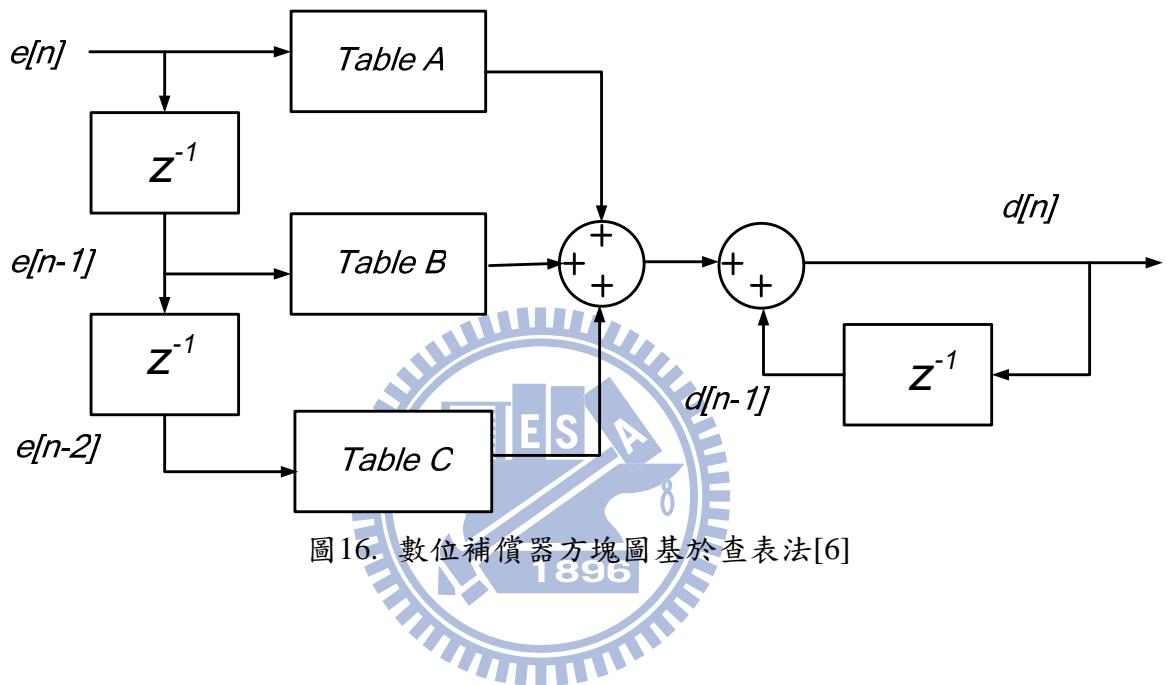

故這邊採用查表法(Look Up Table)[7, 14]如圖 16 所示的方式來取代圖 15 的乘法器，所謂的查表法則是說表格裡面已經儲存了所有輸入會發生的可能性，每一輸入值將會對應到一個輸出值，舉例來說圖 16 裡面的 Table A 他表格裡面所包含地資訊為  $a \cdot e[n]$ ，不管輸入  $e[n]$  為什麼值，它能相當快的對應出一輸出值，故這非常適合在高速及低功率

的應用中，唯一的缺點它需要大的面積。但在我們這整個系統的設計當中，由於前一級我們是採用窗型類比數位轉換器，所以我們的誤差訊號  $e[n]$  是介於 -4~+4 之間，使用查表法我們的輸入只有九種狀態，查表裡面所需的面積即可大大的減少。

圖 16. 數位補償器方塊圖基於查表法[6]

## 2.1.6 數位脈波寬度調變(DPWM)

在這邊所看到的數位脈波寬度調變在整個數位控制系統當中的功用是將離散的訊號轉為連續訊號，也就是將前一級數位補償電路輸出的工作週期控制訊號  $d[n]$  轉為連續的脈波寬度訊號  $c(t)$  如圖 17 所示。在這邊我們探討一下  $d[n]$  對輸出  $V_{out}(t)$  的影響是什麼，在前面的章節有提輸入電壓  $V_{in}$  於輸出電壓  $V_{out}(t)$  關係由式子(2.1)表示，在數位降壓電路的系統當中  $d[n]$  於  $D$  兩者是可以相應對的如下式(2.14)， $N_{dpwm}$  為數位脈波寬度調變的位元數而  $\Delta d$  為它的解析度，當  $N_{dpwm}$  趨近於無限大時數位脈波寬度調變就等同於類比脈波寬度調變。當得知  $d[n]$  於  $D$  的關係式之後，我們可以代換過去式子(2.1)，而得到式子(2.16)。

$$D = \frac{d[n]}{2^{N_{dpwm}}} \quad (2.14)$$

$$\Delta d = \frac{1}{2^{N_{dpwm}}} \quad (2.15)$$

$$V_{out}(t) = V_{in} \cdot \frac{d[n]}{2^{N_{dpwm}}} \quad (2.16)$$

圖 17. 數位類比轉換圖

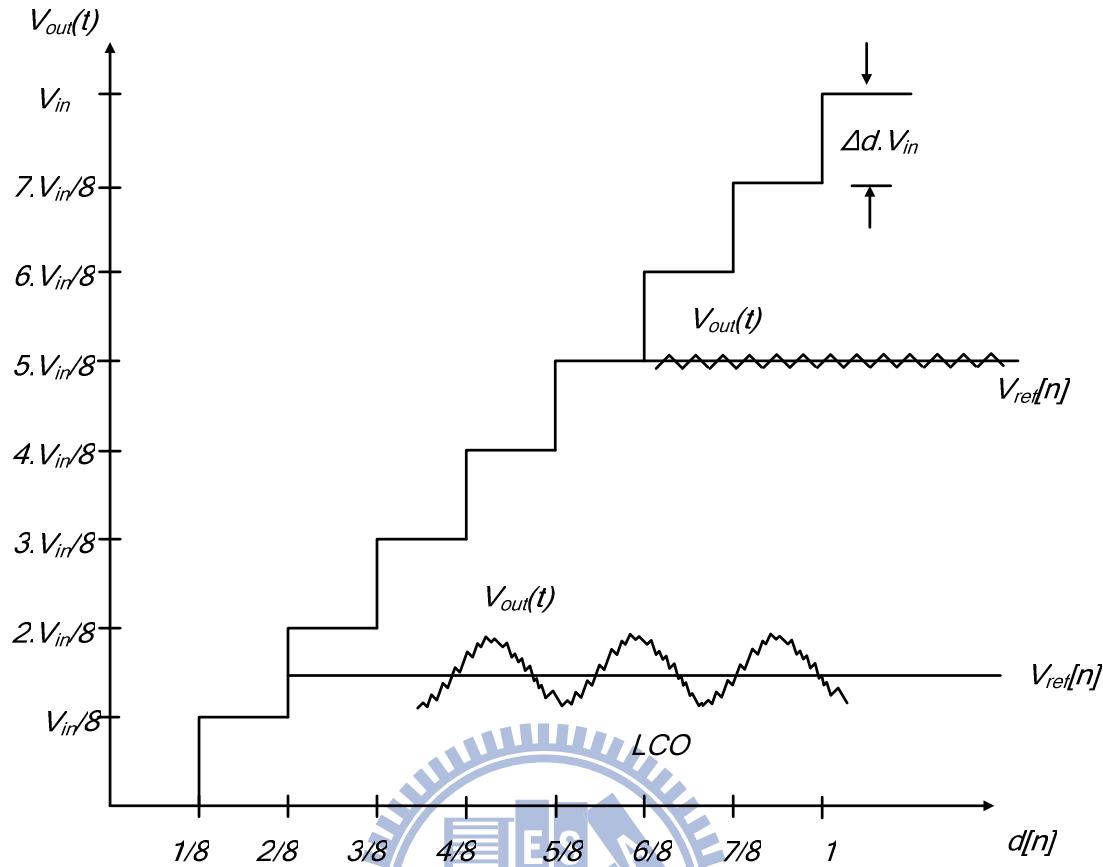

這邊討論一下數位脈波寬度調變的解析度[15, 16]要如何決定，當解析度不足時對系統的影響又會是如何。如下圖 18 所示，我們假設  $N_{dpwm}$  為三個位元，我們可以得到  $d[n]$  會有八種狀態故可以看到輸出將會在這八種狀態內變化， $d[n]$  對輸出  $V_{out}(t)$  的解析度為  $\Delta d \cdot V_{in}$ ，而類比數位轉換器的解析度為  $\Delta V_q$ ，在這邊我們假設  $\Delta d \cdot V_{in} \cdot K_{div} > \Delta V_q$ 。接下來舉例兩種狀況來討論，第一種狀況如下圖所示我們的參考碼  $V_{ref}[n]$  剛好給在  $\frac{5V_{in}}{8}$ ，當整個系統的補償器設計的恰當時，經由鎖定時  $d[n]$  的值會為  $\frac{5}{8}$  而所對應到的輸出  $V_{out}(t)$  也會是  $\frac{5V_{in}}{8}$ ，此時會如圖所式輸出  $V_{out}(t)$  會鎖在  $V_{ref}[n]$  上。

圖18. 脈波工作週期解析度與輸出電壓關係圖[6]

第二種狀況則是當參考碼  $V_{ref}[n]$  是介於  $\frac{V_{in}}{8} \sim \frac{2V_{in}}{8}$ ，可以發現當輸出  $V_{out}(t)$  在對  $V_{ref}[n]$  鎮定時，一開始的  $V_{out}(t)$  值小於  $V_{ref}[n]$  經由誤差類比數位轉換器產生出一正的誤差  $e[n]$  進入數位補償器出來的  $d[n]$  則會變大而輸出將會繼續充電上去，由於  $d[n]$  每加一格上去對輸出電壓則是上升  $\frac{V_{in}}{8}$ ，因此輸出電壓充電會大於  $V_{ref}[n]$ ，經由誤差類比數位轉換器產生出一負的誤差  $e[n]$  進入數位補償器出來的  $d[n]$  則會變小一格，因此輸出將會放電  $\frac{V_{in}}{8}$ ，如此一日復一日就產生所謂的環形震盪(Limit Cycle Oscillations)造成輸出  $V_{out}(t)$  有一個震盪存在。會產生這一震盪主要是因為數位脈波寬度調變的解析度  $\Delta d \cdot V_{in}$  大於類比數位轉換器的解析度  $\Delta V_q$ ，所以在每一週期充放電時才會產生這種狀況，故數位脈波寬度調變的解析度可由式子(2.17)來決定。

$$\Delta d \cdot V_{in} \cdot k_{div} < \Delta V_q \quad (2.17)$$

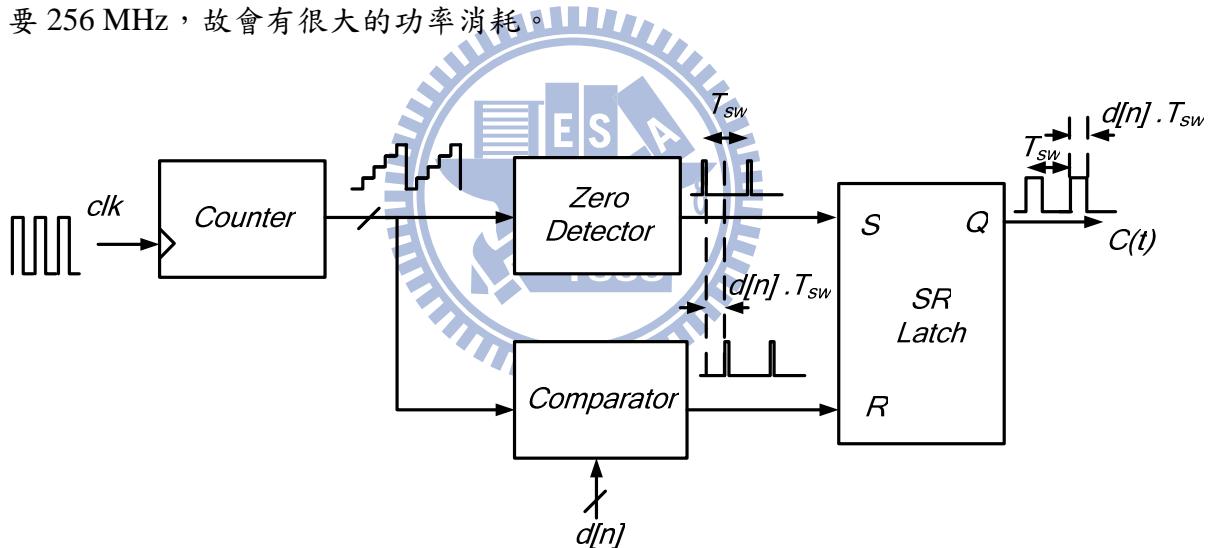

接下來要介紹及比較幾種數位脈波寬度調變[17]的電路，第一種介紹如下圖 19 所示為計數器模式數位脈波寬度調變(Counter Based DPWM)，它主要是由一計數器、零值偵測、比較器及 SR 拾鎖器所組成的。它的動作原理為一開始計數器為零值經由零值偵測會給 SR 拾鎖器的 S 端為高的準位，此時 SR 拾鎖器的輸出 Q 的訊號為高的準位。當計數器開始累加時 Q 的訊號會維持直到計數器的值累加到跟  $d[n]$  一樣時再經由比較器輸出給 SR 拾鎖器的輸入 R 高的準位，此時輸出 Q 的訊號為低的準位進而達到數位脈波寬度調變。計數器模式數位脈波寬度調變它的動作模式其實跟類比的脈波寬度調變是非常的像的，這邊可以將計數器的輸出看成像是再類比的鋸齒波產生器一樣，使用  $d[n]$  的值來跟它做比較產生脈波寬度調變。在這邊可以發現這電路需要非常高的時脈以及很大的功率消耗，舉例來說當系統頻率  $F_{sw}$  為 1MHz， $d[n]$  為八位元，此時計數器的外部時脈需要 256 MHz，故會有很大的功率消耗。

圖19. 計數器模式數位脈波寬度調變[6]

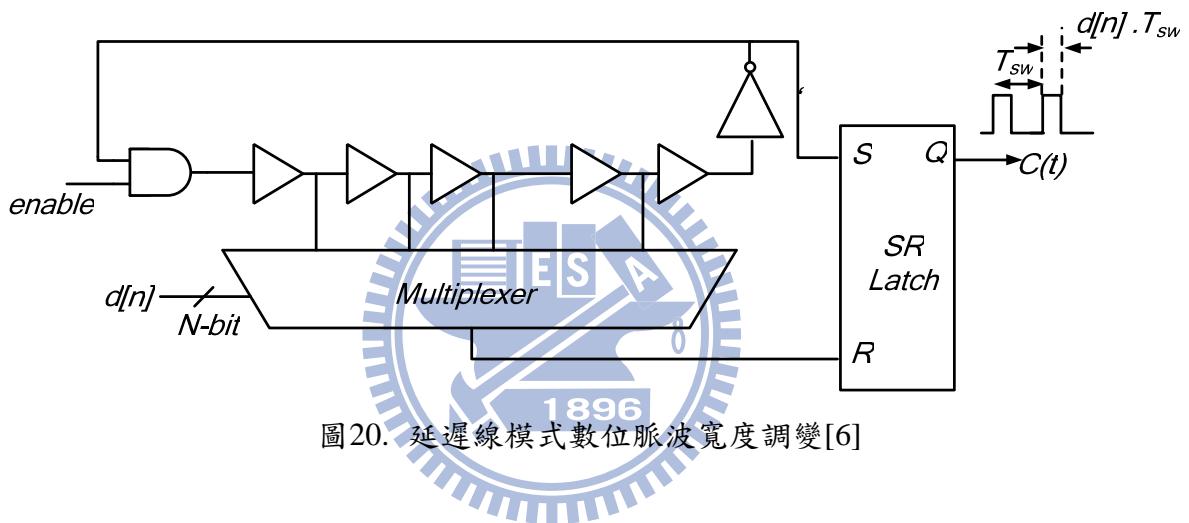

第二種介紹的數位脈波寬度調變的電路為延遲線模式數位脈波寬度調變( Delay Line Based DPWM)如下圖 20 所示，它是由一大串的延遲元件及一組多工器和 SR 拾鎖器所組成的，其動作原理為當致能訊號為低準位時，整串的延遲元件都會為低準位，此時電路為低功率消耗。當致能訊號為高準位時，我們可以發現這一串的延遲元件加上一反向器形成一震盪器，電路一開始時 SR 拾鎖器的 S 端為高的準位，此時 SR 拾鎖器的輸出 Q 的訊號為高的準位，接下來這一串的延遲元件就發揮它的功能，每延遲元件的輸

出接到多工器的輸入，等效來看多工器每一級的輸入互相都是相位偏移，當多工器的輸入為高準位在相位移動剛好為選擇腳所選擇的輸入時，此時多工器的輸出將為高準位，也就是 SR 捏鎖器的輸入 R 高的準位，此時輸出 Q 的訊號為低的準位進而達到數位脈波寬度調變。我們可以發現延遲線模式數位脈波寬度調變會比計數器模式數位脈波寬度調變擁有較低的功率消耗，因為他不需要一外部的時脈驅動，但相較之下由於它是由延遲元件所組成的，故他對於製程或溫度的變化相當敏感，可能會造成系統頻率的漂移，除此之外它需要非常大的晶片面積。

圖 20. 延遲線模式數位脈波寬度調變[6]

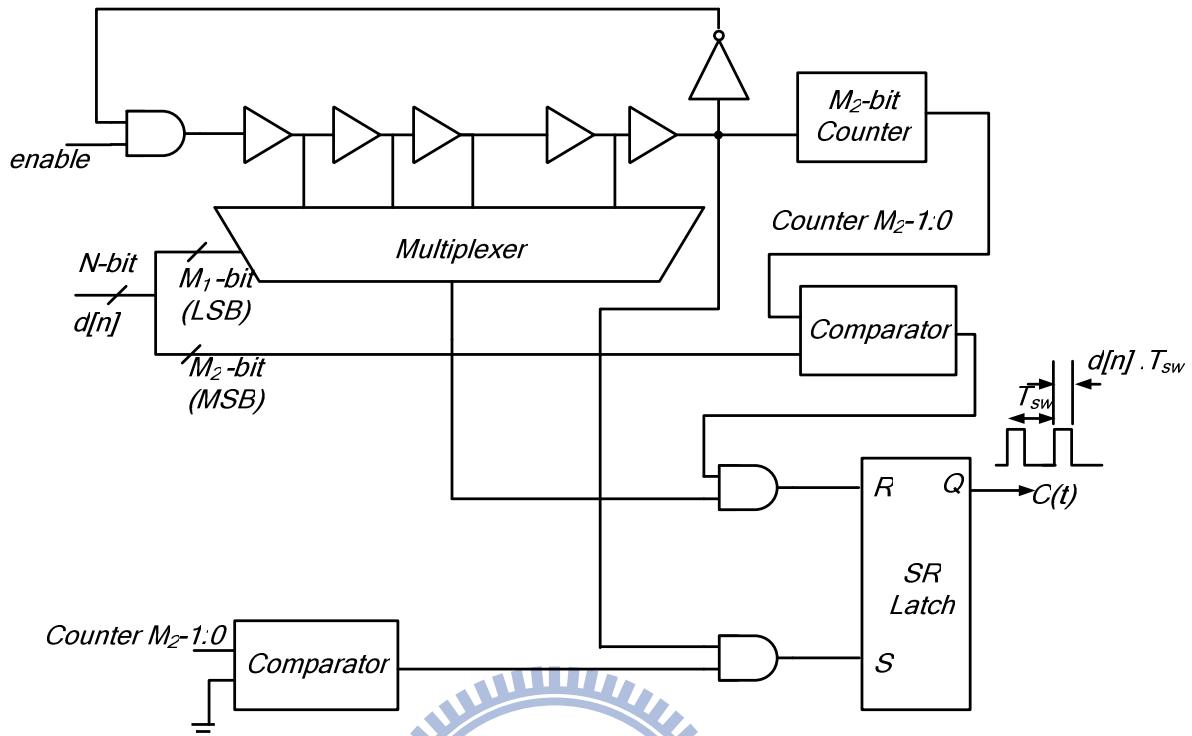

第三種介紹的則是混合計數延遲線模式數位脈波寬度調變電路(Hybrid Counter-Delay Line DPWM)如下圖 21 所示。它其實是結合了計數器模式和延遲線模式，這邊可以將  $d[n]$  位元數拆成兩部份，分別為低位元  $M_1$ -bit 及高位元  $M_2$ -bit.。 $M_1$ -bit 則為多工器的選擇腳，每當延遲元件相位移動一圈的時候  $M_2$ -bit 計數器會累加 1， $M_2$ -bit 計數器的輸出則會和  $M_2$ -bit 做比較，進而達到脈波寬度的調變。混合計數延遲線模式數位脈波寬度調變的電路它的功率消耗會比計數器模式還要低，它所需要的面積小於延遲線模式，故它是介於這兩者之間。

圖21. 混合計數延遲線模式數位脈波寬度調變電路[6]

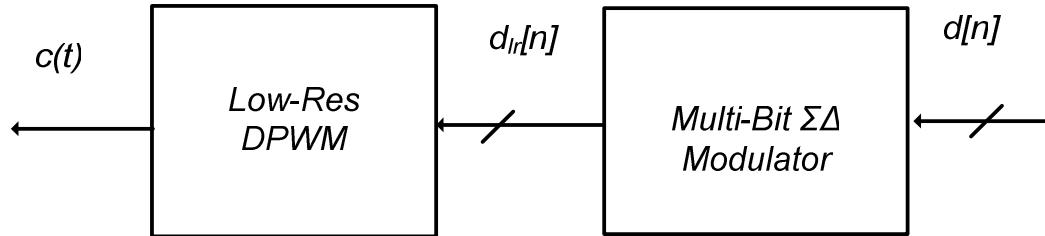

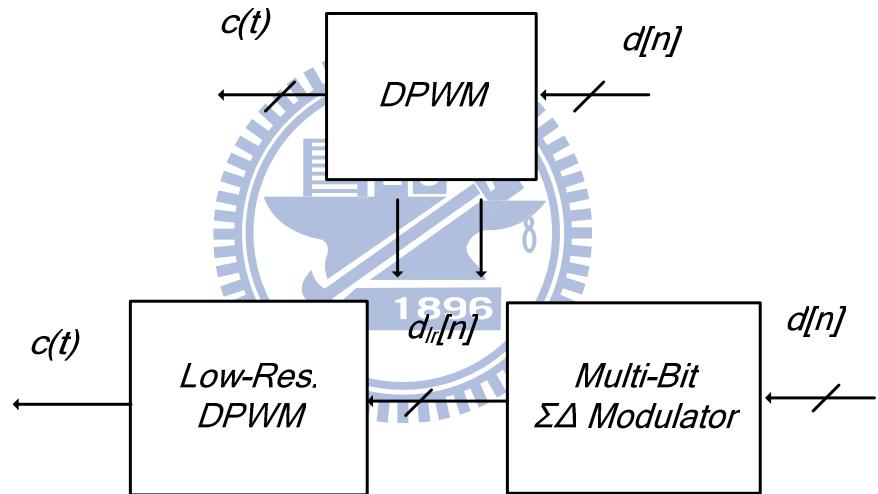

第四種介紹的是 $\Sigma\Delta$ 數位脈波寬度調變電路( $\Sigma\Delta$ -DPWM)如下圖 22 所示，它是由多位元的 $\Sigma\Delta$ 調變器加上一低解析度的數位脈波寬度調變電路，這低解析度的數位脈波寬度調變電路可以由計數器模式或延遲線模式的數位脈波寬度調變電路來組成。可以看到之前所提到的計數器模式數位脈波寬度調變電路需要額外高速的時脈，並且有很大的功率消耗，而延遲線模式的數位脈波寬度調變電路則是需要很大的晶片面積，並且容易受到製程及溫度的影響。當系統希望操作在高速及低功率消耗時則可採用 $\Sigma\Delta$ 數位脈波寬度調變電路。舉例來說這邊的低解析度的數位脈波寬度調變電路要是由計數器模式組成的話舉例說可以由  $d[n]$  八位元變成  $d_L[n]$  四位元，外部的時脈可以減少十六倍，大大減少功率消耗及晶片的面積。但必須討論的是 $\Sigma\Delta$ 數位脈波寬度調變電路裡面要低解析度的數位脈波寬度調變電路要是由計數器模式來取代，也就是說解析度會從原本的八位元變成四位元，這樣對輸出會造成很大的影響。故在低解析度的數位脈波寬度調變電路前一級加上多位元的 $\Sigma\Delta$ 調變器，我們知道 $\Sigma\Delta$ 調變器其中一個主要的精神則是平均，我們則是

利用這平均的概念，將原本八位元的  $d[n]$  經由  $\Sigma\Delta$  調變器經由多個週期之後的平均，可以由四位元的  $d_{lr}[n]$  來表示。

圖22.  $\Delta\Sigma$  數位脈波寬度調變電路[6]

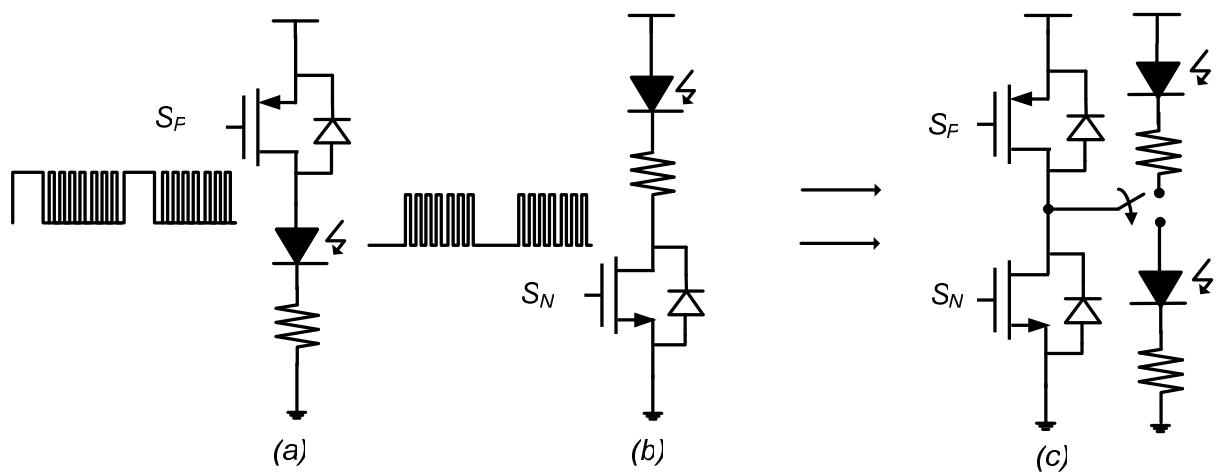

## 2.2 LED 及馬達基本操作原理

如下圖 23 所示為操作 LED 的基本原理，LED 最主要是則是亮度的控制，這邊可以知道 LED 為電流控制的元件，當流過電流越大 LED 的亮度則會越亮，故可使用脈波寬度調變達到亮度、閃爍頻率及亮度時間控制。圖 23 (a) 及圖 23 (b) 分別為使用 P 及 N 功率晶體來驅動 LED，這此論文當中採用圖 23 (c)，我們可以經由控制指令達到圖 23 (a) 及圖 23 (b) 的效果。

圖23. LED 操作電路圖

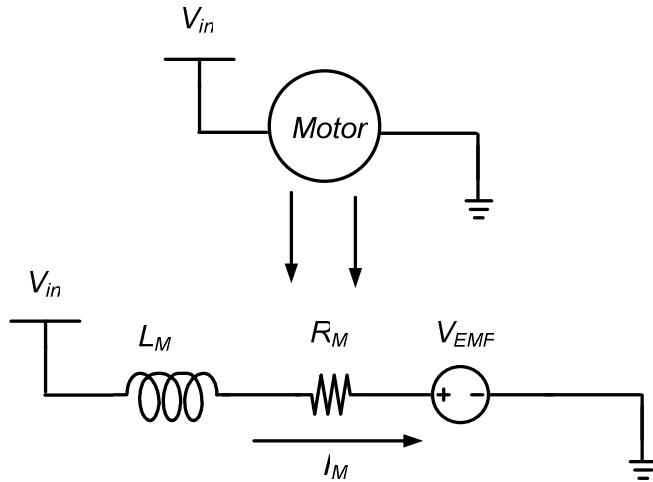

如下圖 24 所示為直流馬達的等效模型[18]，它由一線圈電感( $L_M$ )、線圈電阻( $R_M$ )及一反電動勢( $V_{EMF}$ )所組成。

圖24. 馬達等效模型[18]

我們可以將馬達的動作拆為電子與機械模式來看， $I_M$  為馬達上的電流， $K_{emf}$  為轉速常數， $\omega$  為馬達的角速度， $T$  轉矩大小， $K_T$  為轉矩常數， $J$  為馬達和驅動負載的慣性量。由式子(2.18)~(2.21)可以知道當  $V_{in}$  電壓越大馬達的轉速越快，馬達上的反電動勢就越大，故馬達上的電流就很小，也就是說只需要一點點的電流就可以使馬達轉的很快。由式子(2.18)~(2.21)來看當將馬達的負載加到很大，它的轉速變為零，反電動勢電壓也為零，此時電壓全降在線圈電阻上，馬達上的電流會變很大，有可能會使馬達燒壞。

$$V_{in} = L_M \cdot \frac{dI_M}{dt} + I_M \cdot R_M + V_{EMF} \quad (2.18)$$

$$V_{EMF} = K_{emf} \cdot \omega \quad (2.19)$$

$$T = K_T \cdot I_M \quad (2.20)$$

$$T = J \cdot \frac{d\omega}{dt} + B \cdot \omega \quad (2.21)$$

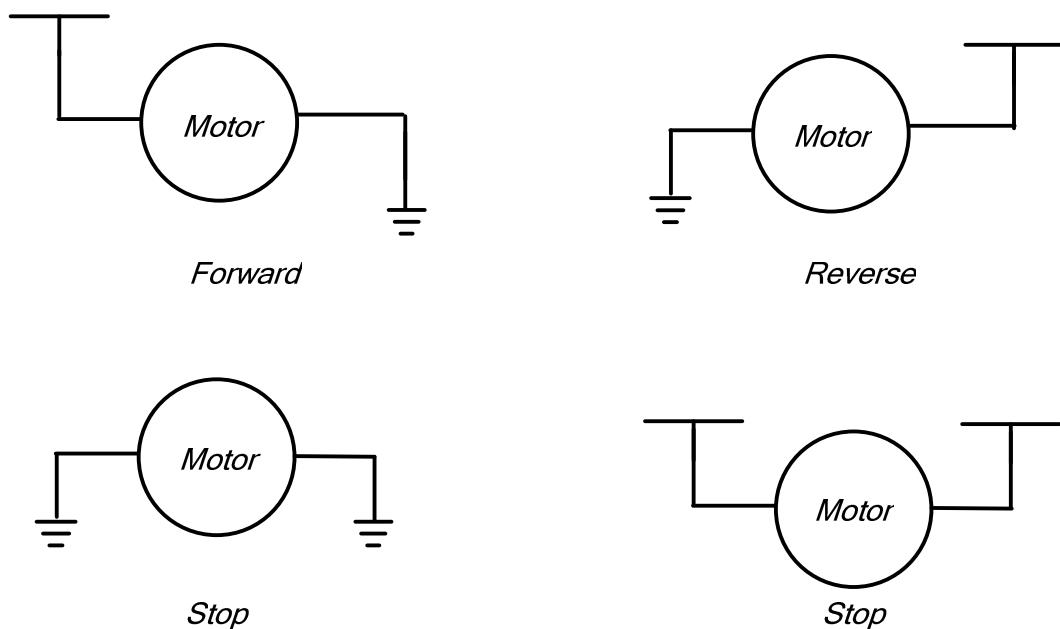

這由上式(2.18)~(2.21)可以知道驅動馬達的轉速是取決於它上面的跨壓大小。如下圖所 25 示為馬達正轉、反轉、即停止的表示圖。我們可以使用 H 橋模式[18]如下圖 26 所示來達到正反轉及停止，由於馬達是電壓控制，我們亦可使用脈波寬度調變來調整馬達上的跨壓，進而達到轉速的控制。

圖25. 馬達轉向示意圖

圖26. H 橋驅動馬達[18]

# 第三章

---

## 可程式車用功率積體電路設計

在這一章節當中一開始先介紹可程式車用功率積體電路整體系統的設計，如何達到可程式化應用以及整合馬達、LED 及降壓電路。接下來制定數位降壓電路的規格，當規格制定好之後進入數位降壓電路裡面的方塊圖，在數位脈波寬度調變探討一階及二階  $\Delta\Sigma$  調變，在誤差類比數位轉換器區塊決定它的解析度，最後數位補償器設計經由類比補償器 s 平面設計完之後再映射到 z 平面。

### 3.1 驅動晶片系統設計及規格制定

#### 3.1.1 可程式車用功率積體電路系統設計

在整個車用功率積體電路當中，每一顆驅動晶片上面會有四組的輸出訊號，每一組輸出訊號可以推動一組開關由 P 及 N 型的功率電晶體所組成，由第一章節可以看到每一組的輸出訊號可以控制馬達、LED 及降壓電路如下圖 27 所示。在這邊我們可以知道馬達、LED 及降壓電路它們都是經由脈波寬度調變來調整轉速、亮度及輸出電壓大小。前一章節介紹了許多數位脈波寬度調變的電路，這邊採用是  $\Sigma\Delta$  數位脈波寬度調變電路如圖 28 所示來當作可程式車用功率積體電路裡面的數位脈波寬度調變的電路，在此系統應用當中有幾個優點，第一它是由多位元的  $\Sigma\Delta$  調變電路加上一低解析度的數位脈波寬度調變的電路，故具有高速及低功率及的優點。第二則是可以使馬達、LED 及降壓電路共同使用，前面提到的幾種數位脈波寬度調變的電路只有計數器模式和  $\Sigma\Delta$  調變模式可以讓它們共同使用，計數器模式太耗功率，故我們採用  $\Sigma\Delta$  數位脈波寬度調變電路。

圖27. 整合馬達、LED 及降壓電路

圖28. 數位脈波寬度調變電路採用  $\Delta\Sigma$  調變[9]

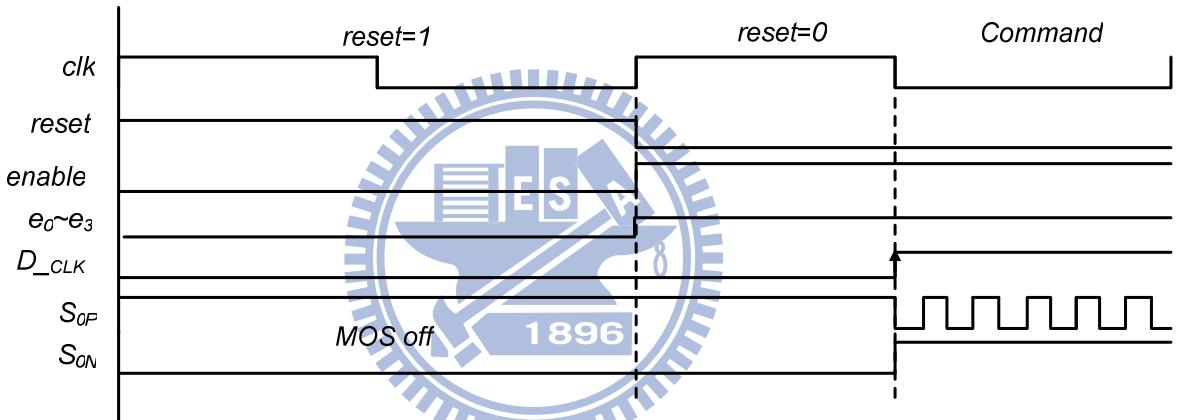

如下圖 29 所示為整個可程式車用功率積體電路的架構圖，它是由一解碼器、拴鎖器及一控制電路組成，整個架構的時間流程圖為圖 30 所示，一開始我們會將系統做重置的動作，使所有的數位元件都清除，輸出給功率晶體的訊號都為關閉。當指令傳過來的時候，首先會經由解碼器先確定是否為這一顆晶片動作，當確定為這一顆晶片動作時，接下來指令會進入系統當中並且指定要哪一組開關動作，此時指令會經由拴鎖器把資料給鎖住在指定的那一組開關內再經由控制電路最後則產生輸出脈波寬度調變訊號。控制電路則是由  $\Sigma\Delta$  數位脈波寬度調變電路、數位降壓電路及一些數位元件，例如像多工器、邏輯閘所組成的。

圖29. 可程式車用功率積體電路系統

圖30. 可程式車用功率積體電路系統時間流程圖

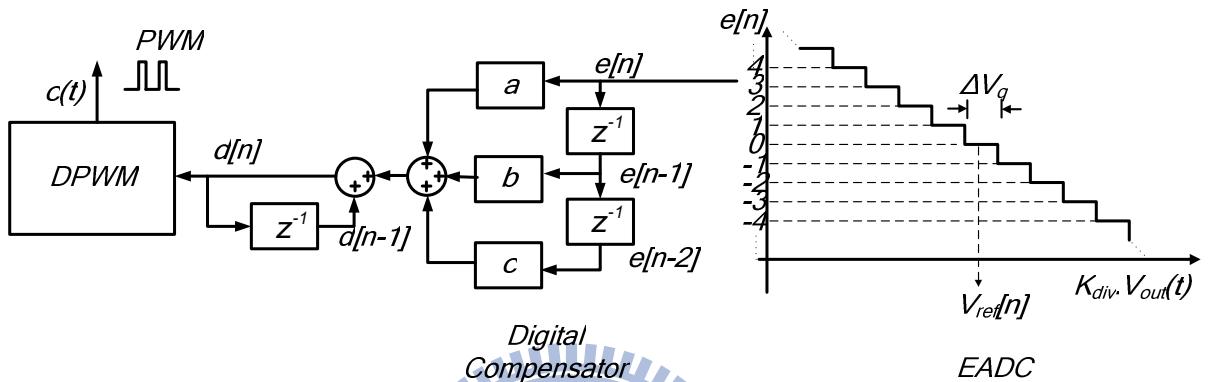

### 3.1.2 規格制定

整體數位降壓電路如圖 31 所示，它是由功率區塊、誤差類比數位轉換器、數位補償器、 $\Delta\Sigma$  數位脈波寬度調變電路以及死區時間(Dead Time)所組成。在這一章節我們制定整個數位降壓電路的規格如表 2 所示，在車用電子裡面所蓄電池提供的電壓為 12V，故輸入  $V_{in}$  為 12V，而輸出電壓  $V_{out}(t)$  為較常用到的 1.5~9V，抽載的電流定在 0~2A。在車用電子裡面系統切換頻率大概為 100~500kHz，在這邊我們配合 FPGA 板子所提供的最高時脈除頻下來，我們切換頻率  $F_{SW}$  為 390.625kHz。這邊輸出的漣波大小我們設計小於 1.5 V 的 6%，故  $\Delta V_o$  大約為 100mV。前面式子(2.10)提到，故誤差類比數位轉換器的  $\Delta V_q$  經由編碼為 58.6 mV。

圖31. 直流-直流降壓電路系統方塊圖[6]

接下來決定數位脈波寬度調變的解析度，為了避免輸出有 LCO，由式子(2.17)可以知道，通常設計都小於 3~6 倍，故這邊設計數位脈波寬度調變的解析度為 9 位元。電感及電容值為  $22\mu$  可以由式子(2.3)~(2.8)計算輸出電感上電流漣波及輸出電壓漣波算出。

表2. 數位降壓電路的規格如表所示

| Parameter              | Symbol       | Value   | Units     |

|------------------------|--------------|---------|-----------|

| Input Voltage          | $V_{in}$     | 12      | V         |

| Output Voltage         | $V_{out}$    | 1.5~9   | V         |

| Load Current           | $I_{load}$   | 0~2     | A         |

| Switch Frequency       | $F_{sw}$     | 390.625 | kHz       |

| Output Voltage Ripple  | $\Delta V_o$ | 100     | mV        |

| EADC Quantization Step | $\Delta V_q$ | 58.6    | mV        |

| DPWM Resolution        | $N_{DPWM}$   | 9       | bits      |

| Inductor               | L            | 22      | $\mu H$   |

| Capacitor              | C            | 22      | $\mu H$   |

| ESR                    | $R_C$        | 200     | $m\Omega$ |

| DCR                    | $R_L$        | 180     | $m\Omega$ |

| Zero Frequency         | $f_{ESR}$    | 36      | kHz       |

| Double Pole Frequency  | $f_o$        | 7.234   | kHz       |

| Attenuation            | $K_{div}$    | 1/2.4   |           |

## 3.2 $\Sigma\Delta$ 數位脈波寬度調變電路

這一章節主要介紹數位脈波寬度調變電路基於雜訊整形(Noise-Shaping)的概念，並且比較一階級二階的  $\Sigma\Delta$  數位脈波寬度調變電路，在後面的比較會發現一階的  $\Sigma\Delta$  會有低頻的諧波(Tones)，進而造成輸出會有類似像震盪的效果，使得輸出漣波變大。而二階的  $\Sigma\Delta$  則是可以改善這低頻的諧波，故最後系統採用二階的  $\Sigma\Delta$  數位脈波寬度調變電路。

### 3.2.1 數位脈波寬度調變電路基於雜訊整形概念

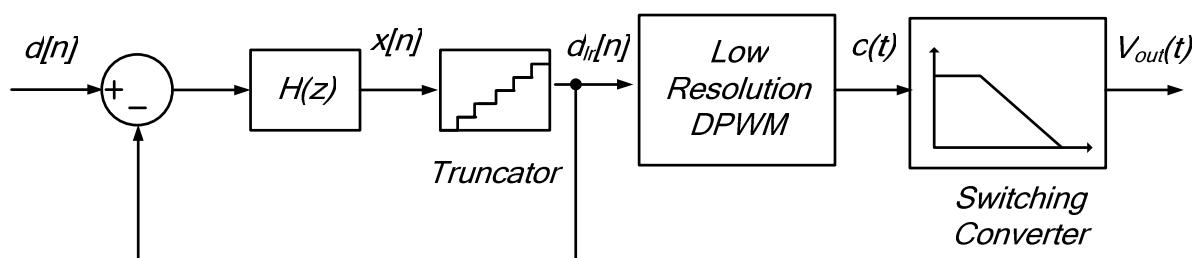

$\Sigma\Delta$  數位脈波寬度調變電路[3, 4]在最近幾年已被發表如下圖 32 所示，它是由  $\Sigma\Delta$  雜訊整形迴路及一低解析度數位脈波寬度調變電路連接到切換轉換器。在這邊可以將  $\Sigma\Delta$  雜訊整形迴路及一低解析度數位脈波寬度調變電路取代高解析度的數位脈波寬度調變電路是適合操作在低功率及高頻率的應用。另外一方面低解度的數位脈波調變電路可能會造成輸出 LCO 的問題，可以經由前一級的  $\Sigma\Delta$  雜訊整形迴路在多個週期改變  $d_{lr}[n]$ ，使它的平均等於高解析度的  $d[n]$ 。

圖32. 基本  $\Sigma\Delta$  雜訊整形迴路架構[6]

如下圖 33 所示可以看到  $e_T[n]$  為圖 32 截取器(Truncator)所產生的誤差，可以導出  $d_{lr}[n]$  對  $d[n]$  的 Z 轉換如式(3.1)。 $D(z)$  為高解析度的 Z 轉換， $E_T(z)$  為截取器所產生的誤差，這邊可以觀察到  $H(z)$  的功能可以來抑制截取器所產生的誤差。

$$D_{lr}(z) = \frac{H(z)}{1+H(z)} \cdot D(z) + \frac{1}{1+H(z)} \cdot E_T(z) \quad (3.1)$$

當  $H(z)$  的值為非常大的時候，可以看到  $E_T(z)$  被  $\Sigma\Delta$  雜訊整形迴路給抑制，此次我們可以看到  $D_{lr}(z)$  會等於  $D(z)$  如下式(3.3)。

$$D_{lr}(z)|_{H(z) \rightarrow \infty} = \frac{H(z)}{1+H(z)}|_{H(z) \rightarrow \infty} \cdot D(z) + \frac{1}{1+H(z)}|_{H(z) \rightarrow \infty} \cdot E_T(z) \quad (3.2)$$

$$D_{lr}(z)|_{H(z) \rightarrow \infty} = D(z) \quad (3.3)$$

但在實際當中  $H(z)$  在低頻時它的值才會非常大，此時高解析度的  $D(z)$  才會等於  $D_{lr}(z)$ 。 $H(z)$  會因頻率的上升，值會慢慢的下降，此時截取器所產生的誤差  $E_T(z)$  將會進入  $D_{lr}(z)$ ，使得  $D_{lr}(z)$  不等同於  $D(z)$ 。但在數位降壓電路當中，低解析度數位脈波寬度調變器的下一級為二階的低通濾波器，故可幫助抑制高頻的雜訊。

圖33.  $\Sigma\Delta$  雜訊整形迴路架構-加了雜訊[6]

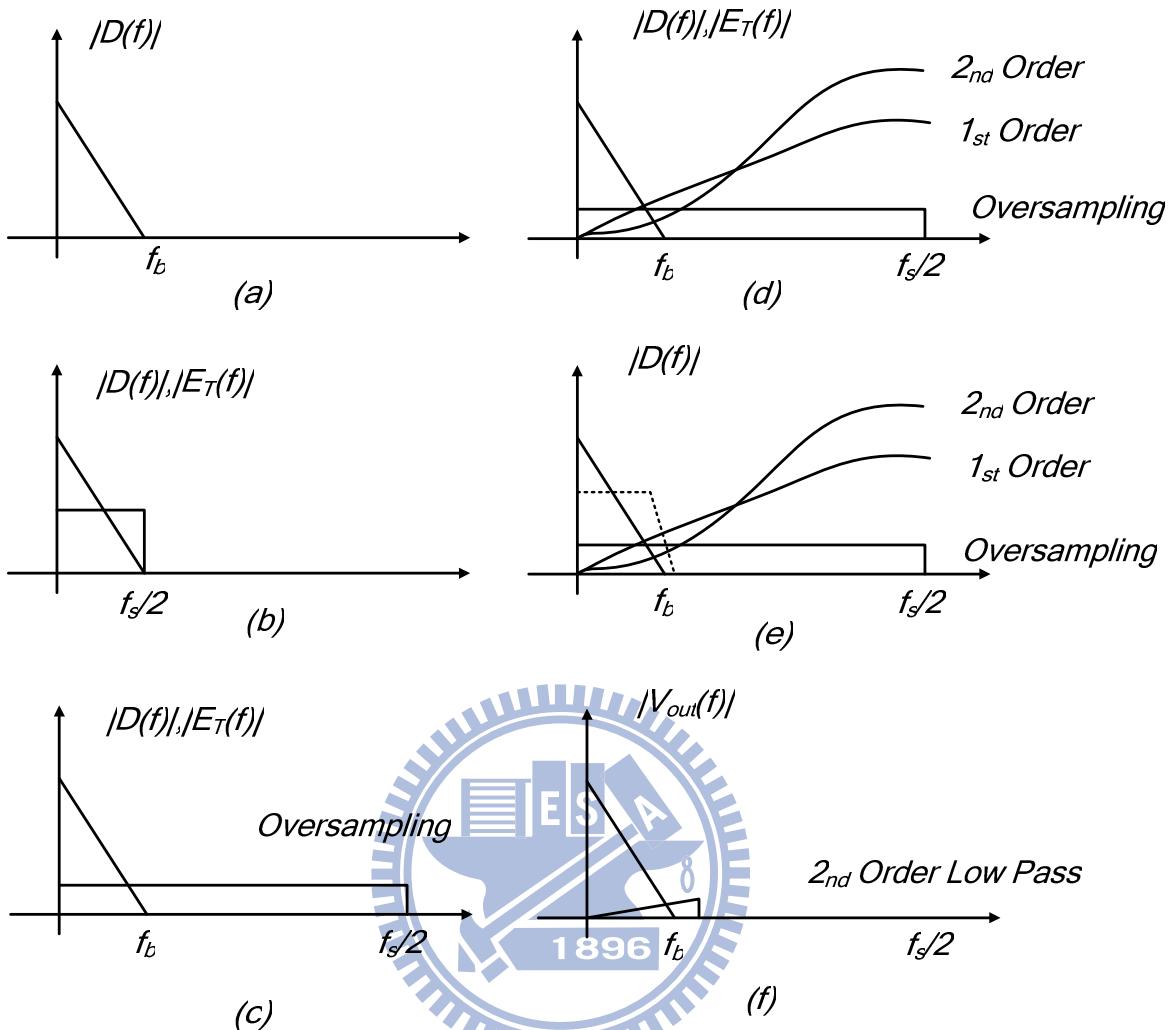

在這邊可由下圖 34 的頻譜來看出  $\Sigma\Delta$  數位脈波寬度調變電路  $d[n]$  經由雜訊整形迴路和二階的低通濾波器之後所看的輸出頻譜。一開始可以看到圖 34(a)為  $d[n]$  在頻寬  $f_b$  大小。圖 34(b)表示的是在奈式定理(Nyquist Rate)取樣下所看到的  $d[n]$  及  $e_T[n]$  頻譜大小，它的訊號雜訊比(SNR)如式(3.4)所表示，在這邊所考慮的的雜訊都是白雜訊(white noise)。

$$SNR = 6.02N + 1.76dB \quad (3.4)$$

接下來圖 34(c)所表示的為在超取樣(Oversampling)下所得到的  $d[n]$  及  $e_T[n]$  頻譜大小，這邊可以看到  $E_T(z)$  經由超取樣的技巧下整個雜訊的功率大小被壓低，平均散部在取樣頻率之下。而它的 SNR 如式(3.5)所表示。

$$SNR = 6.02N + 1.76dB + 10\log(OSR) \quad (3.5)$$

圖 34(d)所表示為經由一階及二階  $\Sigma\Delta$  雜訊整形迴路所看到的  $d[n]$  及  $e_T[n]$  頻譜大小，當  $\Sigma\Delta$  雜訊整形迴路的階數越高，雜訊會被推到越高頻。最後在經由二階的低通濾波器可以看到如圖 34(e)所示，在低通濾波器的頻寬以下，雜訊以被大大的減少，我們可以看到一階及二階的 SNR 如式(3.7)及式(3.8)所表示為

$$SNR_{1_{st}} = 6.02N + 1.76dB - 5.17 + 30\log(OSR) \quad (3.7)$$

$$SNR_{2_{nd}} = 6.02N + 1.76dB - 12.9 + 50\log(OSR) \quad (3.8)$$

最後可以看到圖(f)為輸出  $V_{out}(t)$  的頻譜，它將會追蹤高解析度  $d[n]$  的變化。

圖 34.  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變頻譜分析[6]

### 3.2.2 一階 $\Sigma\Delta$ 雜訊整型數位脈波寬度調變電路

由下圖 35 所示為基本一階  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變電路[6, 9]，在這邊可以看到  $H(z)$  可以由離散的積分所組成如式(3.9)所表示，在  $z$  為 1 時，也就是頻率為零時， $H(z)$  的值為無限大，當隨著頻率上升時  $H(z)$  的值會慢慢的下降。

$$H(z) = \frac{z^{-1}}{1 - z^{-1}} = \frac{1}{z - 1} \quad (3.9)$$

圖35. 基本一階雜訊整形迴路數位脈波寬度調變[3]

在這一章節所舉例的為 8 位元輸入的一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路，其系統動作原理為低階析度的  $d_{lr}[n]$  將回授與輸出高解析度的  $d[n]$  相減所得到的  $e_T[n]$  在經由  $H(z)$  積分器得到  $x[n]$ 。 $d_{lr}[n]$  經由幾週期之後的平均會等於  $d[n]$ 。接下來將觀察一下整體一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路的  $z$  轉換，如下式：

$$D_{lr}(z) = z^{-1} \cdot D(z) + (1 - z^{-1}) \cdot E_T(z) \quad (3.10)$$

這邊可以觀察到  $D(z)$  對  $D_{lr}(z)$  相差了一個週期，而  $E_T(z)$  對  $D(z)$  則是一高通濾波器，也就是當頻率越高時，雜訊對我們系統的影響越大。我們又可將整體的  $z$  轉換整理為如下式(3.11)， $STF(z)$  為訊號對輸出的轉移函式， $NTF(z)$  為雜訊對輸出的轉移函式。

$$D_{lr}(z) = STF(z) \cdot D(z) + NTF(z) \cdot E_T(z) \quad (3.11)$$

$$STF(z) = z^{-1} \quad (3.12)$$

$$NTF(z) = 1 - z^{-1} \quad (3.13)$$

接下來我們藉由表 3 來驗證圖一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路，在這邊我們輸入的  $d[n]$  為 8 位元，當輸出為  $d[n]=50/256=0.193$ ，可以由表 3 看到每一點的變化，這邊可以看到在  $n=9 \sim 16$  的時候， $d_{lr}[n]$  為  $0.25, 0.1875, 0.1875, 0.1875, 0.1875, 0.1875, 0.1875, 0.1875$  將這一些值取平均之後為  $0.1953$ ，可驗證之前的理論， $d_{lr}[n]$  將會經由多個週期後的平均與  $d[n]$  相同。

表3.  $d[n]$ 為50經由一階 $\Sigma\Delta$ 雜訊整形迴路所觀察到輸出  $d_{lr}[n][9]$

| n  | D  | $d[n]$ | $e_T[n]$ | $x[n+1]$ | $x[n]$ | $d_{lr}[n]$   | $d_{av}[n]$  |

|----|----|--------|----------|----------|--------|---------------|--------------|

| 1  | 50 | 0.1953 | 0.1953   | 0.1953   | 0      | 0             | 0            |

| 2  | 50 | 0.1953 | 0.0781   | 0.2031   | 0.1953 | 0.1875        | 0.0937       |

| 3  | 50 | 0.1953 | 0.0781   | 0.2019   | 0.2031 | 0.1875        | 0.125        |

| 4  | 50 | 0.1953 | 0.0781   | 0.2187   | 0.2019 | 0.1875        | 0.140        |

| 5  | 50 | 0.1953 | 0.0781   | 0.2265   | 0.2187 | 0.1875        | 0.15         |

| 6  | 50 | 0.1953 | 0.0781   | 0.2343   | 0.2265 | 0.1875        | 0.16         |

| 7  | 50 | 0.1953 | 0.0781   | 0.2421   | 0.2343 | 0.1875        | 0.164        |

| 8  | 50 | 0.1953 | 0.0781   | 0.25     | 0.2421 | 0.1875        | 0.173        |

| 9  | 50 | 0.1953 | -0.0546  | 0.1953   | 0.25   | <b>0.25</b>   | <b>0.175</b> |

| 10 | 50 | 0.1953 | 0.0781   | 0.2031   | 0.1953 | <b>0.1875</b> | <b>0.176</b> |

| 11 | 50 | 0.1953 | 0.0781   | 0.2019   | 0.2031 | <b>0.1875</b> | <b>0.177</b> |

| 12 | 50 | 0.1953 | 0.0781   | 0.2187   | 0.2019 | <b>0.1875</b> | <b>0.177</b> |

| 13 | 50 | 0.1953 | 0.0781   | 0.2265   | 0.2187 | <b>0.1875</b> | <b>0.178</b> |

| 14 | 50 | 0.1953 | 0.0781   | 0.2343   | 0.2265 | <b>0.1875</b> | <b>0.179</b> |

| 15 | 50 | 0.1953 | 0.0781   | 0.2421   | 0.2343 | <b>0.1875</b> | <b>0.179</b> |

| 16 | 50 | 0.1953 | 0.0781   | 0.25     | 0.2421 | <b>0.1875</b> | <b>0.183</b> |

| 17 | 50 | 0.1953 | -0.0546  | 0.1953   | 0.25   | 0.25          | 0.184        |

| 18 | 50 | 0.1953 | 0.0781   | 0.2031   | 0.1953 | 0.1875        | 0.184        |

| 19 | 50 | 0.1953 | 0.0781   | 0.2019   | 0.2031 | 0.1875        | 0.184        |

| 20 | 50 | 0.1953 | 0.0781   | 0.2187   | 0.2019 | 0.1875        | 0.184        |

| 21 | 50 | 0.1953 | 0.0781   | 0.2265   | 0.2187 | 0.1875        | 0.184        |

| 22 | 50 | 0.1953 | 0.0781   | 0.2343   | 0.2265 | 0.1875        | 0.184        |

| 23 | 50 | 0.1953 | 0.0781   | 0.2421   | 0.2343 | 0.1875        | 0.184        |

| 24 | 50 | 0.1953 | 0.0781   | 0.25     | 0.2421 | 0.1875        | 0.184        |

| 25 | 50 | 0.1953 | -0.0546  | 0.1953   | 0.25   | 0.25          | 0.187        |

| 26 | 50 | 0.1953 | 0.0781   | 0.2031   | 0.1953 | 0.1875        | 0.184        |

| 27 | 50 | 0.1953 | 0.0781   | 0.2019   | 0.2031 | 0.1875        | 0.184        |

| 28 | 50 | 0.1953 | 0.0781   | 0.2187   | 0.2019 | 0.1875        | 0.184        |

| 29 | 50 | 0.1953 | 0.0781   | 0.2265   | 0.2187 | 0.1875        | 0.184        |

| 30 | 50 | 0.1953 | 0.0781   | 0.2343   | 0.2265 | 0.1875        | 0.184        |

| 31 | 50 | 0.1953 | 0.0781   | 0.2421   | 0.2343 | 0.1875        | 0.184        |

| 32 | 50 | 0.1953 | 0.0781   | 0.25     | 0.2421 | 0.1875        | 0.184        |

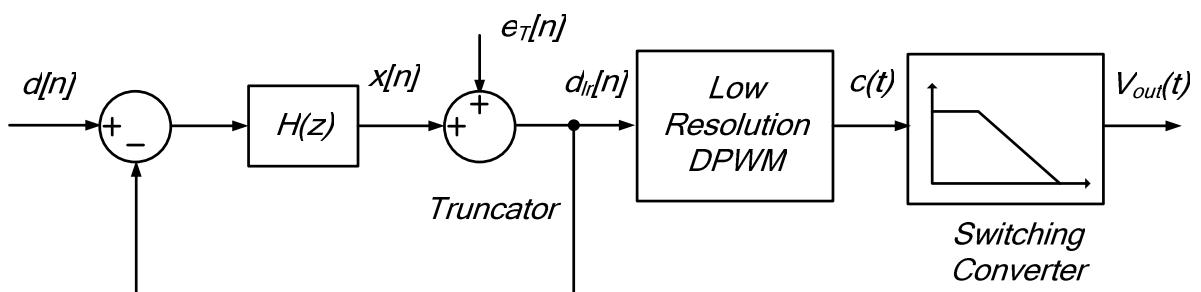

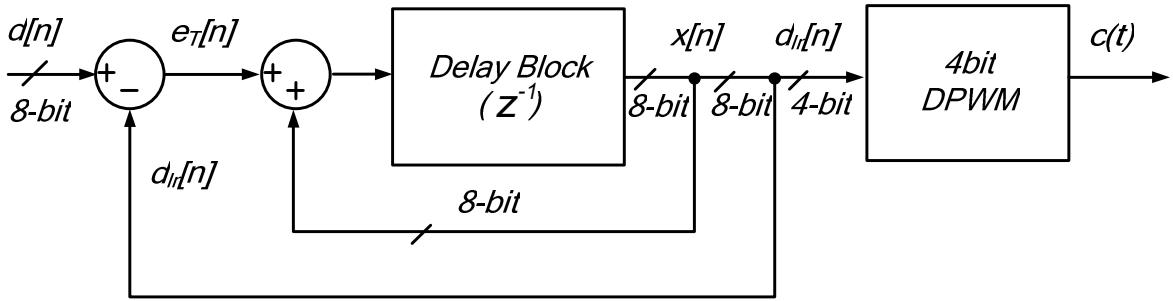

另外一種一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路是基於一階誤差回授(Error Feedback)的電路[6, 9]如下圖 36 所示，可以看到此電路是將  $x[n]$  的較低位元組經由一延遲電路與高解晰度的輸入  $d[n]$  做相加得到  $e_d[n]$ ，再經由限幅器(limiter)電路得到  $x[n]$ ， $x[n]$  的較高位元組為  $d_{lr}[n]$ ，經由幾週期之後的平均會等於  $d[n]$ 。這邊的限幅器主要是當電路在計算時， $e_d[n]$  要是發生溢位(Overflow)可以強制使  $x[n]$  維持在最大值或會小值，防止電路誤動作。接下來我們經由式子推導出  $d[n]$  對  $d_{lr}[n]$  的  $z$  轉換如下式(3.18)表示。

$$d_{lr}[n] = x[n] + e_T[n] \quad (3.14)$$

$$e_d[n] = d[n] - e_T[n-1] \quad (3.15)$$

$$x[n] = e_d[n] \quad (3.16)$$

$$d_{lr}[n] = d[n] - e_T[n-1] + e_T[n] \quad (3.17)$$

$$D_{lr}[z] = D[z] + (1 - z^{-1})E_T(z) \quad (3.18)$$

可以由下式(3.19)看到  $STF(z)$  為 1，跟前面所介紹的一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路  $STF(z)$  為  $z^{-1}$  不同，以電路來看的話可以輸入  $d[n]$  與輸出  $d_{lr}[n]$  差了一時脈的延遲，以系統面來說我們增加了數位降壓電路上的穩定度，我們可以看到  $z^{-1}$  對系統面來說是多個極點，也就是會減少系統的相位邊界。

$$STF(z) = 1 \quad (3.19)$$

$$NTF(z) = 1 - z^{-1} \quad (3.20)$$

圖 36. 一階誤差回授  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路[6]

如圖 36 可以觀察階誤差回授一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路另一個優點則是它的數位元件相較前面提到的減少許多，例如延遲電路。

接下來我們來探討一下一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路所產生的問題，當輸入一固定高解析度的  $d[n]$ ，經由一階  $\Sigma\Delta$  雜訊整型迴路所出來的  $d_{lr}[n]$  會是一個具有週期性的低頻諧波，可以看到  $d_{lr}[n]$  將會震盪在鄰近的兩個值之間使平均為  $d[n]$ ，如表所示可以看到  $d[n]=50/256$ ，而  $d_{lr}[n]$  隨著每一週期的變化為：

$$\begin{aligned} & 0.1875, 0.1875, 0.1875, 0.1875, 0.1875, 0.1875, 0.1875, \mathbf{0.25}, 0.1875, 0.1875, \\ & 0.1875, 0.1875, 0.1875, 0.1875, 0.1875, \mathbf{0.25}, 0.1875, 0.1875, 0.1875, 0.1875, \\ & 0.1875, 0.1875, 0.1875, \mathbf{0.25} \dots\dots \end{aligned}$$

這邊可藉由圖 36 來推導出  $d_{lr}[n]$  產生週期性的式子，首先一開始先假設在  $n < 0$  的初始狀態及  $n \geq 0$  高解析度  $d[n]$  及低解析度  $d_{lr}[n]$  之間的關係式可由圖 37(a)， $\Delta d$  為高解析度  $d[n]$  的最小 LSB，這邊的  $N$  及  $N_{PWM}$  分別為  $d[n]$  及  $d_{lr}[n]$  的位元數。

$$d[n] = d_{lr}[n] = x[n] = d_{LR0}, \quad n < 0 \quad (3.21)$$

$$d[n] = d_{LR0} + k \cdot \Delta d, \quad n \geq 0 \quad (3.22)$$

$$\Delta d = \frac{1}{2^N} \quad (3.23)$$

$$\Delta d_{LR} = 2^{(N-N_{PWM})} \cdot \Delta d \quad (3.24)$$

接下來可以經由整理得出式子(3.26)，再經由 Z 轉換得到式子(3.27)，最後在經由反 Z 轉換得到式子(3.28)及(3.29)，可以看到  $e_T[n]$  及  $x[n]$  隨著週期線性的增加，可由圖 37(a)(c) 所示。

$$e_T[n] = d_{lr}[n] + k \cdot \Delta d + e_T[n-1] - d_{lr}[n] \quad (3.25)$$

$$e_T[n] = e_T[n-1] + k \cdot \Delta d \quad (3.26)$$

$$E_T(z) = z \frac{k \cdot \Delta d \cdot z^{-1}}{(1-z^{-2})^2} \quad (3.27)$$

$$e_T[n] = (n+1) \cdot k \cdot \Delta d \cdot u[n+1] \quad (3.28)$$

$$x[n] = d_{LR0} + (n+1) \cdot k \cdot \Delta d \cdot u[n] \quad (3.29)$$

圖37. 一階  $\Sigma\Delta$  雜訊整型迴路訊號圖(a)高解析度  $d[n]$  及內部  $x[n]$ (b)低解析度  $d[n]$ (c)誤差值  $e_T[n]$ [6]

由式子(3.28)及(3.29)及圖 37 觀察到  $e_T[n]$  及  $x[n]$  隨著週期線性的增加， $d[n]$  在鄰近的兩個週期性的跳來跳去，這些低頻的諧波在輸出會造成震盪，而這最小的低頻諧波頻率可以由式子(3.30)表示， $N$  及  $M$  分別代表輸入高解析度的  $d[n]$  及低解析度的  $d_{lr}[n]$ ，而  $F_{sw}$  則是系統的切換頻率。

$$f_{tone\_min} = \frac{F_{sw}}{2^{N-M}} \quad (3.30)$$

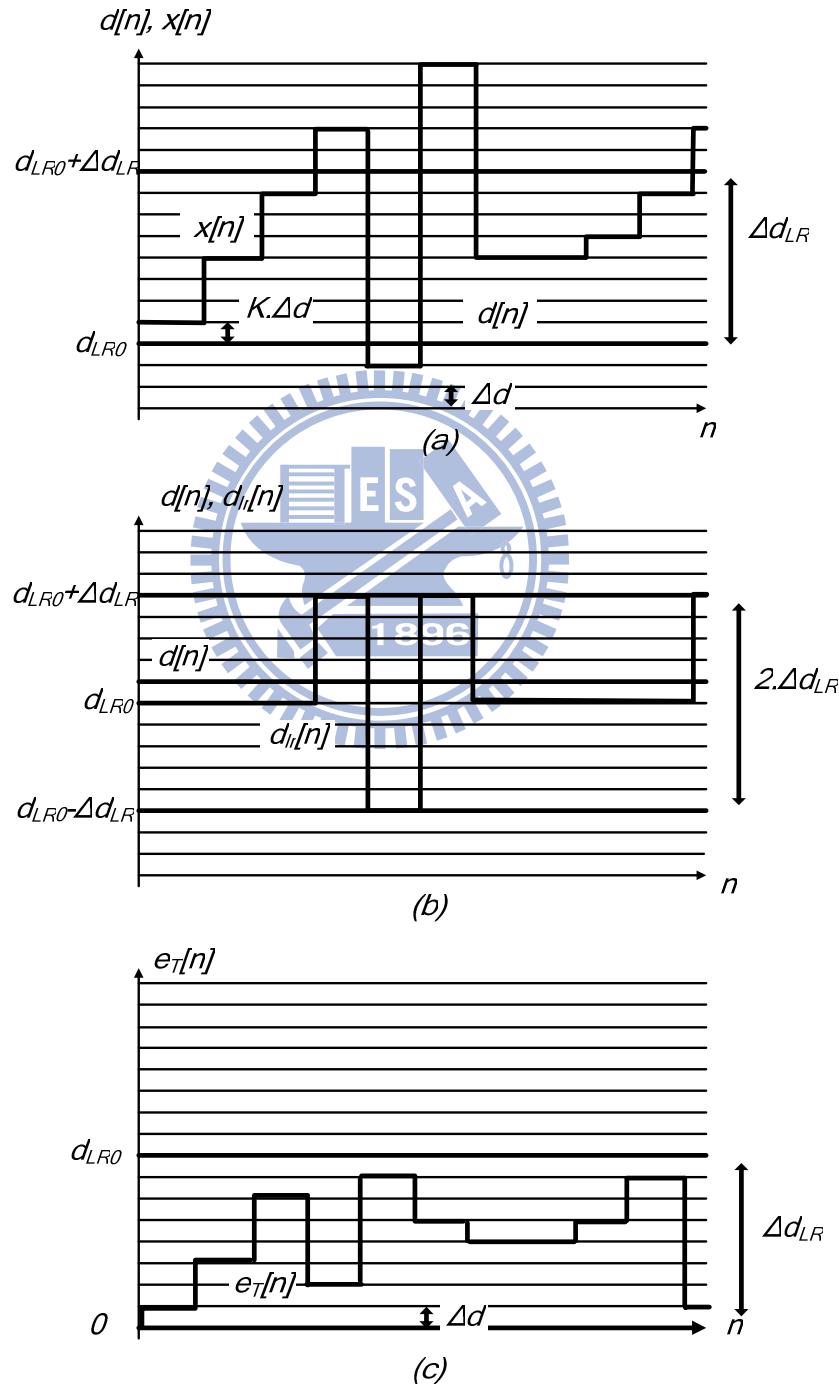

接下來我們使用 Simulink 來驗證前面所推的式子如圖 38 所示，這邊給一固定的高解析度  $d[n]$  為  $(321/512)$ ，輸入電壓  $V_{in}$  為  $12V$ ，功率區塊裡面的電感及電容各為  $22\mu$ ，故它的雙極點在  $7.23kHz$ ，這邊可由圖看到  $d_{lr}[n]$  的經由 64 周期之後的平均將會等效於  $d[n]$ 。也可看到  $e_T[n]$  隨著線性的變化，進而輸出的有一低頻的震盪頻率為  $5.27 kHz$  如圖 39 所示，可看到震盪造成輸出電壓的峰對峰值大約為  $280mV$ 。會造成輸出會有一個低頻諧波的原因是因為  $e_T[n]$  隨著每週期都是線性的增加，已經違反了一開始假設截取器所造成的雜訊為白雜訊。故我們經由實驗驗證  $e_T[n]$  被假設為白雜訊在一階的  $\Sigma\Delta$  雜訊整型是不成立的。

圖38. 一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路 Simulink 模型圖[19]

圖39. 一階  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路模擬結果

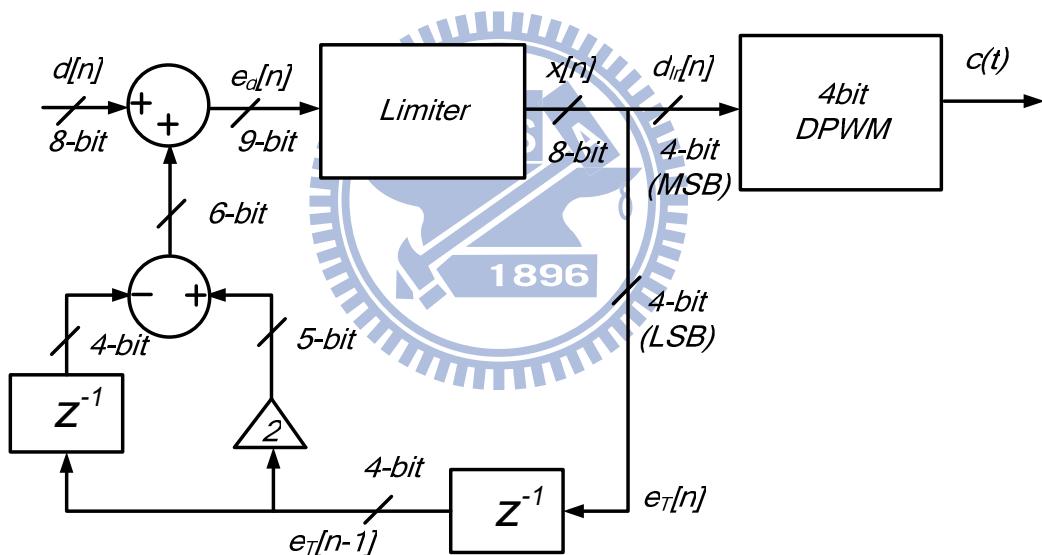

### 3.2.3 二階 $\Sigma\Delta$ 雜訊整形數位脈波寬度調變電路

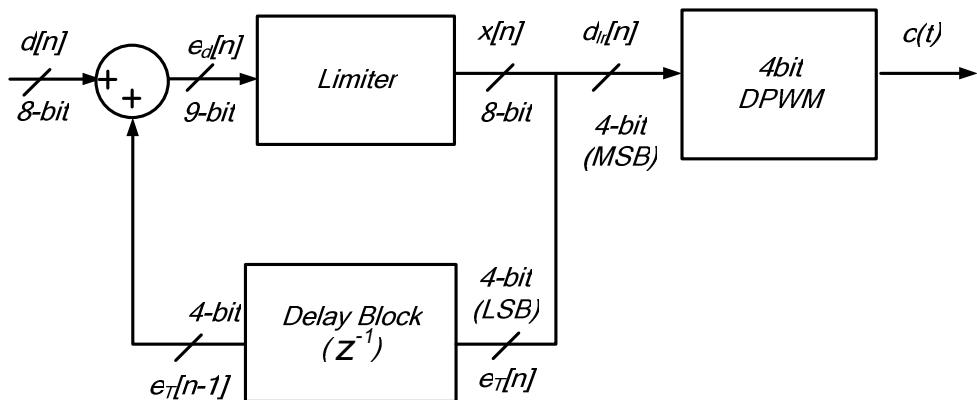

在上一章節所提到一階的  $\Sigma\Delta$  雜訊整形迴路所造成的輸出低頻諧波其實可以經由抖動技術(Dithering)[20]或二階的  $\Sigma\Delta$  雜訊整形迴路[6, 9]來降低。抖動技術主要的精神則是在截取器之前加入亂數(Random)的值，進而打斷  $e_T[n]$  週期性產生的情形。然而抖動技術在系統當中也會造成一低頻的雜訊並且造成調變器的不穩定。另一方面二階的  $\Sigma\Delta$  雜訊整形迴路架構以被提出運用在類比數位轉換轉換器等電路。其架構如下圖 40 所示為二階誤差回授  $\Sigma\Delta$  雜訊整形迴路，其架構不同於一階的  $\Sigma\Delta$  雜訊整形迴路在於回授的路徑多了一級的延遲電路、乘二電路及減法器。加了這些電路主要想要將  $e_T[n]$  週期性的訊號打斷，使它成為近似亂數的訊號，這樣在頻譜上所看到的  $E_T(z)$  才會近似於白雜訊。

圖 40. 二階誤差回授  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變[6]

這邊將用式子來驗證二階誤差回授  $\Sigma\Delta$  雜訊整形迴路的整體行為，可以經由圖 40 得到式子(3.31)及式子(3.32)經由整理得到式子(3.33)，最後經由  $z$  轉換以及反  $z$  轉換得到式子(3.34)，這邊可以看到  $e_T[n]$  跟一階誤差回授  $\Sigma\Delta$  雜訊整形迴路  $e_T[n]$  相比，已經從線性上升變為二次方的變化由圖 41(c)所示。

$$x[n] = d[n] + 2e_T[n-1] - e_T[n-2] \quad (3.31)$$

$$e_T[n] = x[n] - d_{LR}[n] \quad (3.32)$$

$$e_T[n] = 2e_T[n-1] - e_T[n-2] + k \cdot \Delta d \quad (3.33)$$

$$e_T[n] = \frac{(n+1)(n+2)}{2} \cdot k \cdot \Delta d \cdot u[n+2] \quad (3.34)$$

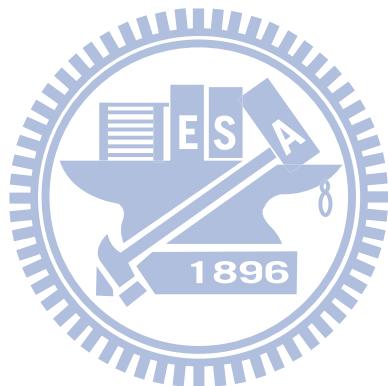

圖41. 二階  $\Sigma\Delta$  誤差回授雜訊整型迴路訊號圖(a)高解析度  $d[n]$  及內部  $x[n]$ (b)低解析度  $d[n]$ (c)誤差值  $e_T[n]$ [6]

接下來將式子(3.34)帶回式子(3.31)得到式子(3.35)，可以看到式子(3.35), $x[n]$ 裡面包含了二次方項，每一週期變化時，輸出將不會是線性變化，也可由圖 41(b)看到  $d[n]$  已不僅僅是在鄰近的兩個值之間變化。最後我們將用 Simulink 來模擬二階的  $\Sigma\Delta$  雜訊整型數位脈波寬度調變電路如圖 42 所示，輸入給固定的高解析度  $d[n]$  為(321/512)，輸入電壓  $V_{in}$  為 12V，這邊可由圖 43 看到  $d_{lr}[n]$  的經由許多周期之後的平均將會等效於  $d[n]$ 。也可看到  $e_T[n]$  隨著二次方的變化，輸出的對峰值約為 120mV。

$$x[n] = d_{LR0} + (1+n(n+1)u[n+1] - \frac{n(n-1)}{2}u[n])k \cdot \Delta d \quad (3.35)$$

圖42. 二階  $\Sigma\Delta$  誤差回授雜訊整型數位脈波寬度調變電路 Simulink 模型圖[19]

圖43. 二階  $\Sigma\Delta$  誤差回授雜訊整型數位脈波寬度調變電路模擬結果

### 3.3 誤差類比數位轉換器

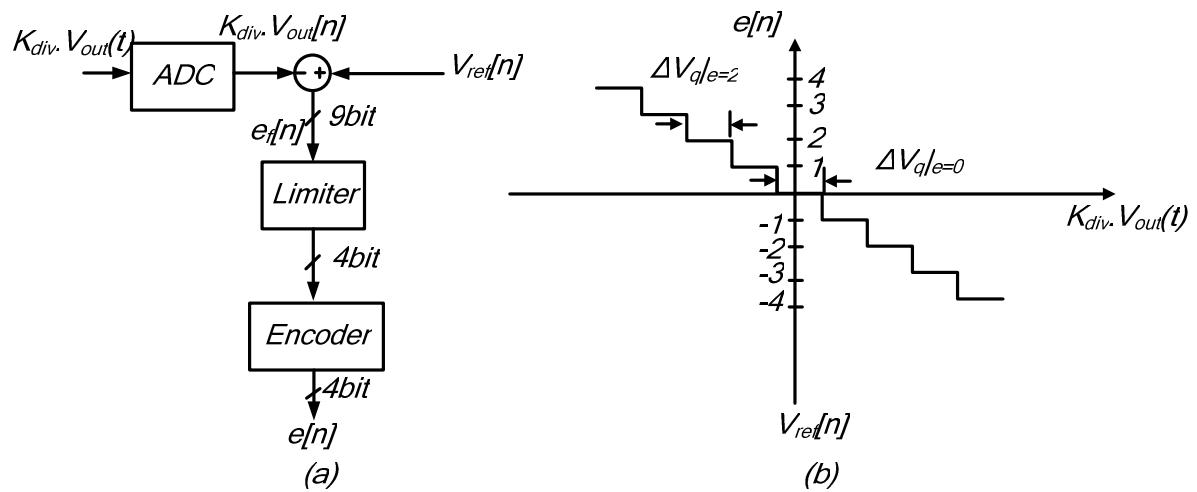

在這一章節所要介紹的是誤差類比數位轉換器基於窗型類比數位轉換器(Window ADC)[6, 7, 9]的概念，它在數位直流-直流降壓電路有三個很大的優點，第一優點由於它的作法如下圖 44 (a)所示是輸出電壓  $V_{out}(t)$  經由衰減器  $K_{div}$ ，再經由類比數位轉換器得到數位碼  $K_{div} \cdot V_{out}[n]$  與參考碼  $V_{ref}[n]$  相減之後得到一誤差  $e_f[n]$ ，最後經由編碼器得到  $e[n]$ 。編碼過後的誤差  $e[n]$  將會限制在 -4~+4 之間，也就是當誤差類比數位轉換器輸出的值超過 +4 或 -4 時將它會飽和掉，由於誤差類比數位轉換器的輸出只有 -4~+4，故後面那一級的數位補償器可以減少很大的面積成本及計算的功率消耗。第二優點則是在數位直流-直流降壓電路可以省去緩啟動(Soft Start)電路，在類比直流-直流轉換器中會在代差參考電壓做緩啟動，使代差參考電壓慢慢的上升，因此脈波寬度調變才不會一開始就是全開狀態使得電感上的電流及輸出電壓暴衝，窗型類比數位轉換器也等同於這一原理，在電路剛啟動時誤差量  $e[n]$  為 +4 經由數位補償器之後所產生的脈波寬度則是慢慢增大其功能等效於緩啟動。第三優點則是可以減少切換頻率雜訊對系統的影響，在這邊將每一誤差的量化  $\Delta V_q$  設計不等距離如下圖 44(b)及表所示，當取樣到有切換頻率雜訊時，誤差可以由之前的非常大到現在的 -1 或 +1，在數位補償器來說對雜訊的敏感度降低了。

在這邊如何決定每一格誤差  $e[n]$  的大小，由於切換開關造成的切換雜訊會隨著印刷電路板子(PCB)的佈局的不同會影響切換雜訊的大小，在最差情況下大約為 170mV，在這邊希望  $e[n]$  當遇到切換雜訊時能在 -1 或 +1，故設計  $e[n]$  在 -1 或 +1 為兩格  $\Delta V_q$ 。這邊也希望當負載大變化時  $e[n]$  能在 -4 或 4 即時反應，此降壓電路規格負載最大為 2A 故  $e[n]$  在 -4 或 4 為七格  $\Delta V_q$  如表 4 所示。

圖44. (a)誤差類比數位轉換器編碼(b) 誤差類比數位轉換器輸入與輸出對應圖

表4. 誤差類比數位轉換器編碼

| $e_f = V_{ref} - K_{div} \cdot V_{out}$ | $e[n]$              | $e_f = V_{ref} - K_{div} \cdot V_{out}$ | $e[n]$               |

|-----------------------------------------|---------------------|-----------------------------------------|----------------------|

| $(7)_{10} (0111)_2$                     | $(4)_{10} (0100)_2$ | $(-7)_{10} (1001)_2$                    | $(-4)_{10} (1100)_2$ |

| $(6)_{10} (0110)_2$                     | $(3)_{10} (0011)_2$ | $(-6)_{10} (1010)_2$                    | $(-3)_{10} (1101)_2$ |

| $(5)_{10} (0101)_2$                     |                     | $(-5)_{10} (1011)_2$                    |                      |

| $(4)_{10} (0100)_2$                     | $(2)_{10} (0010)_2$ | $(-4)_{10} (1100)_2$                    | $(-2)_{10} (1110)_2$ |

| $(3)_{10} (0011)_2$                     |                     | $(-3)_{10} (1101)_2$                    |                      |

| $(2)_{10} (0010)_2$                     | $(1)_{10} (0001)_2$ | $(-2)_{10} (1110)_2$                    | $(-1)_{10} (1111)_2$ |

| $(1)_{10} (0001)_2$                     |                     |                                         |                      |

| $(0)_{10} (0000)_2$                     | $(0)_{10} (0000)_2$ | $(-1)_{10} (1111)_2$                    | $(0)_{10} (0000)_2$  |

### 3.4 數位正比積分微分補償器

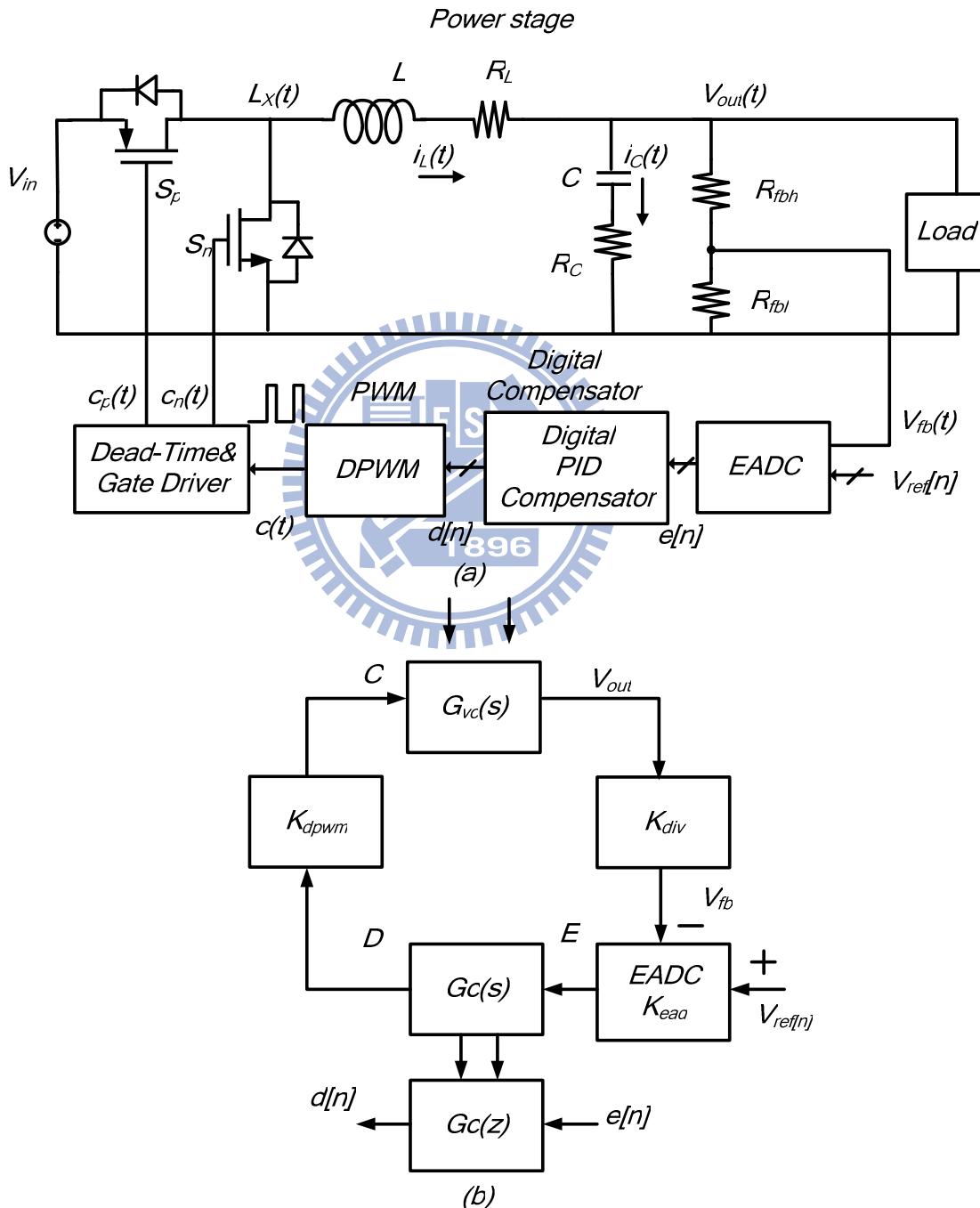

在這一章節將設計數位正比積分微分補償器[5, 12-14, 21]，數位降壓電路系統裡面數位補償器在整體系統裡面的功能其實就等同於類比的補償器。如下圖 45(a)[22, 23]所示為數位降壓電路，可將它拆為功率區塊、衰減器、誤差類比數位轉換器、數位補償器及數位脈波寬度調變電路。

圖45. (a)數位降壓電路系統方塊圖(b)降壓電路系統轉移函式圖[22]

這邊將圖 45(a)各區塊的轉移函式由圖 45(b)來表示。一開始設計我們先將各個區塊連續時間的轉移函式導出來，接下來加入連續時間補償器電路設計，最後再將連續時間的補償器電路  $G_c(s)$  經由  $s$  平面轉到  $z$  平面上[11, 12]得到離散時間的補償器電路  $G_c(z)$  如圖 45(b)所示。如下式(3.36)所示  $T(s)$  為數位降壓電路系統的開迴路轉移函式， $K_{div}$  為衰減器的增益， $K_{ead}$  為類比數位轉換器的增益， $K_{dpwm}$  為數位脈波寬度調變器的增益， $G_{vc}(s)$  為功率區塊得轉移函式。

$$T(s) = G_{vc}(s) \cdot K_{div} \cdot K_{ead} \cdot G_c(s) \cdot K_{dpwm} \quad (3.36)$$

$$K_{div} = \frac{V_{fb}}{V_{out}} \quad (3.37)$$

$$K_{ead} = \frac{2^{N_{ADC}}}{V_{fb}} = \frac{1}{(\Delta V_q \cdot K_{div})} \quad (3.38)$$

$$K_{dpwm} = \frac{1}{2^{N_{DPWM}}} \quad (3.39)$$

$$G_{vc}(s) = V_{in} \frac{\frac{1+sCR_C}{R_{Load}} + s^2LC}{1+s[CR_{Load}(R_L+R_C)+L]} \quad (3.40)$$

在規格表可以知道系統的雙極點在 7.23kHz，ESR 零點在 36kHz，首先我們先看開迴路轉移函式  $T(s)$  在沒有補償轉移函式  $G_c(s)$  輕載及重載的波德圖如圖 46 所示，可有式子(3.40)看到  $G_{vc}(s)$  在輕載模式下  $LC$  所產生的雙極點將會是共軛極點，在重載模式下  $LC$  所產生的雙極點為負實數的極點。可看到輕載模式下所產生的相位下降得比重載模式還要快，故在這邊補償我們以輕載模式為最差個案來設計。

$$f_0 = \frac{1}{2\pi\sqrt{LC}} \quad (3.41)$$

$$f_{ESR} = \frac{1}{2\pi R_C C} \quad (3.42)$$

當這邊已知道開迴路  $T(s)$  在沒有  $G_c(s)$  的轉移函式，接下來還要決定幾個參數，可由規格表知道系統德切換頻率  $F_{SW}$  為 390.625kHz，在直流-直流轉換器系統的單位增益頻寬大概都設計在切換頻率的 1/5~1/20。這邊設計開迴路增益的單微增益頻寬  $f_c$  為 20kHz，相位邊界為 60 度。

圖46.  $G_c(s)$ 輕載及重載的頻率響應圖

在開迴路  $T(s)$  在沒有  $G_c(s)$  的轉移函式當中可以看到有兩個極點及一零點，由於此零點是與輸出電容上等效串聯電阻有關聯，它會隨著不同材質的電容會有不同的阻抗，舉例來說輸出電容採用的是陶瓷電容等效串聯電阻可以小到  $5m\Omega$ ，採用的如果是鉭質電容等效串聯電阻可以大到  $200m\Omega$ ，當採用等效串聯電阻大的電阻可以補償系統的相位但會造成輸出的漣波變大如式(2.5)。採用等效串聯電阻小的電阻無法補償到系統的相位但輸出的漣波卻可變小。這邊採用的補償方式為正比積分微分如下式(3.43)所示，正比主要是來增加增益，積分則是減少穩態的誤差，微分則是增加系統的穩定度，接下來又可以將它整理成式子(3.4)，可看到為兩個零點、一極點及一增益常數。

$$G_c(s) = k_p + \frac{k_I}{s} + sk_D \quad (3.43)$$

$$G_c(s) = \frac{D(s)}{E(s)} = k_c \frac{(1 + \frac{s}{\omega_{z1}})(1 + \frac{s}{\omega_{z2}})}{s} \quad (3.44)$$

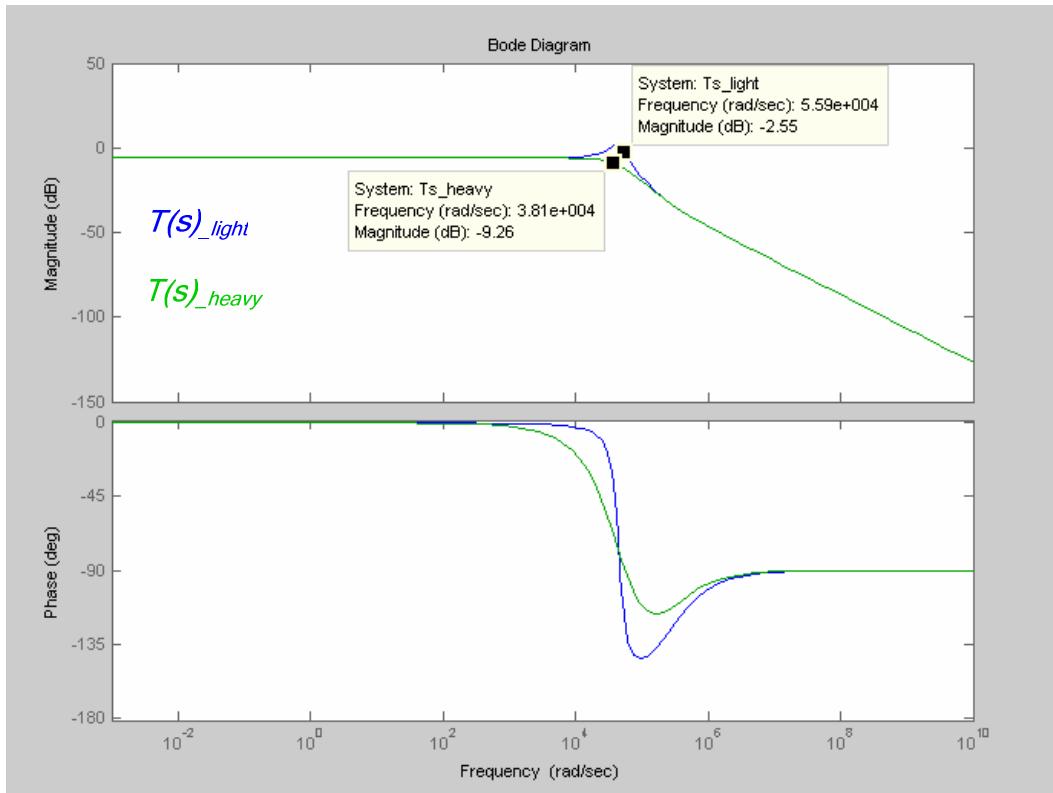

一開始先將補償器的一零點  $\omega_{z1}$  設計為與  $\omega_0$  對消掉一極點，接下來從相位邊界著手得到零點  $\omega_{z2}$ ，最後再從單位增益頻寬得到  $k_c$ 。將設計出的  $G_c(s)$  帶入開迴路  $T(s)$  中，使用 Matlab 來模擬  $T(s)$  的波德圖如下圖 47 所示，可看到單增益頻寬為 20.21kHz，相位邊界為 64 度。

圖47. 系統  $T(s)$  頻率響應圖

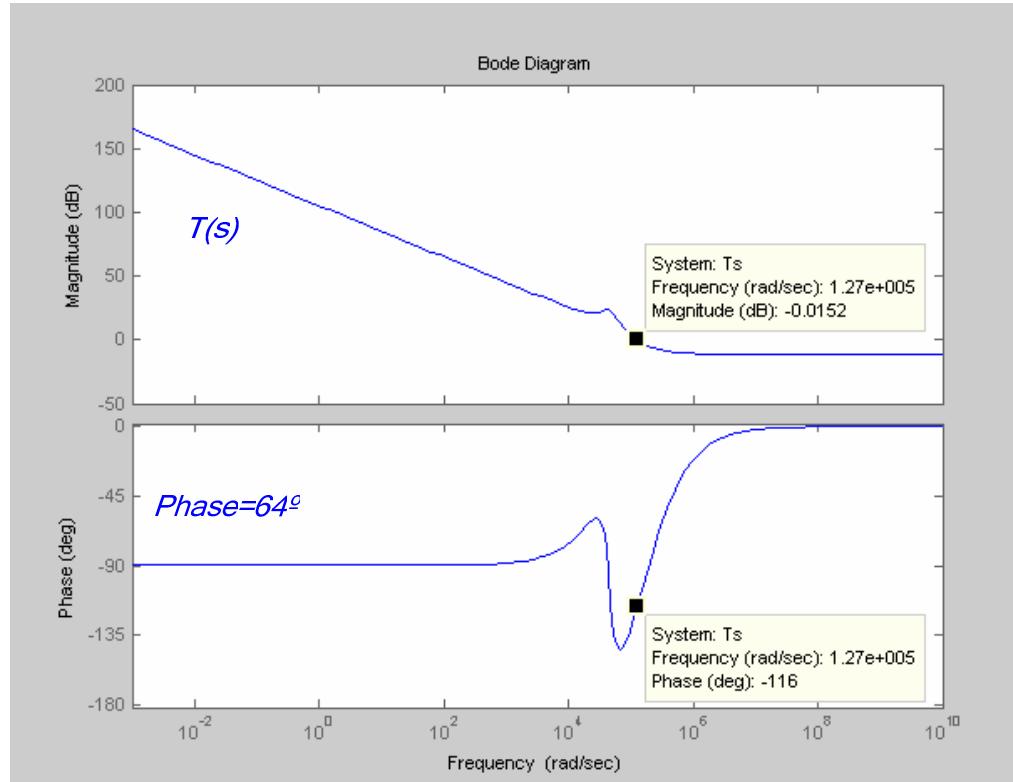

當連續的補償轉移函式  $G_c(s)$  設計出來之後，接下來將  $s$  平面映射到  $z$  平面上。在數位的控制系統或數位訊號處理的書上有提到可以利用尤拉規則(Eular's Rule)、雙線性轉移(Bilinear Transform)或零極點映射(ZPM)，即可達到  $z$  平面上轉移函式。在這邊使用第一種方式則是雙線性轉移如下式(3.45)所示為  $s$  平面映射到  $z$  平面上， $T_d$  為取樣時間，在  $z$  平面的單位圓內等同於是  $s$  平面的左半平面。接下來將式子(3.45)帶入  $G_c(s)$  得到  $G_c(z)$  如下式(3.46)所示，最後將  $G_c(z)$  反  $z$  轉換得到式子(3.48)，可以看到  $e[n]$  為誤差類比數位轉換器的誤差值，而  $e[n-1]$  及  $e[n-2]$  則是  $e[n]$  上一個及上上一個狀態值。 $d[n]$  則是我們系統脈波工作週期比值，而  $d[n-1]$  則是上一個狀態值。雙線性轉移得到式子的值分別為：

$$a=35.466, b=-58.917, c=24.357$$

$$s = \frac{2}{T_d} \left( \frac{1-z^{-1}}{1+z^{-1}} \right) \quad (3.45)$$

$$G_c(z) = \frac{D(z)}{E(z)} = k_p + k_I \frac{T_d}{2} \left( \frac{z+1}{z-1} \right) + k_D \frac{1}{T_d} \left( \frac{z-1}{z} \right) \quad (3.46)$$

$$G_c(z) = \frac{D(z)}{E(z)} = \frac{a + bz^{-1} + cz^{-2}}{1 - z^{-1}} \quad (3.47)$$

$$d[n] = d[n-1] + a \cdot e[n] + b \cdot e[n-1] + c \cdot e[n-2] \quad (3.48)$$

第二種 s 平面映射到 z 平面上為尤拉規則，所導出來式子的值分別為：

$$a=35.928, b=-59.367, c=24.357$$

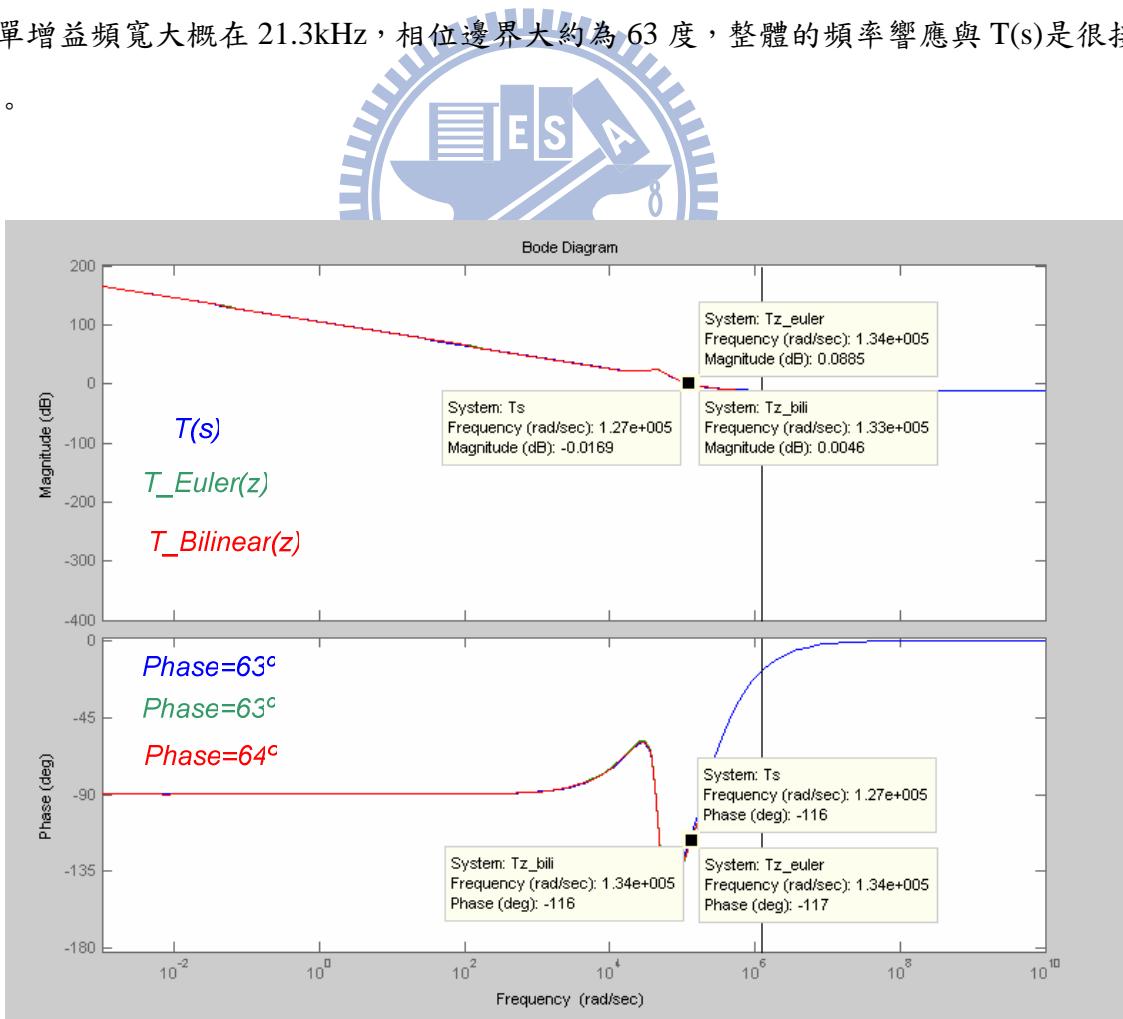

可發現尤拉規則及雙線性轉移所倒出來的轉移函式是非常接近的。如下圖 48 所示為連續訊號  $T(s)$  及尤拉和雙線性開迴路  $T(z)$  的頻率響應圖，可看到尤拉規則及雙線性轉移的單增益頻寬大概在 21.3kHz，相位邊界大約為 63 度，整體的頻率響應與  $T(s)$  是很接近的。

圖48. 連續訊號  $T(s)$  及尤拉和雙線性開迴路  $T(z)$  的頻率響應圖

當設計出直接形式(Direct Form)如式子，接下來就是將它實現為電路，可觀察式子(3.48)當中需要的數位元件當中有 D 型正反器、乘法器及加法器。我們可以將式子由圖 15 所表示。可以看到圖 15 當中需要三個乘法器達到  $a.e[n]$ 、 $b.e[n-1]$  及  $c.e[n-2]$ ，三個 D 型正反器達到儲存上一個狀態值，最後則是加法器。在這邊可以看到一個相當嚴重的問題則是功率消耗會相當的大，原因是裡面的乘法器，使用乘法器會耗費掉很大的面積以及耗費很多的時間在計算，故產生大的功率消耗。

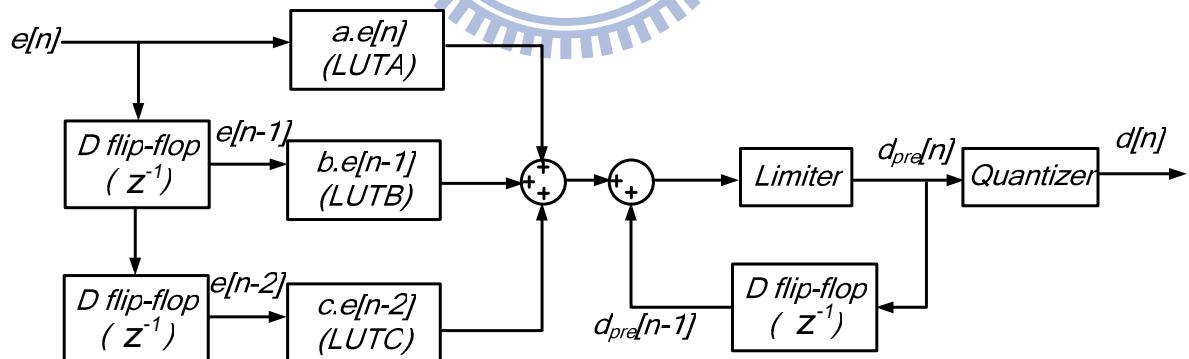

在這邊我們採用查表法(Look Up Table)[6, 7, 9, 14]如下圖 49 所示為 D 型正反器、加法器、查表圖、限幅器及量化器，所謂的查表法則是說我的表格裡面已經儲存了所有輸入會發生的可能性，每一輸入值將會對應到一個輸出值，舉例來說如圖所示裡面的 LUT A 表格裡面所包含地資訊為  $a.e[n]$ ，不管輸入  $e[n]$  為如何查表法能相當快的對應出一輸出值，故這非常適合在高速及低功率的應用中，唯一的缺點它需要很大的面積。但在整個系統的設計當中，由於前一級我們是採用窗型類比數位轉換器，所以我們的誤差訊號  $e[n]$  是介於 -4~+4 之間，使用查表法我們的輸入只有九種狀態，查表裡面所需的面積即可大大的減少。

圖49. 正比積分微分補償器基於查表法

# 第四章

---

## 模擬結果

在這一章節我們使用 Matlab 裡面的 Simulink 來建立數位降壓電路的模型[6, 19, 24]並且模擬它的動作。一開始先模擬數位降壓電路在計數模式數位脈波寬度調變下輸入  $V_{in}$  為 12V，觀察負載變化之下的輸出鎖定電壓以及輸出電壓峰對峰值的大小。在來則是模擬驗證數位降壓電路在二階的  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變輸入  $V_{in}$  為 12V，觀察負載變化之下的輸出鎖定電壓以及輸出電壓峰對峰值的大小。

### 4.1 計數模式數位脈波寬度調變數位降壓電路模擬驗證

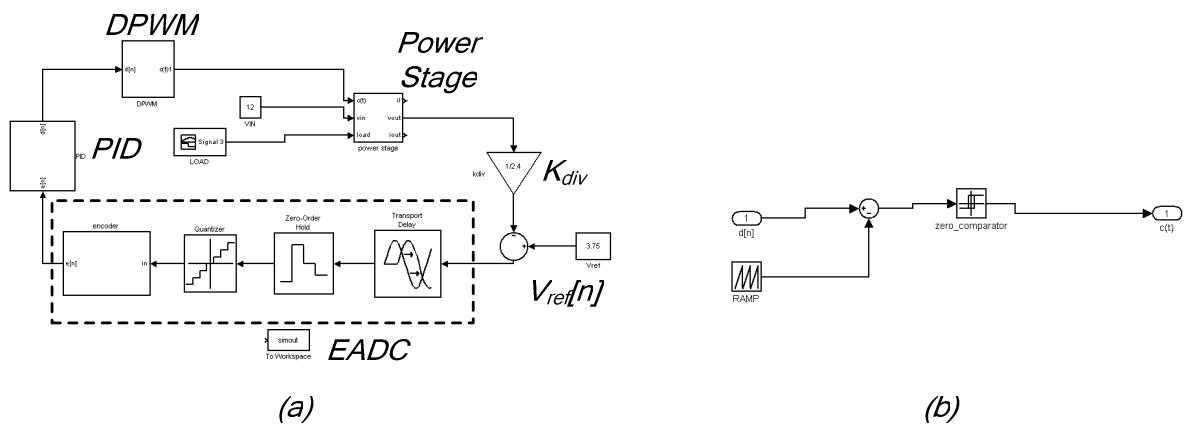

如圖 50(a)所示為計數模式數位脈波寬度調變數位降壓電路在 Simulink 所建立的模型，裡面包含了功率區塊如 50 圖(c)所示、數位脈波寬度調變圖 50(b)所示、數位補償器圖 50(d)所示、誤差類比數位轉換器、衰減器及參考電壓。

圖50. (a) 計數器模式數位脈波寬度調變降壓電路系統模型(b) 數位脈波寬度調變電路模型

(c) 功率區塊模型(d) 數位正比積分微分補償器

下表 5 為計數模式數位脈波寬度調變數位降壓電路輸出電壓鎖定在 1.5V~9V 性能表現，模擬如圖 51~54 所示。表 5 的參數模擬值包含有輸出的漣波大小  $\Delta V_{out}$ 、負載由 500mA 到 1A 抽載時所造成輸出過衝電壓  $V_{over}$  (Overshoot Voltge)、過衝回復時間  $T_{over\_r}$  (Overshoot Recovery Time)、負載由 1A 到 500mA 抽載時所造成輸出下衝電壓  $V_{under}$  (Undershoot Voltge)、下衝回復時間  $T_{under\_r}$  (Undershoot Recovery Time)。

表5. 計數器模式數位脈波寬度調變降壓電路負載變化下輸出電壓性能表現

| Parameter                | symbol           | 1.5V         | 3V           | 5V          | 9V          |

|--------------------------|------------------|--------------|--------------|-------------|-------------|

| Output Voltage           | $\Delta V_{out}$ | 35mV         | 50mV         | 75mV        | 50mV        |

| Overshoot Voltage        | $V_{over}$       | 180mV        | 200mV        | 200mV       | 200mV       |

| Overshoot Recovery Time  | $T_{over\_r}$    | 87.5 $\mu$ s | 87.5 $\mu$ s | 100 $\mu$ s | 130 $\mu$ s |

| Undershoot Voltage       | $V_{under}$      | 200mV        | 200mV        | 200mV       | 180mV       |

| Undershoot Recovery Time | $T_{under\_r}$   | 75 $\mu$ s   | 100 $\mu$ s  | 100 $\mu$ s | 130 $\mu$ s |

圖51. 計數器模式數位脈波寬度調變負載抽載輸出電壓 1.5V 模擬圖 (a)輸出負載  $i_{load}(t)$ 、電感電流  $i_L(t)$ 、輸出電壓  $V_{out}(t)$ 及誤差值  $e[n]$  (b)負載 500mA 時  $i_L(t)$ 及  $V_{out}(t)$

(c)負載 1A 時  $i_L(t)$ 及  $V_{out}(t)$

圖52. 計數器模式數位脈波寬度調變負載抽載輸出電壓 3V 模擬圖 (a)輸出負載  $i_{load}(t)$ 、電感電流  $i_L(t)$ 、輸出電壓  $V_{out}(t)$ 及誤差值  $e[n]$  (b)負載 500mA 時  $i_L(t)$ 及  $V_{out}(t)$  (c)負載 1A 時  $i_L(t)$ 及  $V_{out}(t)$

圖53. 計數器模式數位脈波寬度調變負載抽載輸出電壓5V模擬圖 (a)輸出負載  $i_{load}(t)$ 、電感電流  $i_L(t)$ 、輸出電壓  $V_{out}(t)$ 及誤差值  $e[n]$  (b)負載 500mA 時  $i_L(t)$ 及  $V_{out}(t)$  (c)負載 1A 時  $i_L(t)$ 及  $V_{out}(t)$

圖54. 計數器模式數位脈波寬度調變負載抽載輸出電壓9V模擬圖 (a)輸出負載  $i_{load}(t)$ 、電感電流  $i_L(t)$ 、輸出電壓  $V_{out}(t)$ 及誤差值  $e[n]$  (b)負載 500mA 時  $i_L(t)$ 及  $V_{out}(t)$  (c)負載 1A 時  $i_L(t)$ 及  $V_{out}(t)$

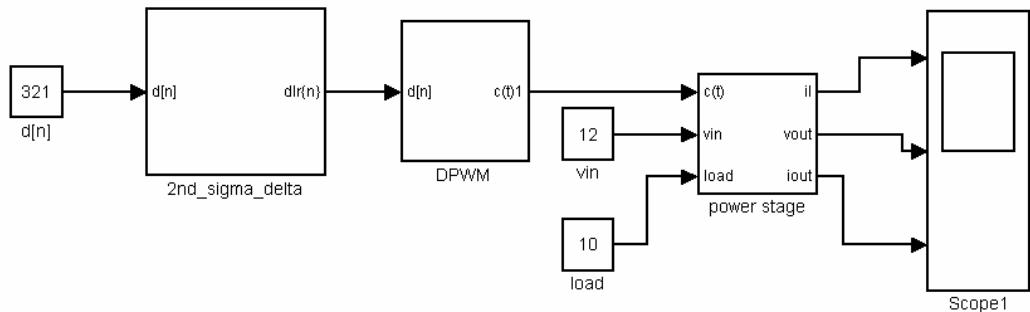

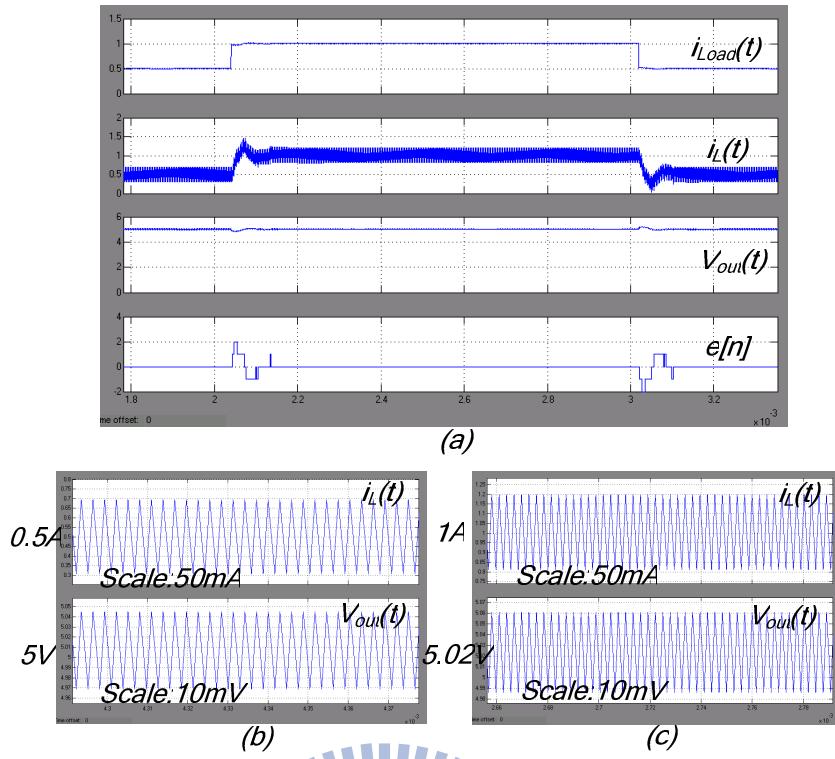

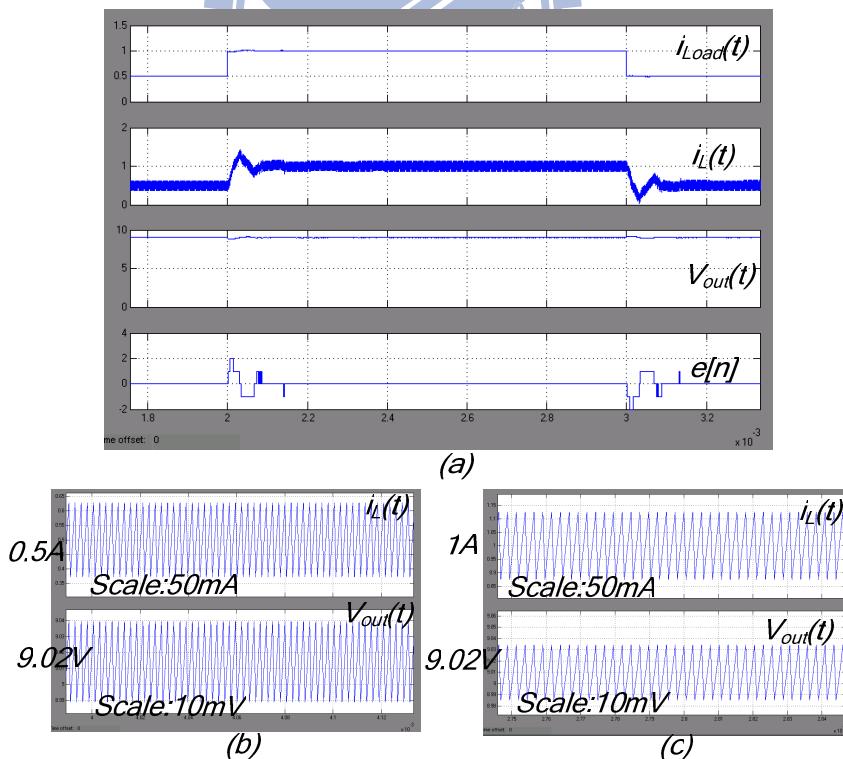

## 4.2 二階 $\Sigma\Delta$ 雜訊整形迴路數位脈波寬度調變數位降壓電路模擬驗證

如下圖 55(a)所示為二階  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變在 Simulink 所建立的模型，裡面包含了功率區塊、二階  $\Sigma\Delta$  雜訊整形迴路如圖 55(b)所示、數位脈波寬度調變、數位補償器、誤差類比數位轉換器、衰減器及參考電壓。

圖55. (a)二階  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變降壓電路系統模型(b) 二階  $\Sigma\Delta$  雜訊整形迴路調變

如下表 6 為二階  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變數位降壓電路輸出電壓鎖定在 1.5V~9V 性能表現，模擬如圖 56~59 所示。表格的參數模擬值包含有輸出的漣波大小  $\Delta V_{out}$ 、負載由 500mA 到 1A 抽載時所造成輸出過衝電壓  $V_{over}$  (Overshoot Voltge)、過衝回復時間  $T_{over\_r}$  (Overshoot Recovery Time)、負載由 1A 到 500mA 抽載時所造成輸出下衝電壓  $V_{under}$  (Undershoot Voltge)、下衝回復時間  $T_{under\_r}$  (Undershoot Recovery Time)。

表6. 二階  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變降壓電路負載變化下輸出電壓性能表現

| Parameter                | symbol           | 1.5V  | 3V    | 5V    | 9V    |

|--------------------------|------------------|-------|-------|-------|-------|

| Output Voltage           | $\Delta V_{out}$ | 45mV  | 60mV  | 80mV  | 60mV  |

| Overshoot Voltage        | $V_{over}$       | 160mV | 180mV | 200mV | 200mV |

| Overshoot Recovery Time  | $T_{over\_r}$    | 80μs  | 100μs | 120μs | 130μs |

| Undershoot Voltage       | $V_{under}$      | 180mV | 180mV | 200mV | 200mV |

| Undershoot Recovery Time | $T_{under\_r}$   | 70μs  | 70μs  | 100μs | 140μs |

圖56. 二階  $\Sigma\Delta$  數位脈波寬度調變負載抽載輸出電壓 1.5V 模擬圖 (a)輸出負載  $i_{load}(t)$ 、電感電流  $i_L(t)$ 、輸出電壓  $V_{out}(t)$ 及誤差值  $e[n]$  (b)負載 500mA 時  $i_L(t)$ 及  $V_{out}(t)$  (c)負載 1A 時  $i_L(t)$ 及  $V_{out}(t)$

圖57. 二階  $\Sigma\Delta$  數位脈波寬度調變負載抽載輸出電壓 3V 模擬圖 (a)輸出負載  $i_{load}(t)$ 、電感電流  $i_L(t)$ 、輸出電壓  $V_{out}(t)$ 及誤差值  $e[n]$  (b)負載 500mA 時  $i_L(t)$ 及  $V_{out}(t)$  (c)負載 1A 時  $i_L(t)$ 及  $V_{out}(t)$

圖58. 二階  $\Sigma\Delta$  數位脈波寬度調變負載抽載輸出電壓 5V 模擬圖 (a)輸出負載  $i_{load}(t)$ 、電感電流  $i_L(t)$ 、輸出電壓  $V_{out}(t)$ 及誤差值  $e[n]$  (b)負載 500mA 時  $i_L(t)$ 及  $V_{out}(t)$  (c)負載 1A 時  $i_L(t)$ 及  $V_{out}(t)$

圖59. 二階  $\Sigma\Delta$  數位脈波寬度調變負載抽載輸出電壓 9V 模擬圖 (a)輸出負載  $i_{load}(t)$ 、電感電流  $i_L(t)$ 、輸出電壓  $V_{out}(t)$ 及誤差值  $e[n]$  (b)負載 500mA 時  $i_L(t)$ 及  $V_{out}(t)$  (c)負載 1A 時  $i_L(t)$ 及  $V_{out}(t)$

# 第五章

---

## FPGA 驗證結果

在這一章節分成三部份，第一部分為車用電子測試環境及硬體架構，在測試的環境裡分別有傳送訊號的車用電源線、傳輸端(TX)、接收端 (RX) 及可程式車用功率積體電路，在硬體方面有開關、馬達、LED 及直流-直流降壓電路。第二部份則是直流-直流降壓電路在不同負載即不同的輸入電壓下所看到的輸出電壓及輸出電壓的漣波。第三部份則是馬達的轉速控制及 LED 的亮度調控、閃爍頻率及亮度時間的調控。

### 5.1 車用電子測試環境及硬體架構

整體車用電子的測試環境及硬體方塊圖如下圖 60 所示由控制開關、傳輸端(TX)、車用電源線、接收端 (RX)、可程式車用功率積體電路、馬達、LED 及直流-直流降壓電路，實際測試環境及硬體架構圖如圖 61 所示。在這邊的可程式車用功率積體電路及接收端 (RX) 的電路是寫入在 FPGA Spartan 3E 裡面，傳輸端(TX)的電路則是在 FPGA Spartan 3A 裡面，電源線上的電源則是 12V，訊號經由電源線由傳輸端傳送到接收端。為了方便測試電路，原本控制指令為 32 位元，這邊我們利用控制開關其中的 5 位元配合查表法列出 32 種狀態來測試電路如表 7 所示。

圖60. 車用電子電源線通訊及可程式車用功率積體電路示意圖

圖61. (a)車用電子電源線通訊及可程式車用功率積體電路實際圖(b)接收端（RX）、馬達、LED 及降壓電路(c)傳輸端(TX)及開關

表7. 5位元控制指令表

| Con[4:0]   | function               |            |                                  |

|------------|------------------------|------------|----------------------------------|

| 00000_(0)  | 1.5V                   | 10000_(16) | LED (NMOS) dimming 80%           |

| 00001_(1)  | 3V                     | 10001_(17) | LED (NMOS) 6Hz                   |

| 00010_(2)  | 5V                     | 10010_(18) | LED (NMOS) 3Hz                   |

| 00011_(3)  | 9V                     | 10011_(19) | LED (NMOS) 1.5Hz                 |

| 00100_(4)  | LED (PMOS) dimming 20% | 10100_(20) | LED (NMOS) 0.75Hz                |

| 00101_(5)  | LED (PMOS) dimming 50% | 10101_(21) | LED (NMOS) on-time 20%           |

| 00110_(6)  | LED (PMOS) dimming 80% | 10110_(22) | LED (NMOS) on-time 50%           |

| 00111_(7)  | LED (PMOS) 6Hz         | 10111_(23) | LED (NMOS) on-time 80%           |

| 01000_(8)  | LED (PMOS) 3HZ         | 11000_(24) | Motor(s2)(PMOS= on) (NMOS= off)  |

| 01001_(9)  | LED (PMOS) 1.5Hz       | 11001_(25) | Motor(s3)(PMOS= off) (NMOS= 20%) |

| 01010_(10) | LED (PMOS) 0.75Hz      | 11010_(26) | Motor(s3)(PMOS= off) (NMOS= 50%) |

| 01011_(11) | LED (PMOS) on-time 20% | 11011_(27) | Motor(s3)(PMOS= off) (NMOS= 80%) |

| 01100_(12) | LED (PMOS) on-time 50% | 11100_(28) | Motor(s3)(PMOS= on) (NMOS= off)  |

| 01101_(13) | LED (PMOS) on-time 80% | 11101_(29) | Motor(s2)(PMOS= off) (NMOS= 20%) |

| 01110_(14) | LED (NMOS) dimming 20% | 11110_(30) | Motor(s2)(PMOS= off) (NMOS= 50%) |

| 01111_(15) | LED (NMOS) dimming 50% | 11111_(31) | Motor(s2)(PMOS= off) (NMOS= 80%) |

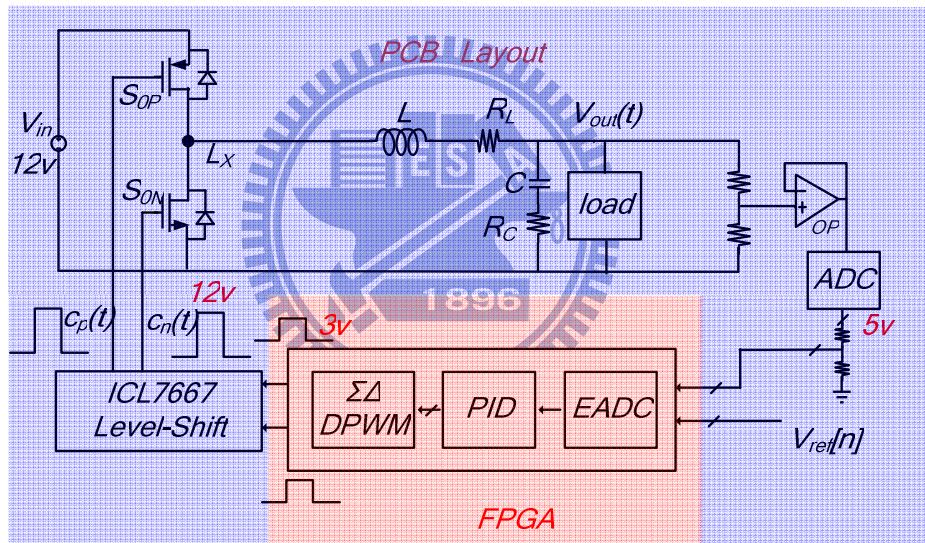

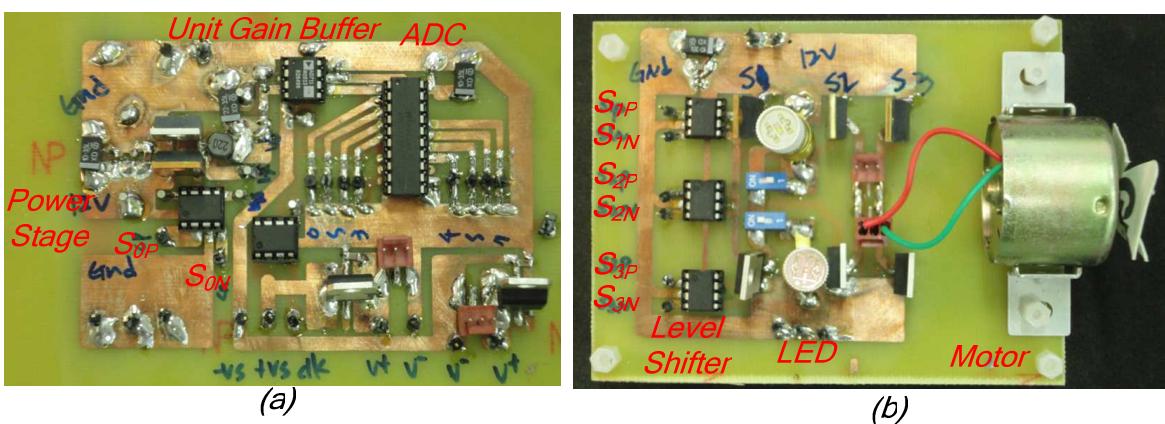

如下圖 62 所示為直流-直流降壓電路圖，FPGA 所輸出的訊號為 3V 脈波寬度調變經由電壓準位移位器 ICL7667(Level Shifter)升為 12V 來推動 P 型的功率晶體 IRF9Z34N 及 N 型的功率晶體 IRFZ34N，在功率區塊的電感採用的是功率電感 SCD0504 可承受 1A 的電流，直流電阻(DCR)為 180 m 歐姆。輸出電容採用的是 Vishay Sprague 的鉛值電容，輸出電容的等效串聯電容(ESR)大約為 200m 歐姆。經由每一週期充放電輸出電壓經由衰減器和一單位增益緩衝器 AD711 到類比數位轉換器 ADC0820CCN，最後類比數位轉換器輸出再接回 FPGA 的輸入。下圖 63(a)為直流-直流降壓電路的硬體部分，圖 63(b)為馬達及 LED 的硬體。

圖62. 直流-直流降壓印刷電路板子元件佈局圖

圖63. (a)直流-直流降壓印刷電路板子實際圖(b)馬達及 LED 印刷電路板子實際圖

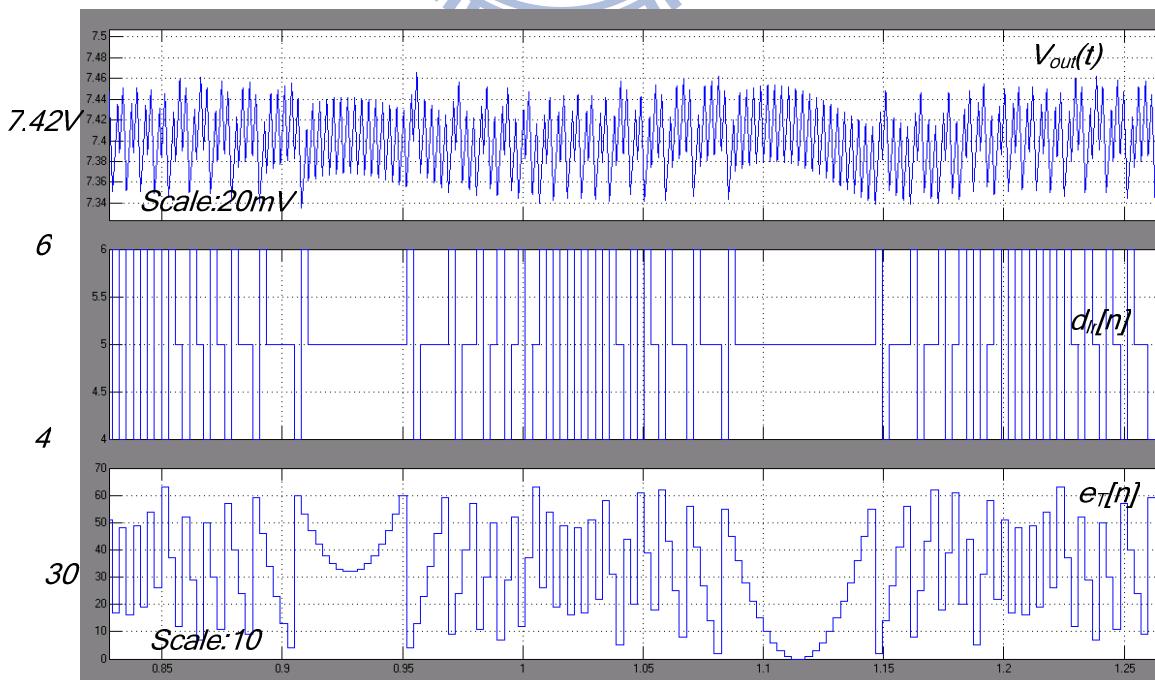

## 5.2 直流-直流降壓電路驗證

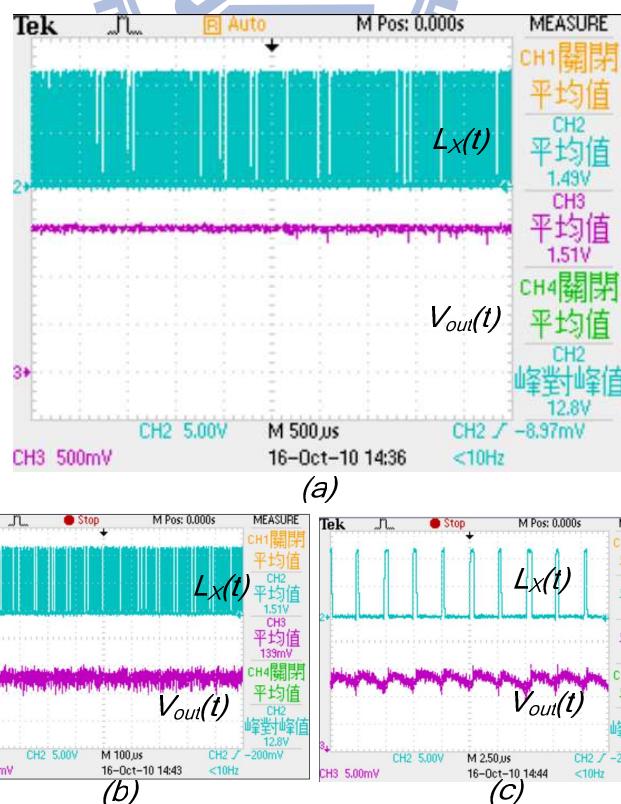

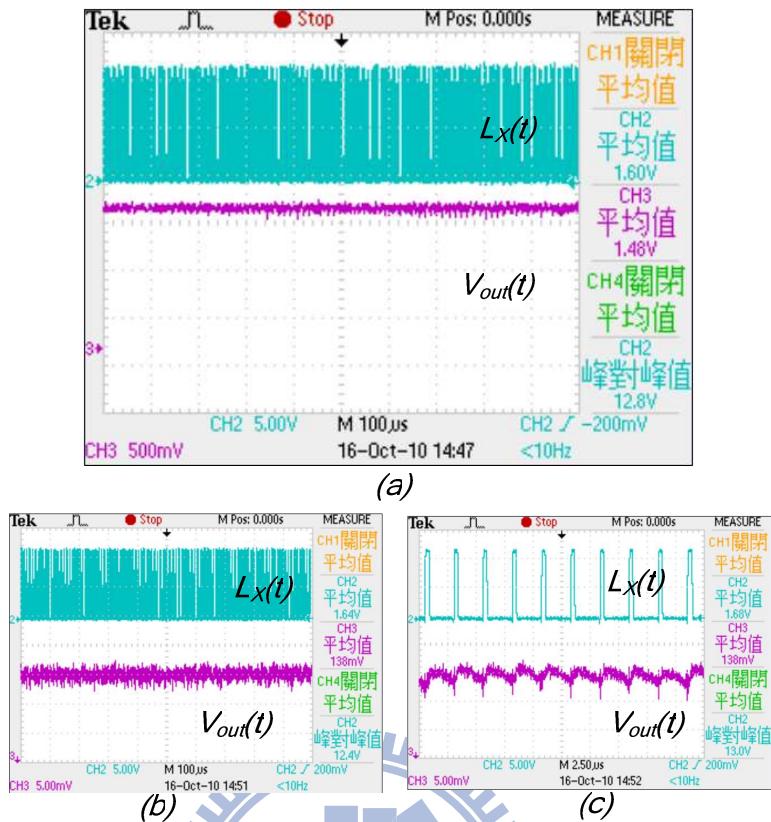

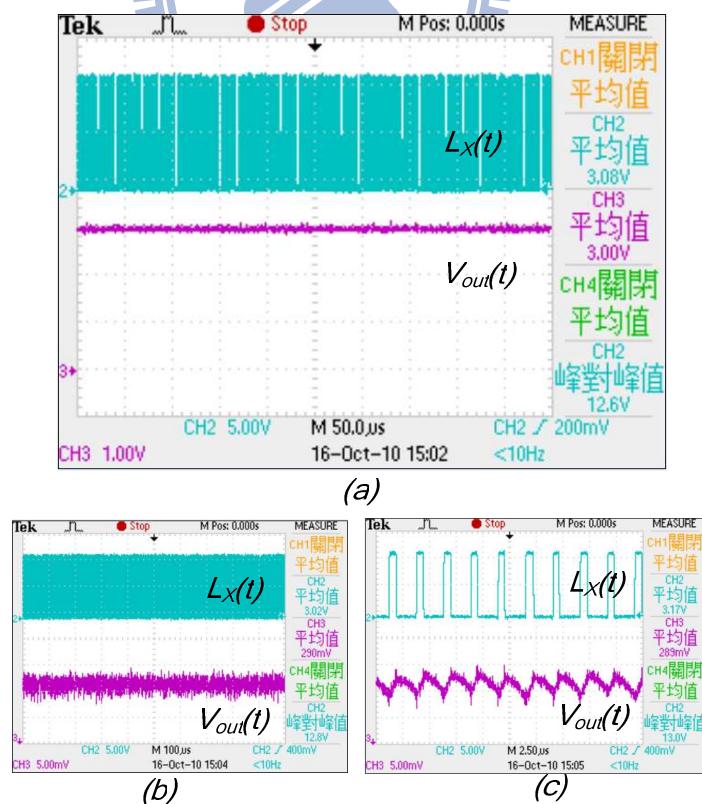

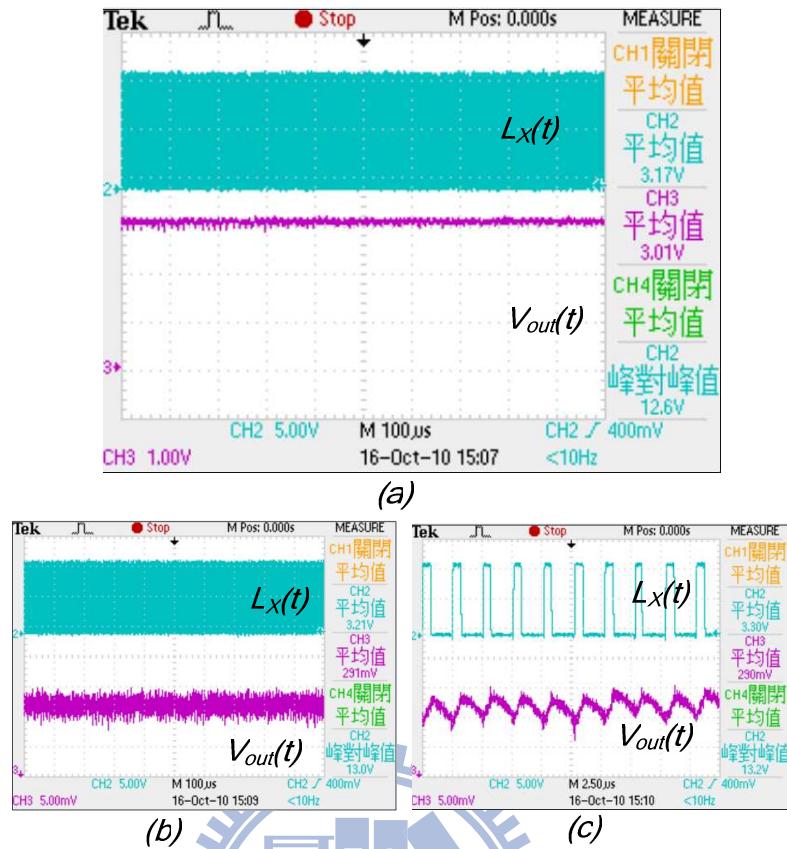

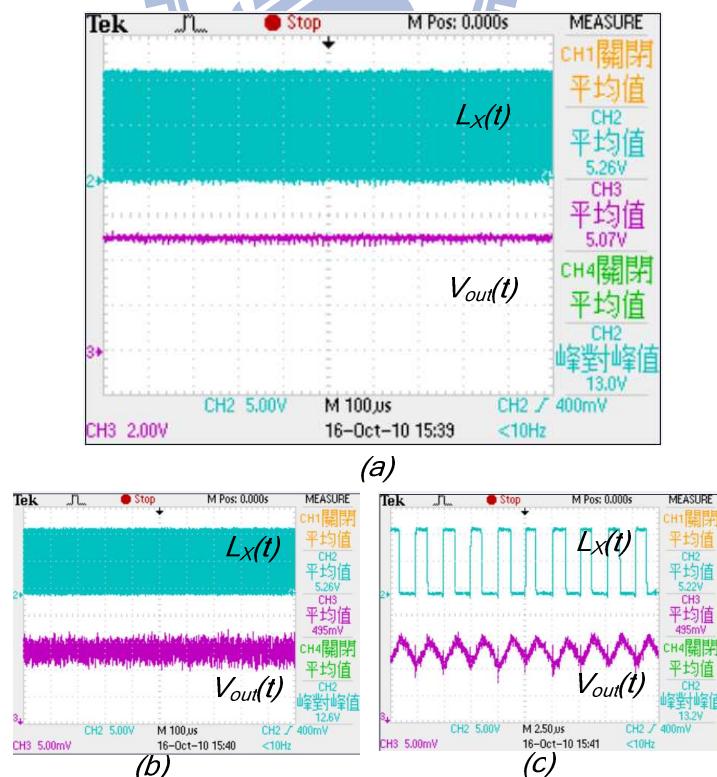

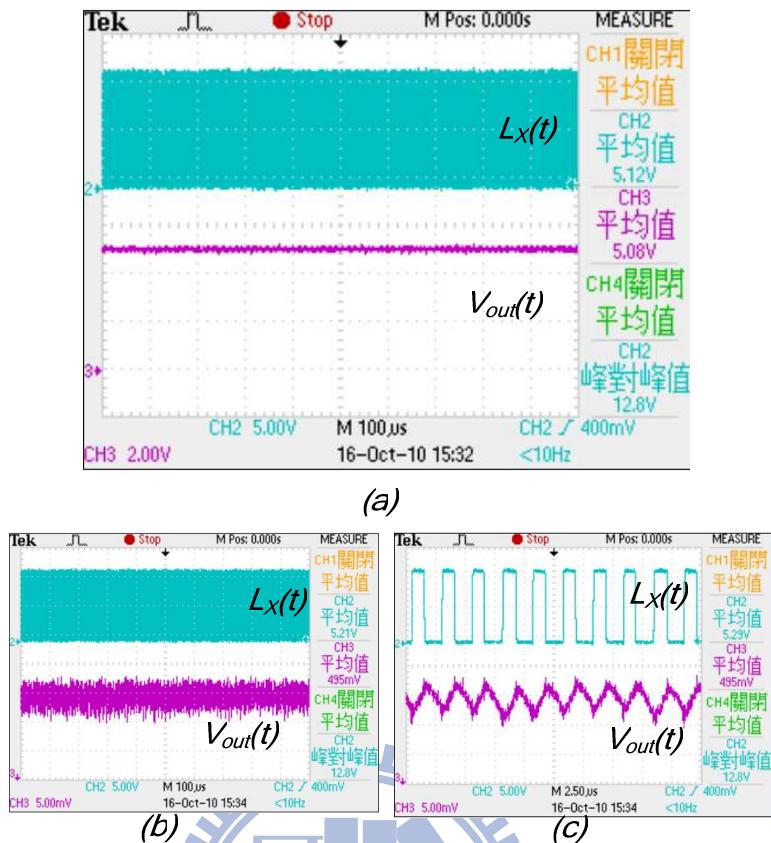

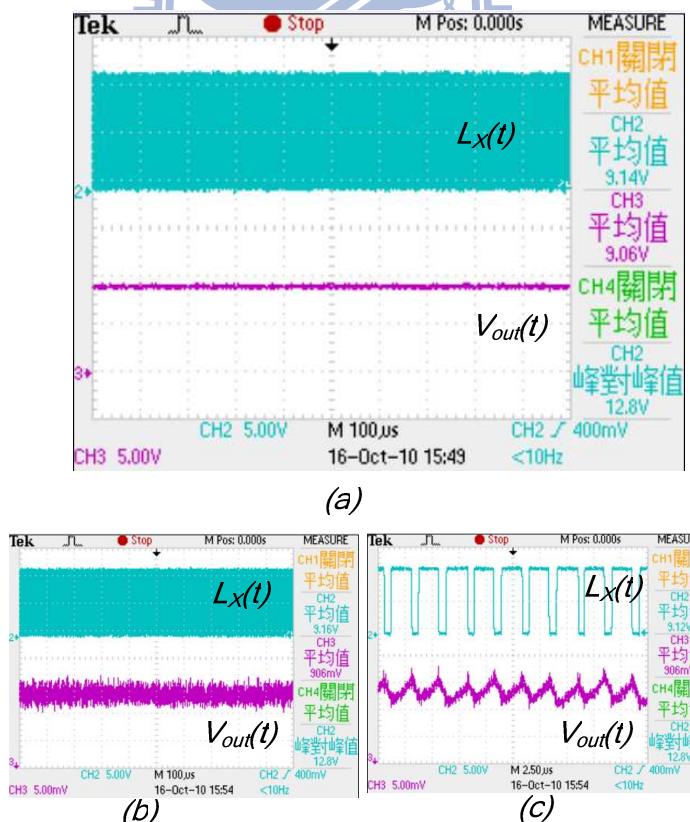

在這一章節主要是驗證直流-直流降壓電路在不同的負載及不同的輸入電壓，將輸出鎖定在 1.5~9V 並且觀察輸出電壓的漣波大小。如表 8 所示為輸入電壓為 12V，輸出電壓在不同的負載下所觀察的輸出電壓的漣波大小。這邊的抽載所使用的是在輸出電壓上掛一水泥電阻達到抽載的效果，圖 64~71 所示為輸出電壓鎖在 1.5~9V，圖 64~71(a)可觀察輸出電壓的平均值，圖 64~71 (b)將探棒(probe)的刻度調乘於 10 倍，故示波器為每一格為  $5\text{mV} \times 10 = 50\text{mV}$ ，由此可觀察到輸出電壓的漣波大小，圖 64~71 (c)所示為輸出電壓在每一週期的充放電狀態。

表8. 輸入電壓為12V，輸出電壓在不同的負載的性能表現

| $V_{out}$                     | 1.5V             | 3V               | 5V               | 9V               |

|-------------------------------|------------------|------------------|------------------|------------------|

| $\Delta V_{out}$<br>(no load) | 48mV             | 65mV             | 80mV             | 65mV             |

| $\Delta V_{out}$<br>(load)    | 48mV<br>( 500mA) | 65mV<br>( 600mA) | 80mV<br>( 500mA) | 65mV<br>( 600mA) |

圖64. 輸出 1.5V(no load) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電

圖65. 輸出 1.5V(load=500mA) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電圖66. 輸出 3V(no load) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電

圖67. 輸出 3V(load=600mA) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電圖68. 輸出 5V(no load) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電

圖69. 輸出 5V(load=500mA) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電圖70. 輸出 9V(no load) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電

圖71. 輸出 9V(load=600mA) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電

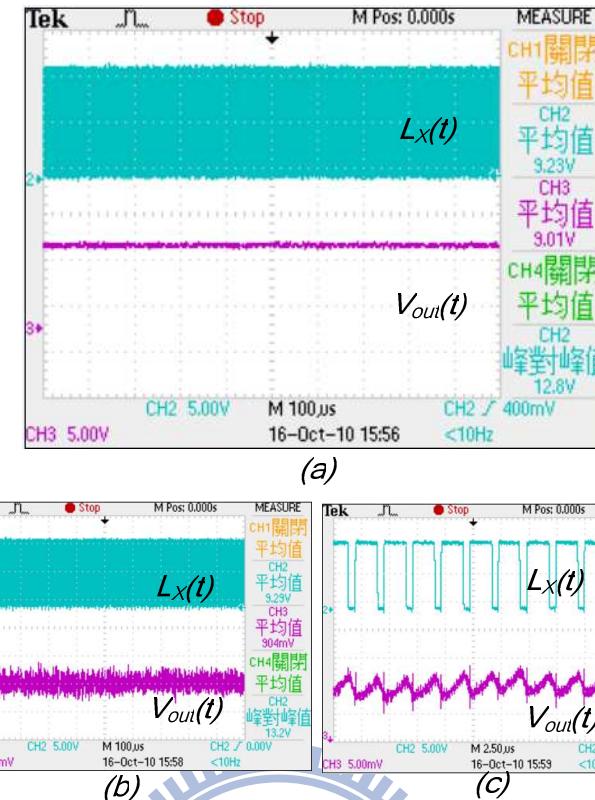

接下來則是不同的輸入電壓，將輸出鎖定在 1.5~9V 並且觀察它的輸出電壓的漣波大小。如表 9 所示為輸出電壓在不同的電壓下所觀察的輸出電壓的漣波大小。圖 72~75 所示為輸出電壓鎖在 1.5~9V，圖 72~75 (a)可觀察輸出電壓的平均值，圖 72~75 (b)將探棒(probe)的刻度調乘於 10 倍，故示波器為每一格為  $5mV \times 10 = 50mV$ ，由此可觀察到輸出電壓的漣波大小，圖 72~75 (c)所示為輸出電壓再每一週期的充放電狀態。

表9. 在無負載狀態下，輸出電壓在不同輸入電壓的性能表現

| $V_{out}$                     | 1.5V                     | 3V                       | 5V                       | 9V                       |

|-------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| $\Delta V_{out}$<br>(no load) | 48mV<br>( $V_{in}=12V$ ) | 65mV<br>( $V_{in}=12V$ ) | 80mV<br>( $V_{in}=12V$ ) | 65mV<br>( $V_{in}=12V$ ) |

| $\Delta V_{out}$<br>(no load) | 45mV<br>( $V_{in}=5V$ )  | 45mV<br>( $V_{in}=5V$ )  | 40mV<br>( $V_{in}=6V$ )  | 45mV<br>( $V_{in}=10V$ ) |

圖72. 輸出 1.5V( $V_{in}=5V$ ) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電圖73. 輸出 3V( $V_{in}=5V$ ) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電

圖74. 輸出 5V( $V_{in}=6V$ ) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電圖75. 輸出 9V( $V_{in}=10V$ ) ,  $V_{out}(t)$  (a)平均值 (b)漣波大小 (c)每週期充放電

## 5.3 馬達及 LED 驗證

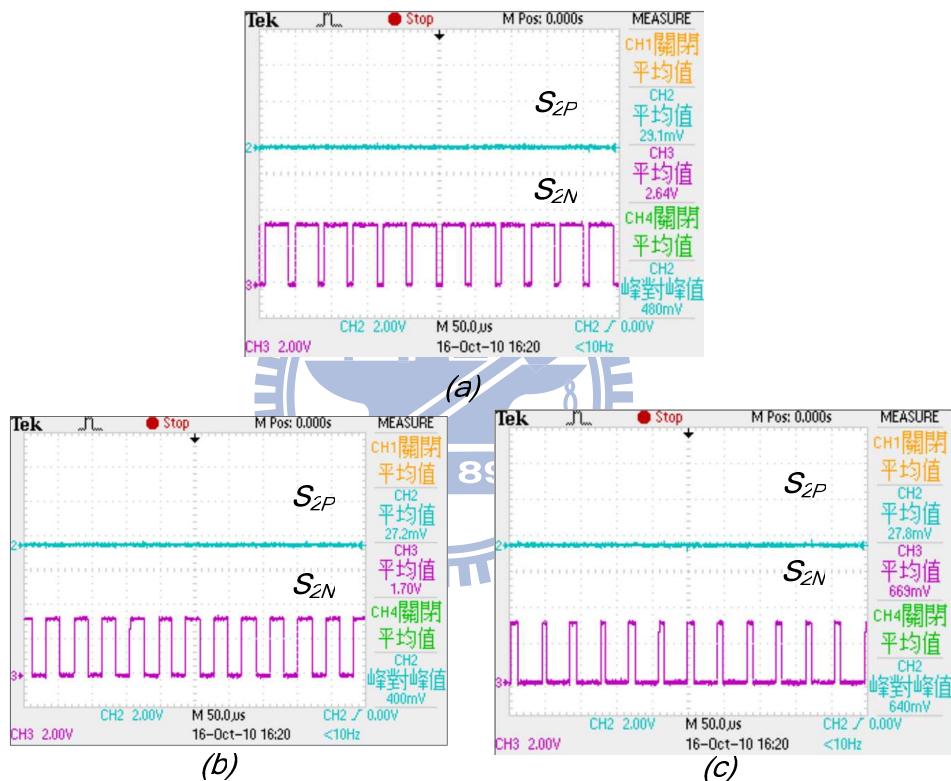

如下圖 76 所示為馬達轉速的驗證，我們利用表給控制訊號，馬達操作頻率為 24kHz，這邊 P 型功率晶體為關閉狀態，N 型功率晶體為脈波寬度的調變。由於電壓準位移位器(Level Shifter)為反向，下圖所測的波形為 FPGA 的輸出訊號還沒經過電壓準位移位器(Level Shifter)，因此可看到 S<sub>2P</sub> 為低電壓，S<sub>2N</sub> 為脈波調變。圖 76(a)為轉速 20%，圖 76(b)為轉速 50%，圖 76(c)為轉速 80%。

圖 76. 馬達轉速(a)轉速 20%(b)轉速 50%(c)轉速 80%

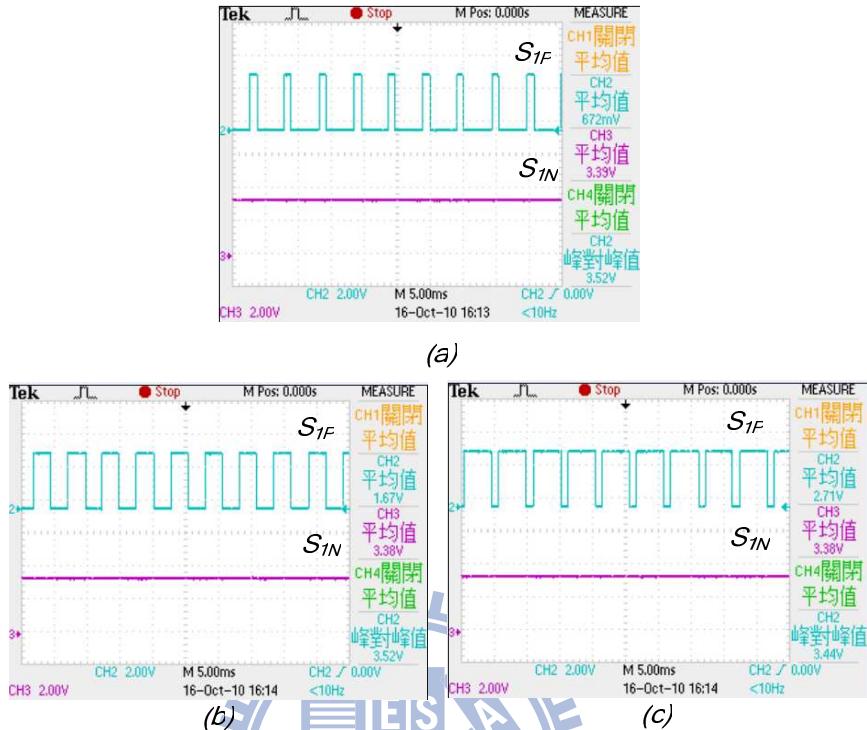

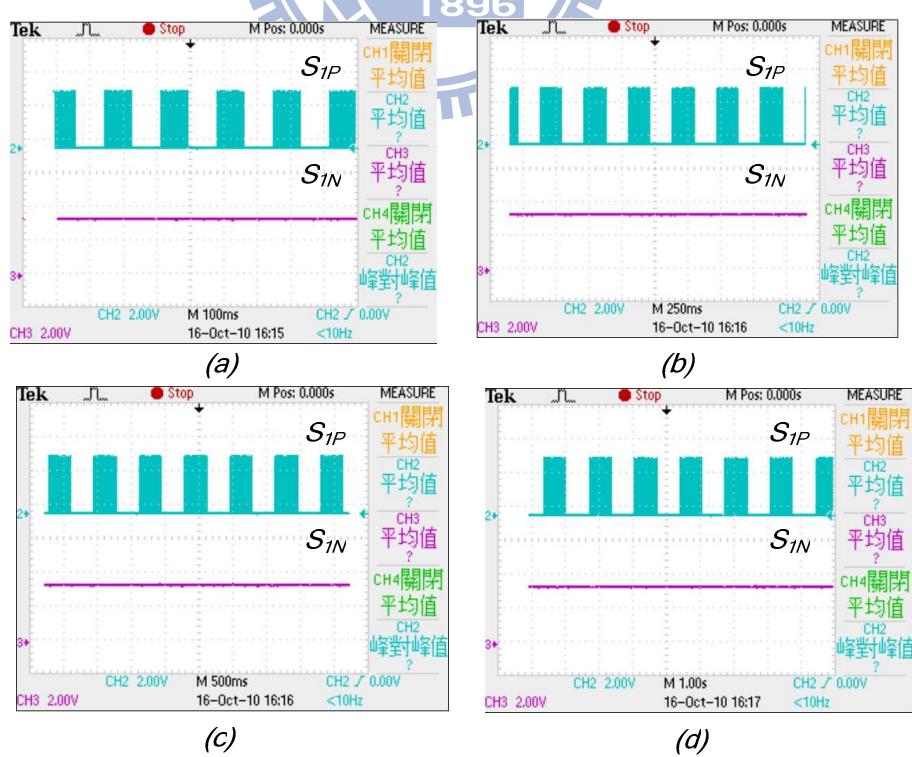

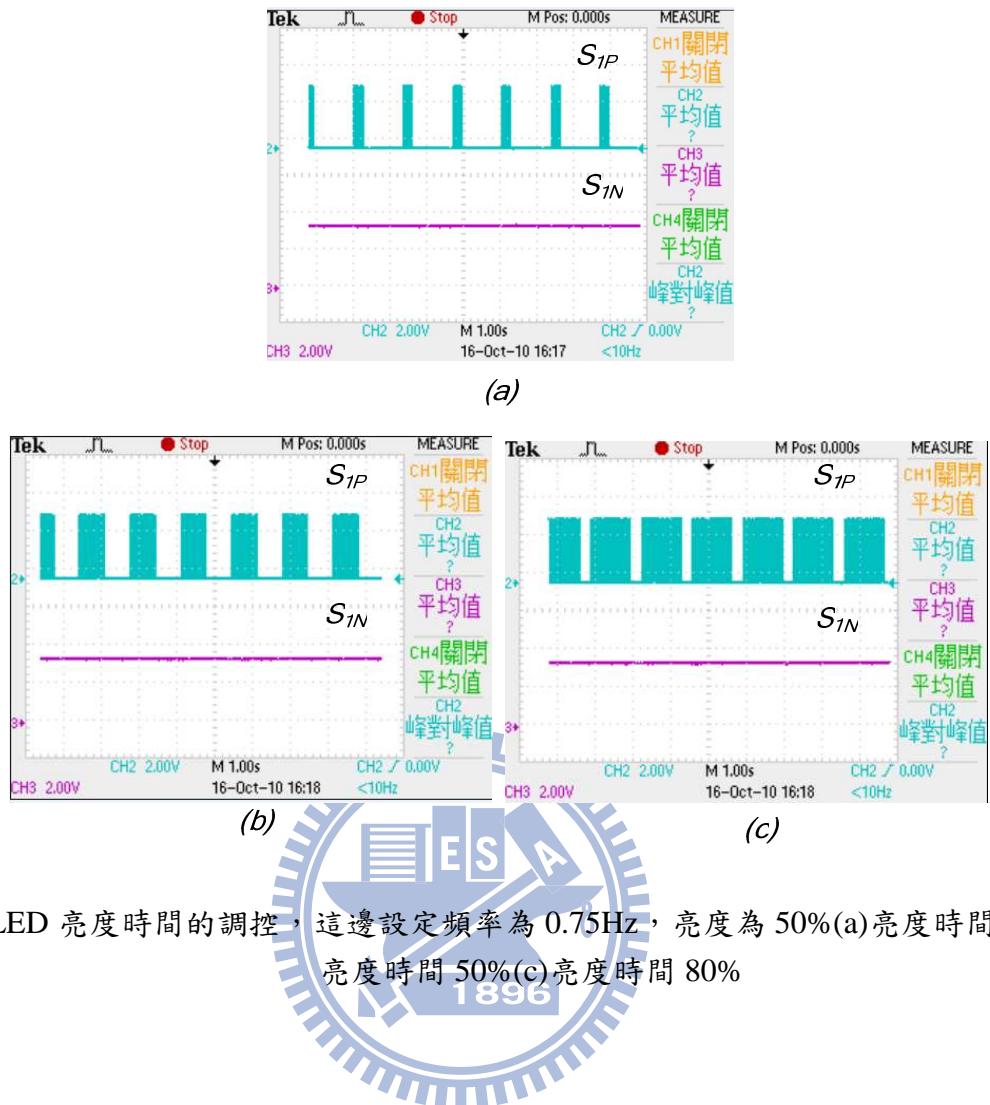

圖 77 所示為 LED 亮度的調控，由於人類看不到的閃爍頻率大約要 150Hz 以上，這邊的頻率為 190Hz，圖 77(a)為亮度 20%，圖 77(b)為亮度 50%，圖 77(c)為亮度 80%。圖 78 為 LED 頻率的調控，這邊的亮度調變為 50%，圖 78(a)為頻率 6Hz，圖 78(b)為頻率 3Hz，圖 78(c)為頻率 1.5Hz，圖 78(d)為頻率 0.75Hz。最後則是 LED 亮度時間的調控，這邊設定頻率為 0.75Hz，亮度為 50%，圖 79(a)為亮度時間 20%，圖 79(b)為亮度時間 50%，圖 79(c)為亮度時間 80%。

圖 77. LED 亮度的調控圖(a)亮度 20% (b)亮度 50% (c)亮度 80%

圖 78. LED 頻率的調控(a)頻率 6Hz(b)頻率 3Hz(c)頻率 1.5Hz(d)頻率 0.75Hz

圖 79. LED 亮度時間的調控，這邊設定頻率為 0.75Hz，亮度為 50% (a) 亮度時間 20% (b)

亮度時間 50% (c) 亮度時間 80%

# 第六章

## 結論

在這一篇論文當中提出了可程式車用功率積體電路，晶片的控制訊號經由電源線傳送共有 32 位元，裡面包含了有晶片位址、清除開關訊號、系統開閉迴路選擇、開關選擇、PN 功率晶體動作、頻率、亮度時間、控制馬達轉速、LED 亮度及降壓電路的控制。由於功率驅動晶片共有 4 組的輸出控制訊號，每一組分別為控制 P 功率晶體及 N 功率晶體。這邊希望每一組的控制訊號皆能控制馬達、LED 及降壓電路，在分別控制馬達、LED 及降壓電路可了解到它們有共通的電路則是數位脈波寬度調變。在此論文採用的則是二階的  $\Sigma\Delta$  雜訊整形迴路數位脈波寬度調變電路，在前面章節有提到它的許多優點，分別為低功率消耗、可操作在高速、在這邊最主要是能將馬達、LED 及降壓電路結合在一起，節省多餘的面積及功率消耗。

最後我們使用 FPGA 來驗證整體系統的可行性，Spartan 3A 及 Spartan 3E 來當作車用電子電源線通訊的接收端及傳輸端，電源線則是傳送指令進而達到降壓電路輸出電壓鎖定、控制馬達的轉速控制及 LED 的亮度調控、閃爍頻率及亮度時間的調控。

# 參考文獻

- [1] D. M. R.W.Erickson, *Fundaments of Power Electronics*, 2nd ed.: Kluwer Academic, Inc, 2001.

- [2] C. Basso, *Switch-mode power supplies*, 2008.

- [3] D. K. Johns, Martin, *Analog integrated circuit design*, 1997.

- [4] R. Schreier, *Understanding delta-sigma data converters*, 2005.

- [5] R. Dorf, *Modern control systems*, 1998.

- [6] P.-K. Leong, "Design of Sigma-Delta DPWM Controller for 1MHz DC-DC Switch-Mode Power Supplies," NCKU, Taiwan, 2009-01-10

- [7] B. J. Patella, *et al.*, "High-frequency digital PWM controller IC for DC-DC converters," *IEEE Transactions on Power Electronics*, vol. 18, pp. 438-446, 2003.

- [8] P. Hao, *et al.*, "Modeling of quantization effects in digitally controlled DC-DC converters," in *IEEE Transactions on Power Electronics*, 2004, pp. 4312-4318 Vol.6.

- [9] Z. Lukic, *et al.*, "Multi-bit sigma-delta PWM Digital Controller IC for DC-DC Converters Operating at Switching Frequencies Beyond 10 MHz," *IEEE Transactions on Power Electronics*, vol. 22, pp. 1693-1707, 2007.

- [10] L. Pui-Kei, *et al.*, "Design and implementation of sigma-delta DPWM controller for switching converter," in *IEEE International Symposium on Circuits and Systems*, 2009, pp. 3074-3077.

- [11] Y. Duan and H. Jin, "Digital controller design for switchmode power converters," in *APEC '99. Fourteenth Annual*, 1999, pp. 967-973 vol.2.

- [12] C. Phillips, *Digital control system analysis and design*, 1990.

- [13] A. Oppenheim, *Discrete-time signal processing*, 2010.

- [14] A. Prodic and D. Maksimovic, "Design of a digital PID regulator based on look-up tables for control of high-frequency DC-DC converters," in *IEEE on Power Electronics*, 2002, pp. 18-22.

- [15] A. V. Peterchev and S. R. Sanders, "Quantization resolution and limit cycling in digitally controlled PWM converters," *IEEE Transactions on Power Electronics*, vol. 18, pp. 301-308, 2003.

- [16] A. Prodic, *et al.*, "Design and implementation of a digital PWM controller for a high-frequency switching DC-DC power converter," in *Industrial Electronics Society*, 2001, pp. 893-898 vol.2.

- [17] A. Syed, *et al.*, "Digital pulse width modulator architectures," *IEEE 35th Annual Power Electronics Specialists Conference*, 2004, pp. 4689-4695 Vol.6.

- [18] N. Mohan, *Power electronics: converters, applications, and design, third edition*, 2003.

- [19] A. Prodic and D. Maksimovic, "Mixed-signal simulation of digitally controlled switching converters," *IEEE Computers in Power Electronics*, 2002, pp. 100-105.

- [20] W. Chou and R. M. Gray, "Dithering and its effects on sigma-delta and multistage sigma-delta modulation," *IEEE Transactions on Information Theory*, vol. 37, pp. 500-513, 1991.

- [21] A. Syed, *et al.*, "Digital PWM controller with feed-forward compensation," in *IEEE Nineteenth Annual Applied Power Electronics Conference and Exposition*, 2004, pp. 60-66 Vol.1.

- [22] S. Choudhury, "Digital Control Design and Implementation of a DSP Based High-Frequency DC-DC Switching Power Converter," Texas Instruments Inc.

- [23] A. Prodic and D. Maksimovic, "Digital PWM controller and current estimator for a low-power switching converter," *Computers in Power Electronics*, 2000, pp. 123-128.

- [24] L. Chi-Wai, *et al.*, "An integrated GUI design tool for digitally controlled switching DC-DC converter," *ICCCAS 2008. International Conference on Communications, Circuits and Systems*, 2008, pp. 1324-1327.