國立交通大學

電子物理學系

碩士論文

符合於 IEEE802.11b

互補式金氧半頻率合成器設計

The Design of CMOS Frequency Synthesizer

for IEEE802.11b

研究生：黃賢生

指導教授：謝太炯 博士

中華民國九十三年七月

符合於 IEEE802.11b 互補式金氧半頻率合成器設計

The Design of CMOS Frequency Synthesizer for IEEE802.11b

研究 生:黃 賢 生

Student : Hsien-Sheng Huang

指 導 教 授:謝 太 炯 博 士

Advisor : Dr. Tai-Chiung Hsieh

國 立 交 通 大 學

理 學 院

電 子 物 理 學 系

碩 士 論 文

Submitted to Institute and Department of Electrophysics

College of Science

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of Master in Electrophysics

July 2004

HsinChu, Taiwan, Republic of China

中 華 民 國 九 十 二 年 七 月

# 符合於 IEEE802.11b 互補式金氧半頻率合成器設計

研究生：黃賢生

指導教授：謝太炯 博士

國立交通大學電子物理學系碩士班

## 摘要

本論文研究一個符合 IEEE802.11b 的互補式金氧半頻率合成器之設計。電路主要透過國家晶片系統中心，以台灣積體電路製造股份有限公司提供的  $0.25\mu\text{m}$  製程技術來實現。我們所設計的頻率合成器為雙電荷峯浦的架構，包含四相位輸出之壓控振盪器、除頻器、相位頻率偵測器、電荷峯浦及低通濾波器，操作電壓為  $2.5\text{V}$ 。所設計的頻率合成器經由 ADS 模擬，顯示電路可以正常工作，其中壓控振盪器除了模擬外，晶片也製作量測完成。

模擬結果顯示，所設計的頻率合成器在  $2.5\text{V}$  的工作電壓下，參考訊號為  $10\text{MHz}$ ，輸出頻率為  $2.4\text{GHz}$  到  $2.526\text{GHz}$ ，每  $10\text{MHz}$  一個間隔，共為 64 個頻率，輸出功率大小  $-6\text{dBm}$ ，共消耗功率約  $53.76\text{mW}$ 。壓控振盪器的模擬結果輸出頻率從  $2.25\text{GHz}$  到  $2.68\text{GHz}$ ，增益約為  $-450\text{MHz/V}$ ，輸出功率最大可到  $-5.29\text{dBm}$ ，四個輸出彼此間隔  $90^\circ$ ，而總消耗功率為  $48.41\text{mW}$ 。其相位雜訊在  $100\text{kHz}$  時為  $-98.28\text{dBc/Hz}$ 。壓控振盪器的晶片量測數據主要有：消耗功率為  $39.5\text{mW}$ ，輸出頻率範圍從  $2.097\text{GHz}$  到  $2.315\text{GHz}$ ，增益為  $-167\text{MHz/V}$ ，最大的輸出功率為  $-9.3\text{dBm}$ ，相位雜訊在  $100\text{kHz}$  時為  $-75.47\text{dBc/Hz}$ ，相位誤差為  $10.2^\circ$ 。

# The Design of CMOS Frequency Synthesizer for IEEE802.11b

Student: Hsien-Sheng Huang

Advisor: Dr. Tai-Chiung Hsieh

Institute and Department of Electrophysics

National Chiao Tung University

## Abstract

In this thesis, a CMOS frequency synthesizer is studied and designed to meet the IEEE802.11b standard. This frequency synthesizer has a two-charge-pump structure. It includes a quadrature voltage-controlled oscillator (VCO), frequency divider, phase frequency detector, charge pump and low-pass filter, and operates at 2.5-V power supply. The synthesizer circuit is simulated by ADS. The simulation results show that this circuit can fulfill the design specifications. Besides the simulation study, VCO is fabricated by TSMC 0.25  $\mu$ m process.

The designed frequency synthesizer can be operated well with 10-MHz reference frequency at 2.5-V power supply. ADS-simulation shows that this synthesizer deliver output frequency from 2.4 GHz to 2.526 GHz with a spacing 10 MHz. Its output power is -6 dBm and the total power consumption is 53.76 mW. The quadrature VCO's simulation results reveal that the output frequencies are tunable from 2.25 GHz to 2.68 GHz, and VCO's gain is about -450 MHz/V. Its maximum output power is -5.29dBm, the phase difference of the four output is 90°, and the total power consumption is about 48.41 mW. The phase noise is -98.28 dBc/Hz at 100-kHz offset frequency. In the real chip implementation, the VCO has been measured with the output frequencies tunable from 2.097 GHz to 2.315 GHz. The VCO's gain is -167 MHz/V, and has total power consumption 39.5 mW. The maximum output power is -9.3dBm, the phase noise is -75.47 dBc/Hz at 100-kHz offset frequency and the phase difference of the VCO outputs is deviated from 90° by a magnitude of 10.2°.

# 誌 謝

本碩士論文能順利完成，首要感謝謝太炯老師在這兩年給予辛勤的指導，提供研究環境及自由的發展空間。使我在兩年的碩士學業生涯中，不管是在學問上或著生活態度上都深受薰陶。並感謝陳振芳教授、趙天生教授和高曜煌教授在課業上的教導並撥冗擔任我的口試委員，提供寶貴的意見。

感謝郭立民學長和趙靜軒學長在繁忙的工作中仍撥空來指導、給予意見，也感謝工研院量測中心和薛文崇學長在晶片量測上的協助及建議。

在求學過程中，感謝玉璽、柏獅、欽鴻、俊誌等學長曾經提供的幫助。感謝在實驗室一起度過豐富研究生生活的伙伴們，柏霖、善強、伯洋、宙穎及學弟俊穎和敬智，在每個禮拜的挑戰中增添了不少娛樂及點綴。感謝電物系羽球隊的隊友們，在大學和研究所六年有規律的運動和最溫暖的友情。

最感謝父母的養育、無悔的付出與關懷，妹妹和淑婷支持及陪伴，使我有最安穩的避風港，以健全的態度來面對各種挑戰。最後，僅以此論文獻給所有我感謝的人。

黃 賢 生

2004, 7 於新竹交大

# 目 錄

|           |      |

|-----------|------|

| 中文摘要..... | i    |

| 英文摘要..... | ii   |

| 誌謝.....   | iii  |

| 目錄.....   | iv   |

| 表目錄.....  | vii  |

| 圖目錄.....  | viii |

## 第一章 緒論

|                   |   |

|-------------------|---|

| 1.1 無線區域網路簡介..... | 1 |

| 1.2 論文目標與架構.....  | 3 |

## 第二章 頻率合成器系統架構與設計

|                         |    |

|-------------------------|----|

| 2.1 頻率合成器的架構與理論.....    | 5  |

| 2.1.1 一階頻率合成器線性模型.....  | 8  |

| 2.1.2 二階頻率合成器線性模型.....  | 9  |

| 2.1.3 三階頻率合成器線性模型.....  | 11 |

| 2.1.4 雙電荷容浦三階頻率合成器..... | 13 |

| 2.1.5 系統雜訊考量.....       | 15 |

| 2.2 系統設計考量.....         | 18 |

| 2.2.1 系統設計規格.....       | 18 |

| 2.2.2 系統設計架構.....       | 19 |

| 2.3 行為模型和模擬.....        | 20 |

## 第三章 電路設計實現與模擬

|       |                 |    |

|-------|-----------------|----|

| 3.1   | 壓控振盪器.....      | 24 |

| 3.1.1 | 壓控振盪器的基本理論..... | 24 |

| 3.1.2 | 相位雜訊.....       | 29 |

| 3.1.3 | 電路實現與設計考量.....  | 32 |

| 3.1.4 | 模擬結果一.....      | 38 |

| 3.1.5 | 佈局考量.....       | 41 |

| 3.1.6 | 模擬結果二.....      | 42 |

| 3.2   | 除頻器.....        | 43 |

| 3.2.1 | 除頻器架構.....      | 44 |

| 3.2.2 | 預除器.....        | 45 |

| 3.2.3 | 除頻器電路與設計考量..... | 49 |

| 3.2.4 | 模擬結果.....       | 51 |

| 3.3   | 相位頻率偵測器.....    | 54 |

| 3.3.1 | 操作原理與電路實現.....  | 54 |

| 3.3.2 | 模擬結果.....       | 56 |

| 3.4   | 電荷容浦和迴路濾波器..... | 57 |

| 3.4.1 | 設計考量與電路實現.....  | 57 |

| 3.4.2 | 模擬結果.....       | 60 |

| 3.5   | 頻率合成器.....      | 61 |

## 第四章 實驗及量測結果

|     |             |    |

|-----|-------------|----|

| 4.1 | 量測儀器架設..... | 64 |

| 4.2 | 量測結果.....   | 68 |

| 4.3 | 量測結果討論..... | 73 |

## 第五章 討論與結論

|     |         |    |

|-----|---------|----|

| 5.1 | 討論..... | 79 |

|-----|---------|----|

5.2 結論 ..... 80

參考資料 ..... 83

# 表 目 錄

|                            |    |

|----------------------------|----|

| 表 2.1 頻率合成器參數與計算及模擬結果..... | 22 |

| 表 2.2 行為模型模擬結果.....        | 23 |

| 表 3.1 壓控振盪器規格表.....        | 41 |

| 表 4.1 壓控振盪器的模擬與量測比較.....   | 78 |

| 表 5.1 頻率合成器穩定時間比較.....     | 80 |

# 圖 目 錄

|                                      |    |

|--------------------------------------|----|

| 圖 1.1 基本通訊系統接收機.....                 | 2  |

| 圖 2.1 (a)基本鎖相迴路 (b)頻率合成器.....        | 6  |

| 圖 2.2 電荷倉浦示意圖.....                   | 7  |

| 圖 2.3 頻率合成器線性模型.....                 | 7  |

| 圖 2.4 三階頻率合成器的濾波器.....               | 12 |

| 圖 2.5 雙電荷倉浦三階頻率合成器.....              | 14 |

| 圖 2.6 切換電容等效電阻.....                  | 14 |

| 圖 2.7 含雜訊源的頻率合成器模型.....              | 15 |

| 圖 2.8 相位雜訊表示圖.....                   | 18 |

| 圖 2.9 頻率合成器架構.....                   | 20 |

| 圖 2.10 行為模型的開/閉迴路大小響應.....           | 22 |

| 圖 2.11 行為模型的開/閉迴路相角響應.....           | 23 |

| 圖 2.12 行為模型的暫態響應.....                | 23 |

| 圖 3.1 負電阻振盪器概念圖.....                 | 25 |

| 圖 3.2 單一電晶體振盪器.....                  | 25 |

| 圖 3.3 計算輸入阻抗的小訊號模型.....              | 25 |

| 圖 3.4 並聯電阻電感轉串聯電阻電感.....             | 26 |

| 圖 3.5 交錯耦合電容電感振盪器.....               | 27 |

| 圖 3.6 輸出振幅與偏壓電流關係圖.....              | 29 |

| 圖 3.7 Leeson 模型的相位雜訊頻譜.....          | 30 |

| 圖 3.8 RC 網路四相位產生器.....               | 33 |

| 圖 3.9 (a) 振盪器與耦合差動對，(b) 簡單小訊號模型..... | 33 |

| 圖 3.10 兩個振盪器與耦合差動對串接的小訊號模型.....      | 33 |

|                                       |    |

|---------------------------------------|----|

| 圖 3.11 四相位輸出的交錯耦合振盪器.....             | 34 |

| 圖 3.12 本論文的四相位壓控振盪器.....              | 35 |

| 圖 3.13 PMOS 可變電容特性曲線圖.....            | 36 |

| 圖 3.14 四相位輸出波形.....                   | 38 |

| 圖 3.15 輸出訊號各諧波頻譜.....                 | 39 |

| 圖 3.16 相位雜訊頻譜.....                    | 39 |

| 圖 3.17 控制電壓對輸出頻率作圖.....               | 40 |

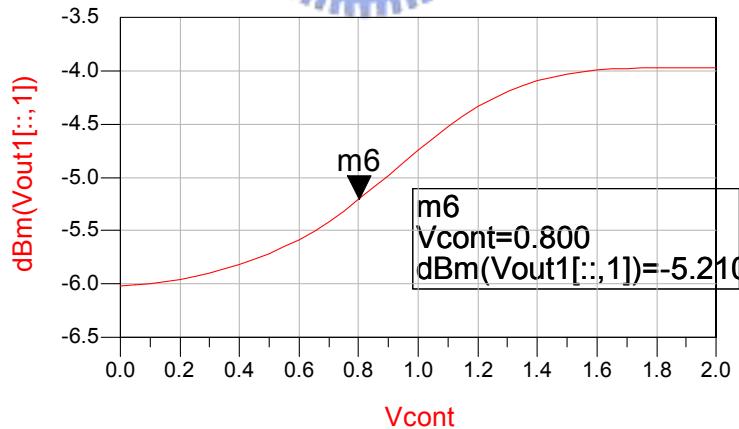

| 圖 3.18 輸出功率對控制電壓作圖.....               | 40 |

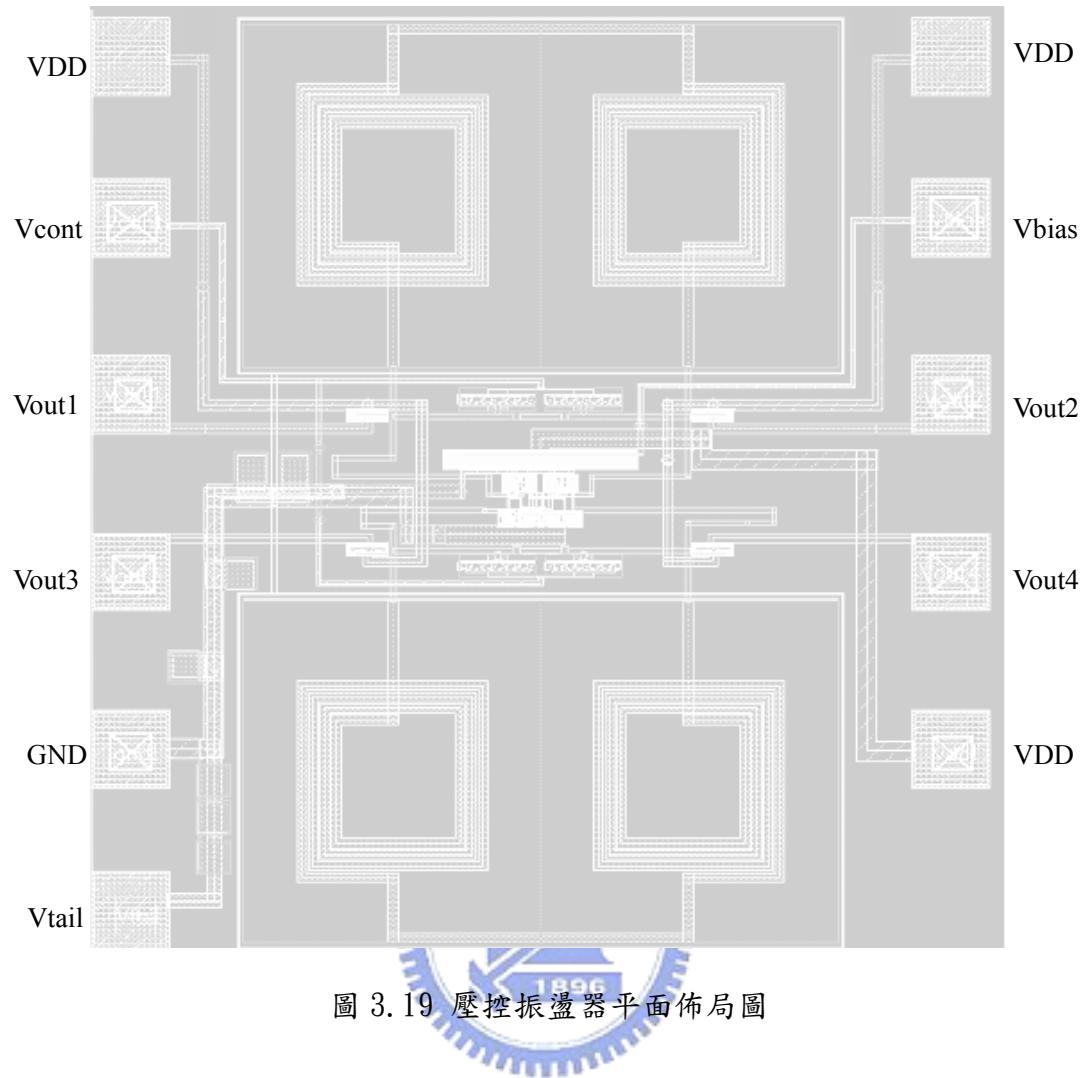

| 圖 3.19 壓控振盪器平面佈局圖.....                | 42 |

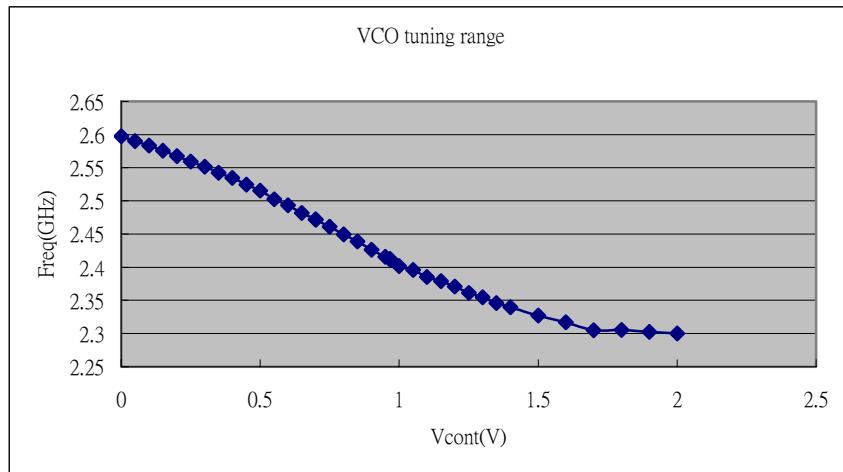

| 圖 3.20 新壓控振盪器的輸出頻率對控制電壓作圖.....        | 43 |

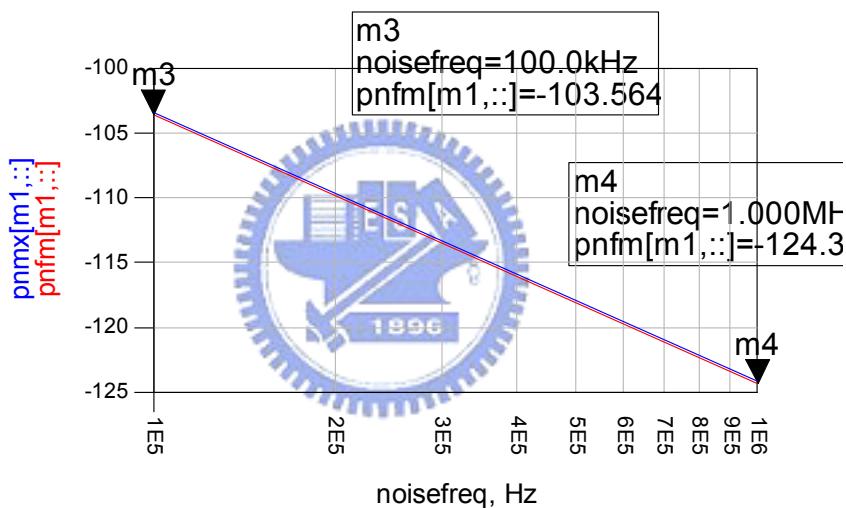

| 圖 3.21 新壓控振盪器的相位雜訊模擬結果.....           | 43 |

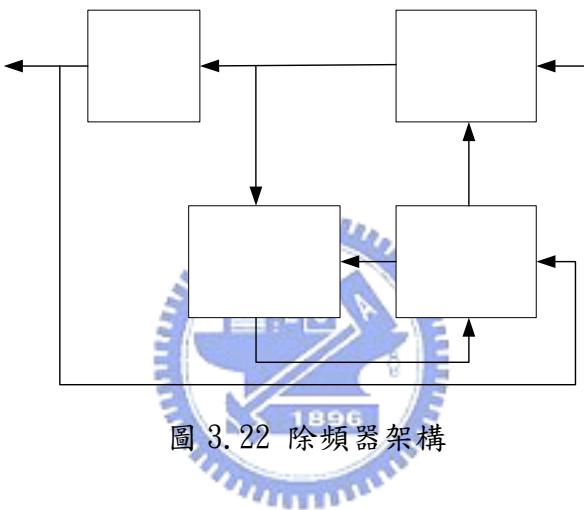

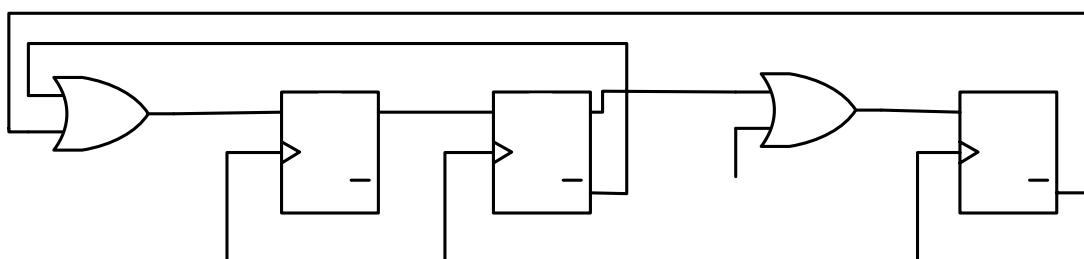

| 圖 3.22 除頻器架構.....                     | 44 |

| 圖 3.23 SCL D 正反器.....                 | 45 |

| 圖 3.24 頻率除二電路.....                    | 46 |

| 圖 3.24 除四除五電路.....                    | 48 |

| 圖 3.25 SCL OR 閘.....                  | 49 |

| 圖 3.26 完整除頻器電路.....                   | 50 |

| 圖 3.27 (a) 脈衝觸發器，(b) 脈衝觸發器的時序圖.....   | 50 |

| 圖 3.28 除頻器執行除 1202.....               | 52 |

| 圖 3.29 除頻器執行除 1215.....               | 53 |

| 圖 3.30 三態相位偵測器 (a) 操作波形，(b) 三態圖.....  | 54 |

| 圖 3.31 相位頻率偵測器 (a) 電路實現，(b) 操作波形..... | 55 |

| 圖 3.32 相位頻率偵測器模擬結果.....               | 56 |

| 圖 3.33 電荷容浦示意圖.....                   | 58 |

| 圖 3.34 電荷容浦和濾波器電路圖.....               | 58 |

| 圖 3.35 迴路濾波器.....                     | 59 |

|                                                                      |    |

|----------------------------------------------------------------------|----|

| 圖 3.36 電荷容浦與濾波器模擬結果.....                                             | 59 |

| 圖 3.37 簡單的緩衝器.....                                                   | 61 |

| 圖 3.38 緩衝器模擬結果.....                                                  | 62 |

| 圖 3.39 頻率合成器穩定時間模擬結果.....                                            | 63 |

| 圖 4.1 量測儀器架設圖.....                                                   | 64 |

| 圖 4.2 壓控振盪器晶片及微帶線電路.....                                             | 64 |

| 圖 4.3 晶片打線圖.....                                                     | 65 |

| 圖 4.4 偏壓電路板.....                                                     | 65 |

| 圖 4.5 偏壓電路圖.....                                                     | 65 |

| 圖 4.6 Wiltron Swept Frequency Synthesizer 67458 (100MHz~18GHz) ..... | 66 |

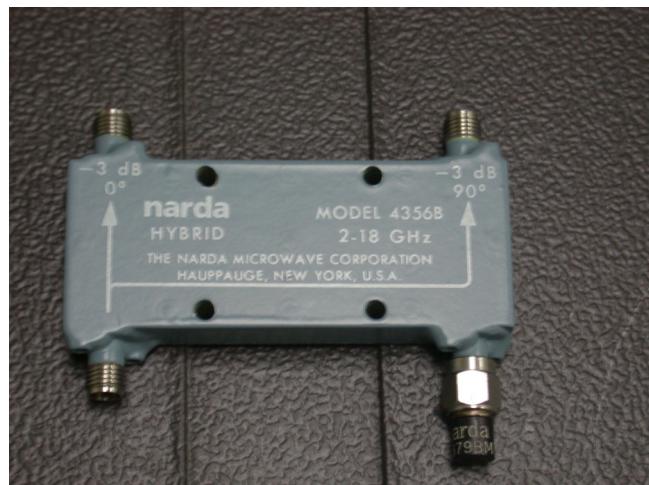

| 圖 4.7 Narda Hybrid 4356B (2~18GHz) .....                             | 66 |

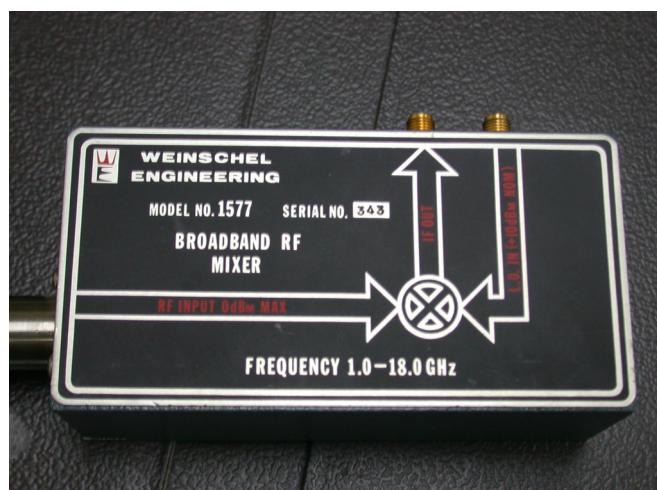

| 圖 4.8 WE Broadband RF Mixer 1577 (1~18GHz) .....                     | 66 |

| 圖 4.9 Narda Power Divider 4456.2 (2~18GHz) .....                     | 67 |

| 圖 4.10 四相位量測示意圖.....                                                 | 68 |

| 圖 4.11 振盪器在 2.2GHz 頻段的可調頻率範圍.....                                    | 69 |

| 圖 4.12 振盪器最大輸出功率-9.3dBm.....                                         | 70 |

| 圖 4.13 振盪器在 2.2GHz 頻段輸出功率與輸出頻率關係圖.....                               | 70 |

| 圖 4.14 振盪器在 2.2GHz 頻段的可調頻率範圍.....                                    | 70 |

| 圖 4.15 雙頻振盪現象.....                                                   | 71 |

| 圖 4.16 相位雜訊量測.....                                                   | 71 |

| 圖 4.17 四相位量測.....                                                    | 72 |

| 圖 4.18 可變電容漏電流.....                                                  | 73 |

| 圖 4.19 可調頻率範圍.....                                                   | 74 |

| 圖 4.20 相位雜訊.....                                                     | 74 |

| 圖 4.21 跳頻現象.....                                                     | 75 |

| 圖 4.22 外加刺激電流源.....                                                  | 75 |

圖 4.23 振盪器暫態分析 (3GHz) ..... 76

圖 4.24 振盪器暫態分析 (2.34GHz) ..... 76

# 第一章 緒論

## 1.1 無線區域網路與頻率合成器簡介

無線區域網路 (Wireless Local Area Network, WLAN) 發展至今日已十幾年的歷史，要求的傳輸速率與操作速度越來越快。在 1999 年由電機電子工程師協會 (The Institute of Electrical and Electronics Engineers, IEEE) 制訂了 IEEE802.11a 及 IEEE802.11b 兩種規格，分別操作在 5.2GHz 和 2.4GHz 兩個頻帶，傳輸速率分別為 54Mbps 和 11Mbps。而最新制訂的規格為 IEEE802.11g，其操作的頻率為 2.4GHz，傳輸速率為 54Mbps，並相容於以上兩種規格。由於 IEEE802.11b 相容於早先發表的規格 IEEE802.11，所以目前廣為使用。

IEEE802.11b 為單載波系統，使用直接序列展頻技術 (Direct Sequence Spread Spectrum, DSSS) 並且採用互補碼移位鍵 (Complementary Code Keying, CCK)，以達到 11Mbps 的傳輸速率。它所使用的頻帶從 2.412GHz 到 2.472GHz，間隔 10MHz 共七個通道。其最小的輸入大小敏感度 (minimum input level sensitivity) 為 -76dBm。

無線區域網路的規格都操作在很高的頻率，在這些高頻效應的影響之下，使用深次微米的 CMOS 製程對電路設計者的挑戰也相對較大。最新的 CMOS 製程也帶來許多好處，通道長度的縮短使得單位增益頻寬上升，較低的操作電壓使得消耗的功率減低，而且將系統各功能區塊整合到同一塊晶片上 (SOC) 以節省成本及

所佔體積。但這些好處也帶給設計者挑戰，如短通道效應，各元件的整合等。

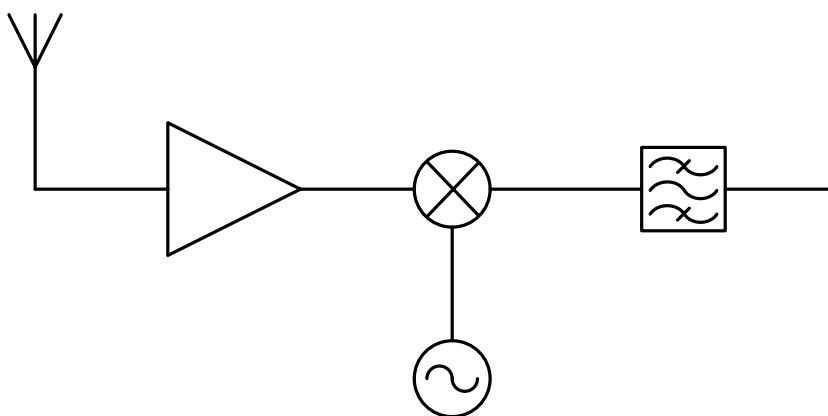

所謂的頻率合成器，是指可以產生所要的任何一個頻率。但是實際上我們所使用的頻率合成器只能產生某一段頻率範圍內的訊號，並且不是任何頻率，而是有最小的頻率間隔。這某一段頻率範圍和最小的頻率間隔，隨著不同的頻率合成器而有所不同。在無線通訊上，頻率合成器最重要的功能是用來選頻。如圖 1.1，當射頻訊號由天線接收進入接收機後，由低雜訊放大器將射頻訊號放大後，便與頻率合成器所提供的本地振盪訊號進行混波。混波之後，由帶通濾波器負責將不要的頻率濾除，使帶有我們想要訊息的中頻訊號通過，進入解調系統。我們若要選擇頻道，從帶通濾波器著手絕不會是好方法，因為一個可調的濾波器是昂貴，而且不能保證調整之後，一些基本特性能夠相同。因此我們需要一個頻率合成器產生可以變化頻率的本地振盪訊號，與想要的射頻訊號混波之後，變成一個固定的中頻訊號，此中頻訊號可以通過帶通濾波器。

圖 1.1 基本通訊系統接收機

在不同的通訊系統，對頻率合成器規格的要求也不一樣。但主要要求的規格

不外乎輸出頻率、頻率間隔、相位雜訊、頻率切換鎖定時間。不同架構的頻率合成器，在這些規格表現的優劣也會不同。在高頻的通訊系統中，主要所採用的是由鎖相迴路所組成的頻率合成器。在無線通訊的需求越來越強勁的同時，對這些規格的要求也越來越嚴格。在多人投入的研究下，低相位雜訊[1]、快速鎖定時間[2]的論文都陸續被發表了。使用分數型除頻器和 $\Sigma\Delta$ 調變來降低相位雜訊[3]和雙迴路式的頻率合成器[4]等更複雜的架構也越來越多人研究。而在我們的設計中，是要使用更經濟的方法，來達成快速的鎖定時間。

## 1.2 論文目標與架構

本論文是要實現一個符合 IEEE802.11b 規格的頻率合成器，所以工作頻率在 2.4GHz 附近，並且提供給直接轉換 (Direct Convergence or Zero IF) 架構的接收機使用。使用直接轉換架構的接收機有兩個優點，第一可以避免掉假像 (image) 的問題，因為中頻的頻率為 0；第二是 SAW 濾波器和後續的降頻電路都可以被一個低通濾波器和基頻放大器所取代，可以減少許多成本。而這個架構最重要的問題是直流偏移 (DC Offset)，雖然此問題可藉由高通濾波器和一些偏移消除的電路來減輕，但仍然為此架構重要的議題。對於頻率合成器來說，必須要提供七個不同的中心頻率、低相位雜訊和準確的四相位輸出給 I、Q 路徑。本論文所設計的頻率合成器是使用台積電 0.25 毫微米一層多晶矽五層金屬的 CMOS 製程，供給電壓為 2.5 伏特，輸出頻率從 2.4GHz 到 2.526GHz，頻率間隔為 2MHz，

輸入的參考頻率為 2MHz。整個電路由壓控振盪器 (Voltage-Control Oscillator, VCO)、除頻器 (Frequency Divider)、相位頻率偵測器 (Phase Frequency Detector, PFD)、電荷容浦 (Charge Pump, CP) 及低通濾波器 (Low-Pass Filter) 所組成。

接下來的幾個章節，將要介紹說明此電路如何實現完成。第二章要介紹這個頻率合成器是以鎖相迴路為基本架構，推導理論模型，並作行為分析模擬；第三章會把組合成頻率合成器的各個電路逐一詳細介紹並展現設計模擬結果；第四章是所下線晶片的量測方法、量測結果及結果討論；第五章則把整個設計結果作一個綜觀的檢討，以及未來可繼續研究的方向。

## 第二章 頻率合成器系統架構與設計

### 2.1 頻率合成器的架構與理論

在無線區域網路接收器或發射器中，頻率合成器是要提供一個本地振盪(L0)訊號來降頻選擇通道。一般來說，我們有三種實現頻率合成器的架構：1. 直接數位式頻率合成器（又稱為查表式頻率合成器）、2. 直接類比式頻率合成器、3. 非直接式鎖相頻率合成器。第一種合成器是利用記憶體將在合成頻率範圍的波形資料儲存在記憶體中，並使用時脈訊號將資料從記憶體中取出，經過數位類比轉換器和低通濾波器後輸出弦波波形。由於此種合成器最高的輸出頻率受限於時脈訊號的頻率和數位類比轉換器的頻寬，所以要來實現 GHz 級的合成器來說，是不實際的。第二種合成器是直接類比式合成器，它利用多級的混頻器和濾波器來合成一定頻率範圍內的訊號。由於此種合成器消耗不少的功率，對於現代通訊系統低功率設計要求下，是較難被接受的。

第三種合成器是使用鎖相迴路(Phase-Locked Loop, PLL)來完成頻率合成，與前兩種頻率合成器比較，第三種合成器在頻率之間相互切換的穩定時間較長。此種架構利用迴授的機制，使得輸出訊號的頻率會是輸入參考訊號頻率的一個固定倍數，並且因為迴授的關係，輸出頻率對於各元件中規格飄移敏感度很低。再者，輸出訊號會跟輸入參考訊號的相位有同調性，即使它們頻率並不相同但是此架構的穩定時間較長，而且在改變輸出頻率時，相位仍然是連續的。這是因為整

個電路須靠迴授的機制，來回不斷的校正，使輸出頻率達到輸入頻率的一個固定倍數。

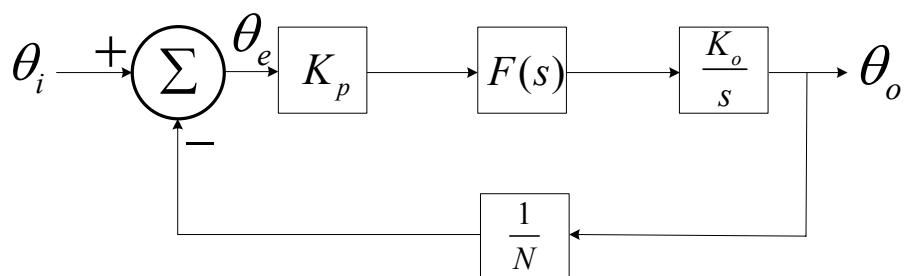

圖 2.1 (a)基本鎖相迴路 (b)頻率合成器

圖 2.1(a)是一個鎖相迴路的基本架構[5]。輸入訊號  $x(t)$  與輸出訊號  $y(t)$  同時進入相位偵測器 (Phase Detector)，比較兩個訊號之間的相位後，經低通濾波器到達壓控振盪器，調控其輸入電壓使其輸出訊號的相位改變。整個迴路直到輸出訊號與輸入訊號的相位差為零時，才會穩定。圖 2.1(b)是一個以鎖相迴

路為基礎的頻率合成器，除使用相位頻率偵測器和電荷容浦使整個迴路可鎖定的範圍加大致壓控振盪器的可調範圍之外，其在迴授路徑上多了一個除頻器。與前述鎖相迴路的原理相同，輸出訊號  $y(t)$  經除頻器後，頻率與  $x(t)$  的頻率相近，再經由相位頻率偵測器輸出  $x(t)$  與  $y(t)$  的不同以控制振盪器輸出訊號  $y(t)$  的頻率與相位。同樣的，直到經除頻器後的訊號與  $x(t)$  的頻率及相位皆相同時，迴

路便穩定。若除頻器的除數為  $N$ ，則  $y(t)$  的頻率即為  $x(t)$  的  $N$  倍。當  $x(t)$  的頻率是固定的，我們可以藉由改變不同的除數  $N$  來改變  $y(t)$  的頻率，但此輸出頻率受限於壓控振盪器的可調頻率範圍。

為提供精確低雜訊的參考訊號  $x(t)$ ，我們使用石英振盪器作頻率合成器的參考訊號源。一個低相位雜訊的參考訊號，會使得整個迴路輸出後的相位雜訊也很低，這在之後的章節會討論。在迴路中的低通濾波器，有很多實現方法，但在顧及到整個迴路步階響應的穩定性，只剩下幾種選擇。其中若使用運算放大器(OP amp) 來實現，會增加許多成本。因此我們選擇以電荷峯浦加上電阻電容來構成此濾波器。所謂電荷峯浦即根據相位頻率偵測器輸出的充電 (UP) 或放電 (DN) 訊號，提供固定電流來對後面的電阻電容作充電放電的動作，如圖 2.2 所示。

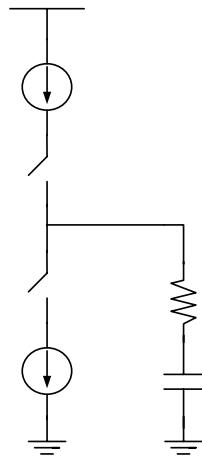

圖 2.2 電荷峯浦示意圖

圖 2.3 頻率合成器線性模型

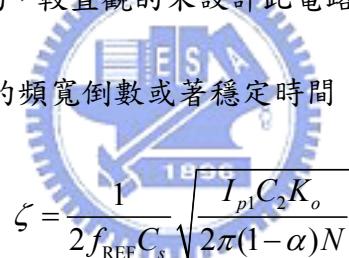

由上述的介紹，可以知道頻率合成器是一個高度非線性的系統。經過長期的研究發現，當整個迴路接近鎖定時，可以用線性微分方程來合理的預測其暫態行為。圖 2.3 為頻率合成器等效的線性模型， $\theta_i$  和  $\theta_o$  分別為輸入和輸出訊號的相位，由相位頻率偵測器所偵測的相位差  $\theta_e = \theta_i - \frac{\theta_o}{N}$ 。其中  $K_p = \frac{I_p}{2\pi}$  為相位頻率偵測器和電荷峯浦的增益， $I_p$  為電荷峯浦的電流，這是因為一個週期的最大相差角度為  $2\pi$ ，所以當此增益乘上  $\theta_e$ ，代表在這個週期內有多少時間是在進行充放電。 $F(s) = \frac{V(s)}{I(s)}$  表示低通濾波器的頻率響應。因為輸出相位  $\theta_o$  是振盪器輸出頻率的積分，所以壓控振盪器以積分器模型  $\frac{K_o}{s}$  代表， $K_o$  為其增益，單位為 Hz/V。

整個頻率合成器的開迴路轉換函數為

$$\frac{\theta_o(s)}{\theta_e(s)} = \frac{K_p F(s) K_o}{s} \quad (2.1)$$

，而閉迴路轉換函數為

$$\frac{\theta_o(s)}{\theta_i(s)} = \frac{N K_p K_o F(s)}{N s + K_p K_o F(s)} \quad (2.2)$$

### 2.1.1 一階頻率合成器線性模型

整個頻率合成器的階數是由開迴路增益其分母最高次項的次方所決定。若  $F(s)$  為常數時（在此令其為 1），則 (2.1) 為

$$\frac{\theta_o(s)}{\theta_e(s)} = \frac{K_p K_o}{s} \quad (2.3)$$

。所以可知當  $F(s)$  為常數時，此頻率合成器便為一階線性迴路。代入

$\theta_o = N(\theta_i - \theta_e)$ ，可以得到轉換函數為

$$\frac{\theta_e(s)}{\theta_i(s)} = \frac{Ns}{K_p K_o + Ns} \quad (2.4)$$

如果輸入訊號的頻率改變了  $\Delta\omega$ ，即輸入頻率為一個步階函數，對輸入相位來說， $\theta_i(s) = \frac{\Delta\omega}{s^2}$ 。將其代入 (2.4)，並利用終值定理求  $\theta_e$  的穩態值：

$$\theta_e(t)|_{t=\infty} = \lim_{s \rightarrow 0} s\theta_e(s) = \frac{N\Delta\omega}{K_p K_o}$$

(2.5)

因此，此一階線性迴路最終會存在一個不為零的相位誤差，而且依輸入訊號頻率改變間距的不同，會有不同的相位誤差。這個結果對我們的無線通訊系統來說是不樂見的。

### 2.1.2 二階頻率合成器線性模型

一個二階的迴路，其濾波器的部份通常如圖 2.2 接在電荷峯浦後的架構，由一個電阻和一個電容串連而成，則轉換函數  $F(s) = R + \frac{1}{sC}$ 。代入 (2.1) 可得二階迴路的開迴路轉換函數

$$\frac{\theta_o(s)}{\theta_e(s)} = \frac{K_p K_o (1 + RCs)}{Cs^2} \quad (2.6)$$

，所以此濾波器引進了一個在零頻的極點，並用另一個零點來增加其相角邊限 (Phase Margin)，使迴路的穩定度上升。如同上一小節，我們代入  $\theta_o = N(\theta_i - \theta_e)$  和  $\theta_i(s) = \frac{\Delta\omega}{s^2}$ ，使用終值定理可得

$$\theta_e(t)|_{t=\infty} = \lim_{s \rightarrow 0} s\theta_e(s) = \lim_{s \rightarrow 0} \left[ \frac{N C s^4}{\Delta\omega K_p K_o (1 + RCs) + \Delta\omega N C s^2} \right] = 0 \quad (2.7)$$

，所以二階的頻率合成器其穩態相位誤差為零。同樣的，更高階迴路的穩態相位誤差亦將為零。

接下來將探討當輸入訊號突然改變頻率的時候，輸出訊號多久可以轉換到相對應的頻率並穩定下來。將  $F(s)$  代入 (2.2) 可得閉迴路轉換函數

$$\frac{\theta_o(s)}{\theta_i(s)} = \frac{\frac{K_p K_o R (s + \frac{1}{RC})}{s^2 + \frac{K_p K_o R}{N} s + \frac{K_p K_o}{NC}}}{s^2 + Ks + K\omega_z} = \frac{NK(s + \omega_z)}{s^2 + Ks + K\omega_z} \quad (2.8)$$

，其中  $K = \frac{K_p K_o R}{N}$  、  $\omega_z = \frac{1}{RC}$  。在上式中假設  $\omega_z \ll K$  ，則可得轉換函數變成

$$\begin{aligned} \frac{\theta_o(s)}{\theta_i(s)} &\approx \frac{NK(s + \omega_z)}{s^2 + (K + \omega_z)s + K\omega_z} \\ &= \frac{NK(s + \omega_z)}{(s + K)(s + \omega_z)} = \frac{NK}{s + K} \end{aligned} \quad (2.9)$$

。所以二階頻率合成器的閉迴路頻寬約等於  $K$  ，這對以後設計頻率合成器時，會有一個很方便的估計。我們再把 (2.8) 改寫成另外一個形式

$$\frac{\theta_o(s)}{\theta_i(s)} = \frac{2N\zeta\omega_n(s + \frac{\omega_n}{2\zeta})}{s^2 + 2\zeta\omega_n s + \omega_n^2} \quad (2.10)$$

，其中  $\zeta = \frac{1}{2} \sqrt{\frac{K}{\omega_z}}$  和  $\omega_n = \sqrt{K\omega_z}$  為阻尼常數 (damping constant) 和自然頻率

(natural frequency)。當  $0 < \zeta < 1$  時，系統響應會先超過穩定值後，形成一個

衰減的振盪，最後衰減到穩定值，稱作欠阻尼 (under damping)；當  $\zeta > 1$  時，

系統會緩慢的趨近穩定值，稱為過阻尼 (over damping)；當  $\zeta = 1$  時，稱作臨界

阻尼 (critical damping)。由於欲觀察系統穩定時間，將  $\theta_i(s) = \frac{\Delta\omega}{s^2}$  代入 (2.10)，

並作拉氏反轉換：

$$\theta_o(t) = \frac{2N\zeta\omega_n}{\Delta\omega} \left\{ \frac{(1-4\zeta^2)\delta(t)\omega_n}{2\zeta} + \frac{e^{-t(\zeta\omega_n+\sqrt{(-1+\zeta^2)\omega_n^2})}\omega_n^2 [(-1+e^{2t\sqrt{(-1+\zeta^2)\omega_n^2}})(1-8\zeta^2+8\zeta^4)\omega_n + 4(1+e^{2t\sqrt{(-1+\zeta^2)\omega_n^2}})\zeta(-1+2\zeta^2)\sqrt{(-1+\zeta^2)\omega_n^2}]}{4\zeta\sqrt{(-1+\zeta^2)\omega_n^2} + \delta(t)} \right\} \quad (2.11)$$

(2.11) 看起來相當複雜，將  $t$  趨近於無限大， $\theta_o(t)$  也將趨近於零，且  $\theta_i(t)$  也趨近於零。所以相位誤差為零，此結果與 (2.7) 的結果相同。在  $t=0$  之後，總括號內的第一項為零，第二項的值主要由  $e^{-\zeta\omega_n t}$  來決定，而不管  $e^{-\zeta\omega_n t}$  或是後面括號內的部份都可以看出  $\zeta\omega_n$  越大， $\theta_o(t)$  也就越快接近於零。所以我們可以以  $(\zeta\omega_n)^{-1}$  來大致表示迴路的穩定時間，在設計頻率合成器的時候，若想要穩定時間越短，則要把  $\zeta\omega_n$  設計的越大。在此例中， $\zeta\omega_n = \frac{K}{2}$ ，所以也可得到頻寬越大，穩定時間越短的結論。

### 2.1.3 三階頻率合成器線性模型

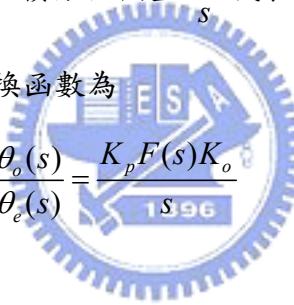

由於二階頻率合成器在追求快速穩定時間的同時，也犧牲了輸出的雜訊品質。由於參考輸入訊號會藉由相位頻率偵測器和電荷峯浦漏到振盪器的電壓控制端，使輸出頻譜在中心振盪頻率的附近產生旁波帶訊號 (Sideband signal)。為了防止或減少旁波帶訊號的產生，因此我們使用如圖 2.4 的濾波器，它會比圖 2.2 的濾波器多貢獻一個極點，可以衰減穿透過來的參考訊號。可以導出此濾波器的轉換函數

$$F(s) = \frac{1}{C_1} \frac{s + \omega_z}{s(s + \omega_p)} \quad (2.12)$$

其中  $\omega_z = \frac{1}{RC_2}$  、 $\omega_p = \frac{C_1 + C_2}{RC_1 C_2}$ 。將 (2.12) 代入 (2.1) 可得開迴路轉換函數

$$\frac{\theta_o(s)}{\theta_e(s)} = \frac{K_p K_o}{C_1} \frac{(s + \omega_z)}{s^2(s + \omega_p)} \quad (2.13)$$

可以看出由此濾波器構成的頻率合成器其開迴路轉換函數分母是三階。因為在頻率為零時，有兩個極點，所以在波德圖上其一開始相角即為 $-180^\circ$ 。因此要設計使 $\omega_z$ 比 $\omega_p$ 小很多，使得相角在單位增益頻寬前先上升到可以保證穩定的相角邊限，通過單位增益頻寬後，才被在 $\omega_p$ 的極點所影響，將整個增益降的更低，衰減穿透的參考訊號。

圖 2.4 三階頻率合成器的濾波器

將濾波器的轉換函數 (2.12) 代入 (2.2) 可得三階頻率合成器的閉迴路轉換函數

$$\frac{\theta_o(s)}{\theta_i(s)} = \frac{\frac{K_p K_o}{C_1} (s + \omega_z)}{s^3 + \omega_p s^2 + \frac{K_p K_o}{C_1 N} s + \frac{K_p K_o}{C_1 N} \omega_z} \quad (2.14)$$

把上式分母的三次項和二次項提出 $s^2$ ，

$$\begin{aligned}

\frac{\theta_o(s)}{\theta_i(s)} &= \frac{\frac{K_p K_o}{C_1} (s + \omega_z)}{(s + \omega_p)^2 + \frac{K_p K_o}{C_1 N} s + \frac{K_p K_o}{C_1 N} \omega_z} \\

&= \frac{\frac{K_p K_o}{C_1 \omega_p} \left( \frac{s}{\omega_p} + 1 \right)}{s^2 + \frac{K_p K_o}{C_1 N \omega_p} s + \frac{K_p K_o}{C_1 N \omega_p} \omega_z} \quad (2.15)

\end{aligned}$$

。在前面有提到，我們會將  $\omega_p$  設計在單位增益頻寬之後以換取對參考訊號更多的衰減，所以可以合理的假設  $C_1 \ll C_2$ ，則  $\omega_p \approx \frac{1}{RC_1}$ 。並且若所關心的頻率遠小於  $\omega_p$ ，可以將 (2.15) 寫成

$$\begin{aligned}

\frac{\theta_o(s)}{\theta_i(s)} &= \frac{\frac{K_p K_o}{C_1 \omega_p} (s + \omega_z)}{s^2 + \frac{K_p K_o}{C_1 N \omega_p} s + \frac{K_p K_o}{C_1 N \omega_p} \omega_z} \\

&= \frac{\frac{K_p K_o R}{N} (s + \omega_z)}{s^2 + \frac{K_p K_o R}{N} s + \frac{K_p K_o R}{N} \omega_z} \quad (2.16)

\end{aligned}$$

可以觀察到 (2.16) 與二階頻率合成器的轉換函數 (2.8) 是相同的，所以我們可以套用二階頻率合成器的結論，其單位增益頻寬為  $K = \frac{K_p K_o R}{N}$ ，穩定時間也和  $K$  成比例。

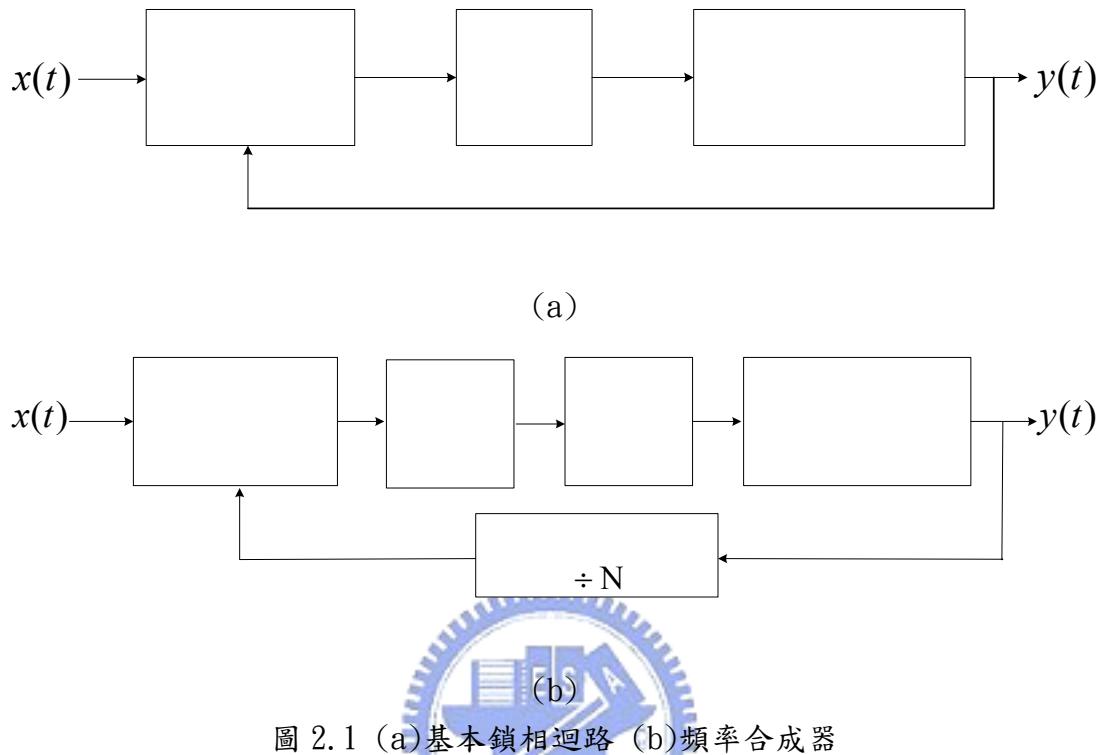

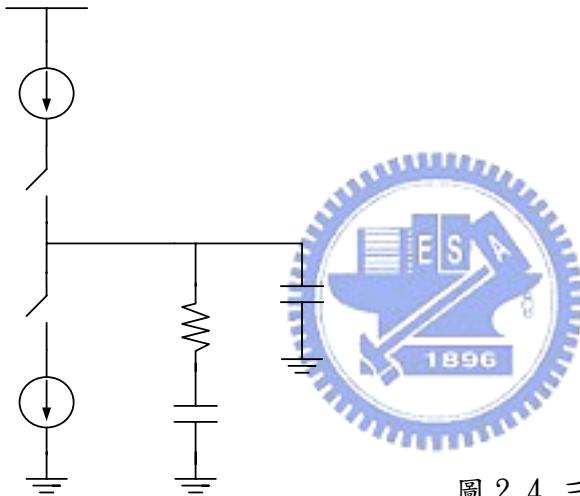

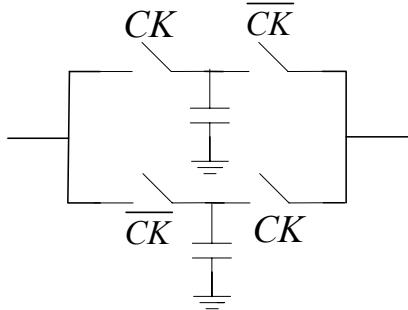

#### 2.1.4 雙電荷容浦三階頻率合成器

本論文頻率合成器所採用的架構是雙電荷容浦的頻率合成器[6]，其電路架構如圖 2.5 所示。這個架構一個電荷容浦接在  $C_1$  上，另一個接在  $C_2$ ，並且使用切換電容來實現濾波器中的電阻，如圖 2.6 所示，其中 CK 的頻率為參考訊號頻率的一半，所以  $R = (f_{\text{REF}} C_s)^{-1}$ 。令由電荷容浦 CP1 所流出來的電流為  $I_{p1}$ ，由 CP2

所流出的電流為  $I_{p2}$ ，且  $I_{p2} = -\alpha I_{p1}$ 。同前面幾節，我們可以導出這個架構的開迴路轉換函數

$$\begin{aligned}\frac{\theta_o(s)}{\theta_e(s)} &= \frac{I_{p1}K_o}{2\pi C_1} \frac{s + \frac{1-\alpha}{RC_2}}{s^2(s + \frac{C_1+C_2}{RC_1C_2})} \\ &= \frac{K_p K_o}{C_1} \frac{s + (1-\alpha)\omega_z}{s^2(s + \omega_p)}\end{aligned}\quad (2.17)$$

其中  $K_p = \frac{I_{p1}}{2\pi}$ 、 $\omega_z = \frac{1}{RC_2}$ 、 $\omega_p = \frac{C_1+C_2}{RC_1C_2}$ 。與 (2.13) 比較，可以發現除了零點

被放大了  $(1-\alpha)$  倍，極點的位置和增益都相同。假設  $\alpha < 1$ ，則零點會移至較低的頻率，如此便可以提高相角邊限。如果使零點不變動的話，則  $C_2$  可以被縮小。

由於在一般的頻率合成器或鎖像迴路中， $C_2$  常常佔很大的面積，故若可以把  $C_2$  縮

小，便可以節省晶片的面積。在此，重寫被縮放後零點的表示式為

$$\omega'_z = \left(1 + \frac{I_{p2}}{I_{p1}}\right) \frac{C_s}{C_2} f_{\text{REF}} \quad (2.18)$$

可以看到零點被  $I_{p1}$  和  $I_{p2}$  及  $C_s$  和  $C_2$  的比例所決定，所以此架構即使受到製程偏移和溫度改變，其轉換函數也不太變動。

圖 2.5 雙電荷容浦三階頻率合成器

圖 2.6 切換電容等效電阻

我們也可以導出閉迴路轉換函數

$$\frac{\theta_o(s)}{\theta_i(s)} = \frac{\frac{K_p K_o}{C_1} (s + \omega'_z)}{s^3 + \omega_p s^2 + \frac{K_p K_o}{C_1 N} s + \frac{K_p K_o}{C_1 N} \omega'_z} \quad (2.19)$$

，此式也與 (2.14) 相同。假如  $C_1 \ll C_2$  且所關心的頻率也遠小於  $\omega_p$ ，則我們也

可以如二階頻率合成器般的，較直觀的來設計此電路。以下列出阻尼常數  $\zeta$ 、非

阻尼振盪頻率  $\omega_n$  和其約略的頻寬倒數或著穩定時間

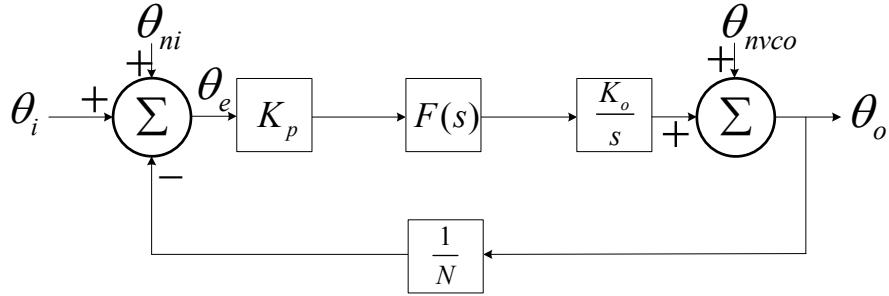

$$\zeta = \frac{1}{2f_{\text{REF}} C_s} \sqrt{\frac{I_{p1} C_2 K_o}{2\pi(1-\alpha)N}} \quad (2.20)$$

$$\omega_n = \sqrt{\frac{2\pi(1-\alpha)I_p K_o}{N C_2}} \quad (2.21)$$

$$\frac{1}{\zeta \omega_n} = \frac{4\pi N f_{\text{REF}} C_s}{I_{p1} K_o} \quad (2.22)$$

### 2.1.5 系統雜訊考量

在頻率合成器內，有很多的雜訊來源，來自如壓控振盪器、除頻器、相位頻率偵測器等。但主要貢獻到輸出相位雜訊，就是壓控震盪器和參考訊號源的相位雜訊。我們可以把雜訊源加入頻率合成器的模型裡來分析，如圖 2.7 所示，其中

$\theta_{ni}$  為參考訊號源的相位雜訊、 $\theta_{nvco}$  為壓控振盪器的相位雜訊。

圖 2.7 含雜訊源的頻率合成器模型

由圖 2.7 可以寫出輸出相位雜訊  $\theta_{no}$  的表示式：

$$\theta_{no}(f) = \frac{NK_p K_o F(s)}{Ns + K_p K_o F(s)} \theta_{ni}(f) + \frac{j2\pi f N}{Ns + K_p K_o F(s)} \theta_{nvco}(f) \quad (2.23)$$

其中  $f$  為頻率， $s = j2\pi f$ 。假如  $K_p K_o F(s)$  很大且在頻率不高的情況下， $\theta_{ni}(f)$  和  $\theta_{nvco}(f)$  對  $\theta_{no}(f)$  的貢獻都是與  $N$  成正比關係。注意，在此的相位雜訊都是方均根值，若以功率來計算的話，將會是與  $N^2$  成正比。所以在頻率合成器中，若除頻器除的倍數越高，輸出相位雜訊便會越大。如果可以的話，盡量將除頻器的倍數作小，使輸出相位雜訊降低。

因為在前面幾節的架構中，都可以簡化成二階頻率合成器來看，所以我們把其濾波器的轉換函數代入 (2.23) 可得

$$\theta_{no}(f) = \frac{NK(s + \omega_z)}{s^2 + Ks + K\omega_z} \theta_{ni}(f) + \frac{s^2}{s^2 + Ks + K\omega_z} \theta_{nvco}(f) \quad (2.24)$$

，其中  $s = j2\pi f$ 。由上式，整個迴路對參考訊號的相位雜訊是低頻通過，而對壓控振盪器的相位雜訊則是高頻通過。上一段有提到，在低頻的時候， $\theta_{ni}(f)$  和  $\theta_{nvco}(f)$  都會被放大  $N$  倍貢獻到輸出，又由 (2.24) 知低頻時的輸出相位雜訊由  $\theta_{ni}(f)$  所主宰。因此，參考訊號源必須在低頻時有夠低的相位雜訊，一般來說，

我們都會選擇石英振盪器來作輸入訊號，因為其擁有極佳的相位雜訊表現。

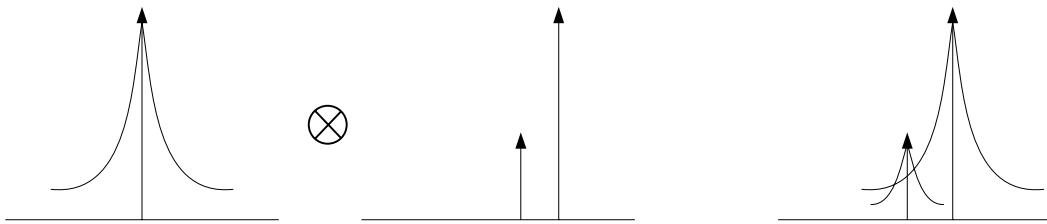

除了以上與迴路轉換函數相關的雜訊之外，從相位頻率偵測器漏出的雜訊也是相當重要，其頻率與參考訊號的頻率相同。此雜訊會由壓控振盪器的電壓控制端，經頻率調變（FM）輸出到合成器的輸出頻譜，會在輸出頻率的兩旁有突波（spur）產生。壓控振盪器輸出角頻率與控制電壓有如此的關係：

$\omega_{out} = \omega_0 + K_o V_{cont}$ ，則輸出訊號可寫成

$$y(t) = A \cos(\omega_0 t + K_o \int_{t_0}^t V_{cont} dt) \quad (2.25)$$

。因為由電壓控制端過來的雜訊其振幅都很小，所以我們可以用窄頻帶頻率調變的近似方法，令  $V_{cont}(t) = V_m \cos \omega_{REF} t$ ， $V_m \ll 1$ ，則 (2.25) 變成

$$y(t) \approx A \cos \omega_0 t + \frac{AV_m K_o}{2\omega_{REF}} [\cos(\omega_0 + \omega_{REF})t - \cos(\omega_0 - \omega_{REF})t] \quad (2.26)$$

。由上式我們可知，突波會產生在  $\omega_0 + \omega_{REF}$  和  $\omega_0 - \omega_{REF}$  兩個頻率上。並且直覺上，似乎降低  $K_o$  和  $V_m$  並升高參考訊號的頻率便可降低此雜訊。事實上， $K_o$  必須與整個迴路的響應一起作考量，為了使整個迴路能快速鎖定，當  $K_o$  小時， $V_m$  常常會變大，我們需要使用濾波器衰減此雜訊。最有效的方法還是提升參考訊號的頻率，突波自然就會在輸出端變小。由於還會有其他雜訊藉由基板耦合到此條控制線，所以在佈局時要十分注意，避免其他訊號線與此控制線距離太近。

在這裡我們可以看到在圖 2.5 所提到的架構中使用切換式電容來替代迴路濾波器裡電阻的另外幾個好處。由於電阻距離基板很近且通常使用在此濾波器的電阻面積很大，所以容易把雜訊耦合上來，直接饋入到控制線上。如果換成切換

式電容就不會有此困擾。此外，當帶著參考訊號頻率的雜訊通過時，原本只有看到  $C_1$ ，現在又加上了  $C_s$ ，便可以再將此雜訊衰減。例如，若  $C_1 = C_s$ ，則除了原本迴路頻寬對雜訊產生的衰減外，又會額外衰減 3dB。所以在輸出雜訊的表現上會比較好。

## 2.2 系統設計考量

### 2.2.1 系統設計規格

在我們的設計中，最重要的考量就是要符合 IEEE802.11b 標準所定的規格。在 IEEE802.11b 標準的說明書上，含有很多的規格，包括基頻、資料傳輸、射頻端等。在射頻方面，直接與頻率合成器相關的規格就是穩定時間、各頻道中心頻率及頻率準確度。穩定時間的規格是在頻道間互相切換之後的  $224\mu s$ ，輸出頻率必須為頻道中心頻率  $\pm 60\text{kHz}$  之內。各頻道的中心頻率從  $2.412\text{GHz}$  到  $2.472\text{GHz}$  每間隔  $10\text{MHz}$  一個頻道。而中心頻率的準確度最大必須在  $\pm 25\text{ppm}$  之內。

在頻率合成器中，另一個重要的規格是輸出的相位雜訊大小。若輸出的相位雜訊不好，則會被鄰近頻道的訊號給蓋掉，無法收到正確的訊息。所以如何讓相位雜訊變低，是在設計頻率合成器的重要議題。所以我們選擇鎖相迴路式的頻率合成器，它擁有較好的相位雜訊表現。

圖 2.8 相位雜訊表示圖

由圖 2.8 我們可以清楚的瞭解到相位雜訊對訊號的影響。由頻率合成器輸出的訊號為本地振盪訊號，可以看到旁邊帶著群擺般的相位雜訊。而由天線接收進來的訊號，除了想要的訊號之外，還有鄰近頻道的訊號。當這些訊號經過混波器混頻之後，相位雜訊變會附在想要的訊號和鄰近的訊號上。由圖中可以看出，若相位雜訊太大，附在鄰近頻道訊號的相位雜訊便會蓋住想要的訊號，所攜帶的訊息便消失了。由 IEEE802.11b 標準可以查出最小的敏感度為  $-76\text{dBm}$ ，而在  $10\text{MHz}$  鄰近頻道訊號大小為  $-41\text{dBm}$ ，則我們可以由下式算出相位雜訊的規格：

$$\begin{aligned} L\{\omega_m\} &= P_{\text{wanted}} - P_{\text{adjacent}} - \text{SNR} - 10 \log(10 \times 10^6) \\ &= -112\text{dBc / Hz} @ 10\text{MHz offset frequency} \end{aligned} \quad (2.28)$$

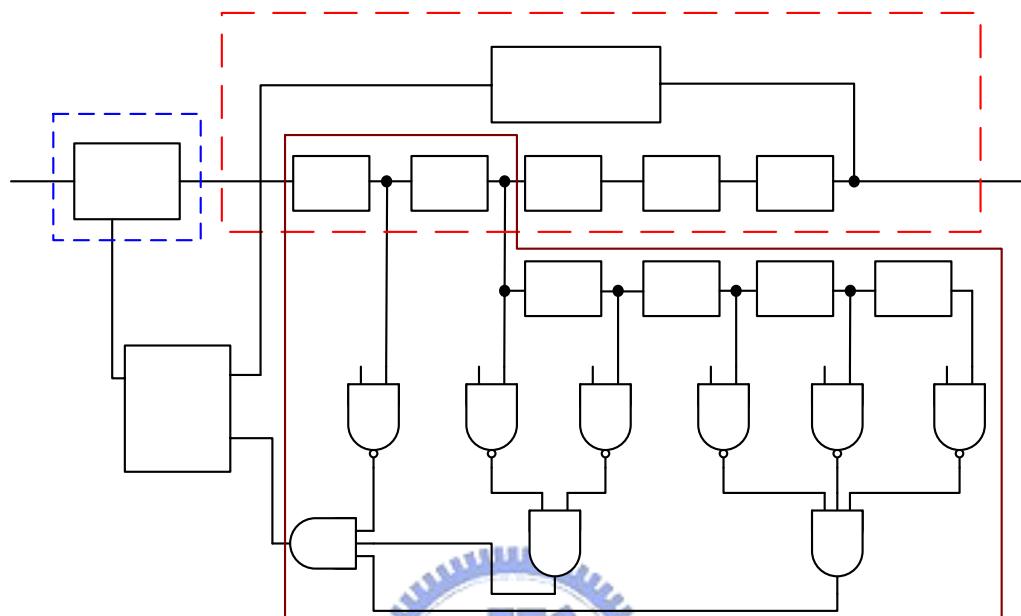

## 2.2.2 系統設計架構

在 §2.1.4 有提到，本論文所採用的架構是雙電荷峩浦式的三階頻率合成器。由於此架構可以把零點往低頻移動，卻不會對在高頻的那一個極點造成很大的影響。在一般的三階頻率合成器，如 (2.12)，我們想要將零點往低頻移動換取更大的相角邊限，有兩個選擇，第一是將  $C_2$  加大但會佔很大的面積，第二是將電阻變大，但是同時若  $C_1$  不改變，在高頻的極點將也會往低頻移動，減少了迴路衰減雜訊的能力。所以，使用雙電荷峩浦可以避免這些缺點，而增加相角邊

限，並且減少  $C_2$  所佔的面積，節省成本。當然，我們得增加一個電荷容浦，增加一點的功率消耗，但是最困難的還是在於兩個電荷容浦之間尺寸要互相匹配。在所有其它的參數都決定了，也根據這些參數將頻率合成器設計出來，假設  $\alpha$  取的接近 1，我們可以以很小的  $C_2$  實現相同的零點，但是由於兩個電荷容浦電流相近，如果有一點的不匹配，將會造成  $\alpha$  的大幅變動，使得迴路的轉換函數變得與當初設計的不相同，影響了實現後的表現。因此  $\alpha$  不宜取得太大。另外，由於使用切換電容來等效電阻，可以實現較大的電阻而不必擔心面積的問題，並且可以有額外衰減雜訊的效果。不過在此要避免控制切換開關的頻率漏到振盪器的控制端，產生額外的雜訊，在設計時要仔細考慮。

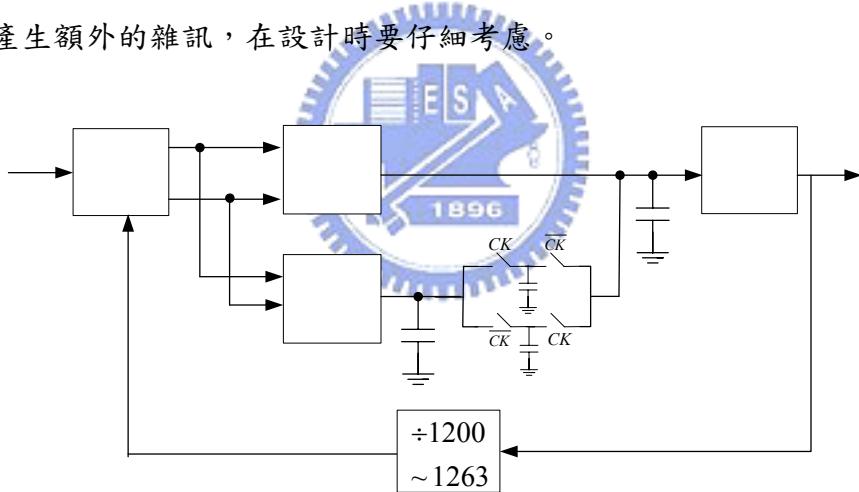

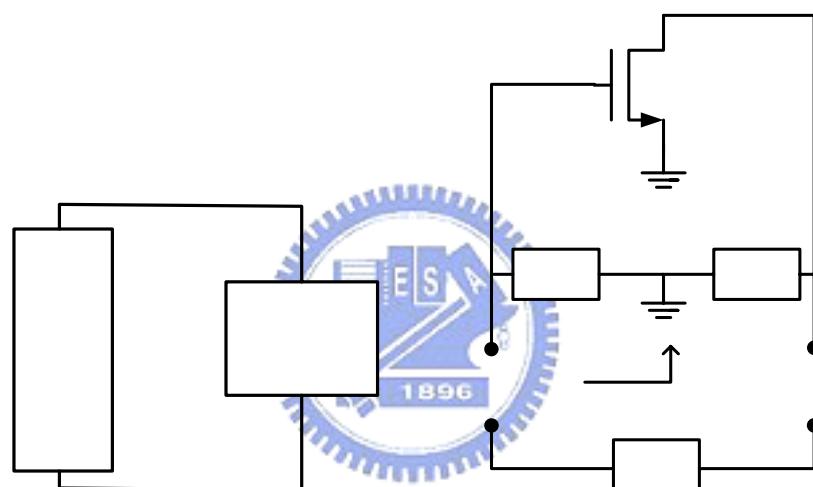

圖 2.9 頻率合成器架構

圖 2.9 為本論文要實現的頻率合成器架構。在除頻器部份，我們選擇整數式除頻器。因為頻道間隔為 10MHz，且第一個頻道中心頻率為 2.412GHz，則最大的參考頻率只能選擇 2MHz，對應的除頻倍數便選為 1200 到 1263，則輸出的頻率範圍為 2.4GHz 到 2.526GHz。我們可以控制除頻器的倍數為 1206、1211、1216、1221、1226、1231 和 1236 來切換七個頻道。在切換電容的切換訊號 CK，使用一個倍數

為 2 的除頻器將參考頻率除 2 提供給切換電容使用。

### 2.3 行為模型和模擬

由於頻率合成器是一個不算小的系統，若草草決定參數，花了很多時間來設計完成後，發現與原來預估的相差很多，到時候要回來更改定是曠日廢時。所以在實際進行電路實現之前，先要建立行為模型，並把想要的參數代入，看看是否出來的結果符合我們的期望。所謂行為模型，便是以程式語言和數學式子來描述模擬一個電路。由於進行模擬時，電腦不需要去計算電晶體的參數，因此我們很快就可以看到結果，而且結果與實際實現出來的電路不會相差很多。

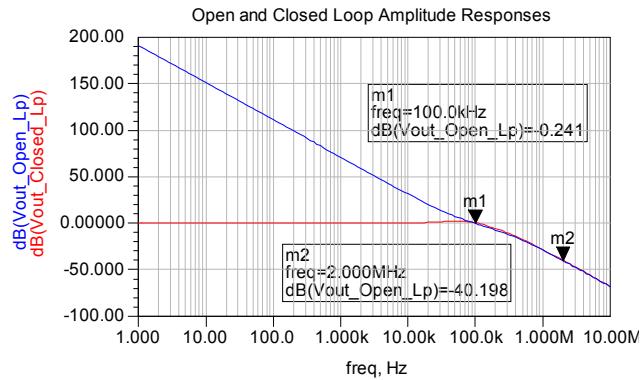

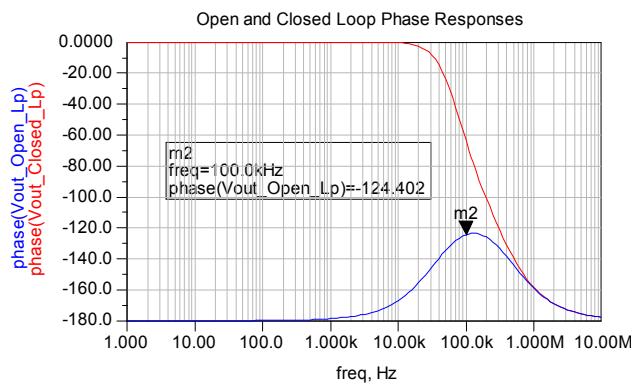

安捷倫公司所發行的 ADS (Advance Design System) 電路模擬軟體提供了一些以建立好的個別元件的行為模型，如相位頻率偵測器、電荷峯浦、壓控振盪器、除頻器等，我們可以輕易的更改參數、或加入所要的濾波器來作行為模型的模擬。注意，在我們的行為模型模擬裡，濾波器內的電阻是以實際的電阻特性來模擬，而非以切換電容的形式。表 2.1 為最後欲設計的參數結果，其中含有由理論數學式子所計算的結果和行為分析的模擬結果。表中， $I_p$  是第一個電荷峯浦的電流、 $\alpha$  為第二個電荷峯浦的電流與第一個的比值、 $f_z$  為零點所在的頻率、 $f_p$  為由濾波器所貢獻的極點所在頻率。在圖 2.10 中，可以看出單位增益頻寬為 100KHz，而在 2MHz 的訊號將會被衰減 40.2dB，但由於在作行為模擬時事直接放電阻，實際上應是等效切換電容  $C_s$ ，則因為在此剛好  $C_1 = C_s$  所以  $C_s$  將會再貢獻 3dB 的衰減。也就是說，在參考頻率的雜訊總共會被衰減 43.2dB。在圖 2.11 中，

單位增益頻寬的相角為  $-124.4^\circ$ ，所以相角邊限為  $180^\circ - 124.4^\circ = 55.6^\circ$ 。會設計這麼大的相角邊限是防止因實際以電路模擬或晶片實際實現後，一些不匹配或製程飄移的結果，而使此電路不穩定。圖 2.12 是頻率合成器的暫態響應，一開始設定除頻器的倍率是 1206 所以輸出頻率是 2.412GHz，在 700ns 之後倍率改到 1236，所以是從頻率最小的頻道切換到頻率最大的頻道，為開機後最差的情況。可以看到在  $20.7\mu\text{s}$  之後，輸出頻率穩定到 2.472GHz。

表 2.2 所列出的為行為模型的模擬結果，其中我們可以注意到在表 2.1 中的  $\zeta\omega_n$  所算出的值與表 2.2 中的單位增益頻寬  $ft$  非常相近，並且和行為模型模擬的穩定時間結果是同一個數量級。所以在前面幾節的討論中，使用的近似是合理而且安全的。

| Ip(uA) | $\alpha$ | Ko(MHz) | C1(pF) | C2(pF) | Cs(pF) | fz(Hz) | fp(Hz)   | $\zeta$ | $1/(\zeta^* \omega_n)$ |

|--------|----------|---------|--------|--------|--------|--------|----------|---------|------------------------|

| 29.65  | 0.65     | 227.5   | 3.5    | 10     | 3.5    | 38993  | 318310.2 | 0.358   | 1.14E-05               |

表 2.1 頻率合成器參數與計算及模擬結果

圖 2.10 行為模型的開/閉迴路大小響應

圖 2.11 行為模型的開/閉迴路相角響應

圖 2.12 行為模型的暫態響應

| ft(KHz) | Att.(dB) | PM(degree) | settling time(us) |

|---------|----------|------------|-------------------|

| 100     | 40.2     | 55.6       | 20.7              |

表 2.2 行為模型模擬結果

# 第三章 電路設計實現與模擬

在第二章我們已經有了頻率合成器的規格，並且根據計算和行為模型的結果，決定了各個組合電路的規格。在這章，我們將要使用台積電  $0.25\text{ }\mu\text{m}$ CMOS 製程參數來實現電路。接下來的幾節分別會介紹各組成電路的原理、實際的電路所面臨的問題，並且該如何來解決。

## 3.1 壓控振盪器

在第二章提過，壓控振盪器是使用電壓來控制輸出的頻率。因為壓控振盪器為頻率合成器的輸出端，所以振盪器設計的好壞直接的影響到頻率合成器輸出的表現。因此接下來我們將討論壓控振盪器的各項議題。

### 3.1.1 壓控振盪器的基本理論

雖然有很多種類的振盪器可以提供設計者選擇，但是由於頻率合成器必須要提供盡量接近單一頻率的正弦波給混波器，以避免其他次諧波干擾混波的結果。所以使用有共振腔的振盪器，較能提供需要的訊號。雖然石英振盪器的輸出相位雜訊非常好，但是到達  $100\text{MHz}$  的振盪頻率已經是很昂貴的花費。還有其它有大體積共振腔的振盪器，也非我們追求 SOC 的目標。所以簡單由電感和電容形成的共振腔，便是很好的選擇。

不論是哪一種的振盪器設計，都是一個「正迴授」的迴路。根據巴克豪森準

則 (Barkhausen criterion)，在欲振盪的頻率下，迴路增益的相角必須是零，且迴路增益的大小必須大於等於 1。關於這一類的電路分析，一般電子學的教科書[7]都可以找到說明。在此我們採用另一種分析方法-負電阻分析法。如圖 3.1 我們可以把振盪器分成兩部分，一部份是會提供能量的負電阻產生器，另一部份是選擇振盪頻率的共振腔。由於一個不完美的共振腔會有能量的損耗，所以使用負電阻產生器補償共振腔的損耗，於是振盪持續產生。

圖 3.1 負電阻振盪器概念圖

圖 3.2 單一電晶體振盪器

圖 3.3 計算輸入阻抗的小訊號模型

下面將使用負電阻分析法分析單一電晶體振盪器。如圖 3.2 所示，圖上並

沒有畫出偏壓電路。其中  $Z1$ 、 $Z2$ 、 $Z3$  的阻抗分別以  $jX_1$ 、 $jX_2$ 、 $jX_3$  表示，若  $X_i$

大於零則為電感性阻抗，小於零則為電容性阻抗。為了計算輸入阻抗  $Z_{in}$ ，我們

將使用圖 3.2 的小訊號模型，如圖 3.3 所示。由圖中，可推出

$$Z_{in} = \frac{v_{in}}{i_{in}} = -g_m \frac{X_1 X_2}{1 - \omega C_{gs} X_1} + j \frac{X_1 + X_2 - \omega C_{gs} X_1 X_2}{1 - \omega C_{gs} X_1} \quad (3.1)$$

。式中，等號右手邊的第一項，若在  $\omega C_{gs} X_1 < 1$  下，則輸入阻抗便有負電阻。如

我們所熟知的，若  $Z1$ 、 $Z2$  為電感， $Z3$  為電容，則此形式的振盪器為哈特萊

(Hartley) 振盪器；若  $Z1$ 、 $Z2$  為電容， $Z3$  為電感，則此形式的振盪器為柯比

茲 (Colpitts) 振盪器。在哈特萊振盪器中，(3.1) 會變成

$$Z_{in} = -g_m \frac{\omega^2 L_1 L_2}{1 - \omega^2 C_{gs} L_1} + j \frac{\omega L_1 + \omega L_2 - \omega^3 C_{gs} L_1 L_2}{1 - \omega^2 C_{gs} L_1} \quad (3.2)$$

。在柯比茲振盪器中，(3.1) 會變成

$$Z_{in} = \frac{-g_m}{\omega^2 C_2 (C_1 + C_{gs})} - j \frac{C_1 + C_2 + C_{gs}}{\omega C_2 (C_1 + C_2)} \quad (3.3)$$

。比較兩種振盪器可以發現，柯比茲振盪器的電阻可以永遠保證是負的。而哈特

萊振盪器的電阻在  $L_1$  和  $C_{gs}$  的共振頻率之前，為負電阻，在之後則為正電阻，所

以在設計時要小心確保振盪頻率要小於  $L_1$  和  $C_{gs}$  的共振頻率。

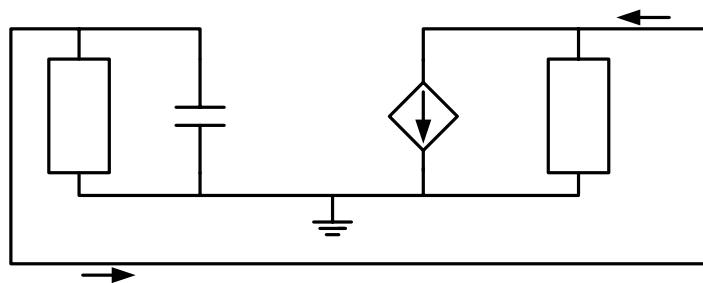

圖 3.4 並聯電阻電感轉串聯電阻電感

再看柯比茲振盪器， $Z3$  為電感，且我們將其它的寄生電阻與此電感並聯。

由於  $Z_m$  為串聯表示式，所以須把並聯的電阻電感改為串聯的電阻電感，如圖 3.4 所示。其中  $R_s = \frac{\omega^2 R_p L_p^2}{R_p^2 + \omega^2 L_p^2}$  、  $L_s = \frac{L_p R_p^2}{R_p^2 + \omega^2 L_p^2}$ 。一般來說， $R_p$  很大，且在所關心的頻率下， $R_s \approx \frac{\omega^2 L_p^2}{R_p}$  、  $L_s = L_p$ 。為了分析方便，令  $C'_1 = C_1 + C_{gs}$ ，則重寫 (3.3)

$$Z_{in} = \frac{-g_m}{\omega^2 C'_1 C_2} - j \frac{C'_1 + C_2}{\omega C'_1 C_2} \quad (3.4)$$

。所以柯比茲振盪器的振盪頻率為

$$\omega_0 = \sqrt{\frac{C'_1 + C_2}{L_p C'_1 C_2}} \quad (3.5)$$

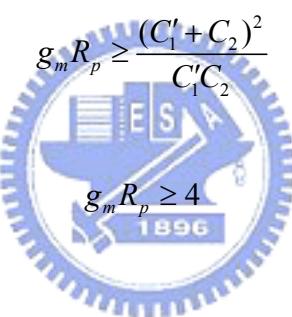

且在負電阻要大於等於  $R_s$  下才會產生振盪，則

$$g_m R_p \geq \frac{(C'_1 + C_2)^2}{C'_1 C_2} \quad (3.6)$$

。在  $C'_1 = C_2$  的條件下，

$$g_m R_p \geq 4 \quad (3.7)$$

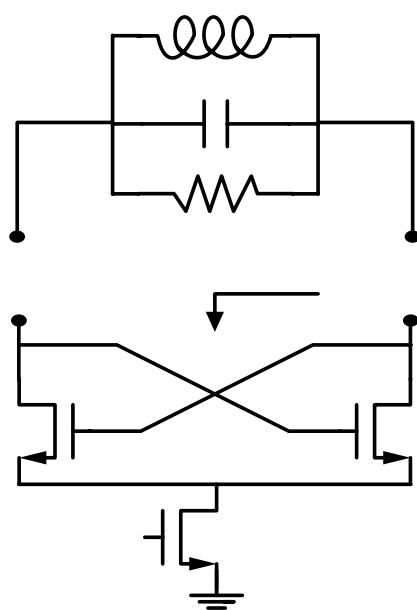

圖 3.5 交錯耦合電容電感振盪器

另一種電容電感振盪器為交錯耦合 (cross-coupled) 電容電感振盪器，如圖 3.5 所示。由小訊號分析 (只考慮  $C_{gs}$ )，可知

$$Z_{in} = \frac{-2g_m}{g_m^2 + \omega^2 C_{gs}^2} - j \frac{2\omega C_{gs}}{g_m^2 + \omega^2 C_{gs}^2} \quad (3.8)$$

。可以發現這種架構也會產生負電阻，且隨著頻率升高，負電阻會漸漸的變小。

忽略  $C_{gs}$ ，則振盪頻率主要由共振腔來決定

$$\omega_0 = \sqrt{\frac{1}{LC}} \quad (3.9)$$

。因為共振腔內是並聯電路，改成導納後即可相加，所以由負電導須大於等於共振腔內的損耗電可以導出

$$g_m R_p \geq 2 \quad (3.10)$$

。與 (3.7) 比較，可知交錯耦合的電容電感振盪器條件較寬鬆，而且在以積體電路實現時，通常電感的 Q 值都不高，所以多以交錯耦合方式實現振盪器。

在圖 3.5 中，我們可以經由  $V_b$  控制最下方的尾電晶體所流出的電流，也就是振盪器核心所通過的偏壓電流  $I_{bias}$ 。振盪器的輸出振幅即是由此偏壓電流和共振腔內的寄生電導所決定。在圖中，共振腔內的電導  $g_{tank} = 1/R_p$ ，我們可以寫出振幅  $V_{amplitude} = I_{bias} / g_{tank}$ 。 $V_b$  逐漸上升，則  $I_{bias}$  變大，使得輸出振幅也變大。當輸出振幅到達一定的大小，會壓迫到尾電晶體的  $V_{DS}$ ，使其操作區域從飽和區進入線性區，則輸出振幅也會到達一個限制。所以稱此為電壓限制區，而前一個狀況則為電流限制區，如圖 3.6 所示。我們將輸出振幅整理如下：

$$V_{amplitude} = \begin{cases} I_{bias} / g_{tank} & (\text{電流限制}) \\ A_{limit} & (\text{電壓限制}) \end{cases} \quad (3.11)$$

圖 3.6 輸出振幅與偏壓電流關係圖

### 3.1.2 相位雜訊

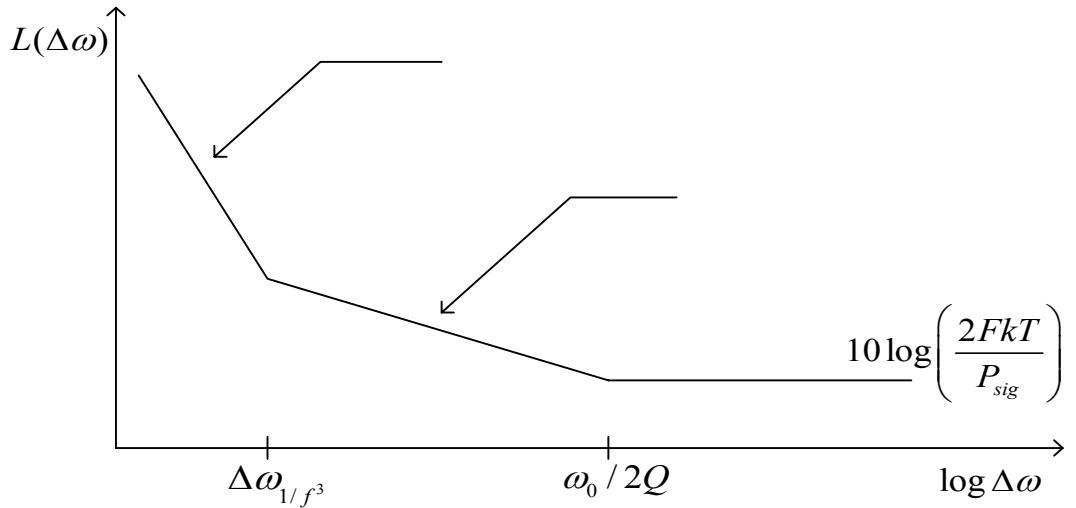

在第二章中，我們提到相位雜訊是頻率合成器重要的表現之一，由於參考訊號源是使用石英振盪器，其相位雜訊很低，所以頻率合成器相位雜訊表現好壞，有大部分責任就落在壓控振盪器身上了。早在 1966 年，Leeson 便由共振腔內的寄生電導所產生的熱雜訊 (thermal noise) 的功率與振盪訊號功率的比值，加上一些推導與量測所發表的相位雜訊表示式 [8]：

$$L(\Delta\omega) = 10 \cdot \log\left(\frac{v_n^2 / \Delta f}{v_{sig}^2}\right) = 10 \cdot \log\left\{\frac{2FkT}{P_{sig}} \cdot \left[1 + \left(\frac{\omega_0}{2Q\Delta\omega}\right)^2\right] \cdot \left(1 + \frac{\Delta\omega_{1/f^3}}{|\Delta\omega|}\right)\right\} \quad (3.12)$$

其中  $k = 1.380 \times 10^{-23} \text{ J/}^\circ\text{K}$ ，為波茲曼常數。 $\omega_0$  是振盪頻率。F 為用來調整雜訊基準 (noise floor) 的因子。Q 是共振腔的品質因子。(3.12) 若由圖 3.7 來看，便可以清楚的瞭解式子所代表的意義。相位雜訊在角頻率  $\Delta\omega_{1/f^3}$  以前與  $\Delta\omega$  的三次方成比例關係，經過此頻率之後便呈現與  $\Delta\omega$  的平方成比例，最後在經過  $\omega_0 / 2Q$  到達雜訊基準。這便是一般振盪器相位雜訊的頻譜變化趨勢。

圖 3.7 Leeson 模型的相位雜訊頻譜

若要瞭解相位雜訊頻譜各個轉折點的來源，可參考 1998 年 Ali Hajimiri 所發表的時變相位雜訊理論 (Time Invariant Phase Noise Theory) [9]。Hajimiri 認為時變本來就是振盪器的性質之一，若要較準確預測相位雜訊，必定要引入時變的概念。他是藉由脈衝敏感函數 (ISF, Impulse Sensitivity Function)  $\Gamma(x)$  來引入時變。 $\Gamma(x)$  是波形或著可說是物理上所說的相圖 (Phase diagram) 的函數，被振盪器的非線性或結構所主宰，可由振盪器的輸出波形得到。因為其亦為週期函數，所以可以將脈衝敏感函數作傅立葉係數展開得

$$\Gamma(\omega_0\tau) = \frac{c_0}{2} + \sum_{n=1}^{\infty} c_n \cos(n\omega_0\tau + \theta_n) \quad (3.13)$$

另外由於電路中各個節點的脈衝敏感函數會不同，所以在不同節點的雜訊所產生的相位雜訊程度也不一樣。假設在某一節點有雜訊電流源  $i(t)$ ，經由迴旋積分後，可推得輸出額外相位

$$\phi(t) = \frac{1}{q_{\max}} \left[ \frac{c_0}{2} \int_{-\infty}^t i(\tau) d\tau + \sum_{n=1}^{\infty} c_n \int_{-\infty}^t i(\tau) \cos(n\omega_0\tau) d\tau \right] \quad (3.14)$$

，其中  $q_{\max}$  為共振腔內的電容與振盪訊號電壓振幅的乘積，即為最大可儲存電

荷。而輸出額外相位可以經相位調變的方式，得到相位雜訊的頻譜。經由一些特殊的  $i(t)$  代入後，這理論可以預測相位雜訊頻譜將有  $1/f^3$ 、 $1/f^2$  和平坦區的存在。一些低頻的雜訊，如閃爍雜訊 (flicker noise)，會被  $c_0$  加權且與  $\Delta\omega$  有三次方關係；白雜訊 (white noise) 的部分會被其他的  $c_n$  項加權而貢獻到  $1/f^2$  的區域。顯然地，假如原來的雜訊電流源有  $1/f^n$  的低頻雜訊項，如爆米花雜訊 (popcorn noise)，它們將會顯現到相位雜訊頻譜的  $1/f^{n+2}$  區域。所以我們可以得知，越是低頻的雜訊，所貢獻的相位雜訊越嚴重。

由 Hajimiri 的理論，我們可以歸納出一些降低相位雜訊的方法：

1. 增加電容值或加大振幅，可使  $q_{\max}$  減小，進而降低相位雜訊。

2. 降低在振盪頻率整數倍附近的偽頻干擾訊號。

3. 設計電路使輸出波形更加對稱。

4. 注意每各半電路對於主要的雜訊源來說要對稱。

這裡，我們來考慮由共振腔所產生的雜訊 [10]。依據熱力學的等分定理 (Equipartition Theorem of Thermodynamics)，在絕對溫度  $T$ ，每一個系統的獨立自由度在平衡時有平均能量  $\frac{kT}{2}$ 。在並聯電容電感共振腔內，這唯一的獨立初始條件可以由電容來決定，則  $\frac{Cv_n^2}{2} = \frac{kT}{2}$ ，可以推導出大家所熟知的  $kT/C$  雜訊，即：

$$\overline{v_n^2} = \frac{kT}{C} \quad (3.15)$$

又由  $\omega_0 = \sqrt{\frac{1}{LC}}$ ，(3.15) 變成

$$\overline{v_n^2} = kT\omega_0^2 L \quad (3.16)$$

我們將 (3.16) 除以 (3.11) 可得雜訊載波比 (noise to carrier ratio) ,

$$\frac{\overline{v_n^2}}{V_{\text{amplitude}}^2} = \begin{cases} kT\omega_0^2 L g_{\text{tank}}^2 / I_{\text{bias}}^2 & (\text{電流限制}) \\ kT\omega_0^2 L / A_{\text{limit}}^2 & (\text{電壓限制}) \end{cases} \quad (3.17)$$

所以在電流限制區工作時，可以把偏壓電流增大，共振腔內寄生電導變小，選擇大電感來降低雜訊載波比，而在電壓限制區時，只能增大電感來降低雜訊載波比。但前面又有提到增加共振腔電容值可以有效的直接降低貢獻在共振腔兩端的雜訊，所以唯有使  $Q$  值上升，即  $g_{\text{tank}}$  減少，才能真正有效地降低相位雜訊。

### 3.1.3 電路實現與設計考量

在第二章有提到，我們的頻率合成器需要提供四個相位的本地振盪訊號給接收端和傳送端的 I、Q 路徑。理想上，這四個相位的訊號彼此之間的相差為  $90^\circ$  。

產生四相位輸出的方法之一是使用由 RC 網路所組成的四相位產生器，如圖 3.8 所示 [11]。但缺點是會使輸出電壓振幅變小、由電阻產生的雜訊較高，並且電容會影響振盪頻率。另外一個目前大家所常用的方法是將兩個交錯耦合電容電感振盪器的四個輸出以四個電晶體互相連接使四個輸出產生彼此相差  $90^\circ$  的訊號 [16]。

圖 3.8 RC 網路四相位產生器

圖 3.9 (a) 振盪器與耦合差動對，(b) 簡單小訊號模型

圖 3.10 兩個振盪器與耦合差動對串接的小訊號模型

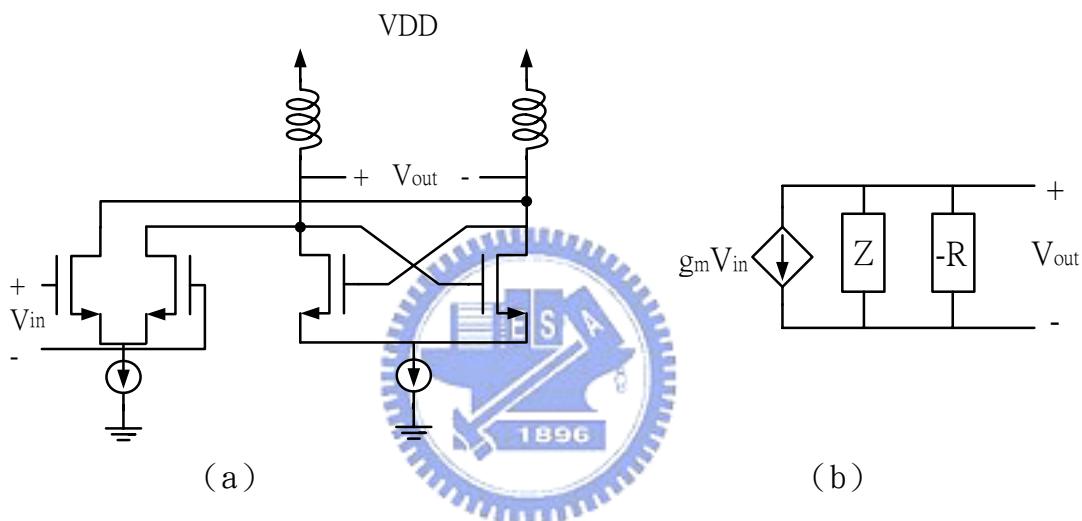

為了探討為何此架構能夠產生四相位的輸出，我們先看圖 3.9 的架構[12]。

在圖 3.9(a)中為一個差動對與一個振盪器串接，為了方便起見，我們省略掉其中的電容。 $Z$  表示除了負電阻 $-R$  以外其它的阻抗。如果  $V_{in}$  的頻率與振盪器的振

盪頻率相同，則  $V_{out}$  會與  $V_{in}$  同相位。假使我們將兩個同樣的此電路串接後，小訊

號模型如圖 3.10 所示。根據電路分析可以得到

$$g_{m1}V_1 \frac{-RZ}{Z-R} = -V_2 \quad (3.18)$$

$$g_{m2}V_2 \frac{-RZ}{Z-R} = -V_1 \quad (3.19)$$

。若將上兩式相除可得

$$g_{m1}V_1^2 - g_{m2}V_2^2 = 0 \quad (3.20)$$

如果 (3.20) 在  $g_{m1} = -g_{m2}$  的情況下，我們將可以得到  $V_1 = \pm jV_2$ ，這表示  $V_1$  與  $V_2$

相位上相差  $90^\circ$ 。這樣的電路，將如圖 3.11 所呈現。

圖 3.11 四相位輸出的交錯耦合振盪器

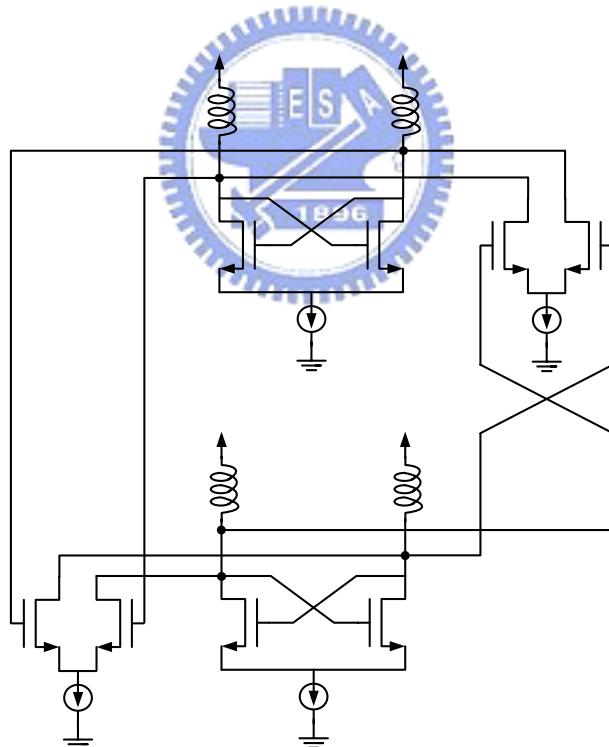

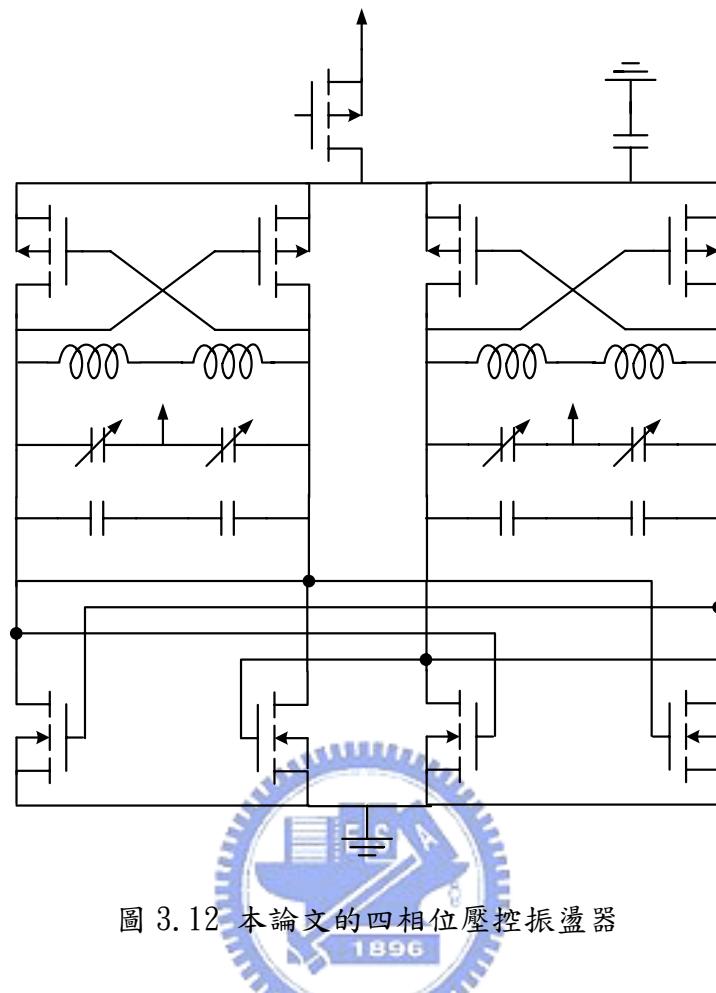

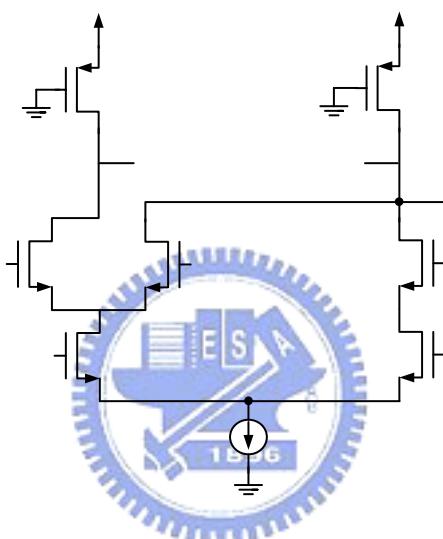

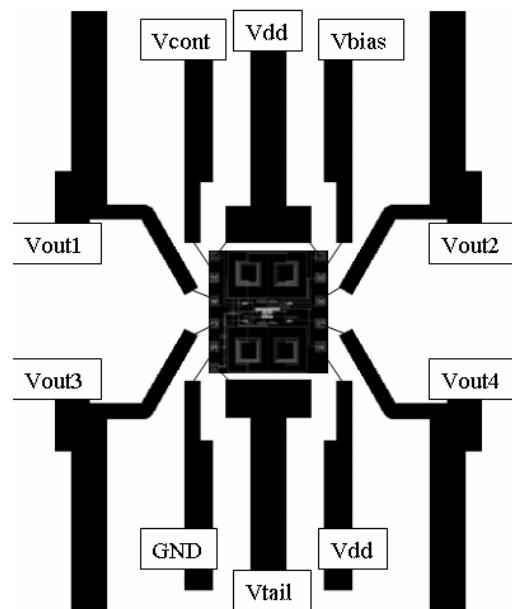

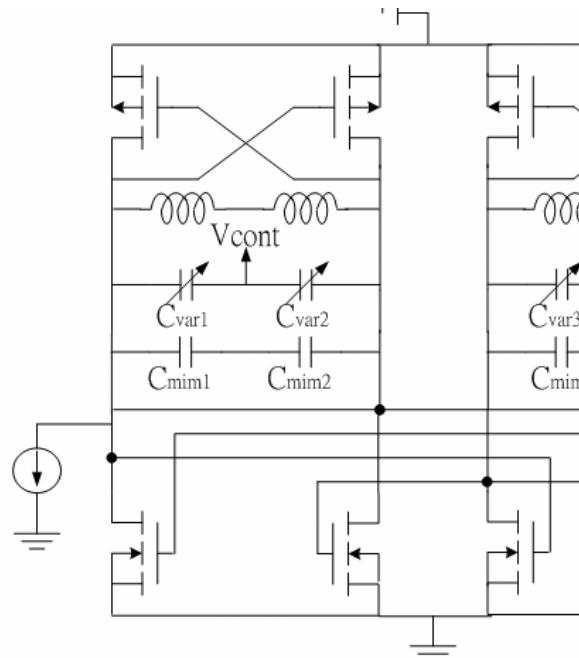

圖 3.12 本論文的四相位壓控振盪器

本論文所設計的四相位壓控振盪器如圖 3.12 所示。如上一小節所說，一般為了降低相位雜訊須使振盪器的輸出波形很對稱，振盪器會設計成完整交錯耦合振盪器，也就是在共振腔的上下方各為由 PMOS 和 NMOS 所組成的負電阻產生器，波形的上推下拉均是由電晶體所推動。如果要產生四相位輸出，就必須要另外加四顆電晶體來交錯相接，此時線路會很複雜。所以我們設計的電路便將原本用來產生負電阻的 NMOS，交錯互接之後，用來產生四相位輸出，並且可以與振盪器共用偏壓電流，降低功率損耗。為什麼不使用 PMOS 的部份而使用 NMOS 的呢？因為 PMOS 的載子電洞會經由埋藏層（buried layer）通過，而不會直接經過氧化層和矽基板之間有不少缺陷的介面，因此 PMOS 的閃爍雜訊會比 NMOS 少 [13]。在

前面有討論過，由於閃爍雜訊對相位雜訊有很大的貢獻，因此便選擇 NMOS 的部份來處理。除此之外，我們也使用 PMOS 當作偏壓電流源移到上方，並且使電晶體的尺寸盡量加大。因為由閃爍雜訊的數學模型

$$\overline{V_n^2} = \frac{K}{C_{ox}WL} \cdot \frac{1}{f} \quad (3.21)$$

可知當尺寸越大時，閃爍雜訊將會越低。

負電阻大小的選擇除了關係到會不會起振，也關係到輸出的振幅大小。負電阻太大時，供應的偏壓電流也比較大，起振時，當主頻率的波形成長到一定的大小後，由於電晶體的非線性，會使其他諧波的大小增加。為了避免能量浪費在不想要的諧波上，根據 Gonzalez 的推導[14]，負電阻為被補償電阻的三倍大，可以最大化輸出功率。如此也可以避免因製程飄移而使得電路無法起振。用來產生四相位的 NMOS，必須調整尺寸使其將波形拉下的能力與 PMOS 的推上相等，使相位雜訊最小，而不是盡量加大尺寸使閃爍雜訊變小。

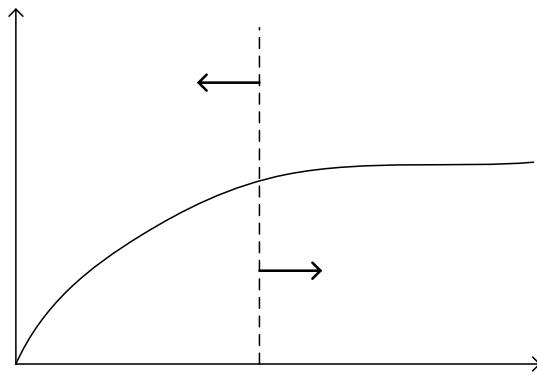

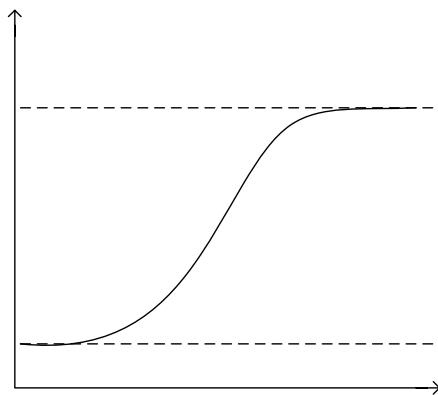

圖 3.13 PMOS 可變電容特性曲線圖

為了可以調整頻率，我們在共振腔內使用可變電容，此電容是以 PMOS 實現的 MOS 電容，其特性曲線如圖 3.13 所示。當電壓增大時，容值會逐漸上升，最

後達到一個最大值。相反的，電壓減少時，容值會逐漸下降，最後到達最小值。

選用 MOS 電容，而沒有選用二極體電容的原因是，對於相同的容值，MOS 電容可以較少的面積達成。另外，以此種電容實現的壓控振盪器，其增益會是負的。因為當電壓增加，電容變大，則振盪頻率變小。在圖 3.12 中，在共振腔內有 MIM (metal-insulator-metal) 電容參與構成共振腔，這是因為 MIM 電容的  $Q$  值較高，如此整個共振腔的  $Q$  值也將會提高。但會有一個缺點，因為加了 MIM 電容後，可變電容的電容變化率在整個電容值所佔的比率便會降低，所以壓控振盪器的頻率可調範圍便會縮小。又容值越大的 MIM 電容，其  $Q$  值越大。所以在相位雜訊與可調頻率範圍之間是需要取捨的。

為了更降低相位雜訊，使偏壓電流的雜訊降低是十分重要的，因為它會貫穿整個振盪路徑。所以我們加了一顆大電容  $C_{bypass}$  在偏壓電流的輸出端，在模擬時，可以明顯地看到在這個節點的漣波變小了。且根據前人的實驗[15]，除了加上  $C_{bypass}$  之外，要接到 VDD 的打線 (bonding wire) 其電感效應也會使相位雜訊降低。

訊號輸出前，必須經過緩衝級後，才能輸出到其它的電路。因為如果不接緩衝級，外界的負載便會影響共振腔，使振盪頻率改變，而且相位雜訊也會大大不同。我們在這裡使用 PMOS 的共源架構當緩衝級，PMOS 的汲極即為輸出。在量測時，需在其後加上匹配網路，否則量測儀器只有  $50\Omega$  的負載會使得輸出功率很小。

### 3.1.4 模擬結果一

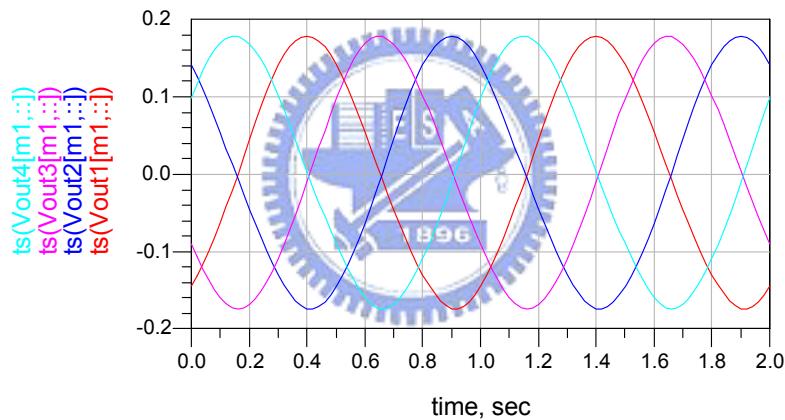

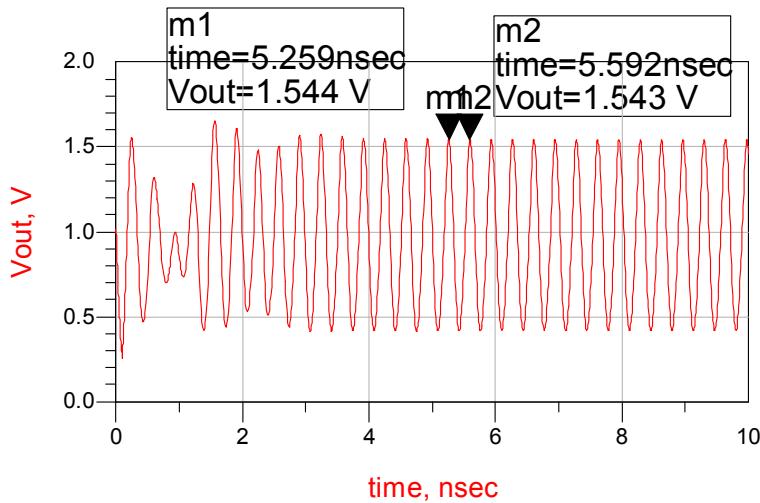

壓控振盪器的模擬結果展現在圖 3.14、圖 3.15、圖 3.16、圖 3.17、圖 3.18，分別是四相位輸出波形、諧波頻譜、相位雜訊、可調頻率範圍及輸出功率與輸出頻率的關係，表 3.1 列出了壓控振盪器的詳細規格。核心偏壓電流為 5.75mA，而整個壓控振盪器（含緩衝級）共消耗 48.41mW。在圖 3.14 中，可以看到四個輸出的波形分別相差  $90^\circ$ ，而且波形相當對稱，振幅約為 190mV，振盪頻率為 2.454GHz。

圖 3.14 四相位輸出波形

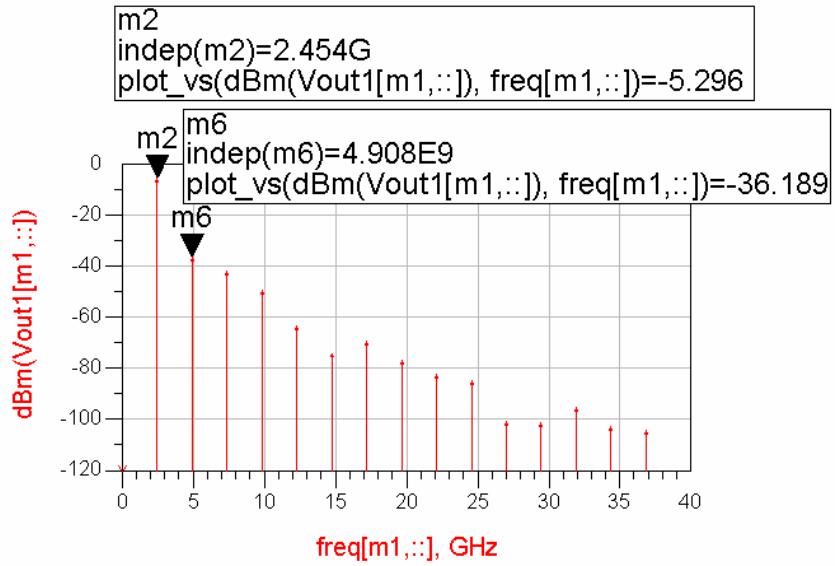

在圖 3.15 中，含有一個主頻率訊號，和其他 14 個諧波。主頻率的輸出功率為  $-5.296\text{dBm}$ ，而第一個諧波比主頻率訊號低了約  $31\text{dBm}$ 。

圖 3.15 輸出訊號各諧波頻譜

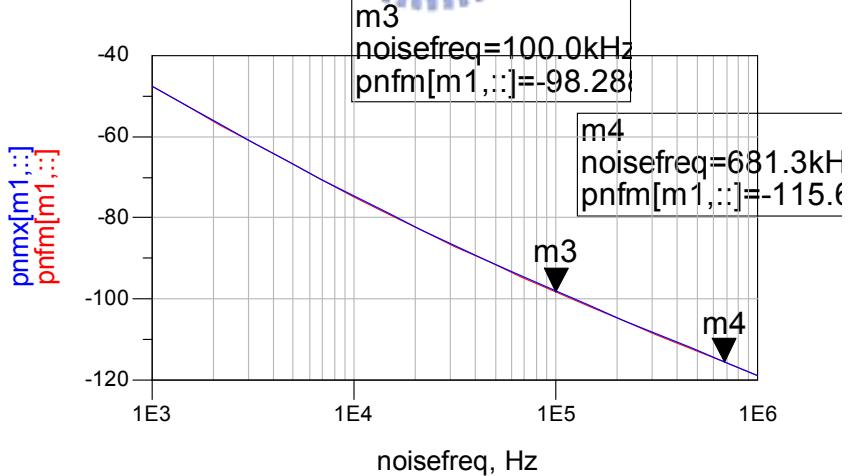

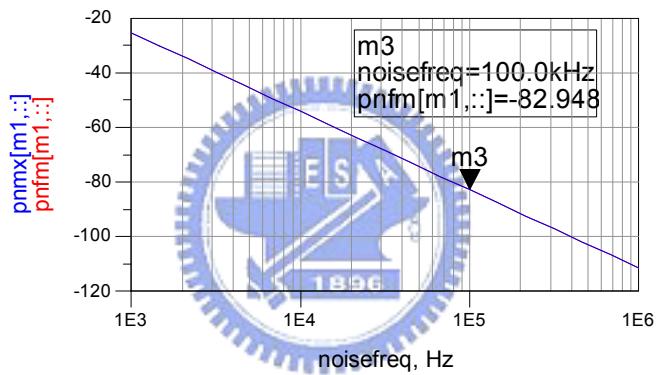

圖 3.16 的相位雜訊是在振盪頻率為 2.454GHz 下所模擬的結果。其在 offset frequency 為 100KHz 時為 -98.28dBc/Hz，在 offset frequency 為 631kHz 時為 -115.6dBc/Hz。

圖 3.16 相位雜訊頻譜

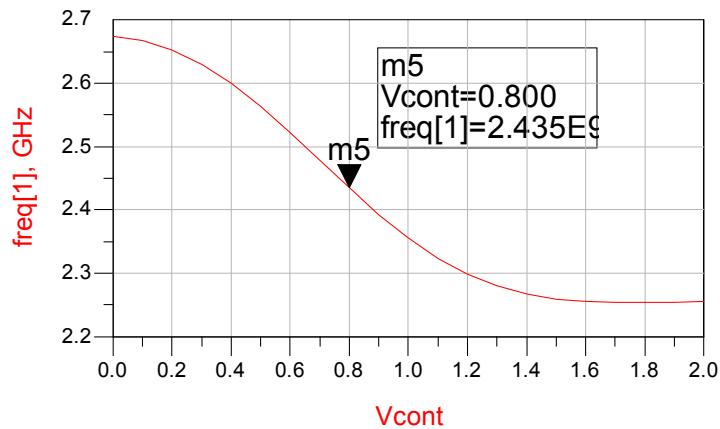

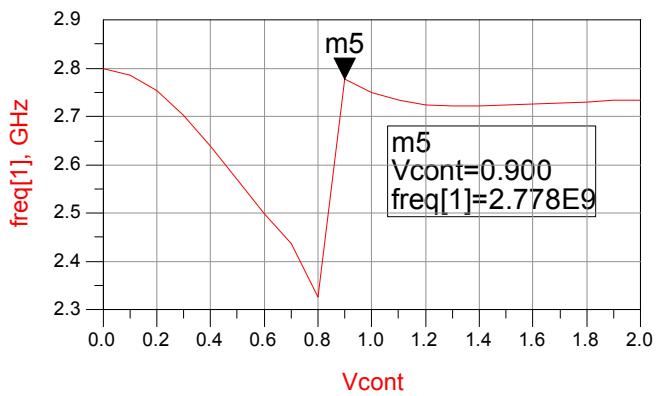

圖 3.17 為可調頻率範圍。在控制電壓 0.8V 時，振盪頻率為 2.435GHz。可

調頻率範圍為 2.25GHz 到 2.68GHz，中心頻率為 2.465GHz，增益約為-450MHz/V。

圖 3.17 控制電壓對輸出頻率作圖

圖 3.18 是輸出功率與控制電壓的關係圖。由於匹配網路的關係，當頻率越高時，最後傳輸到  $50\Omega$  負載的功率也越少。

圖 3.18 輸出功率對控制電壓作圖

| 規格                               | 數值                       |

|----------------------------------|--------------------------|

| 電源供應電壓                           | 2.5V                     |

| 消耗功率                             | 48.41mW(buffer 佔 34.3mW) |

| 輸出功率                             | -5.29dBm                 |

| 壓控振盪器中心頻率                        | 2.465GHz                 |

| 可調頻率範圍                           | 2.25GHz~2.68GHz          |

| 控制電壓範圍                           | 0V~2.0V                  |

| 各輸出波形相位差                         | 90 度                     |

| Phase Noise@ $f_0=2.4\text{GHz}$ | -98.288dBc@100kHz        |

| $K_o(\text{MHz/V})(\text{線性區})$  | -417.5                   |

表 3.1 壓控振盪器規格表

### 3.1.5 佈局考量

佈局在積體電路設計上，是一個很重要的議題。相同的電路，相同的參數設計，不一樣的佈局便會有不一樣的結果產生。這情形在射頻或類比積體電路上尤其明顯。線寬太細，寄生電阻會很大，而且當通過電流很大時，由於載子衝刷金屬線，時間久了會使金屬線有斷路的可能，產生可靠度的問題。但是金屬線太寬，寄生電容會變大。在高頻的情況下，也必須考慮金屬線的電感效應，增加預測的不確定性。並且訊號線靠太近時，兩個訊號會相互耦合影響，路徑的長短會造成訊號相位的變化，所以佈局在射頻電路上也是重要的課題。

雖然說我們在電路設計上，盡量把元件擺的對稱，但是在佈局上的對稱才是實際影響電路表現的重要因素。若佈局中不注意對稱，相位雜訊的表現會很差。電晶體必須平均分佈以利匹配，四個相位的輸出路徑更要盡量等長，否則輸出相位差可能會偏離  $90^\circ$ 。圖 3.19 為壓控振盪器的平面佈局圖

### 3.1.6 模擬結果二

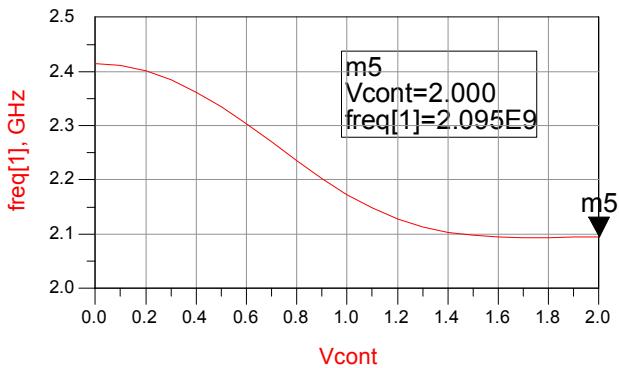

在模擬結果一的壓控振盪器其晶片製作好了之後，經過量測，發現振盪頻率有偏移的現象，量測結果可見於第四章。所以，把量測所得的寄生電容再考慮進去後，設計了一個新的壓控振盪器，其可調頻率範圍如圖 3.20 所示，由 2.3GHz 到 2.59GHz，增益為  $227.5\text{MHz/V}$ 。而相位雜訊比前一個的表現更好一些，在 Offset frequency 為 100KHz 的時候，相位雜訊是  $-103.56\text{dBc/Hz}$ ，如圖 3.21 所示。

圖 3.20 新壓控振盪器的輸出頻率對控制電壓作圖

圖 3.21 新壓控振盪器的相位雜訊模擬結果

## 3.2 除頻器

由壓控振盪器輸出的訊號，必須經由除頻器把頻率降到與參考訊號的頻率相同，才能夠由頻率相位比較器來比較。由於振盪器所輸出的頻率為 2.4GHz，如此高的頻率對除頻器來說是相當大的挑戰。除此之外，除頻器必須要可以調整除

頻倍數，使得頻率合成器的輸出頻率可以接受我們的控制。下面幾小節，便要來說明如何實現這樣的電路。

### 3.2.1 除頻器架構

我們所欲實現的頻率合成器，其必須能夠切換從 2.412GHz 到 2.472GHz 每間隔 10MHz 一個頻道。所以我們設計的除頻器至少需要有 1206、1211、1216、1221、1226、1231、1236 等七個除頻倍數。一般所採用的架構如圖 3.22 所示。

因為由壓控振盪器輸出的頻率很高，所以我們首先需要一個架構與後方數位式除頻器不同的預除器 (prescaler)，把頻率除到後方的數位式除頻器可以處理的。由圖 3.22 可以看到經由預除器之後的訊號，會送到程式計數器 (program counter) 和吞式計數器 (swallow counter)。程式計數器的會在輸入端數到一個固定的個數之後，會在輸出端送出一個訊號。而吞式計數器也是一樣，但我們可以控制吞式計數器計數的次數來控制整個除頻器的除頻倍數，不過先決要件是預除器需為雙模預除器，即可以改變倍數且只差 1。在這裡，我們的雙模預除器是除四除五，當程式計數器送訊號出來時，預除器會除五，而當吞式計數器送訊

號出來時，預除器會除四。先假設程式計數器的計算個數為 B、吞式計數器的為 A，則除頻器的除頻倍數 N 為

$$\begin{aligned}

N &= \overbrace{5+5+\dots+5}^A + \overbrace{4+4+\dots+4}^{B-A} \\

&= 5 \times A + 4 \times (B - A) \\

&= A + 4 \times B

\end{aligned} \tag{3.22}$$

。在我們的設計中，B=300，所以 N=1200+A，又吞式計數器的計數 A 可以由 0、1、2、……、63，所以除頻器的除頻倍數便可為 1200~1263。

### 3.2.2 預除器

要處理頻率為 2.4GHz 的訊號，我們很難使用一般的邏輯電路達成，因為它需要很大的電壓振幅才能達到所需要的準位。因此電流模式邏輯 (current-mode logic, CML) 便是我們另一個選擇，以流過偏壓電流大小來決定邏輯準位。由於使用的是 CMOS 製程，所以即是大家所稱的源極耦合邏輯 (source-coupled logic)。

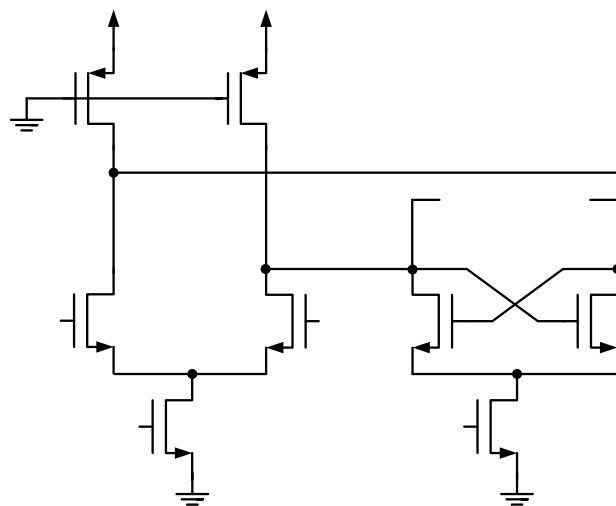

圖 3.23 SCL D 正反器 [17]

圖 3.23 所顯示的是一個 SCL 的 D 正反器。當 CLK 為 1 時，左邊的差動對工作，把 D+ 和 D- 的訊號取到 Q+ 和 Q-。不過因為訊號振幅不大，所以在 CLK 為 0 時，利用右邊的門栓 (latch) 電路把 Q+ 和 Q- 的訊號拉開。此時，左方的差動對不會作用，因此下一個 D+ 和 D- 的訊號並不會影響到 Q+、Q-。在一般的數位電路中，可以把兩個 D 正反器交錯互接，產生一個除頻倍數為二的電路。在電流模式邏輯裡也可以達到相同的功能。如圖 3.24，輸入頻率  $f_{in}$  後，輸出的

圖 3.24 頻率除二電路

頻率  $f_{out}$  會是輸入頻率的一半。接下來我們將分析一下這電路是如何運作，以便設計時可以很快地知道從何著手。經過適當的安排直流偏壓點之後，M1 及 M2 在打開時的電流令其為  $I$ ，在  $Q$  處的直流電壓為  $V_{DC}$ 。令  $v_o(t) = v_{Q+}(t) - v_{Q-}(t)$ ，且在時間  $t=0$  的時候，輸出波形正要從最低點切換到最高點，所以  $v_o(0) = -A$ ，其中  $A$  為輸出振幅。由於我們將 M7 和 M8 的閘極接地，所以 M7、M8 都是工作在三極區 (triode region)。輸入訊號的週期為  $T$ ，且在  $t=0$  時，輸入訊號剛從 0 轉換到 1。所以我們可以寫下在  $0 \leq t < \frac{T}{2}$  時的輸出：

$$v_o(t) = IR - (IR + A)e^{-\frac{t}{RC}} \quad (3.23)$$

其中因為 M7、M8 都在三極區所以  $R = (R_1 + R_2)/2$ ，

$$R_1 = \frac{VDD - V_{DC} + A}{\frac{\mu_p C_{ox}}{2} \frac{W}{L} \left[ 2(VDD - |V_t|)(VDD - V_{DC} + A) - (VDD - V_{DC} + A)^2 \right]}$$

$$R_2 = \frac{VDD - V_{DC} - A}{\frac{\mu_p C_{ox}}{2} \frac{W}{L} \left[ 2(VDD - |V_t|)(VDD - V_{DC} - A) - (VDD - V_{DC} - A)^2 \right]}$$

。當  $t = \frac{T}{2}$  時，左方的差動對便關閉，換右方的門栓電路啟動，而輸出為

$$v_o\left(\frac{T}{2}\right) = v_m = IR - (IR + A)e^{-\frac{t}{RC}} \quad (3.24)$$

。在前面的章節有提到，此種門栓電路會產生負電導，令負電導為  $G_m$ ，所以看

到的等效電阻便為  $\frac{RG_m - 1}{G_m}$ ，則在  $\frac{T}{2} < t < T$  時輸出為

$$v_o(t) = IR - (IR - v_m)e^{-\frac{(t-T/2)G_m}{(RG_m-1)C}} \quad (3.25)$$

。在  $t = T$  時，輸出為

$$v_o(T) = IR - (IR - v_m)e^{-\frac{TG_m}{2(RG_m-1)C}} \quad (3.26)$$

將 (3.24) 代入 (3.26)，可得

$$v_o(T) = IR \left( 1 - e^{-\frac{T}{2C(G_mR-1)R}} \right) - A e^{-\frac{T}{2C(G_mR-1)R}} \quad (3.27)$$

。事實上， $v_o(T) = A$ ，所以

$$A = \frac{1 - e^{-\frac{T}{2C(G_mR-1)R}}}{1 + e^{-\frac{T}{2C(G_mR-1)R}}} IR \quad (3.28)$$

由 (3.23) 或 (3.25) 我們知道，振幅除非直到  $t \rightarrow \infty$ ，否則 A 終將不會等於  $IR$ 。

因此我們假設這樣的時間只足夠 A 成長到  $0.9IR$ ，所以把  $A = 0.9IR$  代入 (3)，便

可以得到

$$f_{\max} = \frac{1}{T} = \frac{2G_m R - 1}{5.89RC(G_m R - 1)} \quad (3.29)$$

，我們稱  $f_{\max}$  為此 SCL 的 D 正反器可以操作的最大頻率。當然，事實上絕對無法大達此頻率，因為我們在過程中使用了很多理想性的假設。不過，我們仍然可以從(3.29)中看出設計的方向。首先若在 Q+、Q-端附近的寄生電容太大便會使  $f_{\max}$  減少，在此寄生電容的主要貢獻者便是電晶體，所以電晶體的尺寸不能太大。第二，M7、M8 是當作電阻來使用，由於第一點說電晶體的尺寸不可太大，所以在避免加大電晶體的情況下，將閘極電壓偏壓到 0V 是最好的方法。若頻率仍無法到達需求，則再把電晶體通道寬度加大，也可以提升操作頻率，不過到達一定的大小後，寄生電容的效應便會主宰，使得操作頻率無法繼續上升。第三， $G_m$  越大，可以使操作頻率上升。不過， $G_m$  越大，M5、M6 就要加大，因為輸出端一次就就會看到由 M5、M6 所貢獻的寄生電阻，把尺寸加大，很容易使時間常數變的更大，又  $G_m$  是小訊號行為，在訊號成長到一定大小時，便由大訊號掌控，所以建議 M5、M6 尺寸小即可。

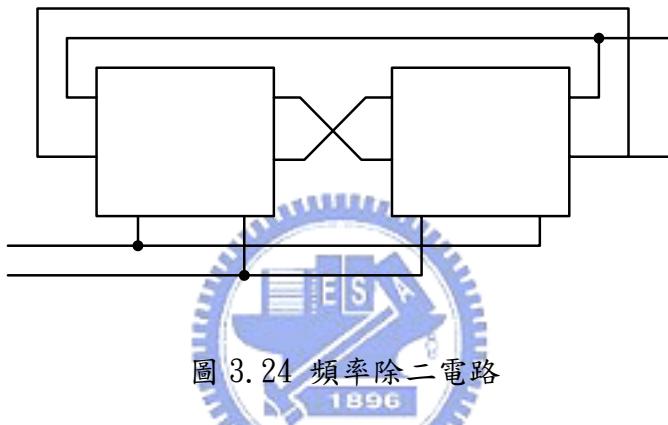

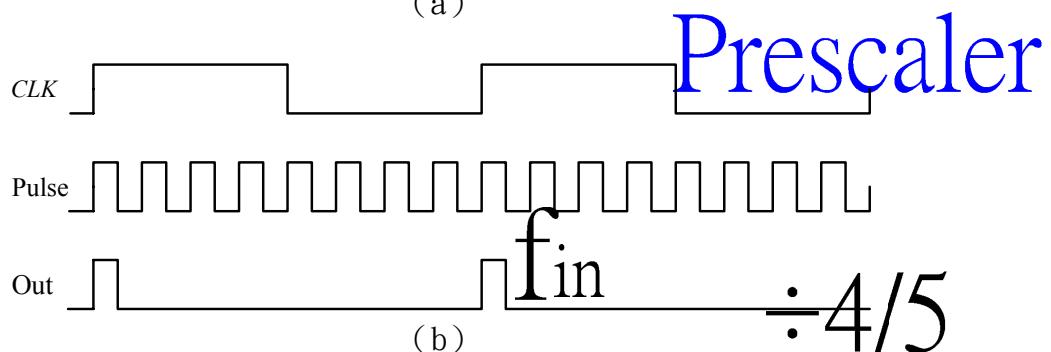

圖 3.24 除四除五電路

由於我們的預除器是可以除四也可以除五的雙模預除器，在數位電路也有此類電路，如圖 3.24 所示，其中 MC 代表模態控制 (mode control)，MC=1 時為除

四功能，MC=0 時為除五功能。此電路中間使用 NOR 閘作串接，另外也可以使用 NAND 閘來作串接，不過此時，MC=0 時為除四，MC=1 時為除五。在我們的設計中為了方便控制設計起見，將使用 NOR 閘的架構。由於我們使用的是 SCL 的架構，所以與圖 3.24 的不同點只是所有單端接改成為雙端，一次就輸出成對的訊號，當然 NOR 閘也要採用 SCL 的架構，如圖 3.25 所示。

圖 3.25 SCL OR 閘[17]

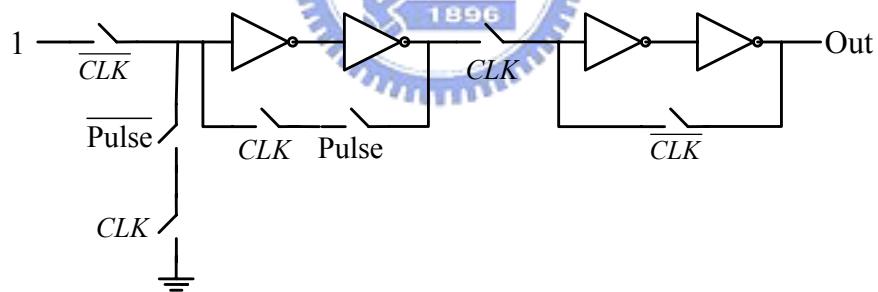

### 3.2.3 除頻器電路與設計考量

整個除頻器電路包括預除器、程式計數器和吞式計數器，如圖 3.26 所示。為了節省功率消耗和面積，將緊接在預除器後方的兩個除二電路給程式計數器和吞式計數器使用。我們可以由二進位制的  $B_5B_4B_3B_2B_1B_0$  來控制吞式計數器的計數次數。控制電路的部份就由一個 SR 正反器來控制，要注意的是由程式計數器和吞式計數器來的訊號寬度不可以太寬，以免干擾到 SR 正反器和預除器的正常運作。因此使用一個脈衝觸發器（pulse trigger）來達成此任務，我們設計的

脈衝觸發器如圖 3.27 所示。由 Pulse 端送入頻率較高的波形，則當 CLK 為 1 的時候，輸出端便會取出一個週期的高頻訊號。

圖 3.26 完整除頻器電路

(a)

圖 3.27 (a) 脈衝觸發器，(b) 脈衝觸發器的時序圖

在整個設計上，還有一些是必須要注意的。在從電流模式邏輯轉接到電壓模

式邏輯時，有可能直流準位不符合後續的操作，這時要作一個準位轉換器，來使兩邊可以順利連接。由於整個除頻器是非同步運作，當程式除頻器送出訊號時，因為經過很多閘延遲，預除器送出來的訊號可能已經跑了半個週期，不過這並不會影響正確的除頻倍數。會使除頻倍數不太正確的延遲效果是在吞式除頻器和程式除頻器之間的延遲，會使除頻倍數有 1~2 的變化，所以在設計時要使延遲時間盡量相同。除了設計時要注意，佈局時這些線路必須盡量縮短，免得使延遲再度不對稱。

### 3.2.4 模擬結果

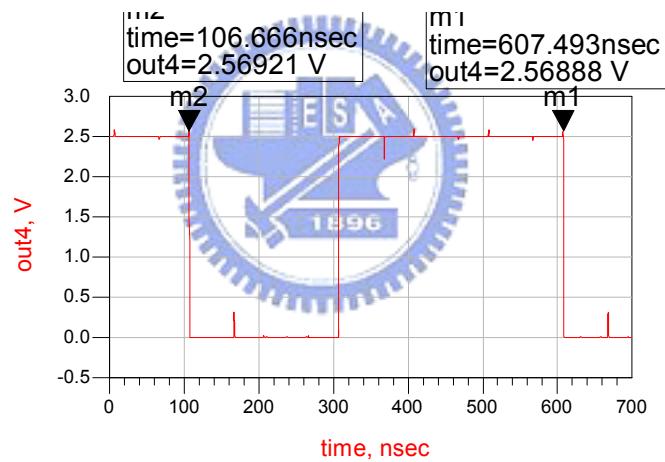

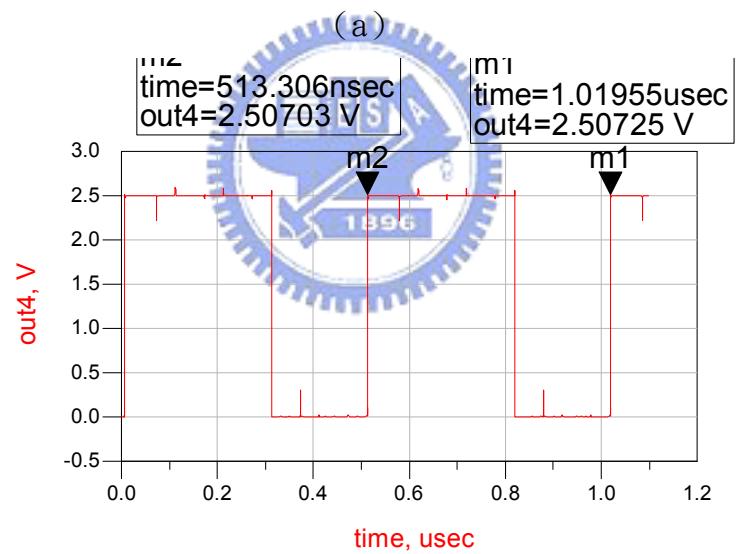

圖 3.28、圖 3.29 為除頻器的模擬結果，分別為在  $B_5B_4B_3B_2B_1B_0 = 000010$  的除 1202 和  $B_5B_4B_3B_2B_1B_0 = 001111$  除 1215。在兩圖中的 (a)，是在圖 3.27 中 SR 正反器的輸入和輸出，而  $V_{out+}$  為預除器的輸出，波形較寬的為除五、波形較窄的為除四。我們可以看到在除 1202 時，有兩個除五的波形，而在除 1215 時，有 15 個除五波形。我們的輸入訊號為 2.4GHz，所以在圖 3.28 (b) 為 1.996697MHz，

在圖 3.29 (b) 為 1.975332MHz。而整個除頻器的消耗功率約為 2.76mW。

(a)

(b)

圖 3.28 除頻器執行除 1202

(b)

圖 3.29 除頻器執行除 1215

### 3.3 相位頻率偵測器

#### 3.3.1 操作原理與電路實現

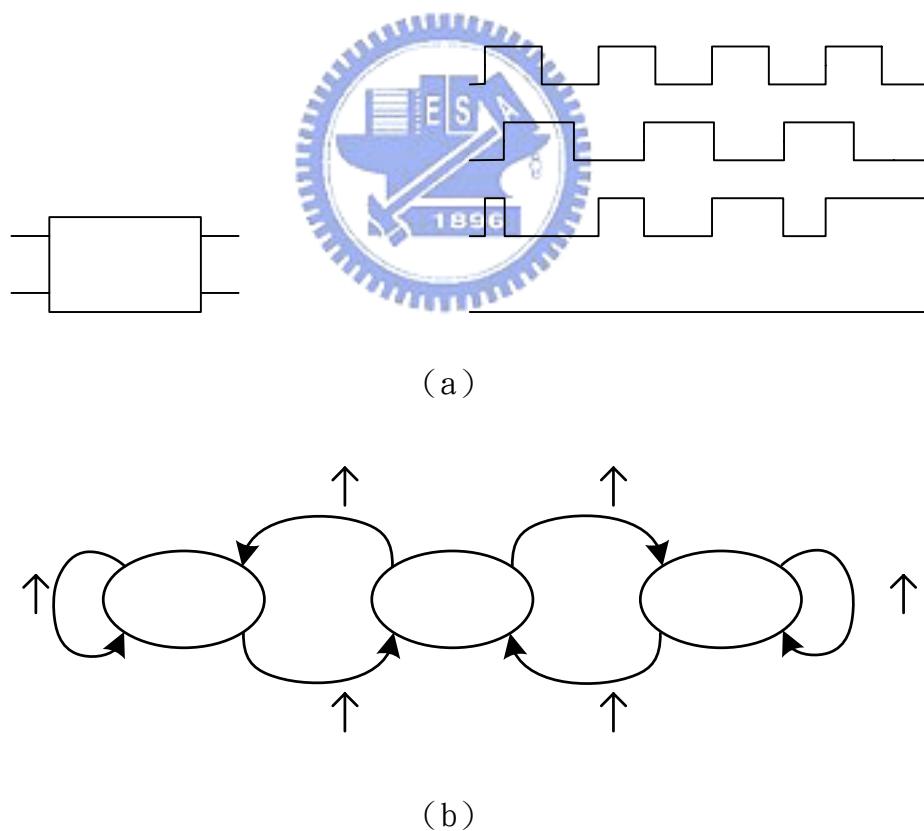

相位頻率偵測器在整個頻率合成器中是一個很重要的角色，它偵測由除頻器出來的訊號和參考訊號之間相位和頻率的變化，並且把之間的差異送出。與早期類比和數位的相位偵測器 (XOR) [5]來相比，因為相位頻率偵測器的兩個輸出並非反相，所以可以利用兩個輸出的不同，表現出兩個訊號在頻率與相位之間的差異，加速整個迴路的鎖定。這類的又稱其為「三態相位偵測器」，我們可以由圖 3.30 看到它如何三個狀態中切換。

圖 3.30 三態相位偵測器 (a) 操作波形，(b) 三態圖。[4]

在圖 3.30(a)為此偵測器的操作波形，我們可以由圖 3.30(b)來瞭解為何會

是如此運作。假設一開始處在 State 0，當在 A 的訊號其上升波形先出現，UP 則會由 0 上升至 1，狀態便會由 State 0 切換到 State I。A 上升波形持續出現，狀態就一直處在 State I。假使此時 B 上升波形開始出現，會使 UP 回到 0，則 State I 切換回 State 0。若在的上升波形未出現前，B 已經再度出現，則 DN 便會由 0 上升到 1，此時會進入 State II。相位頻率偵測器就是在這三個狀態互相切換，並利用 UP 和 DN 告知哪個訊號頻率或相位是領先的。

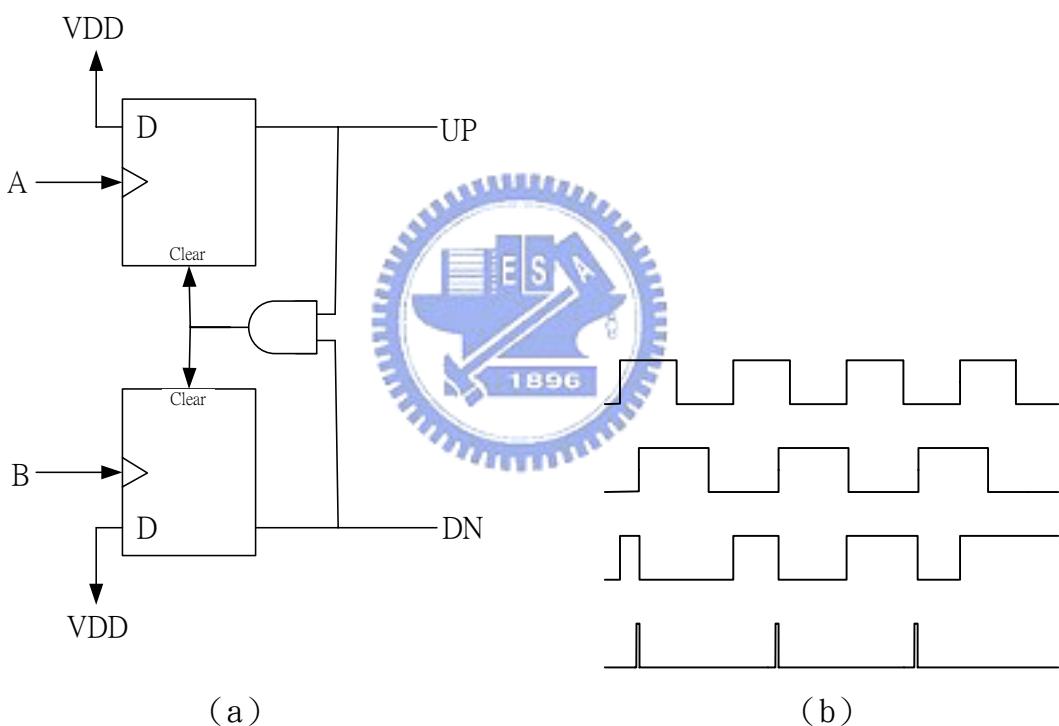

圖 3.31 相位頻率偵測器 (a) 電路實現，(b) 操作波形。

我們可以使用兩個 D 正反器和一個 AND 閘來實現相位頻率偵測器，如圖 3.31 (a)。然而這樣的電路卻有著非理想的效應，我們加上 AND 閘為了當 UP 和 DN 訊號同時為 1 時，使兩個 D 正反器的 Q 皆從 1 變回 0。由於這樣的迴授需要一段延遲的時間，使得輸出會有此段延遲寬度的脈衝，如圖 3.31 所示。這樣的現象

當偵測器兩個訊號同頻率同相位時，產生理想時不應有的雜訊。這也是之前所說的由參考訊號所來的雜訊成因之一。這雜訊在製程越進步、電晶體越小、延遲越短之後，會降低它的影響。

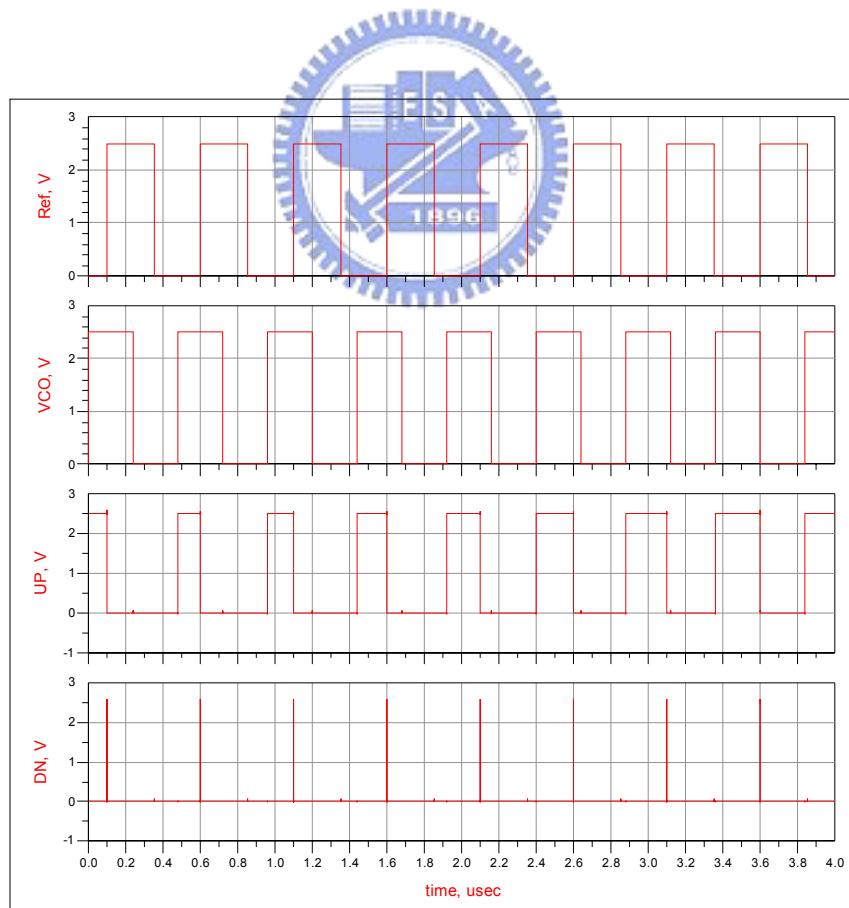

### 3.3.2 模擬結果

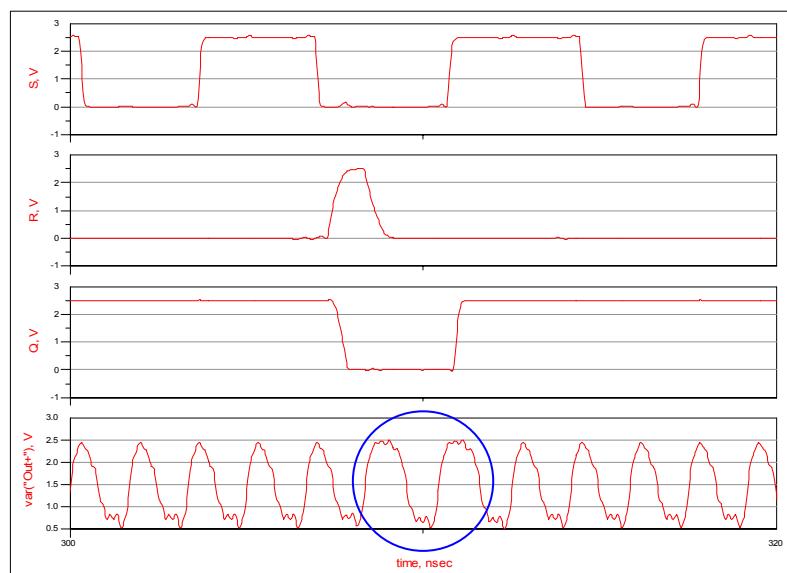

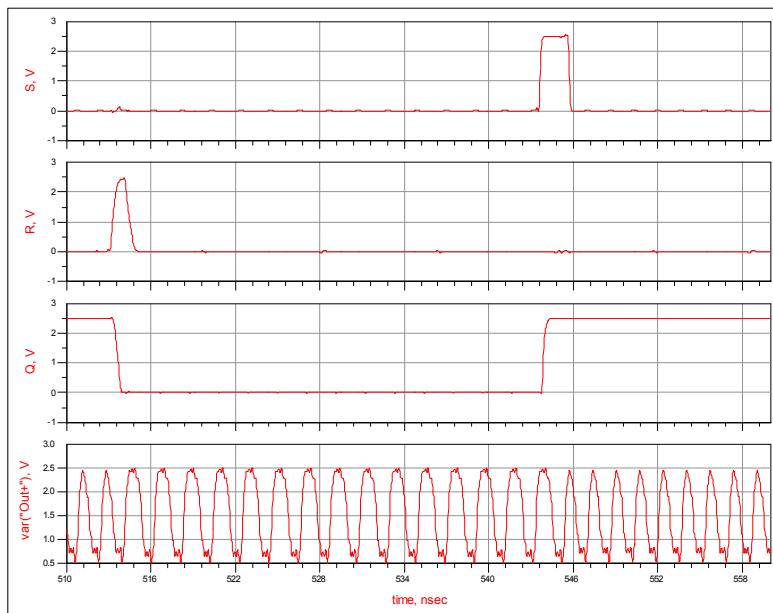

圖 3.32 為相位頻率偵測器的模擬結果，其中 VCO 的訊號為 2.083MHz 而 Ref 的訊號為 2MHz。由於我們所實現的 VCO 其增益為負的，所以若 VCO 的頻率較高，需要使控制電壓升高使得頻率降低。因此其模擬結果與我們預期的模擬結果相同。

圖 3.32 相位頻率偵測器模擬結果

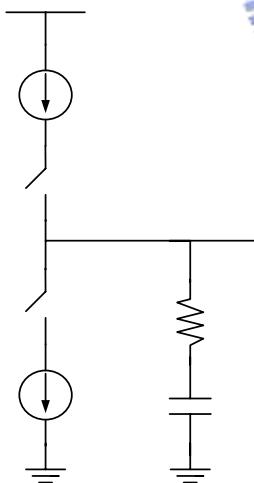

## 3.4 電荷峯浦和迴路濾波器

當相位頻率偵測器送出 UP 和 DN 的訊號需要有電荷峯浦的輔助，將電流充到濾波器裡的電容，才能準確的控制迴路的穩定。若電荷峯浦和迴路濾波器設計的不理想，便會使雜訊影響到壓控振盪器。下面我們將對電荷峯浦和濾波器的電路實現作討論。

### 3.4.1 設計考量與電路實現

電荷峯浦要設計接收從偵測器 UP 和 DN 來的數位訊號，並以固定的電流向濾波器充電。這固定的電流值設定，由第二章的討論知道，對於迴路的響應有非常重大的影響，過大與過小都會使得穩定時間變長。在第二章中，我們已經決定好這電流值的大小。

在電荷峯浦中，雜訊主要的來源是電路的不匹配、電荷分享和時脈饋入 (clock feedthrough) 的問題。電路若不匹配，會使充電電流和放電電流不相同，則即使是參考訊號和振盪器的訊號相位差為零時，控制電壓仍然會改變，使振盪器的振盪頻率改變。在圖 3.33 中，UP 和 DN 各控制一個開關，使充電電流流進濾波器或使放電電流把電荷從濾波器中取出。開關打開時，通道內會存在著許多電荷，而當此開關關閉之後，原本在通道內的電荷有一部分就會往濾波器去。這樣的誤差，必須等到下一個訊號比較時才會再次修正。而時脈饋入的問題是，由於 UP 和 DN 是數位訊號，其波形上升下降都非常的迅速，含有很高頻的成分，使經過電晶體中的寄生電容倒達濾波器中。又 UP 及 DN 的訊號又是有週期性

的，便會在頻率合成器的輸出有突波（spur）的出現。

圖 3.33 電荷砲浦示意圖

圖 3.34 電荷砲浦和濾波器電路圖

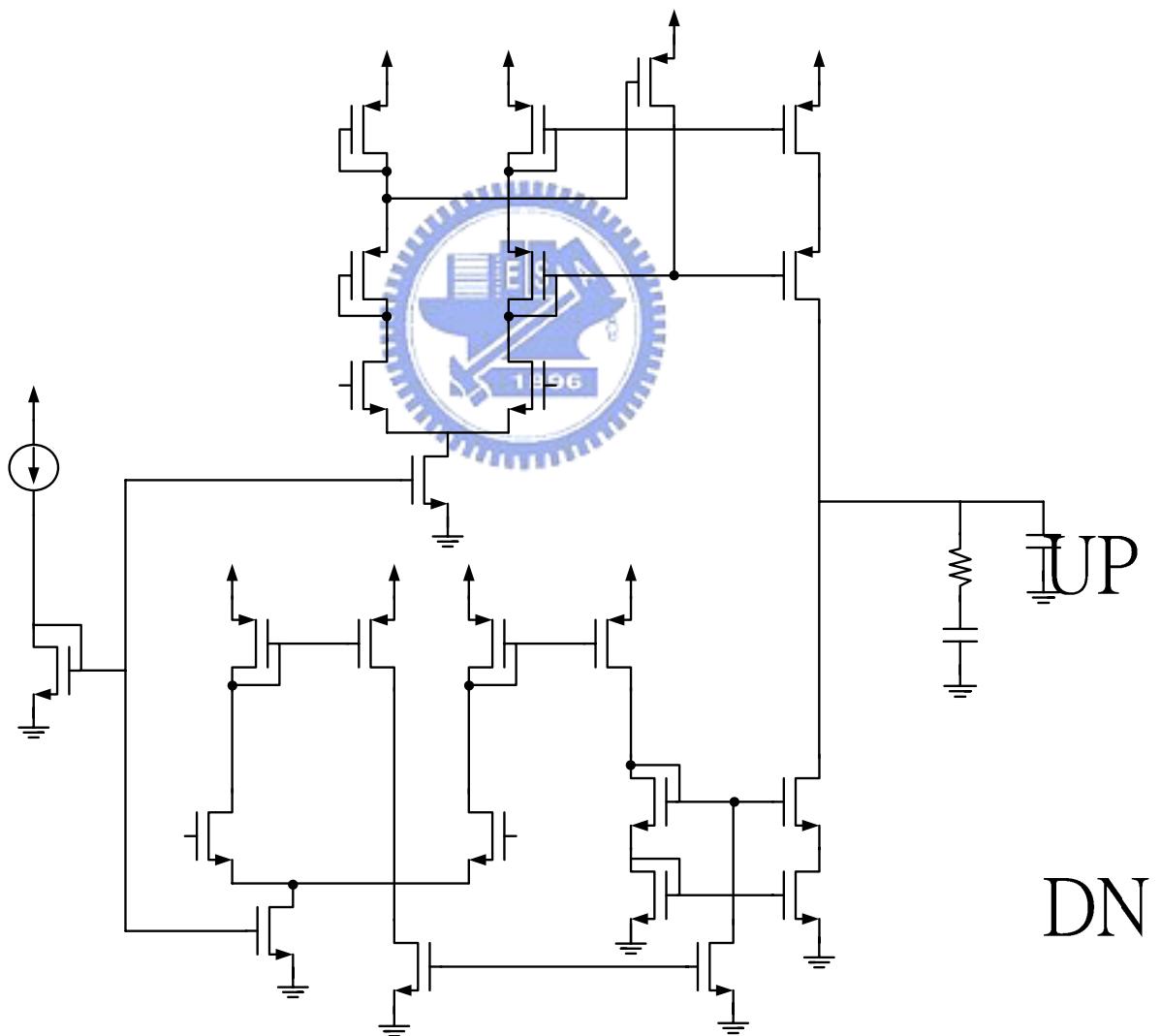

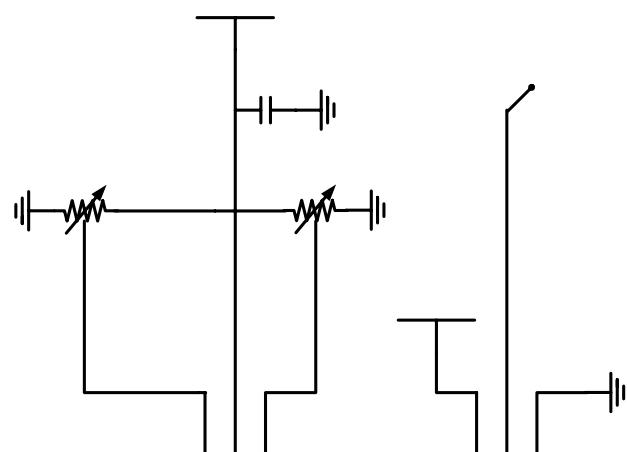

圖 3.34 為我們所設計的電荷砲浦電路圖，其中 UPb 為 UP 的反相，DNb 為 DN

的反相。這電路並不包含在第二章所提到的第二個電荷峩浦。不過第二個電荷峩浦與第一個架構一模一樣，只不過 UP 與 UPb 和 DN 與 DNb 是顛倒過來的。也就是說第一個峩浦充電時，第二個是放電，而第一個峩浦是放電的時候，第二個是充電。另外第二個峩浦的輸出是接在  $R$  和  $C_2$  之間。為了要避免時脈饋入的效應，我們將 DN 和 UP 訊號先由差動對 M3、M4 和 M16、M17 輸入，再由差動對的輸出去控制開關。為了加速電荷峩浦充電和放電的關閉，我們使用差動訊號來控制 M22 和 M10 幫助 M24 和 M14 的關閉。因為控制電壓會改變，所以電荷峩浦輸出點的電壓也會改變，為了使充電和放電電流能不受控制電壓高低的影響，所以採用串疊電流鏡，增加輸出電阻。第一個電荷峩浦與第二個電荷峩浦的電流為維持固定的比例，第一個峩浦的 M2、M15 與第二個的 M2、M15 在佈局時要做好尺寸的匹配。

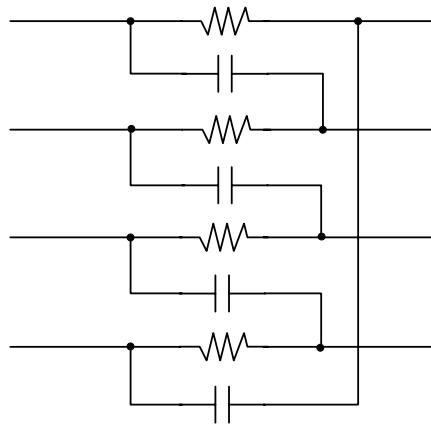

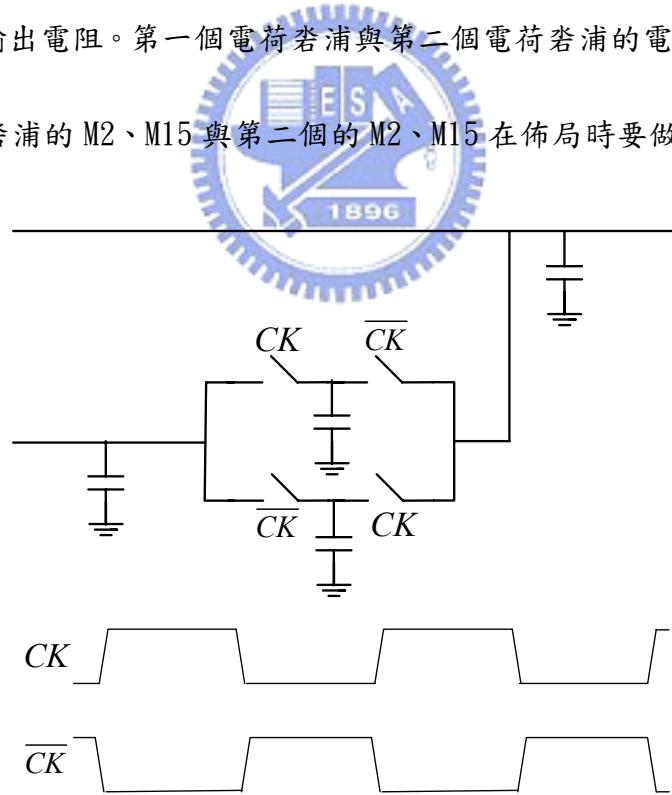

圖 3.35 迴路濾波器

在濾波器中，我們將使用切換電容來取代電阻，如圖 3.35 所示。控制訊號 CK 我們使用一個除二電路將參考訊號的頻率除二，也就是 CK 的頻率為  $f_{ref}/2$ ，

但是要注意不要讓 CK 和  $\overline{CK}$  同時為 1。所以等效電阻將是  $1/f_{ref} C_s$ 。我們的開關將使用 CMOS 實現，且電晶體的尺寸要盡量作小，使電荷分享的效應降到最低，避免 CK 的訊號影響到控制電壓。

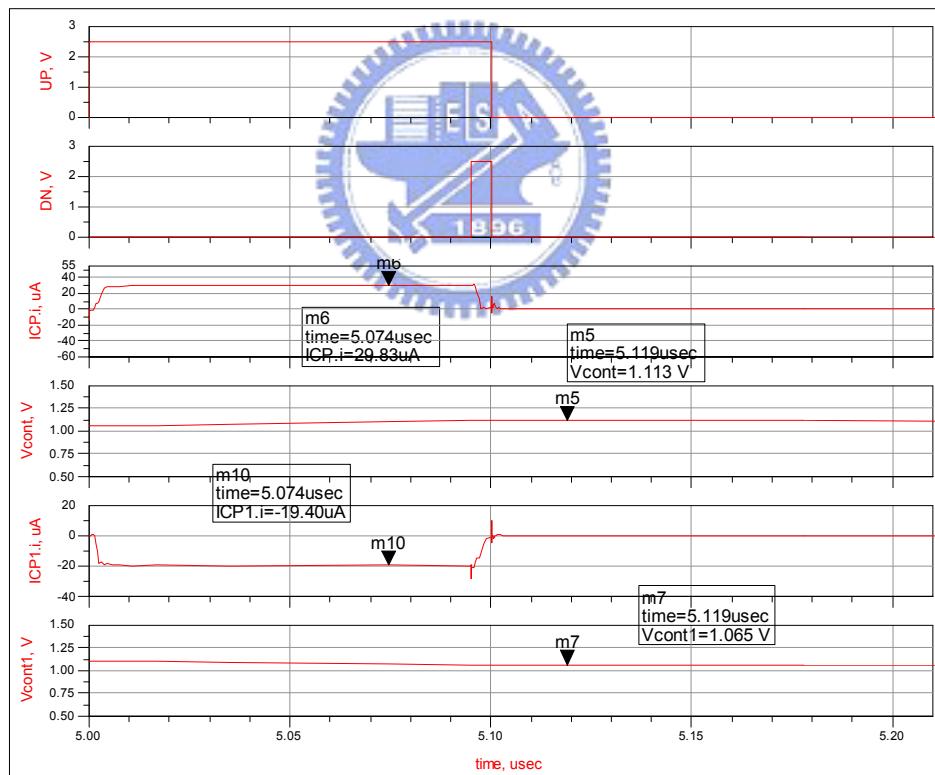

### 3.4.2 模擬結果

圖 3.36 為電荷峯浦與濾波器的模擬結果，其中 CP 指的是第一個電荷峯浦，CP1 指的是第二個電荷峯浦， $V_{cont1}$  為  $R$  與  $C_2$  之間的節點。UP 與 DN 為所加入的理想訊號，濾波器內的電阻是真實的電阻，非切換電容。

圖 3.36 電荷峯浦與濾波器模擬結果

### 3.5 頻率合成器

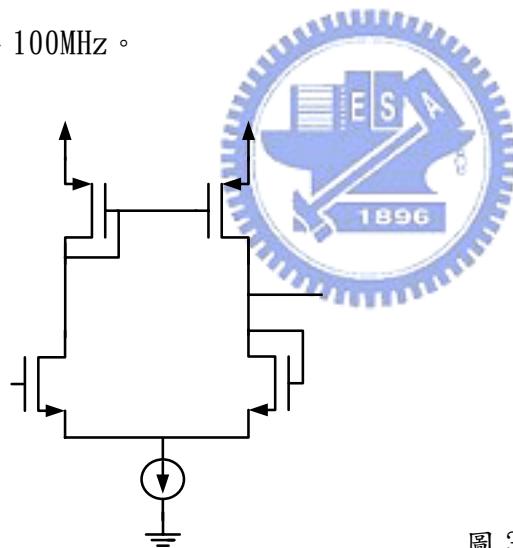

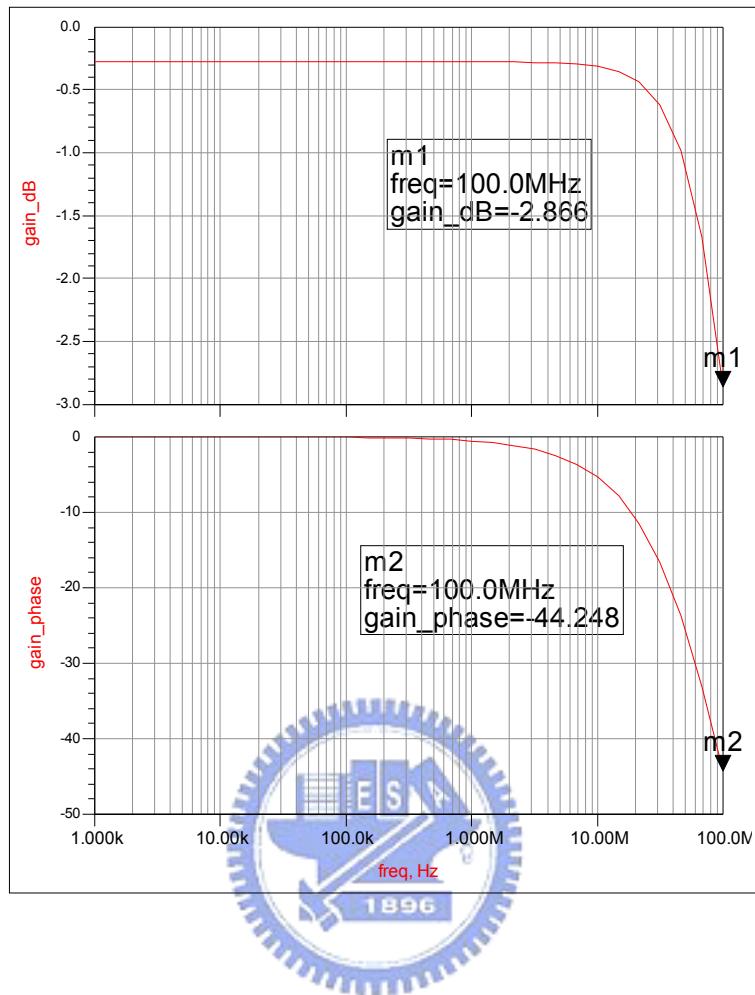

在設計完各部份的電路之後，便把所有的電路連接起來組合成一個頻率合成器。在這之前還必須再加入一個電路，位於濾波器到壓控振盪器之間的緩衝電路。因為由控制電壓端看入振盪器，會有很大的電容，這電容又是壓控電容，所以如果不加緩衝電路，濾波器的特性將會隨著控制電壓的大小而有所改變。對於這個緩衝電路，我們最在意的是它的頻率響應，希望它所貢獻的極點或零點盡量遠離迴路頻寬，以免影響到已設計好的迴路特性。我們使用簡單的主動負載差動電路來實現這個增益為一緩衝電路，如圖 3.37 所示。而其模擬結果如圖 3.38，3dB 頻寬約為 100MHz。

圖 3.37 簡單的緩衝器

圖 3.38 緩衝器模擬結果

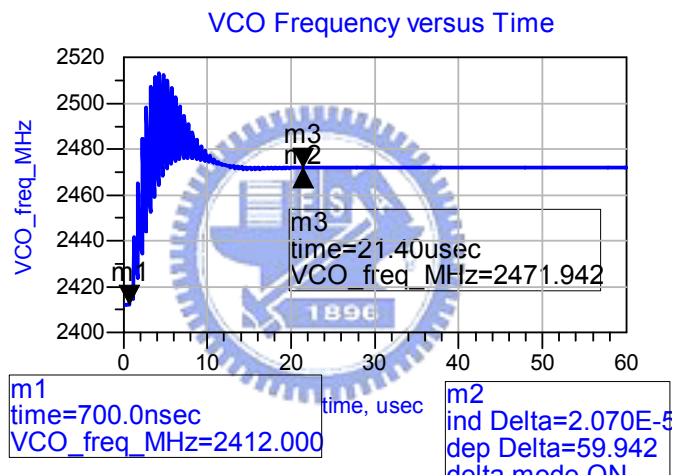

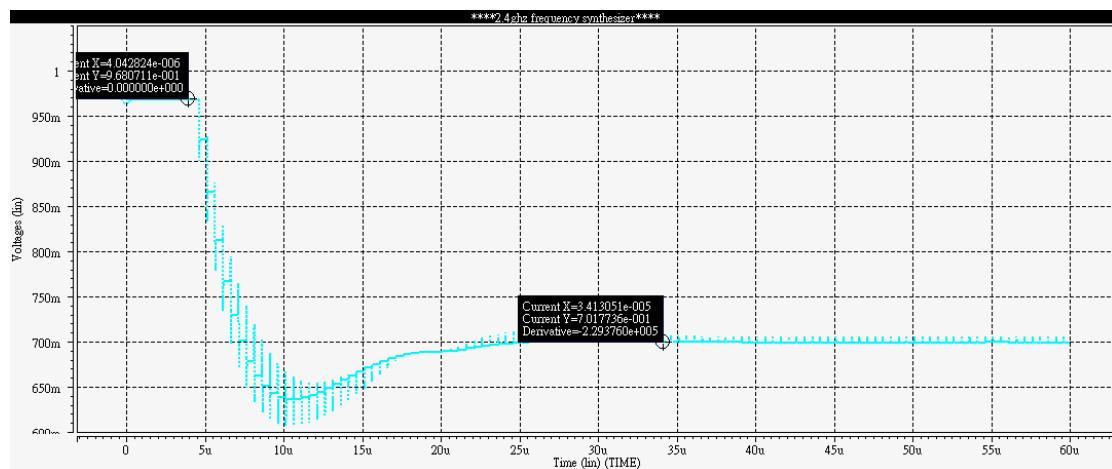

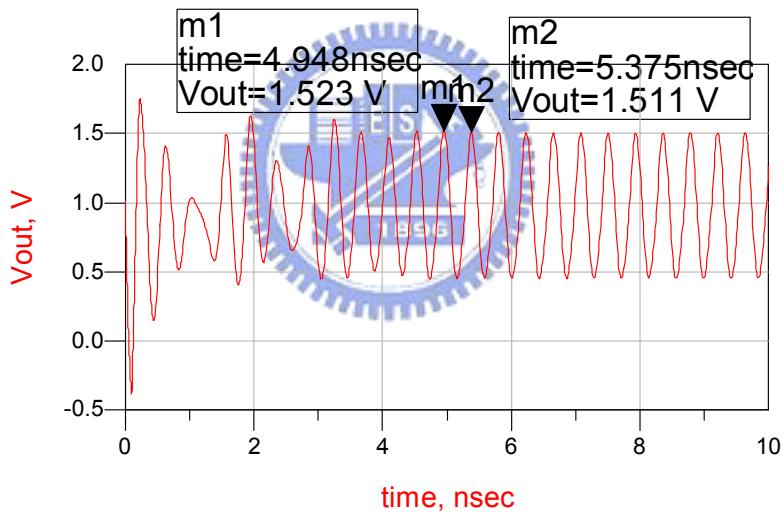

電路全部連接後，便為雙電荷砲浦的三階頻率合成器。由於 ADS 在跑如此長時間的暫態模擬會發生無法收斂的情形，因此將整個電路換到 Hspice 中模擬。我們先將除頻倍率固定在除 1206，在第  $4\mu\text{s}$  時變換除頻倍率到除 1236，也就是從最小通道  $2.412\text{GHz}$  切換到最大通道  $2.472\text{GHz}$ 。可由壓控振盪器的輸出頻率對控制電壓得知頻率合成器約在  $34\mu\text{s}$  時，在穩定範圍之內，所以穩定時間約為  $30\mu\text{s}$ ，與行為模擬差約  $10\mu\text{s}$ 。模擬結果如圖 3.39 所示。新振盪器包含輸入及輸出的緩衝電路消耗功率約  $50\text{mW}$ ，除頻器耗約  $2.76\text{mW}$ ，電荷砲浦耗約  $0.75\text{mW}$ ，

其他電路耗約  $0.25\text{mW}$ ，所以整個頻率合成器總共消耗約  $53.76\text{mW}$ 。

圖 3.39 頻率合成器穩定時間模擬結果

## 第四章 實驗及量測結果

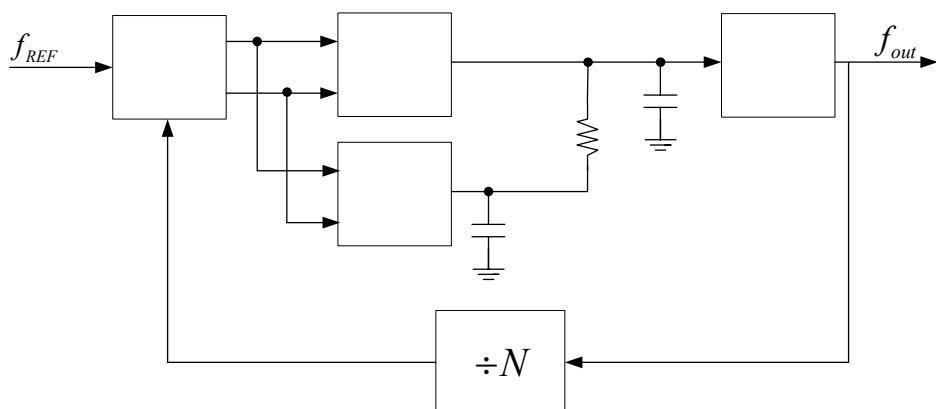

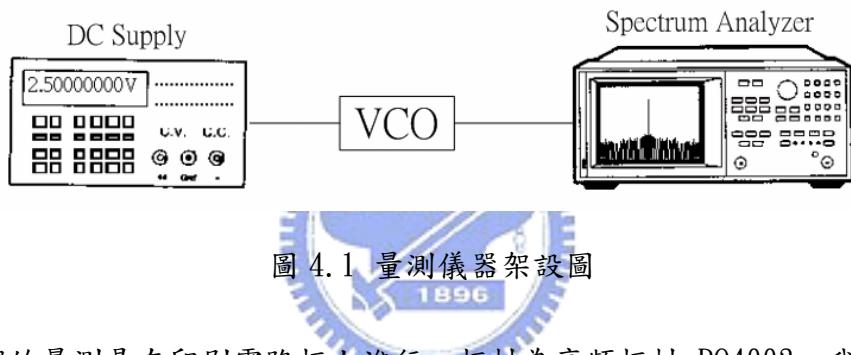

### 4.1 量測儀器架設

由於有限的研究時間只有將壓控振盪器下線於台積電  $0.25\mu\text{m}$  CMOS 製程，所以我們的量測將針對所下出去的壓控振盪器。我們的量測儀器架設如圖 4.1 所示，其中直流電源是使用 DATRON 4808 Multi-Function Calibrator，頻譜分析儀是使用 HP 8566B Spectrum Analyzer，操作頻率為  $100\text{Hz} \sim 2.5\text{GHz}$ 、 $2\text{GHz} \sim 22\text{GHz}$ 。

圖 4.1 量測儀器架設圖

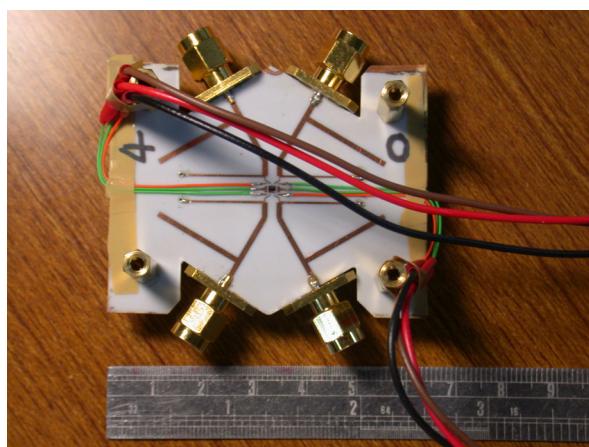

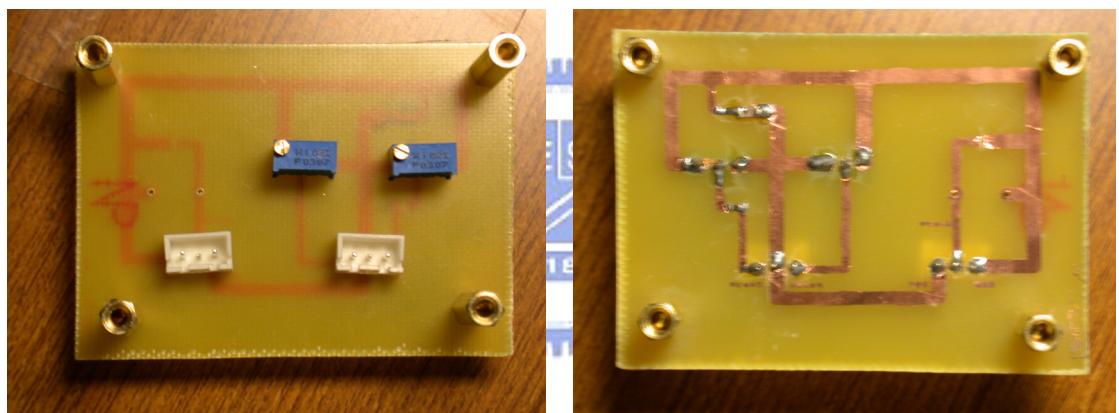

我們的量測是在印刷電路板上進行，板材為高頻板材 R04003，我們將在板上使用微帶線 (microstrip line) 作輸出匹配網路，匹配網路及微帶線電路如圖 4.2 所示。圖 4.3 為晶片打線圖，圖 4.4 為偏壓電路板，圖 4.5 為偏壓電路圖。

圖 4.2 壓控振盪器晶片及微帶線電路

圖 4.3 晶片打線圖

圖 4.4 偏壓電路板

圖 4.5 偏壓電路圖

圖 4.6 Wiltron Swept Frequency Synthesizer 67458 (100MHz~18GHz)

圖 4.7 Narda Hybrid 4356B (2~18GHz)

圖 4.8 WE Broadband RF Mixer 1577 (1~18GHz)

圖 4.9 Narda Power Divider 4456.2 (2~18GHz)

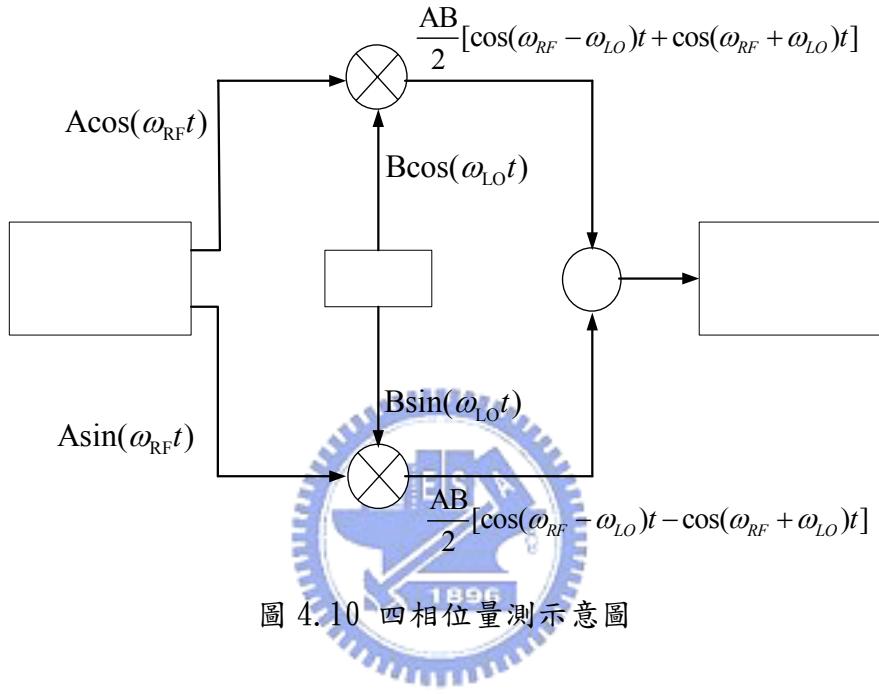

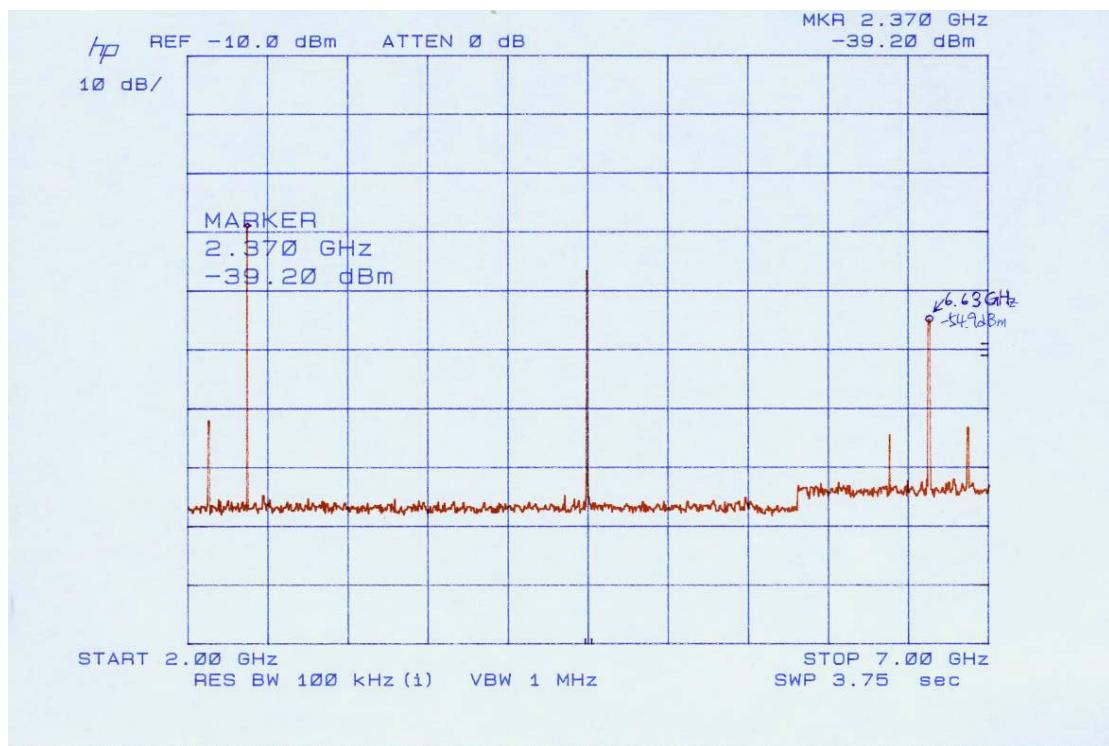

為了量測四相位的訊號，我們將使用一台訊號產生器（圖 4.6）、一個正交分合波器（quadrature hybrid，圖 4.7）、兩個混波器（圖 4.8）、一個功率結合器（Power Combiner，圖 4.9）和頻譜分析儀。如圖 4.10 所示，我們利用訊號產生器和正交分合波器產生輸出相位相差  $90^\circ$  的訊號，與壓控振盪器的輸出作混波後，再相加送入頻譜分析儀。假設若振盪器四個輸出功率皆相等且完美四相位的話，我們將可以在頻譜分析儀上看見只有一根訊號差頻在  $\omega_{RF} - \omega_{LO}$ ，電壓振幅大小為  $AB$ 。若相位與  $90^\circ$  相差  $\phi$ ，則我們將會見到兩根訊號，差頻與和頻。差頻在  $\omega_{RF} - \omega_{LO}$ ，電壓振幅大小為  $AB \cos \frac{\phi}{2}$ 。和頻在  $\omega_{RF} + \omega_{LO}$ ，電壓振幅大小為  $AB \sin \frac{\phi}{2}$ 。若是相位無誤差，但輸出電壓振幅相差  $\delta$ ，則我們也可以看到兩根訊號。一根在  $\omega_{RF} - \omega_{LO}$ ，電壓振幅大小為  $A(2B + \delta)/2$ 。另一根在  $\omega_{RF} + \omega_{LO}$ ，電壓振幅大小為  $A\delta$ 。若相位相差  $\phi$ ，一個振幅為  $B_1$ ，另一個振幅為  $B_2$ ，則我們亦可以在頻譜上發現兩根訊號。差頻訊號在  $\omega_{RF} - \omega_{LO}$ ，電壓振幅大小為

$C_{\omega_{RF}-\omega_{LO}} = \frac{A}{2} \sqrt{B_1^2 + B_2^2 + 2B_1B_2 \cos\phi}$ ，和頻訊號在  $\omega_{RF} + \omega_{LO}$ ，電壓振幅大小則為

$C_{\omega_{RF}+\omega_{LO}} = \frac{A}{2} \sqrt{B_1^2 + B_2^2 - 2B_1B_2 \cos\phi}$ 。所以相位誤差  $\phi$  可由下式算出

$$\left( \frac{C_{\omega_{RF}-\omega_{LO}}}{C_{\omega_{RF}+\omega_{LO}}} \right)^2 = \frac{B_1^2 + B_2^2 + 2B_1B_2 \cos\phi}{B_1^2 + B_2^2 - 2B_1B_2 \cos\phi} \quad (4.1)$$

。

圖 4.10 四相位量測示意圖

## 4.2 量測結果

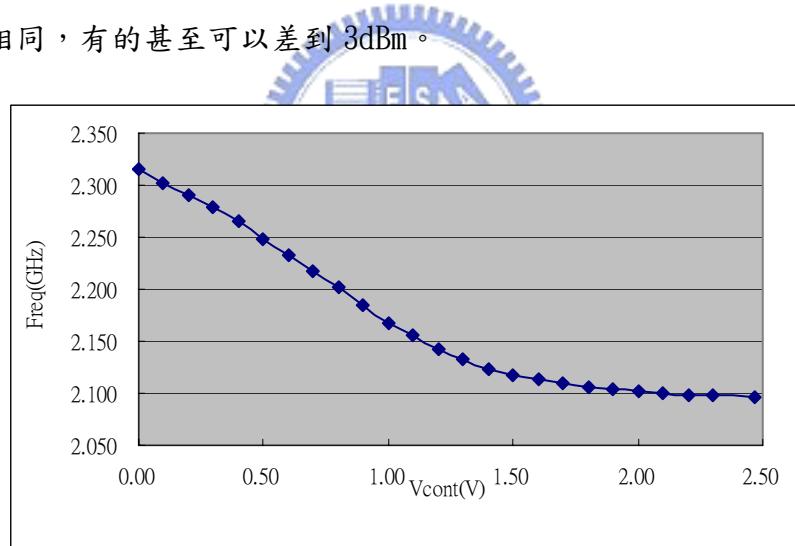

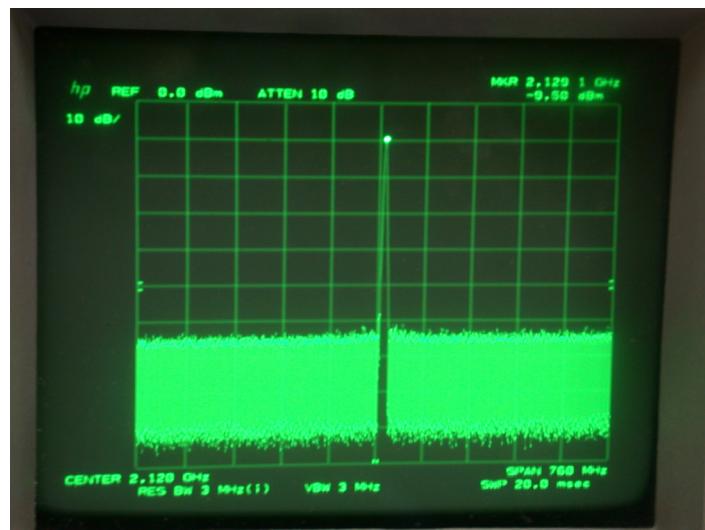

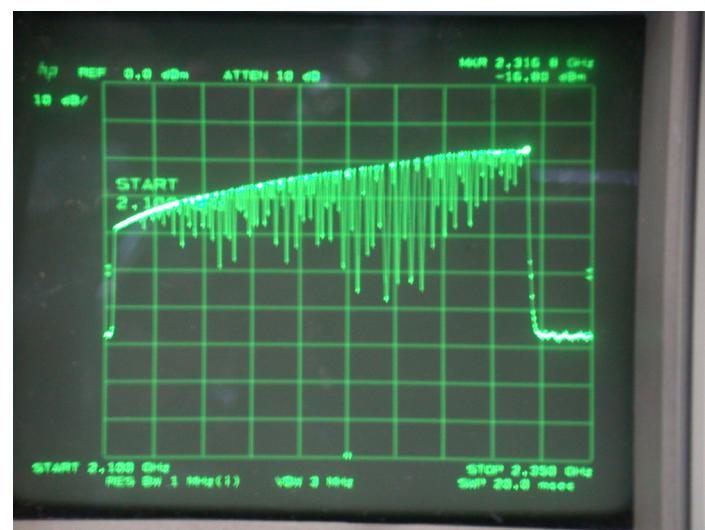

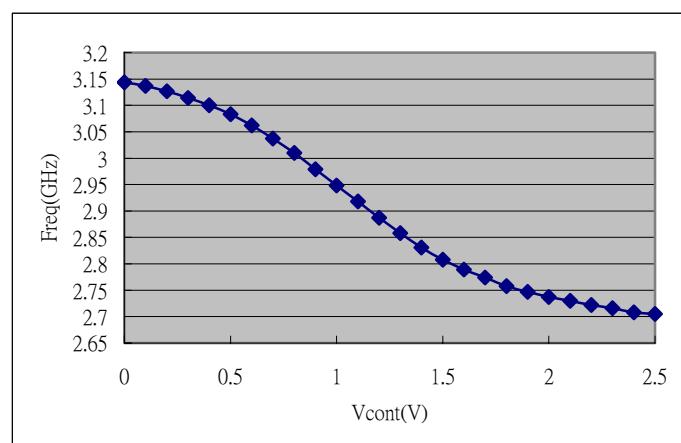

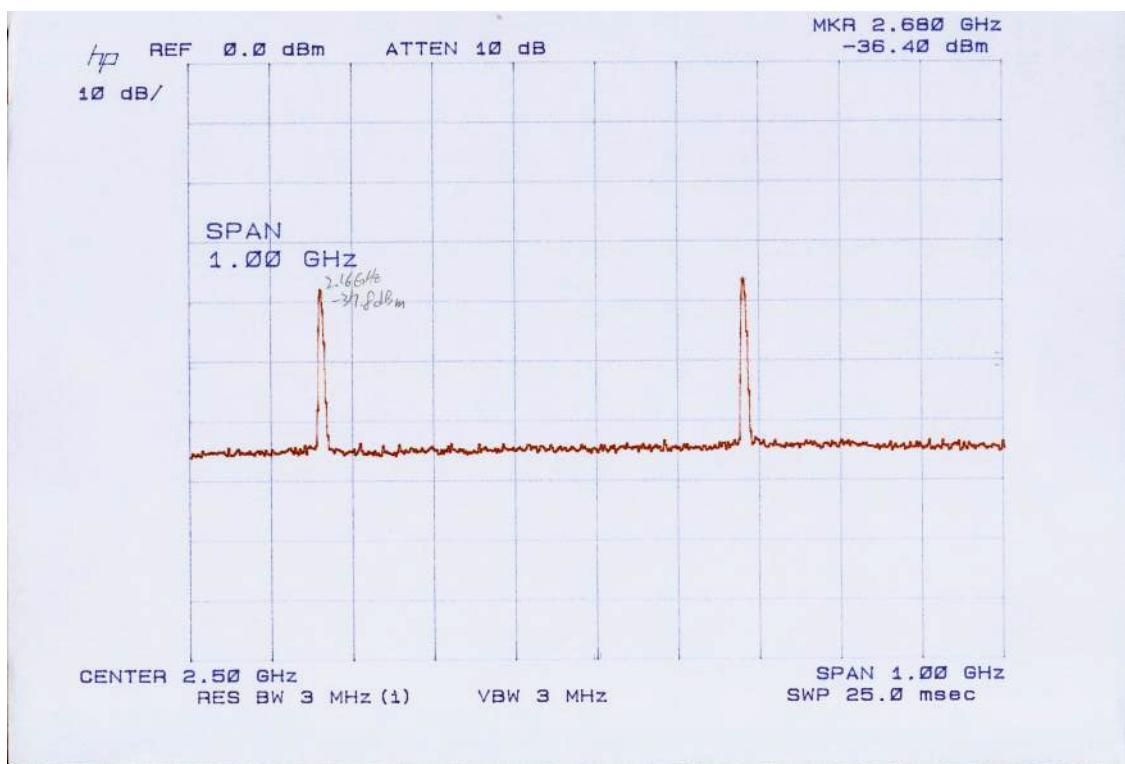

經過量測後，我們發現此振盪器居然會有兩個頻段的振盪頻率，一個約在 2.2GHz 附近，另一個約在 2.8GHz 附近。圖 4.11 為振盪器在 2.2GHz 頻段所量測到的可調頻率，約從 2.097GHz 到 2.315GHz，線性區增益為  $-167\text{MHz/V}$ 。最大的輸出功率為  $-9.5\text{dBm}$  如圖 4.12。圖 4.13 為在調整輸出頻率把各點的最大功率紀錄下來。會有這麼大的變異是因為我們的輸出匹配網路是窄頻的，因此會隨著遠離匹配網路的中心頻率作衰減。圖 4.14 為振盪器在 2.8GHz 頻段所量測到的可調

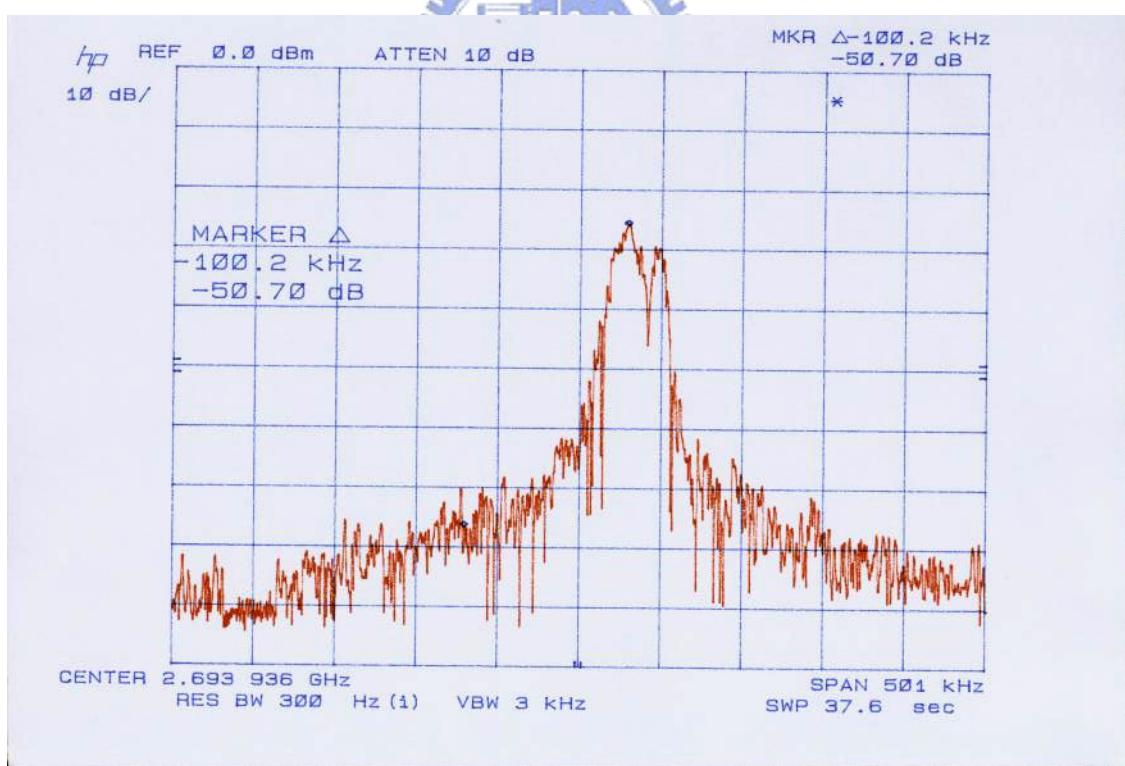

頻率，約從 2.705GHz 到 3.144GHz，線性區增益為  $-300\text{MHz/V}$ 。這兩個頻段有一個晶片只會振在 2.2GHz 的頻段，其它有些晶片有時候是開機後振在 2.2GHz，而過一陣子重開機後振在 2.8GHz。在其中幾個晶片更可以發現在某一個偏壓電壓以下是振在 2.2GHz，某一個偏壓電壓以上是振在 2.8GHz，而在兩個電壓之間會發現，兩個訊號都存在。如圖 4.15 所示，一根在 2.166GHz，一根在 2.68GHz。相位雜訊我們使用頻譜分析儀量測，如圖 4.16 所示。圖中量測雖然 offset frequency 在 100KHz 為  $-50.7\text{dBc}$ ，但因為 Resolution Bandwidth 為 300Hz，所以真正的相位雜訊為  $-50.7 - 10\log 300 = -75.47\text{dBc/Hz}$ 。在四個輸出振幅，我們發現都不太相同，有的甚至可以差到 3dBm。

圖 4.11 振盪器在 2.2GHz 頻段的可調頻率範圍

圖 4.12 振盪器最大輸出功率-9.3dBm

圖 4.13 振盪器在 2.2GHz 頻段輸出功率與輸出頻率關係圖

圖 4.14 振盪器在 2.8GHz 頻段的可調頻率範圍

圖 4.15 雙頻振盪現象

圖 4.16 相位雜訊量測

我們輸出的相位誤差利用圖 4.10 的概念，在振盪器輸出頻率為 2.129GHz，

輸出功率分別為-12.8dBm 和-10.4dBm，而由訊號產生器輸出的頻率為 4.5GHz，經過正交分合波器後功率為 2dBm。我們可以由頻譜分析儀看到差頻 2.37GHz 的功率為-39.2dBm，而和頻 6.63GHz 的功率為-54.9dBm，如圖 4.17。由 (4.1) 我們可以得到相位誤差約  $10.2^\circ$ 。

圖 4.17 四相位量測

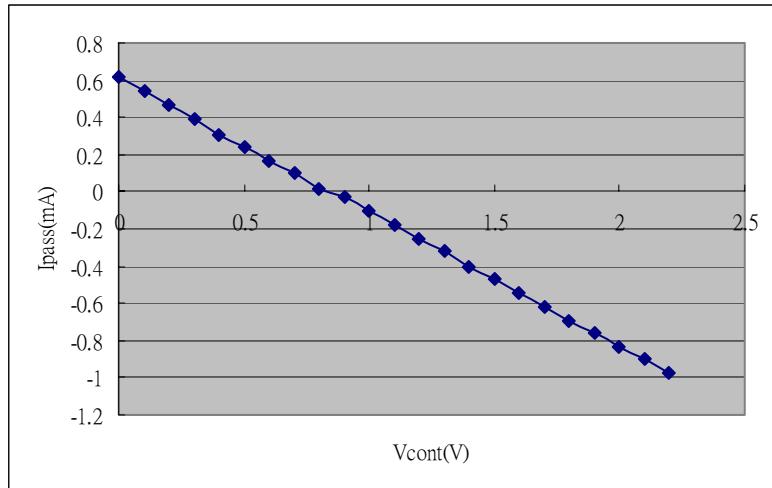

另外，我們在量測的時候發現，由電壓控制端會有電流流出，也就是說會有直流電流流經可變電容，理論上，這是不可能的事。我們量了幾顆後發現，有一顆晶片完全沒有漏電流，有的卻大到幾 mA，而且與電壓成正比，也就是電阻性。我們量測到最小的電阻約為  $338.5\Omega$ ，如圖 4.18 所示。

圖 4.18 可變電容漏電流

### 4.3 量測結果討論

從振盪器中心頻率的飄移，可見共振腔內的電容電感已不是模擬時的值。但是因為我們所用的電感為台積電本身提供的模型，所以誤差也不至於會太大。因此我們推斷額外的寄生電容比模擬時多出了約  $80\text{fF}$ 。這可能是來自於兩個原因，第一電晶體的模型不夠準確，第二是佈局時所沒有考慮到的寄生電容，而這些額外的寄生電容，來自於第二項的原因居多。於是我們多加了寄生電容後再重新模擬，可調頻率範圍如圖 4.19，與量測結果非常類似，至於相位雜訊經過加了寄生電容過後，也下降到在 offset frequency@100KHz 時，相位雜訊為  $-82.9\text{dBc/Hz}$ ，如圖 4.20。

圖 4.19 可調頻率範圍

圖 4.20 相位雜訊

在量測的時候，很驚奇地看到竟然會有兩個振盪頻帶。於是我們便重新模擬，在快接近無法振盪的小偏壓電流下，我們得到了如圖 4.21 的跳頻現象。我們可以發現在  $V_{cont}$  大於 0.9V 時，振盪器是振在 2.8GHz 的頻段，在頻率正要隨著控制電壓下降而上升時，忽然跳到 2.4GHz 的頻帶。這是在使用 ADS 的 Harmonic Balance 的模擬工具所做出來的。

圖 4.21 跳頻現象

若是執行暫態分析，可以發現不必在低偏壓電流時即可得到兩個頻帶的振盪結果。我們將刺激電流源放在共振腔的一端，此刺激電流源僅工作 0.1ns，之後便形成開路，如圖 4.22。當刺激電流源工作的時候為 10mA，會發現此振盪器振盪在 3GHz，如圖 4.23。當刺激電流源為 20mA 或以上，則振盪在 2.34GHz，如圖 4.24。我們可以發現除了振盪頻率不相同外，振幅與直流準位是相同的。

圖 4.22 外加刺激電流源

圖 4.23 振盪器暫態分析 (3GHz)

圖 4.24 振盪器暫態分析 (2.34GHz)

我們試過很多種交錯耦合的電容電感振盪器，如只用 NMOS、只用 PMOS、有四相位、無四相位。發現只要是使用電晶體互相交錯連接的四相位振盪器，在模擬時，只要偏壓電流很小，就會有這種跳頻現象，而其他型態的振盪器則不會。所以推論問題應該出在使振盪器產生四相位輸出的四顆互相交錯的電晶體上，因

為訊號需要穿過兩個電晶體才會回到原來核心振盪器的反向端，需要穿過下面四顆電晶體才會回到原來的節點。而且穿越這些電晶體時，有時電晶體皆在三極區，有時兩顆在三極區、兩顆在飽和區，振盪路徑很複雜，不易使用手算分析。

在可變電容的漏電流方面，第一，由於有詳細檢查過佈局圖，沒有把線路誤接的情況，且可變電容也正常工作；第二，由於此電流並不會隨著振盪頻率或電壓的不同而改變的趨勢有所變化，所以應該是電阻性的漏電流。並且不同晶片漏電流的情形不相同，也有完全沒有漏電流的情形發生。所以推論應該是由於製程的關係所造成的漏電流。

在輸出功率方面，四個輸出的功率會有所不同的原因應該是我們輸出級沒有做好匹配的關係，而當初沒有作匹配是為了整個佈局圖能夠對稱和輸出打線量測方便。因此若要改善，在佈局上需要重新仔細安排。在輸出相位方面，根據量測結果，有  $10.2^\circ$  的誤差。這角度誤差的來源，我們先由 (3.20) 可以得到

$$V_1 = \sqrt{\frac{g_{m2}}{g_{m1}}} V_2 \quad (4.2)$$

，如果  $g_{m1} = -g_{m2}$ ，則  $V_1$  與  $V_2$  相位為正交。如果  $g_{m1} \neq -g_{m2}$ ，且各有實部與虛部，則  $V_1$  與  $V_2$  相位便不會正交，相位誤差便由此產生。所以如果佈局和量測上，訊號所經過的電長度都是相等的話，那就是佈局上，四顆 NMOS 並沒有匹配好，使得  $g_{m1} \neq -g_{m2}$ ，以致於相位產生了誤差。所以與四個輸出功率要相同的問題一樣，我們必須將產生四相位的四顆電晶體在佈局上做好匹配，才能達到較準確的四相位。當然，在訊號所經過的路徑安排上，我們也要盡所能地做到相同。在相位偏

離  $90^\circ$  越少時，以此方法量測相位誤差將會因為實驗上操作的少許誤差而使量測的結果與實際的結果相差比例較大。所以如果有量測高頻的示波器，直接來測量，這樣對於小範圍誤差的量測才會比較準確。

| 規格             | 模擬結果              | 量測結果              |

|----------------|-------------------|-------------------|

| 電源供應電壓         | 2.5V              | 2.5V              |

| 消耗功率           | 48.41mW           | 39.5mW            |

| 輸出功率           | -5.29dBm          | -9.3dBm           |

| 可調頻率範圍         | 2.25GHz~2.68GHz   | 2.097GHz~2.315GHz |

| 各輸出波形相位差       | 90 度              | 100.2 度或 79.8 度   |

| Phase Noise    | -98.288dBc@100kHz | -75.47dBc@100kHz  |

| Ko(MHz/V)(線性區) | -417.5            | -167              |

表 4.1 壓控振盪器的模擬與量測比較

## 第五章 討論與結論

### 5.1 討論

如同我們所預期的，使用雙電荷峯浦的頻率合成器能有效減少低通濾波器中電容所佔的面積。並且此架構只移動整個開迴路響應裡的零點，對於極點影響不大，因此，我們可以將迴路頻寬縮得更小使電路鎖定時間加快且對高頻雜訊衰減的更多，而不必擔心相角邊限所造成穩定度的問題。由於電荷峯浦一直都有固定的功率消耗，所以增加一個電荷峯浦對於在要求低功率消耗的通訊系統來說，無疑是雪上加霜。因此，我們必須使電荷峯浦的充電放電電流儘可能的小，如此濾波器裡的電容也會縮小。另外，最好能使壓控振盪器的增益提高，也會幫助降低電荷峯浦的電流降低。但必須小心的是雖然整個迴路設計會符合我們的期望，在佈局時，若沒有謹慎安排，雜訊將會直接耦合到振盪器的電壓控制端上，小電容和高振盪器增益便會使此雜訊影響輸出甚重。在表 5.1，列出我們的設計和其他已發表的論文比較，由於頻率合成器在不同的規格，會有不同的表現，在此列出的比較皆在 2.4GHz 的頻段，且切換頻道間隔相似的設計。雖然我們的數據僅是模擬結果，但較同架構設計[6]穩定時間少了一半，也比其他設計的穩定時間短。

|      | 架構                                    | 濾波器                      | 參考頻率  | 穩定時間                  |

|------|---------------------------------------|--------------------------|-------|-----------------------|

| 本論文  | 3rd order, integer-N                  | Integrated discrete time | 2MHz  | $30\mu\text{s}^{(a)}$ |

| [6]  | 3rd order, integer-N                  | Integrated discrete time | 1MHz  | $60\mu\text{s}$       |

| [20] | 3rd order, integer-N                  | Off-chip continuous time | 1MHz  | $140\mu\text{s}$      |

| [21] | 3rd order, $\Delta\Sigma$ frational-N | Off-chip continuous time | 13MHz | $120\mu\text{s}$      |

| [22] | 3rd order, integer-N                  | Off-chip continuous time | 1MHz  | $120\mu\text{s}$      |

(a)模擬結果

表 5.1 頻率合成器穩定時間比較

在壓控振盪器上，我們將產生負電阻的電晶體與產生四相位的電晶體串疊，使其共用電流減少功率消耗，並且使其輸出訊號因上升和下降均有電晶體幫助而使波形更加對稱，使相位雜訊降低。為了提升共振腔的品質參數，我們將 MIM 電容與可變電容並聯，雖然提升了相位雜訊的表現卻也減少了振盪器的可調頻率範圍和增益。我們最後模擬的壓控振盪器其相位雜訊在 offset frequency@100KHz 為 $-103.56\text{dBc}$ ，在使用由台積電所提供的品質因子不高的方形螺旋電感，我們已在結構上及電晶體上作了調整，使其達到較好的相位雜訊。但實際上量測出來的結果並沒有模擬中的好，可見我們在佈局的技巧上還要多多加強，將電路中各元件仔細做好匹配，並降低繞線時所產生寄生電阻、電容、電感的效應，才能使實作出來的晶片與模擬結果相近。

## 5.2 結論

在這一篇論文中，我們使用台積電  $0.25\mu\text{m}$  CMOS 製程設計一個有四相位輸出的頻率合成器，其操作電壓為  $2.5\text{V}$ ，參考訊號為  $10\text{MHz}$ ，可輸出頻率為從  $2.4\text{GHz}$  到  $2.526\text{GHz}$ ，每  $10\text{MHz}$  為一個間隔，共為 64 個頻率，輸出功率大小為  $-6\text{dBm}$ 。

對 IEEE802.11b 的規格來說，我們從最小的頻道 (2.412GHz) 切換到最大的頻道 (2.472GHz)，其所需要的穩定時間為  $30\mu\text{s}$ ，比 IEEE 所定的規格  $224\mu\text{s}$  低很多，也較同樣架構設計[6]的穩定時間  $60\mu\text{s}$  短。整個系統共消耗功率約 53.76mW，其中振盪器包含輸入及輸出的緩衝電路消耗功率約 50mW，除頻器耗約 2.76mW，電荷倉浦耗約 0.75mW，其他電路耗約 0.25mW。

第一次下線的振盪器其工作電壓為 2.5V，模擬結果輸出頻率從 2.25GHz 到 2.68GHz，中心頻率為 2.465GHz，增益約為  $-450\text{MHz/V}$ ，輸出功率最大可到  $-5.29\text{dBm}$ ，四個輸出彼此間隔  $90^\circ$ ，而總消耗功率為 48.41mW。其相位雜訊在 offset frequency 為 100KHz 時為  $-98.28\text{dBc/Hz}$ 。晶片的量測結果消耗功率為 39.5mW，從 2.097GHz 到 2.315GHz，線性區增益為  $-167\text{MHz/V}$ ，最大的輸出功率為  $-9.3\text{dBm}$ ，相位雜訊 offset frequency 為 100KHz 時為  $-75.47\text{dBc/Hz}$ ，相位誤差為  $10.2^\circ$ 。

未來的工作首先建議設計一個高品質參數對稱的電感，因為如果電感不是對稱形式，為了降低相位雜訊，我們每一個共振腔就必須擺兩個電感，以維持共振腔的對稱性。又方形的電感其品質參數較差，所以若能設計一個圓形的電感，那品質參數便會提升，相位雜訊也會降低。

在振盪器的設計上，必須把偏壓電路設計在內部，並把偏壓電流加大，使振盪器操作在電壓限制與電流限制的邊緣，如此可取得最佳的功率與相位雜訊比。此外，也能避免振盪器振盪在另外一個頻帶。進一步，可以研究振盪器振在這兩

個頻帶與產生四相位的四顆電晶體的關係。佈局的安排也要仔細規劃，使輸出的緩衝級也能做好匹配使四個相位的輸出功率能夠相同。另外輸出功率對頻率會有變化，如果在 SOC 上，當頻率合成器與混波器作在同一顆晶片上，我們可以不擔心這個問題。如果不是，我們可以加上迴授，來控制輸出功率能維持在某一個值附近。

在頻率合成器方面，可以將相位頻率偵測器改善，使其從偵測到 UP 和 DN 都為 1 時，迴授使其皆為 0 這過程的延遲時間減少，可以使用更先進的製程或著重新設計架構使經過的閘個數減少。如此，可把輸出頻率兩旁的突波降低更多。

## 參考資料

[1] J. Craninckx and M. Steyaert, “A fully integrated CMOS DCS-1800 frequency synthesizer,” IEEE J. Solid-State Circuits, vol. 33, pp.2054-2065, Dec. 1998.

[2] C. S. Vaucher, “An adaptive PLL tuning system architecture combining high spectral purity and fast settling time,” IEEE J. Solid-State Circuits, vol. 35, pp.490-502, April 2000.

[3] B. De Mauer and M. S. J. Steyaert, “A CMOS monolithic  $\Sigma\Delta$ -controlled fractional-N frequency synthesizer for DCS-1800,” IEEE J. Solid-State Circuits, vol. 37, pp.835-844, July 2000.

[4] W. S. T. Yan and H. C. Luong, “A 2-V 900-MHz Monolithic CMOS Dual-Loop Frequency Synthesizer for GSM Receivers,” IEEE J. Solid-State Circuits, vol. 36, pp.204-216, Feb. 2001.

[5] D. H. Wolaver, Phase-Locked Loop Circuit Design, Prentice Hall, 1991.

[6] T. C. Lee, B. Razavi, “A Stabilization Technique for Phase-Locked Frequency Synthesizers,” IEEE J. Solid-State Circuits, vol. 38, pp. 888-894, June 2003.

[7] A. S. Sedra, K. C. Smith, Microelectronic Circuits, 4<sup>th</sup> ed., Oxford University Press, Inc., 1998.

[8] D. B. Leeson, “A simple model of feedback oscillator noise spectrum,” Proc. IEEE, vol. 66, pp.329-330, Feb. 1966.

[9] A. Hajimiri and T. Lee, “A general theory of phase noise in electrical oscillators,” IEEE J. Solid-State Circuits, vol. 33, pp.179-194, Feb. 1998.

[10] D. Ham, A. Hajimiri, “Concepts and Methods in Optimization of Integrated LC VCOs,” IEEE J. Solid-State Circuits, vol. 36, pp.896-909, June 2001.

[11] B. Razavi, RF Microelectronics, Prentice Hall, 1998.

[12] B. Razavi, Design of Integrated Circuits for Optical Communications, McGraw-Hill, 2003.

[13] Y. Tsividis, Operation and Modeling of the MOS Transistor, 2<sup>nd</sup> ed., McGraw-Hill, 1999.

[14] G. Gonzales, Microwave Transistor Amplifiers Analysis and Design, 2<sup>nd</sup> ed., Prentice Hall, 1997.

[15] P. Andreani, H. Sjöland, “Tail Current Noise Suppression in RF CMOS VCOs,” IEEE J. Solid-State Circuits, vol. 37, pp.342-348, March 2002.

[16] B. Chi and B. Shi, “Integrated 2.4 GHz CMOS quadrature VCO with symmetrical spiral inductors and differential varactors” IEEE MTT-S Digest, pp. 561-564, 2002.

[17] J. Lu, L. Tian, “Design techniques of CMOS SCL circuits for Gb/s applications,” ASIC, 2001. Proceedings. 4th International Conference, pp.559-562, Oct. 2001.

[18] A. Blanchard, Phase-Locked Loops, Krieger Publishing Company, 1976.

[19] R. E. Best, Phase-Locked Loops, 4<sup>th</sup> ed., McGraw-Hill, 1999.

[20] A. Ajjikuttira et al., “A fully integrated CMOS RFIC for Bluetooth applications,” IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp. 198–199, Feb. 2001.

[21] N. Filiol et al., “A 22 mW bluetooth RF transceiver with direct RF modulation and on-chip if filtering,” ISSCC Digest of Technical Papers, pp. 202–203, Feb. 2001.

[22] H. Komurasaki et al., “A single-chip 2.4-GHz RF transceiver LSI with a wide-range FV conversion demodulator,” IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp. 206–207, Feb. 2001.