國立交通大學

電機學院 電信學程

碩士論文

內建測試機制的衛星定位接收機前端電路設計

Front End Design With Built In Test Mode for GPS Receiver

研究 生：沈金發

指 導 教 授：高曜煌 博 士

中 華 民 國 九 十 六 年 七 月

內建測試機制的衛星定位接收機前端電路設計

# Front End Design With Built In Test Mode for GPS Receiver

研究 生：沈金發

Student : Chin-Fa Shen

指 導 教 授：高曜煌

Advisor : Prof. Yao-Huang Kao

A Thesis

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Communication Engineering

July 2007

Hsinchu, Taiwan, Republic of China

中華民國九十六年七月

# 內建測試機制的衛星定位接收機前端電路設計

學生：沈金發

指導教授：高曜煌教授

國立交通大學電機學院 電信學程（研究所）碩士班

## 中 文 摘 要

本論文研製之內建測試機制的衛星定位接收機前端電路設計是在敘述如何快速、輕鬆的設計 **RF IC**(Radio frequency integrator circuit)<sup>[1]</sup>。快速、輕鬆的設計 **RF IC**，一直是 **RF IC** 設計者期望的工作環境。但是設計 **RF IC** 傳統上就是很艱困、繁瑣的工作，因此想要輕鬆的設計 **RF IC** 就必須把設計的困難度降低才行，(不過規格是不能放寬的)。因此我們想：若設計出許多規格，然後再從中挑選一個那不就達到目的了嗎？當然要實現這個想法，也要有方法才不會弄巧成拙。因此本文在此推薦了一個 **RF IC** 的設計方法，讓 **RF IC** 設計者，能夠快速且輕鬆的設計 **RF IC**。在此我們藉製作 **GPS Receiver**(Global Positioning System) <sup>[2]</sup>來說明此 **RF IC** 的設計方法。

首先在設計 VCO 時我們內建了數個頻率範圍切換裝置，來克服頻率的不準度。並降低了 KVCO 之值，換句話說我們除了克服頻率的不準度外亦兼具改善了相當程度的電源引起之相位雜訊。

我們更在 **RF IC** 內部的 VCO(Voltage control oscillator)，內建了一組輸出電路，使得 VCO 的輸出，能夠被獨立的量測，因此之故它的性能亦可以單獨的被評估。舉一個例子來說，我們可以來評估它的輸出振幅大小和相位雜訊等等-----。

接著，我們在設計 Crystal OSC 時內建了偏壓電流選擇機制，來權衡耗電流和起振與否的問題。故此電流選擇機制，讓我們可以擁有更大的設計誤差，當然設計速度也提升了。

在設計 Front end 時我們亦特地在 LNA 及 MIXER 之內加了電流選擇裝置，使得 LNA 及 MIXER 的偏壓可以被手動改變。同樣的，有了這個電流選擇裝置後，我們將不再被規格綁緊了。換句話說，設計的困難度降低了。

本文使用了台灣積體電路公司(TSMC)的 CMOS 0.25um 製程，來設計並製造這顆“**內建測試機制的衛星定位接收機**”。目前此晶片已量測完成，量測結果是：**RF IC** 感度 = -94dBm@(S+N)/N=20dB。它的電源電壓為 3.0V，耗電流為 50mA。建立此設計方法之後，接著我們未來將以減少耗電流及提升感度為職志。

# **Front End Design With Built In Test Mode for GPS Receiver**

Student : Chin-Fa Shen

Advisors : Dr. Yao-Huang Kao

Degree Program of Electrical and Computer Engineering

National Chiao Tung University

## **ABSTRACT**

A procedure is easy to design RF IC. RF IC designer wish own environment. But tradition design method is very difficult. At this paper we recommend a method to more easy design RF IC which for RF IC designer, for above reason. We building the GPS Receiver RF IC to present this recommend method.

First, we build the frequency selector in VCO for Local Oscillator. So we have larger frequency range to overcome the IC device non-ideal and improve the phase noise from power supply induce.

Next, we build the Output port for VCO. Then our VCO can be measurement for power level and frequency and phase noise.

Third, we build in the current bias selector for crystal oscillator. Therefore, we can tread-off between current consumption and oscillation start time.

Fourth, we build in the current bias selector for LNA and MIXER. Similar above we can tread-off current consumption and performance for LNA 、 MIXER (we call :FRONT-END).

We have the above some mechanism then RF IC design become not difficult. There are we recommend RF IC design method by make GPS Receiver RF IC.

We use 0.25um CMOS process of TSMC Corporation to design and make this GPS receiver RF IC. This RF IC power supply =3.0V, current consumption about 40 mA and it receiver sensitivity =-94dBm@(S+N)/N=20dB. After set up this method, we will do the reduce consumption current and improve the receiver sensitivity.

## 誌謝

經過 1/4 世紀的半工半讀，終於有機會完成我的第一篇論文。這一路走來要感謝無數曾經幫助過我的人，若沒有大家的鼓勵與幫忙，我應該是沒有機會撰寫這篇論文的。

首先，要感謝我的指導教授高曜煌老師，他不但願意收我這個大字不識幾個的工人爲徒，並且還願意巨細靡遺的教導我待人處事的態度和研究學問的方法，使我可以慢慢的有所長進。後來因爲工廠的長官知道我的老師是高曜煌教授，所以我被公司革職、遣散的情況也減少了，工作也漸漸變得比較順利及穩定。因此家裡的生活情況也改善許多，我也終於獲得了喘息的機會！

更要謝謝我的老朋友和祥，他不但在 IC 電路的模型方面給予我很多的幫助，解決了很多模型方面的問題，使得電路的模擬問題得以迎刃而解。更教我建立模擬電路的電腦系統，讓我的 IC 設計更上一層樓。我的弟弟清祥也在系統的製作與測試方面，給予我莫大的協助，使得此論文的許多測試數據得以出爐。

# 目 錄

## Front End Design With Built In Test Mode for GPS

|                                               |    |

|-----------------------------------------------|----|

| Receiver .....                                | 2  |

| 中 文 摘 要 .....                                 | 3  |

| ABSTRACT .....                                | 4  |

| 目 錄 .....                                     | 6  |

| 符號說明 .....                                    | 11 |

| 簡寫說明 .....                                    | 11 |

| 一、 緒 論 .....                                  | 12 |

| 1.1 GPS(Global Positioning System)的發展故事 ..... | 12 |

| 1.2 GPS的應用介紹 .....                            | 13 |

| 1.3 GPS 的接收功率簡介 .....                         | 14 |

| 1.4 GPS 參數簡介 .....                            | 14 |

| 1.5 研究動機 .....                                | 15 |

| 1.5.1 典型的RF IC 設計方式 .....                     | 15 |

| 1.5.2 推薦的RF IC 設計方式 .....                     | 16 |

| 二、 研究內容與方法 .....                              | 18 |

| 2.1 GPS Receiver RF IC及系統的研究內容 .....          | 18 |

| 2.1.1 GPS的整組參考成品及應用軟體的來源 .....                | 18 |

| 2.1.2 GPS成品製作內容 .....                         | 18 |

|                                                |           |

|------------------------------------------------|-----------|

| 2.1.3 RF IC的規格來源及內容 .....                      | 18        |

| <b>2.2 研究方法 .....</b>                          | <b>19</b> |

| 2.2.1 推薦的 RF IC之系統設計 .....                     | 20        |

| 2.2.2 系統的驗證方法 .....                            | 23        |

| <b>三、理論 .....</b>                              | <b>24</b> |

| <b>3.1 本地振盪電路 .....</b>                        | <b>24</b> |

| 3.1.1 本地振盪電路的規格 .....                          | 24        |

| 3.1.2 典型的本地振盪結構 .....                          | 24        |

| 3.1.3 推薦的本地振盪結構之一：為VCO加上八個頻帶 .....             | 25        |

| 3.1.4 推薦的本地振盪結構之二：為VCO加上輸出電路 .....             | 27        |

| 3.1.5 推薦的本地振盪電路 .....                          | 28        |

| 3.1.6 推薦的本地振盪電路模擬結果 .....                      | 33        |

| 3.1.7 此電路設計心得 .....                            | 36        |

| <b>3.2 石英晶體振盪電路<sup>[108] [18]</sup> .....</b> | <b>37</b> |

| 3.2.1 石英晶體振盪電路的規格 .....                        | 37        |

| 3.2.2 典型的石英晶體振盪電路 .....                        | 38        |

| 3.2.3 推薦的石英晶體振盪電路：為振盪電路加上電流選擇機制 .....          | 39        |

| 3.2.4 模擬結果 .....                               | 42        |

| 3.2.5 此電路設計註解 .....                            | 43        |

| <b>3.3 前端電路(即LNA+MIXER).....</b>               | <b>44</b> |

| 3.3.1 前端電路的規格 .....                            | 44        |

| 3.3.2 典型的前端電路 .....                            | 44        |

| 3.3.3 推薦的前端電路 .....                            | 45        |

| 3.3.4 前端電路(LNA+MIXER)的模擬結果 .....               | 53        |

|                                                  |           |

|--------------------------------------------------|-----------|

| <b>3.4 佈線圖 .....</b>                             | <b>54</b> |

| <b>四、 實 驗 部 分 .....</b>                          | <b>55</b> |

| <b>4.1 本地振盪電路的量測 .....</b>                       | <b>55</b> |

| 4.1.1 實驗的量測配置圖及量測結果 .....                        | 55        |

| <b>4.2 石英晶體振盪電路量測 .....</b>                      | <b>58</b> |

| 4.2.1 石英晶體振盪電路的量測配置及量測圖形 .....                   | 58        |

| <b>4.3Front End實驗結果 .....</b>                    | <b>62</b> |

| 4.3.1 前端電路的增益量測 .....                            | 63        |

| 4.3.2 前端電路的NF(雜信指數)量測 .....                      | 64        |

| 4.3.3 使用頻譜分析儀來量測P1dB .....                       | 67        |

| 4.3.4 使用頻譜分析儀來量測感度 .....                         | 68        |

| 4.3.5 RFIC量測設定照片 .....                           | 71        |

| <b>4.4 戶外衛星實收測試 .....</b>                        | <b>75</b> |

| 4.4.1 衛星實際接收測試 .....                             | 76        |

| 4.4.2 衛星接收模組 .....                               | 78        |

| <b>五、 結 論 .....</b>                              | <b>79</b> |

| <b>六、 REFERENCES PAPER .....</b>                 | <b>80</b> |

| <b>七、 REFERENCES PRODUC AND DATA SHEET .....</b> | <b>82</b> |

| <b>八、 研究生簡介 .....</b>                            | <b>83</b> |

| <b>九、 自 傳 .....</b>                              | <b>84</b> |

## 圖目錄

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| (圖 1.3.1) GPS 在地面上所收到的信號強度 .....                                      | 14 |

| (圖 1.5.1) 傳統的RF IC功能示意圖.....                                          | 15 |

| (圖 1.5.2) 推薦的RF IC功能示意圖.....                                          | 16 |

| (圖 3.1.2) 典型的本地振盪功能方塊圖 .....                                          | 24 |

| (圖 3.1.3)推薦的本地振盪功能方塊及控制圖 .....                                        | 25 |

| (圖 3.1.3-1) 本地振盪頻帶分配圖 .....                                           | 26 |

| (圖 3.1.4) 為LO OSC加上輸出及電路.....                                         | 27 |

| (圖 3.1.5-1) VCO電路.....                                                | 28 |

| (圖 3.1.5-3) Buffer3 電路 .....                                          | 30 |

| (圖 3.1.5-4) Buffer2 電路 .....                                          | 31 |

| (圖 3.1.6) SK1110B5 Frequency vs. tune voltage simulation result ..... | 34 |

| (圖 3.1.6-1) 推薦的本地振盪器在時域上之模擬結果 .....                                   | 34 |

| (圖 3.1.6-2) 推薦的本地振盪器在頻域上之模擬結果 .....                                   | 35 |

| (圖 3.1.6-3) 推薦的本地振盪器其相位雜訊之模擬結果曲線圖 .....                               | 35 |

| (圖 3.2.2) 典型的石英晶體振盪器方塊及控制圖 .....                                      | 38 |

| (圖 3.2.3-1) 推薦的石英晶體振盪器方塊及控制圖 .....                                    | 39 |

| (圖 3.2.3-2) 推薦的石英晶體振盪器電路圖 .....                                       | 40 |

| (圖 3.2.3-3) 推薦的石英晶體振盪器電路圖---電流選擇機制 .....                              | 41 |

| (圖 3.2.4 及圖 3.2.4-1) 石英晶體振盪電路的數位化後輸出和類比輸出之模擬結果 .....                  | 42 |

| (圖 3.3.2) 典型的前端電路方塊及控制圖 .....                                         | 44 |

| (圖 3.3.3-1) 推薦的前端電路方塊及控制圖 .....                                       | 45 |

| (圖 3.3.3-4) LNA Core circuit .....                                    | 46 |

| (圖 3.3.3-5) LNA Gain simulation result .....                          | 47 |

| (圖 3.3.3-6) LNA Noise simulation result.....                          | 47 |

| (圖 3.3.3-2) 推薦的前端電路---LNA的電流選擇機制.....                                 | 48 |

| (圖 3.3.3-7) MIXER Core circuit .....                                  | 49 |

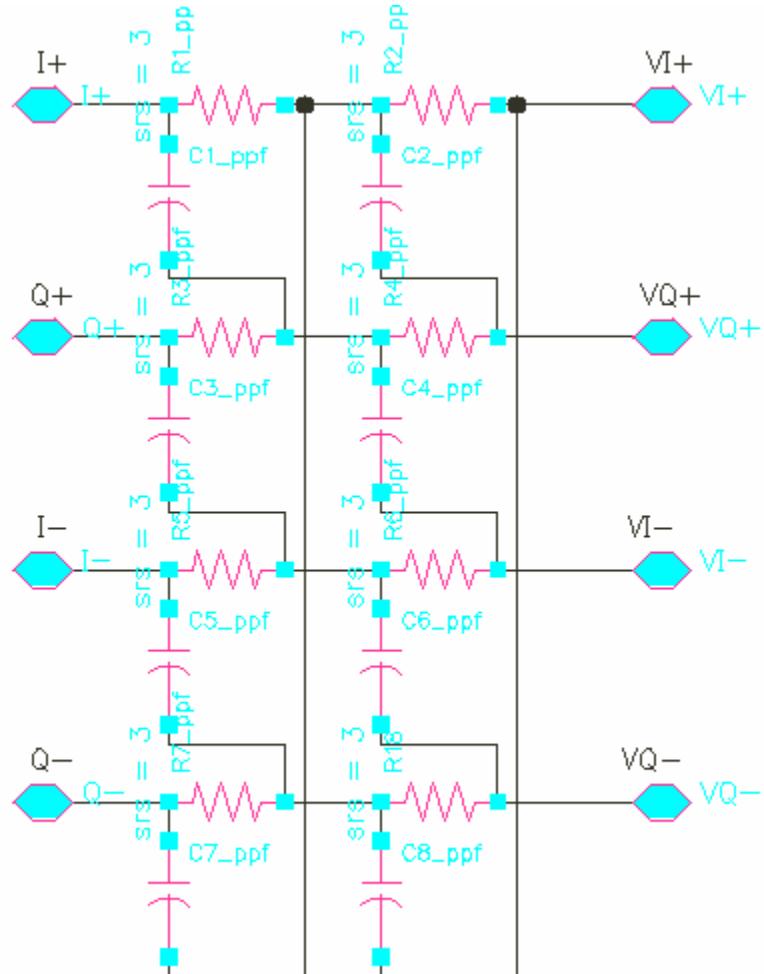

| (圖 3.3.3-6) Poly phase shifter Core circuit .....                     | 51 |

| (圖 3.3.3-3) 推薦的前端電路---Buffer of Mixer的電流選擇機制.....                     | 53 |

| (圖 3.4)RF IC的佈線圖.....                                                 | 54 |

| (圖 4.1.1) 本地振盪電路的量測配置圖 .....                                          | 55 |

| (圖 4.1.1-1) 推薦的本地振盪器其相位雜訊在 100KHz處之量測結果曲線圖 .....                      | 56 |

| (圖 4.2.1) 石英晶體振盪電路的量測配置圖 .....                                        | 58 |

| (圖 4.2.1-1) 石英晶體振盪電路的起振時間之量測結果-----約 0.7mS.....                       | 59 |

| (圖 4.3.1) 前端電路的增益量測之接線圖 .....                                         | 63 |

| (圖 4.3.2-1) 前端電路的NF量測之儀器校正畫面 .....                                    | 65 |

| (圖 4.3.3) 量測P1dB的儀器配置圖.....                                           | 67 |

|                                                   |    |

|---------------------------------------------------|----|

| (圖 4.3.4) 前端電路的感度量測之接線圖 .....                     | 68 |

| (圖 4.3.4-1) 感度量測前之儀器確認：信號雜信比(S+N/N)量測前的確認畫面 ..... | 69 |

| (圖 4.3.4-2) 信號雜信比(S+N/N)的量測畫面 .....               | 70 |

| (圖 4.3.5-1) RF IC 與週邊元件實體圖 .....                  | 71 |

| (圖 4.3.5-2) 用測試治具固定住的P.C.B.....                   | 72 |

| (圖 4.3.5-3) 我們的測試設備組合 .....                       | 73 |

| (圖 4.3.5-4) 待測試模組的接線圖 .....                       | 74 |

| (圖 4.4) GPS System block diagram .....            | 75 |

| (圖 4.4.1-1) 使用我們自己建立的RF IC在「工業東七路」的定位情形 .....     | 76 |

| (圖 4.4.1-2) 使用我們自己建立的RF IC在「新竹市埔頂路」的定位情形 .....    | 77 |

| (圖 4.4.2-1) GPS 模組分解圖.....                        | 78 |

| (圖 4.4.2-2) GPS 模組組合圖.....                        | 78 |

## 表目錄

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| (表 1.4) GPS參數表 .....                                                    | 14 |

| (表 2.2.1) Sige Semiconductor公司出品的RF IC-SE4100 的設計規格 .....               | 20 |

| (表 2.2.2) Link budget chare for <b>GPS RF IC</b> .....                  | 22 |

| 在Front-end中三個主要規格都與前面的計算符合。 .....                                       | 22 |

| (表 2.2.5) 參考Sige Semiconductor公司出品的RF IC-SE4100 所建立之前端電路的設計規格 .....     | 22 |

| (表 2.2.3) 參考Sige Semiconductor公司出品的RF IC-SE4100 所建立之本地振盪電路的設計規格 .....   | 23 |

| (表 2.2.4) 參考Sige Semiconductor公司出品的RF IC-SE4100 所建立之石英晶體振盪電路的設計規格 ..... | 23 |

| 表(3.1.1)本地振盪電路的設計規格 .....                                               | 24 |

| (表 3.1.6) SK1110B5 Frequency vs. tune voltage simulation result.....    | 33 |

| (表 3.1.6-1)Phase noise simulation result table .....                    | 36 |

| (表 3.1.6-2)本地振盪電路的模擬結果整理表 .....                                         | 36 |

| (表 3.2.1) 石英晶體振盪電路的設計規格 .....                                           | 37 |

| (表 3.2.4) 石英晶體振盪電路的DC總消耗電流模擬結果 .....                                    | 42 |

| (表 3.2.4-1) 石英晶體振盪電路的AC模擬結果.....                                        | 43 |

| (表 3.3.1) 前端電路的設計規格 .....                                               | 44 |

| (表 4.1.1-2) Frequency test result .....                                 | 57 |

| (表 4.3)Front End 的量測匯整表 .....                                           | 62 |

## 符號說明

|          |                             |

|----------|-----------------------------|

| G        | : $1 \times 10^9$           |

| M        | : $1 \times 10^6$           |

| K        | : $1 \times 10^3$           |

| m        | : $1 \times 10^{-3}$        |

| $\mu$    | : $1 \times 10^{-6}$        |

| n        | : $1 \times 10^{-9}$        |

| p        | : $1 \times 10^{-12}$       |

| F        | : Unit of capacitor         |

| V        | : Unit of voltage           |

| A        | : Unit of current           |

| $\Omega$ | : Unit of resistor          |

| dB       | : Unit of Deci-bel.(強度指數單位) |

| (S+N)/N  | : Signal to noise ratio     |

## 簡寫說明

|       |                                       |

|-------|---------------------------------------|

| GPS   | : Global Positioning System.          |

| RF IC | : Radio frequency integrator circuit. |

| VCO   | : Voltage control oscillator.         |

| LNA   | : Low noise amplifier                 |

| MIXER | : For frequency conversion            |

| LPF   | : Low pass filter                     |

| PLL   | : Phase lock loop                     |

| PP    | : Poly phase                          |

| Sim   | : Simulation                          |

| P1dB  | : 1dB compression point               |

# 一、緒論

## 1.1 GPS(Global Positioning System)的發展故事

五千年黃帝運用指南針，把蚩尤打得落花流水，GPS 的遠祖---指南針開始展露光芒。約在二千年前指南針更隨著東西方的交流，傳遍世界各地。

最近，在 1985 年韓航客機，因導航系統偏差，而誤闖前蘇聯領空，導致遭攔截戰機擊落的悲劇，此後美國便積極建立與部署衛星定位網----GPS(亦稱數位指南針)開始起飛。經過十年的努力，GPS 系統正式佈建完成，美國總共發射了 24 枚定位用衛星，並平均配屬到 6 條軌道上，其中 21 枚立即投入定位用途的運作，另 3 枚為部分衛星失效時的接替備用，每枚衛星只需花 11 小時 58 分鐘即可繞行地球一周，如此的佈建可涵蓋地球 98% 的面積定位。

不過，GPS 畢竟屬軍方計畫的建設，軍方仍有顧慮，故在定位信號中摻入了部分干擾信號，以干擾其定位精準度，此被稱為 SA(Selective Availability 選擇性可用)。

摻入干擾信號的 GPS，提供給民間使用時其誤差距離最多可達 100 米，一直到 2000 年完全解除干擾後，誤差才縮減至 15~20 米。但是即便解除 SA，軍用、民用的精度依然不一樣。美國及其盟軍可用 P 碼，精度為 2 米，民間使用 C/A 碼(即前述的 15 ~20 米)，P 碼使用定位衛星上的 L1、L2 頻段，C/A 碼僅使用 L1 頻段。

雖然今日大家知道 GPS 是由衛星網所建立的定位系統，但事實上 GPS 只是美國方面的計畫稱呼，其他國家也各自有他們的衛星定位、導航的佈建計畫。例如前蘇聯於 1982 年就提出 GLONASS(Global Navigation Satellite System)計畫，預計在 3 個軌道上部署 8 枚衛星。中國大陸方面亦有「北斗導航系統」計劃。但是目前最普及且確定用戶端可免費接收定位服務的仍是 GPS，其他系統則有些問題及困難待克服。如前蘇聯的 GLONASS 計畫，更是在共產解體後，而無力持續發射替用衛星，使得這個系統無法持續涵蓋全球。而中國大陸的「北斗導航」計劃還處於研發階段，尚未建置完成。

從這個故事中，我們可以預見將來 GPS 必成為生活中重要的工具，舉一個例子：

說不定將來以 GPS 為基礎的時鐘、手錶即將取代現在的石英式時鐘、手錶，就像機械表被淘汰的如出一側。當然 GPS 式的時鐘其最大的優點是「時間與發射台同步」。下一節將介紹一些 GPS 可能的應用。[13]

## 1.2 GPS的應用介紹

- 緣起

在六十年代中期，美國空軍及海軍為了軍事上導航和定位方面的需要各自研擬了定位計劃。於 1973 年時，美國國防部整合這兩項計劃，並且將它擴大應用於民事的定位測量上，而發展成現今之

全球定位系統 **GPS(Global Positioning System)**。

- 高性能的 GPS 其能力在：

平面精度可達 0.4m，高低精度可達 1.5m。

- GPS 可以做成各種不同的應用，例如：

軍事用途：飛彈，精靈炸彈，地面部隊的優化——美國精銳部隊-沙漠雄獅，船艦戰機的優化。

民生用途：汽車防盜，車輛派遣，行車記錄，登山，透過 E911-3G-可做成 indoor GPS 船隻、汽車、飛機等的衛星導航。

測量用途：大地面積，地層下陷。

科學用途：地殼變動，對流層水氣含量，電離層全電子含量

下列文章中我們將開始敘述 GPS 的射頻積體電路，並期待將來的人們更方便、迅速的實現以上的各種應用。[14]

### 1.3 GPS 的接收功率簡介

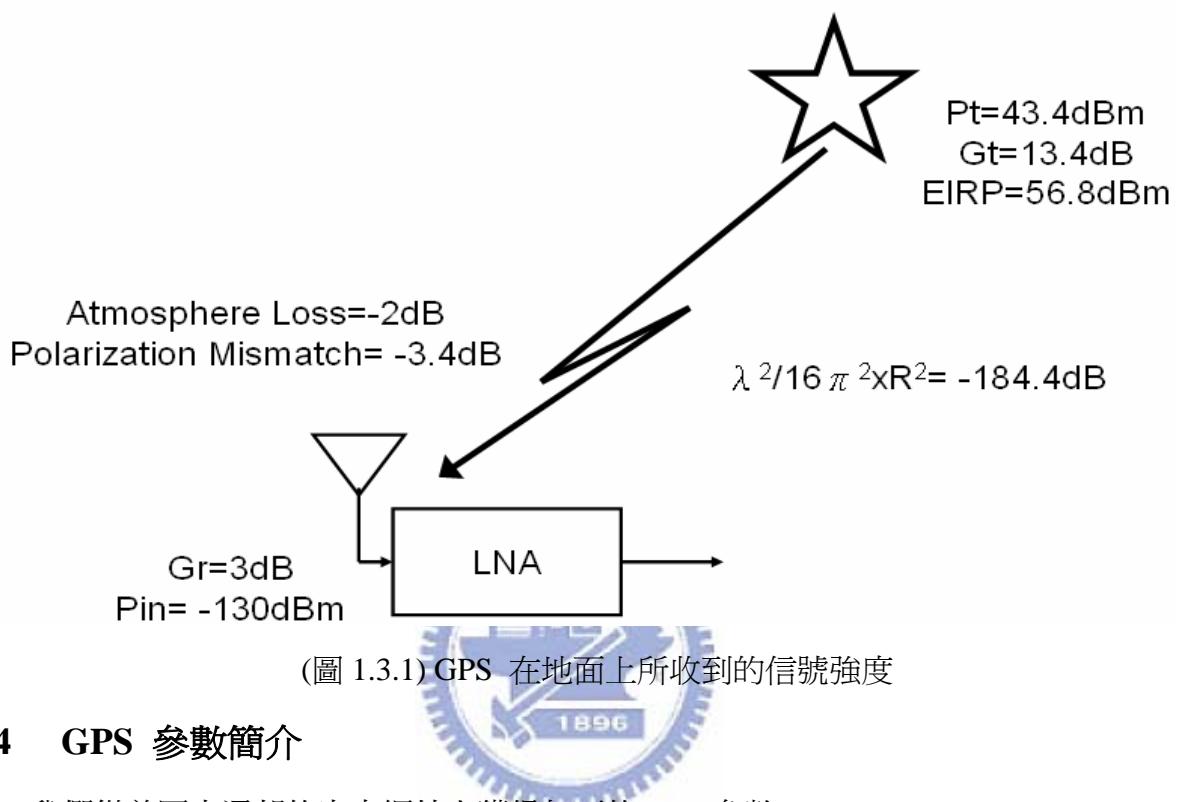

查閱資料得知衛星與地面的載波信號強度如下圖所示，並知 GPS 需能接收-130dBm 以下的載波信號。[15]

### 1.4 GPS 參數簡介

我們從美國交通部的官方網站上獲得如下的 GPS 參數。[110]

| Item                                           | Number  | Unit |

|------------------------------------------------|---------|------|

| 衛星與地面的距離                                       | 20180   | Km   |

| RF Frequency                                   | 1575.42 | MHz  |

| Satellite Transmitter Power                    | 21.9    | W    |

| EIRP                                           | 56.8    | dBm  |

| Polarization Mismatch<br>(Right Hand Circular) | - 3.4   | dB   |

| Propagation Loss in Space                      | - 184.4 | dB   |

| Loss in Atmosphere                             | - 2     | dB   |

| Receiver Power                                 | -130    | dBm  |

| Signal Bandwidth                               | 2       | MHz  |

(表 1.4) GPS 參數表

## 1.5 研究動機

看了前面 GPS 的簡單介紹之後，我們知道 GPS 是一個能豐富未來生活的科技。剛好 GPS 裡面包含了我們的學習領域-----RF IC。而且 RF IC 在此系統中佔有舉足輕重的地位，所以我們就把重點放在 RF IC 的探討上，以下就是我們的探討報告。

### 1.5.1 典型的 RF IC 設計方式

典型的 RF IC 設計方式，是由單一的方塊各自完成後，再組裝成一個較大的功能方塊，最後再組成一個完整的 RF IC 如圖 1.5.1，包含 LNA、Mixer1……等[1]。雖然上述的設計方式，符合邏輯，但是有經驗的工程師知道，設計工作很少有這麼順利的情況！

(圖 1.5.1) 傳統的 RF IC 功能示意圖

在經驗上，我們常遇到的問題是：當我們把所有的功能方塊，組合在一起的時候，我們就無法對某些功能作測試了。且因為信號線沒有拉出來，故也不能灌信號進去(若信號線全拉出來，則 IC PIN 就太多了，我們知道這樣的方法對性能的影響甚鉅)。當然我們可以用裸晶測試，但裸晶測試需要使用-高頻電子顯微鏡測試設備 (RF Probe station)，且此設備不但價格高昂、操作起來更是耗時費力，還得在裸晶上，先預放測試點才能測試，非常不方便。

更致命的是：組合一些功能方塊之後，某些功能居然出了問題，且導致整個 IC 無法繼續驗證下去，使得整個工程團隊的努力付之一炬。福無雙至，禍不單行，惡夢並未因此打住，更糟的是這個 IC 的某些內部方塊，是在組合後才出問題的且又無法偵測，所以我們並未找到真正的原因。如果運氣不好，再加上經驗未成熟，則試做(Tape out)再多次也是枉然的！

### 1.5.2 推薦的 RF IC 設計方式

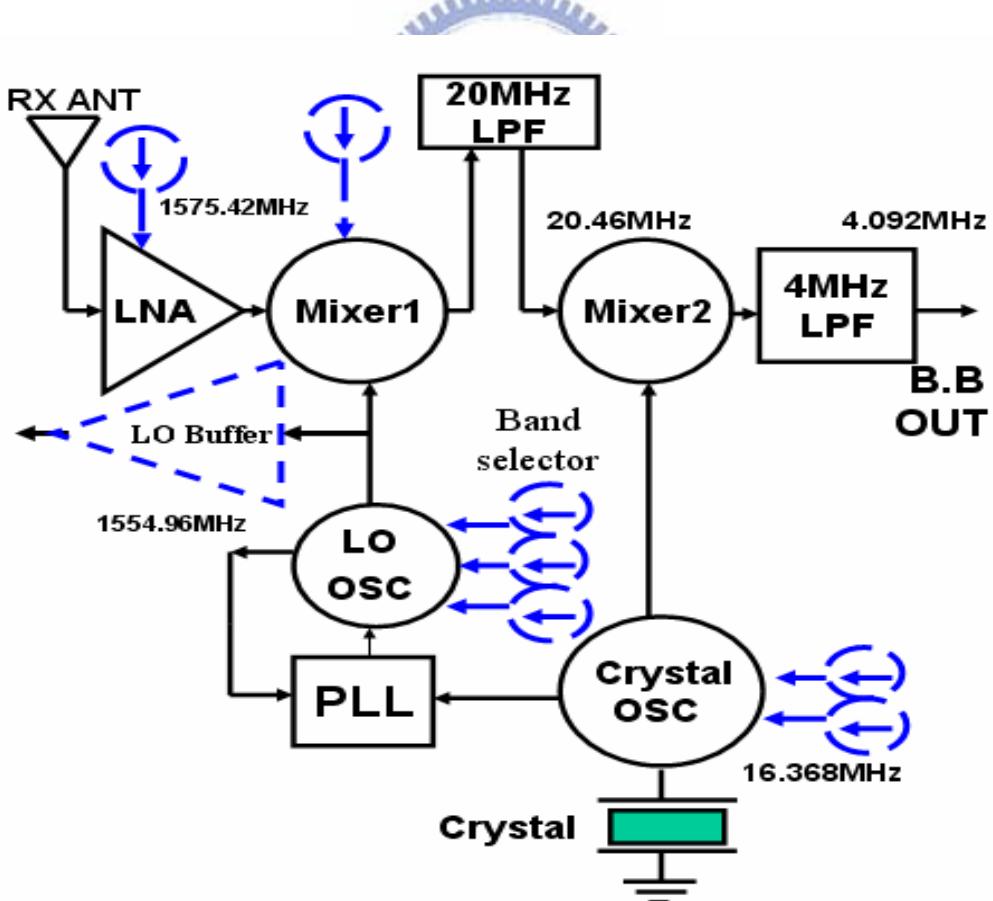

因此我們迫切需要一個巧妙的設計，以便在無 RF Probe station 設備的實驗室裡，就能立刻完成測試及偵錯，進而確認問題，以確保下一次 Tape out 的成果。此巧妙的設計機制，即為本文所推薦的 **RF IC** 設計法 (如圖 1.5.2) 所示，虛線所示即為與傳統方式不同之處。簡單的說我們使用改變 DC 電流的方法來最佳化 LNA 及 Mixer，然後亦將一個 OSC 變成八個 OSC，如此一來我們的成功機會將比典型的設計之機會提升許多了。

(圖 1.5.2) 推薦的 RF IC 功能示意圖

誠如功能示意圖(圖 1.5.2)所展示的樣子，我們只是在大多數的功能方塊間，加上一些可控制的信號開關(SWITCH)及輸出/輸入(I/O)緩衝器。如此我們就可以測得到大多數的功能方塊或群組方塊，進而達到最佳化規格的設計目的。

我們採用 3wire[12] [109]，來控制這些信號開關，以減低 RF IC 的設計困難度。3wire 雖已被成熟的運用做為 RF IC 的電流開關，甚至先進的 RF IC 設計已將它設計成自動校正系統以提高良品比率，雖與本文相較之下確有異曲同工之妙。但本文運用 3wire 來改善設計困難度，在目的上不完全與其它運用相同。所以 3wire 是一種控制開關，至於它的應用應是包羅萬象。

### 1.5.3 系統方塊圖說明

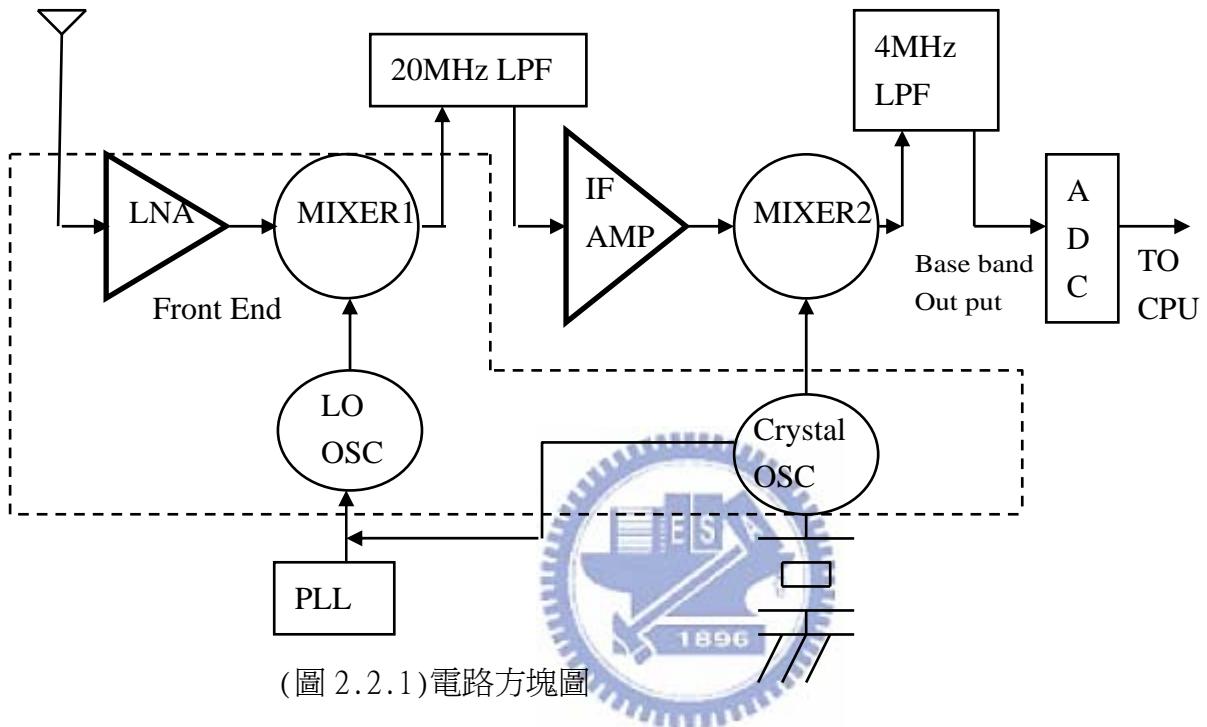

在 1.3 節中求的 Receiver LNA IN PUT 為-130dBm 以下。在未加上數位電路處理之前 LNA IN PUT 為-130dBm +43dBm=-87dBm，所以理論上純 RF 部分只要做到-87dBm 即可，因為數位電路會提升 43dB 的增益，我們稱為 Processing Gain。

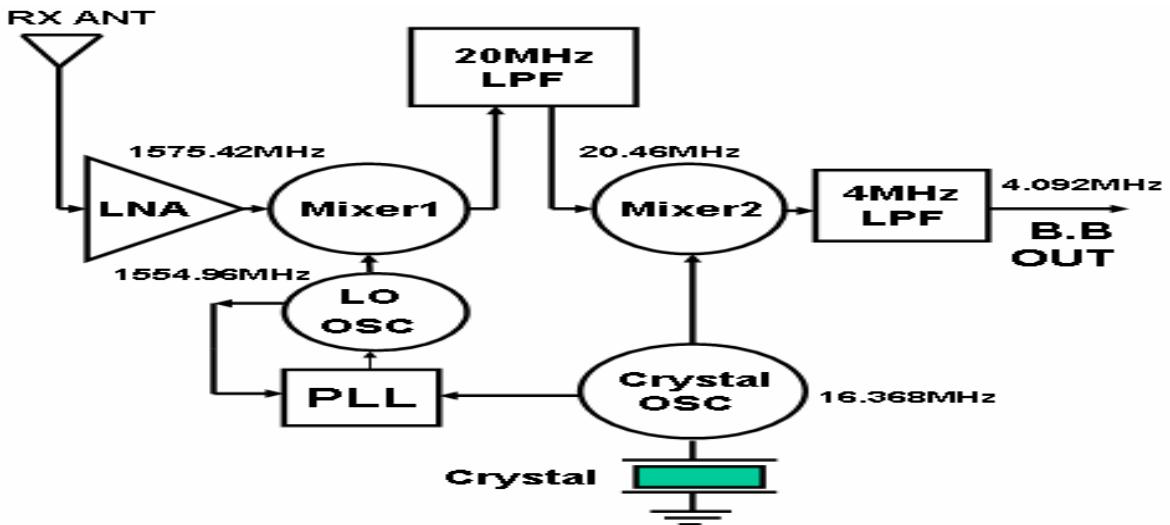

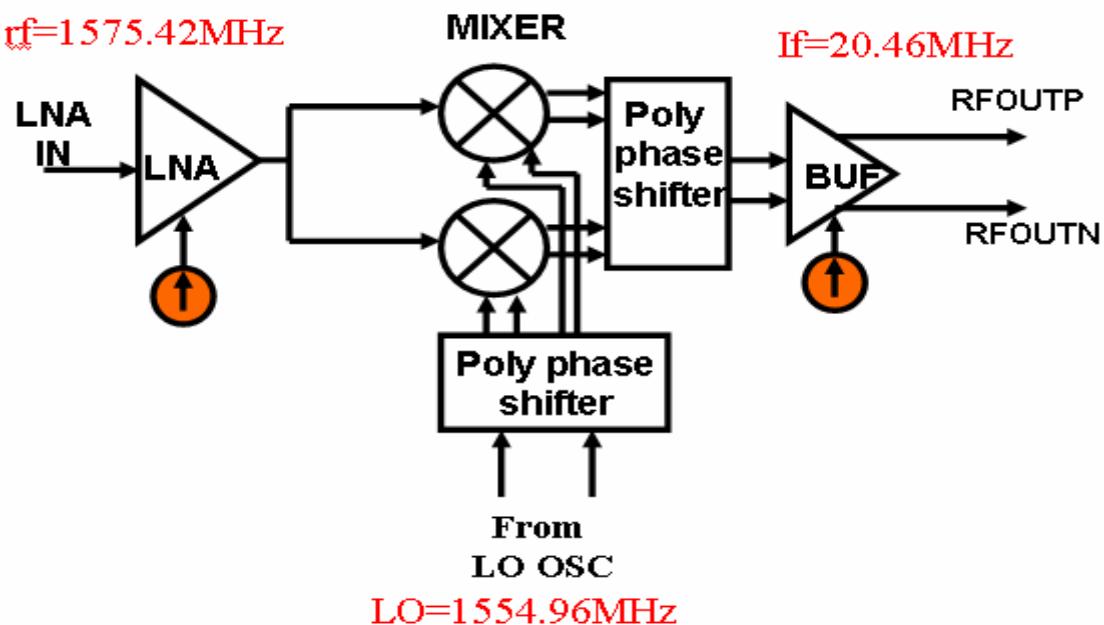

(如圖 1.5.2)所示，在此系統中我們選擇 20MHz 為第一中頻，4MHz 為第二中頻。主要是因為此種架構具有如下優點：

1. 可以避免處理 DC OFF SET 的問題。

2. 有外部現成的濾波器可購買使用。

3. 採取兩個中頻可以避免 IC 內之中頻放大器使用大電容，而佔用晶片面積。

我們使用了假象拒斥混波器<sup>[3]</sup>，以節省一個外部假象濾波器。

註：本文中尚未討論“假象拒斥混波器”的問題，僅參考現成電路製作。

系統頻率計算：

$$RF=1575.42\text{MHz}$$

$$LO=1554.96\text{MHz}$$

$$\therefore IF=1575.42-1554.96=20.46(\text{MHz})$$

## 二、研究內容與方法

本章將開始敘述我們的研究內容及方法。

### 2.1 GPS Receiver RF IC及系統的研究內容

由於我們將所有的心力都聚焦在 **RF IC** 的設計上，所以我們對於其他必需的資源都採取外購的方式來進行。下列將敘述一些關鍵資源的出處。

#### 2.1.1 GPS的整組參考成品及應用軟體的來源

此參考成品以台幣 3500 元購自交通大學內的附設書局。購買此成品時即附增試用 60 天的應用軟體。由於此成品已含天線，所以我們就有了現成的天線了。

當然此成品也含整套的基頻零組件及韌體，所以我也擁有這些基頻零組件及韌體了。

#### 2.1.2 GPS成品製作內容

當擁有這些軟硬體後，我們只要將此參考成品的 **RF IC** 挖除並換上我們自己設計的 **RF IC** 之後，那就可以驗證自己設計的 **RF IC** 了。(話雖如此，但是情並沒有這麼簡單，事實上我們事先經過仔細的核對、測試及評估才如此替換的。)這就是我們製造此 GPS 成品的方法。當然製造此 GPS 成品並非我們的最終目標，我們的最終目的是在驗證“內建測試機制的衛星定位接收機”，不過要先有 GPS 成品才能驗證此“**RF IC**”能否收到衛星的信號，這也是我們去買這組成品的原因。

#### 2.1.3 RF IC的規格來源及內容

從美國交通部海岸巡防隊(U.S COAST GUARD)出版的 GPS 標準定位信號規格中 (Global Positioning System standard positioning service signal specification)，我們知道了系統規格，並且因為它是權威單位，所以我們把它當作最高的設計原則。(圖 2.1.3)為美國交通部海岸巡防隊的網頁，從這裡可以查到一些 GPS 所需的規格。[110]

從拆解外購的整組 **GPS** 中，我們知道了此 **RF IC** 的型號為 SE4100L。這顆 **RF IC** 的詳細規格如附錄一、GPS Receiver RFIC Data sheet-SE4100 from Sige Semiconductor。

因為這是此系統的 RFIC 規格，所以這個規格成為最靠近我們將推薦的 “**RF IC**” 之規格。[111]

從上列兩個規格來源中，我們整理出新的規格，以便讓我們在設計本文將推薦的 “**RF IC**” 時，有一個遵循的標準。由於這篇論文將焦點集中在 **RF IC** 的設計方法上，故對於 IC 的 Performance 之追求，除了依據整理出的新規格外，我們就僅先止於能否收到衛星並執行正確的定位為止。

除了上列兩篇主要的依據文章外，我們也收集了一些大廠的同類產品及 DATA SHEET，來做為輔助的參考，以增強我們自製規格之可信度，這些資料來源列在此論文的最後頁---- **REFERENCES PRODUC AND DATA SHEET.**

## 2.2 研究方法

在 1.1 節的研究動機中我們提及 RF IC 在設計上，常常遭遇到規格逼近不易的問題，在此我們提出一個規格逼近法，就是在設計 RF IC 時我們就在內部建立測試機制。在此我們將研究方法敘述如下：

1. 以 Sige Semiconductor 公司出品的 RF IC-SE4100 為參考基準，再重新設計出一顆 “內建測試機制的 GPS Receiver RF IC”。

2. 以理論的推演及實際的量測一一展現此 “內建測試機制的方法” 的優點。

### 2.2.1 推薦的 RF IC之系統設計

為了方便說明，首先我們將電路方塊圖更進一步重繪出於下並將欲展示的部分用虛線框起來，然後使用數學式子把所需的規格計算出來並作成表格。此偏論文著重於 RF IC 的設計方法，至於系統及 Processing Gain 是列於參考書目 [15] 。

解析及量測 Sige Semiconductor 公司出品的 RF IC-SE4100，我們整理出整個 RFIC 的規格如下表：

| Item              | Specification | Unit |

|-------------------|---------------|------|

| Input power range | -94~ 40       | dBm  |

| Cascade Gain      | 100~110       | dB   |

| (S/N) required    | 8~10          | dB   |

| Filter Bandwidth  | 2             | MHz  |

| Signal Bandwidth  | 1             | MHz  |

(表 2.2.1) Sige Semiconductor 公司出品的 RF IC-SE4100 的設計規格

我們使用課本上的方法並將此方法建立成試算表，以方便分配 IC 內部各個方塊的增益及雜信指數。[1] [17]

**Power Gain 的分配依據：**我們根據外接零件廠商所提供的電性資料(如 20M-LPF、4M-LPF)及量測一般單級 RF IC 的增益分配成如下表數值。

**P1dB 的分配依據：**參考上表 2.2.1 知道 RF IC 最高輸入為-40dBm，所以我們將 LNA 的 P1dB 定為-40dBm。預估 MIXER1 具有不超過 20dB 的增益所以我們決定 MIXER1 P1dB 為-20dBm。由於 LOW PASS FILTER 為被動元件，它的 P1dB 大於 20dBm 但因為此接收路徑信號不會超過 10dBm( 限制放大器 IF AMP 的作用)，所以我們決定 20M-LPF 及 4M-LPF 之 P1dB 大於 10dBm 就可以了。此衛星定位為調頻系統[3]所以我們可將信號做振幅限制放大，因此 IF AMP 是一組高增益(80dB)的限制放大器，這樣的安排不但可以得到高的增益而且也不需太高的線性信號動態範圍，我們將它定在大於 0dBm 就符合系統所需了。事實上經過我們如 1.3 節的估算，衛星信號到達 LNA 的強度不會大於-60dBm 所以- 40dBm 的預估是至少留 20dB 的寬鬆餘度。

**IIP3 的分配依據：**從課本中的導出結果中，我們得知 P1dB 與 IIP3 約差 9.6dB 所以我們將 IIP3 定為 P1dB 加 10dB 之值。[17]

下表為上列各項目之整理列表及多級增益公式。

Total Gain(dB)= G1(dB)+ G2(dB)+ G3(dB)+-----公式(1)

| Gain name  | LNA  | MIXER1 | 20M-LPF | IF AMP | MIXER2 | 4M-LPF | Total | Unit |

|------------|------|--------|---------|--------|--------|--------|-------|------|

| Gain stage | G1   | G2     | G3      | G4     | G5     | G6     |       |      |

| Power Gain | 18   | 11     | -6      | 80     | 10     | -3     | 110   | dB   |

| P1dB       | >-40 | >-20   | >10     | >0     | >0     | >10    | NA    | dBm  |

| IIP3       | >-30 | >-10   | >20     | >10    | >10    | >20    | NA    | dBm  |

接著我們來分配各級雜信指數，再來計算可接收的最小信號強度，在專業術語中我們稱它為感度(Sensitivity)。

Ftot=F1+(F2-1)/(G1)+(F3-1)/(G1G2)+(F4-1)/(G1G2G3)+-----公式(2)

| Gain name    | LNA | MIXER1 | 20M-LPF | IF AMP | MIXER2 | 4M-LPF | Unit |

|--------------|-----|--------|---------|--------|--------|--------|------|

| Noise Factor | F1  | F2     | F3      | F4     | F5     | F6     |      |

| Factor value | 2.5 | 10     | 6       | 20     | 12     | 3      | dB   |

| Gain stage    | G1         | G2  | G3     | G4     | G5      | Ftot   | Ftot(dB) |      |

|---------------|------------|-----|--------|--------|---------|--------|----------|------|

|               | Gain times | 18  | 198    | -1188  | -95040  | 158400 |          |      |

| F1+(Fn-1)/Gn! | 2.5        | 0.5 | 0.0014 | -4E-06 | 2.7E-11 | 3E-17  | 3.0      | 4.77 |

$$(S/N)_{input} = F_{tot} + (S/N)_{output} + 10 \log(f_b/B) \quad \text{公式(3)}$$

| (S/N)input= | Ftot(dB) | (S/N)output(dB) | Filter BW | Signal BW | log(fb/B) | (S/N)input |

|-------------|----------|-----------------|-----------|-----------|-----------|------------|

|             | 4.77     | 12              | 2000000   | 1000000   | 3.01      | 19.8       |

$$(S)_{input} = -174 + 10 \log \text{Signal BW} + (S/N)_{input} = -94.2 \text{ (dBm)} \quad \text{公式(4)}$$

上列數值經過多次的調整分配後得到公式 4 的計算結果，我們知道此 RF IC 的接收感度為 -94dBm。

所以經過上列調整試算後我們擬定 IC Front-end 內部各個方塊的增益及雜信指數的配置如下表：

| Gain name<br>Item | LNA | MIXER1<br>(含 Poly+Buffer) | 20MHz<br>LPF | IF<br>AMP | MIXER2 | 4M<br>LPF | Total | Unit |

|-------------------|-----|---------------------------|--------------|-----------|--------|-----------|-------|------|

| Power Gain        | 18  | 11                        | -6           | 80        | 10     | -3        | 110   | dB   |

| Noise Factor      | 2.5 | 10                        | 6            | 20        | 12     | 3         | 5     | dB   |

(表 2.2.2) Link budget chart for GPS RF IC

我們更進一步的將欲展示的三大方塊(Front-end、VCO、Crystal OSC)規格詳細列出如下表，這是一般商業販售 IC 常見之格式，我們是參考並量測它所建立起來的。在 Front-end 中三個主要規格都與前面的計算符合。

AC electrical characteristics      Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^\circ C$

| RF Front-End (LNA/Mixer cascaded) |                       |      |     |     |     |      |

|-----------------------------------|-----------------------|------|-----|-----|-----|------|

| Symbol                            | Parameter             | Note | MIN | TYP | MAX | Unit |

| RF <sub>Gain</sub>                | Front-End Gain        |      | 25  | 29  | 34  | dB   |

| NF                                | Noise Figure          |      |     | 4   | 6   | dB   |

| P <sub>1dB</sub>                  | 1dB Compression point |      | -38 | -35 | -32 | dBm  |

(表 2.2.5) 參考 Sige Semiconductor 公司出品的 RF IC-SE4100 所建立之

前端電路的設計規格

AC electrical characteristics

Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^\circ C$

| VCO (Local Oscillator) |                                     |     |         |     |        |  |

|------------------------|-------------------------------------|-----|---------|-----|--------|--|

| Symbol                 | Parameter                           | MIN | TYP     | MAX | Unit   |  |

| $f_{LO}$               | LO Center Frequency                 |     | 1554.96 |     | MHz    |  |

| $K_{VCO}$              | VCO Gain                            |     | 35      |     | MHz/V  |  |

| $f_{LOlevel}$          | LO output level                     |     | -5      |     | dBm    |  |

| $L_{10K}$              | LO SSB Phase Noise at 10KHz Offset  |     | -75     |     | dBc/Hz |  |

| $L_{100K}$             | LO SSB Phase Noise at 100KHz Offset |     | -80     |     | dBc/Hz |  |

| $L_{1M}$               | LO SSB Phase Noise at 1MHz Offset   |     | -105    |     | dBc/Hz |  |

| $L_{2M}$               | LO SSB Phase Noise at 2MHz Offset   |     | Na      |     | dBc/Hz |  |

(表 2.2.3) 參考 Sige Semiconductor 公司出品的 RF IC-SE4100 所建立之

本地振盪電路的設計規格

AC electrical characteristics

Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^\circ C$

| Crystal Oscillator |                                                                                    |      |      |        |      |      |

|--------------------|------------------------------------------------------------------------------------|------|------|--------|------|------|

| Symbol             | Parameter                                                                          | Note | MIN  | TYP    | MAX  | Unit |

| $f_{XTAL}$         | Oscillator Frequency                                                               |      | 16.2 |        | 16.5 | MHz  |

|                    | Recommended Crystal Parameters                                                     | 1    |      | 16.368 |      | MHz  |

|                    | Frequency                                                                          |      |      | 12     |      | pF   |

|                    | $C_{LOAD}$                                                                         |      |      |        |      |      |

| $t_{START}$        | Oscillator startup time to 95% final amplitude and within 10ppm of final frequency |      |      |        | 2    | msec |

| Duty rate          |                                                                                    |      | 45   | 50     | 55   | %    |

| Amplitude          |                                                                                    |      | 2.8  | 3      | 3.2  | V    |

Note: (1) Recommended crystal parameters assume a parallel ,fundamental model crystal is used.

(表 2.2.4) 參考 Sige Semiconductor 公司出品的 RF IC-SE4100 所建立之

石英晶體振盪電路的設計規格

## 2.2.2 系統的驗證方法

建立如上規格表後我們將依照上列數據一一的設計及實現我們的 “RF IC” 。

最後我們將挖除外購的 GPS 系統之 RF IC，並換上自己設計的 “RF IC”，以驗證我們推薦的設計方法。

### 三、 理論

本章將分節敘述 RF IC 的各個電路之理論模擬，依序是：本地振盪電路、石英晶體振盪電路和前端電路(即 LNA+MIXER)。

#### 3.1 本地振盪電路

##### 3.1.1 本地振盪電路的規格

我們已於 2.2.1 節中整理出本地振盪電路的設計規格，現在為了方便說明，我們重列(表 2.2.3)於下，以爲此的設計規格之憑據:<sup>[8]</sup>

AC electrical characteristics

Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^{\circ}C$

| VCO (Local Oscillator) |                                     |     |         |     |        |

|------------------------|-------------------------------------|-----|---------|-----|--------|

| Symbol                 | Parameter                           | MIN | TYP     | MAX | Unit   |

| $f_{LO}$               | LO Center Frequency                 |     | 1554.96 |     | MHz    |

| $K_{VCO}$              | VCO Gain                            |     | 35      |     | MHz/V  |

| $f_{LOlevel}$          | LO output level                     |     | -5      |     | dBm    |

| $L_{10K}$              | LO SSB Phase Noise at 10KHz Offset  |     | -75     |     | dBc/Hz |

| $L_{100K}$             | LO SSB Phase Noise at 100KHz Offset |     | -80     |     | dBc/Hz |

| $L_{1M}$               | LO SSB Phase Noise at 1MHz Offset   |     | -105    |     | dBc/Hz |

| $L_{2M}$               | LO SSB Phase Noise at 2MHz Offset   |     | Na      |     | dBc/Hz |

表(3.1.1)本地振盪電路的設計規格

##### 3.1.2 典型的本地振盪結構

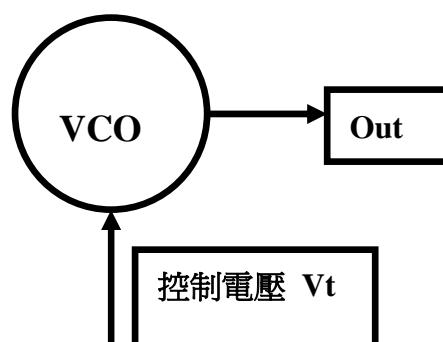

一般典型的本地振盪電路結構如(圖 3.1.2)，基本上它包含一個振盪器、輸出級和受控端，受控端是接受控制電壓以調整振盪頻率。

(圖 3.1.2) 典型的本地振盪功能方塊圖

### 3.1.3 推薦的本地振盪結構之一：為VCO加上八個頻帶

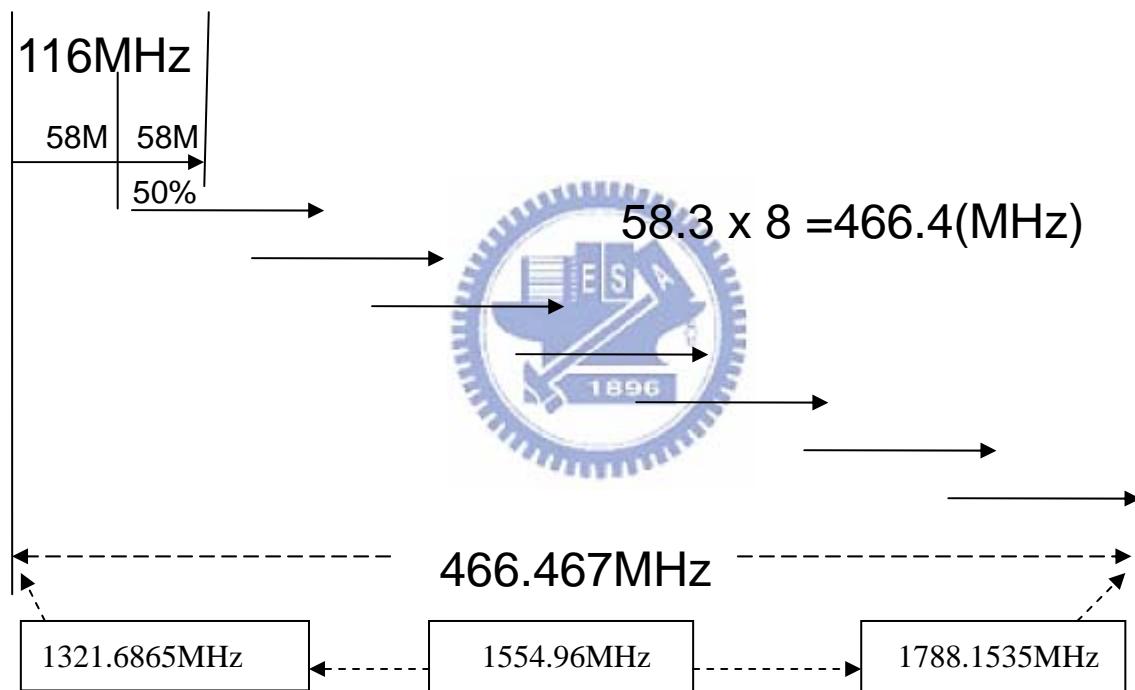

傳統上，欲達到上表中的 LO 頻率目標(1554.96 MHz)可能需要幾次的試做才能到達目標，當然我們可以把 VCO Gain 擴大，就足夠應付理論與實務的誤差(通常總誤差達 30%，經驗上粗估理論與實務的誤差約 +/-5% 共占 10%，製程誤差約 +/-10% 共占 20%)，但這時候相位雜訊就可能超過上表中的規格了。下列式子表示 30% 的誤差換算成頻率是 466.476MHz，若 VDD=3V 則 VCO Gain 需 155.492MHz/V 才行。

$$1554.96 \times 30\% = 466.476(\text{MHz})$$

$$466.476/3 = 155.492 (\text{MHz/V})$$

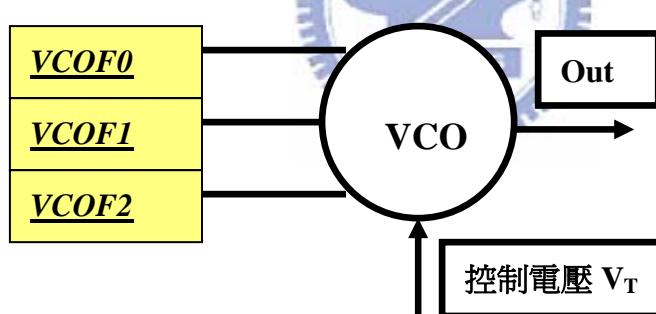

為了縮短設計時程及希望在第一次的試做中就可以命中目標，並使 VCO 的控制電壓大約維持在 1/2 VDD 之間(以應付溫度的飄移)，因此我們推薦在 VCO 電路內，建立 8 個可切換的頻帶，以便設計者能輕鬆的就達到這個目標。此推薦做法如下示意圖(圖 3.1.3)，加底線的文字方塊為我們新加上的電路，加底線的文字方塊為原本的傳統電路。

(圖 3.1.3)推薦的本地振盪功能方塊及控制圖

如上圖(圖 3.1.3)右方所示，共有 3 個位元，可供切換至 8 個頻帶。如此可使 VCO Gain 大幅降低到 19.4365MHz/V。下列 3 個式子表示 VCO Gain 可由 155.492MHz/V，大幅降低到 19.4365MHz/V。

$$1554.96 \times 30\% = 466.476(\text{MHz})$$

$$466.476/8 = 58.3095 (\text{MHz})$$

$$58.3095/3 = 19.4365 (\text{MHz})$$

不過為了避免頻率有不連續的情況發生，我們讓每個頻帶都有約 50%的重疊，所以最後的 VCO Gain 必須再增加 2 倍，為  $38.873\text{MHz/V}$ 。因此我們重新列式計算最後的 VCO Gain 如下： $1554.96 \times 30\% = 466.476(\text{MHz})$

$$466.476 / (8/2) = 116.619(\text{MHz})$$

$$116.619 / 3 = 38.873 (\text{MHz})$$

所以整個頻帶以  $1554.96\text{MHz}$  為中心，並擴展  $466.476\text{MHz}$ ，變成從  $1321.6865\text{MHz}$  到  $1788.1535\text{MHz}$ 。為了詳細闡述這個頻帶分配的想法，我們將此 8 個頻帶的配置示意圖(圖 3.1.3-1)繪製如下：

(圖 3.1.3-1) 本地振盪頻帶分配圖

依照這個做法，理論上即可很容易的達到上表所列的相位雜訊之規格。

在撰寫此論文的過程之中，我們已蒐集到一篇標題為「片上 VCO 可以進行數位化調整」的文章，此文章敘述如何將這 8 個頻帶做成自動選擇機制並可在 Cadence 的 Spectre RF 上模擬。此文出自 2004/12 月的電子工程專輯，網址是：[www.eettaiwan.com](http://www.eettaiwan.com)，作者是 Franck Banag，他的工作單位是：Cadence 設計系統公司/類比/混合訊號/RF 組/主管設計工程師。

### 3.1.4 推薦的本地振盪結構之二：為VCO加上輸出電路

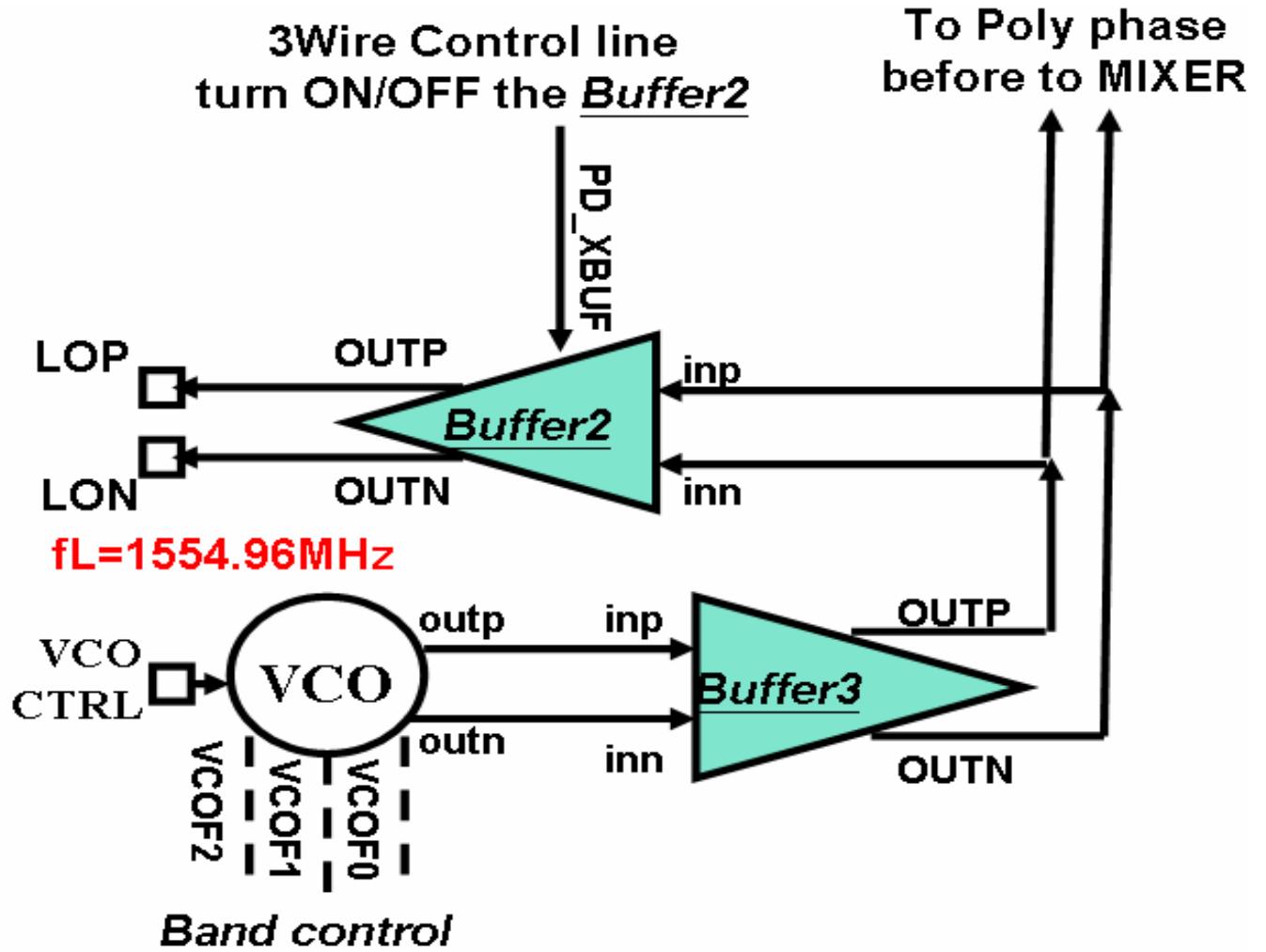

為了量測及驗證此 VCO 的性能，我們在 IC 內部，為 VCO 建立了輸出及輸入電路，現在將示意圖(圖 3.1.4)繪製如下以方便說明：加底線的文字方塊為我們新加上的電路，無加底線的文字方塊為原本的傳統電路。

(圖 3.1.4) 為 LO OSC 加上輸出及電路

從圖中我們可以看出 VCO 信號經由 Buffer3 及 Buffer2，可到達輸出入 Pin (LOP 及 LON)，如此我們即可在 IC 外面量測到 VCO 的「類真」性能了，包括振幅、頻率和相位雜訊等重要參數(因為 VCO 信號經過一個額外的 Buffer2，所以我們稱此信號為「類真」，故量測到的性能亦稱為「類真」性能)。

甚至，若我們不滿意原 IC 內部的 VCO 之性能，或想比較一下儀器級的 VCO，也

可以從 IC 外面灌入 1554.96 MHz 的信號，以取代 IC 內部的 VCO 之功能(通常外灌信號是使用射頻信號產生器)。當然這個時候須改變一下電路的偏壓情況，才能使 VCO 的信號路徑依我們的意思行進。事實上改變的是：供給 Buffer1 所需的偏壓，及切斷 Buffer3 和 Buffer2 的偏壓。

### 3.1.5 推薦的本地振盪電路

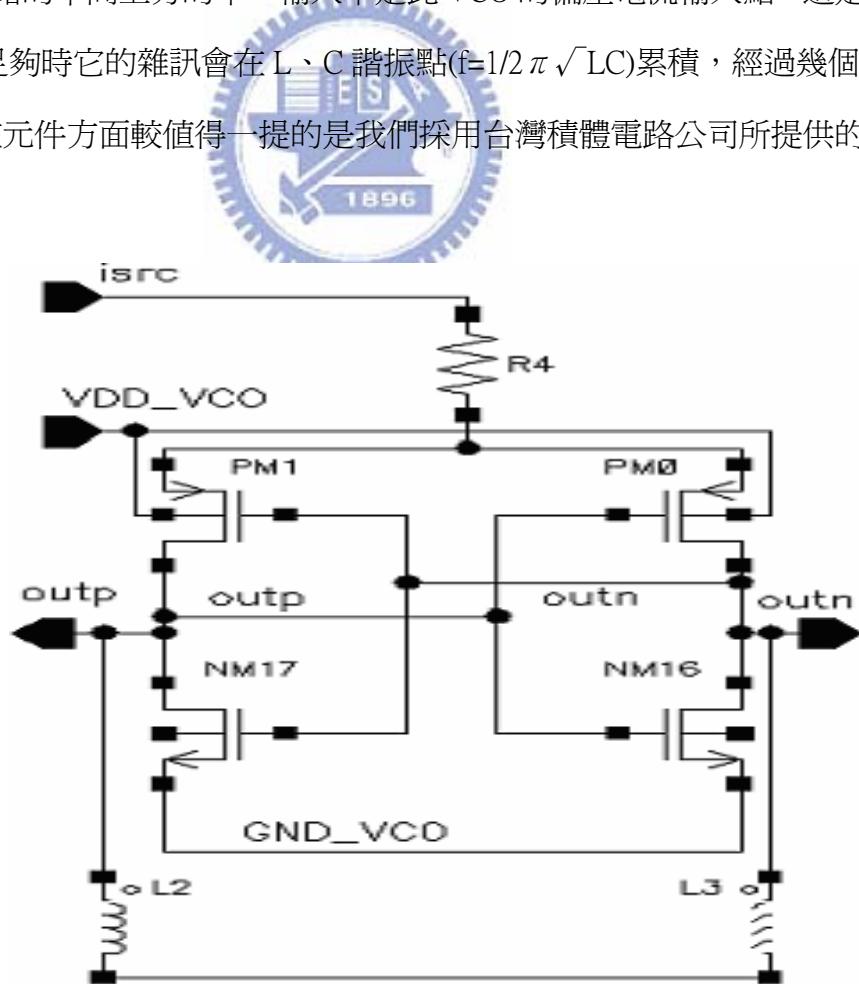

震盪電路依輸出波形分類為：弦波、方波及三角波，當然我們需要的是弦波。弦波振盪電路又區分為低頻用(如 RC 三節相移震盪器)及高頻用(LC 震盪器)。在此我們參考一般商用 IC 常用的振盪電路而採用了 LC 交互偶合震盪電路。<sup>[111]</sup> 下圖(圖 3.1.5-1)的四個電晶體(PM0,PM1,NM16,NM17)及電感(L2,L3)則是 VCO 的核心(LC 交互偶合震盪電路)。此電路的中間的兩個輸出埠則是 VCO 的輸出端點，此端點將接到下一個緩衝級(Buffer3)。又此電路的中間上方的單一輸入埠是此 VCO 的偏壓電流輸入點。這是一正回授電路，當電源足夠時它的雜訊會在 L、C 諧振點( $f=1/2 \pi \sqrt{LC}$ )累積，經過幾個週期後就會起振盪了。在元件方面較值得一提的是我們採用台灣積體電路公司所提供的環狀型電感。

(圖 3.1.5-1) VCO 電路

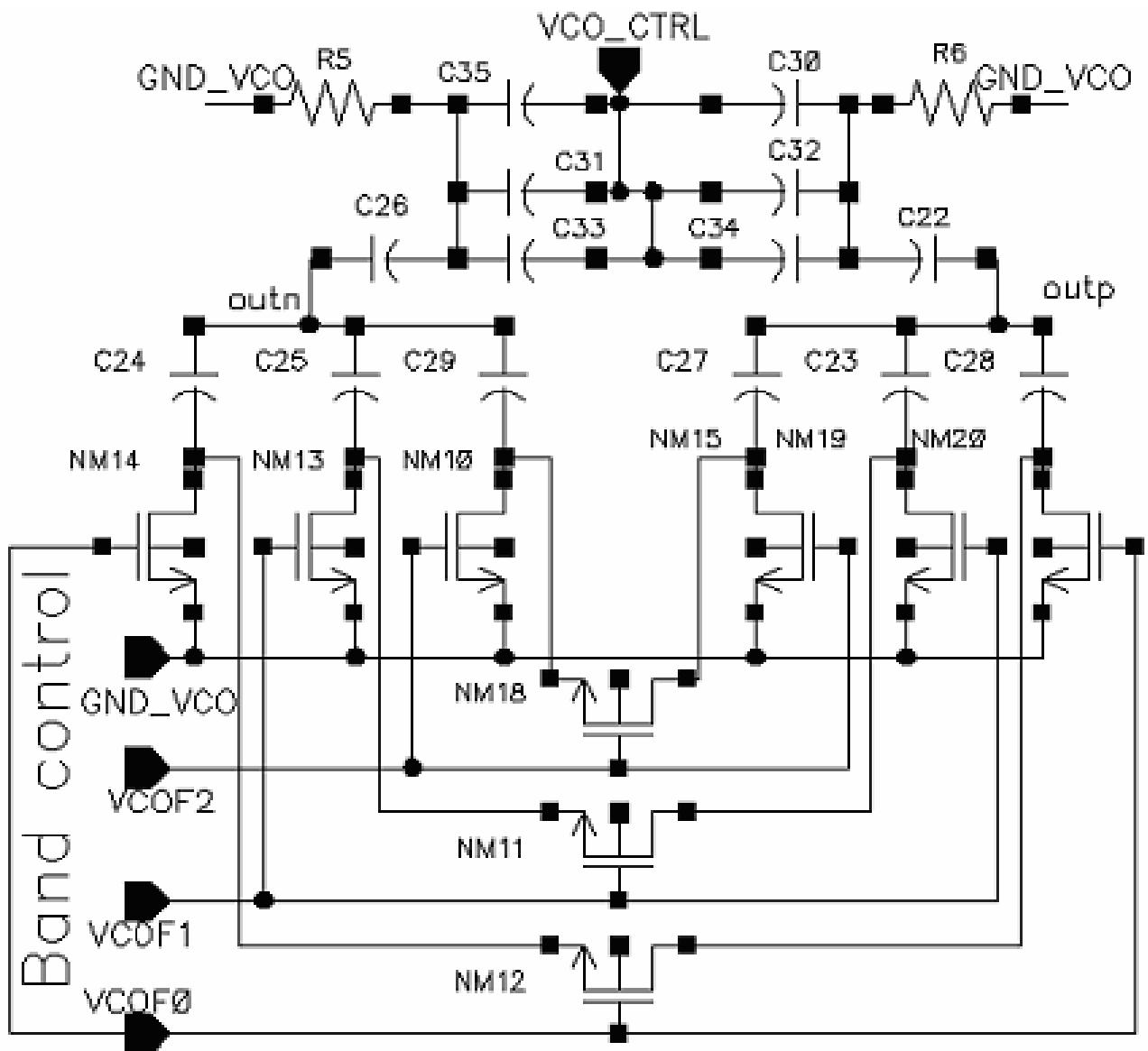

在下圖中(圖 3.1.5-2)的左下方有三個輸入埠(VCOF0~VCOF2)，就是 3.1.3 節所提到的頻帶選擇輸入埠(3-wire bit 0~2)，它們是用來選取電路中間的電容，以實現八個頻帶的功能。上方中間的單一輸入埠是 VCO\_CTRL(控制頻率的電壓)，C30~C35 是變容二極體，這是微調頻率的主要裝置。

NM18 將 C29 和 C27 串接在一起，就如同 C33 和 C34 一般結構，使 VCO 看到的電容效應更大。NM10 與 NM15 是當作電阻使用以確保 NM18 的源極與汲極偏壓都在 0V，避免此二極偏壓處在未知狀態。

(圖 3.1.5-2) VCO 頻帶選擇電路

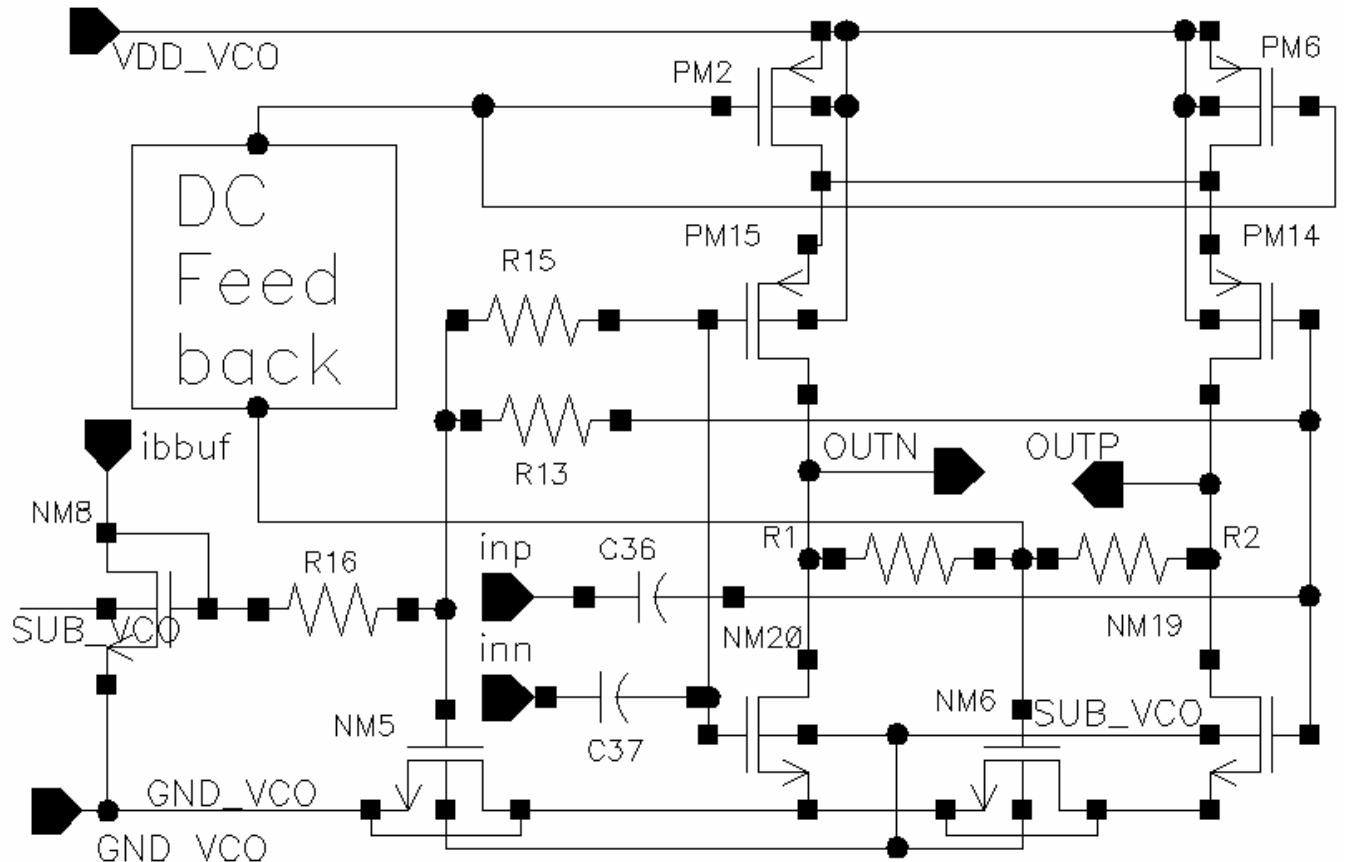

在下圖中(圖 3.1.5-3)就是 3.1.4 節所提到的 Buffer3 電路，此電路最主要是提供 VCO 與下一級電路有較好的隔離。所以它被設計成擁有高的輸入阻抗及低的輸出阻抗。為了防止電路工作點飄移我們亦採取直流回授的機制，讓此電路的穩定性更佳。

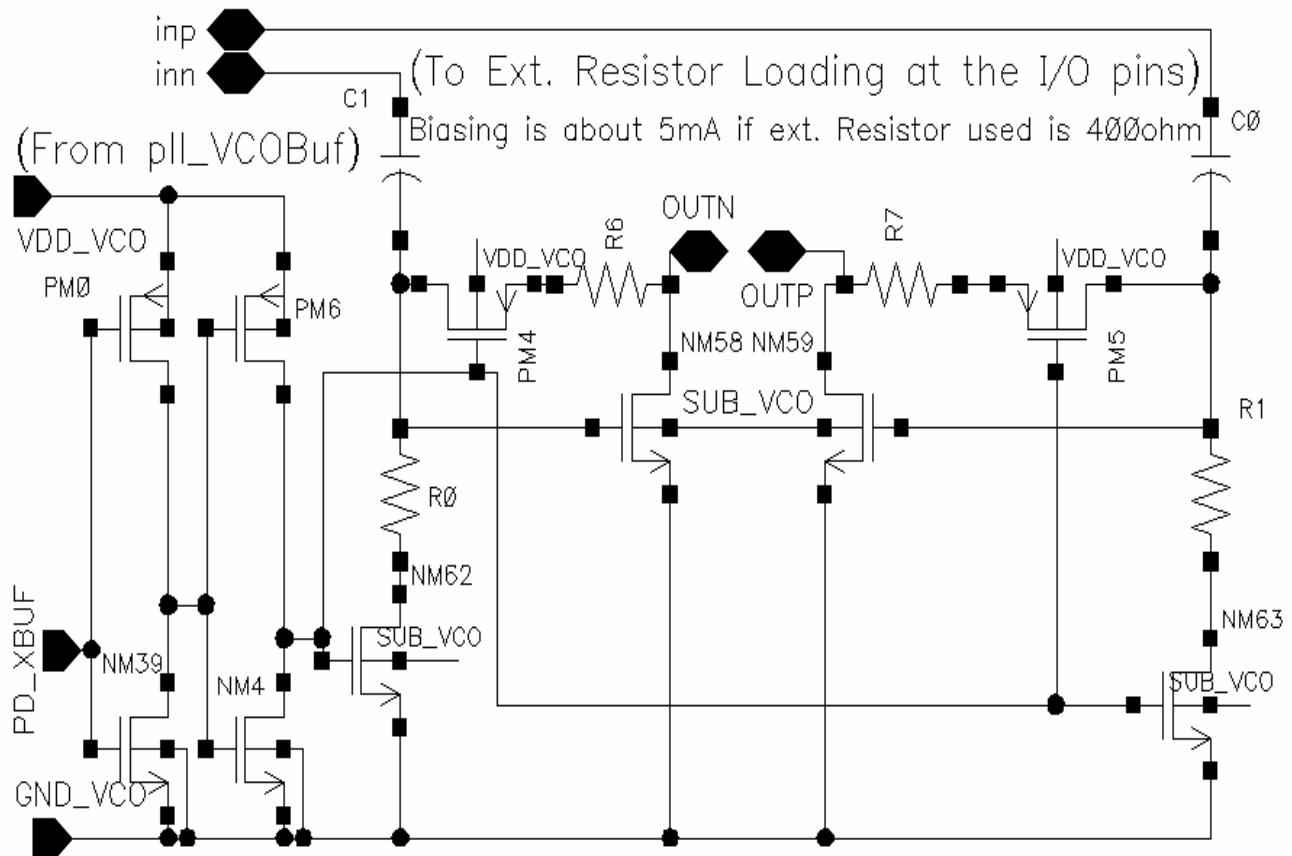

(圖 3.1.5-3) Buffer3 電路

在下圖中(圖 3.1.5-4)是 3.1.4 節所提到的 Buffer2 電路，此電路最主要是使 VCO 能輸出到 IC 外面，以便使用  $50\Omega$  儀器來量測它。故在非量測時此電路是被關掉的，所以他的消耗電流不計在 IC 的消耗電流內。當這個電路工作時它的消耗電流約為  $10mA$ ，設計上的特色是輸出阻抗可由外界設定，如  $50\Omega$ ， $75\Omega$ ----等。

(圖 3.1.5-4) Buffer2 電路

此電路是 IC 平衡輸出的外界電路，我們在模擬時加上這個 Balum(KO)電路，以便將來與儀器測試結果做對照。這個電路主要的目的是將 IC 的平衡信號，轉換成非平衡信號，以利單端儀器量測(例如：頻譜分析儀等)。最右端的 PORT0 是代表  $50\Omega$  的儀器阻抗，這個符號是模擬軟體特有之形狀。LOP、LON 是 IC 的平衡輸出，可對照到示意圖(圖 3.1.4)。

(圖 3.1.5-4) IC 本地震盪器之外界電路

### 3.1.6 推薦的本地振盪電路模擬結果

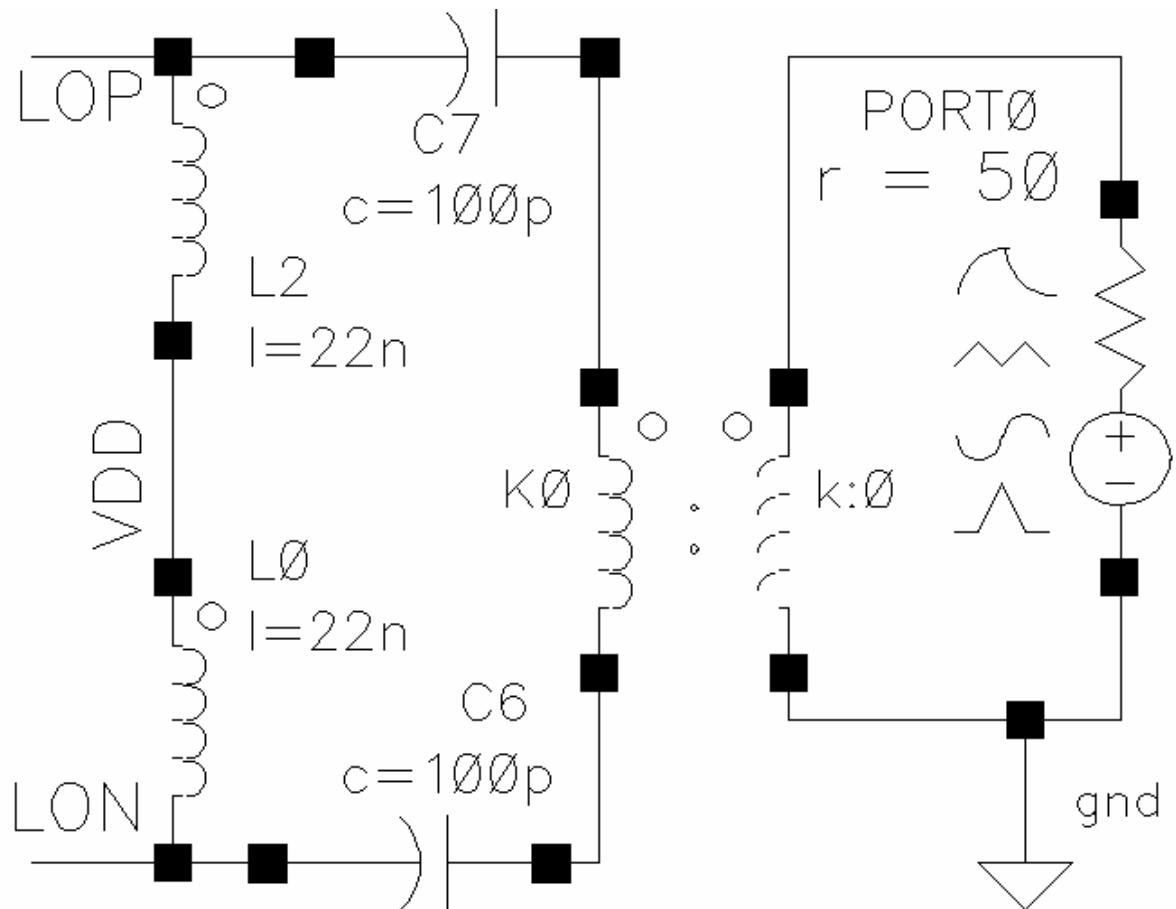

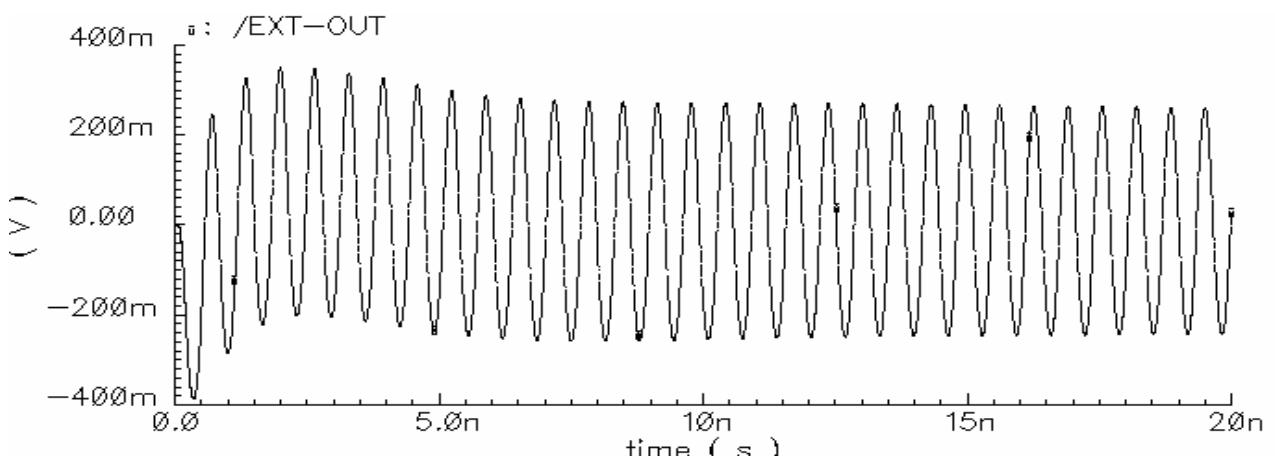

下表(表 3.1.6)為推薦的本地振盪器之輸出頻率模擬結果，統計曲線如(圖 3.1.6)。輸出信號如(圖 3.1.6-1)。雖然此模擬結果的最低頻及最高沒有符合(圖 3.1.3-1 頻帶分配圖)般的描述值，不過此結果的每一個頻帶都有將近 50% 的重疊，不會出現不連續的情形。

在下表中(表 3.1.6)我們設計了從 1431MHz~1741MHz 的頻率範圍，不過將來只用到一個頻率，就是 1554.92MHz。其對應之曲線亦繪於下圖(圖 3.1.6)。

| 3Wire_12 11 10 C_Bin<br>VCO_F2 F1 F0 | Frequency Simulation result<br>Unit=(MHz) |         |         | KVCO<br>Unit=(MHz) |         |

|--------------------------------------|-------------------------------------------|---------|---------|--------------------|---------|

|                                      | Vt=0.7V                                   | Vt=1.5V | Vt=2.8V | Band               | Average |

| 0 0 0 0P                             | 1665                                      | 1702    | 1741    | 36.2               | 29.2    |

| 0 0 1 0.25P                          | 1627                                      | 1662    | 1699    | 34                 |         |

| 0 1 0 0.5P                           | 1588                                      | 1620    | 1654    | 31                 |         |

| 0 1 1 0.75P                          | 1555                                      | 1586    | 1618    | 30                 |         |

| 1 0 0 1.0P                           | 1517                                      | 1545    | 1575    | 27.6               |         |

| 1 0 1 1.25P                          | 1488                                      | 1515    | 1543    | 26.2               |         |

| 1 1 0 1.5P                           | 1457                                      | 1483    | 1509    | 24.76              |         |

| 1 1 1 1.75P                          | 1431                                      | 1456    | 1481    | 23.8               |         |

(表 3.1.6) SK1110B5 Frequency vs. tune voltage simulation result

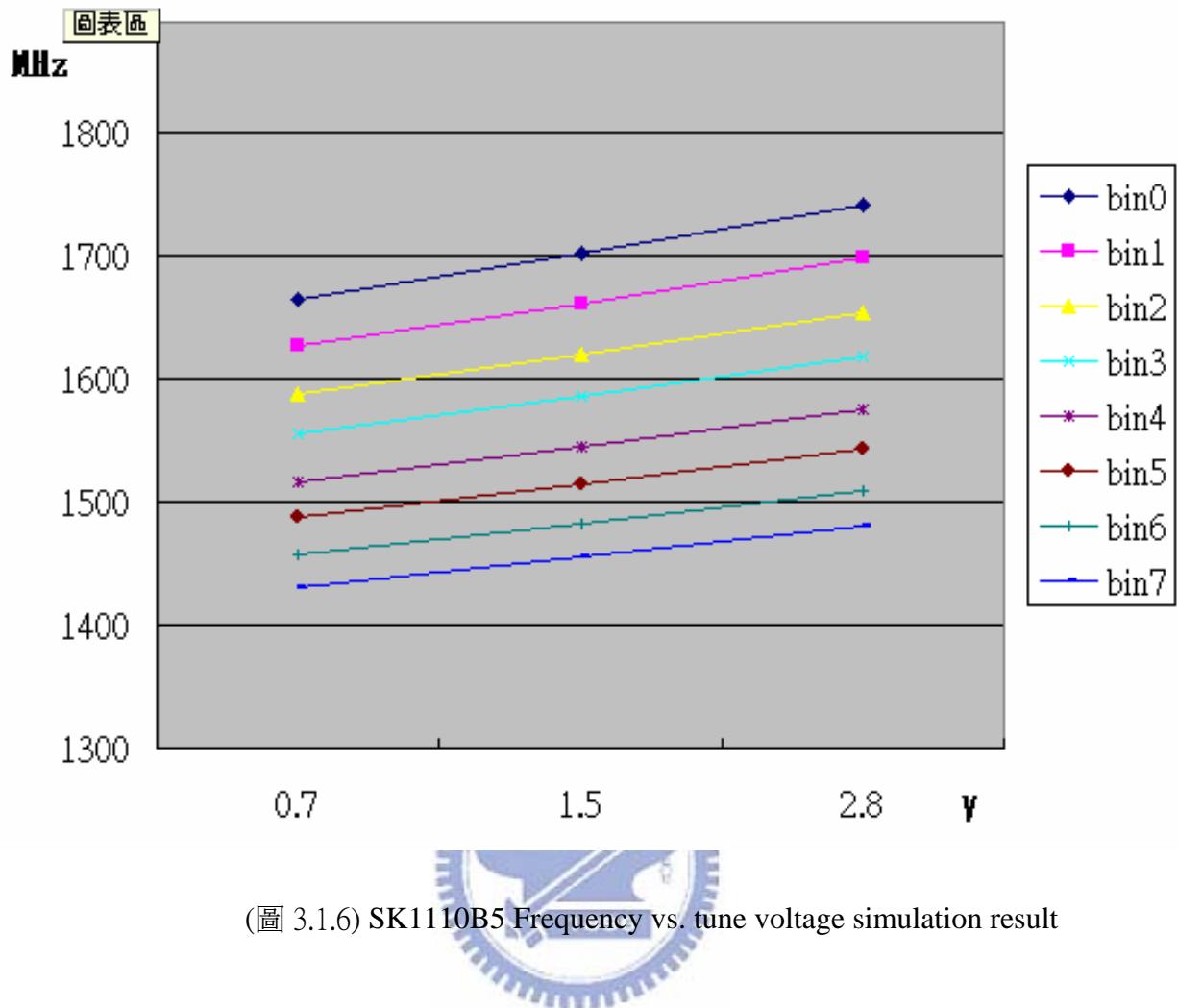

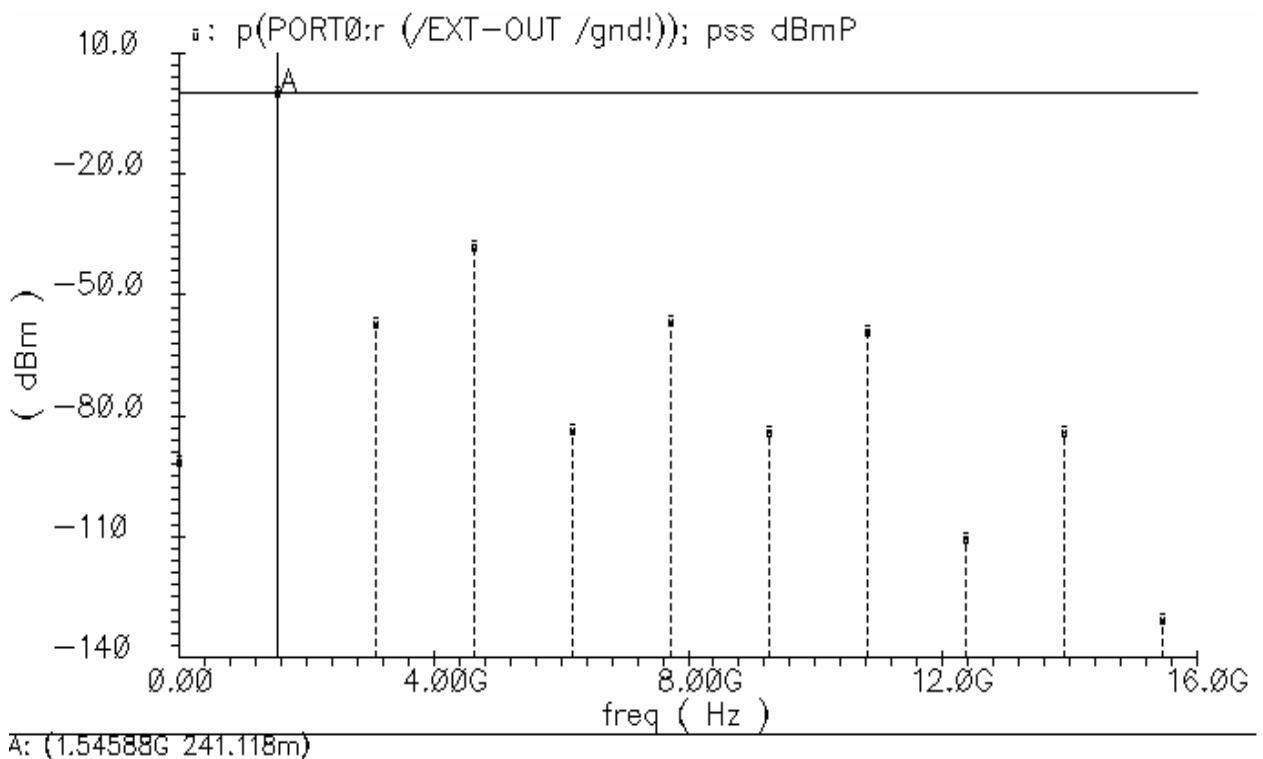

下二個圖為推薦的本地振盪器，分別在時域及頻域上之模擬結果。它的振幅約有 500mVp-p，相當於 0dBm 左右的功率(在  $50\Omega$  的阻抗中)。

(圖 3.1.6-1) 推薦的本地振盪器在時域上之模擬結果

(圖 3.1.6-2) 推薦的本地振盪器在頻域上之模擬結果

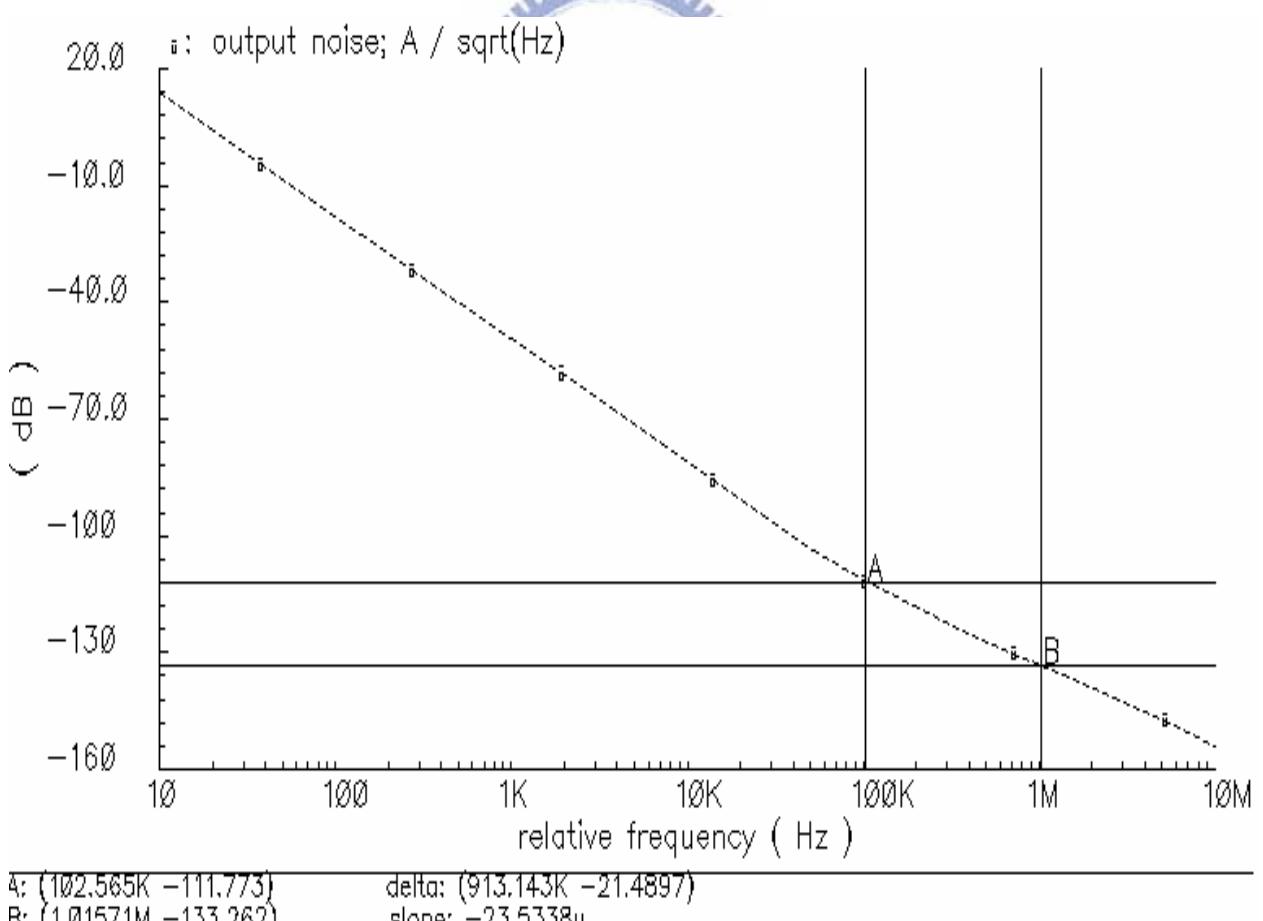

(圖 3.1.6-3) 推薦的本地振盪器其相位雜訊之模擬結果曲線圖

下列的(表 3.1.6-1)，為(上圖)相位雜信的模擬結果之整理表。

Conditions :  $V_{CC}=V_{DD}=3.0V, T_A=25^{\circ}C$ ,

| Offset | Specifications | Simulation Result | Unit   |

|--------|----------------|-------------------|--------|

| 10KHz  | -75            | -81               | dBc/Hz |

| 100KHz | -80            | -111              | dBc/Hz |

| 1MHz   | -105           | -133              | dBc/Hz |

| 2MHz   | Na             | -139              | dBc/Hz |

(表 3.1.6-1)Phase noise simulation result table

我們在本節最後將規格與模擬結果，整理於下(表 3.1.6-2)中。

AC electrical characteristics

Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^{\circ}C$

| VCO and Local Oscillator |                                     |                    |                   |        |

|--------------------------|-------------------------------------|--------------------|-------------------|--------|

| Symbol                   | Parameter                           | Spec               | Simulation result | Unit   |

| $f_{LO}$                 | LO Center Frequency                 | 1554.96<br>+/-0.01 | Na                | MHz    |

| $K_{VCO}$                | VCO Gain                            | 30+/-10            | <b>23.8~36.2</b>  | MHz/V  |

| $f_{LOlevel}$            | LO output level                     | >-5                | <b>0</b>          | dBm    |

| $L_{10K}$                | LO SSB Phase Noise at 10KHz Offset  | <-75               | <b>-81</b>        | dBc/Hz |

| $L_{100K}$               | LO SSB Phase Noise at 100KHz Offset | <-80               | <b>-111</b>       | dBc/Hz |

| $L_{1M}$                 | LO SSB Phase Noise at 1MHz Offset   | <-105              | <b>-133</b>       | dBc/Hz |

| $L_{2M}$                 | LO SSB Phase Noise at 2MHz Offset   | Na                 | <b>-139</b>       | dBc/Hz |

(表 3.1.6-2)本地振盪電路的模擬結果整理表

### 3.1.7 此電路設計心得

為 VCO 內建 8 個頻帶及輸出入電路後，此 VCO 介面變得更友善、更容易操作，相對的也能使設計者更深入的了解自己設計的電路，進而縮短試作次數。

### 3.2 石英晶體振盪電路<sup>[108] [18]</sup>

在此節中我們將開始石英晶體振盪電路的電腦模擬。由於我們將電路的設計方法列為重點，所以石英晶體的模型及各種起振電路的詳細說明，請參考到[108] RAKON DATA SHEET “RSX-3 Very small low profile AT-cut quartz crystal” 和[18] Robert J.Matthys , Crystal Oscillator Circuits, Krieger publishing company Malabar,Florida.1992. 二資料，在此就謹簡單介紹。

#### 3.2.1 石英晶體振盪電路的規格

我們已於 2.2.1 節中整理出石英晶體振盪電路的設計規格，現在為了方便說明，重列(表 2.2.4)於下，以爲此的設計規格之憑據：

| AC electrical characteristics |                                                                                    | Conditions: V <sub>CC</sub> =V <sub>DD</sub> =3.0V,T <sub>A</sub> =25°C |      |        |      |      |

|-------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|--------|------|------|

| Symbol                        | Parameter                                                                          | Note                                                                    | MIN  | TYP    | MAX  | Unit |

| f <sub>XTAL</sub>             | Oscillator Frequency                                                               |                                                                         | 16.2 |        | 16.5 | MHz  |

|                               | Recommended Crystal Parameters                                                     | 1                                                                       |      | 16.368 |      | MHz  |

|                               | Frequency                                                                          |                                                                         |      | 12     |      | pF   |

|                               | C <sub>LOAD</sub>                                                                  |                                                                         |      |        |      |      |

| t <sub>START</sub>            | Oscillator startup time to 95% final amplitude and within 10ppm of final frequency |                                                                         |      |        | 2    | msec |

| Duty rate                     |                                                                                    |                                                                         | 45   | 50     | 55   | %    |

| Amplitude                     |                                                                                    |                                                                         | 2.8  | 3      | 3.2  | V    |

Note: (1) Recommended crystal parameters assume a parallel ,fundamental model crystal is used.

(表 3.2.1) 石英晶體振盪電路的設計規格

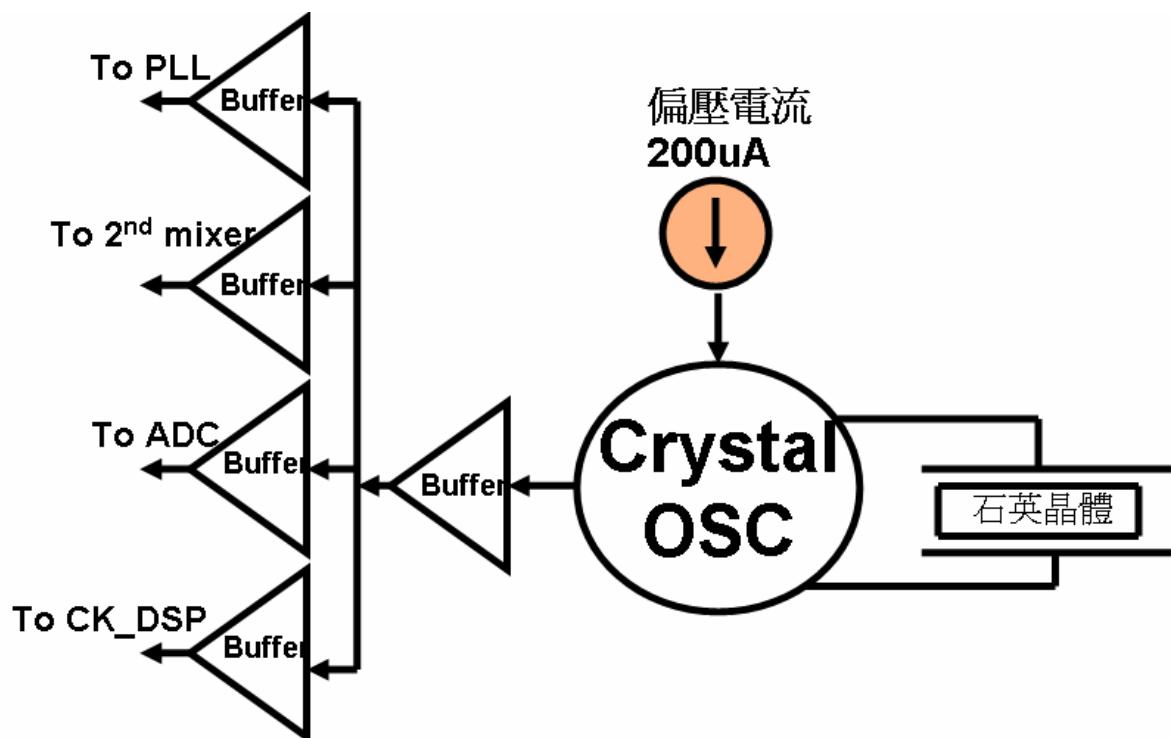

### 3.2.2 典型的石英晶體振盪電路

典型的石英晶體振盪電路如下圖：它包含了一個振盪器、輸出緩衝器和電流供應電路，石英晶體是外掛在 IC 外面的元件。由於此電路起振與否，是由主振盪器(Crystal OSC)的負電阻決定的。而著上顏色的方塊-電流供應電路(200uA)的作用是改變主振盪器之負電阻，所以下一節我們將由此著手改變設計的方法。

(圖 3.2.2) 典型的石英晶體振盪器方塊及控制圖

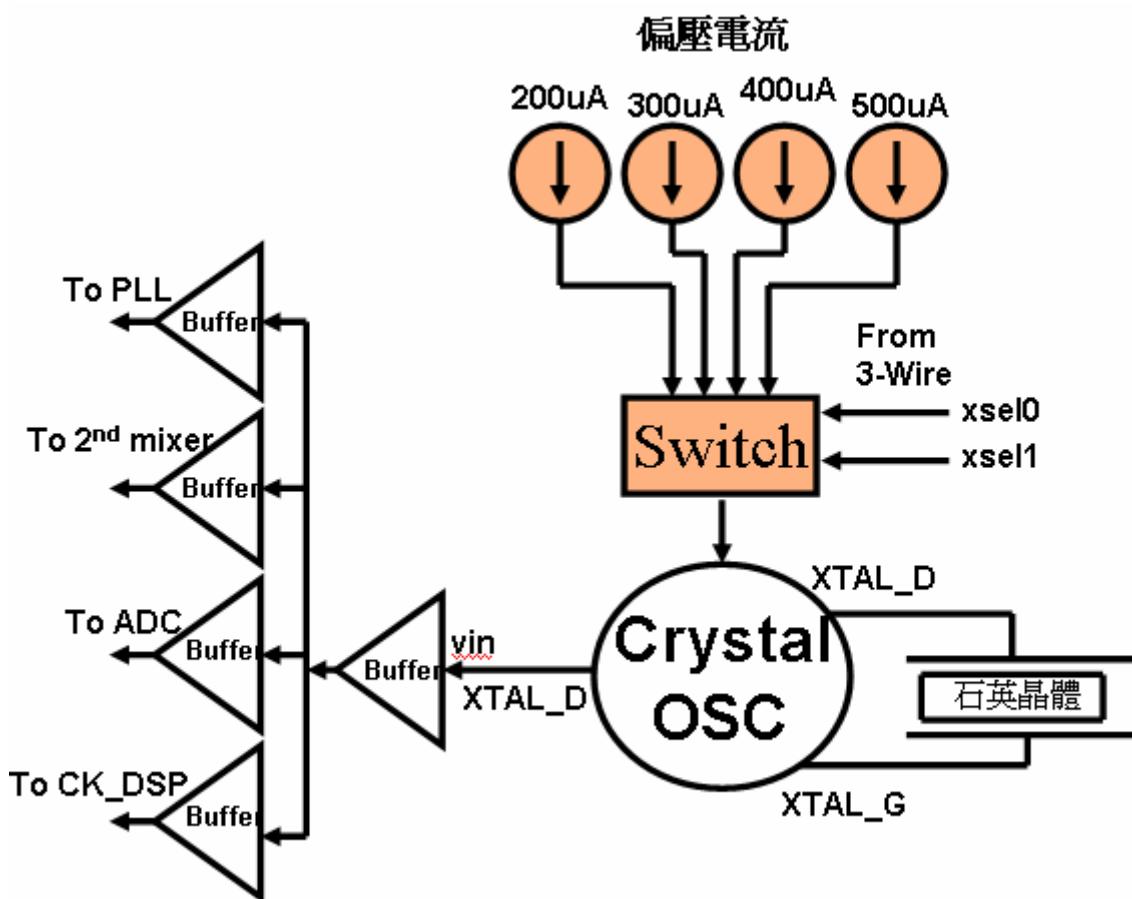

### 3.2.3 推薦的石英晶體振盪電路：為振盪電路加上電流選擇機制

經驗上，在量測石英晶體振盪電路時，我們常遇到不起振或是要用電表棒碰一下 IC 腳，才起振的窘境，在這個時候通常只要把振盪電路的電流加大些(事實上是增加負電阻)，則此石英晶體振盪電路就表現得很正常了。不過在 IC 的設計上，我們都希望儘量節省電路面積及消耗電流。所以很明顯的，我們期望設計一個性能正常，且電路面積及消耗電流都儘量小的最佳振盪電路。

我們將此電流選擇機制繪製如下，以方便說明：著上顏色的方塊是有別於傳統電路之處，也就是我們推薦的電路設計方法。

(圖 3.2.3-1) 推薦的石英晶體振盪器方塊及控制圖

從上圖中我們可以看到，石英晶體振盪電路的偏壓電流，可透過 3-Wire 來做選擇，

分別是：200uA、300uA、400uA 及 500uA 等 4 種。有了這 4 種電流供選擇之後，則此電路更能適應不同的製程變化及各種不同的石英晶體參數了。換句話說，有了此偏壓電流選擇機制，則 RF IC 設計者更能高枕無憂。

有數種的石英晶體振盪器電路可供我們來做為設計電路的參考，如反向器式振盪器[18]、Colpitts oscillator[18]及 Hartley oscillator[18]等。在此我們仍依我們購買的 Sige Semiconductor 公司出品的 RF IC-SE4100 所採用的考畢子振盪器電路，來做為設計的參考電路。

下圖(圖 3.2.3-2)是我們採用的考畢子振盪器電路而設計成的石英晶體振盪器電路。

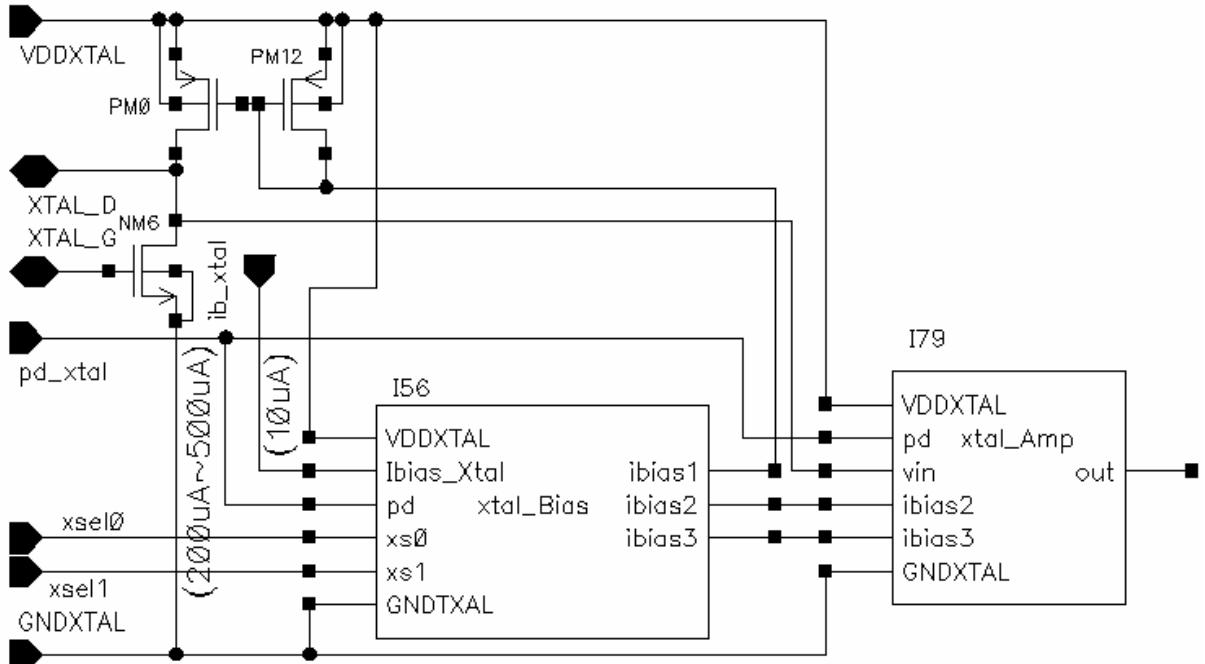

(圖 3.2.3-2) 推薦的石英晶體振盪器電路圖

電路運作簡單說明：NM6 是主放大器，它提供足夠的增益以利震盪的產生。I56 電路方塊是一個電流選擇電路，它使得電流鏡有 4 個定額電流可用(40uA、60uA、80uA 及 100uA)，連接到 PM0，PM12 是一組 1 : 5 的電流鏡它們提供主放大器定額的偏壓電流，所以最後可分別供應振盪器 200uA、300uA、400uA 及 500uA 等 4 種電流。I56 內部的電路討論如下頁。I79 為一限制放大器它使得輸出的波形為極似方波(CLOCK)，此(CLOCK)

即為整個 RF IC 之標準時脈，它亦當成第二次降頻之本地振盪器。

石英晶體與附帶零件，例如並聯電阻與雙電接地電容皆採外掛方式。而 Crystal 是接在 NM62 的源極與汲極兩端<sup>[108] [18]</sup>。

當然為了適應不同的製程變化及各種不同的石英晶體參數，我們設計了---電流選擇機制(圖 3.2.3-2，I56)，其電流的操作方式如電路圖所示的邏輯狀態之對應。

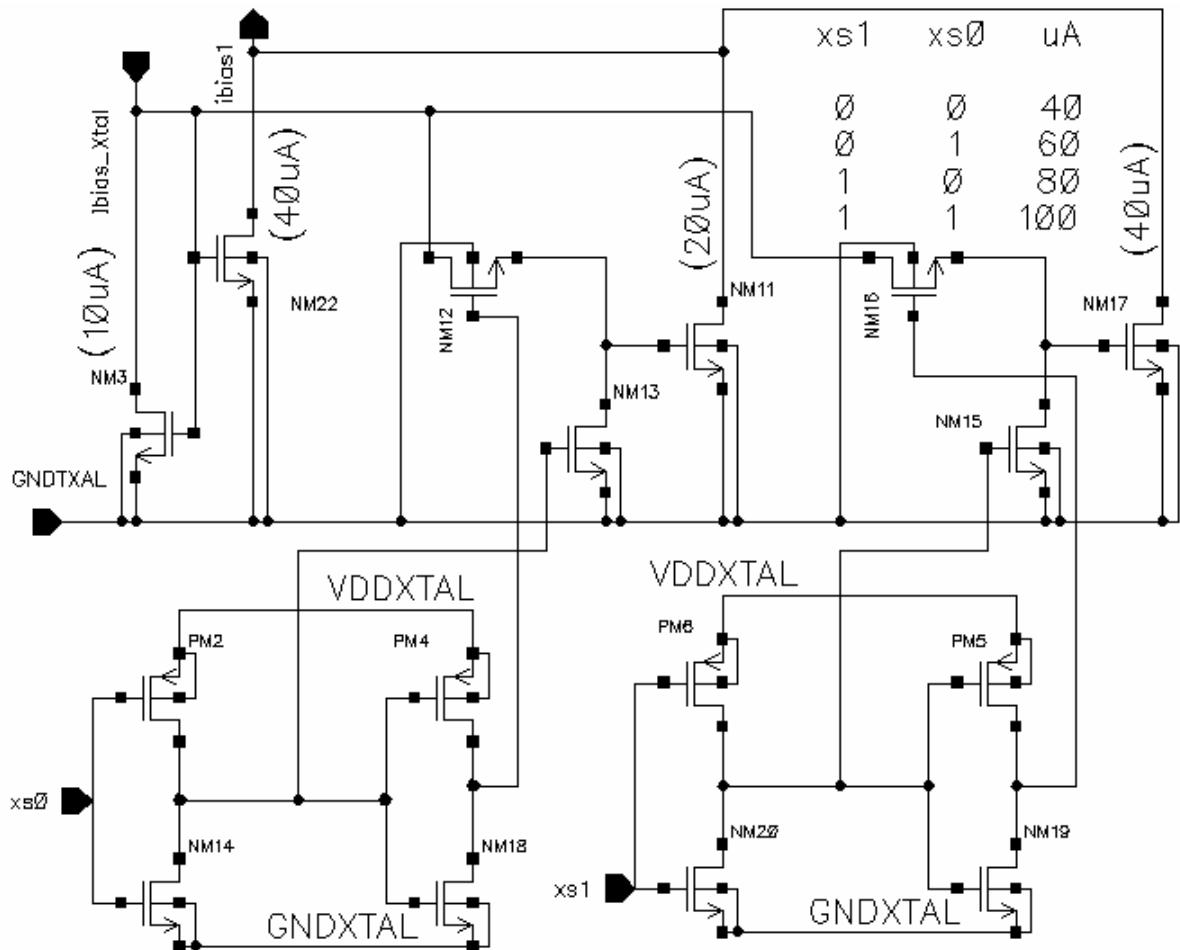

(圖 3.2.3-3) 推薦的石英晶體振盪器電路圖---電流選擇機制

如上圖所示這個電流選擇電路可以提供 40uA、60uA、80uA 及 100uA 等 4 種電流供主放大器使用。以改變主放大器的起振能力以便適應不同的製程變化及各種不同的石英晶體參數，避免 IC 做好了卻無法起振的窘境。(雖然有時候我們經過詳細模擬精算，但是有一句諺語說：人算不如天算。我們還是要留有預防萬一不起振的方法)

### 3.2.4 模擬結果

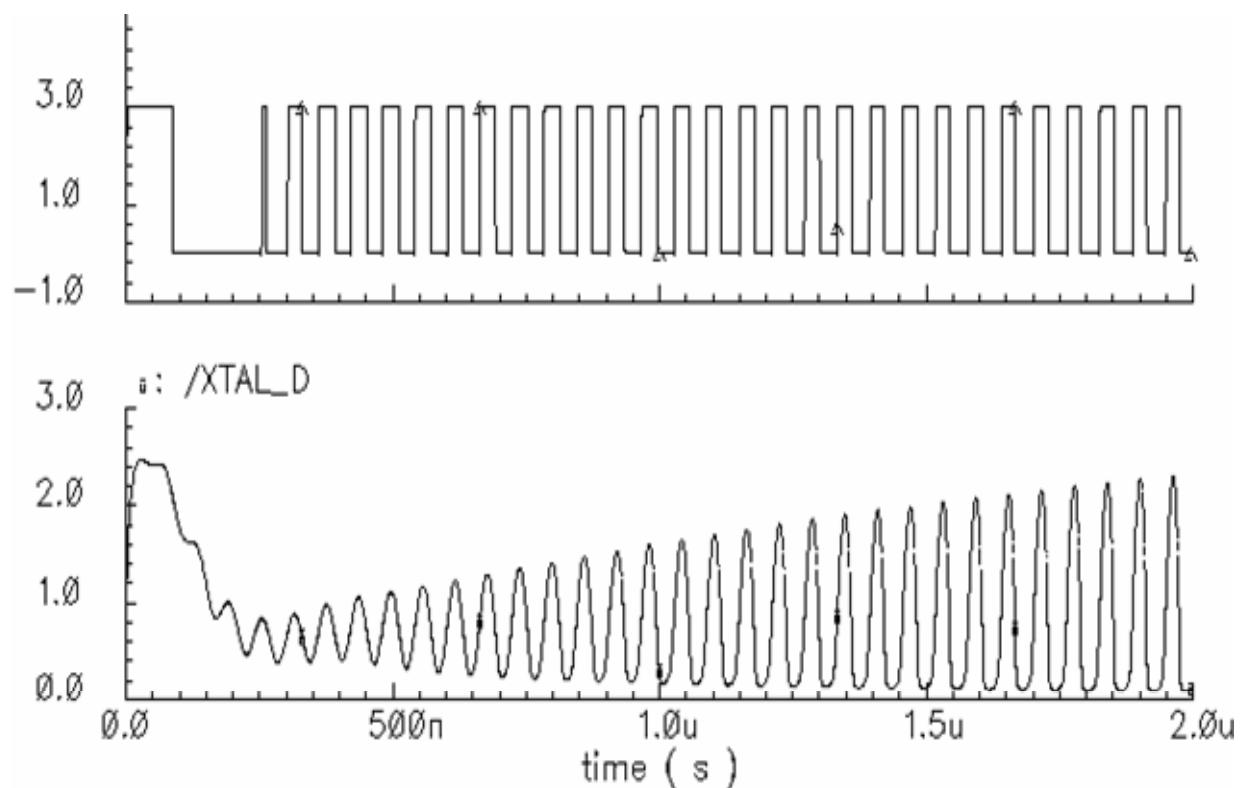

下列二圖(圖 3.2.4 及圖 3.2.4-1)依序展示的是：石英晶體振盪電路的數位化後輸出和類比輸出之模擬結果。類比輸出是石英晶體振盪電路本身的輸出。數位化波型是 I79 限制放大器的輸出，其實此 I79 限制放大器內部僅為三個反向器所組成，我們將反向器當成限制放大器來使用了。下二之模擬結果是在最小號電流 200uA 模式下所得之結果。

: /out

(圖 3.2.4 及圖 3.2.4-1) 石英晶體振盪電路的數位化後輸出和類比輸出之模擬結果

下表(表 3.2.4)展示 4 種電流選擇機制，的石英晶體振盪電路，之總消耗電流。

| 模式：   | Select1 | Select0 | 模擬結果 (此電路總耗電流) | Unit |

|-------|---------|---------|----------------|------|

| 200uA | 0       | 0       | 743            | uA   |

| 300uA | 0       | 1       | 868            | uA   |

| 400uA | 1       | 0       | 992            | uA   |

| 500uA | 1       | 1       | 1150           | uA   |

(表 3.2.4) 石英晶體振盪電路的 DC 總消耗電流模擬結果

我們將規格及模擬結果，一起展示於下(表 3.2.4-1)中。

AC electrical characteristics

Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^{\circ}C$

| Symbol      | Parameter                                                                          | Note | SPEC         | Sim    | Unit      |

|-------------|------------------------------------------------------------------------------------|------|--------------|--------|-----------|

| $f_{XTAL}$  | Recommended Crystal Parameters<br>Frequency<br>$C_{LOAD}$                          | 1    | 16.368<br>12 | 16.368 | MHz<br>pF |

| $t_{START}$ | Oscillator startup time to 95% final amplitude and within 10ppm of final frequency |      | 2            | 0.2    | msec      |

| Duty rate   |                                                                                    |      | 50% +/-5     | 50%    | NA        |

| Amplitude   |                                                                                    |      | 3 +/-0.2     | 3      | V         |

Note 1.石英晶體震盪器的震盪頻率，是依外掛的石英晶體來決定頻率的。

(表 3.2.4-1) 石英晶體振盪電路的 AC 模擬結果

### 3.2.5 此電路設計註解

當然精準的元件模型和計算可以達到最我們的期望，不過這僅是理論值而已。

而且因為我們是 IC 供應者，僅能建議我們的客戶(IC 使用者)採用特定的石英晶體，所以我們可能需要一個調整電流的機制，來適應各種不同的參數的石英晶體。甚至這個電流調整機制，還可能有機會拯救，萬一不幸失效的設計。

### 3.3 前端電路(即LNA+MIXER)

#### 3.3.1 前端電路的規格

我們已於 2.2.1 節中整理出前端電路的設計規格，現在為了方便說明，我們重列(表 2.2.3)於下，以爲此的設計規格之憑據：<sup>[4][5][6][7][9]</sup>

AC electrical characteristics      Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^{\circ}C$

| RF Front-End (LNA/Mixer cascaded) |                       |      |     |     |     |      |

|-----------------------------------|-----------------------|------|-----|-----|-----|------|

| Symbol                            | Parameter             | Note | MIN | TYP | MAX | Unit |

| RF <sub>Gain</sub>                | Front-End Gain        |      | 25  | 29  | 34  | dB   |

| NF                                | Noise Figure          |      |     | 4   | 6   | dB   |

| P <sub>1dB</sub>                  | 1dB Compression point |      | -38 | -35 | -32 | dBm  |

(表 3.3.1) 前端電路的設計規格

#### 3.3.2 典型的前端電路

典型的前端電路細部方塊如下圖(圖 3.3.2-1)，它主要包含一個低雜信放大器(LNA)和一個鏡像拒斥混波器(MIXER)<sup>[3]</sup>，在頻率經過轉換後，它需要兩個雙端轉單端的轉換電路(PP)及輸出緩衝器(BUF)，來推動下一級的電路。

(圖 3.3.2) 典型的前端電路方塊及控制圖

### 3.3.3 推薦的前端電路

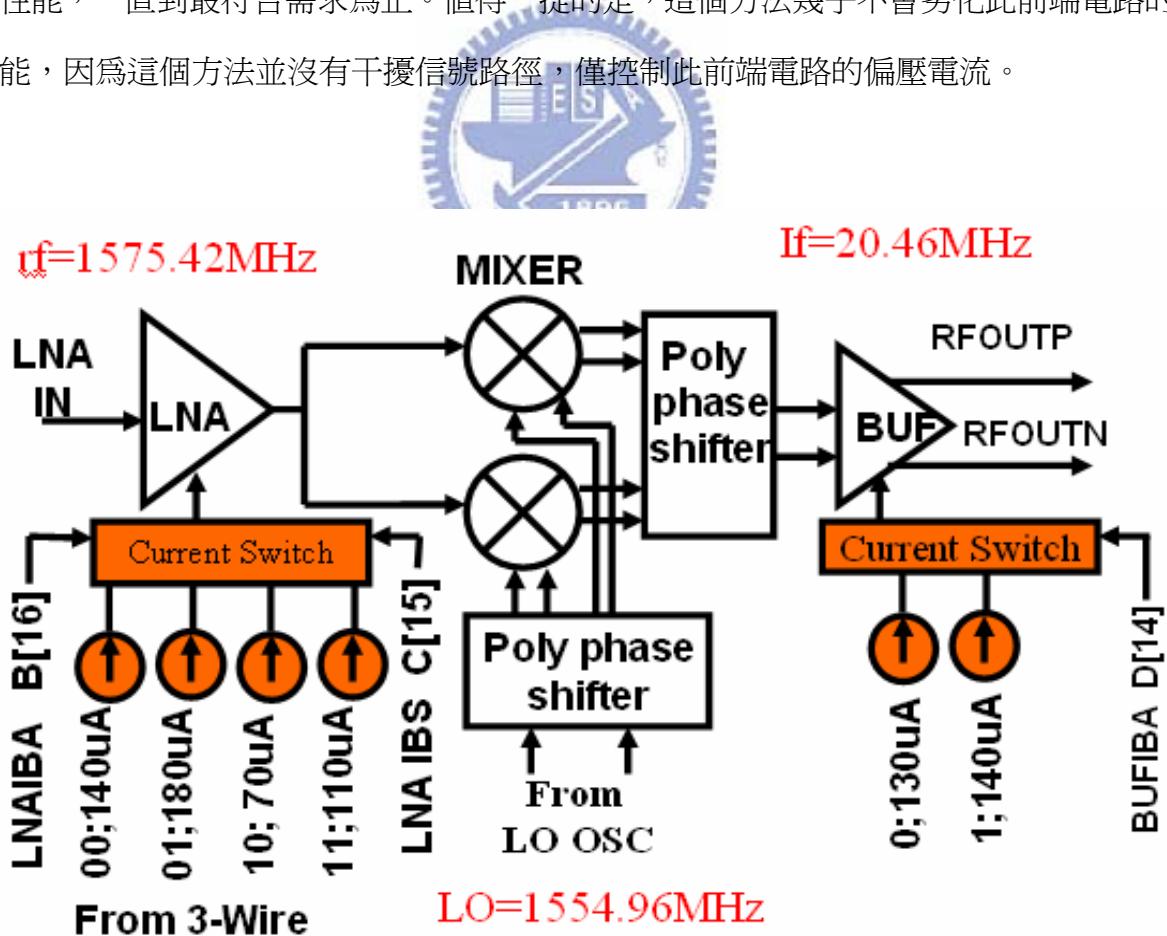

前端電路含有兩個重要的電路，如 LNA 和 MIXER。LNA 之設計我們僅採用了一般單端輸入電路，不過為了讓此 LNA 有良好的接地特性，我們將此接地特別接一支腳到外部來。MIXER 之設計則採用常用的雙端 Gilbert cell 之電路。由於本論文主要目的是在探討 RFIC 的內建測試機制，故對詳細的功能電路未能深入著墨<sup>[3][4][5][6][7][9]</sup>，但亦將 LNA、MIXER 和 Poly phase shift 之電路圖繪出如下，接著我們進入主題來討論此測試機制。

推薦的前端電路結構如下圖(圖 3.3.3-1)，它與傳統的電路差別是：多了一些偏壓電流選擇機制，如標上顏色的方塊。

有了這個機制，在 RF IC 製作完成後，我們就可以使用這些機制來調整此前端電路的性能，一直到最符合需求為止。值得一提的是，這個方法幾乎不會劣化此前端電路的性能，因為這個方法並沒有干擾信號路徑，僅控制此前端電路的偏壓電流。

(圖 3.3.3-1) 推薦的前端電路方塊及控制圖

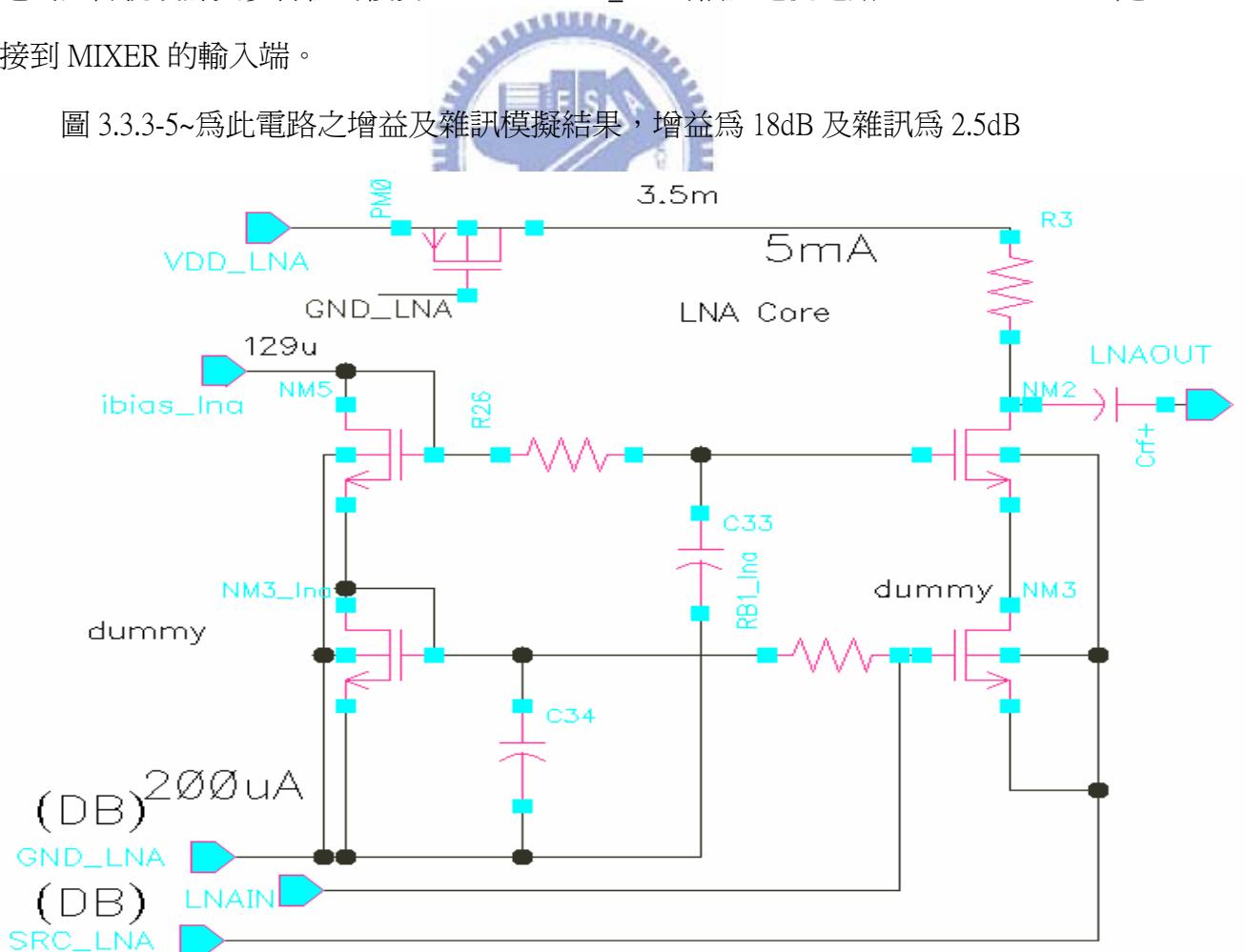

### LNA(低雜信)電路設計考量說明：

此電路主要需求為：求取雜訊與增益的平衡，以達到表 2.2.2 所示增益為 18dB 以上雜訊為 2.5dB 以下的需求。

### LNA(低雜信)電路動作簡要說明：

NM3、NM2 為一 Cascoding Amplifier circuit，此種電路的優點為可以減少米勒效應 (Miller effect) 及擁有好的輸出、輸入絕緣性。我們從 LNA 電路設計<sup>[6]</sup>中得知電晶體最佳寬度  $W_{opt} = (2/3)(LC_{ax}\omega_0 R_s Q_s, opt)$  之觀念再配合模擬以設計出雜訊與增益平衡的 LNA 電路。

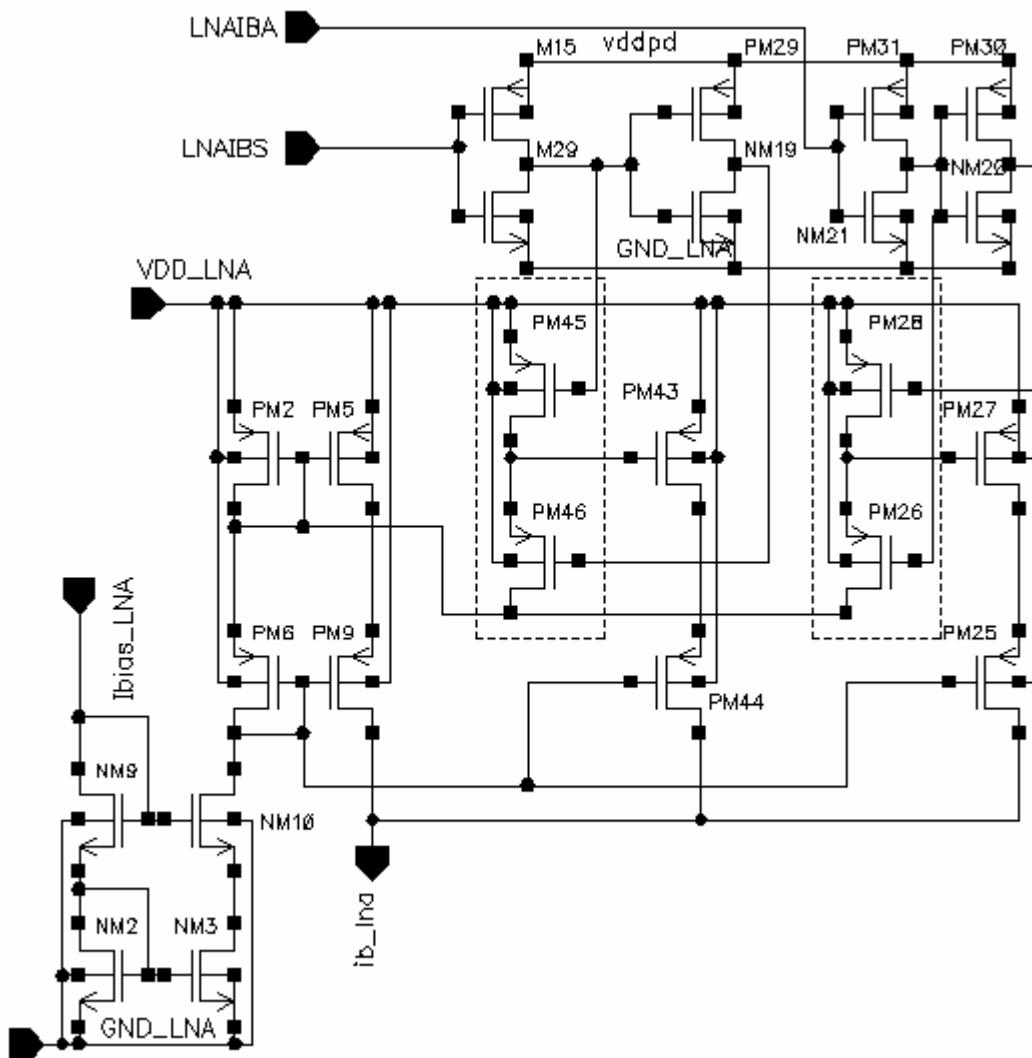

從圖 3.3.3-2 中我們可以看到有一個電流輸出 PORT(ib\_lna)，這個 PORT 是連接到此電路的 ibias\_lna，以便控制此 LNA<sup>[17]</sup>的偏壓電流，使得此 LNA 的特性得以被改變，以達到比傳統設計更多特性的優勢。NM5、NM3\_lna 為偏壓電流電路。LNAOUT PORT 是接到 MIXER 的輸入端。

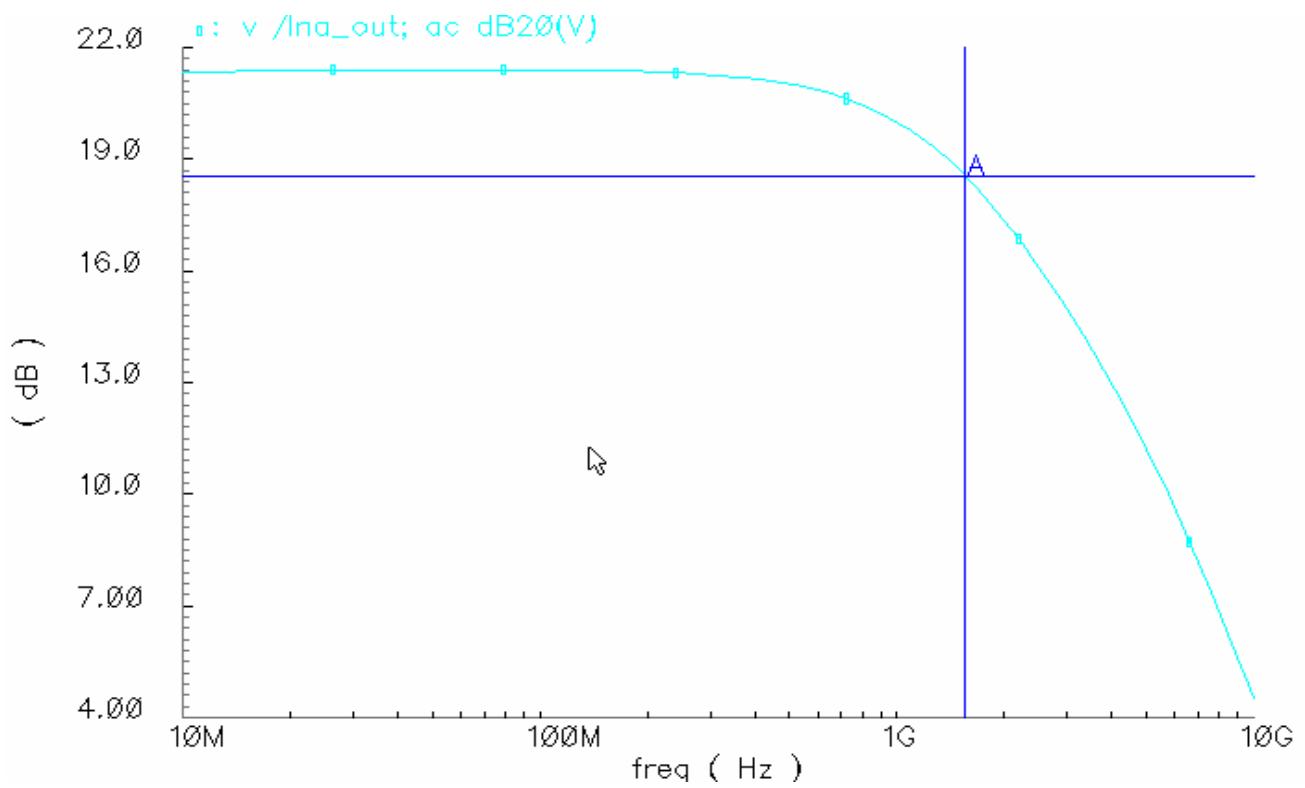

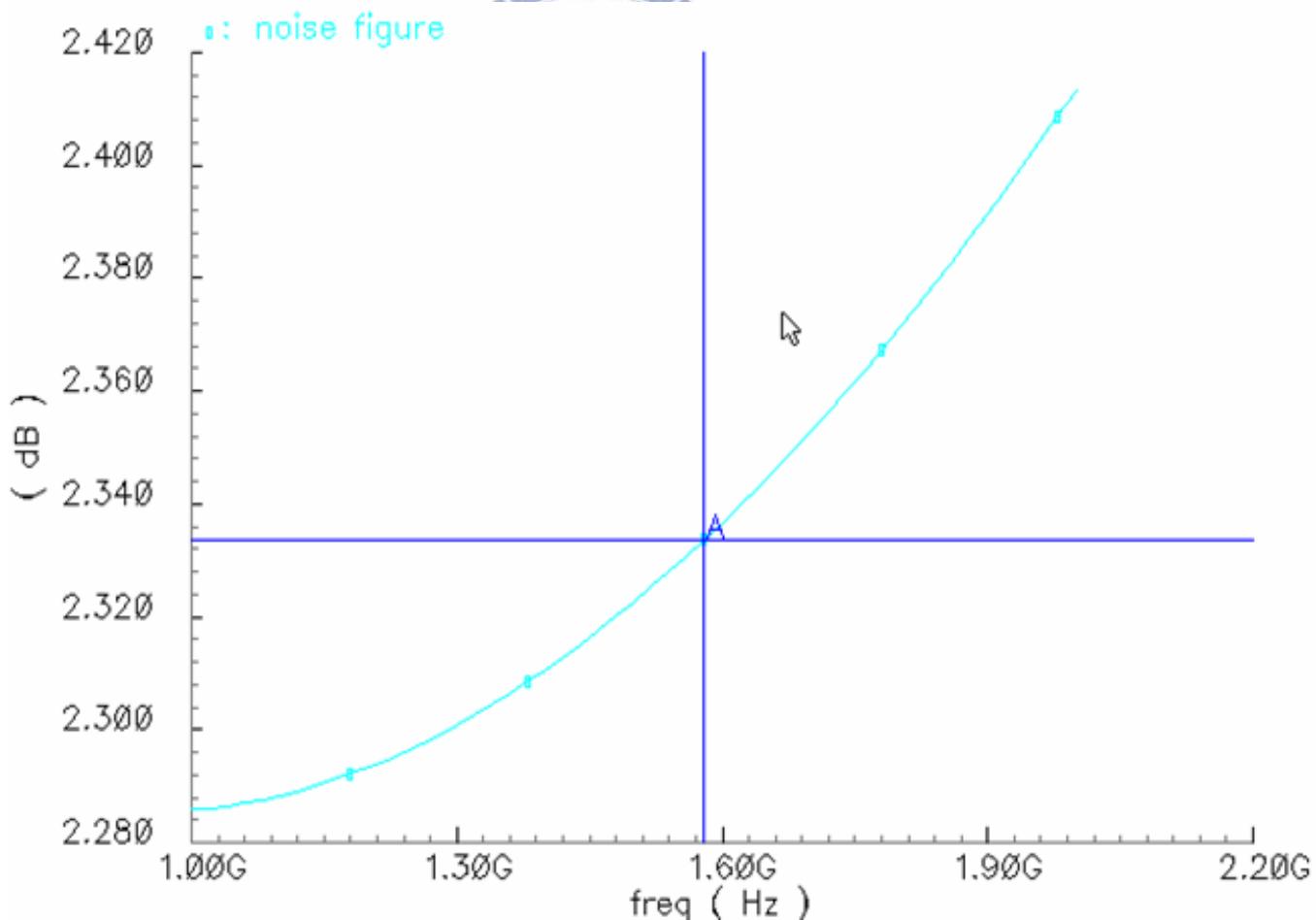

圖 3.3.3-5~為此電路之增益及雜訊模擬結果，增益為 18dB 及雜訊為 2.5dB

(圖 3.3.3-4) LNA Core circuit

(圖 3.3.3-5) LNA Gain simulation result

(圖 3.3.3-6) LNA Noise simulation result

### 電流選擇電路簡要說明：

我們為了調整前端電路的性能，故設計此一電流選擇機制。我們可以操作 LNAIBA 及 LNAIBS 的邏輯狀態，來決定  $ib_{lna}$  之電流大小，並調整前端電路的性能( $ib_{lna}$  是接到 LNA 之電流境  $ibias_{lna}$ )。

當邏輯輸入為 1,0 時則送到 LNA 的偏壓電流為最小(70uA)，如(表 3.3.4 模擬結果)所示。若邏輯輸入為 0,1 時則送到 LNA 的偏壓電流為最大(180uA)。如此我們即可擁有改變 LNA 特性的四個機會，比傳統的單一特性機會多了三個。

(圖 3.3.3-2) 推薦的前端電路----LNA 的電流選擇機制

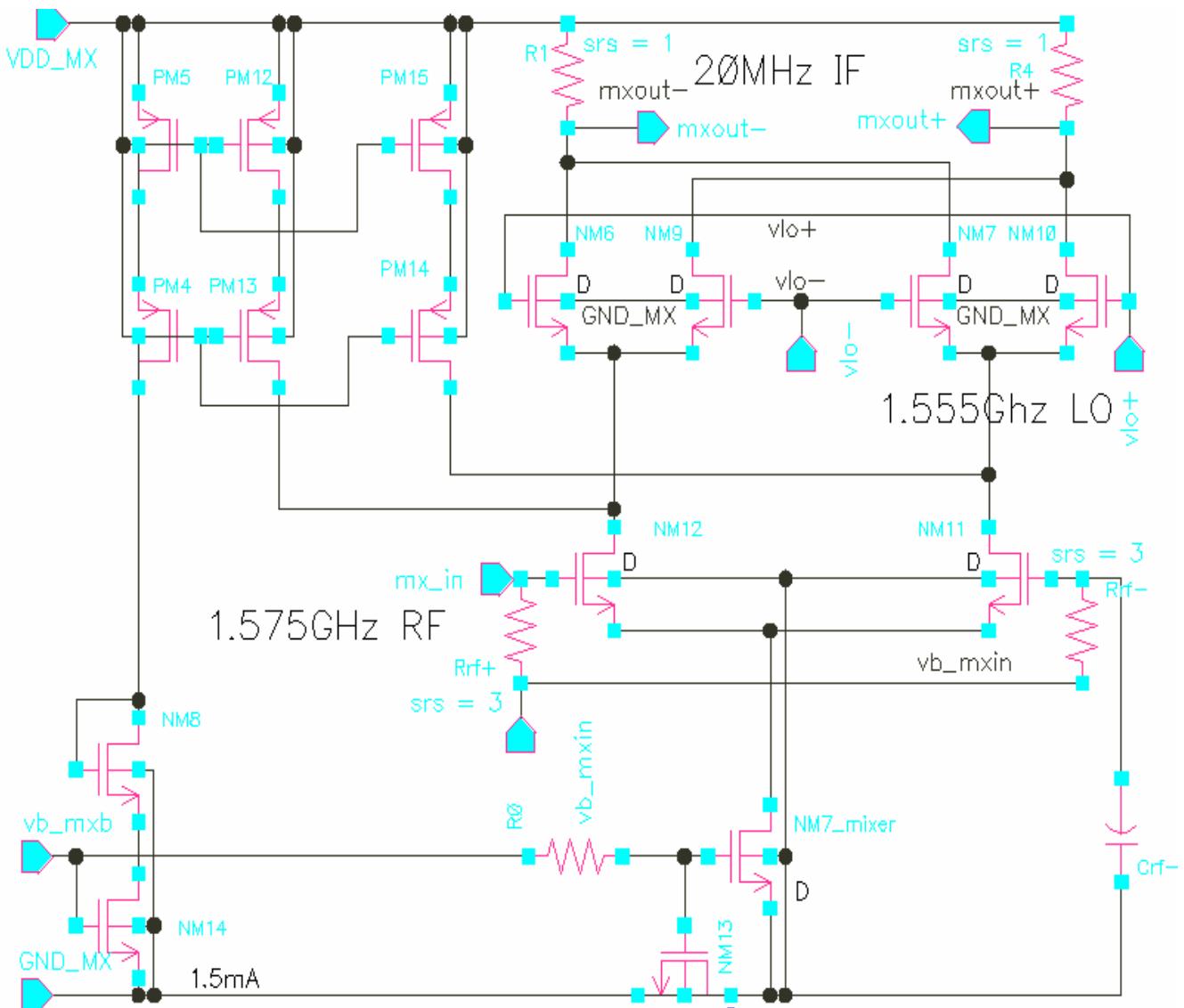

### MIXER 電路設計考量說明：

此電路主要需求為：求取高的轉換增益。依表 2.2.2 所示需要 11dB 的功率增益，唯因系統上使用了兩組 MIXER 電路，所以單一 MIXER 電路需要 8dB 以上的增益即可滿足系統需求。(兩組電路之振幅為一組的兩倍，所以可以增加 3dB)

我們使用 P1dB 來衡量此電路的線性工作範圍。假設 LNA 端的輸入信號小於 -40dBm，則此電路之 P1dB 為 -20dBm 即可滿足系統所需。

### MIXER 電路簡要說明：

此為傳統的主動式混波器[17]，NM 6、NM7、NM9、NM10 為混波器，NM11、NM12 連接到 LNA 的輸出端。因為 LNA 為單端輸出所以 NM11 的閘級用電容接地，以便將此單端信號轉換成雙端信號。

(圖 3.3.3-7) MIXER Core circuit

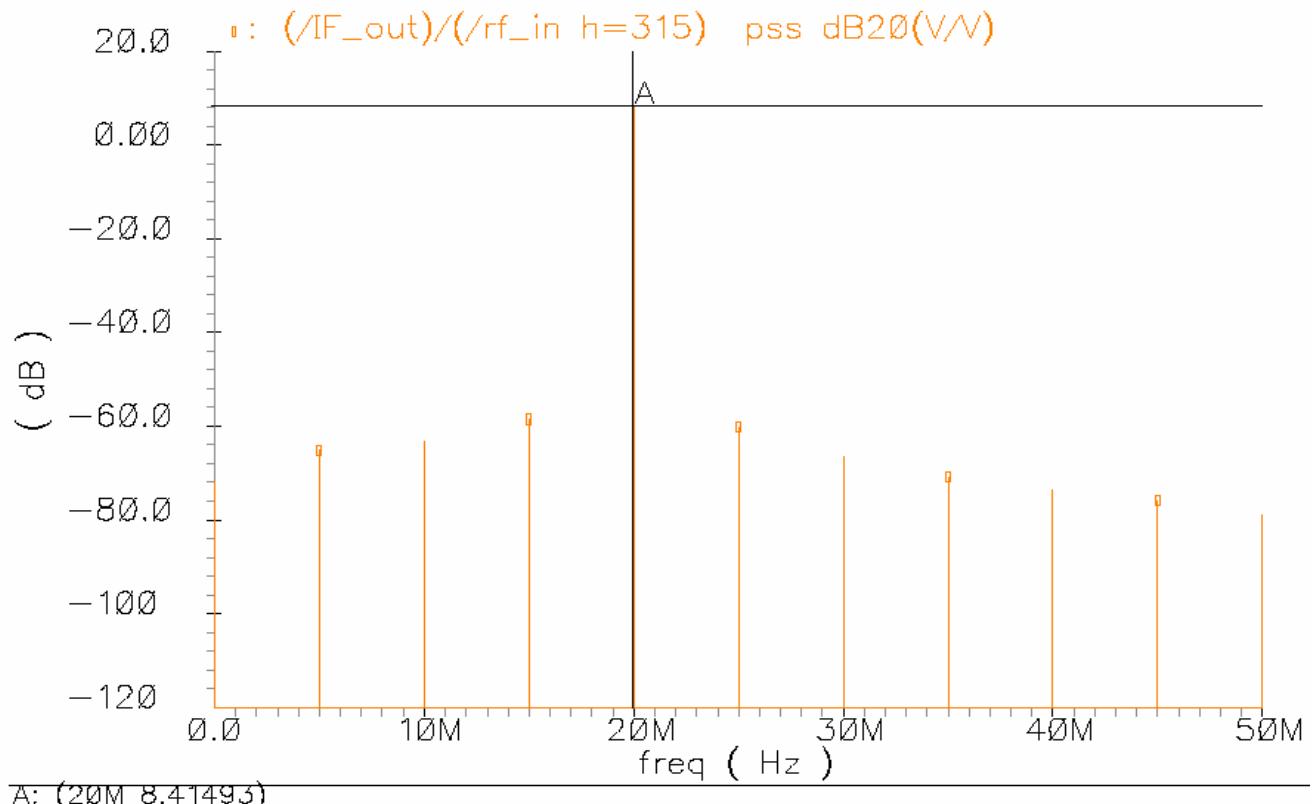

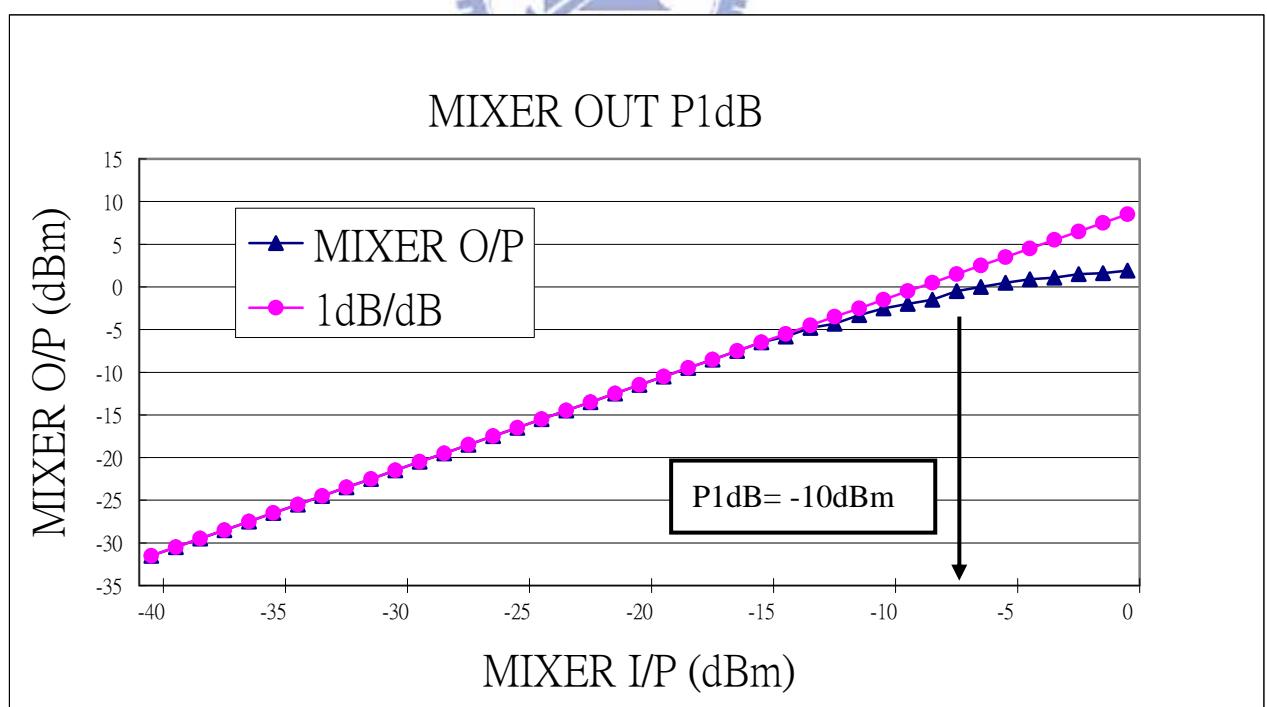

從下二圖中我們可以看出此 Mixer，具有 8.4dB 的轉換增益性能。它的 P1dB

約在-10dBm。我們將以此 Mixer 擔任降 RF 到 IF 的工作。

(圖 3.3.3-8) Simulation result for MIXER conversion gain

(圖 3.3.3-9) Simulation result for MIXER P1dB=-10dBm

### Poly phase shifter<sup>[17]</sup>電路動作簡要說明：

此為傳統的相位  $90^\circ$  移動器<sup>[17]</sup>。它將輸入信號轉  $90^\circ$  後輸出。它的信號損失約為  $1\text{dB}$ 。

(圖 3.3.3-6) Poly phase shifter Core circuit

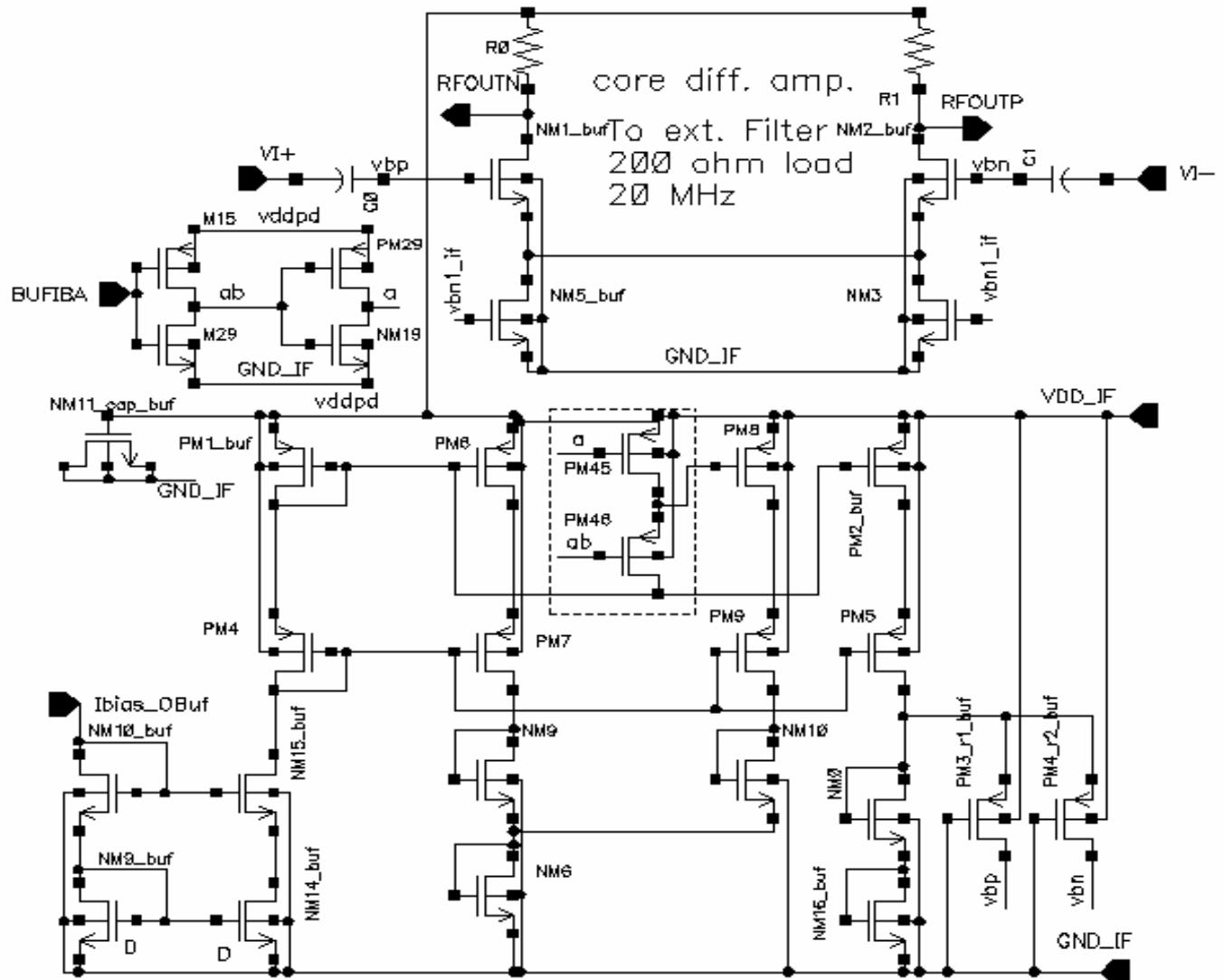

## Buffer 電路簡要說明：

此電流選擇機制是調整  $v_{bp}$ 、 $v_{bn}$  的電壓，進而調整輸出電路的驅動能力。此電路有兩個操作狀態，即是設定 BUFIBA 為邏輯 high 或 low. 當邏輯 High 時 Buffer(Core diff amp) 則消耗比較大的電流，若為邏輯 Low 時 Buffer(Core diff amp) 則消耗比較小的電流。如此我們又擁有兩個不同的電路特性了。

組合 LNA 與 Buffer 兩種電路特性，我們總共可以得到八個特性，比傳統單一特性的做法多了七個特性。

在使用最經濟電流之下，它的電壓增益約為 1dB。剛好補足 Poly phase shifter<sup>[17]</sup>電路的損失。

(圖 3.3.3-3) 推薦的前端電路---Buffer of Mixer 的電流選擇機制

### 3.3.4 前端電路(LNA+MIXER)的模擬結果

| Input control signal            |                               |                           | Simulation Result         |               |                                       |                      |                                       |

|---------------------------------|-------------------------------|---------------------------|---------------------------|---------------|---------------------------------------|----------------------|---------------------------------------|

| LNA<br>Low<br>bias-BS<br>B [16] | LNA High<br>bias_BA<br>C [15] | Mixer<br>BUFIBA<br>D [14] | DC current<br>Consumption |               | RF <sub>Gain</sub><br>SPEC>29<br>(dB) | NF<br>SPEC<6<br>(dB) | P <sub>1dB</sub><br>SPEC>-32<br>(dBm) |

|                                 |                               |                           | LNA<br>(mA)               | MIXER<br>(mA) |                                       |                      |                                       |

| 0                               | 0                             | 0                         | 3.95                      | 11.86         | 32                                    | 4.1                  | -32                                   |

| 0                               | 0                             | 1                         | 3.95                      | 12.9          | 32                                    | 4.0                  | -30                                   |

| 0                               | 1                             | 0                         | 4.94                      | 11.86         | 33                                    | 3.7                  | -32                                   |

| 0                               | 1                             | 1                         | 4.94                      | 12.9          | 33                                    | 3.6                  | -30                                   |

| 1                               | 0                             | 0                         | 2.09                      | 11.86         | 29                                    | 5.8                  | -27                                   |

| 1                               | 0                             | 1                         | 2.09                      | 12.9          | 29                                    | 5.7                  | -27                                   |

| 1                               | 1                             | 0                         | 3.17                      | 11.86         | 31                                    | 4.6                  | -29                                   |

| 1                               | 1                             | 1                         | 3.17                      | 12.9          | 31                                    | 4.3                  | -29                                   |

(表 3.3.4)前端電路模擬結果整理表

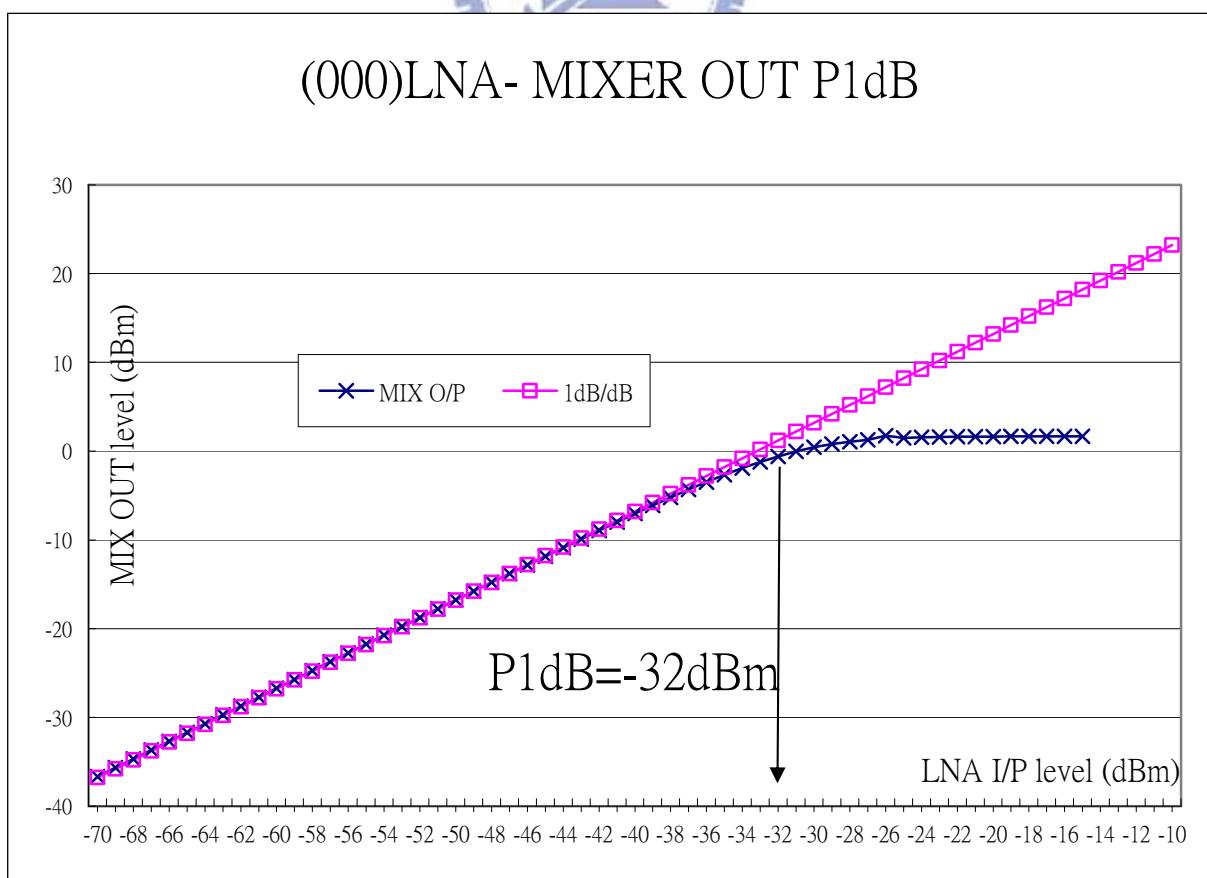

利用模擬軟體將前端電路的 P<sub>1dB</sub> 模擬曲線圖展示於(圖 3.3.4)中。

(圖 3.3.4)前端電路的 P1dB 模擬曲線圖

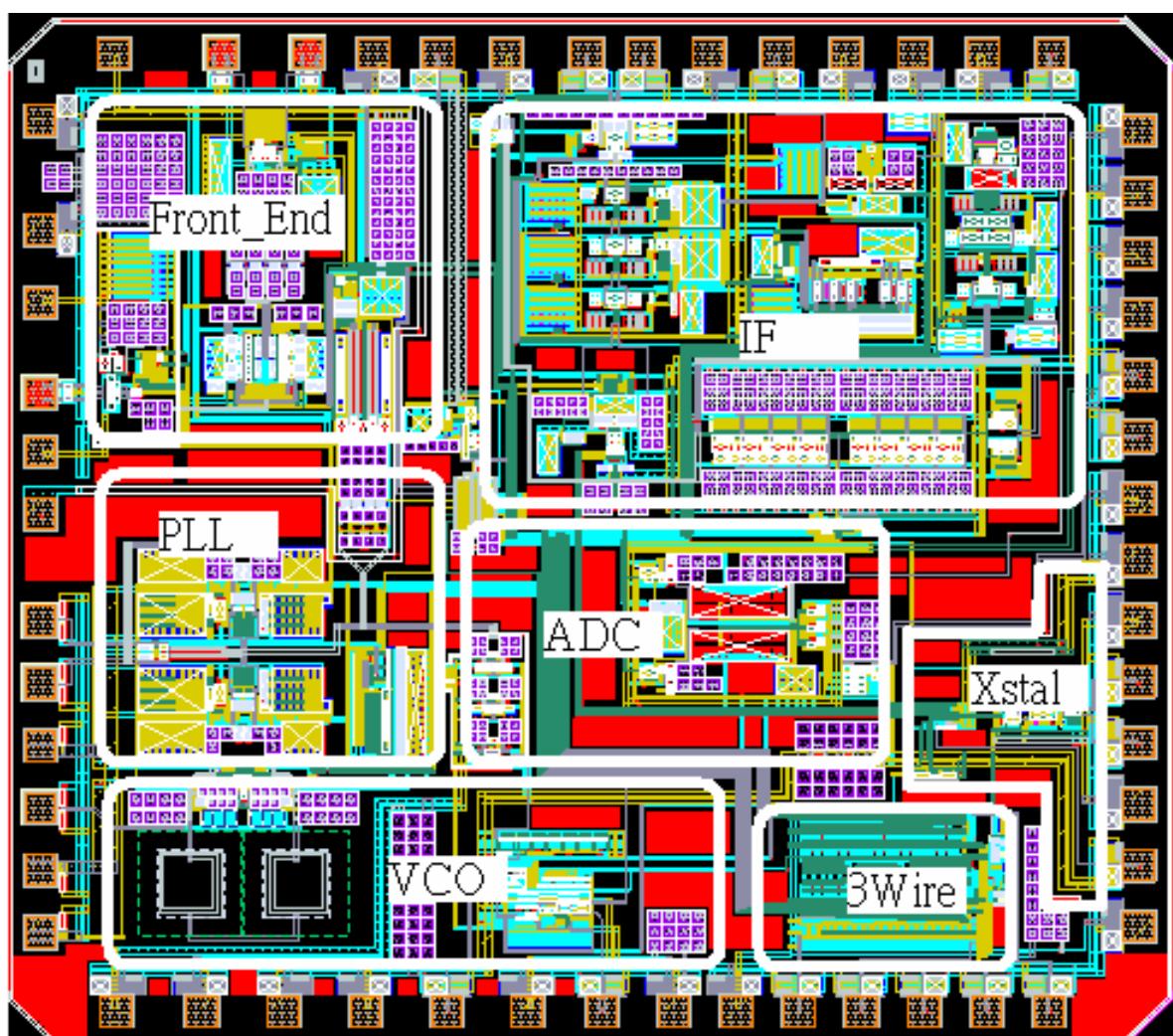

### 3.4 佈線圖

我們將整顆 RF IC 的佈線圖，展示於下圖(圖 3.4)。

本論文有論述的部分是：上半部左邊是前端電路，左中是石英晶體的振盪電路。左下是本地振盪電路。

本論文沒有論述的部分是：上半部右邊是中頻電路，中心是 ADC(類比信號轉數位信號)，右中是 PLL(本地振盪器的頻率鎖定器)，右下是 3Wire(電路控制中樞)。

(圖 3.4)RF IC 的佈線圖

此晶片使用台灣積體電路公司之 CMOS 0.25um 製程。

雖然由於實驗室的人力資源有限，我們無法將所有的 Section 論述完畢，但是為了收到衛星信號，我們還是把 RF IC 應有的 Section 完成，只是有些 Section 未出現在論述

中。

## 四、實驗部分

### 4.1本地振盪電路的量測

#### 4.1.1 實驗的量測配置圖及量測結果

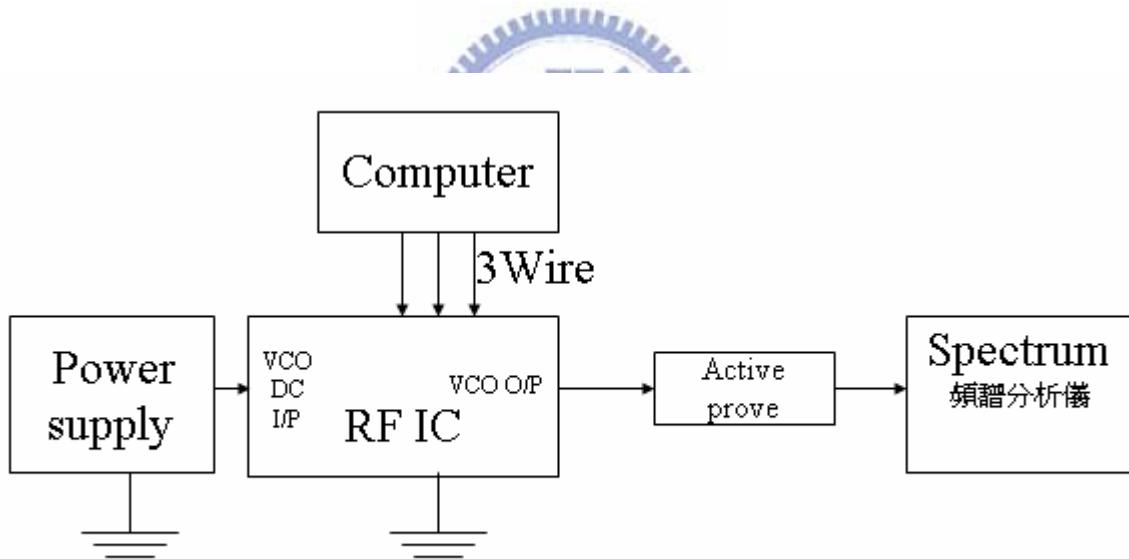

(圖 4.1.1) 為本地振盪電路的量測配置圖，我們將依照此配置圖來量得本地振盪電路的有關數據。

(表 4.1.1) 為八個頻帶的控制電壓及對應震盪頻率的量測結果。

(表 4.1.1-1) 為八個頻帶的 Phase noise test result table。

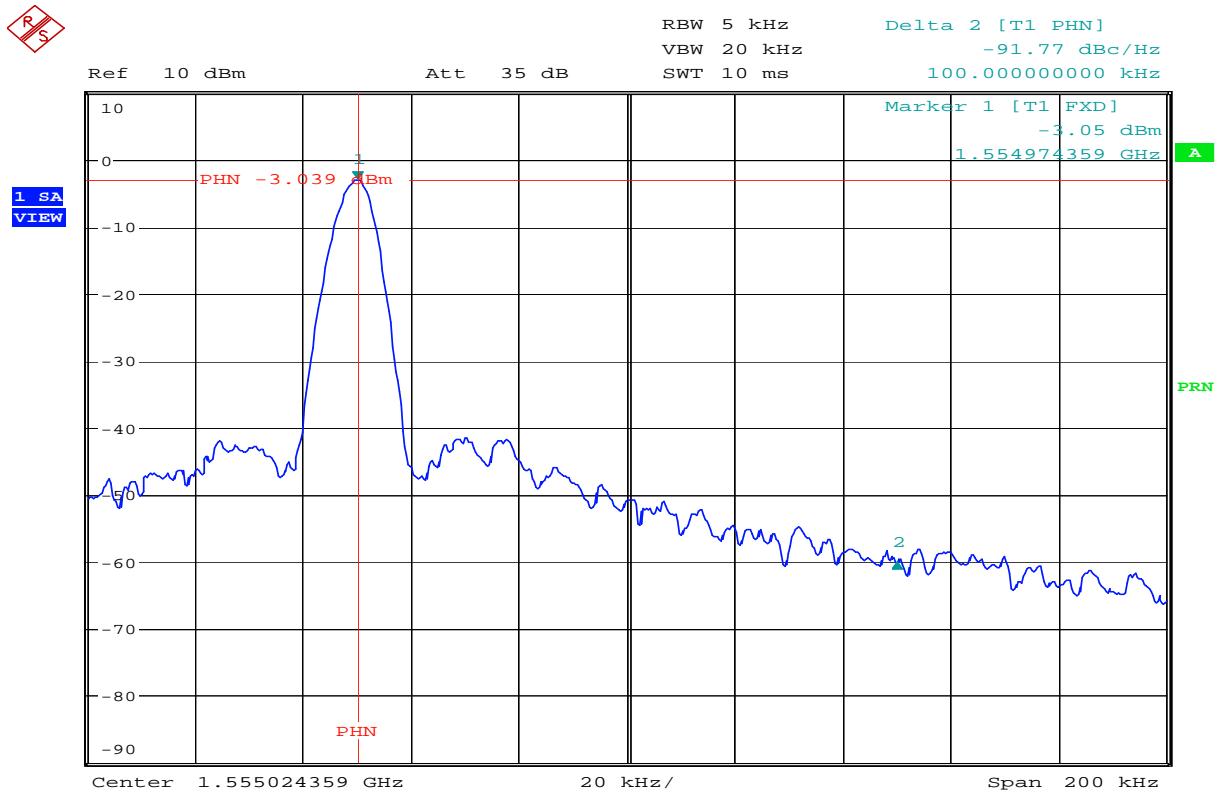

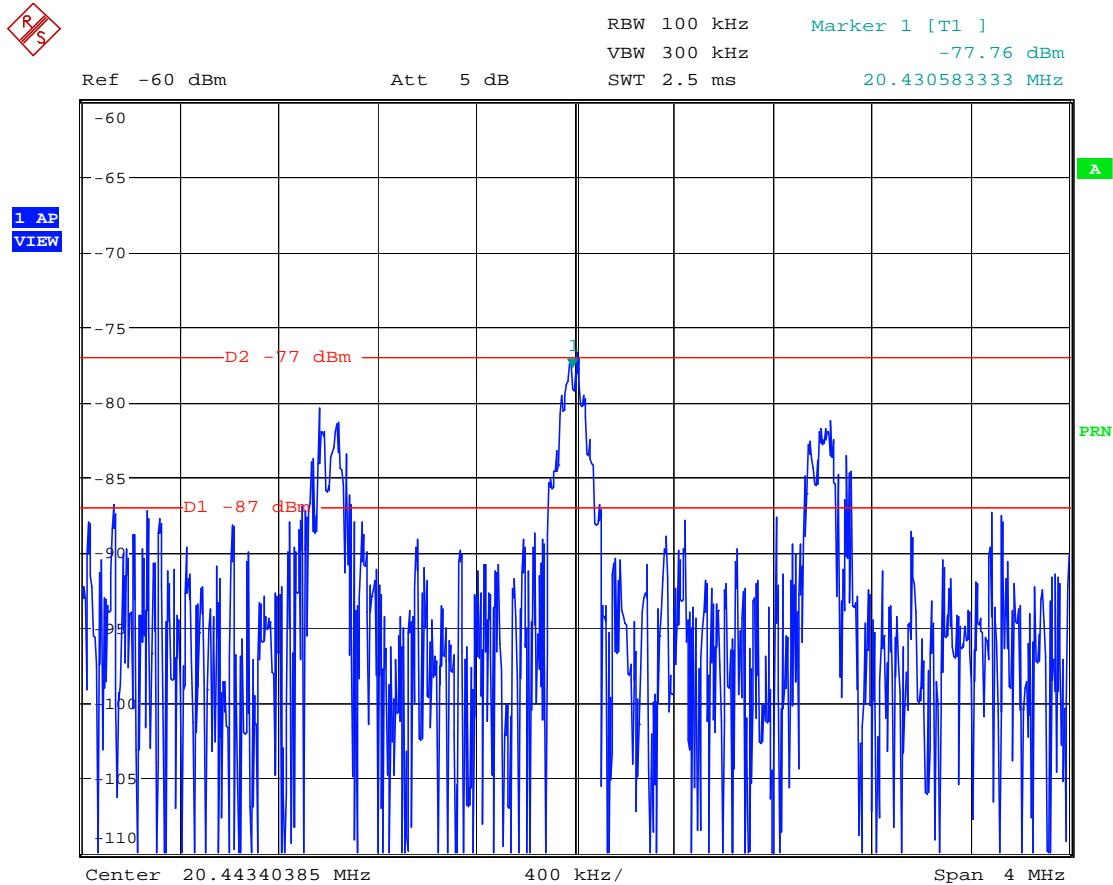

(圖 4.1.1-1) 為本地振盪器其相位雜訊在 100KHz 處之量測結果曲線圖

(圖 4.1.1) 本地振盪電路的量測配置圖

(圖 4.1.1-1) 推薦的本地振盪器其相位雜訊在 100KHz 處之量測結果曲線圖

| Offset | Specifications | Simulation Result | Test result | Unit   |

|--------|----------------|-------------------|-------------|--------|

| 10KHz  | -75            | -81               | -78         | dBc/Hz |

| 100KHz | -80            | -111              | -92         | dBc/Hz |

| 1MHz   | -105           | -133              | -110        | dBc/Hz |

| 2MHz   | Na             | -139              | -112        | dBc/Hz |

(表 4.1.1-1)Phase noise test result table

| Band<br>F2 F1F0 |      | Frequency result Unit=(MHz) |             |             |      |             |               |                       |

|-----------------|------|-----------------------------|-------------|-------------|------|-------------|---------------|-----------------------|

|                 |      | Vt=0.7V                     |             | Vt=1.5V     |      | Vt=2.8V     |               | KVCO<br>(MHz/V)       |

|                 | Sim  | Test                        | Sim         | Test        | Sim  | Test        | Sim<br>AVG=29 | Test<br><b>AVG=32</b> |

| 0 0 0           | 1665 | <b>1767</b>                 | 1702        | <b>1810</b> | 1741 | <b>1853</b> | 36.3          | <b>41</b>             |

| 0 0 1           | 1627 | <b>1721</b>                 | 1662        | <b>1762</b> | 1699 | <b>1801</b> | 34            | <b>38</b>             |

| 0 1 0           | 1588 | <b>1676</b>                 | 1620        | <b>1713</b> | 1654 | <b>1750</b> | 31            | <b>35</b>             |

| 0 1 1           | 1555 | <b>1637</b>                 | 1586        | <b>1671</b> | 1618 | <b>1705</b> | 30            | <b>32</b>             |

| 1 0 0           | 1517 | <b>1596</b>                 | <u>1545</u> | <b>1628</b> | 1575 | <b>1659</b> | 27.6          | <b>30</b>             |

| 1 0 1           | 1488 | <b>1561</b>                 | 1515        | <b>1591</b> | 1543 | <b>1620</b> | 26.2          | <b>28</b>             |

| 1 1 0           | 1457 | <b>1526</b>                 | 1483        | <u>1554</u> | 1509 | <b>1582</b> | 24.76         | <b>27</b>             |

| 1 1 1           | 1431 | <b>1496</b>                 | 1456        | <b>1522</b> | 1481 | <b>1548</b> | 23.8          | <b>25</b>             |

(表 4.1.1-2) Frequency test result

(表 4.1)所示為本地振盪電路的量測結果匯整表，我們將於本章下列的子章節中重點式的描述其量測過程及圖形。並且說明一些模擬與量測間的誤差原因。

AC electrical characteristics

Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^\circ C$

| VCO and Local Oscillator |                                     |                 |                   |                |        |

|--------------------------|-------------------------------------|-----------------|-------------------|----------------|--------|

| Symbol                   | Parameter                           | SPEC            | Simulation result | Test result    | Unit   |

| $f_{LO}$                 | LO Center Frequency                 | 1554.96 +/-0.01 | Na                | <b>1554.96</b> | MHz    |

| $K_{VCO}$                | VCO Gain                            | 30+/-10         | 29.2              | <b>32</b>      | MHz/V  |

| $f_{LOlevel}$            | LO output level                     | >-5             | 0                 | <b>-3</b>      | dBm    |

| $L_{10K}$                | LO SSB Phase Noise at 10KHz Offset  | <-75            | -81               | <b>-78</b>     | dBc/Hz |

| $L_{100K}$               | LO SSB Phase Noise at 100KHz Offset | <-80            | -111              | <b>-92</b>     | dBc/Hz |

| $L_{1M}$                 | LO SSB Phase Noise at 1MHz Offset   | <-105           | -133              | <b>-110</b>    | dBc/Hz |

| $L_{2M}$                 | LO SSB Phase Noise at 2MHz Offset   | Na              | -139              | <b>-112</b>    | dBc/Hz |

(表 4.1)本地振盪電路的各種量測結果匯整表

## 4.2 石英晶體振盪電路量測

### 4.2.1 石英晶體振盪電路的量測配置及量測圖形

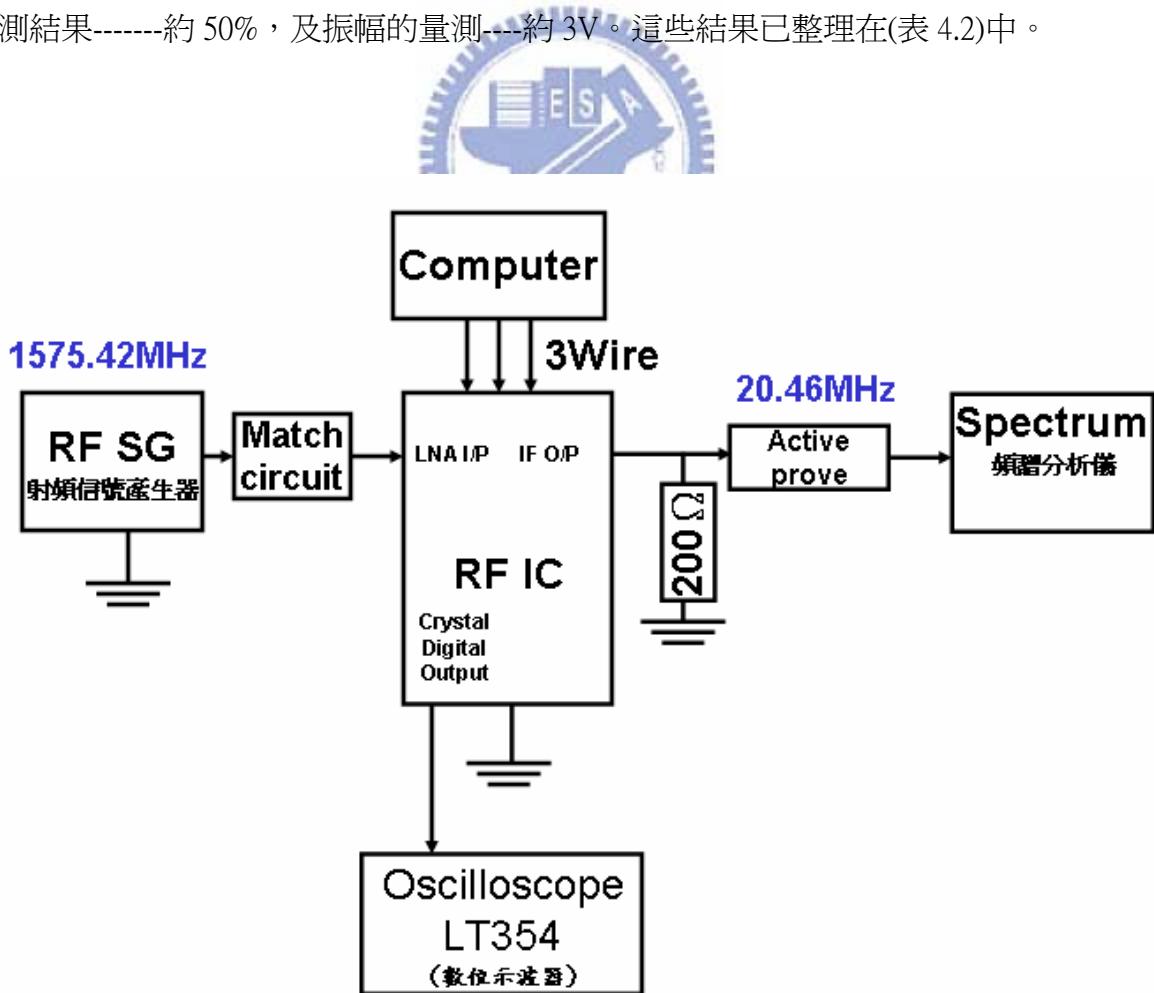

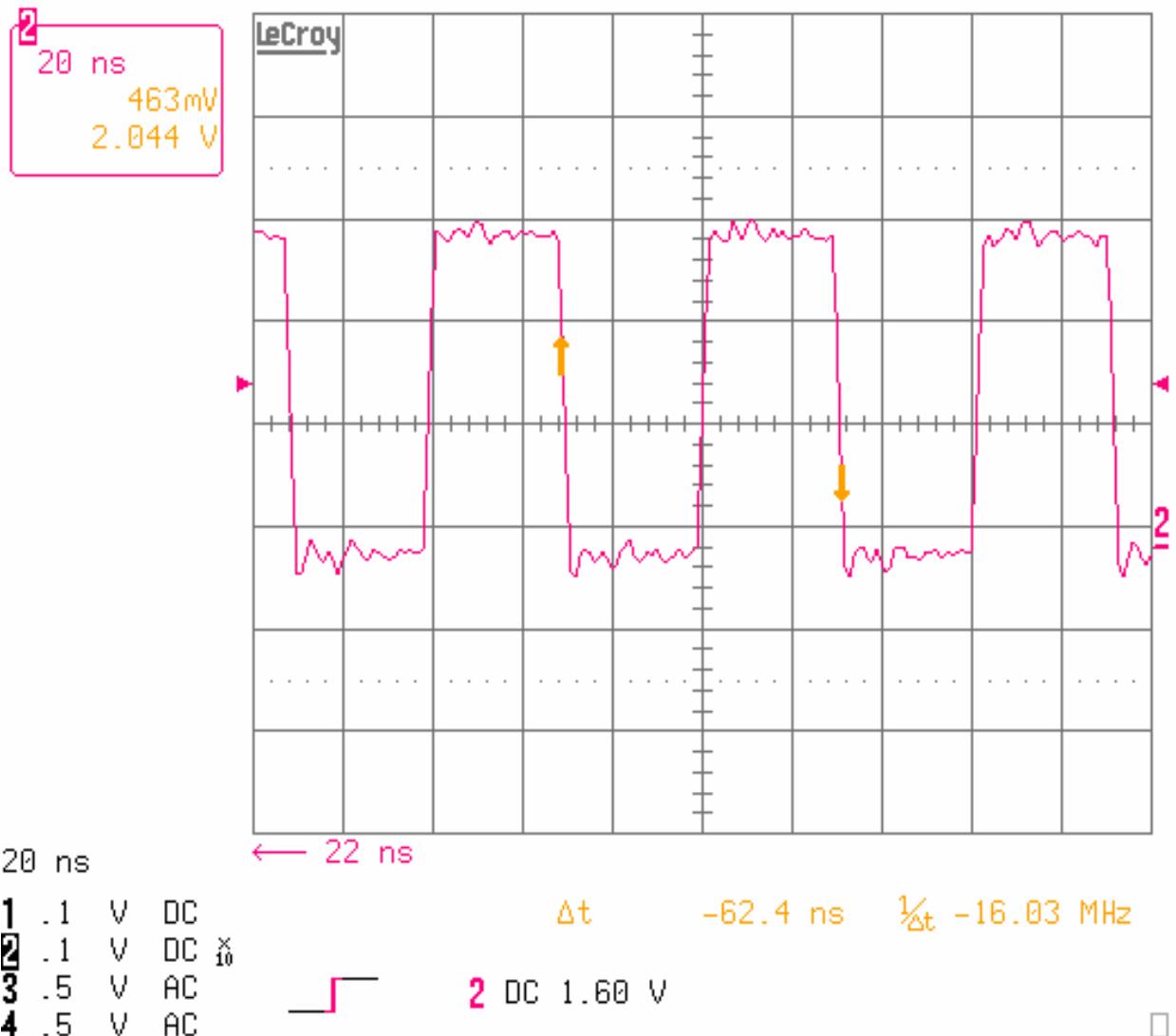

(圖 4.2.1)是此部分 RF IC 之量測配置圖，我們將依照此配置圖來量得石英晶體振盪電路的有關數據。電流的選擇模式在佈線(Layout)時已設定到 300uA 的狀態，即 Select1=0, Select0=1。因為這個電路比較單純，所以我們只用佈線(Layout)來選到 300uA 的狀態，待有需要改變的時候，可以用 MATEL Change 來改變。

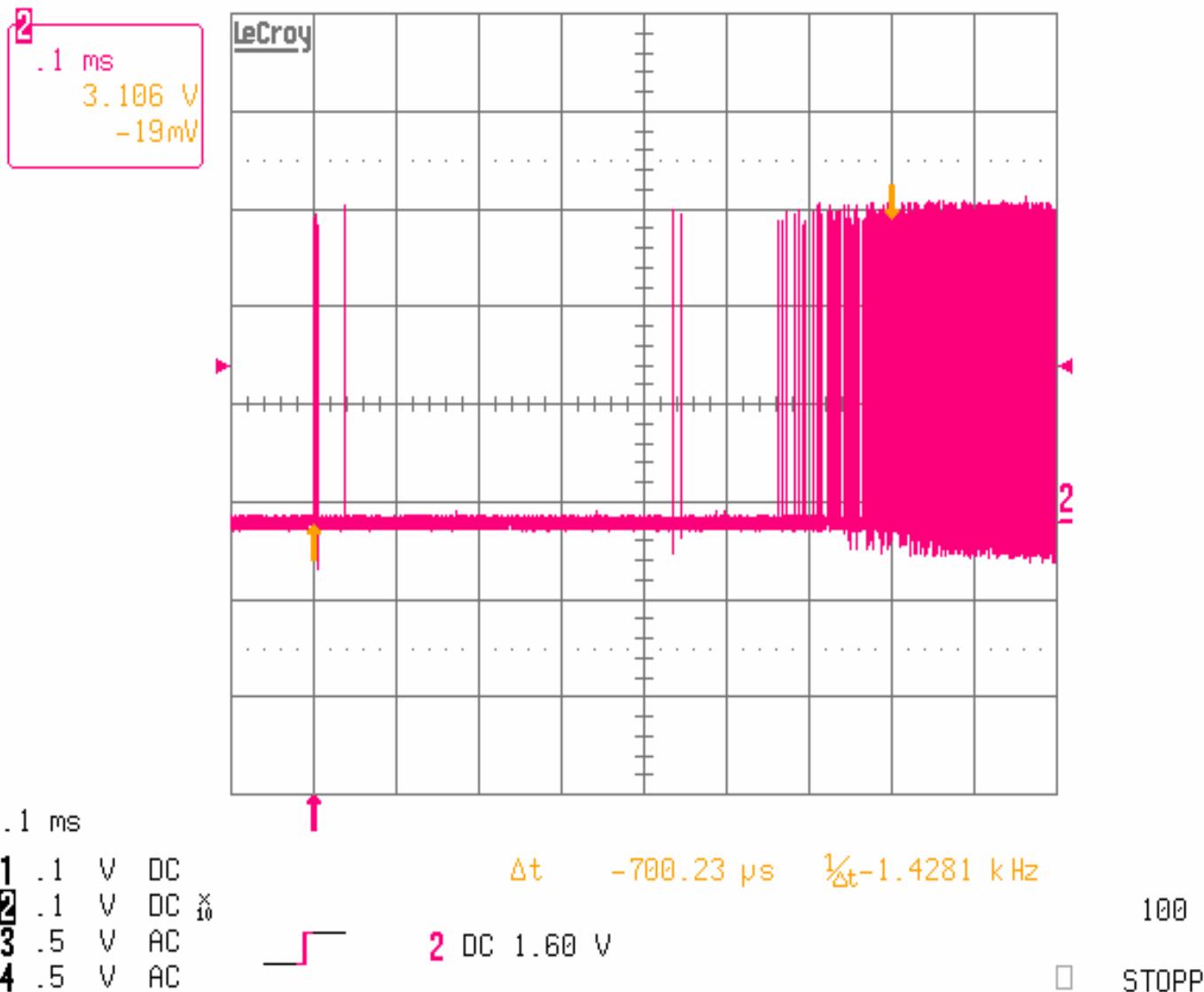

我們量測起振時間的方法為：先用 3Wire 將此電路的偏壓電流關掉，然後再用原 3Wire 啓動此電路的偏壓電流，如此我們就可以觀測到此電路的起振時間了。如(圖 4.2.1-1)所示之石英晶體振盪電路的起振時間之量測結果-----約 0.7mS。

我們量測 Duty rate 及振幅的結果如(圖 4.2.1-2)所示之石英晶體振盪電路的 Duty rate 量測結果-----約 50%，及振幅的量測----約 3V。這些結果已整理在(表 4.2)中。

(圖 4.2.1) 石英晶體振盪電路的量測配置圖

示波器畫面說明:當電源打開瞬間,示波即被觸發(視窗的左下方箭頭向上處),一直到 700 $\mu$ s 時我們見波形已開始穩定輸出,所以將此值填入(表 4.2)中。

13-Apr-05

18:50:24

### Reading Floppy Disk Drive

(圖 4.2.1-1) 石英晶體振盪電路的起振時間之量測結果-----約 0.7mS

示波器畫面說明:我們檢視上半波及下半波所占面積約各佔 50%。

13-Apr-05      Reading Floppy Disk Drive

18:57:51

(圖 4.2.1-2) 石英晶體振盪電路的 Duty rate 量測結果-----約 50%，及振幅的量測---約 3V。

(表 4.2)是我們的量測結果，在本章的下列子章節中我們將部份描述這些量測的設定及量測結果圖。

AC electrical characteristics

Conditions:  $V_{CC}=V_{DD}=3.0V, T_A=25^\circ C$

| Crystal Oscillator |                                                                                    |      |              |              |        |           |

|--------------------|------------------------------------------------------------------------------------|------|--------------|--------------|--------|-----------|

| Symbol             | Parameter                                                                          | Note | SPEC         | Sim          | Test   | Unit      |

| $f_{XTAL}$         | Recommended Crystal Parameters<br>Frequency<br>$C_{LOAD}$                          | 1    | 16.368<br>12 | 16.368<br>12 | 16.368 | MHz<br>pF |

| $t_{START}$        | Oscillator startup time to 95% final amplitude and within 10ppm of final frequency |      | 2            | 0.2          | 0.7    | msec      |

| Duty rate          |                                                                                    |      | 50% +/- 5    | 50%          | 50%    | NA        |

| Amplitude          |                                                                                    |      | 3 +/- 0.2    | 3            | 3      | V         |

Note 1.石英晶體震盪器的震盪頻率，是依外掛的石英晶體來決定頻率的。

(表 4.2) 石英晶體振盪電路的量測結果

### 4.3 Front End 實驗結果

我們先將前端電路的一些量測結果匯整於(表 4.3)中，再於下列子章節中敘述這些量測的過程。

在(表 4.3)中的 Sensitivity(感度)項，由於我們尚未建立雜信模擬機制，所以沒有做感度的模擬，故目前無法列出數值與實測值相比較。

| Input control signal |       |       | Experiment result                     |           |                       |      |                                       |      |                                    |      |

|----------------------|-------|-------|---------------------------------------|-----------|-----------------------|------|---------------------------------------|------|------------------------------------|------|

| B[16]                | C[15] | D[14] | RF <sub>Gain</sub><br>SPEC>29<br>(dB) |           | NF<br>SPEC<12<br>(dB) |      | P <sub>1dB</sub><br>SPEC>-32<br>(dBm) |      | Sensitivity<br>(S+N)/N>20<br>(dBm) |      |

|                      |       |       | Sim                                   | TEST      | Sim                   | TEST | Sim                                   | TEST | Sim                                | TEST |

| 0                    | 0     | 0     | 32                                    | 31<br>4.1 | 7.4                   | -32  | -33                                   | NA   | -94                                |      |

| 0                    | 0     | 1     | 32                                    | 32<br>4.0 | 7.1                   | -30  | -31                                   | NA   | -95                                |      |

| 0                    | 1     | 0     | 33                                    | 32<br>3.7 | 6.8                   | -32  | -33                                   | NA   | -94                                |      |

| 0                    | 1     | 1     | 33                                    | 33<br>3.6 | 6.5                   | -30  | -31                                   | NA   | -95                                |      |

| 1                    | 0     | 0     | 29                                    | 28<br>5.8 | 9.8                   | -27  | -28                                   | NA   | -90                                |      |

| 1                    | 0     | 1     | 29                                    | 29<br>5.7 | 9.4                   | -27  | -28                                   | NA   | -91                                |      |

| 1                    | 1     | 0     | 31                                    | 30<br>4.6 | 8.0                   | -29  | -30                                   | NA   | -92                                |      |

| 1                    | 1     | 1     | 31                                    | 30<br>4.3 | 7.8                   | -29  | -30                                   | NA   | -93                                |      |

(表 4.3)Front End 的量測匯整表

### 4.3.1 前端電路的增益量測

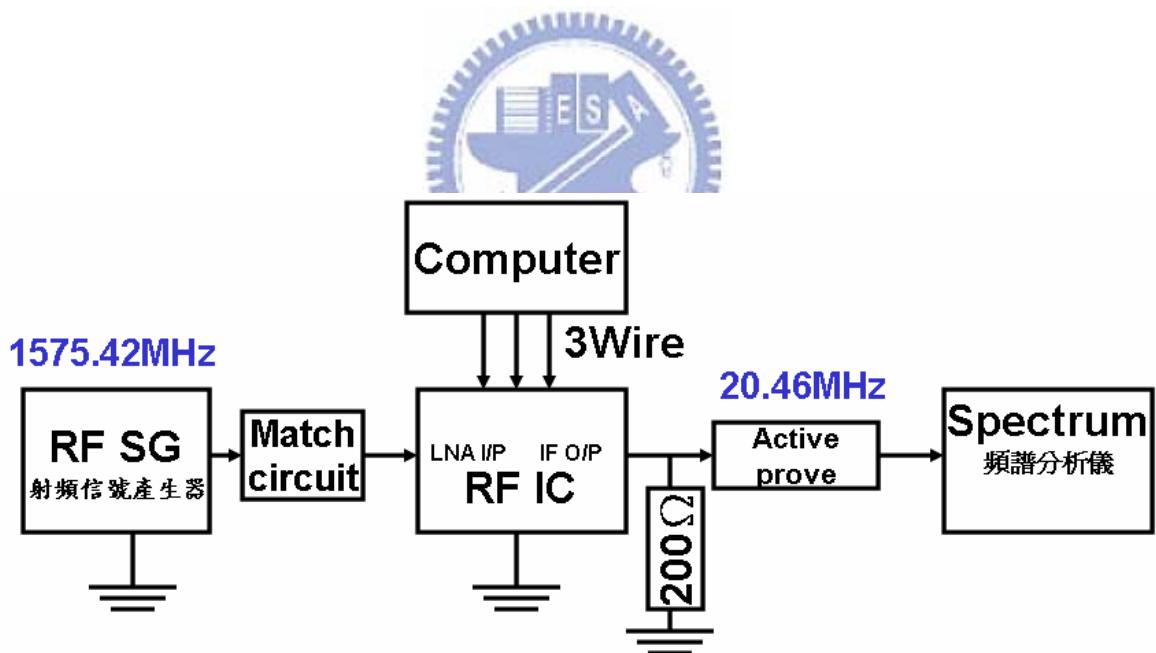

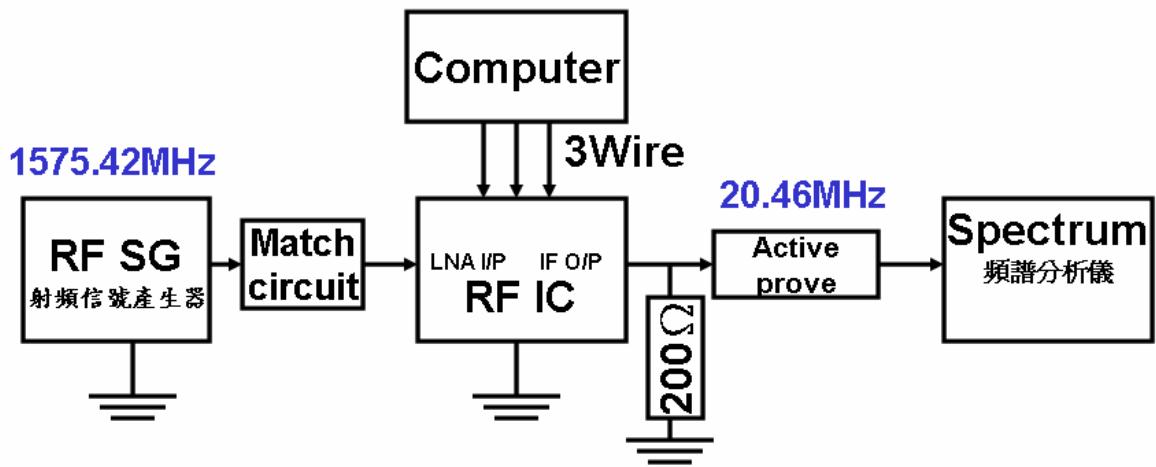

前端電路的量測結果，已顯示在(表 4.3)中，本節主要在說明，量測的儀器配置和接線方式。我們是使用 3Wire 來切換前端電路的八種偏壓電流，以量得此八種不同的轉換增益。

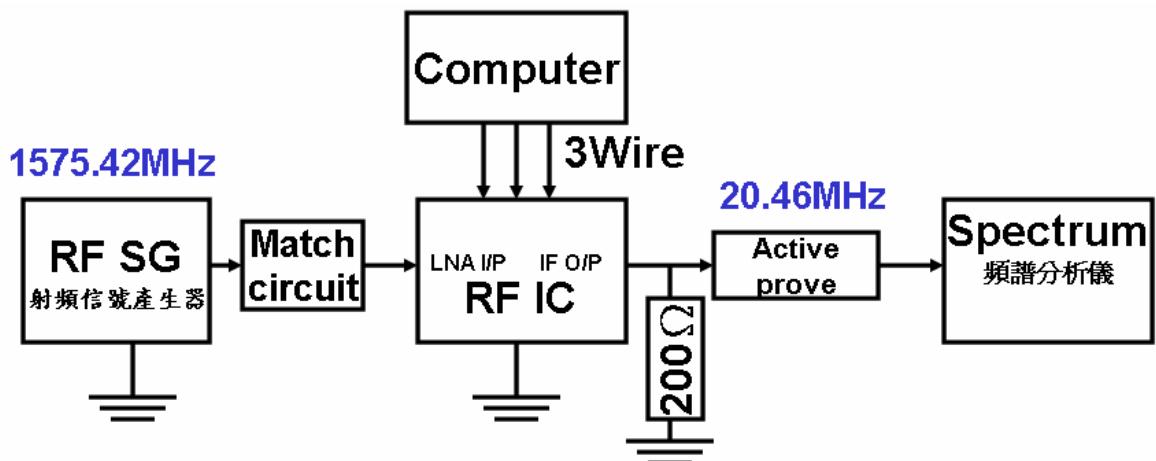

首先我們用 RF SG 從 LNA 端輸入一個-90dBm(輸入信號需夠小才能使電路工作在線性範圍)的載波信號(頻率為 1575.42MHz)，經過 MIXER 及 LO(頻率為 1554.96MHz)的轉換後得到一 IF 信號輸出(頻率為 20.46MHz)，再用 Spectrum 量得此信號的振幅。如此將輸出、輸入振幅一比，就可以得到此前端電路的增益了，然後再將此結果紀錄於(表 4.3)中。

(圖 4.3.1) 前端電路的增益量測之接線圖

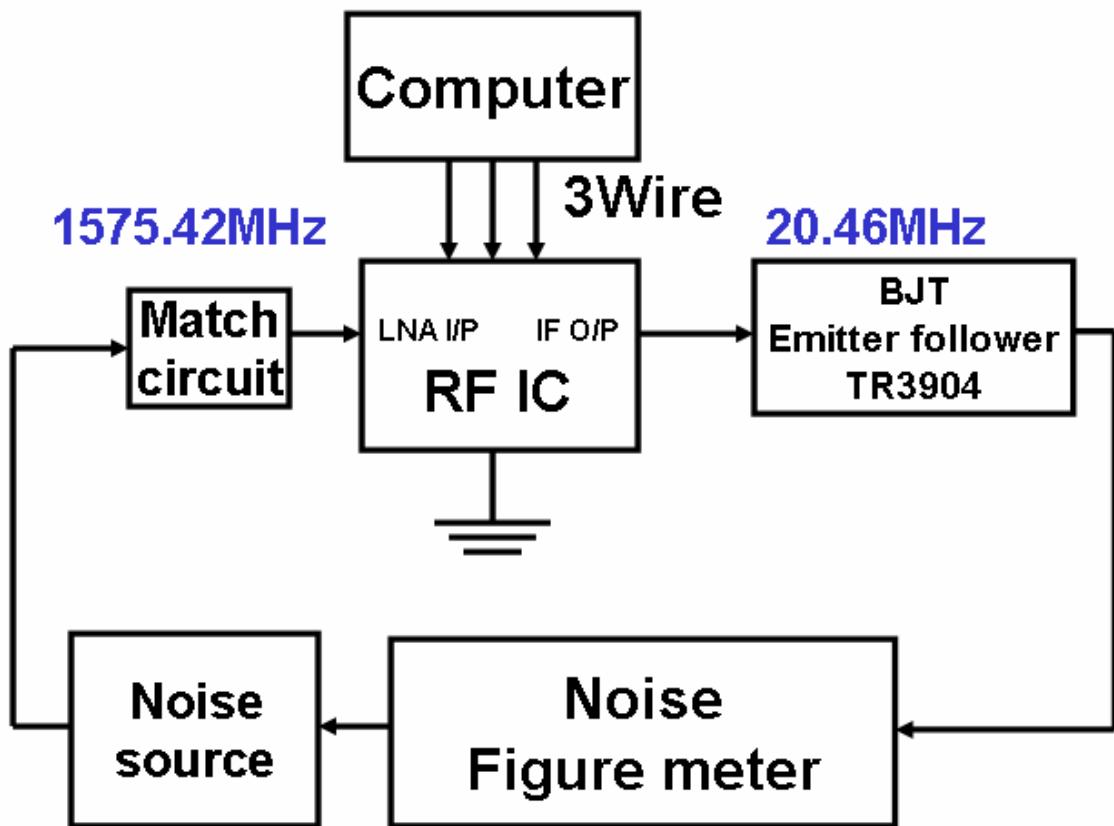

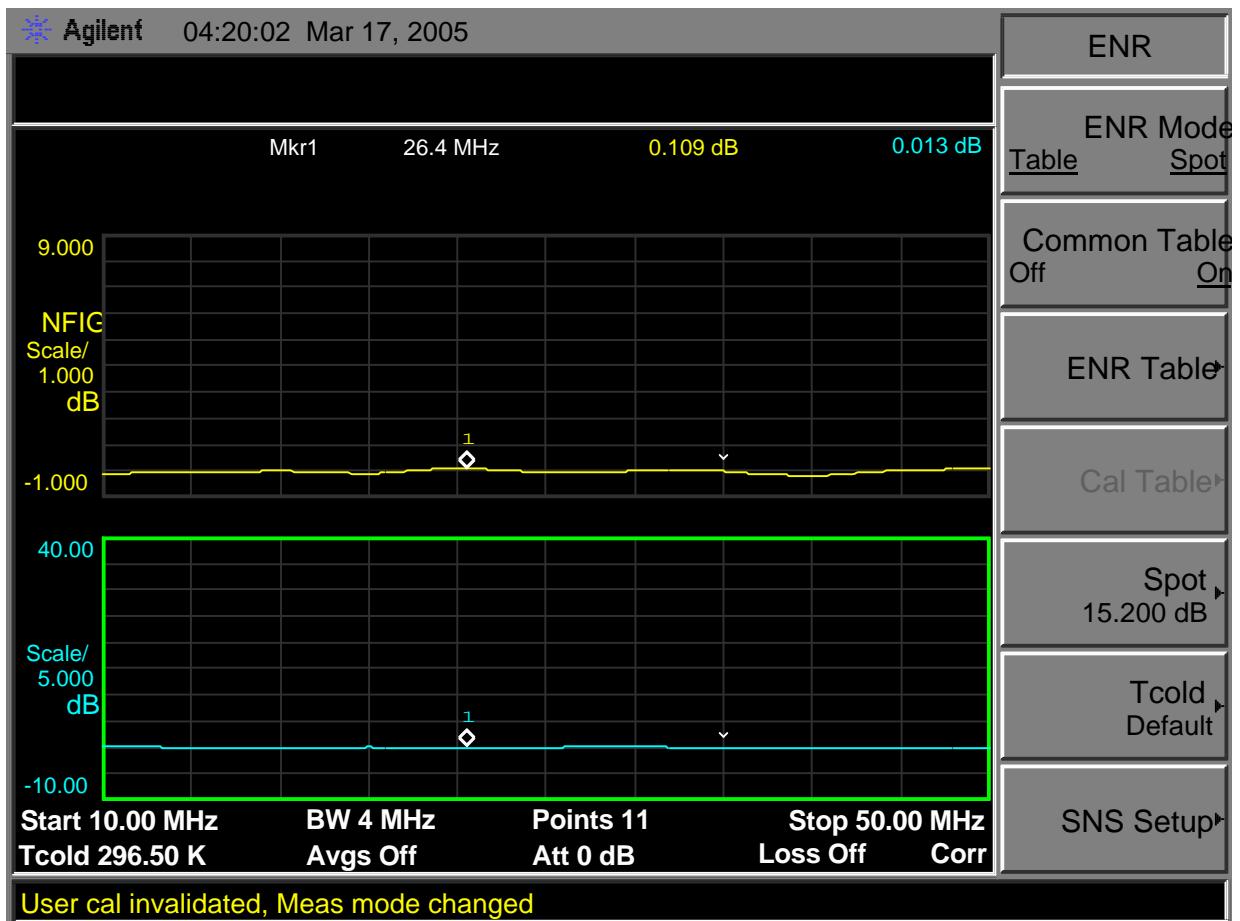

### 4.3.2 前端電路的NF(雜信指數)量測

前端電路的八種狀態之量測結果，已顯示在(表 4.3)中，本節下列文章主要在說明，量測的一些過程。

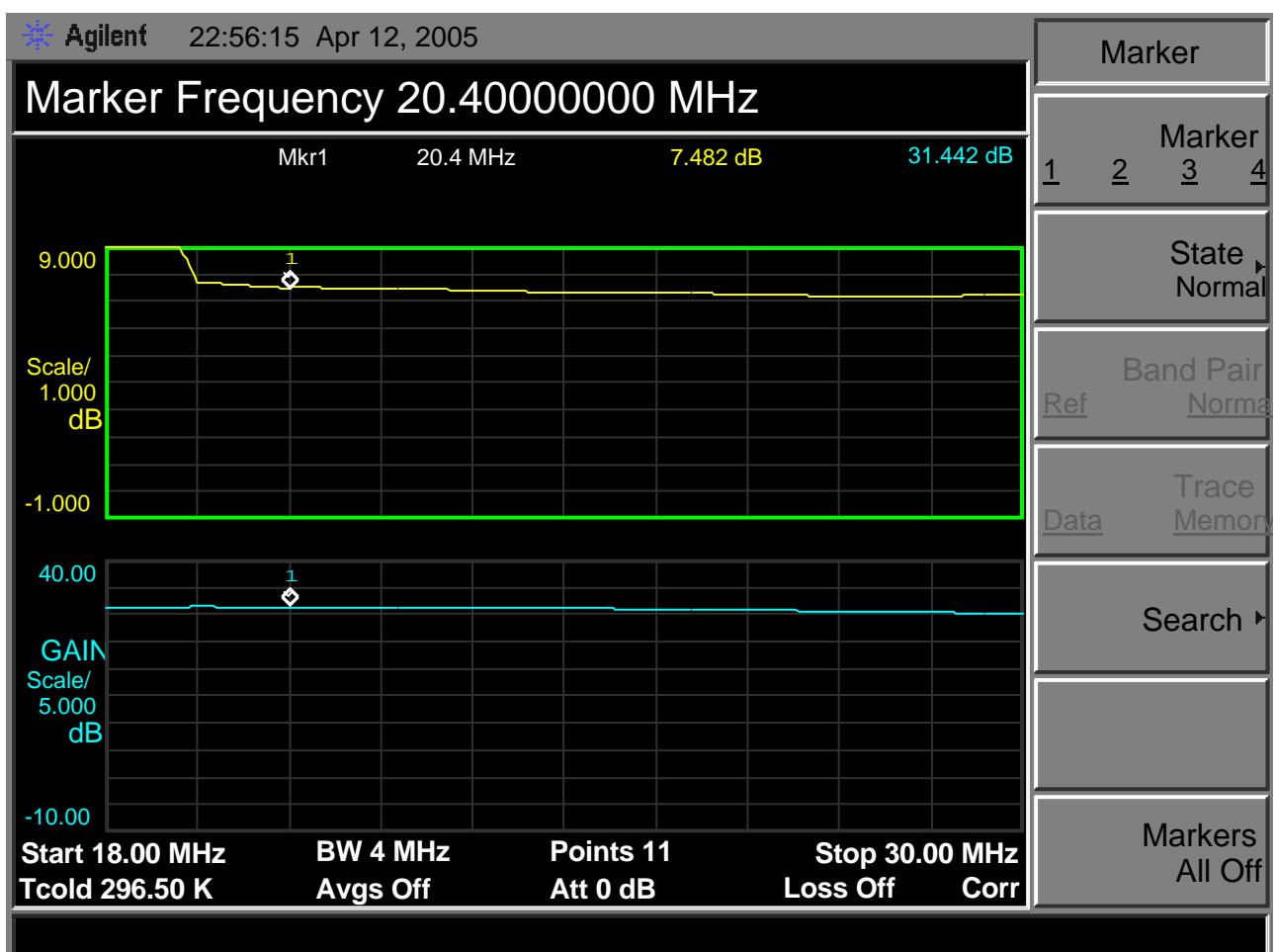

本節第一張圖(圖 4.3.2)為我們的前端電路，NF 量測之接線圖。在量測之前我們先將儀器校正好以確保量測的結果之可靠度，本節第二張圖(圖 4.3.2-1)所展示的畫面即為量測前的儀器校正畫面。本節第三張圖(圖 4.3.2-2)為八種狀態中的 Normal type(0.0.0)之量測結果，我們將此項的量測結果依序紀錄於(表 4.3)中。

(圖 4.3.2) 前端電路的 NF 量測之接線圖

此儀器內含校正說明，我們依此說明，將 NF 及 Gain 校正到趨近於零的狀態。

(圖 4.3.2-1) 前端電路的 NF 量測之儀器校正畫面

我們量得的結果是  $NF=7.48dB$ ，增益為  $31.44dB$ 。

(圖 4.3.2-2) 前端電路的 NF 量測畫面

### 4.3.3 使用頻譜分析儀來量測P1dB

P1dB 的量測結果已顯示在(表 4.3)中，下列(圖 4.3.3)主要是展示此測試的儀器配置。我們量測 P1dB 的程序是：

- (1.) 使用 RF SG 輸入一個-100dBm 的載波信號(頻率為 1575.42MHz)，並紀錄輸出在 Spectrum 顯示的 Power level，再將輸出、輸入相減得到增益值。

- (2.) 然後再將 RF SG 的載波信號調高 1dB，並依序紀錄其增益值的。

- (3.) 重複這些步驟一直到此增益值比第一步驟少掉 1dB 為止。

- (4.) 再將此步驟的 RF SG Power level 紀錄下來，即為 P1dB 的量測結果。

依序改變 3Wire 的設定並重複以上四個步驟，並把值紀錄於(表 4.3)中。

(圖 4.3.3) 量測 P1dB 的儀器配置圖

#### 4.3.4 使用頻譜分析儀來量測感度

感度的量測結果已顯示在(表 4.3)中，本節下列文章是在敘述感度的量測的方法及過程。首先我們將前端電路的感度量測之接線圖，展示於下列第一個圖中，如(圖 4.3.4)。接著我們把儀器校正的結果，展示於下列第二個圖中，如(圖 4.3.4-1)感度量測前之儀器確認。最後我們把量測結果，展示於下列第三個圖中，如(圖 4.3.4-1)信號雜信比(S+N/N)的量測畫面。

(圖 4.3.4) 前端電路的感度量測之接線圖

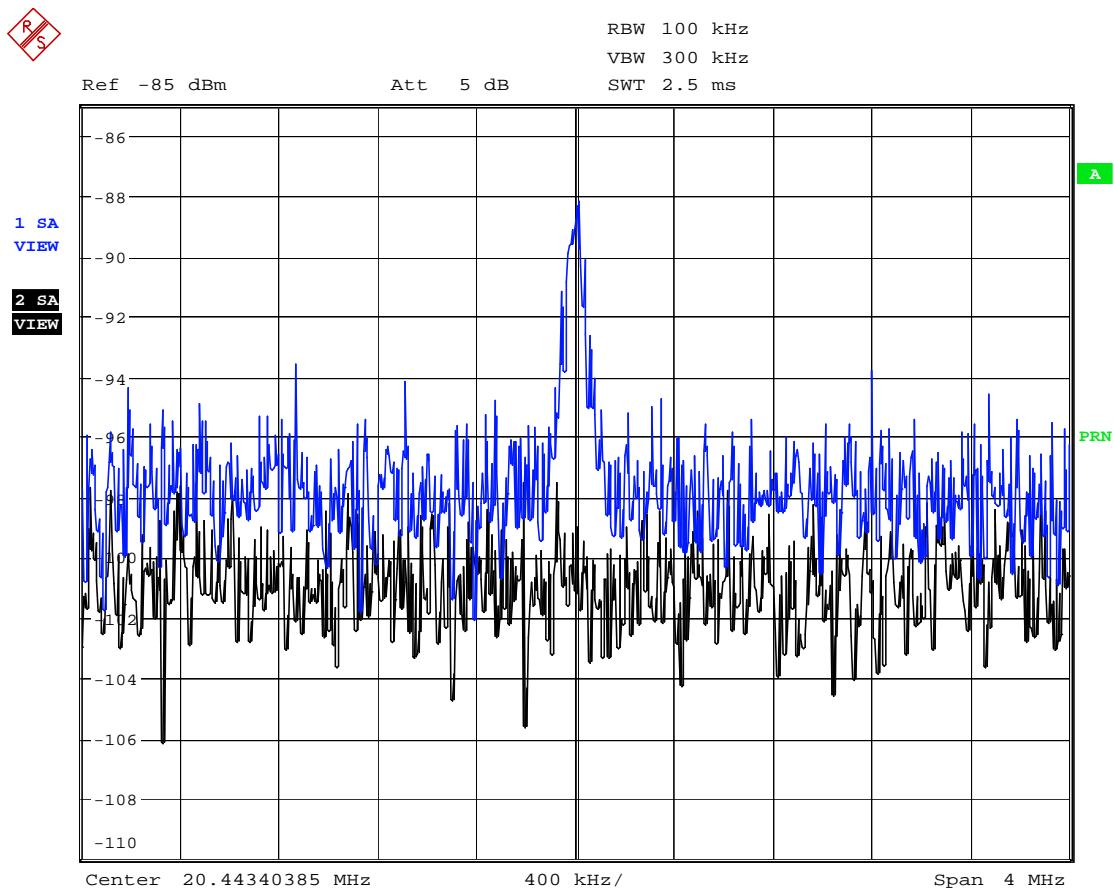

我們想使用頻譜分析儀來量測感度，所以我們首先來確認一下此頻譜分析儀是否能量測此系統的信號雜信比。我們的做法是：

(1.) 利用射頻信號產生器，從 LNA 打入一個很小能量的載波信號約-120dBm，然後從混波級的輸出端觀測到此輸出頻譜，並讓儀器自動紀錄此頻譜。如(圖 4.3.5-1)中之上面的頻譜。

(2.) 關掉此電路(LNA+MIXER)之電源，則此頻譜能量需小於此電路電源打開時的能量。

至少肉眼能清楚辨識。如(圖 4.3-1)中之下方的頻譜。

做完以上兩點確認之後，我們知道量此測試設備(頻譜分析儀)真的可以量測到欲量測電路所產生的雜信，換句話說欲量測電路所產生的雜信已大於測試設備(頻譜分析儀)的雜信了。若做完以上兩點之後，此二頻譜的差距仍然不夠大(就是肉眼無法清楚分辨)，則此方法就不能使用，即應另謀它策了！

(圖 4.3.5-1)中有兩組曲線，下面那一組是 RF IC 電源關掉的雜訊頻譜圖，上面那一組是 RF IC 電源打開的雜訊頻譜圖。如上說明，我們欲使用這個方法來量測信號雜信比，進而求得此系統的感度。

Date: 15.MAR.2005 07:15:16

(圖 4.3.4-1)感度量測前之儀器確認：信號雜信比(S+N/N)量測前的確認畫面

做完了上面的頻譜分析儀，量測雜信的能力確認後，我們就不能再調整頻譜分析儀的任何旋鈕了。我們只要調整射頻信號產生器使得頻譜分析儀上顯示信號與雜信比剛好等於 20dB 時，在讀取整射頻信號產生器的射出功率，即為我們的電路系統在(S+N/N)=20dB 之感度了。頻譜分析儀上的顯示如(圖 4.3.1-1)所示。

(圖 4.3.4-2)信號雜信比(S+N/N)的量測畫面

### 4.3.5 RFIC量測設定照片

我們將 RF IC 量測的設定方式，敘述如下：

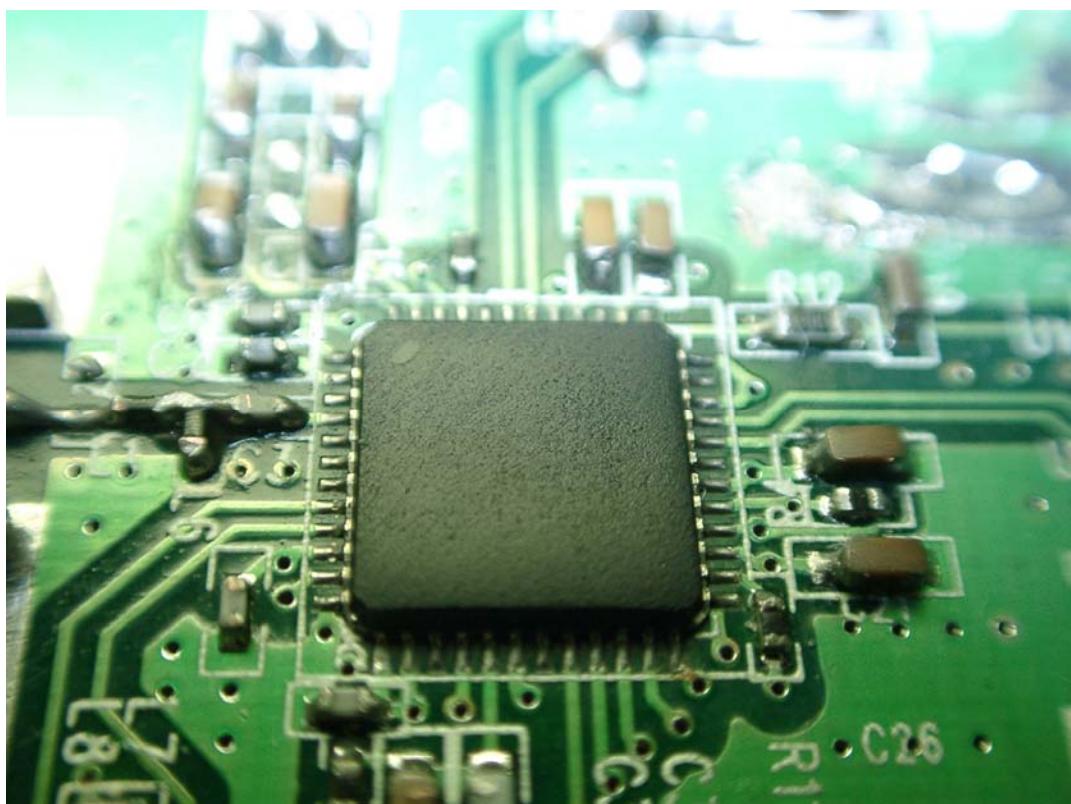

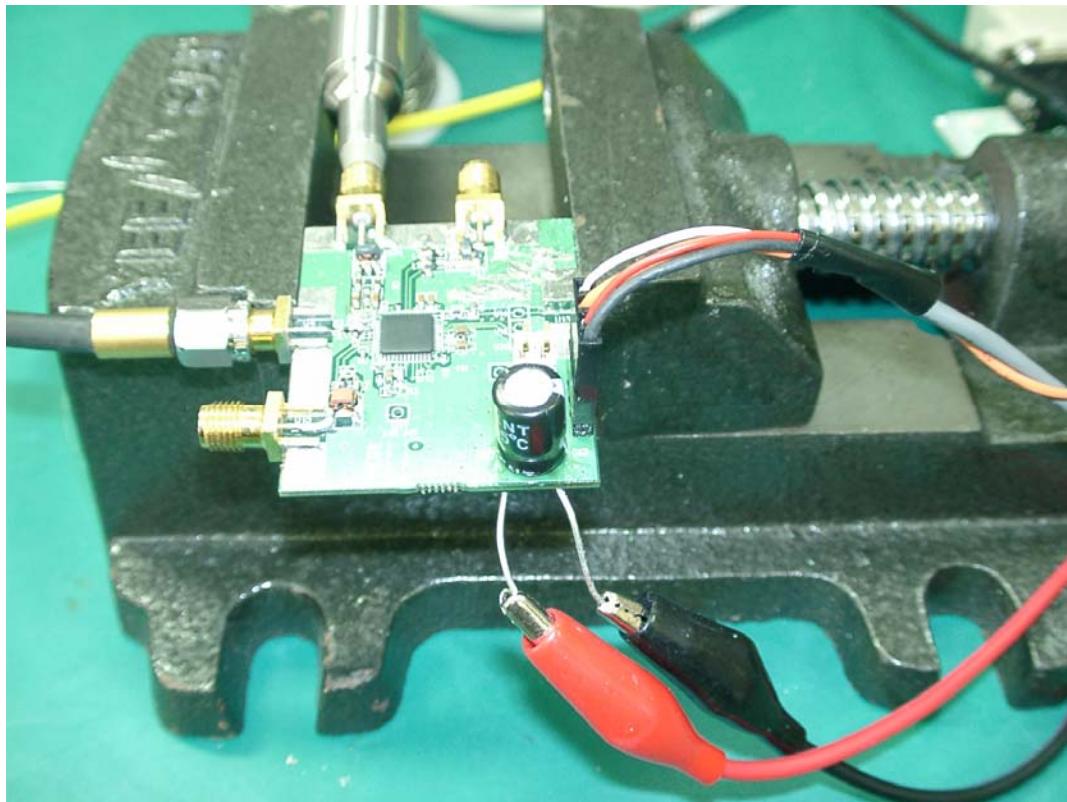

- (1.) 首先我們將自己設計之 RF IC 與週邊元件、接頭.....等焊接於 P.C.B 上，如下

(圖 4-1)。從圖中可以看出這是一個 48 腳位包裝的 IC，旁邊搭配了一些必要的電感、電容等元件。

(圖 4.3.5-1) RF IC 與週邊元件實體圖

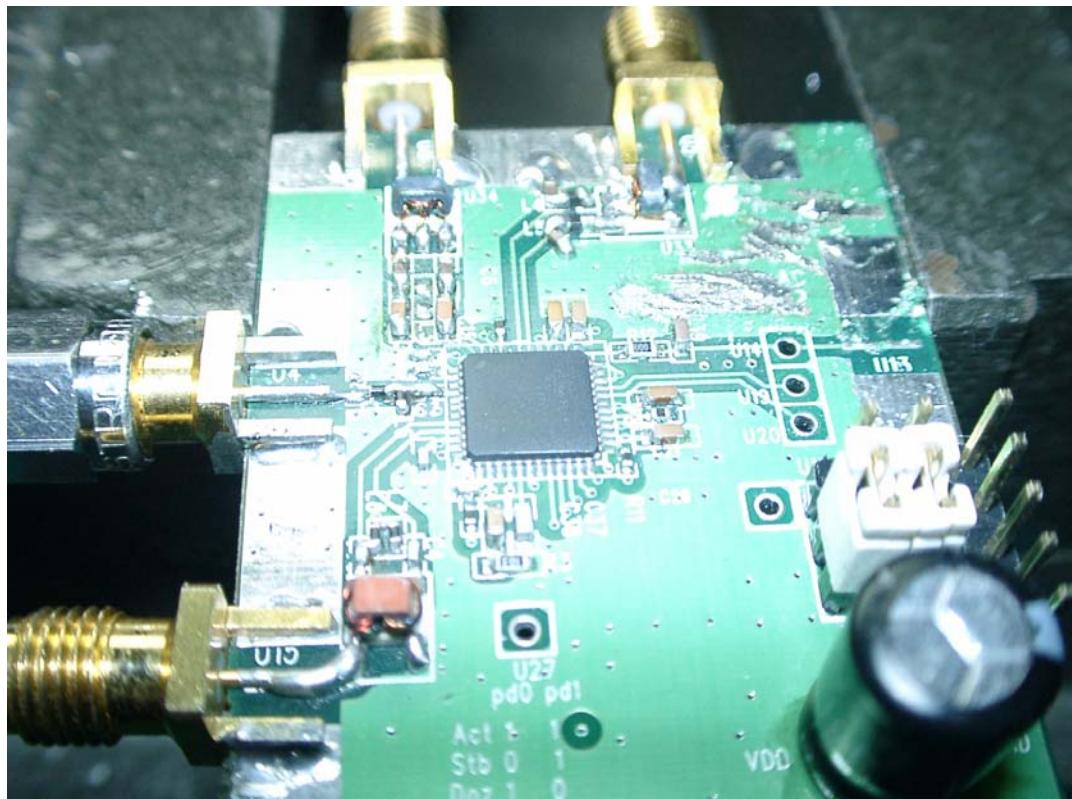

(2.) 並用測試治具牢靠的固定住 P.C.B 如下(圖 4.3.5-2)。此圖中的上方右邊 SMA Connector 為中頻輸入(IF Input)，上方左邊 SMA Connector 為中頻輸出(IF Output)，左側上為 LNA Input，左側下為 OSC Output。右側為電源輸入端及。

(圖 4.3.5-2) 用測試治具固定住的 P.C.B

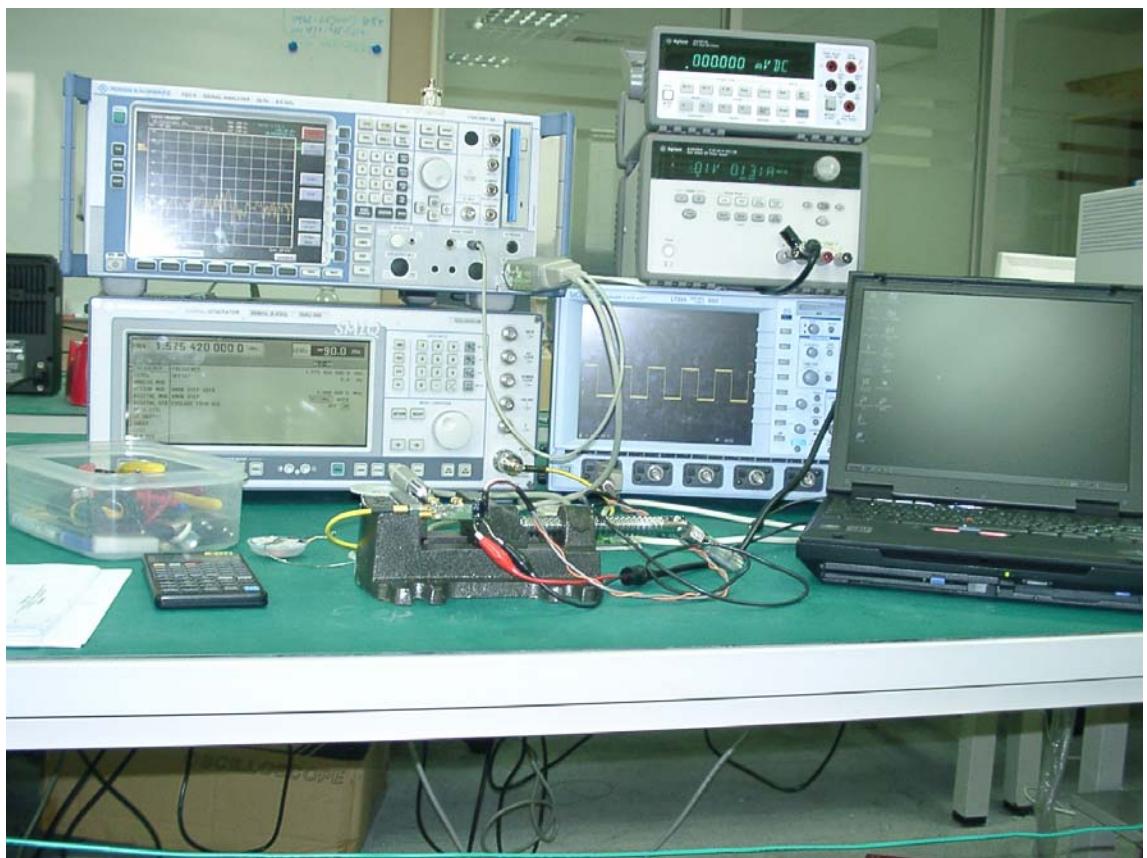

(3.) 再來我們將所需之儀器架設起來如下(圖 4.3.5-3)。由圖中可以看到使用的儀器有：

左上方-頻譜分析儀、左下方-射頻信號產生器、中間上方-數位電表、中間中央-電源供應器、中間下方-示波器、最右邊為筆記型電腦，負責送信號給 IC(透過 3Wire)以調整各個電路的電流量。

(圖 4.3.5-3)我們的測試設備組合

(4.) 連接上我們的 P.C.B 如(圖 4.3.5-4)。在這個圖中可以清楚的看到我們已將電源接上、

控制線(3wire)、RF Cable 等都接上基板了。

(圖 4.3.5-4)待測試模組的接線圖

這是我們就建立的測試平台，在此章節中所有的測試都以如此的設定為基礎。

#### 4.4 戶外衛星實收測試

我們使用衛星接收模組(內含我們自製的 RF IC)、電腦來做衛星實收測試，以檢驗我們推薦的方法所做成的 RF IC 是否可行？

在此我們自己設定的檢驗規則是：如果 RF IC 能收到衛星信號並使整個系統運作，則我們推薦的方法為可行。若不能達到此狀況則我們判定此方法為不可行。

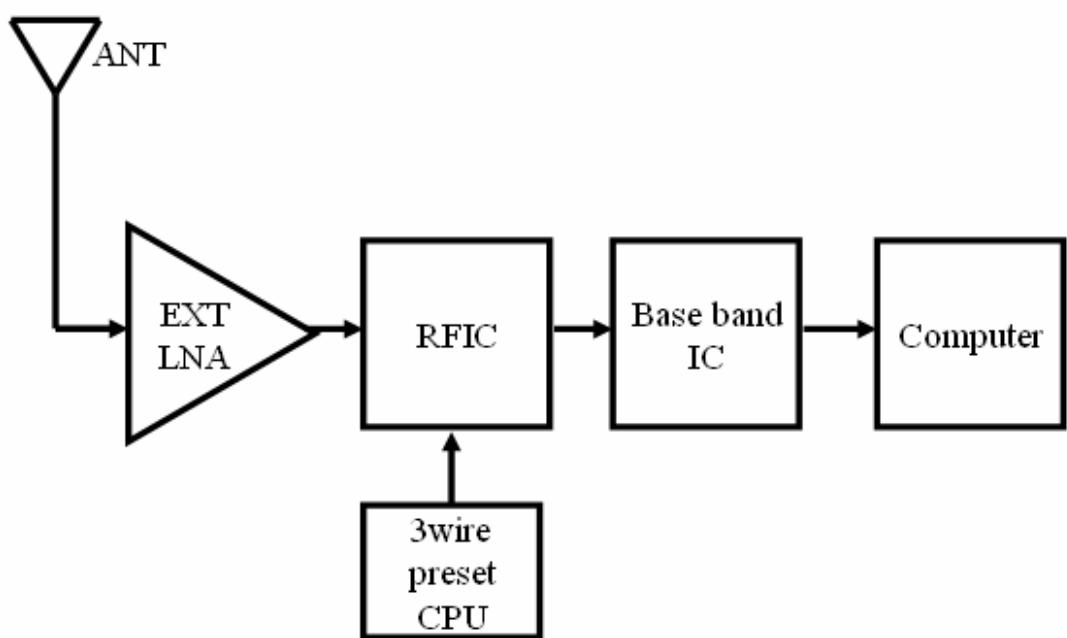

下圖(圖 4.4)即為整個 GPS Receiver 的系統方塊圖，我們將使用這樣的系統來檢驗我們推薦的方法所做成的 RF IC。我們也找到了 EXT-LNA 的技術資料，附於參考資料中 [112]。EXT-LNA 是我們在做實測時發現雲層厚的時候偶而會有斷線的情況，雖然若不加上此 EXT-LNA 我們依然能夠完成此測試，不過為了更實用我們最後決定加上去。

事實上我們的 EXT-LNA 是使用 Philips BFG425 之電晶體來製作的，它的 Noise figure 為 1.2dB，功率增益為 18dB。重新估算整個射頻系統的感度為：-101dBm，足足比原先的設計(-94dBm)改善了 6dB，從此我們得到一個經驗：就是要留足夠的餘度才能使系統運轉順暢。

(圖 4.4)GPS System block diagram

#### 4.4.1 衛星實際接收測試

拔除外購 GPS 系統上的 RF IC，換上我們建構的 RF IC。且經過一番的理論推演及實驗室測試組合之後，我們試著接收天上的衛星，看看能不能讓系統運作？結果我們得到了滿意的答案。

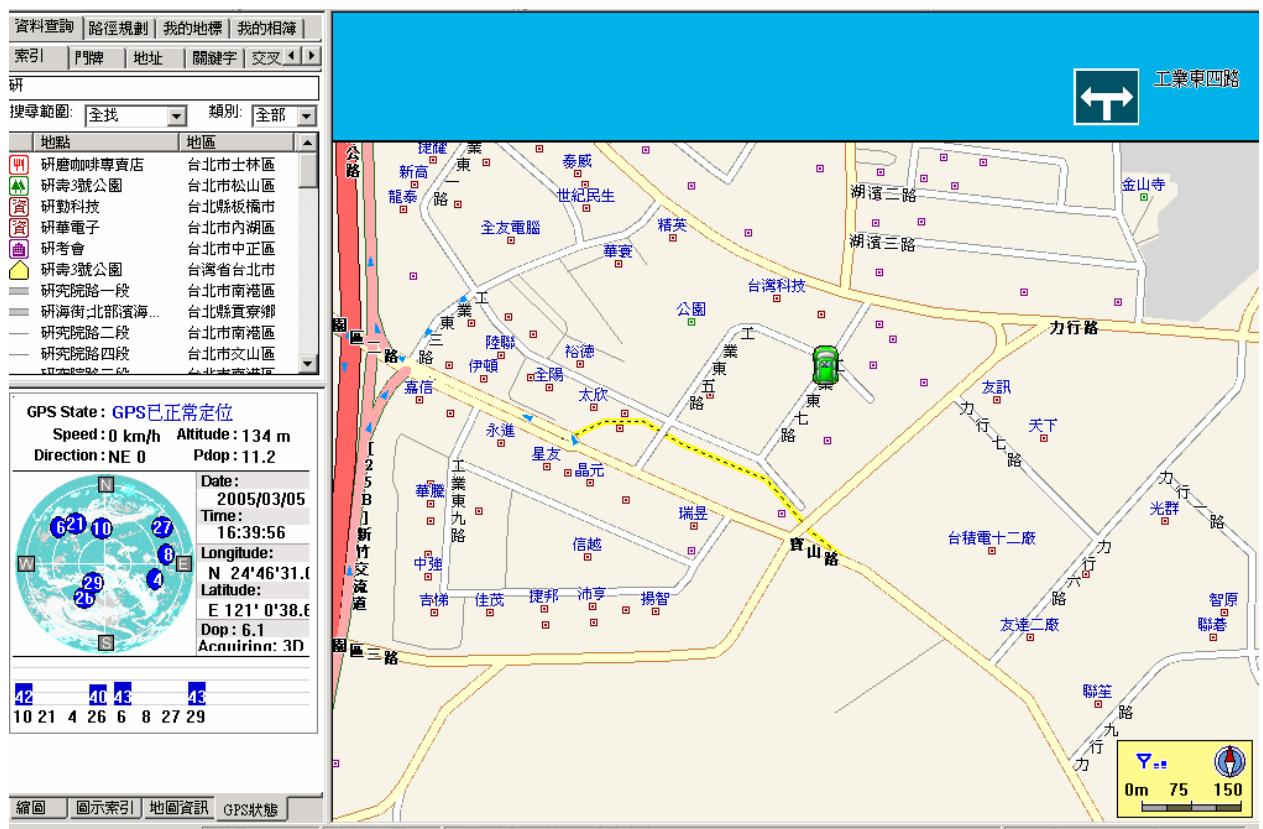

下列兩張圖(圖 4.4.1-1 及圖 4.4.1-2)就是我們推薦的 RF IC(“內建測試機制的 GPS Receiver RF IC” )接收到衛星信號的成果。第一張圖顯示在「新竹科學園區的工業東七路」的定位情形，第二張圖顯示在「新竹市埔頂路」的定位情形。所以我們最後確認自己建立的 RF IC 是可以接收到天上的衛星信號並讓系統正常運作。

(圖 4.4.1-1) 使用我們自己建立的 RF IC 在「工業東七路」的定位情形

(圖 4.4.1-2) 使用我們自己建立的 RF IC 在「新竹市埔頂路」的定位情形

#### 4.4.2 衛星接收模組

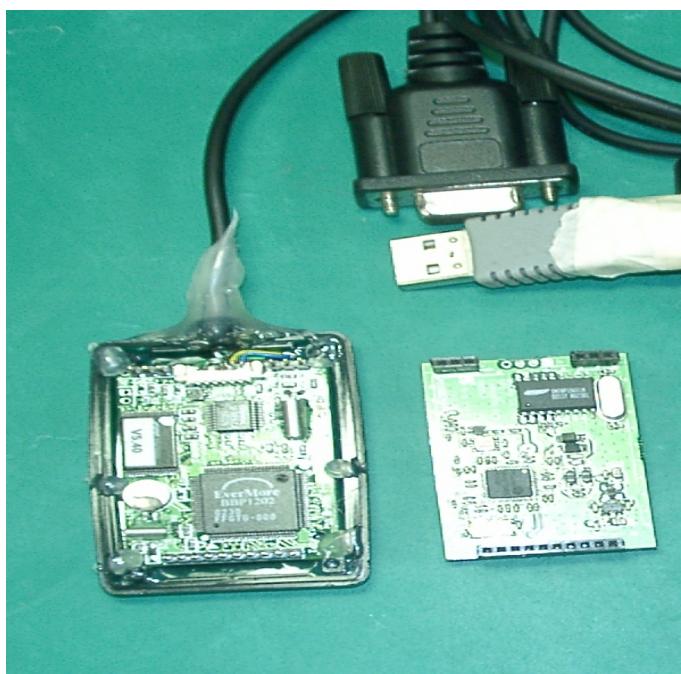

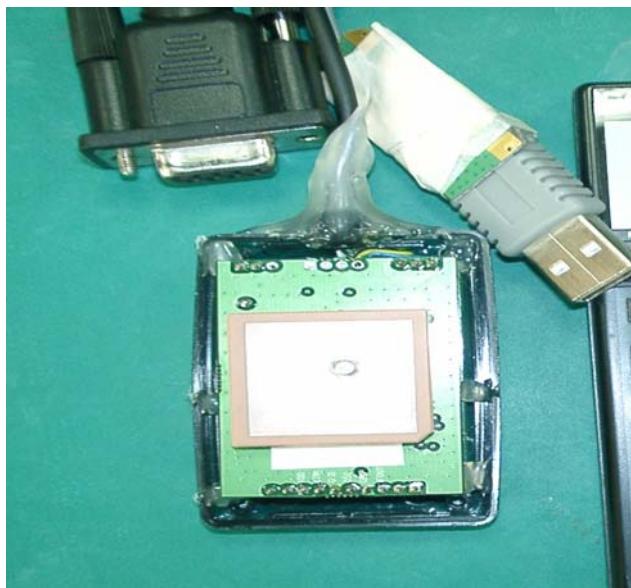

下圖(圖 4.4.2-1)中間為 RF IC 及其周邊元件所構成的射頻模組，右邊為基頻模組，上方的電線及接頭為連結電腦系統的配件。

(圖 4.4.2-1)GPS 模組分解圖

下圖(圖 4.4.2-2)為我們將基頻模組和射頻模組組合後的一個完整的 GPS 系統。

(圖 4.4.2-2)GPS 模組組合圖

## 五、 結論

由於晶圓的面積極為昂貴，若單晶面積變大，則相同晶圓切割出來的單晶數目就變少，商業利潤當然也就縮水了。縱然只是差 1%，在商場如戰場的時代裡，此亦是勝負關鍵。可是我們卻在 RF IC 內，建立了測試機制，也耗費了將近 40% 的面積，這豈非與商業價值背道而馳？其實不然也，因為我們設計的內建測試機制之電路，皆是獨立的模組化電路，待此晶片發展成熟時，內建測試機制之電路即可刪除(例如：3-Wire 電路，額外的輸出/入緩衝器等)。這個事情就好像在登山的時候，我們都會攜帶行囊的道理一樣，因為在登山的路途中我們會碰到許多需求和困難，譬如肚子餓了要從行囊中拿出事先準備的食物來充飢。待登山完畢了，此行囊即可功成身退，等下次要登山或遠行時再披掛上陣。若此時我們沒有攜帶此行囊，那此次的登山行動可能要失敗重來了。這就是以退為進的迂迴戰術，我們將它應用在困難重重的 RF IC 設計之中。

當然若有把握一次設計就能命中規格中心，那就沒有必要這麼辛苦的內建測試電路了。但據我們的經驗所及，一次就精準命中規格的機會，微乎其微！所以我想耗費面積這個副作用應是值得的付出。

當然我們也想研究此內建測試模式所造成的其它副作用，不過這個工程太浩大了(要做兩顆 RFIC)，我想把它當成下次的研究標的。

## 六、 REFERENCES PAPER

- [1] Takahide Kadoyama, Norihiro Suzuki, Noboru Sasho, Hiroshi Iizuka, Ikuho Nagase, Hideaki Usukubo, and Masayuki Katakura, “A Complete Single-Chip GPS Receiver With 1.6-V 24-mW Radio in 0.18- $\mu$ m CMOS,” IEEE JOURNAL OF SOLID-STATE CIRCUITS ,VOL.39,NO.4,APRIL 2004.

- [2] Farbod Behbahani , Hamid Firouzkouhi, Ramesh Chokkalingam, Siamak Delshadpour, Alireza Kheirkhahi, Mohammad Nariman, Matteo Cota, and Saket Bhatia, “A Fully Integrated Low-IF CMOS GPS Radio With On-Chip Analog Image Rejection,” IEEE JOURNAL OF SOLID-STATE CIRCUITS ,VOL.37,NO.12,DECEMBER 2002.

- [3] Arvin R. Shahani, Derek K. Shaeffer, and Thomas H. Lee “A 12 mW Wide Dynamic Range CMOS Front-End for a Portable GPS receiver,” ISSCC97 / SESSION 22 / COMMUNICATIONS BUILDING BLOCK II / PAPER SP 22.3.

- [4] Jie Long and Robert J. Weber , “A Low Voltage, Low Noise CMOS RF Receiver Front-End,” IEEE COMPUTER SOCIETY, VLSID’ 04,2004.

- [5] 謝義濱,高曜煌 “The Design and Analysis of 2.4-GHz CMOS Low Noise Amplifier” 國立交通大學 電信工程研究所 1998 碩士論文.

- [6] 紀震,高曜煌 “LNA and Limiter Circuit Design for Direct conversion Receiver” 國立交通大學 電信工程研究所 2004 碩士論文.

- [7] 林志軒,Dr. Kuei-Ann Wen “0.18um CMOS RF Front-End Receiver Design For Bluetooth System” 國立交通大學 電子工程研究所 2002 碩士論文.

- [8] 莊朝喜,高曜煌 “The Design and Analysis of 2GHz CMOS VCO” 國立交通大學 電信工程研究所 2000 碩士論文.

- [9] 林哲煜,高曜煌 “The Design and Analysis of 2.4-GHz CMOS Mixer” 國立交通大學 電信工程研究所 1999 碩士論文.

- [10] 陳界鎧,高曜煌 “Studies on Mixer and Channel Select Filter for ISM Band Direct

Conversion Receiver” 國立交通大學 電信工程研究所 2004 碩士論文.

[11] Behzad Razavi , “RF MICROELECTRONICS” 1998 Prentice Hall PTR Prentice-Hall,Inc.

A simon & Schuster Company Upper Saddle River NJ 07458

[12] 彭康俊，洪子聖 “無線通訊分數式頻率合成器之現場可程式邏輯陣列電路設計”

國立中山大學 電機工程學系 2000 碩士論文.

[13] 電子時報 2005/3/7 出版的技術 IT 頻道 作者為：郭長祐先生，

網址為：[www.digitimes.com.tw](http://www.digitimes.com.tw)

[14] 中華民國國科會精密儀器發展中心 林修國博士 所著之通訊技術發展與應用研習

講座。

[15] Thomas H.Lee, The design and implementation of low-power CMOS radio receivers 04,2004.

[16] Rhea,Randy./Noble High-frequency oscillator design Publishing Corp. 2003.

[17] Behzad Razavi , RF Microelectronics, Prentice Hall PTR Prentice-Hall,Inc.1998.

[18] Robert J.Matthys , Crystal Oscillator Circuits, Krieger publishing company

Malabar,Florida.1992.

## 七、 REFERENCES PRODUC AND DATA SHEET

- [101] SONY DATA SHEET “CXD2951GA-2 Single Chip GPS LSI”

- [102]NEC DATA SHEET “UPB1005GS 3V DUAL DOWNCONVERTER AND PLL FREQUENCY SYNTHESIZER”

- [103]NEC DATA SHEET “uPB1007K RF/IF FREQUENCY DOWN-CONVERTER + PLL FREQUENCY SYNTHESIZER IC FOR GPS RECEIVER”

- [104]MOTOROLA APPLICATION NOTE “AN1610 Using Motorola’s MRFIC1502 in Global Positioning System Receivers”

- [105]MOTOROLA DATA SHEET “MRFIC1505 Integrated GPS Down converter”

- [106]ZARLINK APPLICATION NOTE “GP2000 GPS Receiver Hardware Design”

- [107]ZARLINK DATA SHEET “GP2015 GPS Receiver RF Front End”

- [108] RAKON DATA SHEET “RSX-3 Very small low profile AT-cut quartz crystal”

- [109] SONY DATA SHEET “CXA3275Q PLL/OSC/MIX IC for Digital Tuner”

- [110] 美國交通部海岸巡防隊的網頁, <http://www.navcen.uscg.gov/Default.htm>

- [111] GPS Receiver RFIC Data sheet-SE4100 from Sige Semiconductor.

- [112] (EXT LNA) Philips data sheet “BFG 425W NPN 25GHz Wideband transistor”

## 八、研 究 生 簡 介

| 學校名稱                                 | 修習科目                                | 時期(民國)       | 任職場所                                 |

|--------------------------------------|-------------------------------------|--------------|--------------------------------------|

| 領東工商(夜間部)                            | 電子工程                                | 69~71 年      | 日商 Uniden 電子公司 3 年<br>(擔任:無線電話修護技術員) |

| 健行工專(夜間部)                            | 電子工程                                | 73~75 年      | 康翔電子公司 9 年                           |

| 中原大學(選讀生)<br>(夜間部)                   | 通識課程                                | 77~80 年      | (擔任:無線電話技術工程師)                       |

| *****                                | *****                               | 80~84 年      | 憶華電機公司 3 年<br>(擔任:衛星接收器設計工作)         |

| *****                                | *****                               | 84~89 年      | 怡安科技公司 5 年<br>(擔任:無線影音傳輸器設計工作)       |

| 交通大學碩士班<br><br>RF IC 指導老師:<br>高曜煌 教授 | RF 電路設計<br>高曜煌 教授                   | 87.11~88.1 年 |                                      |

|                                      | 類比 IC 設計<br>吳介琮 教授                  | 88.9~89.1 年  |                                      |

|                                      | 數位 IC 設計<br>吳錦川 教授                  | 89.2~89.6 年  |                                      |

|                                      | 微波工程(一)<br>鐘世忠 教授                   | 89.9~90.1 年  |                                      |

|                                      | *****                               | 89~91 年      | 和茂科技公司 2 年<br>(擔任:RF IC 設計工作)        |

|                                      | 微電子學<br>蔡中 教授                       | 90.9~90.11 年 |                                      |

|                                      | 數位通訊系統<br>溫?岸 教授                    | 91.9~92.1 年  |                                      |

|                                      | RF IC design<br>孟慶宗 教授              | 92.2~92.6 年  |                                      |

|                                      | *****                               | 92 年~95 年    | 嘉矽電子公司 3 年<br>(擔任:RF IC 設計工作)        |

|                                      | Phase Lock Loop<br>design<br>高曜煌 教授 | 92.9~93.1 年  |                                      |

|                                      | 類比 IC 實做<br>吳介琮 教授                  | 94.9~95.1 年  |                                      |

|                                      | *****                               | 95 年~        | 智邦科技<br>(擔任:RD 專案經理)                 |

## 九、自傳

民國 66 年仲夏，在一個東方剛露出魚肚白的清晨裡-----新竹香山郊外的巨大煙囪，揮舞著猙獰的黑霧，筆直的聳入雲霄。小學剛畢業的我為了糊口，正和父母在與溫度高達數百度的紅磚搏鬥。熾熱的煤渣亂篡、不知道何時會斷裂的鋼索，使得危險狀況層出不窮，磚頭砸裂腳趾頭、手套著火等情事更不是意外。好不容易在被熾熱擊垮之前，我們的奮戰進入了尾聲，這時我開口向媽媽說：『我想去讀國中！』這下-----媽媽又得向人家借錢去了！這是我考慮了好久好久才做下的決定，也是我為自己的人生做下的第一個決定。

在國中時期我們仍得晚上與紅磚搏鬥，天亮才梳洗準備上學。記得有一天我的腳趾頭又被磚頭砸到了，不但劇烈疼痛而且又引發高燒，這時我只好躺在鋪著煤渣灰的台車上等待退燒，待燒退了再繼續未完成的工作，完全不知道自己，已身處險境！

國中畢業後，我到台中潭子加工區的日商有力電子公司工作，晚上則「考上」嶺東工商夜間部電子科進修，當然能「考上」是因為全額錄取。就在這個時候公司缺修理無線電的技術員，雖然依規定技術員需要專科以上才能擔任，但公司可能一時找不到人，竟找我去擔任修理無線電話的工作（這個時候我的學歷是國中畢業），從此我便與無線電結下不解之緣。畢業後也順利的通過資格考試，取得正式的高工畢業證書。

高工畢業後因為我有一技之長，所以也順利的找到了電子技術員的工作。在這期間又讀了健行工專夜間部。這是學分班，就是先讀書以後再補入學考的一種升學方法。

工專畢業了我又如法泡製，到中原大學去讀學分班。共讀了五年，不過最後沒有考上也沒有畢業。後來因為結婚及養育小孩，中斷了好幾年沒有讀書，

一直到一個偶然的機會-----民國 89 年臘月，交通大學的培訓班剛好中場休息，教授正不厭其煩的回答學員的提問。我向老師請教：『工程數學需要考幾分才能進交大就讀？』老師回答：『七八十分。』我再追問：『一定要這麼高嗎？』老師回答：『五六十分可能可以。』我仍窮追不捨的再問：『有沒有可能再低？』老師不厭其煩的回答說：『至少要二三十分！』果然不久之後我以工程數學 8 分的成績被考委會拒於門外。這個時候

我想：『那有沒有可能先進去讀，入學考試以後再說？』，當然這次又被我料中了，不久之後交通大學開辦了學分班，我也珍惜了這個機會。培訓班的老師就是我現在的指導教授，換句話說，我花了超過五年的時間才將碩士班告一段落！

很多人認為無線通訊是一個辛苦又難賺錢的行業，但是我認為只要能求得溫飽，辛苦又何妨！總比回去搬磚頭當捆工好多了吧？時光任冉，回頭一算，從事無線電這個工作，已經超過 28 個年頭，現在這個工作已經成為我謀生的技倆，當然在我心裡未來繼續這個工作的信念仍然堅定！