# Analysis and Design of the 0.13- $\mu$ m CMOS Shunt–Series Series–Shunt Dual-Feedback Amplifier

Tzung-Han Wu, Member, IEEE, Jin-Siang Syu, Student Member, IEEE, and Chin-Chun Meng, Member, IEEE

Abstract—This paper demonstrates the design methodology of the shunt–series series–shunt dual-feedback Meyer wideband amplifier. The small-signal S-parameters are obtained for the first time using the pole-and-zero analysis, thus giving the RF designers a detailed insight into the Meyer amplifier. A 10-GHz wideband amplifier is demonstrated in this paper, using 0.13- $\mu$ m CMOS technology to verify our design theory. The experimental results of the S-parameters highly agree with our theory.

Index Terms—Dual feedback, Meyer amplifier, series-shunt feedback, shunt-series feedback, wideband amplifier.

### I. INTRODUCTION

R ECENTLY, high-frequency and wideband communication applications, such as the 60-GHz (WLAN, ultrawideband (UWB), and even Direct Broadcast Satellite (DBS)/low noise block (LNB), have arisen. In the past, the DBS or LNB receivers have required a high-frequency LNA to receive the desired signal and a wideband buffer amplifier for additional gain amplification [1]–[3] when the gain of the first-stage LNA is insufficient. In addition, the 60-GHz WLAN front-end receiver [4], [5] has become more and more important, and this application may also require some extra gain block, depending on the system architecture and frequency planning. The UWB system inevitably needs a wideband LNA to increase the sensitivity of the entire receiver chain through 3–10-GHz RFs. There are already tremendous research topics about the wideband LNA [6]–[14] for UWB.

The wideband amplifier is a general-purpose gain building block, and the main requirement of a wideband amplifier is its gain and input/output matching bandwidth. It is worthwhile to mention that not only the gain bandwidth but also the matching bandwidth has to meet the system requirement to provide extra gain to any RF system. The  $P_{1\,\mathrm{dB}}$  gain saturation point, the linearity performance, and the noise performance are also important criteria to judge whether a wideband amplifier is good or

Manuscript received May 26, 2008; revised September 23, 2008. First published February 18, 2009; current version published November 04, 2009. This work was supported by the National Science Council of Taiwan, Republic of China, under Contract NSC 98-2221-E-009-033-MY3 and by the MoE ATU Program under Contract 95W803. This paper was recommended by Associate Editor B. Bakkaloglu.

T.-H. Wu was with the Department of Communication Engineering, National Chiao Tung University, Hsinchu 300, Taiwan. He is now with the RFIC design team, MediaTek Inc., Hsinchu, Taiwan.

J.-S. Syu and C.-C. Meng are with the Department of Electrical Engineering, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: ccmeng@mail. nctu.edu.tw).

Digital Object Identifier 10.1109/TCSI.2009.2015603

not. In the past, the microwave distributed amplifier has dominated the wideband application [15]–[17]. However, the distributed amplifier wastes too many valuable chip estates, and thus, the cost cannot be low. Recently, the mainstream technology is the feedback amplifiers [6]–[11], [18], [19].

Most of the feedback wideband amplifiers are single-stage amplifiers with inductive peaking techniques [6]–[10], [20]. Although the lumped feedback amplifiers have already saved a lot of space when compared with the distributed counterparts, the on-chip peaking inductors still consume extra chip space. As a result, the other useful two-stage amplifier topologies consisting of resistive feedback loops are more attractive for a low-cost consideration [21]–[27]. Among so many wideband amplifier topologies, there are basically two most popular two-stage wideband amplifier configurations—the Meyer (shunt–series series–shunt feedbacks) topology [21]–[23] and the Kukielka (shunt–series shunt–shunt feedbacks) topology [11], [24]–[26].

The Kukielka topology is a Cherry–Hopper amplifier [28] with a global shunt–series feedback loop [11], [26]. The Cherry–Hopper amplifier basically consists of a transconductance amplifier in the first stage and a transimpedance amplifier in the second stage. The Kukielka amplifier preserves the broadband characteristic of the Cherry–Hopper amplifier, and the global shunt–series feedback loop can further increase the bandwidth. The input and output matching is achieved simultaneously by the global shunt–series feedback loop and the local shunt–shunt feedback loop. The design methodology of the Kukielka amplifier has already been well established in [11] and [26].

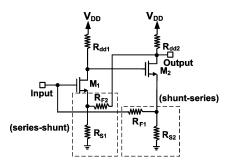

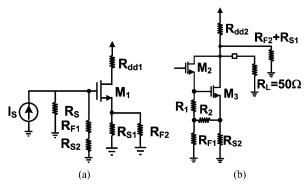

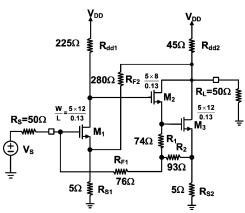

In this paper, those design equations considering the S-parameters of the Meyer wideband amplifier are determined. The Meyer topology is a two-stage amplifier with two global shunt–series and series–shunt feedback loops, and this schematic makes the Meyer configuration totally different from the Kukielka topology. However, the gain bandwidth and the input/output matching bandwidth can be simultaneously achieved by two feedback loops, as shown in Fig. 1. Because there are two global feedback loops in the Meyer topology, the input and output common-mode level, as well as the bias currents, is well defined, as shown in Fig. 1.

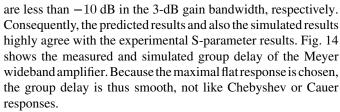

In our previous work on the Kukielka amplifier [26], the loop gain T is always less than one when the input matching is achieved. Therefore, the bandwidth is limited because the amplifier has an overdamped gain response. The capacitive peaking technique was employed to extend the bandwidth but the peak gain is 2 dB more than the dc gain and the group

Fig. 1. Circuit schematic of the Meyer (shunt-series and series-shunt) amplifier.

delay has a variation of 20 ps within the 3-dB bandwidth. On the contrary, our proposed topology eliminates this fundamental constraint; thus, the input/output matching can be achieved while the loop gain T is still flexible. Without using the capacitive peaking, the 10-GHz bandwidth is achieved with a maximally flat gain response and only a 5-ps group-delay variation within the bandwidth.

Previous works [21], [22] have discussed the design equations of the Meyer amplifier using bipolar junction transistor (BJT) technologies; however, the previously reported approach has limitations for the CMOS technologies caused by an invalid analytical approximation, as described in the following sections of this paper. To realize the insights of the Meyer wideband amplifier, we use the pole-and-zero analysis [29], [30] to determine all of the design equations of the S-parameter. This paper provides a consistent method to determine the frequency response of the gain and the terminal impedance matching when compared with [21] and [22]. Methods to solve the small-signal parameters between this paper and previous counterparts are discussed at the end of Section II. It is worthwhile to mention that the method we have proposed in this paper is more complete and general, particularly for the deep submicrometer CMOS technologies.

To our best knowledge, the small-signal S-parameters of the Meyer topology has been established for the first time in this paper. Section II presents the detailed design parameters of the Meyer amplifier, including the gain, input/output impedances, loop gain, poles, and S-parameters. A Meyer amplifier based on these design principles is discussed in Section III. Measurement results are shown in Section IV, and Section V concludes this paper.

#### II. ANALYSIS OF THE MEYER WIDEBAND AMPLIFIER

# A. DC Voltage Gain, Input Resistance, and Output Resistance of the Meyer Wideband Amplifier

The Meyer configuration consists of two feedback loops, as shown in Fig. 1. One of the feedback loops is the shunt–series global feedback, consisting of  $R_{F1}$  and  $R_{S2}$ , between the first-and second-stage common-source amplifiers. This feedback loop is a current-sampling shunt-mixing loop; therefore, the feedback loop provides current–current feedback [30]. On the other hand, the global series–shunt feedback is a voltage-sampling series-mixing feedback loop, consisting of  $R_{F2}$  and  $R_{S1}$ ,

Fig. 2. Block diagram of the Meyer wideband amplifier.

and provides voltage–voltage feedback [30]. The shunt–series and series–shunt feedback loops are represented by  $\beta_I$  and  $\beta_V$ , respectively.

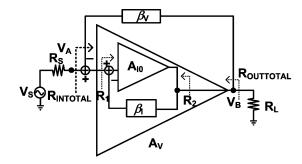

Because the Meyer configuration contains two feedback loops, the A- and  $\beta$ -circuits are too complicated to find. However, the Meyer wideband amplifier can be decomposed step by step as follows. Fig. 2 shows the block diagram of the Meyer amplifier. As shown in Fig. 2, the Meyer amplifier can be treated as a voltage amplifier  $A_V$  with a voltage–voltage feedback loop  $\beta_V$ . Moreover, the A-circuit  $A_V$  of the Meyer amplifier is a current feedback amplifier. As long as the open loop current gain  $A_{I0}$  and the feedback loop  $\beta_I$  are found, the voltage gain to the load  $A_V$  can be determined by

$$A_V = A_I \times \frac{R_2 || R_L}{R_1} = \frac{A_{I0}}{1 + A_{I0} \beta_I} \times \frac{R_2 || R_L}{R_1}.$$

(1)

$R_1$  and  $R_2$  are the dc input and output resistances of the current feedback amplifier. Therefore, the total closed-loop gain of the Meyer amplifier from input node A to output node B is

$$A_{\text{Vtotal}} = \frac{V_B}{V_A} = \frac{A_V}{1 + A_V \beta_V}.$$

(2)

The analytic forms of  $\beta_V$  and  $\beta_I$  will be defined later in the following section.

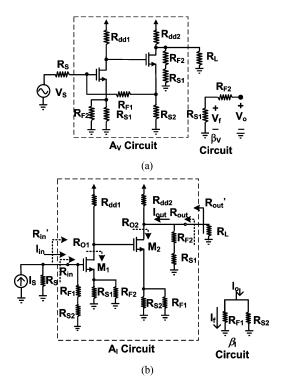

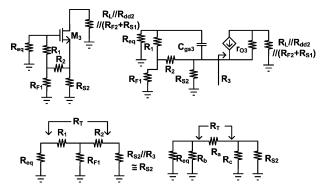

Fig. 3 shows the decomposition sequences of the Meyer amplifier. First, the Meyer topology shown in Fig. 1 can be decomposed into the circuit shown in Fig. 3(a). Fig. 3(a) contains a voltage amplifier and a voltage feedback loop  $\beta_V$ . It is interesting that the A-circuit shown in Fig. 3(a) is actually a current amplifier with a shunt–series feedback loop. Hence, the A-circuit shown in Fig. 3(a) can be further decomposed into a current amplifier with a feedback loop  $\beta_I$ , as shown in Fig. 3(b).

First, the overall open-loop voltage gain  $(V_B/V_A)$  of the Meyer topology can be described as (2).  $A_V$  can be obtained by solving the closed-loop current gain  $A_I$ , the input resistance  $R'_{\rm IN}$ , and the output resistance  $R'_{\rm OUT}$ , including the loading effect [30] of the wideband amplifier circuit, as shown in Fig. 3(b). Therefore

$$A_{\text{Vtotal}} = \frac{A_I \times \frac{R'_{\text{OUT}} || R_L}{R'_{\text{IN}}}}{1 + A_I \times \frac{R'_{\text{OUT}} || R_L}{R'_{\text{IN}}} \times \beta_V}$$

$$= \frac{\frac{A_{I0}}{1 + A_{I0} \beta_I} \times \frac{R'_{\text{OUT}} || R_L}{R'_{\text{IN}}}}{1 + \frac{A_{I0}}{1 + A_{I0} \beta_I} \times \frac{R'_{\text{OUT}} || R_L}{R'_{\text{IN}}} \times \beta_V}.$$

(3)

Fig. 3. (a)  $A_V$  and  $\beta_V$  circuits of the Meyer amplifier after first decomposition. (b)  $A_I$  and  $\beta_I$  circuits after second decomposition.

Next, we calculate the  $A_{I0}$ ,  $R'_{\rm IN}$  (the input resistance when the shunt–series feedback is taken into consideration), and  $R'_{\rm OUT}$  (the output resistance when the series–shunt feedback is taken into consideration) of the current amplifier, as shown in Fig. 3(b). The  $A_{I0}$  is straightforward

$$A_{I0} = \frac{I_{\text{out}}}{I_{\text{in}}}$$

$$\cong (R_{F1} + R_{S2}) \times G_{m1} \times (R_{dd1} || R_{O1}) \times G_{m2}$$

$$= (R_{F1} + R_{S2}) \times \frac{g_{m1}}{1 + g_{m1} \cdot (R_{S1} || R_{F2})}$$

$$\times (R_{\text{dd1}} || R_{O1}) \times \frac{g_{m2}}{1 + g_{m2} \cdot (R_{S2} || R_{F1})}$$

(4)

where the resistance  $R_{O1}$  is the output resistance when looking into the drain node of the transistor  $M_1$ . The input resistance of the current amplifier is

$$R'_{\rm IN} = \frac{R_{\rm IN}}{1 + A_{I0}\beta_I} = \frac{(R_{F1} + R_{S2})}{1 + A_{I0}\beta_I}.$$

(5)

Thus, the total dc input resistance of the Meyer amplifier can be determined by

$$R_{\text{INTOTAL}} = \frac{(R_{F1} + R_{S2}) \times (1 + A_V \beta_V)}{(1 + A_{I0} \beta_I)}$$

(6)

with the feedback factors

$$\beta_I = -\frac{R_{S2}}{R_{S2} + R_{F1}} \quad \beta_V = -\frac{R_{S1}}{R_{S1} + R_{F2}}.$$

(7)

Similarly, the output resistance can be obtained by

$$R'_{\text{OUT}} = R_{O2} ||(R_{F2} + R_{S1})|| R_{\text{dd2}} \cong (R_{F2} + R_{S1}) || R_{\text{dd2}}.$$

(8)

where the resistance  $R_{O2}$  is the output resistance when looking into the drain node of the transistor  $M_2$ . The resistance  $R_{O2}$  is greatly increased because the source node of the transistor  $M_2$  is in series with a large shunt–series feedback resistance [30]. Therefore, the  $R_{O2}$  is very large [30], and the value of  $R_{O2}$  can be neglected when  $R_{O2}$ ,  $(R_{F2}+R_{S1})$ , and  $R_{\rm dd2}$  are parallel. Thus, the dc total output impedance of the Meyer amplifier is equal to

$$R_{\text{OUTTOTAL}} = \frac{R'_{\text{OUT}}}{(1 + A_{V0}\beta_V)} \cong \frac{(R_{F2} + R_{S1})||R_{\text{dd2}}|}{(1 + A_{V0}\beta_V)}.$$

(9)

Using the circuit shown in Fig. 3,  $A_V$  now can be described as follows:

$$A_{V} = \frac{A_{I0}}{1 + A_{I0} \times \beta_{I}} \times \frac{R'_{OUT} || R_{L}}{R'_{IN}}$$

$$= \frac{A_{I0}}{1 + A_{I0} \times \beta_{I}} \times \frac{(R_{F2} + R_{S1}) || R_{dd2} || R_{L}}{\frac{(R_{F1} + R_{S2})}{1 + A_{I0} \times \beta_{I}}}$$

$$= A_{I0} \times \frac{(R_{F2} + R_{S1}) || R_{dd2} || R_{L}}{(R_{F1} + R_{S2})}.$$

(10)

The total dc voltage gain of the Meyer amplifier is

$$A_{V \text{ total}} = \frac{A_{V}}{1 + A_{V} \times \beta_{V}}$$

$$= \frac{A_{I0} \times \frac{(R_{F2} + R_{S1}) || R_{\text{dd2}} || R_{L}}{(R_{F1} + R_{S2})}}{1 + A_{I0} \times \frac{(R_{F2} + R_{S1}) || R_{\text{dd2}} || R_{L}}{(R_{E1} + R_{S2})} \times \beta_{V}}. (11)$$

Consequently, as shown in Figs. 1 and 2, the dc voltage gain from the voltage source  $V_S$  to the load  $R_L$  can be described as

$$A_{V\,\mathrm{DC}} = \frac{V_B}{V_S} = \frac{R_S}{R_S + R_{\mathrm{in\,total}}} \times \frac{A_V}{1 + A_V \times \beta_V}.$$

(12)

The dc values of the voltage gain, the input resistance, and the output resistance of the Meyer wideband amplifier are determined by (6), (9), and (12).

# B. System Transfer Function

In order to determine the frequency response of the small-signal voltage forward transmission coefficient  $S_{21}$ , we have to determine the system transfer function of the Meyer amplifier. From (11), the system transfer function must be

$$A_{V \text{ total}}(s) = \frac{A_{V}(s)}{1 + A_{V}(s) \times \beta_{V}}$$

$$= \frac{A_{I0}(s) \cdot K}{1 + A_{I0}(s) \cdot K \times \beta_{V}}$$

$$= \frac{A_{I0} \cdot K}{\left(1 + \frac{s}{\omega_{1}}\right) \left(1 + \frac{s}{\omega_{2}}\right) + A_{I0} \cdot K \times \beta_{V}}$$

(13)

where  $A_{I0}K$  is the voltage gain and K is a ratio of resistances

$$K = \frac{(R_{F2} + R_{S1}) || R_{\text{dd2}} || R_L}{(R_{F1} + R_{S2})}.$$

(14)

Therefore, the loop gain T of the Meyer amplifier can be described as

$$T = A_{I0}K\beta_{V}$$

$$= -(R_{F1} + R_{S2}) \times \frac{g_{m1}}{1 + g_{m1} \cdot (R_{S1} || R_{F2})}$$

$$\times (R_{dd1} || R_{O1}) \times \frac{g_{m2}}{1 + g_{m2} \cdot (R_{S2} || R_{F1})}$$

$$\times \frac{(R_{F2} + R_{S1}) || R_{dd2} || R_{L}}{(R_{F1} + R_{S2})} \times \frac{R_{S1}}{R_{S1} + R_{F2}}. \quad (15)$$

The denominator in (13) can be expressed as

$$s^{2} + s(\omega_{1} + \omega_{2}) + (1 + T)\omega_{1}\omega_{2}. \tag{16}$$

Next, as long as  $\omega_1$  and  $\omega_2$  are determined, the frequency response of the system-transfer function can be obtained. The original two poles ( $\omega_1$  and  $\omega_2$ ) change to two complex poles ( $P_1$  and  $P_2$ ), caused by the voltage feedback loop. The feedback poles  $P_1$  and  $P_2$  can be calculated as

$$P_1, P_2 = -\frac{1}{2}(\omega_1 + \omega_2) \pm \frac{1}{2}\sqrt{(\omega_1 + \omega_2)^2 - 4(1+T)\omega_1\omega_2}.$$

(17)

The characteristic (16) can be changed to the following standard form:

$$s^2 + s \frac{\omega_0}{Q} + \omega_0^2 = 0 \tag{18}$$

where  $\omega_0$  is the natural frequency and can be described as

$$\omega_0 = \sqrt{(1+T)\,\omega_1\omega_2} \tag{19}$$

and Q is the quality factor

$$Q = \frac{\sqrt{(1+T)\,\omega_1\omega_2}}{\omega_1 + \omega_2}.\tag{20}$$

There are various pole/zero locations for the frequency responses of a feedback amplifier design. For example, the inverse Chebyshev and Cauer responses have specific transmission zeros which cannot be applied to our all-pole system in this paper. On the other hand, the Chebyshev response has a wider bandwidth but a worse group-delay flatness in a given gain-ripple condition while the Bessel–Thomson response has an equal-ripple delay response but a narrower gain bandwidth. Compared with the aforementioned choices, the Butterworth (maximally flat) response is a good tradeoff among the gain,

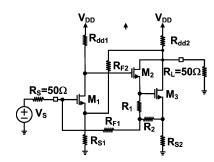

Fig. 4. Final topology of the modified Meyer wideband amplifier.

group-delay flatness, and the bandwidth. Moreover, to maximize the speed of the overall two-stage amplifier system, the two separate poles ( $\omega_1$  and  $\omega_2$ ) of each single-stage amplifier are set the same. Consequently, in order for the transfer function (18) to have the maximally flat response, the Q has to be 0.707. Since  $\omega_1$  equals to  $\omega_2$ , the loop gain ( $T=A_{I0}K\beta_V$ ) should be one by (20) in this paper. Furthermore, as the Q value is lower than 0.707, for example, the two-pole Bessel–Thomson response, the bandwidth is sacrificed but the system is more stable since the two complex poles are far from the imaginary axis in the complex frequency domain. On the contrary, as the Q value is higher than 0.707, e.g., the two-pole Chebyshev response, the gain peak exists and is inclined to instability because the poles are close to the imaginary axis. Thus, a Q of 0.707 is a good choice for stability concerns.

# C. Pole Locations of the Meyer Amplifier

Different from the Kukielka amplifier, the Meyer topology does not use the Cherry–Hopper structure for the basic amplifier. A simple common-source amplifier definitely suffers from a poor frequency response; therefore, the speed of the second stage must be improved. In practical applications, the Darlington configuration can be used for the second stage in the Meyer amplifier. Fig. 4 shows the typical topology of the Meyer wideband amplifier including the source impedance  $R_S$  and the loading impedance  $R_L$ . As shown in Fig. 4, the Meyer amplifier consists of two source degenerative stages; the first stage is a common-source amplifier, and the second stage is a Darlington frequency doubler.

Assume that the Meyer amplifier is a two-pole system, the first pole is the dominant pole of the first-stage common-source amplifier, and the second pole is the dominant pole of the second-stage Darlington amplifier. The equivalent small-signal model used for solving the first pole of amplifier  $A_{I0}$  is shown in Fig. 5(a). Neglecting the biasing resistors  $R_1$  and  $R_2$ , the first pole can be obtained by the open-circuit time constant method [31]

$$\omega_1 = \frac{1}{C_{gs1}R_{gs1} + C_{gd1}R_{gd1}}$$

(21)

where the  $R_{\rm gs1}$  is approximated

$$\frac{[R_S||(R_{F1} + R_{S2})] + (R_{S1}||R_{F2})}{1 + q_{m1}(R_{S1}||R_{F2})}$$

(22)

Fig. 5. Small-signal model for solving (a) the first pole and (b) the second pole.

Fig. 6. Small-signal model of the Darlington stage used to solve the frequency response.

while the resistor  $R_S$  (the source impedance) is 50  $\Omega$  and  $R_{\rm gd1}$  equals

$$R_{\rm gd1} = R_1' + R_{L1}' + \frac{g_{m1}}{1 + q_{m1}(R_{S1}||R_{F2})} R_1' R_L'$$

(23)

where  $R'_1 = R_S || (R_{F1} + R_{S2})$  and  $R'_{L1} \cong R_{dd1}$ .

The second pole can be obtained by the small-signal model shown in Fig. 5(b). Although the second stage is a Darlington pair, the dominant pole can be approximated by [30]

$$\omega_2 \cong \frac{1}{C_{\rm gs}R_{\rm gs} + C_{\rm gd}R_{\rm gd}}.$$

(24)

The transconductance  $g_{m2}$  of the common-drain transistor  $M_2$  is normally much smaller than that of the transistor  $M_3$  in the Darlington configuration. Consequently, the capacitance of  $C_{\rm gd2}$  and  $C_{\rm gs2}$  can be neglected, and only the capacitance of  $C_{\rm gs3}$  and  $C_{\rm gd3}$  is taken into consideration. Therefore, the dominant pole of the Darlington stage is approximated by calculating the pole of the transistor  $M_3$ . Some parameters must be found before calculating  $R_{\rm gs}$  and  $R_{\rm gd}$ .

Assuming that the resistor  $R_{S2}$  is small enough, which is usually valid for the CMOS amplifiers, since the CMOS transistor  $g_m$  is naturally much smaller, the resistors  $R_{\rm gs}$  and  $R_{\rm gd}$  can be determined using the small-signal model shown in Fig. 6. The resistor  $R_{\rm eq}$  is the output resistance of the source node of the transistor  $M_2$ , and it is approximated as

$$R_{\rm eq} \cong \frac{1}{g_{m2}}.\tag{25}$$

As shown in Fig. 6, the resistances can be calculated by changing the T-network  $(R_1, R_2, \text{ and } R_{F1})$  into the  $\Pi$ -network  $(R_a, R_b, \text{ and } R_c)$  [32]. Thus, the resistances are

$$\begin{cases}

R_a = \frac{R_1 R_2 + R_1 R_{F1} + R_2 R_{F1}}{R_{F1}} \\

R_b = \frac{R_1 R_2 + R_1 R_{F1} + R_2 R_{F1}}{R_1} \\

R_c = \frac{R_1 R_2 + R_1 R_{F1} + R_2 R_{F1}}{R_2}.

\end{cases} (26)$$

Therefore, the  $R_{\rm gs}$  and  $R_{\rm gd}$  can be derived as [30]

$$R_{\rm gs} = \left[ R_a || \left( \frac{(R_c || R_{s2}) + (R_{\rm eq} || R_b)}{1 + g_{m3} (R_c || R_{s2})} \right) \right]$$

$$R_{\rm gd} = \left( (R_{\rm eq} || R_b) || R'_2 + R'_L + \frac{g_{m3}}{1 + g_{m3} (R_c || R_{s2})} (R_{\rm eq} || R_b) R'_L \right)$$

(27)

where

$$R'_{2} = (R_{a} + (R_{c}||R_{s2}) + g_{m3}R_{a}(R_{c}||R_{s2}))$$

$$R'_{L} = R_{L}||R_{dd2}||(R_{F2} + R_{S1}).$$

(28)

Because the source impedance  $(R_S)$  and load impedance  $(R_L)$  are both 50  $\Omega$ , the  $S_{21}$  of the amplifier is just the same as the voltage gain with a scaling factor of two by definition. Therefore, according to (21) and (24),  $S_{21}$  can be determined once the  $A_{I0}$  and K are obtained by (4) and (14)

$$S_{21}(s) = 2 \times \frac{V_B}{V_S} = \frac{2 \times A_{V \, DC}}{\left(1 + \frac{s}{P_1}\right) \left(1 + \frac{s}{P_2}\right)}.$$

(29)

According to [6], [7], and [9], we intentionally assume that all the S-parameters have the same poles  $(P_1 \text{ and } P_2)$ ; therefore, the S-parameters can be obtained by following:

$$S_{11}(s) = \frac{R_{\text{INTOTAL}} - R_S(=50 \,\Omega)}{R_{\text{INTOTAL}} + R_S(=50 \,\Omega)} \frac{\left(1 + \frac{s}{Z_1}\right) \left(1 + \frac{s}{Z_2}\right)}{\left(1 + \frac{s}{P_1}\right) \left(1 + \frac{s}{P_2}\right)}$$

(30)

$$S_{22}(s) = \frac{R_{\text{OUTTOTAL}} - R_L(=50 \,\Omega)}{R_{\text{OUTTOTAL}} + R_L(=50 \,\Omega)} \frac{\left(1 + \frac{s}{Z_3}\right) \left(1 + \frac{s}{Z_4}\right)}{\left(1 + \frac{s}{P_1}\right) \left(1 + \frac{s}{P_2}\right)}.$$

(31)

The zeros  $Z_1$  and  $Z_2$  can be obtained by solving the root of the denominator in (17), by changing  $R_S$  into  $-R_S$  [26], [29], [30]. Similarly, the zeros  $Z_3$  and  $Z_4$  are the root of the denominator in (17), by changing  $R_L$  into  $-R_L$ .

# D. Simplified Design Equations and Design Methodology

Although the design equations of the dc values and pole locations are found in the previous sections, it is still difficult to give the designer an approach to arrange the values of resistors in order to optimize the gain, the input/output resistances, and the bandwidth. However, the first-order design methodology of the Meyer amplifier is very clear, based on some practical assumptions. As shown in (19), if the designer wants the largest bandwidth, the  $\omega_1$  must equal  $\omega_2$ , and  $A_{I0}K\beta_V$  has to equal one. If the loop gain  $(A_{I0}K\beta_V)$  is equal to one, then (32) is true, as shown at the bottom of the page. Therefore, the input and output resistances can be simplified into (33) and (34), as shown at the bottom of the page. As we can see, these equations are helpful for the designers to determine the values of the resistors when the gain-bandwidth product is maximized. In order to obtain the first-order design equation, some extra but reasonable assumptions must be made. Assuming that  $\beta_I$  and  $\beta_V$  are too small to achieve the unity loop gain, the term  $R_{F1} + R_{S2}$ and the term  $R_{F2} + R_{S1}$  therefore has to be large enough. For the output impedance matching, the resistance  $R_{\rm dd2}$  in (34) can be described as

$$2 \times 50 = R_{dd2}$$

. (35)

Therefore, the resistance of the loading resistor  $R_{dd2}$  must be near 100  $\Omega$  for the perfect impedance matching. Under the same assumptions, (33) can be simplified to

$$50 = \frac{2R_L R_{S1} R_{dd2} (R_{F1} + R_{S2})}{(R_{F2} + R_{S1}) R_{S2} R_L + (R_{F2} + R_{S1}) R_{S2} R_{dd2}}.$$

(36)

Using the results in (14) and (35), the voltage gain of the A-circuit, as shown in Fig. 3(a), is

$$A_{I0} \cdot K = 33G_{m1}R_{dd1}G_{m2}. \tag{37}$$

Consequently, the first-order design flow for the maximum gain-bandwidth product is summarized as follows.

- 1) Assume  $A_{I0}K\beta_V = 1$ , and thus,  $R_{dd2}$  approximates 100  $\Omega$  for the output impedance matching.

- 2) Design the pole locations by (21) and (24). The first pole must be equal to the second pole.

- 3) The values determined in design flow 2) have to be checked by (36) to perform the input impedance matching.

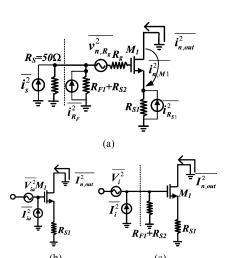

Fig. 7. (a) Noise contributions of the first stage. (b) Equivalent input-referred noise voltage/current of the first stage before feedback. (c) After feedback.

4) Recursively repeat processes 1)-3) until the optimized values of the S-parameters are found.

### E. Noise Analysis

The demonstrated work is a cascade amplifier with dual feedback loops. The noise contribution from the second stage can be neglected because the gain of the first stage is high enough (> 10 dB) [11]. Therefore, we can obtain the noise figure by simply calculating the total short-circuit output noise current spectral density from the first stage.

There are several key noise sources in the first stage, as shown in Fig. 7(a). The channel thermal noise current spectral density of a MOSFET in the saturation region is modeled as  $i_d^2$  $4kT \cdot NEF \cdot g_m \Delta f$ , where  $NEF = \gamma g_{d0}/g_m$  represents the noise excess factor while  $g_{d0}$  is the zero-bias conductance. The parameter  $\gamma$  is a bias-dependent factor which equals 2/3 only for a long-channel device but it is much greater than 2/3 for a short-channel device [3], [33]. In addition, the gate resistance  $(R_q)$  and the source degeneration resistance  $(R_{S1})$  also need to be considered. Fortunately, the gate resistance of the MOSFET

$$A_{I0}K\beta_{V} = 1 \cong (R_{F1} + R_{S2}) \times G_{m1} \times R_{dd1} \times G_{m2} \times \frac{(R_{F2} + R_{S1}) || R_{dd2} || R_{L}}{(R_{F1} + R_{S2})} \times \frac{R_{S1}}{(R_{F2} + R_{S1})}$$

$$\therefore G_{m1}R_{dd1}G_{m2} = \frac{(R_{F2} + R_{S1})R_{dd2} + (R_{F2} + R_{S1})R_{L} + R_{dd2}R_{L}}{R_{S1}R_{dd2}R_{L}}.$$

(32)

$$R_{\text{INTOTAL}} = \frac{(R_{F1} + R_{S2}) \times 2}{(1 + A_{I0}\beta_I)} = \frac{2(R_{F1} + R_{S2})}{1 + (R_{F1} + R_{S2})G_{m1}R_{\text{dd1}}G_{m2}\frac{R_{S2}}{R_{F1} + R_{S2}}}$$

$$= \frac{2R_L \times R_{S1} \times R_{\text{dd2}}(R_{F1} + R_{S2})}{R_{S1}R_{\text{dd2}}R_L + R_{S2}[(R_{F2} + R_{S1})R_L + (R_{F2} + R_{S1})R_{\text{dd2}} + R_LR_{\text{dd2}}]}$$

$$R_{\text{OUTTOTAL}} = \frac{(R_{F2} + R_{S1}) \|R_{\text{dd2}}}{2} = \frac{(R_{F2} + R_{S1})R_{\text{dd2}}}{2(R_{F2} + R_{S1} + R_{\text{dd2}})}.$$

(33)

$$R_{\text{OUTTOTAL}} = \frac{(R_{F2} + R_{S1}) \| R_{\text{dd2}}}{2} = \frac{(R_{F2} + R_{S1}) R_{dd2}}{2(R_{F2} + R_{S1} + R_{\text{dd2}})}.$$

(34)

has a small effect on the gain performance, owing to the relatively high input impedance looking into the gate node.

The equivalent input-referred noise voltage  $(\overline{V_{ia}^2})$  and noise current  $(\overline{I_{ia}^2})$  of the first stage without feedback, as shown in Fig. 7(b), are written as follows [9], [35]:

$$\overline{V_{ia}^2} = 4kTR_g\Delta f + 4kTR_{S1}\Delta f + 4kT \cdot NEF \cdot \frac{1}{g_{m1}}\Delta f$$

(38)

$$\overline{I_{ia}^2} = 4kT \cdot \frac{NEF}{q_{m1}} \Delta f \cdot |\omega C_{\text{eff}}|^2$$

(39)

where  $C_{\text{eff}}$  is composed of  $C_{\text{gs1}}/(1+g_{m1}R_{S1})$  and a parasitic capacitance shunted to ground.

As shown in Fig. 7(c), since the shunt-type feedback resistance only affects the equivalent input-referred noise current but not the noise voltage [11], [35],  $\overline{V_i^2} \approx \overline{V_{ia}^2}$  still holds, and the equivalent input-referred noise current density  $(\overline{I_i^2})$  can be modified as

$$\overline{I_i^2} = \overline{I_{ia}^2} + \frac{\overline{V_{ia}^2}}{R_F^2} + \frac{4kT}{R_F} \Delta f$$

$$= 4kT \cdot \frac{NEF}{g_{m1}} \Delta f \cdot |\omega C_{\text{eff}}|^2$$

$$+ \frac{4kTR_g \Delta f + 4kTR_{S1} \Delta f + 4kT \cdot \frac{NEF}{g_{m1}} \Delta f}{R_F^2} + \frac{4kT}{R_F} \Delta f.$$

(40)

Consequently, the overall noise figure is given by

$$NF = 1 + \frac{\overline{V_i^2} + \overline{I_i^2} R_S^2}{4kTR_S \Delta f}$$

$$= 1 + \left(1 + \frac{R_S^2}{R_F^2}\right) \frac{R_g + R_{S1} + \frac{NEF}{g_{m1}}}{R_S} + \frac{R_S}{R_F}$$

$$+ NEF \cdot \frac{R_S}{q_{m1}} C_{\text{eff}}^2 \omega^2. \tag{41}$$

Equation (41) gives a direct insight that the noise figure increases when the feedback resistor  $R_F (= R_{F1} + R_{S2})$  decreases (i.e., the amount of feedback  $(\beta_I = R_{S2}/(R_{F1} + R_{S2}))$  increases) while the ideal noiseless feedback does not change the noise figure performance [35]. However, if  $R_F$  is large enough, the noise performance is determined by the size and the bias of the transistor  $M_1$ , not the resistor  $R_F$ . Moreover, the noise arises at high frequencies due to the capacitance at the gate node.

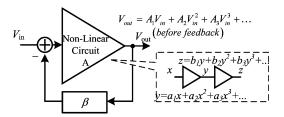

#### F. Linearity

Fig. 8 is the block diagram of a nonlinear circuit with a feedback loop. Equation (41) shows that, without considering the feedback loops, the linearity performance of a cascade amplifier usually dominates at the latter stage since the gain of the first stage is high. The mathematical expressions of the input/output relations of the nonlinear amplifier before/after feedback are described in (43) [36]. Although the linear gain degrades by a factor of  $(1+A_1\beta)$  after feedback, the third-order distortion can be much more reduced. As a consequence, the third-order

Fig. 8. Block diagram of a nonlinear circuit with a feedback loop.

output-referred intercept point  $(OIP_3)$  can be predicted to have an improvement of  $10 \log(1 + A_1\beta)$  dB as described in (44).

$$\frac{1}{V_{OIP3}^2} \approx \frac{1}{a_1^2 b_1^2 V_{OIP3,1}^2} + \frac{1}{b_1^2 V_{OIP3,2}^2} \tag{42}$$

$$\begin{cases} v_{\text{out}}(\text{before f.b.}) = A_1 v_{\text{in}} + A_3 v_{\text{in}}^3 + \cdots \\ v_{\text{out}}(\text{after f.b.}) = \frac{A_1}{1 + A_1 \beta} v_{\text{in}} + \frac{A_3}{(1 + A_1 \beta)^4} v_{\text{in}}^3 + \cdots \end{cases}$$

(43)

$$V_{OIP3}(\text{after f.b.}) = V_{OIP3}(\text{before f.b.}) \times \sqrt{1 + A_1 \beta}.$$

(44)

Since the loop gain  $T = A_V \beta_V$  is set as unity for the Butterworth gain response of the proposed dual-feedback amplifier, the linearity performance does not improve much.

# G. Comparisons of the Small-Signal Parameters in This Paper and Previous Works

Compared with the previous works [21], [22], and [26], the derived circuit parameters in this paper, such as the total terminal impedances and gain in this paper, are more general, because the transistor  $q_m$  need not be very large in our assumption. According to the work in [22], there is a major assumption that the current gain of the transistor is large enough (which is true for the bipolar transistors), and thus, both of the current and voltage feedback loops have an equal feedback loop gain with the closed-loop voltage gain. This assumption is employed to obtain the input and output impedance in [22]. Obviously, the higher current gain makes the bandwidth lower, since the gain-bandwidth product is a constant in the feedback amplifier design. However, the  $g_m$  of the CMOS transistor is usually much smaller than that of the BJT transistor; hence, the current gain of MOS transistors may not be large enough, and this assumption is not suitable for the CMOS Meyer wideband amplifier.

In addition, as described by [21] and [22], the derived  $S_{21}$  is approximated to

$$S_{21} \cong \frac{1}{2} \frac{R_{F2} + R_{E1}}{R_{E1}}. (45)$$

The source degenerative resistor  $R_{E1}$  in (45) equals the source degeneration resistor  $R_{S1}$  in this paper. As shown in (45), the term  $S_{21}$  is proportional to  $1/\beta_V$ , which is based on the very huge loop gain of the voltage feedback path, and only the voltage feedback loop (consisting of resistors  $R_{F2}$  and  $R_{S1}$ ) is taken into consideration in this special case. Under this circumstance, the loop gain is greatly larger than one; therefore, the bandwidth is not optimized. The result of  $S_{21}$  in (45) implies that only the voltage feedback loop dominates the dual feedback system; however, this is not true for analyzing the terminal impedance matching, particularly for CMOS technologies.

Fig. 9. Demonstrated 0.13- $\mu m$  CMOS Meyer wideband amplifier with its component values.

Consequently, the approaches of [21] and [22] for determining the terminal impedances and the gain are based on the conflicting assumptions in a single circuit. This paper has not provided completely unique information but a general formula to determine the gain and input/output impedance.

# III. CIRCUIT DESIGN

In this section, a shunt–series series–shunt dual feedback wideband amplifier is demonstrated using 0.13- $\mu$ m CMOS technology. The advanced 0.13- $\mu$ m CMOS technology is suitable to implement the high-performance RFICs. The circuit schematic and the designed values of the resistors are shown in Fig. 9. This Meyer amplifier is designed and implemented with CMOS technology to verify our theory because of its excellent cutoff frequency provided by the technology. This Meyer amplifier is designed without the source capacitive peaking technique in order to simplify the prediction of the pole locations.

A successful wideband amplifier must contain the following specifications: wide gain bandwidth and matching bandwidth, acceptable noise performance, and reasonable linearity. In order to achieve the goals, a proper dc biasing point and the device size should be decided first.

The dc biasing current and device size influence the noise and linearity performance. A larger dc with a smaller MOS device increase the  $f_T$ , and thus, the gain and noise performance upgrade [6], [7], and [9]. However, a higher gain generally introduces a worse linearity performance, and a smaller device size causes more mismatches between devices, although the Meyer amplifier is single ended. A small device also may increase the gate resistance, and thus, the noise degrades [6], [7], and [9].

In this paper, some tradeoffs between noise performance, gain, bandwidth, and linearity are made. In order to extend the bandwidth up to 10 GHz with a dc gain larger than 16 dB, the linearity is traded a little bit. In addition, the first stage of the Meyer amplifier basically dominates the noise performance of the two-stage Meyer amplifier. The  $f_T$  of the first-stage common-source amplifier shall be as high as possible. Unfortunately, a higher  $f_T$  requires a larger dc, and thus, the voltage drop across resistor  $R_{S1}$  will be too large. As a result, we optimized the circuit elements, as shown in Fig. 9.

As shown in Fig. 9, a Darlington pair is employed in the second stage of the demonstrated Meyer amplifier. The wideband amplifier is implemented using 0.13-µm CMOS

TABLE I EQUIVALENT SMALL-SIGNAL PARAMETERS OF THE CMOS.

|                     | $M_1$ | $M_2$ | M <sub>3</sub> |

|---------------------|-------|-------|----------------|

| g <sub>m</sub> (mS) | 30    | 24    | 54             |

| $C_{gs}(fF)$        | 40    | 21    | 97             |

| $C_{gd}$ (fF)       | 32    | 12    | 38             |

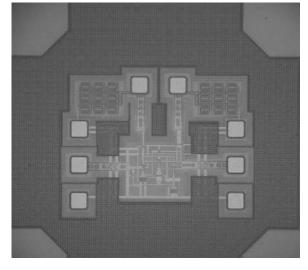

Fig. 10. Die photograph of the 0.13- $\mu$ m CMOS shunt–series series–shunt dual feedback amplifier.

technology. The minimum gate length of this technology is 0.13- $\mu$ m, and the maximum cutoff frequency  $f_T$  is around 80 GHz. As shown in Fig. 9, the first-stage common-source transistor  $M_1$  has a gate length of 0.13  $\mu$ m and 12 gate fingers. Similarly, gate length, finger number, and finger width are shown in Fig. 9. Some tradeoffs are made in order to optimize the circuit performance in terms of gain, port matching, noise figure, and linearity. The small-signal parameters of transistors  $M_1$ ,  $M_2$ , and  $M_3$  are summarized in Table I.

# IV. MEASUREMENT RESULTS

The die photo of the 0.13- $\mu m$  CMOS wideband amplifier is shown in Fig. 10. The input RF ground–signal–ground (GSG) pads are on the left, while the output RFGSG pads are on the right. There are two dc bias pads on the top. As shown in Fig. 10, the chip consumes an area of  $800\times800\,\mu m^2$ . The wideband amplifier only needs a chip area of  $150\times150\,\mu m^2$ , and the probing pads, metal dummies, and poly dummies occupy the remaining 96% chip area. This is because the 0.13- $\mu m$  process requires dummies to perform the chemical–mechanical polishing process. The dc supply is 2.5 V, and the current consumption is 24 mA.

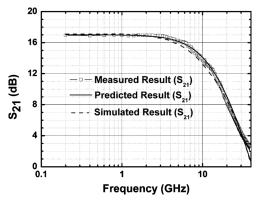

An HP8510 network analyzer, in conjunction with the cascade on-wafer probe station, is used to measure the S-parameter performances. Fig. 11 shows the measured power gain  $S_{21}$  of the fabricated wideband amplifier. In addition, the predicted  $S_{21}$ , by our theory, and the simulated  $S_{21}$  are shown in the same figure for comparison. The Meyer amplifier has a 17-dB gain with a 10-GHz bandwidth.

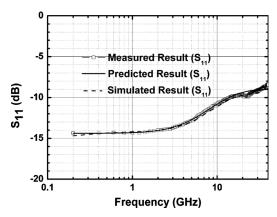

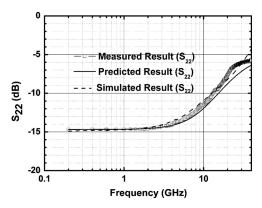

Fig. 12 shows the measured, predicted, and simulated  $S_{11}$  values while the measured, predicted, and simulated  $S_{22}$  values are shown in Fig. 13. The measured input and output return losses

Fig. 11. Measured, predicted, and simulated  $S_{21}$  values of the 0.13- $\mu$ m CMOS Meyer wideband amplifier.

Fig. 12. Measured, predicted, and simulated  $S_{21}$  values of the 0.13- $\mu$ m CMOS Meyer wideband amplifier.

Fig. 13. Measured, predicted, and simulated  $S_{21}$  values of the 0.13-  $\!\mu$  m CMOS Meyer wideband amplifier.

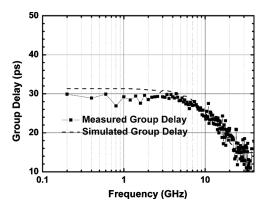

The measured noise figure of the Meyer wideband amplifier is shown in Fig. 15. The measured noise figure is lower than 8.2 dB in the 3-dB gain bandwidth. The simulated and predicted noise performances are also shown in Fig. 15. Here, the predicted noise figure is calculated with the modification of NEF=1.6. However, the measured noise figure is, on average, 0.5 dB higher than

Fig. 14. Measured and simulated group delay of the 0.13-  $\!\mu{\rm m}$  CMOS Meyer wideband amplifier.

Fig. 15. Measured and simulated noise figure of the 0.13-  $\mu\mathrm{m}$  CMOS Meyer wideband amplifier.

Fig. 16. Measured power performance of the 0.13- $\mu$ m CMOS Meyer wideband amplifier.

our simulation results because the BSIM3 model only provides long-channel noise modeling parameters which are not suitable for the advanced CMOS technologies nowadays [33], [37], but the simulation still shows the same trend as the measured data. Compared to the reported CMOS wideband amplifiers [6], [7], and [9], the measured curve trend of the noise figure as a function of the RF frequency is also the same. The noise figure increases rapidly as the RF frequency becomes higher.

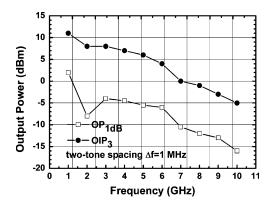

Fig. 16 shows the measured  $OP_{1\,\mathrm{dB}}$  and  $OIP_{3}$  of the demonstrated Meyer wideband amplifier. The power performances degrade as the operating frequency gets higher. The  $OP_{1\,\mathrm{dB}}$  is  $-16\,\mathrm{dBm}$ , and the  $OIP_{3}$  is  $-5\,\mathrm{dBm}$  when the frequency equals 10 GHz.

#### V. CONCLUSION

The first-order design methodology of the shunt–series series–shunt double-feedback Meyer wideband amplifier has been developed. A 10-GHz wideband amplifier has been demonstrated using a 0.13- $\mu$ m CMOS technology. Experimental results highly agree with our theory, and the design tradeoffs are discussed. The small-signal S-parameters are obtained by the approach of pole-and-zero analysis; therefore, the insight of the Meyer wideband amplifier is given to the RF designers. The fabricated 0.13- $\mu$ m CMOS wideband amplifier has a 17-dB gain, a -10-dB input return loss, and a -10-dB output return loss with a 10-GHz bandwidth. The noise figure of the demonstrated amplifier is lower than 8.2 dB, while the  $OP_{\rm 1dB}$  and  $OIP_{\rm 3}$  are better than -16 and -5 dBm, respectively, over the usable bandwidth.

#### ACKNOWLEDGMENT

The authors would like to thank the National Nano Device Laboratory for the RF measurement support, the National Chip Implementation Center for the chip-fabrication support, and Prof. S.-S. Lu for the idea of noise analysis.

#### REFERENCES

- G. Girlando, T. Copani, S. A. Smerzi, and G. Palmisano, "A Ku-band monolithic tuner-LNB for satellite applications," in *Proc. IEEE Custom Integr. Circuits Conf.*, 2004, pp. 613–616.

- [2] F. Bruccoleri, E. A. M. Klumperink, and B. Nauta, "Noise cancelling in wideband CMOS LNAs," in *Proc. ISSCC*, 2002, pp. 406–407.

- [3] F. Bruccoleri, E. A. M. Klumperink, and B. Nauta, "Wide-band CMOS low-noise amplifier exploiting thermal noise canceling," *IEEE J. Solid-State Circuits*, vol. 39, no. 2, pp. 275–282, Feb. 2004.

- [4] B. Razavi, "A 60-GHz CMOS receiver front-end," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 17–22, Jan. 2006.

- [5] S. Emami, C. H. Doan, A. M. Niknejad, and R. W. Brodersen, "A highly integrated 60 GHz CMOS front-end receiver," in *Proc. IEEE Int. Solid-State Circuits Conf.*, Feb. 2007, pp. 190–191.

- [6] A. Bevilacqua and A. M. Niknejad, "An ultrawideband CMOS lownoise amplifier for 3.1–10.6-GHz wireless receivers," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2259–2268, Dec. 2004.

- [7] C. W. Kim, M. S. Kang, P. T. Anh, H. T. Kim, and S. G. Lee, "An ultra-wideband CMOS low noise amplifier for 3–5-GHz UWB system," *IEEE J. Solid-State Circuits*, vol. 40, no. 2, pp. 544–547, Feb. 2005.

- [8] A. Liscidini, M. Brandolini, D. Sanzogni, and R. Castello, "A 0.13 μm CMOS front-end, for DCS1800/UMTS/802.11b-g with multiband positive feedback low-noise amplifier," *IEEE J. Solid-State Circuits*, vol. 41, no. 4, pp. 981–989, Apr. 2006.

- [9] Y.-T. Lin, H.-C. Chen, T. Wang, Y.-S. Lin, and S.-S. Lu, "3–10-GHz ultra-wideband low-noise amplifier utilizing Miller effect and inductive shunt–shunt feedback technique," *IEEE Trans. Microw. Theory Tech.*, vol. 55, no. 9, pp. 1832–1843, Sep. 2007.

- [10] P. Rossi, A. Liscidini, M. Brandolini, and F. Svelto, "A variable gain RF front-end, based on a voltage-voltage feedback LNA, for multistandard applications," *IEEE J. Solid-State Circuits*, vol. 40, no. 3, pp. 690–697, Mar. 2005.

- [11] J. Lee and J. D. Cressler, "Analysis and design of an ultra-wideband low-noise amplifier using resistive feedback in SiGe HBT technology," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 3, pp. 1262–1268, Mar. 2006.

- [12] K. Chen, J. Lu, B. Chen, and S. Liu, "An ultra-wide-band 0.4–10-GHz LNA in 0.18-\mu CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 54, no. 3, pp. 217–221, Mar. 2007.

- [13] T. K. K. Tsang, K. Lin, and M. N. El-Gamal, "Design techniques of CMOS ultra-wide-band amplifiers for multistandard communications," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 55, no. 3, pp. 214–218, Mar. 2008.

- [14] Y. E. Chen and Y. Huang, "Development of integrated broad-band CMOS low-noise amplifiers," *IEEE Trans. Circuits Syst. I, Reg. Pa*pers, vol. 54, no. 10, pp. 2120–2127, Oct. 2007.

- [15] K. W. Kobayashi, R. Esfandiari, M. E. Hafizi, D. C. Streit, A. K. Oki, L. T. Tran, D. K. Umemoto, and M. E. Kim, "GaAs HBT wideband matrix distributed and Darlington feedback amplifiers to 24 GHz," *IEEE Trans. Microw. Theory Tech.*, vol. 39, no. 12, pp. 2001–2009, Dec. 1991.

- [16] F. Zhang and P. R. Kinget, "Low-power programmable gain CMOS distributed LNA," *IEEE J. Solid-State Circuits*, vol. 41, no. 6, pp. 1333–1343, Jun. 2006.

- [17] K. Moez and M. I. Elmasry, "A low-noise CMOS distributed amplifier for ultra-wide-band applications," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 55, no. 2, pp. 126–130, Feb. 2008.

- [18] K. Y. Toh, R. G. Meyer, D. C. Soo, G. M. Chin, and A. M. Voshchenkov, "Wide-band, low-noise, matched-impedance amplifiers in submicrometer MOS technology," *IEEE J. Solid-State Circuits*, vol. SSC-22, no. 6, pp. 1031–1040, Dec. 1987.

- [19] J. C. Zhan and S. S. Taylor, "A 5 GHz resistive-feedback CMOS LNA for low-cost multi-standard applications," in *Proc. ISSCC*, 2006, pp. 721–722.

- [20] S. Shekhar, J. S. Walling, and D. J. Allstot, "Bandwidth extension techniques for CMOS amplifiers," *IEEE J. Solid-State Circuits*, vol. 41, no. 11, pp. 2424–2439, Nov. 2006.

- [21] R. G. Meyer and R. A. Blauschild, "A 4-terminal wide-band monolithic amplifier," *IEEE J. Solid-State Circuits*, vol. SSC-16, no. 6, pp. 634–638, Dec. 1981.

- [22] R. G. Meyer, R. Eschenbach, and R. Chin, "A wide-band ultralinear amplifier from 3 to 300 MHz," *IEEE J. Solid-State Circuits*, vol. SSC-9, no. 4, pp. 167–175, Aug. 1974.

- [23] K. H. Chan and R. G. Meyer, "A low-distortion monolithic wide-band amplifier," *IEEE J. Solid-State Circuits*, vol. SSC-12, no. 6, pp. 685–690, Dec. 1977.

- [24] C. D. Hull and R. G. Meyer, "Principles of monolithic wideband feed-back amplifier design," *Int. J. High Speed Electron.*, vol. 3, no. 1, pp. 53–93, Mar. 1992.

- [25] I. Kipnis, J. K. Kukielka, J. Wholey, and C. P. Snapp, "Silicon bipolar fixed and variable gain amplifier MMICs for microwave and lightwave applications up to 6 GHz," in *Proc. IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 1989, vol. 1, pp. 109–112.

- [26] M. C. Chiang, S. S. Lu, C. C. Meng, S. A. Yu, S. C. Yang, and Y. J. Chan, "Analysis, design, and optimization of InGaP–GaAs HBT matched-impedance wide-band amplifiers with multiple feedback loops," *IEEE J. Solid-State Circuits*, vol. 37, no. 6, pp. 694–701, Jun. 2002

- [27] "NEC Silicon Microwave Wideband Amplifier MMICs User Manual," 3rd ed. NEC, Tokyo, Japan, Apr. 1996 [Online]. Available: http://www.eu.necel.com/\_pdf/P11438EJ3V0UM00.PDF, Document No.EJ3V0UM00

- [28] E. M. Cherry and D. E. Hooper, "The design of wide-band transistor feedback amplifiers," *Proc. IEEE*, vol. 110, pp. 375–389, Feb. 1963.

- [29] S. S. Lu, Y. S. Lin, H. W. Chiu, Y. C. Chen, and C. C. Meng, "The determination of S-parameters from the poles of voltage-gain transfer function for RF IC design," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 1, pp. 191–199, Jan. 2005.

- [30] S. S. Lu, C. C. Meng, T. W. Chen, and H. C. Chen, "A novel interpretation of transistor S-parameters by poles and zeros for RF IC circuit design," *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 2, pp. 406–409, Feb. 2001.

- [31] P. R. Gray and R. G. Meyer, Analysis and Design of Analog Integrated Circuits, 4th ed. New York: Wiley, 2001, ch. 7.

- [32] C. K. Alexander and M. N. O. Sadiku, Fundamentals of Electric Circuits, International ed. New York: McGraw-Hill, 2000, pp. 50–51.

- [33] A. A. Abidi, "High-frequency noise measurements on FET's with small dimensions," *IEEE Trans. Electron Devices*, vol. ED-33, no. 11, pp. 1801–1805, Nov. 1986.

- [34] H.-K. Chen, D.-C. Chang, Y.-Z. Juang, and S.-S. Lu, "A compact wide-band CMOS low-noise amplifier using shunt resistive-feedback and series inductive-peaking techniques," *IEEE Microw. Wireless Compon. Lett.*, vol. 17, no. 8, pp. 616–618, Aug. 2007.

- [35] P. R. Gray, L. Hurst, S. H. Lewis, and R. G. Meyer, Analysis and Design of Analog Integrated Circuits, 4th ed. New York: Wiley, 2001, ch. 11.

- [36] A. A. Abidi, "General relations between IP2, IP3, and offsets in differential circuits and the effects of feedback," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 5, pp. 1610–1612, May 2003.

- [37] W. Liu, MOSFET Models for SPICE Simulation Including BSIM3v3 and BSIM4. New York: Wiley, 2001, ch. 4.

Tzung-Han Wu (S'06–M'08) was born in Taipei, Taiwan, in 1979. He received the B.S. and M.S. degrees from the Department of Electrical Engineering, National Chung-Hsing University, Taichung, Taiwan, in 2001 and 2003, respectively, and the Ph.D. degree from the Department of Communication Engineering, National Chiao Tung University, Hsinchu, Taiwan, in 2007. For his M.S. thesis, he worked on GaInP/GaAs HBTs, SiGe HBTs, and CMOS RFICs.

He is currently with the RFIC design team of MediaTek Inc., Hsinchu, Taiwan. His current research interests are in the areas of RFICs and analog ICs.

Dr. Wu is a member of Phi Tau Phi.

**Jin-Siang Syu** (S'09) was born in Taoyuan, Taiwan, in 1984. He received the B.S. degree from the Department of Communication Engineering, National Chiao Tung University, Hsinchu, Taiwan, in 2006, where he is currently working toward the Ph.D. degree in electrical engineering.

His current research interests are in the areas of RFICs.

Mr. Syu is a member of Phi Tau Phi.

Chin-Chun Meng (M'02) received the B.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, in 1985 and the Ph.D. degree in electrical engineering from University of California, Los Angeles, in 1992.

He is currently a Full Professor with the Department of Electrical Engineering, National Chiao Tung University, Hsinchu, Taiwan. His current research interests are in the areas of RFIC and microwave and millimeter-wave integrated circuits.