# 國立交通大學

電信工程學系

碩士論文

多媒體串流處理器之運算單元設計

1896

An ALU Cluster Design for Media Streaming Processors Architecture

研究生:林庭瑋

指導教授:關河鳴博士

中華民國九十四年九月

## 多媒體串流處理器之運算單元設計

#### An ALU Cluster Design for

#### Media Streaming Processors Architecture

研究生:林庭瑋 Student:Ting-Wei Lin

指導教授:闕河鳴 博士 Advisor: Dr. Herming Chiueh

#### A Thesis

Submitted to Department of Communication Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Communication Engineering September 2005 Hsinchu, Taiwan.

中華民國九十四年九月

## 多媒體串流處理器之運算單元設計

研究生:林庭瑋 指導教授:闕河鳴 博士

# 國立交通大學 電信工程學系碩士班

## 摘要

近期相關的研究已提出利用串流架構來解決多媒體應用在傳統處理器架構上執行的缺點。除此之外,對行動式的系統而言,低功率消耗的考量已變成一個重要的議題,但是目前的串流架構並沒有針對以上的要求去解決。因此,在本研究中提出了將一個多媒體串流架構與數個低功率電路設計的方法結合在一起來解決以上的要求。而本論文的目的是設計一個多媒體串流處理器的運算單元,且基於史丹佛大學所提出的串流處理器架構,在本研究的微架構上考慮了設計的可行性,及利用電腦輔助軟體的模擬結果來決定各個功能單元的架構。並且此架構結合了階層式的頻寬設計,來有效的利用記憶體之間的頻寬。在實驗數據的預估顯示上,針對多媒體應用及基頻通訊系統方面去執行所選定的標準檢查程式,並藉由動態的選擇所要使用的運算單元總數目,可將功率損耗與能量消耗變成可調整式的。因此,對於一個行動式的系統,其即時的效能表現與能量消耗之間的取捨成為可以做最佳化的。所以此提出的架構與相關類似的架構相比之下,已經對有限的電池壽命在功率消耗和執行時間之間提供一個重要的突破。

## An ALU Cluster Design for

#### Media Streaming Processors Architecture

Student: Ting-Wei Lin Advisor: Dr. Herming Chiueh

Department of Communication Engineering

National Chiao Tung University

Hsinchu, Taiwan

#### **Abstract**

Recent research has proposed using streaming architecture to provide a leap in media applications that are poorly matched to conventional processor architecture. Besides, low power considerations are becoming an important issue for mobile systems, but streaming architecture solutions do not fit in above requirements. Therefore, in this research, a combination of media streaming architecture and low power circuitry design methodology is proposed. An ALU Cluster design for media streaming architecture is presented in this thesis, which is based on Stanford Imagine stream architecture with the consideration of implementation feasibility. The back-end simulation results decide the final micro-architecture of each component, and utilize communication bandwidth hierarchy design to effectively solve the problem of scarce memory bandwidth. The experimental results show that the power and energy consumption of selected benchmark for multimedia and baseband communication systems become scalable by dynamic selecting the number of utilized ALU Clusters. Thus, the instant performance and energy consumption of an entire work can be optimized for mobile systems. The proposed design has provided a breakthrough for similar architectures.

$\Pi$

## **ACKNOWLEDGMENTS**

This thesis would not have been possible without the support of many exceptional people. First and foremost, thanks go to my research advisor, Professor Herming Chiueh. He has always been an inspiration to me and everyone else on this project through his vision and leadership. He also provided irreplaceable guidance for me when I needed for a fascinating problem, good advice, constructive criticism, support, and flexibility.

I would also like to thank all team members of the SoC LAB group, especially my classmates over the years: Elliott Lee, Gary Chan, Maggie Lin, and Uan Cheng. They not only put up with me all of those years, but also made my days as an enjoyable graduate student.

Finally, I can not say enough about the support provided by my family. My parents have been my biggest supporters and for that I am forever grateful. My sister and girlfriend have always providing timely encouragement and advice. To all of my friends and family members who have helped me in one way or another over the years, I would like to say thanks.

# **CONTENTS**

| 摘要                                                  | I   |

|-----------------------------------------------------|-----|

| Abstract                                            | II  |

| Acknowledgments                                     | III |

| Chapter 1 Introduction                              | 1   |

| Chapter 2 Background                                | 4   |

| 2.1 Design Methodology                              |     |

| 2.2 Stream Processing Model                         | 9   |

| Stream Processing Model      Related Research       | 11  |

| 2.4 Low Power Considerations                        | 13  |

| 2.5 Media Streaming Processor Architecture          | 13  |

| 1896                                                |     |

| Chapter 3 Design of ALU Cluster Microarchitecture   | 16  |

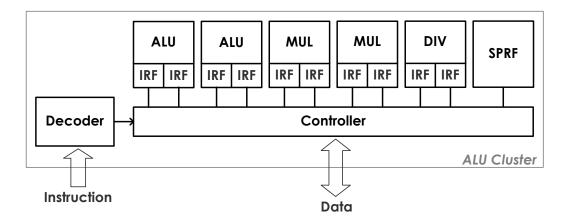

| 3.1 ALU Cluster Block Diagram                       | 16  |

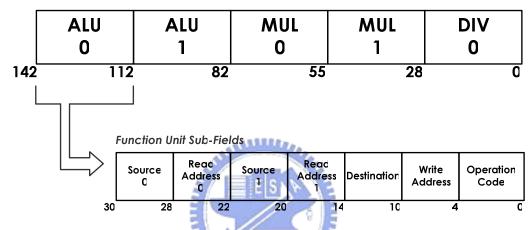

| 3.2 Instruction Set Format                          | 18  |

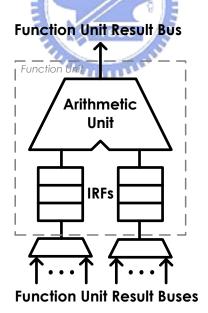

| 3.3 ALU Cluster Function Units                      | 19  |

| 3.3.1 ALU Unit                                      | 20  |

| 3.3.2 MUL Unit                                      | 21  |

| 3.3.3 DIV Unit                                      | 22  |

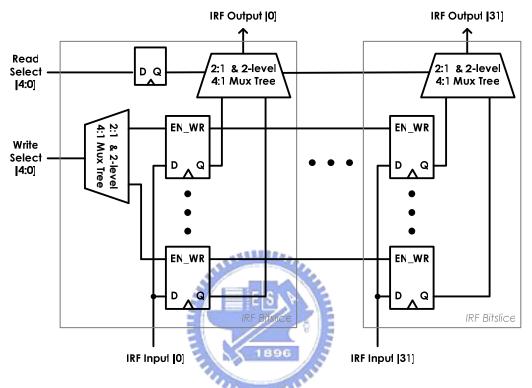

| 3.3.4 IRF Unit                                      | 23  |

| 3.3.5 SPRF Unit                                     | 24  |

| 3.3.6 Decoder Unit                                  | 25  |

| 3.3.7 Controller Unit                               | 25  |

| 3.4 System Operation                                | 25  |

| Chapter 4 Implementation                            | 28  |

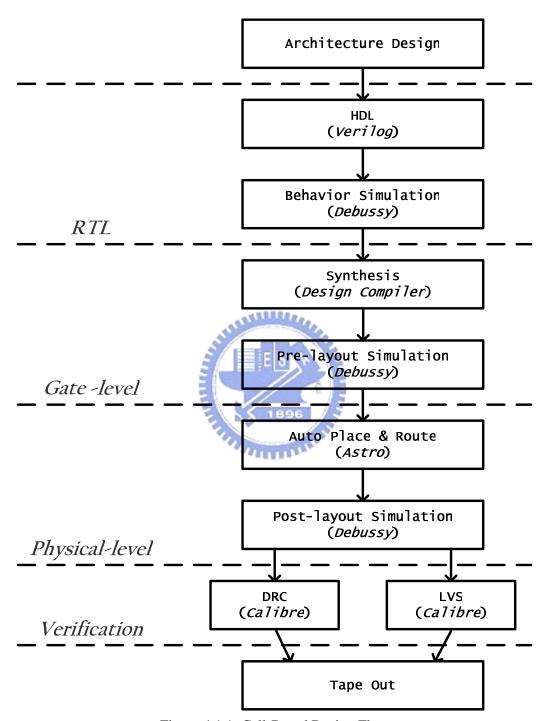

| 4.1 Design Flow                                     | 28  |

| 4.2 Circuit Implementation and Results              | 31  |

| 4.3 Circuit Verification and Performance Evaluation | 35  |

| 4.3.1 Test Bench: FIR Filter                                    | 35 |

|-----------------------------------------------------------------|----|

| 4.3.2 Functionality Verification                                |    |

| 4.3.3 Performance Evaluation Results                            | 41 |

| 4.4 Performance Comparison                                      | 44 |

| 4.5 Low Power Techniques Implementation                         | 45 |

| 4.6 Summary                                                     | 49 |

| Chapter 5 Conclusion                                            | 51 |

| Bibliography                                                    | 52 |

| Appendix A: Summary of the Defined Microcode in Instruction Set | 55 |

| Appendix B: Assembly Code of Test Bench                         | 57 |

# LIST OF TABLES

| Table 3.3.1.1 | The Operations Correspond to the ALU Unit                   | 20 |

|---------------|-------------------------------------------------------------|----|

| Table 3.3.1.2 | 2 Synthesis Results Correspond to Different Architecture    | 21 |

| Table 3.3.2.1 | The Operation Corresponds to the MUL Unit                   | 22 |

| Table 3.3.2.2 | 2 Synthesis Results Correspond to Different Pipeline Stages | 22 |

| Table 3.3.3.1 | The Operations Correspond to the DIV Unit                   | 23 |

| Table 3.3.3.2 | 2 Synthesis Results Correspond to Different Architecture    | 23 |

|               |                                                             |    |

| Table 4.2.1   | Circuit Summaries                                           | 31 |

| Table 4.2.2   | The Definition of the I/O Ports                             | 33 |

| Table 4.4.1   | Comparison Results                                          | 44 |

# LIST OF FIGURES

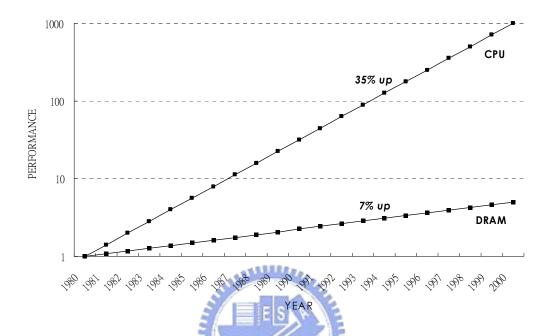

| Figure 1.1     | Gap between Processor and Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

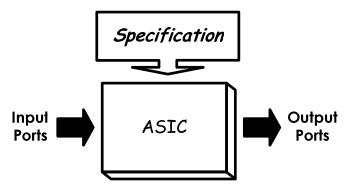

| Figure 2.1.1   | An Example of ASIC Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5  |

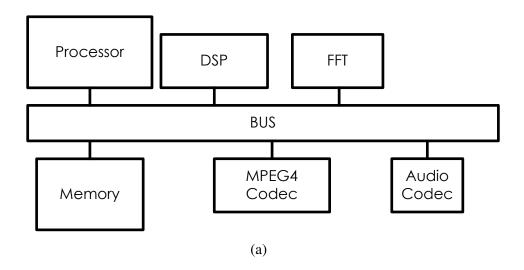

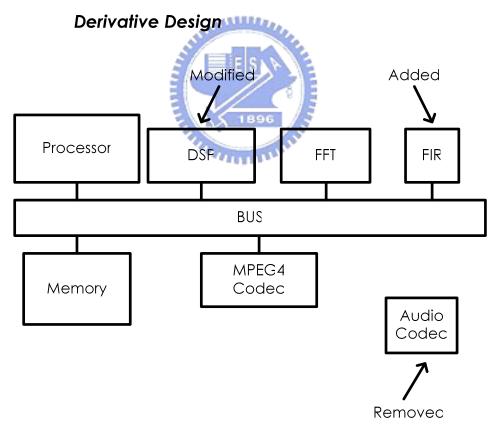

| Figure 2.1.2   | An Example of Platform-Based Architecture Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| Figure 2.1.3   | An Example of Reconfigurable Architecture Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

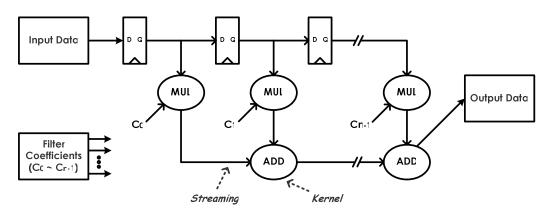

| Figure 2.2.1   | Direct-Form Realization of an FIR Filter System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| Figure 2.2.2   | A Simplified Structure of an FIR Filter System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

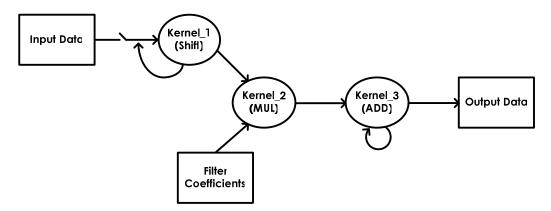

| Figure 2.5.1   | Media Streaming Processor Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| Figure 3.1.1   | ALU Cluster Architecture Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17 |

| Figure 3.2.1   | Instruction Set Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18 |

| Figure 3.3.1   | Function Unit Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19 |

| Figure 3.3.4.1 | IRF ArchitectureES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

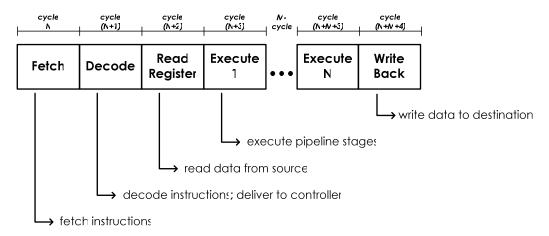

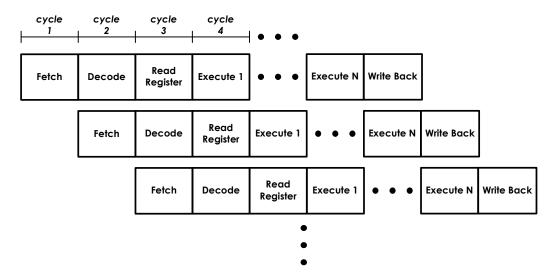

| Figure 3.4.1   | Pipeline Execution Diagram Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

| Figure 3.4.2   | Sequence Pipeline Operation Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27 |

|                | THE STATE OF THE S |    |

| Figure 4.1.1   | Cell-Based Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30 |

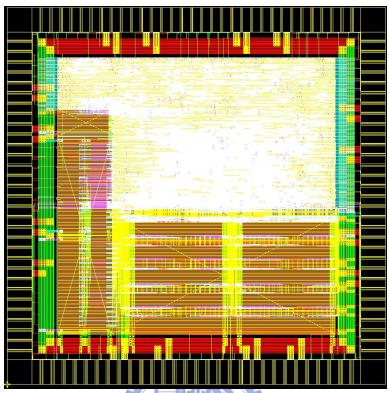

| Figure 4.2.1   | Layout of the ALU Cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32 |

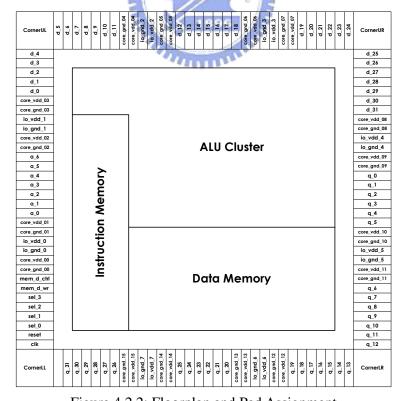

| Figure 4.2.2   | Floorplan and Pad Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32 |

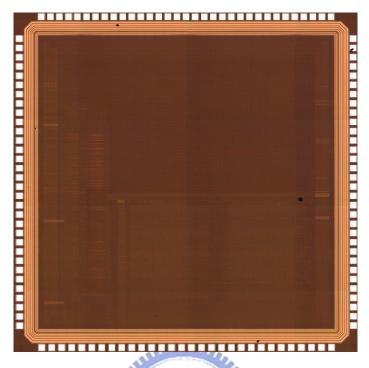

| Figure 4.2.3   | Die Microphotograph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

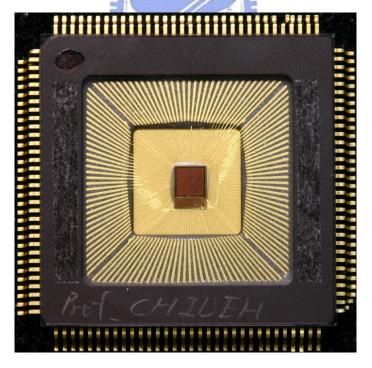

| Figure 4.2.4   | Photograph of Prototype with Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34 |

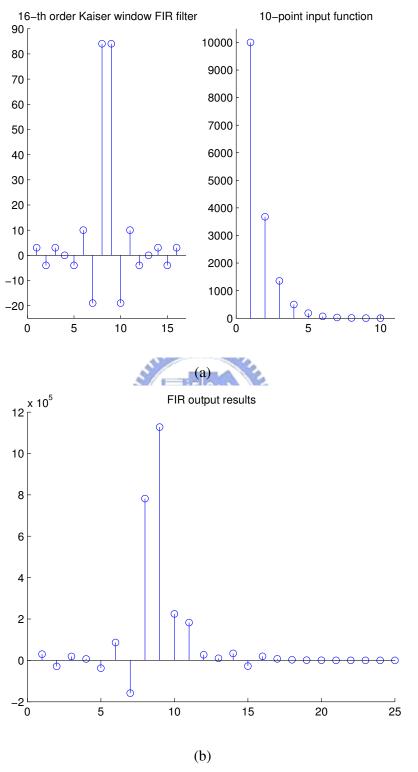

| Figure 4.3.1.1 | Filter Coefficients, Input Data, and Executed Results of the FIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|                | Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36 |

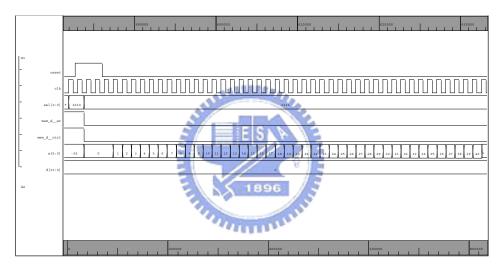

| Figure 4.3.2.1 | The Overall Operation Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39 |

| Figure 4.3.2.2 | The Operation of WRITE Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39 |

| Figure 4.3.2.3 | Insertion of Filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39 |

| Figure 4.3.2.4 | Insertion of Input Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40 |

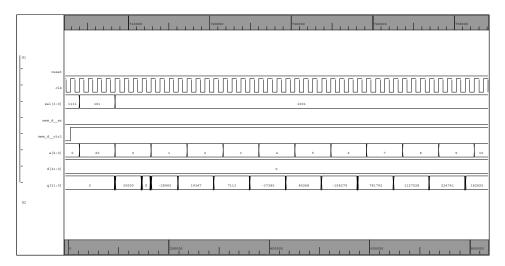

| Figure 4.3.2.5 | The Operation of EXECUTION Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40 |

| Figure 4.3.2.6 | The Operation of READ Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40 |

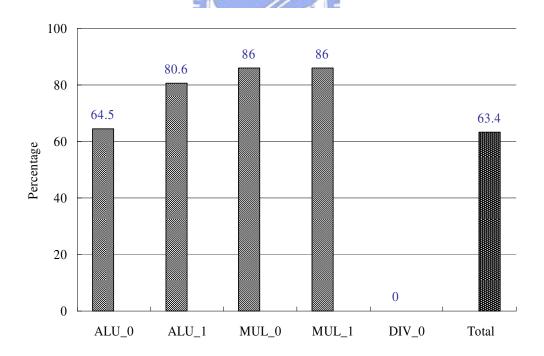

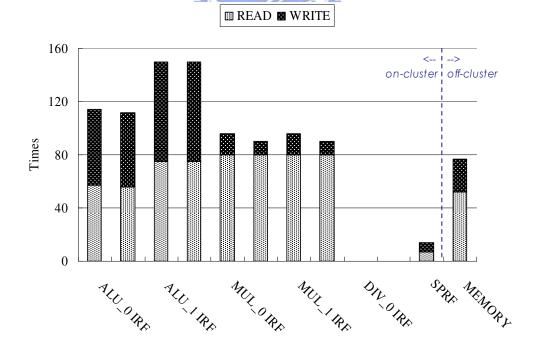

| Figure 4.3.3.1 | The Code Utilization of Each Arithmetic Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42 |

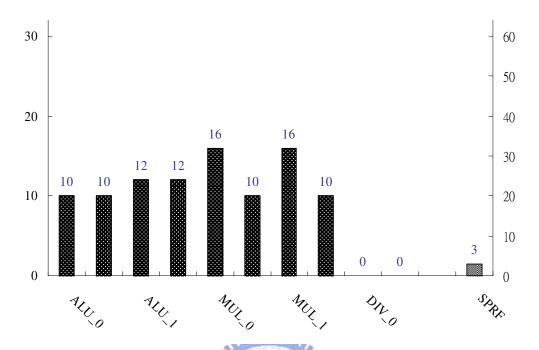

| Figure 4.3.3.2 | The Memory Utilization for Capacity Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43 |

| Figure 4.3.3.3 | The Memory Utilization for Data Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43 |

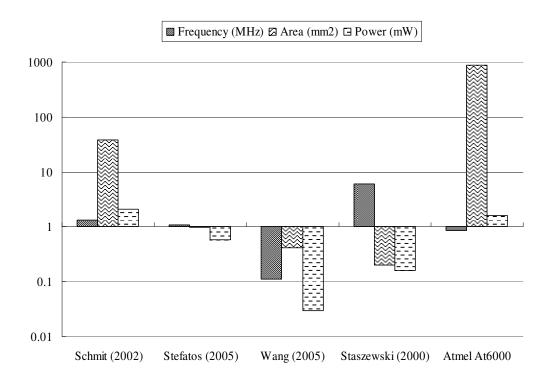

| Figure 4.4.1 | The Normalized Comparison Results                        | 45 |

|--------------|----------------------------------------------------------|----|

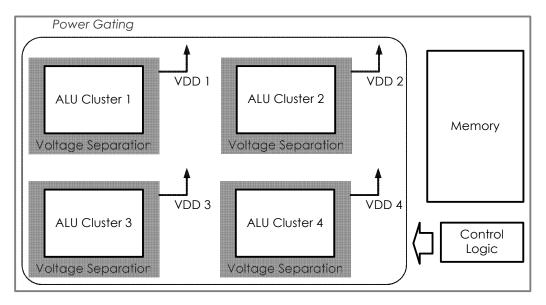

| Figure 4.5.1 | Multi-Cluster Architecture with Low Power Techniques     | 47 |

| Figure 4.5.2 | Layout of Multi-Cluster with Low Power Equipments        | 47 |

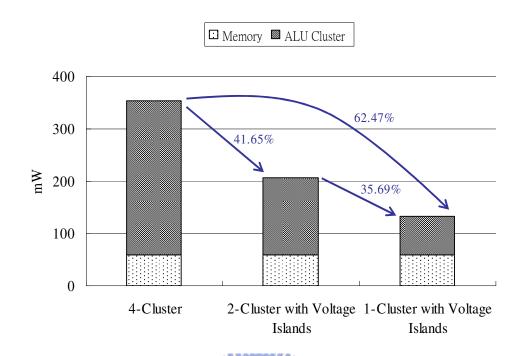

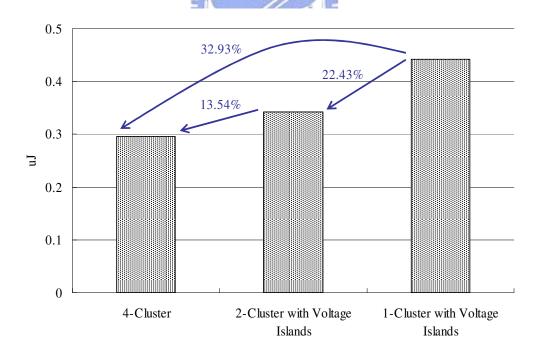

| Figure 4.5.3 | Power Dissipation on the Multi-Cluster Architecture      | 48 |

| Figure 4.5.4 | Energy Consumption on the Multi-Cluster Architecture     | 48 |

| Figure 4.5.5 | Future Mobile Multimedia and Communication System Design |    |

|              | Trend                                                    | 49 |

# CHAPTER 1 INTRODUCTION

Media processing applications have possession of three key important characteristics: large available parallelism, little data reuse, and a high computation of memory access ratio [1]. However, these characteristics are poorly matched to conventional general-purpose architectures. In the mean time, there is a processor-memory performance gap as well as a memory wall problem arisen that goes off-chip from processor to memory incurs severe latency and bandwidth penalties, as shown in Figure 1.1 [2]. In recent years, the current research has proposed to use the streaming architecture by fitting modern very large scale integrated-circuit (VLSI) technology with lots of arithmetic logic units (ALUs) on a single chip and the hierarchical communication bandwidth design to provide a leap in media processing applications [3][4][5]. Relative topics of recent research are Imagine Stream Processor [6][7][8], Smart Memories [9], and Processing-In-Memory [10][11]. Nevertheless, in contemporary VLSI circuitry for mobile systems, such as handheld audio and video applications, low power considerations are becoming an important issue as battery life and geometry of mobile systems are limited [12]. The streaming architecture and processor-in-memory solutions do not fit in above requirements since it generally occupies a huge die size to trade for the data and processing parallelism. Thus, in recent developments, most of these architectures are focused on the super computing architectures rather than the media processing applications.

However, the streaming architecture has been suggested as an efficient architecture for both media processing applications and baseband architecture by using the software defined radio mechanism [13][14]. In order to design the next generation portable multimedia and communication systems, the power dissipation of such a system is an emergency issue. Therefore, a low-power ALU Cluster for the streaming architecture is proposed, which combines the software-defined mechanism

and the modern low-power circuitry technique in the streaming architecture to provide a breakthrough in the operating time and power dissipation in the limited battery power.

Figure 1.1: Gap between Processor and Memory

In this thesis, our major motivation is to improve media processing applications weakly matched to conventional processor architectures. In other words, we aim at the micro-architecture design of the 32-bit ALU Cluster for media streaming processor architectures because ALU Cluster is the nexus computation part of the processors and one main factor of increasing high kernel performance. However, two primary problems have been met are the required high computation throughput and the processor-memory performance gap. So our proposed solution methods to solve these performance bottlenecks are concurrency and locality, respectively. Concurrency is to provide abundant data-level parallelism which means moderate multiple function units in one ALU Cluster. Locality is to decrease the use of the global bandwidth to access the high latency off-chip memory, which means the temporary high speed storage units included inside the ALU Cluster that could form the memory bandwidth hierarchy architectures. With these solution methods, the performance of the media processing applications can be greatly improved.

This thesis focuses on an ALU Cluster architecture design of media streaming processors. The remaining of organization of this thesis is as follow.

In Chapter 2, the various design methodology styles, the streaming applications processing model, the current relative research topics, and the proposed media streaming processor architecture are introduced.

In Chapter 3, the detail micro-architecture of each components of ALU Cluster is designed. Instruction set format, and overall system pipeline operation from instructions read, data reads, operations execute to outcome writes back are also explained.

In Chapter 4, the electronic design automation (EDA) flow of implementing this work is presented. The benchmark simulation, performance evaluation, and comparison to recent related architecture design reports are discussed. Besides, a low power ALU Cluster design under group collaboration is also presented.

In Chapter 5, the conclusion of this proposed design is addressed.

# CHAPTER 2 BACKGROUND

In this chapter, a briefly review of the background of the design methodology about three different design implementation styles, and three primary related research topics nowadays about the streaming architectures are described. In addition, the proposed media streaming processor architecture that bases on improving the disadvantages of the current existed streaming architectures is presented.

#### 2.1 Design Methodology

Generally speaking, there are many different methods when implementing a design. In this section, three distinct design methodology styles which are application-specific architecture, platform-based architecture, and reconfigurable architecture will be briefly introduced on the basis of time to market demands, physical area, utilizing flexibility, etc. Furthermore, the pros and cons of these design methodology styles are also discussed.

First, the application-specific architecture design is easier among these architectures. Figure 2.1.1 is plotted an example of application-specific integrated circuit (ASIC) design. The chip implementation could be finished quickly as long as following the given well-defined specification. The physical area, operation frequency, and power dissipation could be optimized that depends on demands, too. Nevertheless, the application-specific architecture design is not so flexible and reusable, and needs to redo the overall design flow while the specific applications or specifications are changed.

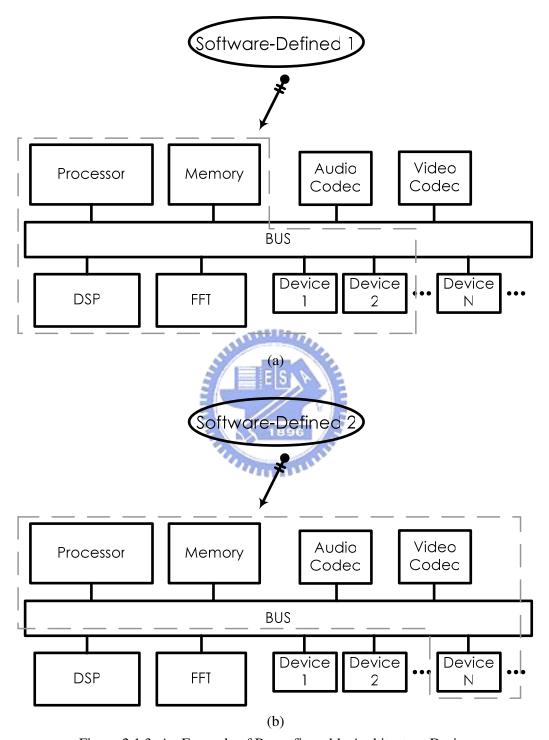

Figure 2.1.1: An Example of ASIC Design

Second, the platform-based architecture design is more flexible than application-specific architecture design. An example of platform-based architecture design is given in Figure 2.1.2. The general platform-based architectures typically include a processor, memory, and communication bus [15]. The intellectual property (IP), such as digital signal processing (DSP), fast Fourier transform (FFT), moving pictures experts group (MPEG) coder and decoder, and audio/video compression and decompression, etc, are all designed with the same protocol of bus and available from the IP libraries to the platform by the application demands. For example, the general platform-based architecture with DSP and audio/video compression decompression can be used for the video applications, or with DSP and FFT filter can be used for baseband communication. In Figure 2.1.2.(a), the reference design is set for the original specific applications. However, when the specific applications or the required functions are changed, the IP block could be modified, added, and removed to reach the derivatives design which is depicted in Figure 2.1.2.(b). Therefore, the major characteristic of platform-based architecture design is to reduce the design time, since all the devices are based on the same protocol of bus and can be integrated quickly. Unlike application-specific architecture design, the platform-based architecture design could extend to execute more applications by including the extra required IP blocks. In the mean time, the power dissipation will be increased when more and more IP blocks included. The idle unused IP blocks will also waste unnecessary power dissipation. However, in current VLSI circuitry for mobile systems, low power considerations are becoming an important subject since battery life and geometry of mobile systems are limited. Besides, the speed performance will be depended on the slower function units, or mismatch between IP blocks and communication bus. In addition, the scarce memory bandwidth problem between IP blocks and communication bus is not solved totally.

#### Reference Design

(b) Figure 2.1.2: An Example of Platform-Based Architecture Design