# Current-mode design techniques in low-voltage 24-GHz RF CMOS receiver front-end

Chung-Yu Wu · Wen-Chieh Wang · Fadi R. Shahroury · Zue-Der Huang · Hao-Jie Zhan

Received: 1 August 2007/Revised: 18 December 2007/Accepted: 20 December 2007/Published online: 19 January 2008 © Springer Science+Business Media, LLC 2008

**Abstract** A new high frequency CMOS current-mode receiver front-end composed of a current-mode low noise amplifier (LNA) and a current-mode down-conversion mixer has been proposed in the frequency band of 24 GHz and fabricated in 0.13-µm 1P8M CMOS technology. The measurement of the current-mode receiver front-end exhibits a conversion gain of 11.3 dB, a noise figure (NF) of 14.2 dB, the input-referred 1-dB compression point  $(P_{-1\,dB})$  of -13.5 dBm and the input-referred third-order intercept point  $(P_{\text{IIP3}})$  of -1 dBm. The receiver dissipates 27.8 mW where the supply of LNA is 0.8 V and the supply of mixer is 1.2 V. The power consumption of output buffer is not included. The receiver front-end occupies the active area of  $1.45 \times 0.72 \text{ mm}^2$  including testing pads. The measured results show that the proposed current-mode approach can be applied to a high-frequency receiver frontend and is capable of low-voltage applications in the advanced CMOS technologies.

**Keywords** 24-GHz · CMOS · Current-mode · Receiver front-end

C.-Y. Wu  $(\boxtimes)\cdot$  W.-C. Wang  $\cdot$  F. R. Shahroury  $\cdot$  Z.-D. Huang  $\cdot$  H.-J. Zhan

Nanoelectronics and Gigascale Systems Laboratory, Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

e-mail: cywu@alab.ee.nctu.edu.tw

W.-C. Wang

e-mail: wangste@ieee.org

F. R. Shahroury

e-mail: fadirs@gmail.com

Z.-D. Huang

e-mail: zuederhu@gmail.com

## 1 Introduction

Over the last two decades, the frequency spectra below 10 GHz have gradually become crowded because of massive requirements of data transmission from the modern wireless applications such as Bluetooth, wireless local area network (WLAN) and ultra-wideband (UWB), etc. Consequently, many researchers start to investigate RF transceiver front-end circuits in much higher frequency bands like 24 and 60 GHz for example because higher operating frequency can provide more bandwidth. In addition to the original industrial-science-medical (ISM) band within 24-24.25 GHz, the FCC has opened the 22-29-GHz frequency band in 2002 for short-range automotive radar systems, autonomous cruise control (ACC) for example [1]. In the 24-GHz frequency range, some applications such as radars, wireless local area networks, point-to-point wireless communications, local multipoint distribution services (LMDS) and other ISM band applications are implemented by CMOS, SiGe BiCMOS and III-V compound semiconductor [2–6].

Table 1 shows the pros and cons of different technologies which are used for the implementation of 24-GHz systems. Although III–V compound semiconductor and SiGe BiCMOS have good performance in higher frequency RF circuits, the cost of these technologies is relatively higher than CMOS technologies. In addition, these technologies suffer from the difficulties to integrate with complex digital systems which are usually realized by CMOS technologies for low cost and low power. With the fast advancement of CMOS technologies, the nanometer CMOS technologies have already become a candidate to realize 24-GHz or even 60-GHz RF systems. Consequently, nanometer CMOS technologies are recommended to realize 24-GHz systems because of their advantages of

Table 1 The pros and cons of different technologies

|                        | GaAs | BiCMOS   | CMOS     |

|------------------------|------|----------|----------|

| g <sub>m</sub>         | High | High     | Low      |

| $f_{ m T}$             | High | Moderate | Moderate |

| RF performance         | High | High     | Moderate |

| Yield                  | Low  | Moderate | High     |

| Integration            | Low  | Moderate | High     |

| Cost                   | High | Moderate | Low      |

| Technology improvement | Slow | Moderate | Fast     |

|                        |      |          |          |

higher integration level, smaller chip area, lower power consumption and lower cost.

As the CMOS technology is scaled down to nanometer nodes, the supply voltage is gradually reduced to around or even below 1 V. The lower the supply voltage, the smaller the voltage headroom is left in the design of CMOS RF circuits. In voltage-mode circuits, the impedances of internal nodes are usually large so that the signal information can be mostly carried with the time-varying voltage signals. Since large enough voltage swing is required to keep signal information, it is difficult for voltage-mode circuits to use reduced voltage headroom under low supply voltage.

In current-mode circuits, however, the impedances of internal nodes are smaller than those in voltage-mode circuits and voltage swings at internal nodes become smaller. But the signal information is mainly carried with the time-varying current signals. Consequently, current-mode circuits can be designed under small voltage headroom. Furthermore, when dealing with signal processing, it is easy to perform the function of summation by simply connecting the signal paths together without additional amplifiers. Thus power consumption can be further reduced. With the above advantages, current-mode RF circuits are capable of operating in low supply voltage and dissipating smaller power. The current-mode design techniques can have great potential in the design of CMOS RF front-end in the advanced nanometer CMOS technologies.

Two current-mode CMOS RF front-end circuits have been published by the present authors [7, 8]. A 24-GHz current-mode power amplifier (PA) was designed in 0.13-µm bulk CMOS technology [7]. This CMOS current-mode PA can achieve large output power with high power added efficiency (PAE) in the 24-GHz frequency range. The proposed PA is capable of operating in the low supply voltage of 1.2 V. In [8], a 24-GHz transmitter using current-mode approach in 0.13-µm CMOS technology is proposed. The transmitter is operated in low supply voltage of 1 V, and it consumes very small power. So far, no current-mode CMOS receiver circuit is proposed.

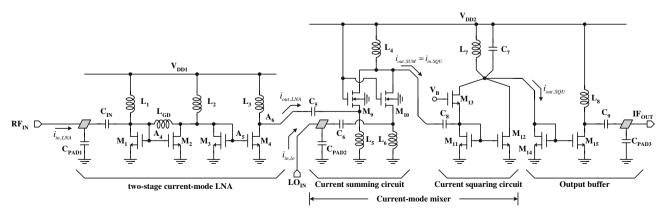

The first 24-GHz receiver front-end using current-mode design techniques in 130-nm CMOS technology is

proposed, analyzed, and measured. The proposed currentmode receiver front-end is of single-balance structure and integrated with a current-mode LNA and a current-mode down-conversion mixer. In the proposed current-mode LNA, two cascaded current-mirror amplifiers are adopted to realize the amplification of current signals. Following the LNA is the current summing circuit to perform the summation of RF and LO signals. The summed signal is sent to the current squaring circuit to perform the function of current mixing of RF and LO signals. The measurement results have shown that the proposed current-mode CMOS receiver achieves the conversion gain of 11.3 dB, the  $P_{1\,dB}$ of -13.5 dBm, and the  $P_{\rm IIP3}$  of -1 dBm. The measured total NF is 14.2 dB at RF frequency of 24 GHz and LO frequency of 19 GHz. The current-mode receiver front-end dissipates 27.8 mW under the condition that the supply of the LNA is 0.8 V and the supply of the mixer is 1.2 V. Compared to other implementations for 24-GHz receiver front-ends in [2] and [5], the proposed 24-GHz currentmode receiver front-end has the advantage of low-voltage operation and low-power dissipation with comparable performances.

In Sect. 2, the architecture, operational principles, and circuit realizations of CMOS current-mode RF receiver front-end are described. The experimental chip is designed and fabricated in 130-nm 1P8M CMOS technology. The measurement results are presented in Sect. 3 to verify the circuit performances. Finally, the conclusion is given in Sect. 4.

#### 2 Operational principles and circuit realizations

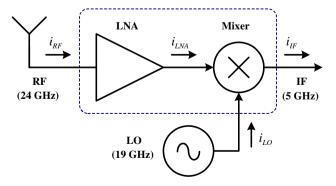

The block diagram of the designed 24-GHz receiver frontend is shown in Fig. 1. It is composed of a LNA and a mixer. The off-chip signal generator provides the local oscillator (LO) signal for the receiver. With the LO signal at 19 GHz, the received RF signal at 24 GHz is

Fig. 1 Block diagram of the 24-GHz current-mode receiver front-end

down-converted to the intermediate frequency (IF) which is at the frequency band of 5 GHz by the Mixer. The IF is chosen at 5 GHz so that the mature RF receiver front-end circuits at 5 GHz can be adopted to realize the second-step down-conversion from the IF to the baseband.

In the design of CMOS LNA, the CMOS current-mirror structure is adopted as the current amplifier and two stages of current-mirror amplifiers are cascaded to provide sufficient gain. As for the current-mode down-conversion mixer, the high frequency analog current multiplier is proposed. It consists of a current summing circuit and a current squaring circuit. The detailed circuit designs and analyses are presented in the following.

#### 2.1 Current-mode LNA

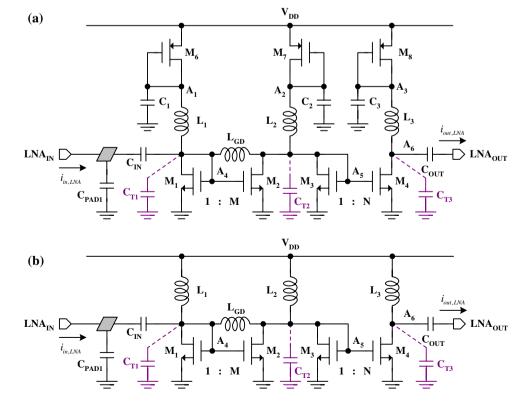

The circuit diagram of the proposed current-mode LNA is shown in Fig. 2(a) where  $M_1$  and  $M_2$  form the first-stage current-mirror amplifier and  $M_3$  and  $M_4$  form the second stage cascaded with the first stage. All MOS are operated in the saturation region. The aspect ratio of  $M_2$  is designed M times of that of  $M_1$  whereas the aspect ratio of  $M_4$  is designed N times of that of  $M_3$ . Therefore, the gate-source capacitances of  $M_2(M_4)$ ,  $C_{GS,M_2}(C_{GS,M_4})$ , is about M(N) times of  $C_{GS,M_1}(C_{GS,M_3})$ .  $M_6-M_8$  with gate shorted to drain are used to reduce the supply voltage to the amplifiers

so that the LNA can be biased well and operated at low dc power dissipation. The bypass capacitors  $C_1-C_3$  are used at the nodes  $A_1-A_3$ , respectively, to make them ac ground and bypass the supply noise. If  $V_{\rm DD}$  is low enough,  $M_6-M_8$  and  $C_1-C_3$  is not required as shown in Fig. 2(b). To reduce the signal losses at the operating frequency, the inductors  $L_1-L_3$  are chosen as the loads of the current-mode LNA to resonate out the parasitic capacitances  $C_{T_1}$ ,  $C_{T_2}$ , and  $C_{T_3}$  at the nodes  $A_4$ ,  $A_5$ , and  $A_6$ , respectively, where  $C_{T_1}=(1+M)C_{{\rm GS},M_1}+C_{{\rm DS},M_1}$ ,  $C_{T_2}=(1+N)C_{{\rm GS},M_3}+C_{{\rm DS},M_2}+C_{{\rm DS},M_3}$  and  $C_{T_3}=C_{{\rm DS},M_4}$ .

The input ac coupling capacitor  $C_{\rm IN}$  and the input pad with the capacitance of  $C_{\rm PAD1}$  form the input matching network of the current-mode LNA.  $C_{\rm OUT}$  is the capacitor that blocks dc between LNA and the following current-mode mixer. Only ac current signals can pass to the next stage.  $L_{\rm GD}$  is designed to resonate out the gate-drain capacitor  $C_{\rm GD2}$  of  $M_2$  at the operating frequency  $\omega_0$  in order to enhance the reverse isolation of the LNA. After resonating out the parasitic capacitances of the transistor between its gate and drain, the transistor becomes more unilateral so that the stability can be improved. In addition, the input matching network is easier to design because of good isolation of the LNA.

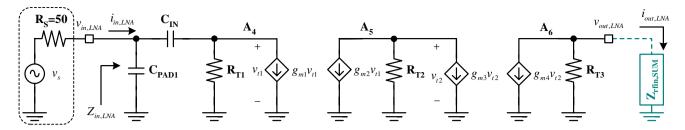

At the operating frequency  $\omega_0$ , inductors  $L_1-L_3$  and the respective parasitic capacitors  $C_{T_1}-C_{T_3}$  are resonated. The small-signal equivalent circuits of the current-mode

Fig. 2 (a) Circuit diagram of the current-mode LNA and (b) circuit diagram of the currentmode LNA of low-voltage version

Fig. 3 Small-signal equivalent circuit of the current-mode LNA at the operating frequency  $\omega_0$

LNA of Fig. 2(a) and 2(b) at the operation frequency  $\omega_0$  are the same and can be depicted in Fig. 3 where  $R_{T_1}=(R_{p,L_1}//r_{o,M_1}), \quad R_{T_2}=(R_{p,L_2}//r_{o,M_2}//r_{o,M_3})$  and  $R_{T_3}=(R_{p,L_3}//r_{o,M_4}). R_{p,L_1}-R_{p,L_3}$  are the equivalent parallel resistances of the inductors  $L_1-L_3$ .  $r_{o,M_1}-r_{o,M_4}$  and  $g_{m_1}-g_{m_4}$  are the output impedance and transconductance of the transistors  $M_1-M_4$ , respectively. Because the circuit dimensions are much smaller than the wavelengths involved, the distributed effect of circuits is negligible. Thus the lumped small-signal equivalent circuit is adopted.

From Fig. 3, the input impedance  $Z_{in,LNA}$  in s-domain can be expressed as

$$Z_{\text{in,LNA}}(s) = \frac{1}{sC_{\text{PADI}}} \| \left[ \frac{1}{sC_{\text{IN}}} + \left( R_{T_1} \| \frac{1}{g_{m_1}} \right) \right]$$

$$= \frac{(1 + g_{m_1}R_{T_1}) + sR_{T_1}C_{\text{IN}}}{s(C_{\text{PADI}} + C_{\text{IN}}) + s^2C_{\text{PADI}}C_{\text{IN}}R_{T_1}}.$$

(1)

Let  $s = j\omega$  and the input impedance of the LNA can be calculated as

The imaginary part of the  $Z_{\text{in,LNA}}$  can be eliminated at  $\omega_0$  if the following equation is satisfied.

$$(1 + g_{m_1}R_{T_1})(C_{PAD1} + C_{IN}) - \omega_0^2 R_{T_1}^2 C_{IN}^2 C_{PAD1} = 0.$$

(3)

Thus the relation among  $C_{\text{IN}}$ ,  $C_{\text{PAD1}}$ ,  $R_{T_1}$ ,  $g_{m_1}$ , and  $\omega_0$  can be designed according to the following equation

$$\omega_0 = \frac{1}{R_{T_1} C_{\text{IN}}} \sqrt{(1 + g_{m_1} R_{T_1}) \left(1 + \frac{C_{\text{IN}}}{C_{\text{PAD1}}}\right)}.$$

(4)

Substituting (4) into (2), the input impedance at the operation frequency  $\omega_0$  can be expressed as

$$Z_{\text{in,LNA}}|_{\omega=\omega_0} = \frac{R_{T_1}C_{\text{IN}}[(C_{\text{PAD1}} + C_{\text{IN}}) - (1 + g_{m_1}R_{T_1})C_{\text{PAD1}}]}{\left[(C_{\text{PAD1}} + C_{\text{IN}})^2 + (\omega_0R_{T_1}C_{\text{PAD1}}C_{\text{IN}})^2\right]}.$$

(5)

To calculate the current gain  $A_i$  and the voltage gain  $A_{\nu}$  of the LNA, the input impedance  $Z_{\rm rfin,SUM}$  of the following current mixer should be taken into considerations. From Fig. 3, the current gain  $A_i$  at the operating frequency  $\omega_0$  can be calculated and expressed as

$$\begin{aligned} A_{i}|_{\omega=\omega_{0}} &\equiv \frac{i_{\text{out,LNA}}}{i_{\text{in,LNA}}} \Big|_{\omega=\omega_{0}} \\ &= \frac{g_{m_{2}}g_{m_{4}}R_{T_{1}}R_{T_{2}}}{(1+g_{m_{3}}R_{T_{2}})\sqrt{(1+g_{m_{1}}R_{T_{1}})^{2}(1+C_{\text{PAD1}}/C_{\text{IN}})^{2}+\omega_{0}^{2}R_{T_{1}}^{2}C_{\text{PAD1}}^{2}}} \cdot \left(\frac{R_{T_{3}}}{Z_{\text{rfin,SUM}}+R_{T_{3}}}\right). \end{aligned}$$

(6)

$$\begin{split} Z_{\text{in,LNA}}(j\omega) &= \frac{\omega R_{T_{1}} C_{\text{IN}}[(C_{\text{PAD1}} + C_{\text{IN}}) - (1 + g_{m_{1}} R_{T_{1}}) C_{\text{PAD1}}]}{\omega \Big[ (C_{\text{PAD1}} + C_{\text{IN}})^{2} + (\omega R_{T_{1}} C_{\text{PAD1}} C_{\text{IN}})^{2} \Big]} \\ &- j \frac{\Big[ (1 + g_{m_{1}} R_{T_{1}}) (C_{\text{PAD1}} + C_{\text{IN}}) - \omega^{2} R_{T_{1}}^{2} C_{\text{IN}}^{2} C_{\text{PAD1}} \Big]}{\omega \Big[ (C_{\text{PAD1}} + C_{\text{IN}})^{2} + (\omega R_{T_{1}} C_{\text{PAD1}} C_{\text{IN}})^{2} \Big]}. \end{split}$$

(2)

In order to achieve maximum power transfer,  $Z_{\text{in,LNA}}$  should be equal to 50  $\Omega$  at the operation frequency  $\omega_0$ .

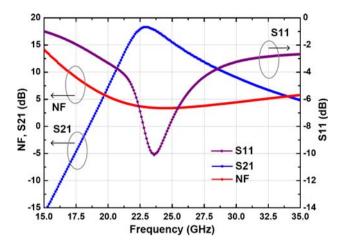

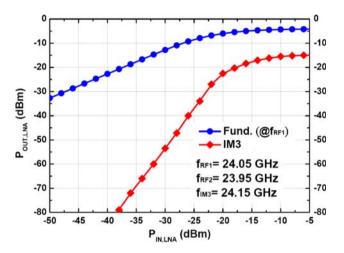

The simulated gain, NF, and input matching characteristics of the current-mode LNA in Fig. 2(b) are shown in Fig. 4. The LNA can achieve the maximum gain of 17 dB at the operating frequency of 24 GHz. It can reach the NF of 3.4 dB at 24 GHz. The linearity performance of the LNA is verified by harmonic balance (HB) simulation. With the signals at 23.9 and 24.1 GHz, the simulated linearity curves shown in Fig. 5 depicts a  $P_{-1\,\mathrm{dB,LNA}}$  of  $-18.5\,\mathrm{dBm}$  and a  $P_{\mathrm{IIP3,LNA}}$  of  $-10.8\,\mathrm{dBm}$ . The LNA in Fig. 2(b) drains 20.4 mA from the supply voltage of 0.8 V and drains 34.82 mA from the supply voltage of

Fig. 4 Simulated gain, NF, and input matching characteristics of the current-mode LNA

Fig. 5 Simulated linearity performance of the current-mode LNA

$1.2~\rm V$ . The increase in simulated current consumption from  $20.4~\rm to~34.82~mA$  is because the overdrive voltage of LNA is changed from  $0.8~\rm to~1.2~\rm V$  as the supply voltage is increased from  $0.8~\rm to~1.2~\rm V$ .

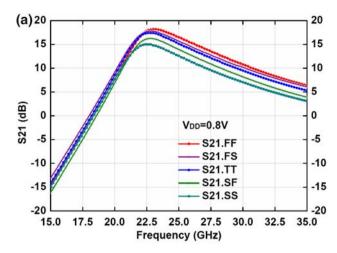

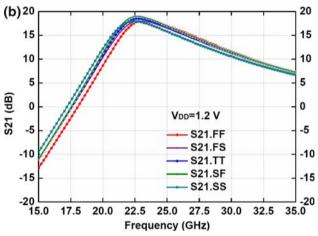

The accuracy of the gain  $(S_{21})$  of the LNA over different process corners including FF, FS, TT, SF, SS are depicted in Fig. 6(a) and (b). The  $S_{21}$  is varied from around 17.6 to 13.8 dB at the supply voltage of 0.8 V and is varied from about 18.1 to 16.9 dB at the supply voltage of 1.2 V.

## 2.2 Current-mode down-conversion mixer

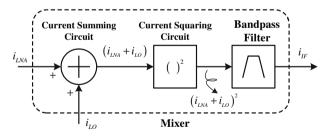

The conceptual block diagram of the proposed current-mode down-conversion mixer is depicted in Fig. 7. This mixer is composed of a current summing circuit, a current squaring circuit, and a band-pass filter (BPF). The RF input

**Fig. 6**  $S_{21}$  of the LNA in different process corners (a) at the supply voltage of 0.8 V and (b) at the supply voltage of 1.2 V

Fig. 7 Conceptual block diagram of the current-mode down-conversion mixer

current signal  $i_{\rm LNA} = I_{\rm LNA}\cos\omega_{\rm RF}t$  from the current-mode LNA and the LO input current signal  $i_{\rm LO} = I_{\rm LO}\cos\omega_{\rm LO}t$  from the off-chip LO signal generator are summed in advance through the current summing circuit. The summed current signal  $i_{\rm SUM} = (i_{\rm LNA} + i_{\rm LO}) = (I_{\rm LNA}\cos\omega_{\rm RF}t + I_{\rm LO}\cos\omega_{\rm LO}t)$  are sent to the following current squaring circuit which results in the square components of  $i_{\rm LNA}^2$  and  $i_{\rm LO}^2$  and the multiplication component  $i_{\rm LNA} \times i_{\rm LO}$ . The

multiplication component of two current input signals provides the function of double sideband mixing.

Through the double sideband mixing, the received 24-GHz signal is converted to 5 GHz which is the lower sideband (LSB) and 43 GHz which is the upper sideband (USB) with the LO signal at 19 GHz. Following the current squaring circuit is the BPF which is capable of frequency selectivity. In this receiver design, the center frequency of the BPF is designed at 5 GHz so that the targeted LSB can be obtained and the unwanted USB can be attenuated. The detailed operational principles of the current squaring circuit and the current summing circuit are described in the following subsections.

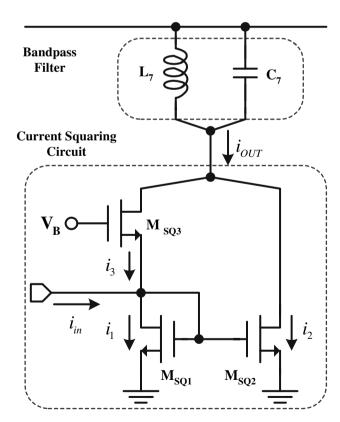

## 2.2.1 Current squaring circuit and band-pass filter

The conceptual circuit of the current squaring circuit as modified from [9] is shown in Fig. 8 where  $M_{\rm SQ_1}$  and  $M_{\rm SQ_2}$  are current mirror circuit. The bulk and source of  $M_{\rm SQ_3}$  are connected together to eliminate the body effect. Assume that both short-channel effect and channel-length modulation effect are negligible, and the MOS transistors  $M_{\rm SQ_1}-M_{\rm SQ_3}$  are well matched with the same channel width/length W/L. If all MOS devices are in the saturation

Fig. 8 Circuit diagram of the current squaring circuit and bandpass filter

$$v_{\text{GS,MSQ}_1} = \frac{V_{\text{B}}}{2} + \frac{i_{\text{in}}}{k_n \frac{W}{L} (V_{\text{B}} - 2V_{\text{th}})},\tag{7}$$

$$v_{\text{GS,MSQ}_3} = \frac{V_{\text{B}}}{2} - \frac{i_{\text{in}}}{k_n \frac{W}{K} (V_{\text{R}} - 2V_{\text{th}})},\tag{8}$$

where  $k_n = \mu_n C_{\rm OX}$  is the mobility  $\mu_n$  times the oxide capacitance per unit area  $C_{\rm OX}$ ,  $V_{\rm th}$  is the threshold voltage,  $v_{\rm GS}$  is gate-to-source voltage, and  $V_{\rm B}$  is the dc bias voltage of the current squaring circuit and equal to  $(v_{\rm GS,MSQ_1} + v_{\rm GS,MSQ_2})$ . From (7) and (8), the drain currents  $i_1$  and  $i_3$  of  $M_{\rm SQ_1}$  and  $M_{\rm SQ_3}$ , respectively, can be calculated. Since  $i_1 = i_2$ , the output current  $i_{\rm OUT}$  can be written as

$$i_{\text{OUT}} = i_1 + i_3 = I_{\text{B}} + \frac{i_{\text{in}}^2}{4I_{\text{R}}},$$

(9)

where

$$I_{\rm B} = \frac{1}{4} k_n \frac{W}{I} (V_{\rm B} - 2V_{\rm th})^2. \tag{10}$$

Suppose the input current  $i_{\rm in}$  of the current squaring circuit equals  $(I_{\rm RF}\cos\omega_{\rm RF}t+I_{\rm LO}\cos\omega_{\rm LO}t)$ , the output current signal of the current squaring circuit from (9) can be expressed as

$$\begin{split} i_{\text{OUT}}(t) &= \left(I_{\text{B}} + \frac{I_{\text{RF}}^2 + I_{\text{LO}}^2}{8I_{\text{B}}}\right) \\ &+ \frac{1}{8I_{\text{B}}} \left(I_{\text{RF}}^2 \cos 2\omega_{\text{RF}}t + I_{\text{LO}}^2 \cos 2\omega_{\text{LO}}t\right) \\ &+ \frac{I_{\text{RF}}I_{\text{LO}}}{4I_{\text{B}}} \left[\cos(\omega_{\text{RF}} + \omega_{\text{LO}})t + \cos(\omega_{\text{RF}} - \omega_{\text{LO}})t\right]. \end{split}$$

From the last term in (11), the double sideband mixing is achieved and the RF signal at the frequency  $\omega_{RF}$  is mixed with the LO signal at the frequency of  $\omega_{LO}$ . The signal at  $\omega_{RF}$  is converted into the signals at  $(\omega_{RF}+\omega_{LO})$  and at  $(\omega_{RF}-\omega_{LO})$ . The  $\omega_{IF}$  in this design is set to  $(\omega_{RF}-\omega_{LO})$ . The current conversion gain of the current squaring circuit can be defined as

Currnet conversion gain =

$$\frac{i_{\rm OUT}|_{\omega=(\omega_{\rm RF}-\omega_{\rm LO})}}{i_{\rm RF}} = \frac{I_{\rm LO}}{4I_{\rm B}}$$

$$= \frac{I_{\rm LO}}{k_{\rm B}\frac{W}{I}(V_{\rm B}-2V_{\rm th})^2}.$$

(12)

From (12), the current conversion gain can be controlled by the magnitude of LO signal and the biasing voltage  $V_{\rm B}$ .

The load of the current squaring circuit can be designed by a LC tank which is resonated at IF and serves as a BPF. Because of its bandpass characteristics, both harmonic and inter-modulation components with frequencies far away

from the IF can be suppressed. Only the IF signal can be selected and sent to the output.

With the advanced of the CMOS technology, the device current is not of the square characteristic. Due to the short-channel effect, the relation among drain current  $i_{\rm DS}$ , overdrive voltage  $v_{\rm OV}$  and drain to source voltage  $v_{\rm DS}$  can be written as

$$i_{\rm DS} = \frac{1}{2} k \frac{W}{L} (v_{\rm OV})^m (1 + \lambda v_{\rm DS}),$$

(13)

where  $1 \le m < 2$ ,  $v_{\rm OV} = v_{\rm GS} - V_{\rm th}$ , and the coefficient  $\lambda$  models the effect of the channel length modulation which is related to  $v_{\rm DS}$ . Besides, the parameter m is roughly equal 2 if the overdrive voltage of the MOS is small. Because the drain to source voltage  $v_{\rm DS}$  between  $M_{\rm SQ_1}$  and  $M_{\rm SQ_3}$  are not exactly the same when the biasing voltage  $V_{\rm B}$  is slightly varied, the channel-length modulation effect should be considered as in (13).

Because  $V_{\rm B}$  is usually designed a little higher than two times threshold voltage of  $M_{\rm SQ_1}$  and  $M_{\rm SQ_3}$  from the consideration of the current conversion gain as shown in (12), the overdrive voltage voltages of both  $M_{\rm SQ_1}$  and  $M_{\rm SQ_3}$  are not high. Consequently, the coefficient m in (13) can be approximated as 2. If  $\delta = (v_{\rm DS,MSQ_3} - v_{\rm DS,MSQ_1})/2$  and  $\sigma = (v_{\rm DS,MSQ_3} + v_{\rm DS,MSQ_1})/2$  is assumed, the expression  $i_{\rm OUT}$  in (9) can be modified as

$$i_{\mathrm{OUT}} = i_{\mathrm{in}}^2 \frac{(1-\chi)}{4I_{\mathrm{B}}} + i_{\mathrm{in}} (V_{\mathrm{B}} - 2V_{\mathrm{th}})^2$$

$$\times \frac{\lambda}{\left(1+\lambda\sigma\right)^{2}} \cdot \left\{ \frac{\frac{\delta}{2I_{\mathrm{B}}} + \left[\sigma + \lambda\sigma^{2} - \delta\frac{\left(2+2\lambda\sigma - 27\lambda^{2}\sigma^{2}\right)}{(2+3\lambda\sigma)}\right]}{(2+3\lambda\sigma)}\right] \\ - \delta\lambda\sigma\left[\frac{\left(3+10\lambda\sigma + 11\lambda^{2}\sigma^{2} + 4\lambda^{3}\sigma^{3}\right)}{(2+3\lambda\sigma)}\right] \right\}$$

$$+I_{\rm B}\left[\frac{(1+2\lambda\sigma+2\delta\lambda)(2+3\lambda\sigma)^{2}}{2(2+3\lambda\sigma)(1+\lambda\sigma)^{2}+2\lambda(3\delta+7\delta\lambda\sigma+4\lambda^{2}\sigma^{2})}\right],$$

(14)

where

$$\chi = \frac{\lambda}{2(1+\lambda\sigma)^4} \cdot \left[ \sigma(1+\lambda\sigma)^2 (1+2\lambda\sigma) - \delta(1-\lambda\sigma) \right]. \tag{15}$$

If the effect of channel length modulation effect is neglected as  $\lambda=0$ ,  $\chi$  is equal 0 and (14) can be simplified to (9). The factor of the  $i_{\rm in}^2$  in (14) reveals that the conversion gain of the squaring circuit with the channel-length modulation becomes  $(1-\chi)$  times smaller than that without channel-length modulation.

Moreover, even if the drain to source voltage differences of  $M_{SQ_1}$  and  $M_{SQ_3}$  are the same, we have  $\delta = 0$ . But the

channel length modulation effect makes the coefficient  $\chi$  not equal 0. In this case, (14) can be simplified to

$$i_{\text{OUT}} = i_{\text{in}}^{2} \frac{(1 - \gamma)}{4I_{\text{B}}} + i_{\text{in}} (V_{\text{B}} - 2V_{\text{th}})^{2} \left(\frac{\lambda \sigma}{1 + \lambda \sigma}\right) + \frac{I_{\text{B}}}{2} \left[\frac{(1 + 2\lambda \sigma)(2 + 3\lambda \sigma)^{2}}{(2 + 3\lambda \sigma)(1 + \lambda \sigma)^{2} + 4\lambda^{3} \sigma^{2}}\right],$$

(16)

where

$$\gamma = \frac{\lambda \sigma (1 + 2\lambda \sigma)}{2(1 + \lambda \sigma)^2}.$$

(17)

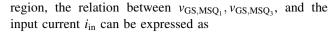

From the above derivations, channel length modulation effect degrades the conversion gain of the current squaring circuit which is  $(1-\chi)$  smaller in (14) or  $(1-\gamma)$  smaller in (16). Besides, this effect also results in the leakage of the fundamental signal of LO and RF signals. The simulation results in Fig. 9 show that the conversion gain approaches maximum when the biasing voltage  $V_{\rm B}$  equals  $V_{\rm DD}$  which is 1.2 V in this design. Meanwhile, the minimum value of drain to source voltage difference of  $M_{\rm SQ_1}$  and  $M_{\rm SQ_3}$  can be achieved under this condition.

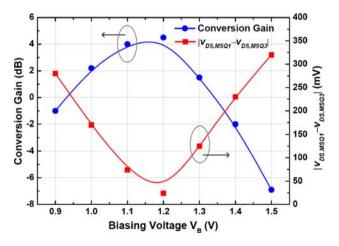

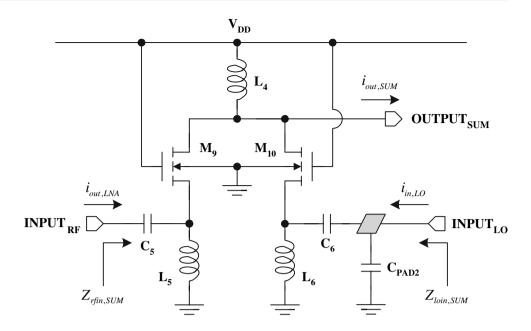

## 2.2.2 Current summing circuit

Figure 10 shows the current summing circuit. Two common-gate transistors  $M_9$  and  $M_{10}$  operated in the saturation region function as current buffers. The bulks of  $M_9$  and  $M_{10}$  are connected to ground. Although  $M_9$  and  $M_{10}$  suffer from the body effect resulting in slightly increase of their threshold voltage, the isolation among the input port of RF, the input port of LO, and the output port can be improved. Besides, the voltage headroom of this circuit is sufficient because the inductor  $L_4$  is tied to  $V_{\rm DD}$  and  $L_5-L_6$  are tied to

**Fig. 9** Simulated conversion gain and  $|v_{\text{DS,MSQ}_1} - v_{\text{DS,MSQ}_3}|$  versus  $V_{\text{B}}$ .

**Fig. 10** Circuit diagram of the current summing circuit

ground. This current summing circuit can be operated at very low supply voltage.

Due to the advantage of current-mode signal processing, the current signals  $i_{out,LNA}$  from LNA circuit and  $i_{in,LO}$  from off-chip LO signal generator are summed by connecting the drains of  $M_9$  and  $M_{10}$  together.  $L_4$  is designed to provide high impedance at the output so that the summed current signal  $(i_{\text{out,LNA}} + i_{\text{in,LO}})$  can be fed into the following current squaring circuit.  $C_5$  is the dc blocking capacitor to prevent from disturbing the biasing point of the LNA. At the frequency of RF, L<sub>5</sub> is resonated with the parasitic gate-to-source capacitance  $C_{GS,M9}$  of  $M_9$  and source-to-bulk capacitance  $C_{SB,M_9}$  of  $M_9$  to provide high impedance to ac ground so that the input RF current signal from the LNA circuit can flow into  $M_9$ .  $L_6$ ,  $C_6$  and  $C_{PAD2}$ form the matching network for LO input port. The parasitic gate-to-source capacitance  $C_{\mathrm{GS},M_{10}}$  of  $M_{10}$  and source-tobulk capacitance  $C_{SB,M_{10}}$  of  $M_{10}$  are also considered in this matching network.

#### 2.3 Current-mode receiver front-end

The detailed connections of the current-mode receiver front-end circuits under a single supply voltage of  $V_{\rm DD}$  are shown in Fig. 11. The circuits include a two-stage currentmode LNA of low-voltage version, a current summing circuit, and a current squaring circuit. The input signal at  $\omega_{RF}$  is firstly amplified by LNA, and then is mixed with the LO signal at  $\omega_{LO}$  by the current-mode mixer formed by a current summing circuit and a current squaring circuit. The down-converted signal at  $\omega_{\mathrm{IF}}$  is finally sent to output buffer which is a current-mirror amplifier formed by  $M_{14}$ ,  $M_{15}$ , and  $L_8$ . The output matching network is designed by  $L_8$ ,  $C_9$ , and  $C_{PAD3}$  so that the output impedance of the measuring buffer equals 50  $\Omega$  and the maximum power transfer can be achieved. Table 2 shows the design parameters of the two-stage current-mode LNA of low-voltage version. Table 3 shows the design parameters of current-mode down-conversion mixer and output buffer.

Fig. 11 Detailed connections of the 24-GHz current-mode receiver front-end with output buffer

Table 2 Device parameters of 24-GHz CMOS LNA

| Current-mode LNA of low-voltage version |                  |                                           |  |  |  |

|-----------------------------------------|------------------|-------------------------------------------|--|--|--|

| $M_1$                                   | $L = 0.13 \mu m$ | $W = 1.2 \mu \text{m}$                    |  |  |  |

| $M_2$                                   | $L = 0.13 \mu m$ | $W = 52.8 \ \mu m$                        |  |  |  |

| $M_3$                                   | $L = 0.13 \mu m$ | $W = 1.2 \mu \text{m}$                    |  |  |  |

| $M_4$                                   | $L = 0.13 \mu m$ | $W = 31.2 \mu m$                          |  |  |  |

| $C_{\mathrm{PAD1}}$                     | 20 fF            |                                           |  |  |  |

| $C_{ m IN}$                             | 89 fF            |                                           |  |  |  |

| $L_{ m GD}$                             | 506 pH           | Rad = 32.5 $\mu$ m, $w = 3 \mu$ m, nr = 3 |  |  |  |

| $L_1$                                   | 298 pH           | Rad = 15 $\mu$ m, $w = 9 \mu$ m, nr = 1.5 |  |  |  |

| $L_2$                                   | 315 pH           | Rad = 15 m, $w = 3 \mu m$ , nr = 1.5      |  |  |  |

| $L_3$                                   | 315 pH           | Rad = 15 m, $w = 3 \mu m$ , nr = 1.5      |  |  |  |

In this work, the RF input frequency is set at 24 GHz, the LO frequency is set at 19 GHz, and accordingly the IF output frequency is at 5 GHz. The image frequency is at 14 GHz. According to Fig. 4, the image rejection of the proposed receiver front-end is more than 30 dB before the first down-conversion mixer due to the large IF frequency of 5 GHz is selected. This performance is achieved due to the multistage nature of bandpass LNA. If much higher image rejection is required, the off-chip band-select filter

**Table 3** Device parameters of 24-GHz CMOS down-conversion mixer and output buffer

|                      | s output outro            |                                             |

|----------------------|---------------------------|---------------------------------------------|

| Current-n            | node down-convers         | ion mixer                                   |

| Current su           | umming circuit            |                                             |

| $M_9$                | $L=0.13~\mu\mathrm{m}$    | $W = 38.4 \mu \text{m}$                     |

| $M_{10}$             | $L=0.13~\mu\mathrm{m}$    | $W = 38.4 \mu \text{m}$                     |

| $C_{\mathrm{CPAD2}}$ | 20 fF                     |                                             |

| $C_5$                | 63 fF                     |                                             |

| $C_6$                | 274 fF                    |                                             |

| $L_4$                | 443 pH                    | Rad = 27 $\mu$ m, $w = 3 \mu$ m, nr = 1.5   |

| $L_5$                | 945 pH                    | Rad = 20 m, $w = 3 \mu m$ , nr = 3.25       |

| $L_6$                | 916 pH                    | Rad = 26 $\mu$ m, $w = 3 \mu$ m, nr = 2.75  |

| Current so           | quaring circuit           |                                             |

| $M_{11}$             | $L=0.13~\mu\mathrm{m}$    | $W = 14.4 \mu m$                            |

| $M_{12}$             | $L = 0.13 \ \mu \text{m}$ | $W = 14.4 \mu m$                            |

| $M_{13}$             | $L=0.13~\mu\mathrm{m}$    | $W = 14.4 \mu m$                            |

| $L_7$                | 884 pH                    | Rad = 15.5 $\mu$ m, $w = 3 \mu$ m, nr = 3.5 |

| $C_7$                | 1 pF                      |                                             |

| $C_8$                | 132 fF                    |                                             |

| Output bu            | ıffer                     |                                             |

| $M_{14}$             | $L=0.13~\mu\mathrm{m}$    | $W = 1.2 \mu m$                             |

| $M_{15}$             | $L=0.13~\mu\mathrm{m}$    | $W = 150 \mu \text{m}$                      |

| $L_8$                | 1.69 nH                   | Rad = 20 $\mu$ m, $w = 3 \mu$ m, nr = 4.5   |

| $C_9$                | 583 fF                    |                                             |

| $C_{\mathrm{PAD3}}$  | 20 fF                     |                                             |

before the LNA can be used to enhance the performance of image rejection.

For testing consideration, the three ports are also designed to match with 50  $\Omega$ . If multiple power supplies can be used in the receiver front-end, the simulated power consumption of the current-mode receiver is 29.94 mW where the two-stage current-mode LNA of low-voltage version drains 20.4 mA from the supply voltage of 0.8 V. and the current summing circuit and current squaring circuit drain 8.8 and 2.55 mA, respectively, from the supply voltage of 1.2 V. Under this condition, the two-tone analyses by HB simulation with two RF input signals at 23.95 and 24.05 GHz and the LO signal at 19 GHz with the power level of -3 dBm are depicted in Fig. 12. It reveals that the receiver has a simulated conversion gain of 21.5 dB, a  $P_{-1\,dB,RX}$  of  $-29\,dBm$ , and a  $P_{IIP3,RX}$  of -18.2 dBm. The simulated total NF is 4.2 dB with the RF at 24 GHz and LO at 19 GHz.

Moreover, if the receiver front-end is restricted to use single power supply, it consumes 55.4 mW from the supply voltage of 1.2 V. The excess power consumption is from the LNA because higher voltage is adopted to bias the LNA of the low-voltage version, and the LNA drains 34.82 mA from the supply voltage of 1.2 V.

The use of multiple supply voltage of 0.8 and 1.2 V complicates the design. In this design, the supply voltages are from different off-chip power supplies. Therefore, the smaller supply voltage can be easily supported. If the receiver is restricted to use a single supply voltage of 1.2 V, the LNA is recommended to use the circuit in Fig. 2(a) where  $M_6-M_8$  provide a simple way to have the voltage drop of around 400 mV for the LNA such that the voltages of  $A_1-A_3$  are around 0.8 V and  $M_1-M_4$  can be well biased.

Fig. 12 Simulated linearity performance of the 24-GHz current-mode receiver by two-tone HB analyses

### 3 Experimental results

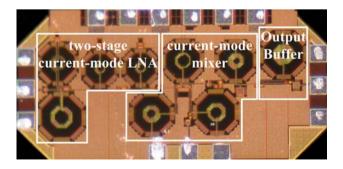

The designed 24-GHz current-mode receiver front-end circuit was fabricated in 0.13- $\mu$ m 1P8M CMOS technology. The top metal of this process is with the thickness of 3.35  $\mu$ m. The equivalent relative dielectric constant  $\epsilon_{\rm eff}$  is about 4.2. Based on the technology information of the backend process, the electromagnetic (EM) tool HFSS is used to evaluate and extract the characteristics of the on-chip octagonal spiral inductors and the interconnections within the circuits.

The floor plans of the proposed receiver front-end are depicted in Fig. 13. Nine on-chip octagonal spiral inductors are used. The distances of each inductor are more than 100 μm to mitigate the magnetic coupling between on-chip inductors. In addition, the distances of the active devices of current-mode LNA, current summing circuit, currentsquaring circuit and output buffer are arranged far, the noise influence between these circuits are kept small. The signal path between input pad and the input of the LNA is drawn as short as possible to avoid additional signal losses and increase of NF. Besides, large on-chip decoupling capacitors are used between the biases and ground, such that high frequency noises can be bypassed to ground and consequently stable biases and supplies of the receiver can be achieved. All dc pads are protected by ESD diodes to enhance the reliability of the proposed receiver. The performance of each circuit block in this 24-GHz current-mode receiver is over-designed to overcome process variations. This chip occupies the active region of  $1.45 \times 0.72 \text{ mm}^2$  including testing pads.

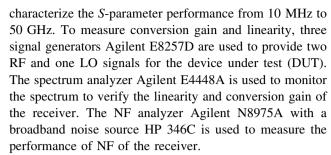

The measurement setups of this fabricated receiver are described as follows. The on-wafer probing measurement is adopted to verify the performance of the receiver frontend. Three GSG RF probes with the pitch of 150  $\mu$ m and a 6-pin dc probe with the pitch of 150  $\mu$ m are applied to probe the testing pads. The S parameters are measured to analyze both the input and output matching characteristics by the network analyzer, Agilent E8364B, which can

Fig. 13 Chip micrograph of the fabricated current-mode receiver front-end

Owing to the layout mistake of the fabricated chip, the focused ion beam (FIB) post-process is used to modify the metal connections of the current-mode LNA. The FIB metal lines connect the LNA circuit to the power supply. Under the condition that multiple power supplies can be used so that the power supply of LNA is 0.8 V and the power supply of the current-mode mixer is 1.2 V, the measured total power consumption is 27.8 mW. Moreover, if the single power supply of 1.2 V is applied to the receiver front-end, the measured power dissipation is increased to about 49.8 mW. The reason why the increase in measured power dissipation from 27.8 mW for the multiple supply voltages to 49.8 mW for the single supply voltage is the supply voltage of LNA is increased from 0.8 to 1.2 V. This results in increasing more overdrive voltage of 400 mV of the LNA, and consequently the measured power dissipation of LNA itself is increased. The measured current consumption of the LNA is 19.45 mA from the supply voltage of 0.8 V and is 31.3 mA from the supply voltage of 1.2 V.

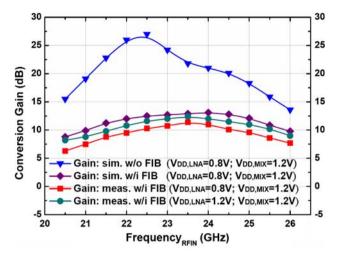

Figure 14 presents the measured and revise-simulated conversion gain versus RF input frequency. The losses from cables, probes and adaptors are compensated. Moreover, the parasitic resistances resulting from FIB postprocess are considered in the revise-simulated results. The tested RF input power is -30 dBm. The LO is set to the frequency which is 5 GHz lower than the RF,  $f_{LO} = f_{RF} - 5$  GHz, and the tested LO input power is -3 dBm. The output is observed at the fixed IF frequency of 5 GHz. The measured conversion gain of the RF frequency at 24 GHz is 11.3 dB under the condition that the power supplies of the LNA and Mixer are 0.8 and 1.2 V, respectively. In addition, the conversion gain is 12 dB under the condition that the power supply of both LNA and Mixer is 1.2 V. Because the parasitic resistances from FIB post-process are in series with the inductive loads of the current-mode LNA, the quality factor of the loads of the LNA is decreased. This makes the gain of the LNA decrease, and consequently the conversion gain of the receiver is decreased.

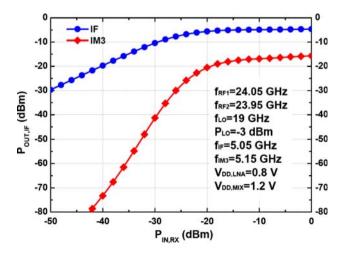

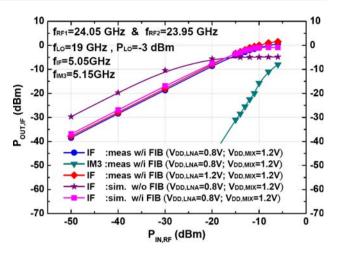

The two-tone test results are shown in Fig. 15. Two RF inputs with 100 MHz frequency spacing are at the frequency of 24.05 and 23.95 GHz and the LO is at 19 GHz with the power of -3 dBm. Because of the conversion gain

Fig. 14 The measured and simulated conversion gain of the receiver versus RF input frequency

reduction of the receiver, the measured  $P_{-1\,\mathrm{dB}}$  and  $P_{\mathrm{IIP3}}$  are raised to -13.5 dBm and -1 dBm, respectively, under the condition that the power supplies of LNA and Mixer are 0.8 and 1.2 V, respectively. Besides, the measured  $P_{-1\,\mathrm{dB}}$  and  $P_{\mathrm{IIP3}}$  are about -12 and -1.5 dBm, respectively, under the condition that the single power supply of 1.2 V for LNA and mixer is adopted. At the RF frequency of 24 GHz and the LO frequency of 19 GHz, the measured total NF of the receiver is 14.2 and 13.3 dB if the power supply of LNA is 0.8 and 1.2 V, respectively.

Table 4 summaries the performance of the proposed current-mode receiver front-end. In addition, some comparison results of published 24-GHz receiver front-end circuits are also provided. Compared to the works published in [2] and [5], the proposed 24-GHz CMOS current-

**Table 4** The measured performances and comparisons results of published 24-GHz receiver front-end circuits

|                              | This work                                  |         | [2]                                                                      | [5]                                                                           |

|------------------------------|--------------------------------------------|---------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Technology                   | 0.13 μm CMOS                               |         | 0.18 μm CMOS                                                             | $0.8 \text{ pm SiGe HBT}$ $f_{\rm T} = 80 \text{ GHz}$                        |

| Receiver architecture        | Direct-conversion<br>(2-stage LNA + Mixer) |         | Direct-conversion<br>(3-stage LNA +<br>single-balanced<br>Gilbert Mixer) | Direct-conversion (3-stage differential LNA + I/Q differential Gilbert Mixer) |

| Topology                     | Current mode                               |         | Voltage mode                                                             | Voltage mode                                                                  |

| Freq <sub>RF</sub> (GHz)     | 24                                         |         | 21.8                                                                     | 24.1                                                                          |

| Freq <sub>LO</sub> (GHz)     | 19                                         |         | 16.9                                                                     | 23.9                                                                          |

| Freq <sub>IF</sub> (GHz)     | 5                                          |         | 4.9                                                                      | 0.2                                                                           |

| Gain <sub>RX</sub> (dB)      | 12                                         | 11.3    | 27.5                                                                     | 31                                                                            |

| $NF_{RX}$ (dB)               | 13.3                                       | 14.2    | 7.7                                                                      | 8.8                                                                           |

| $P_{IIP3, RX}$ (dBm)         | -1.5                                       | -1      | _                                                                        | _                                                                             |

| $P_{1 dB, RX} (dBm)$         | -12                                        | -13.5   | -23                                                                      | -27                                                                           |

| Power (mW)                   | 49.8                                       | 27.8    | 64.5                                                                     | 640                                                                           |

| Supply (V)                   | 1.2                                        | 0.8/1.2 | 1.5                                                                      | 4                                                                             |

| Chip area (mm <sup>2</sup> ) | $1.45 \times 0.72$                         |         | $0.4 \times 0.5$                                                         | $1.48 \times 1.15$                                                            |

Fig. 15 The measured linearity performance of the receiver by twotone testing

mode receiver front-end has the advantage of smaller power dissipations and can be operated in low supply voltage. This current-mode receiver front-end also has better linearity performance.

The layout mistake has been corrected and the modified design is under fabrication now. Therefore, the new test results are unavailable at present.

#### 4 Conclusion

In this work, the current-mode design techniques of CMOS RF circuits are developed and are applied to realize the first 24-GHz CMOS current-mode receiver front-end. The receiver integrated with a current-mode LNA and a

current-mode down-conversion mixer is designed, fabricated in 0.13-µm CMOS technology and measured. Twostage current-mirror amplifiers cascaded are used to realize the current-mode LNA. The LNA has the capability of low voltage operation. The current summing circuit and current squaring circuits are adopted to perform the mixing of the current signals. The measured results demonstrate that the proposed current-mode receiver front-end can operate well in the 24-GHz frequency band. Although the receiver does not achieve the expected performance because of the layout mistake, after the FIB post-process to remedy for the layout mistake, the designed 24-GHz CMOS current-mode receiver front-end still can exhibit the conversion gain of 11.3 dB, the NF of 14.2 dB, and the  $P_{\text{IIP3}}$  of -1 dBm under the condition that power supply of the current-mode LNA is 0.8 V and the power supply of the current-mode mixer is 1.2 V. The total power dissipation of the currentmode receiver front-end under this condition is 27.8 mW. The current-mode design techniques have the capability of designing low-voltage RF circuits in the advanced nanometer CMOS technologies. Future research on the applications of short range automotive radar systems or point-to-point wireless communication systems will be explored and discussed by the proposed current-mode approaches.

Acknowledgements This work was supported by the National Science Council (NSC), Taiwan, under the Grant NSC-95-2221-E-009-292. The authors would like to thank the National Chip Implementation Center (CIC), National Applied Research Laboratories, Taiwan, for the fabrication of testing chip. The authors would also like to thank the support of CAD tools HFSS from Ansoft Taiwan.

## References

- Federal Communications Commission, FCC 02–04, Section XV.515.15.521.

- Guan, X., & Hajimiri, A. (2004). A 24-GHz CMOS front-end. IEEE Journal of Solid-State Circuits, 39(2), 368–373.

- Hajimiri, A., Hashemi, H., Natarajan, A., Guan, X., & Komijani, A. (2005). Integrated phased array systems in silicon. *Proceedings* of the IEEE, 93(9), 1637–1655.

- Hugo, V., Van Der Heijden, E., Notten, M., & Dolmans, G. (2007).

A SiGe-BiCMOS UWB receiver for 24 GHz short-range automotive radar applications. In *IEEE Microwave Symposium*, *IEEE/MTT-S International*, pp. 1791–1794.

- Ojefors, E., Sonmez, E., Chartier, S., Lindberg, P., Schick, C., Rydberg, A., & Schumacher, H. (2007). Monolithic integration of a folded dipole antenna with a 24-GHz receiver in SiGe HBT technology. *IEEE Transactions on Microwave Theory and Techniques*, 55(7), 1467–1475.

- Meliani, C., Huber, M., Boeck, G., & Heinrich, W. (2006). A GaAs HBT low power 24 GHz downconverter with on-chip localoscillator. In *1st European Microwave Integrated Circuits Con*ference, pp. 141–144.

- 7. Wu, C.-Y., Hsu, S.-W., & W.-C. Wang (2007). A 24-GHz CMOS current-mode power amplifier with high PAE and output power. In

- 2007 IEEE International Symposium on Circuits and Systems, ISCAS'07, New Orleans, USA, May 27–30, pp. 2866–2869.

- 8. Wang, W.-C., & Wu, C.-Y. (2007). The 1-V 24-GHz low-voltage low-power current-mode transmitter in 130-nm CMOS technology. In *IEEE 3rd Ph.D. Research in Microelectronics and Electronics*, *PRIME 2007*, Bordeaux, France, July 2–5, 2007, pp. 49–52

- Bult, K., & Wallinga, H. (1987). A class of analog CMOS circuits based on the square-law characteristics of an MOS transistor in saturation. *IEEE Journal of Solid-State Circuits*, SC-22, 357-364.

Chung-Yu Wu was born in 1950. He received the M.S. and Ph.D. degrees from the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, R.O.C., in 1976 and 1980, respectively. In addition, he conducted post-doc research at UC Berkeley in summer of 2002. Since 1980, he has served as a consultant to high-tech industry and research organizations and has built up strong

research collaborations with high-tech industries. From 1980 to 1983, he was an Associate Professor at National Chiao Tung University. During 1984 to 1986, he was a Visiting Associate Professor in the Department of Electrical Engineering, Portland State University, Portland, OR. Since 1987, he has been a Professor at National Chiao Tung University. From 1991 to 1995, he was rotated to serve as the Director of the Division of Engineering and Applied Science on the National Science Council, Taiwan. From 1996 to 1998, he was honored as the Centennial Honorary Chair Professor at National Chiao Tung University, Currently, he is the president and chair professor of National Chiao Tung University. He has published more than 250 technical papers in international journals and conferences. He also has 19 patents including nine U.S. patents. His research interests are nanoelectronics, low-power/low-voltage mixed-signal VLSI design, biochips, neural vision sensors, RF circuits, and CAD analysis. Dr. Wu is a member of Eta Kappa Nu and Phi Tau Phi Honorary Scholastic Societies. He was a recipient of IEEE Fellow Award in 1998 and Third Millennium Medal in 2000. In Taiwan, he received numerous research awards from Ministry of Education, National Science Council, and professional foundations.

Wen-Chieh Wang was born in 1978. He received the B.S. in Electronics Engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2000. He is currently working toward the Ph.D. degree at the National Chiao Tung University. His current research interests are in CMOS low-voltage low-power radio-frequency integrated circuits design and analog integrated circuits design.

Fadi R. Shahroury was born in 1977. He received the B.S. in Electronics Engineering from Princess Sumaya University for Technology, Jordan, in 2000. He is currently working toward the Ph.D. degree at the National Chiao Tung University, Hsinchu, Taiwan. His current research interests are in low-voltage, low-power, and very high-frequency integrated circuits design and analog integrated circuits design in CMOS technology.

Hao-Jie Zhan received the M.S. degree from the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, R.O.C. in 2006. His research interests include CMOS RF integrated circuit design and analog integrated circuit design.

Zue-Der Huang was born in 1975. He received the B.S. and M.S. degrees from the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, R.O.C. and Department of Electrical Engineering, University of Southern California, USA in 1998 and 2002, respectively. From 2002 to 2004, he joined the Atheros Taiwan Research & Development Center as a design engineer. He is now pursuing the Ph.D degree in the Depart-

ment of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan. His research interests include low-voltage current-mode CMOS RF circuits, focusing on RFVCO, frequency synthesizer, and transceiver design.