# 國立交通大學

# 電子工程學系電子研究所

# 博士論文

先進金氧半場效電晶體對於佈局之依賴效應

**Layout Dependent Effect on Advanced MOSFETs**

研究生: 許義明

指導教授 : 陳明哲 博士

中華民國九十六年三月

## 先進金氧半場效電晶體對於佈局之依賴效應

# LAYOUT DEPENDENT EFFECT ON ADVANCED MOSFETS

研究生:許義明 Student: Yi-Ming Sheu

指導教授:陳明哲 博士 Advisor: Dr. Ming-Jer Chen

## 國立交通大學 電子工程學系 電子研究所 博士論文

A Dissertation

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical Engineering and Computer Science

National Chiao-Tung University

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in

**Electronics Engineering**

March 2007 Hsinchu, Taiwan, Republic of China

中華民國九十六年三月

#### 先進金氧半場效電晶體對於佈局之依賴效應

學生: 許義明 指導教授: 陳明哲博士

國立交通大學 電子工程學系 電子研究所

#### **Abstract (in Chinese)**

摘要

次 100 奈米先進互補金氧半技術中之金氧半場效電晶體對於佈局的依賴效應已經日趨明顯。本篇論文展示了兩個主要引起金氧半場效電晶體行為對於佈局依賴性的要素 - 製程引起的機械應力效應和井邊緣親近效應。

在製程引起的機械應力效應方面,第一點,本論文使用閘極長度為65 奈米的先進互補金氧半技術完成了實驗之設計與執行。第二點,以包含種種機械應力來源並考慮全製程的數值運算完整的模擬了整個金氧半場效電晶體結構。第三點,提出了一個新的應力相依的摻雜擴散模型並將之加入於數值模擬軟體中,而模擬結果符合了矽晶片實驗實驗範圍內之金氧半場效電晶體的次臨限(subthreshold)特性。第四點,本論文探討了淺溝渠及熱氧化製程引起的機械應力和金氧半場效電晶體開狀態(on-state)對於佈局的依賴效應的關係,發展出一組精簡、可變化規模(scalable)的新積體電路模擬程式(SPICE)模型來解釋淺溝渠機械應力對金氧半場效電晶體性能的影響,並且成功預測晶片實驗中各條件的實驗結果。

本論文亦使用了次 100 奈米先進互補金氧半技術詳細探討了由離子佈植時邊界摻

i

雜散射引起的井邊緣親近效應。晶片實驗和技術電腦輔助設計(TCAD)模擬被用來從物理和製程的角度探討這個效應。蒙地卡羅離子散射模型和技術電腦輔助設計模擬提供了金氧半場效電晶體內部如何形成改變的物理了解。一個基於此物理了解的精簡新積體電路模擬程式模型被提出來並且以晶片實驗中各測試組結果完成此模型之校正。

**Layout Dependent Effect on Advanced MOSFETs**

Student: Yi-Ming Sheu

Advisor: Dr. Ming-Jer Chen

Department of Electronics Engineering and Institute of Electronics

National Chiao-Tung University

**Abstract (in English)**

The layout dependent effect on the MOSFETs characteristics has become more

and more significant in advanced sub-100nm CMOS technologies. This dissertation

demonstrates the experimental results, theories and modeling of two main factors

making MOSFET behaviors layout dependent - process induced mechanical stress

effect and well-edge proximity effect.

For the process induced mechanical stress effect, first, complete experiments

are designed and conducted using novel CMOS technology with a minimum

physical gate length of 65nm to investigate the mechanical stress effect. Second,

full-process numerical simulations are performed for modeling complete MOSFET

Third, a new structures containing various mechanical stress sources.

stress-dependent dopant diffusion model is proposed and is implemented into the

simulation software and the simulation results match MOSFET subthreshold

characteristics of the silicon wafer experiment within the design space. Fourth, the

iii

relationship between layout dependence of MOSFET on-state characteristics and mechanical stress caused by shallow trench isolation (STI) and thermal oxidation has been investigated, and a new compact and scaleable SPICE model accounting for the STI mechanical stress effect on MOSFET electrical performance is developed and successfully matches the experimental data under various conditions.

The well-edge proximity effect caused by the boundary dopant scattering during ion implantations is further explored using a sub-100nm CMOS technology in detail. TCAD simulations together with silicon wafer experiments have been conducted to investigate the impact of this effect from a physics and process perspective. The Monte Carlo ion scattering model and TCAD simulations provide a physical understanding of how the internal changes of the MOSFETs are formed. A new compact model for SPICE is proposed using physics-based understanding and has been calibrated using experimental silicon test sets.

*Index Terms*: dopant diffusion, mechanical stress, strain, shallow trench isolation, MOSFET, mobility, Well-Edge Proximity, ion scattering, SPICE, modeling and simulation

#### **Acknowledgements**

First of all, I would like to express my sincere gratitude to my advisor, Prof. Ming-Jer Chen, for his constant guidance and support during my doctorate studies. Moreover, I was also deeply affected by his passion and persistence on academic research.

I also wish to show my appreciation to all of the committee members, including, Prof. Lih-Juann Chen, Prof. Jenn-Gwo Hwu, Prof. Ya-Ming Lee, Prof. Tien-Sheng Chao, Dr. Chih-Sheng Chang, Prof. Tahui Wang, Prof. Horng-Chih Lin, and Prof. Ming-Jer Chen for their invaluable comments and suggestions.

I have been very lucky to work with such intelligent and experienced colleagues in Taiwan Semiconductor Manufacturing Company (TSMC) for many years. Especially, I would like to acknowledge Dr. Carlos H. Diaz, Dr. Chih-Sheng Chang, Dr. Ke-Wei Su, Dr. Sheng-Jier Yang, Dr. Huan-Tsung Huang, and Da-Wen Lin for frequently providing insightful opinions and stimulating discussions. My thanks also go to TSMC TCAD group members and my other colleagues who assist in the success of the experiments.

The electronics engineering department of NCTU has provided me not only the base knowledge for my research but also a truly delightful learning experience. I would like to express my appreciation to Prof. S. M. Sze, Prof. Long-Ing Chen, Prof. Ching-Yuan Wu, Prof. Shun-Tung Yen, and all of the scholars who helped expand my knowledge in their classes and lectures.

At last, I would like to thank my family for their never-ending support, love,

and encouragement throughout my whole life. This dissertation is dedicated to them.

#### 謝誌

首先, 誠摯的感謝指導教授陳明哲博士多年以來的細心指導及大力支持。除此之外, 我深受老師對求學問的熱情與堅持所感動。

特別感謝論文口試委員陳力俊教授、胡振國教授、李雅明教授、趙天生教授、張智勝博士、汪大暉教授、林鴻志教授以及陳明哲教授在百忙之中給予寶貴的建議及指教。

很幸運的,能和台灣積體電路製造公司非常具有智慧及經驗的同事一起工作。其中,我特別要感謝 Carlos H. Diaz 博士、張智勝博士、蘇哿偉博士、楊勝傑博士、黃煥宗博士和林大文先生經常提供寶貴的意見及討論。在此,也要對台積電 TCAD 成員及其他對論文中實驗有幫助的同仁表達謝意。

交通大學電子工程研究所不僅提供我研究的基礎知識還有快樂的學習時光。課業上,感謝施敏教授、陳龍英教授、吳慶源教授、顏順通副教授及其他學者教授我豐富的知識及資訊。

最後,我要感謝我的家人長久以來支持、愛和鼓勵。這本論文,獻給他們。

## **Content (Index)**

| Abstract (in Chinese)i                                               |

|----------------------------------------------------------------------|

| Abstract (in English)iii                                             |

| Acknowledgementsv                                                    |

| Content (Index)viii                                                  |

| Table Captionsx                                                      |

| Figure Captionsxi                                                    |

| Chapter 1 Introduction1                                              |

| 1.1 Overview                                                         |

| 1.2 TCAD modeling5                                                   |

| 1.3 Dissertation Organization8                                       |

| References 9                                                         |

| Chapter 2 Dopant Diffusion Under Mechanical Stress                   |

| 2.1 Preface21                                                        |

| 2.2 Stress-dependent Diffusion Model and Modeling Methodology23      |

| 2.2.1 Model Description                                              |

| 2.2.2 Modeling Methodology                                           |

| 2.2.3 Experiment on MOSFET Threshold Voltages and Modeling Results27 |

| 2.3 Experiment on MOSFET Subthreshold Leakage with Stress-Dependent  |

| Transient-Enhanced-Diffusion Effect Included                         |

| 2.4 Anisotropic Diffusion Derivation for Uniaxial Strain Cases       |

| References                                                           |

| Chapter 3 Mechanical Stress Effects on MOSFET Performances and SPICE |

| Modeling                                                 | 66           |

|----------------------------------------------------------|--------------|

| 3.1 Preface                                              | 66           |

| 3.2 STI Mechanical Stress Effects on Modern MOSFET Drive | e Currents66 |

| 3.2.1 Layout Matrix and Experimental Results             | 66           |

| 3.2.2 Simulation and Systematic Analysis                 | 68           |

| 3.3 SPICE Model for STI Mechanical Stress Effect         | 70           |

| 3.3.1 MOSFET Measurement Data Analysis                   | 70           |

| 3.3.2 Model Development                                  | 71           |

| 3.3.3 Model Verification                                 | 74           |

| 3.3.4 Impact on Circuit Design                           | 76           |

| References                                               | 78           |

| Chapter 4 Well-Edge Proximity Effect                     |              |

| 4.1 Preface                                              | 102          |

| 4.2 Ion Scattering Physics and Modeling                  |              |

| 4.3 TCAD Numerical Simulation                            | 105          |

| 4.4 Compact Model for SPICE                              | 107          |

| References                                               | 111          |

| Chapter 5 Summary and Future Work                        | 123          |

| 5.1 Summary                                              | 123          |

| 5.2 Recommendations for Future Work                      | 125          |

| Vita                                                     | 127          |

| Publication list                                         | 192          |

## **Table Captions**

## Chapter 2

Tab. 2.1 Impurity  $\Delta E_S$  extracted in the study

#### **Figure Captions**

#### Chapter 1

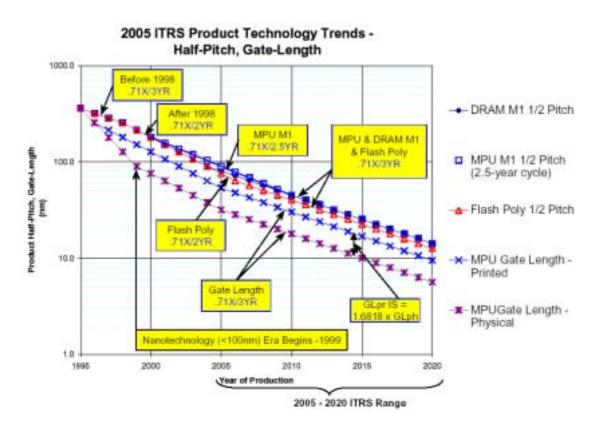

- Fig. 1.1 Half pitch and gate length trends predicted by ITRS (adapted from Ref.[1.1]).

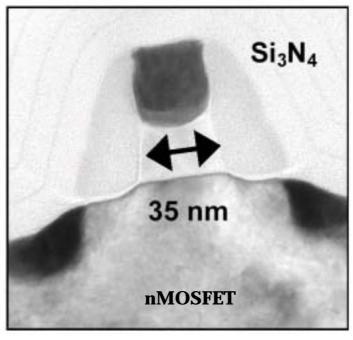

- Fig. 1.2 TEM images of 35nm-gate-length MOSFETs using mechanical strained technologies (adapted from Ref.[1.12]).

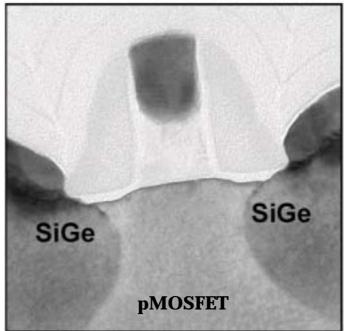

- Fig. 1.3 Schematic representation of the constant-energy ellipses for (a) and (b) unstrained Si and (c) and (d) strained Si. (a) and (c) are for a 3DEG in bulk Si. (b) and (d) are those of a 2DEG in a Si inversion layer. (e) and (f) are the schematic diagrams for bulk strained Si and an inversion layer in strained Si, respectively. (adapted from Ref.[1.19]).

- Fig. 1.4 Simplified valence band E vs. k diagram for strained Si (adapted from Ref.[1.25]).

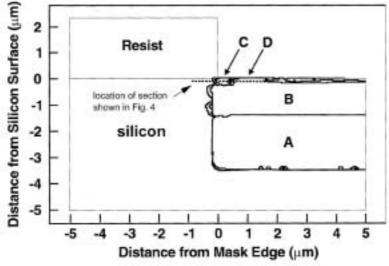

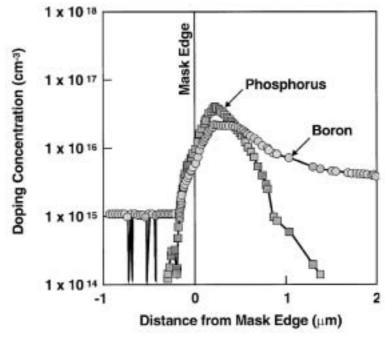

- Fig. 1.5 (a) Contour plot of simulated doping near resist mask edge. Both boron (intermediate and near-surface) and phosphorus (deep) implantations were simulated. (b) Simulated lateral doping profiles of B and P immediately below the silicon surfaces (adapted from Ref.[1.12]).

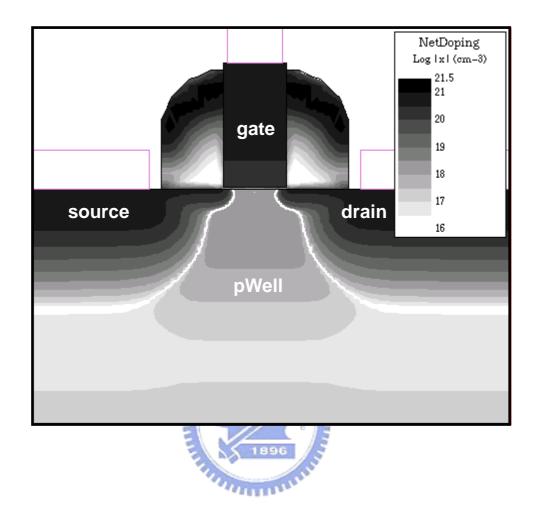

- Fig. 1.6 Simulated dopant distribution contours of a novel MOSFET using a TCAD tool (TSURPEM4).

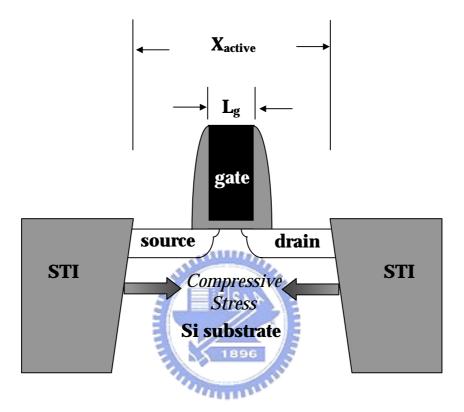

- Fig. 1.7 Simulated (a) electrical current distribution contours (b) output current-voltage plot of the MOSFET shown in Fig. 1.6.

#### Chapter 2

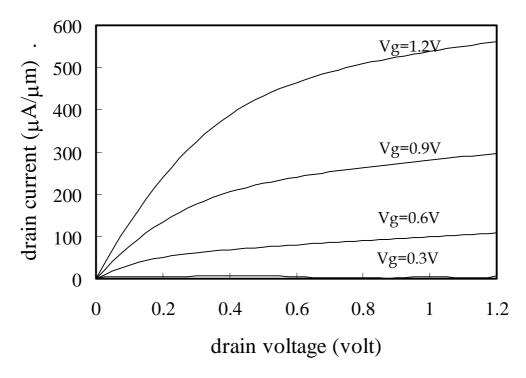

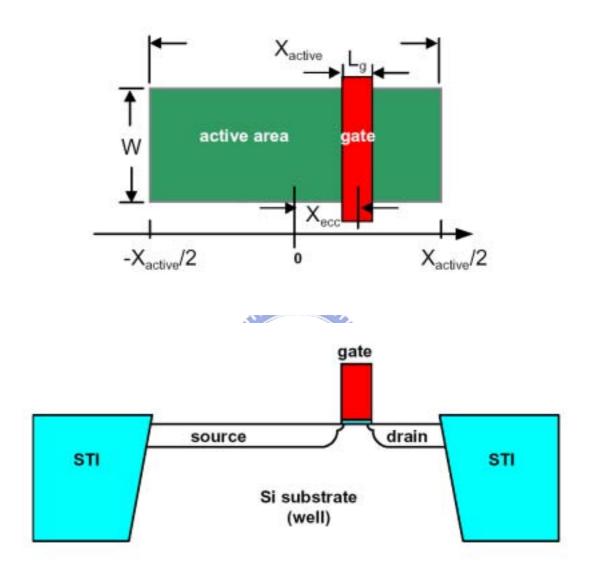

- Fig. 2.1 Schematic cross section of the device along channel length direction with active area size  $X_{active}$  and gate length  $L_g$  both as parameters. The stress condition is compressive mainly because of the lower thermal expansion rate of STI oxide compared to silicon, and the thermal gate oxidation induced volume expansion at the STI edge.

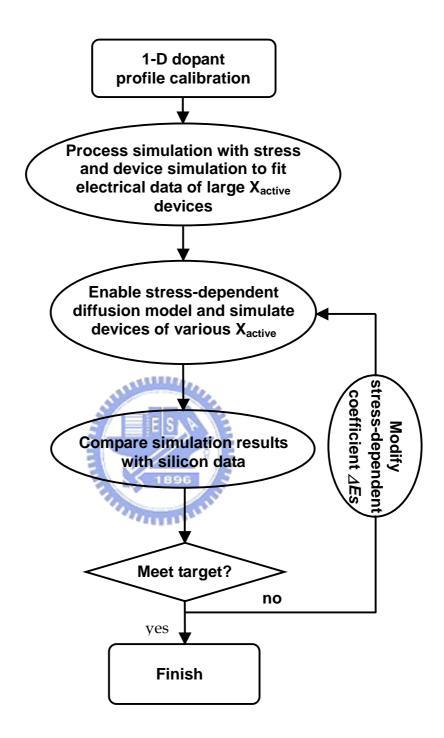

- Fig. 2.2 Flow chart of the modeling procedure.

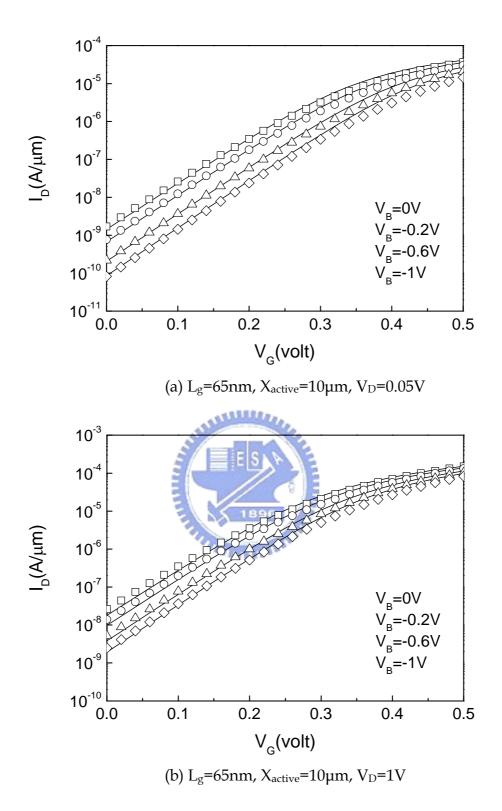

- Fig. 2.3 I-V calibration result of a short channel nMOSFET with large  $X_{active}$  for (a)  $V_D$ =0.05V and (b)  $V_D$ =1V. Lg=65nm and  $X_{active}$ =10 $\mu$ m. Symbols stand for the silicon data. Solid lines are the calibrated simulation result.

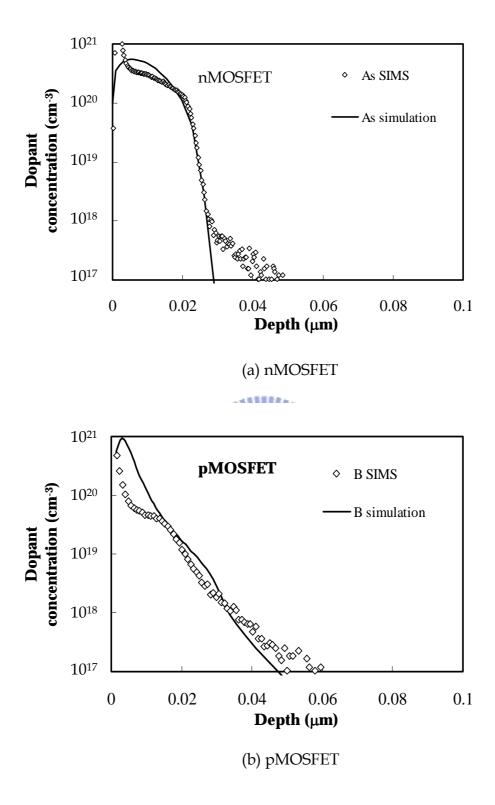

- Fig. 2.4 SIMS and calibration results of one-dimensional dopant profile for (a) nMOSFET and (b) pMOSFET.

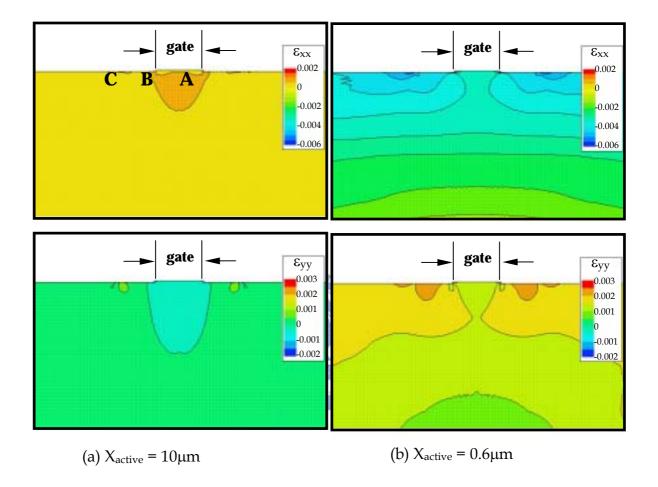

- Fig. 2.5 Simulated strain distribution in the silicon of entire front-end process for Lg=65nm and (a)  $X_{active}$ =10 $\mu$ m and (b)  $X_{active}$ =0.6 $\mu$ m. A small  $X_{active}$  causes a much higher strain.

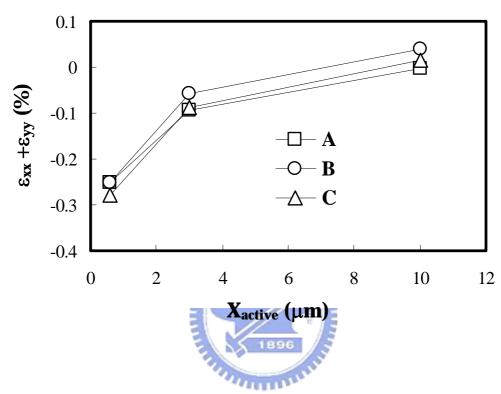

- Fig. 2.6 The magnitude of strain versus  $X_{active}$  corresponding to three points **A**, **B**, and **C** in Fig. 2.5.

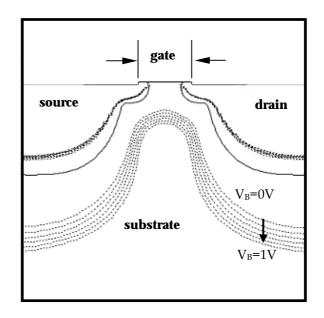

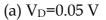

- Fig. 2.7 The depletion region boundaries with substrate bias,  $V_B$ , for 65nm nMOSFET at (a)  $V_D$ =0.05V and (b)  $V_D$ =1V.

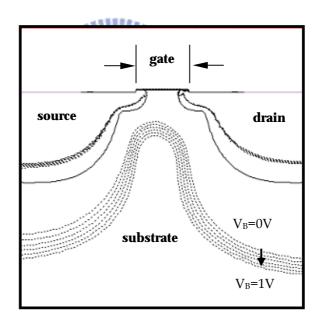

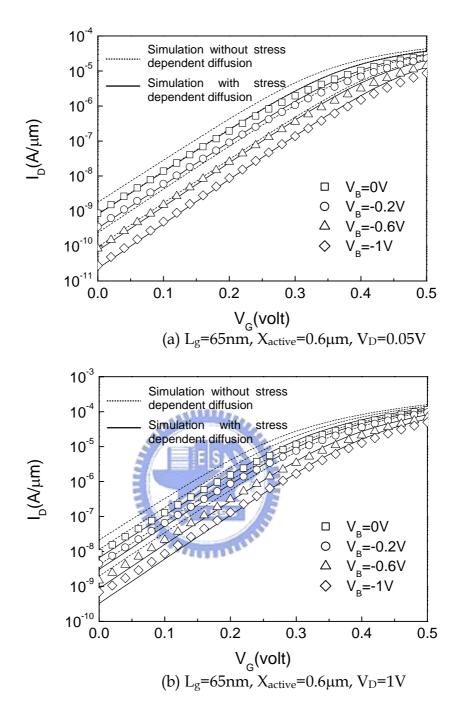

- Fig. 2.8 I-V comparison among experimental data, simulation without stress-dependent diffusion model, and simulation with stress-dependent diffusion model for a small  $X_{active}$  MOSFET at (a)  $V_D$ =0.05V and (b)  $V_D$ =1V.  $L_g$ =65nm and  $X_{active}$ =0.6 $\mu$ m. Symbols stand for the silicon data. Dashed

- lines are the simulation without stress dependent diffusion model. Solid lines are the simulation with stress dependent diffusion model.

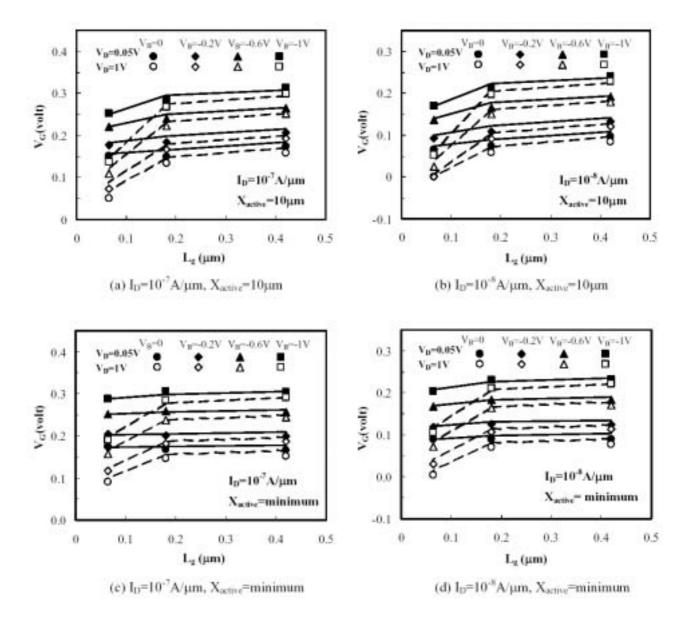

- Fig. 2.9 Comparison of experimental and simulated nMOSFET  $V_G$  at different  $I_D$  level for various  $L_g$  and  $X_{active}$ . Minimum  $X_{active}$  for Lg=65nm is 0.6 $\mu$ m, for Lg=0.18 $\mu$ m is 0.74 $\mu$ m, and for Lg=0.42 $\mu$ m is 1 $\mu$ m. Final set of dopant diffusion parameters can model MOSFETs of different  $X_{active}$  under various drain voltages and substrate biases. Symbols stand for silicon data. Solid lines represent simulations with stress dependent diffusion model.

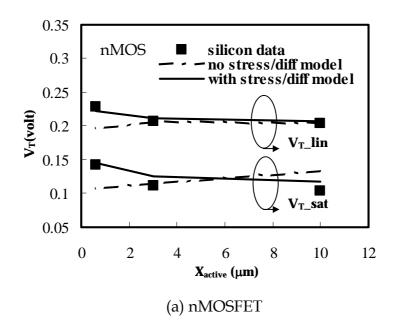

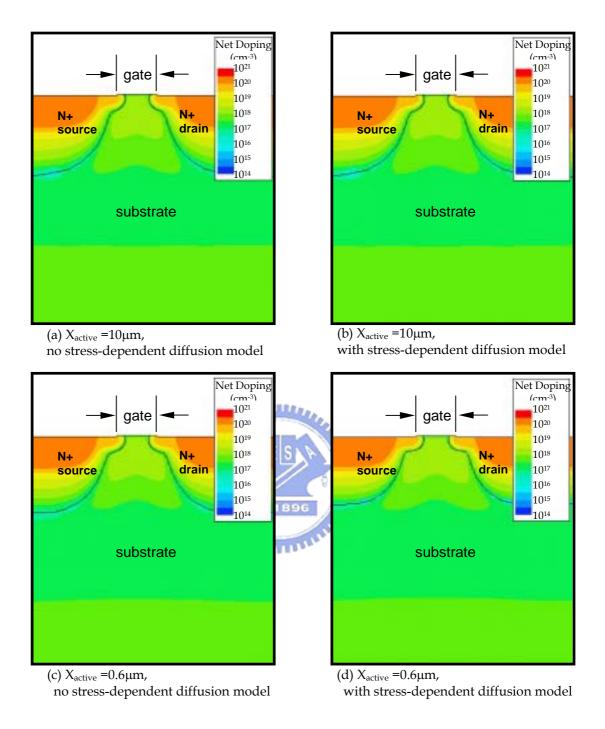

- Fig. 2.10 Experimental and simulated threshold voltage dependence on  $X_{active}$  of (a) nMOSFET and (b) pMOSFET. nMOSFET threshold voltage,  $V_T$ , is more dependent on  $X_{active}$  than the p-type counterpart. Simulation with stress dependent diffusion model is able to describe stress induced  $V_T$  shift.

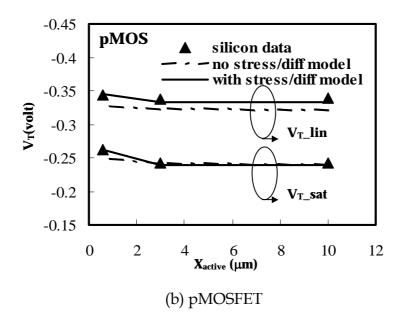

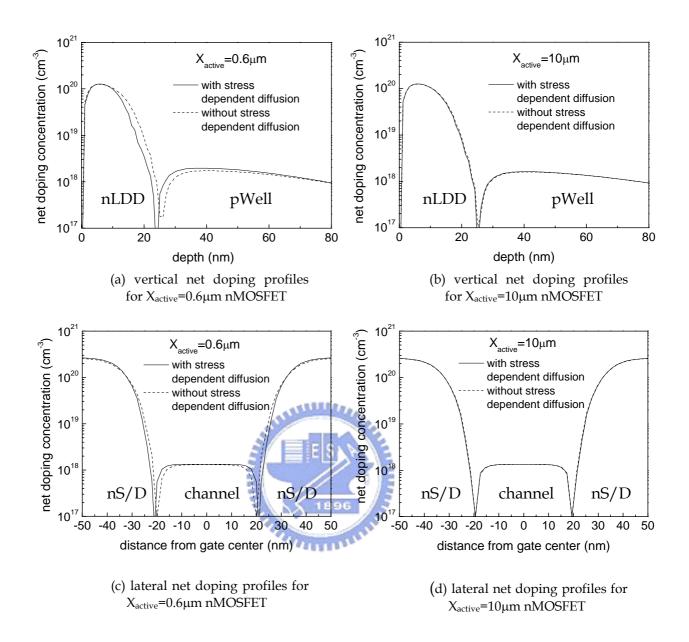

- Fig. 2.11 Net doping contours for (a)  $X_{active}$ =10µm, no stress-dependent model, (b)  $X_{active}$ =10µm, with stress-dependent model, (c)  $X_{active}$ =0.6µm, no stress-dependent model, and (d)  $X_{active}$ =0.6µm, with stress-dependent model. For  $X_{active}$ =0.6µm, the source/drain junction is significantly shallower in the MOSFET core region when the stress-dependent diffusion model is turned on. The gate length is 65nm.

- Fig. 2.12 Dopant profiles of (a) vertical direction for  $X_{active}$ =0.6 $\mu$ m nMOSFET, (b) vertical direction for  $X_{active}$ =10 $\mu$ m nMOSFET, (c) lateral direction for  $X_{active}$ =0.6 $\mu$ m nMOSFET, and (d) lateral direction for  $X_{active}$ =0.6 $\mu$ m nMOSFET. The vertical profiles are taken at gate edge and the lateral profiles are taken at 15nm deep cut-lines of the device. Solid lines are

simulation with stress-dependent diffusion model and dashed lines are without stress-dependent diffusion model.  $X_{active}$ =0.6 $\mu$ m with stress-dependent model device exhibits significant retardation of dopant diffusion.

- Fig. 2.13 Experimental and simulated  $I_D$ - $V_G$  curves for  $X_{active}$ =1.46 $\mu$ m. Symbols represent experimental data, dashed lines are the simulation results without considering stress-dependent diffusion models, and solid lines are the final simulated results including stress-dependent diffusion models.

- Fig. 2.14 Simulated strain distribution in the silicon after entire front-end process for  $X_{active}$ =0.68 $\mu$ m. The total strain is in the MOSFET core region are compressive due to thermal gate oxidation and thermal mismatch between STI oxide and silicon.

- Fig. 2.15  $I_D$  values at  $V_G$ =-0.4 V for  $X_{active}$ =20.2  $\mu m$ ,  $X_{active}$ =1.46 $\mu m$ , and  $X_{active}$ =0.68 $\mu m$ . Symbols represent experimental data and solid lines are the final simulated results including stress-dependent diffusion models.

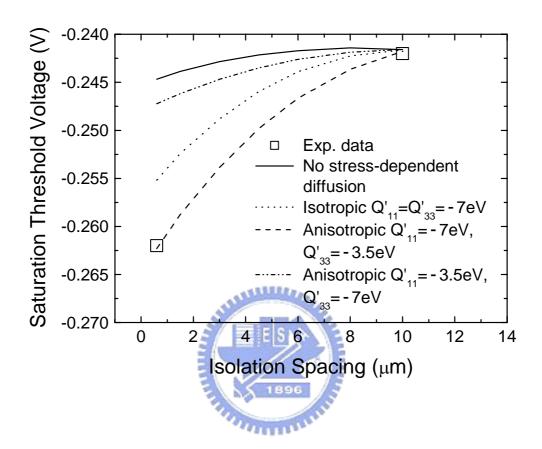

- Fig. 2.16 Measured pMOSFET saturation threshold voltage versus the spacing between the nearby trench isolation sidewalls in the channel length direction. Also shown are those (lines) from the process-device coupled simulation with and without the strain induced activation energies.

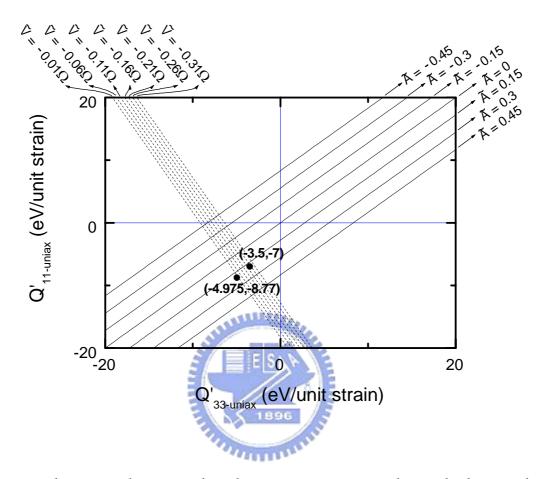

- Fig. 2.17 Uniaxial strain induced activation energy in the applied stress direction (parallel to the silicon surface) versus that normal to the silicon surface.

The lines are from Eq. (2.14) and (2.15) for a literature range (Ref. [3.25]-[3.27]) of the activation volume and the migration strain anisotropy.

Also plotted are the data points from the underlying experiment and the existing *ab initio* calculations (Ref. [3.20], [3.29]).

#### Chapter 3

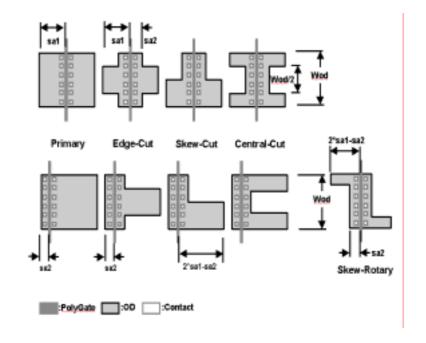

- Fig. 3.1 Key MOSFET layout parameter definitions in this work and schematic cross section along channel length direction.

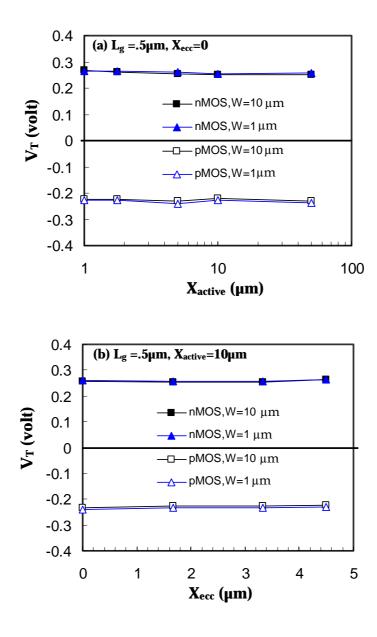

- Fig. 3.2 Long channel threshold voltage  $V_T$  versus (a)  $X_{active}$  and (b)  $X_{ecc}$  for a variety of W. Obviously,  $V_T$  is insensitive to STI mechanical stress.

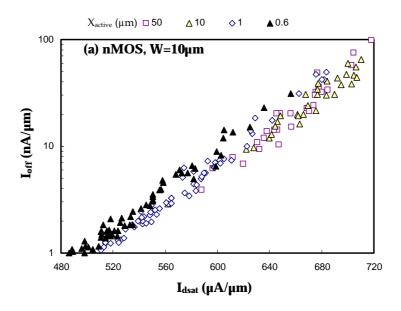

- Fig. 3.3 Short channel Idsat-Ioff for (a) nMOSFET and (b) pMOSFET for a variety of  $X_{active}$ . Idsat at Ioff=10nA/ $\mu$ m is taken as drive current index.

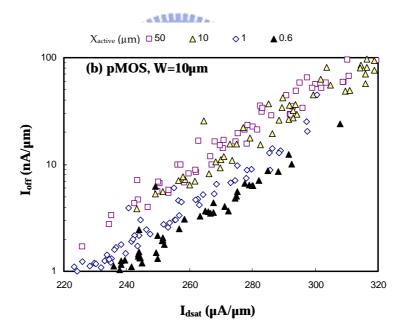

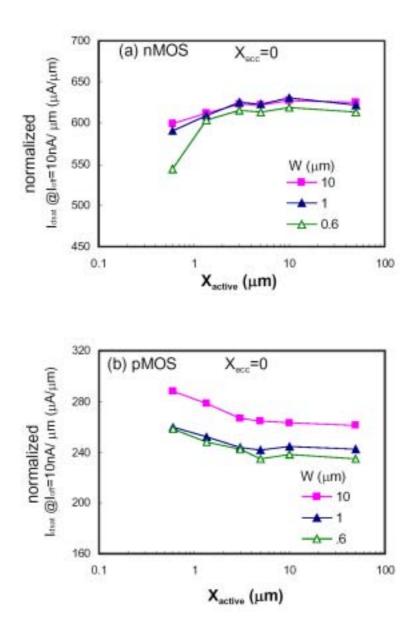

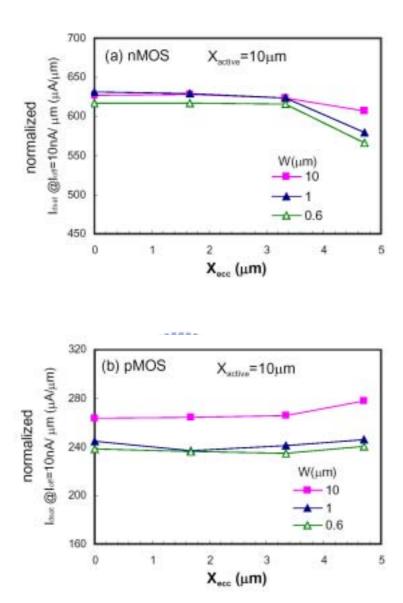

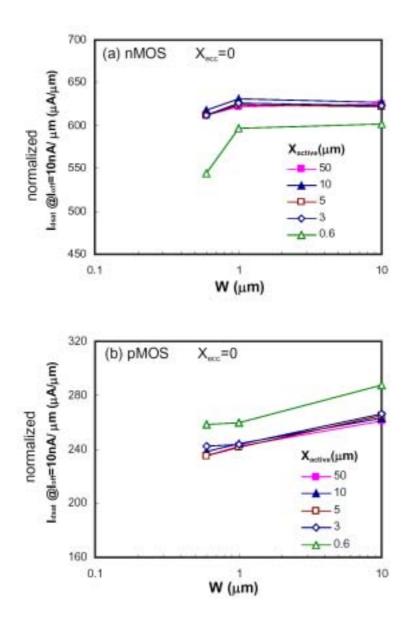

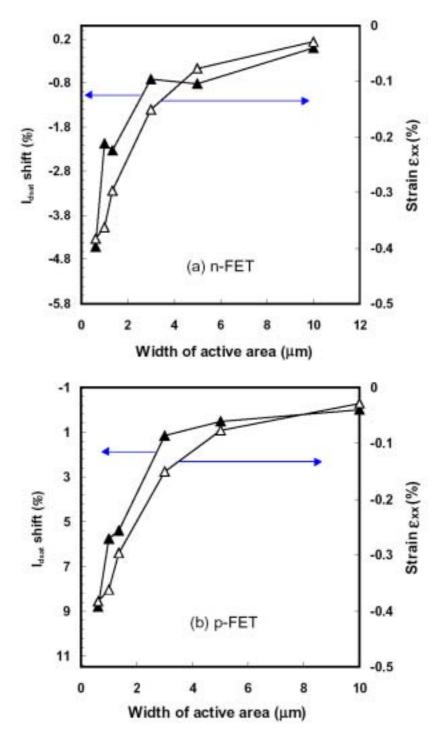

- Fig. 3.4 Short channel Idsat versus active area dimension  $X_{active}$  with different W for (a) nMOSFET and (b) pMOSFET. nMOSFET Idsat is degraded while pMOSFET Idsat is enhanced as active area size decreases. Idsat becomes insensitive to  $X_{active}$  when active area size is greater than  $5\mu m$ .

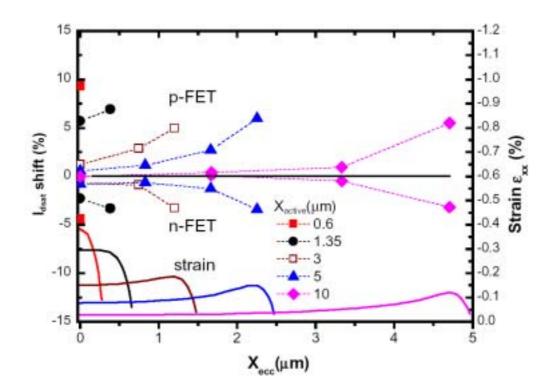

- Fig. 3.5 Short channel Idsat versus gate placement inside active area  $X_{ecc}$  for different W for (a) nMOSFET and (b) pMOSFET. nMOSFET Idsat is degraded while pMOSFET Idsat is enhanced as gate placement is closer to STI edge.

- Fig. 3.6 Short channel Idsat versus W for (a) nMOSFET and (b) pMOSFET with various  $X_{\text{active}}$ . Both n and pMOSFET drain currents degrade as W decreases.

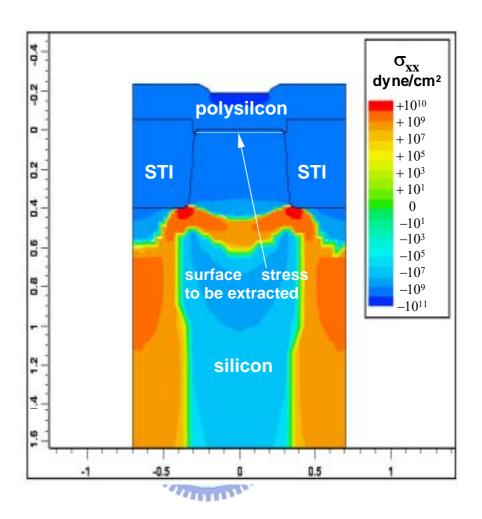

- Fig. 3.7 Simulated final stress  $S_{xx}$  distribution for  $X_{active}$ =0.6 $\mu$ m. Stress near Si/SiO2 interface is found to be compressive.

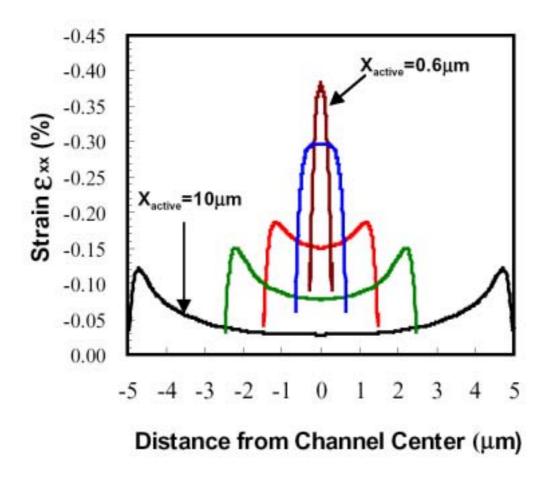

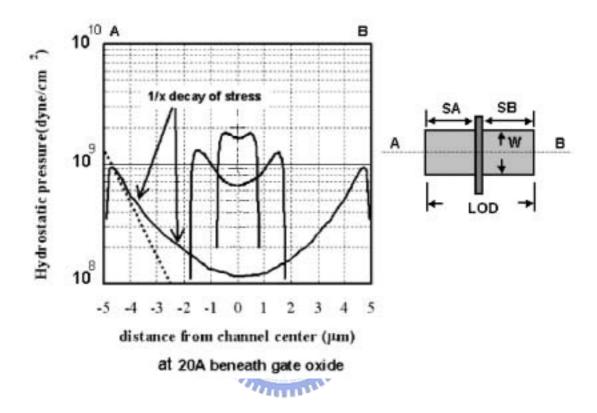

- Fig. 3.8 Simulated strain  $\varepsilon_{xx}$  inside silicon along a line 20Å deep below Si/SiO2 interface for different active area dimensions. Strain magnitude increases as active area size decreases.

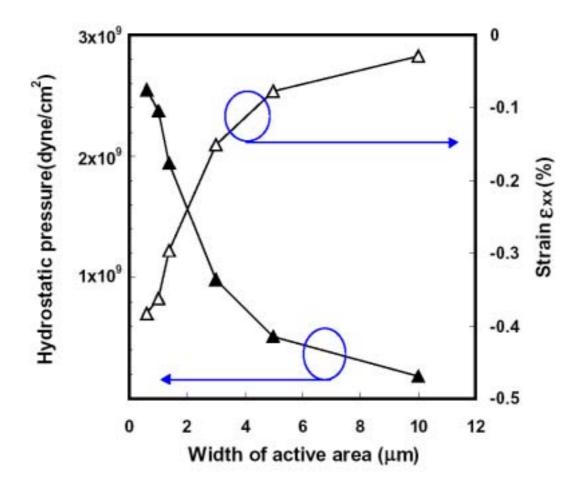

- Fig. 3.9 Simulated hydrostatic pressure and strain  $\epsilon_{xx}$  for different active area dimensions. Stress and strain magnitudes increase rapidly as active area size decreases from around  $5\mu m$ .

- Fig. 3.10 Experimental drive current sensitivity and simulated strain  $\epsilon_{xx}$  both versus active area size for (a) n-FET and (b) p-FET. A one-to-one mapping remains effective for both n-FETs and p-FETs.

- Fig. 3.11 Experimental drive current shift with respect to W=10mm,  $X_{ecc}$ =0 versus  $X_{ecc}$  for different  $X_{active}$ . Simulated strain  $\epsilon_{xx}$  is also shown together for comparisons. The trends of drive current and strain match well.

- Fig. 3.12 Stress distribution near the gate oxide interface of MOSFET using 2D simulation.

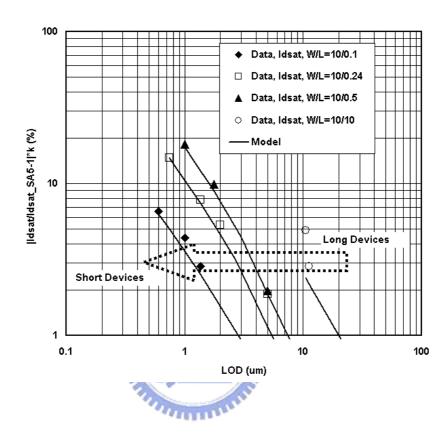

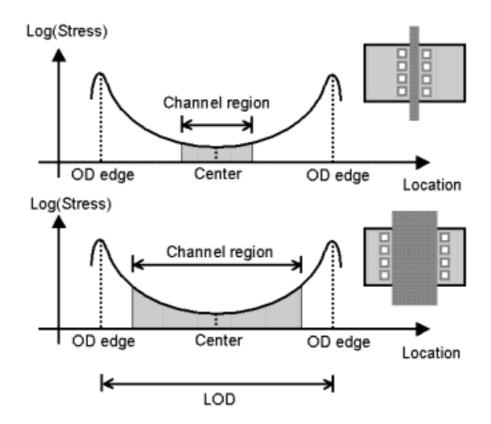

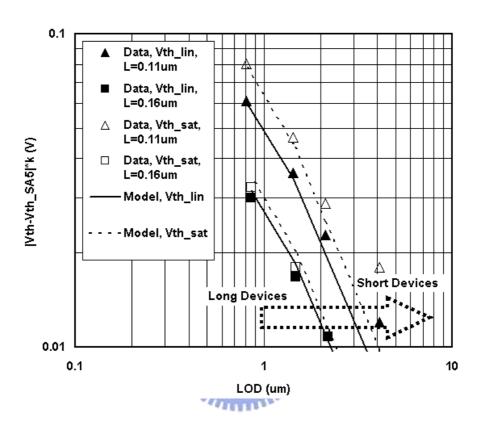

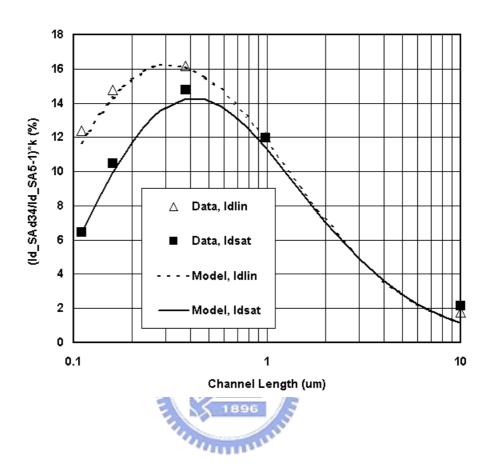

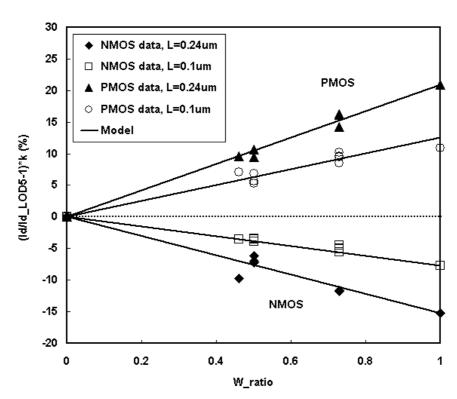

- Fig. 3.13 Drain current shift with respect to different LOD sizes for different channel lengths.

- Fig. 3.14 schematic stress distribution within the channel regions.

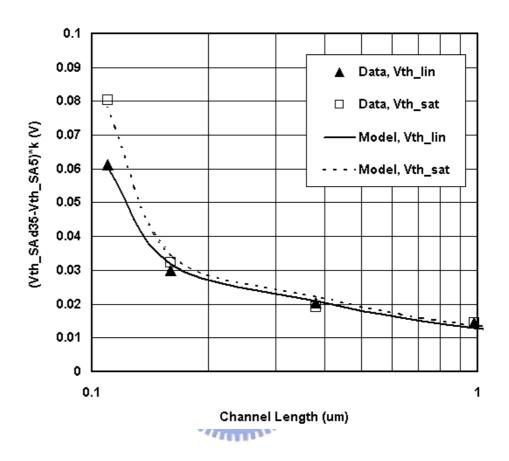

- Fig. 3.15 Threshold voltage shift with respect to different LOD sizes for different channel lengths.

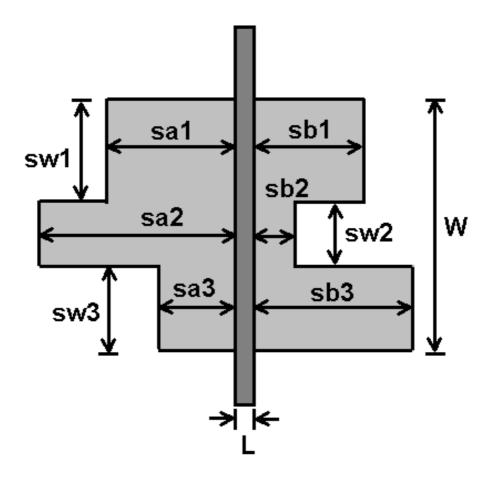

- Fig. 3.16 A typical layout of MOS devices needing more instance parameters (swi, sai and sbi) in addition to the traditional L and W.

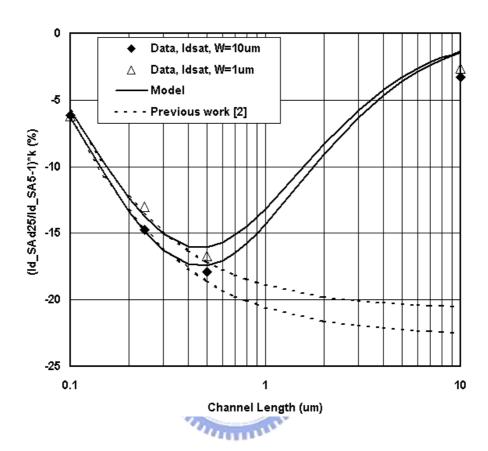

- Fig. 3.17 nMOSFET drain current (Id) difference in percentage between SA=0.25µm and 5µm comparing various channel lengths and widths.

- Fig. 3.18 pMOSFET drain current (Id) difference in percentage between SA=0.25μm and 5μm comparing drain currents in linear and saturation regions.

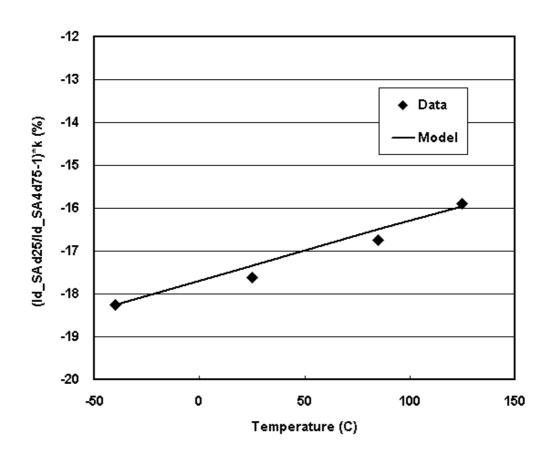

- Fig. 3.19 Temperature sensitivity of LOD effect. LOD effect is quite insensitive to temperature and simply a linear equation could simulate the dependence.

- Fig. 3.20 Vth shift between SA=0.25 $\mu$ m and SA=5 $\mu$ m with Vds=0.1V and Vdd for different channel lengths.

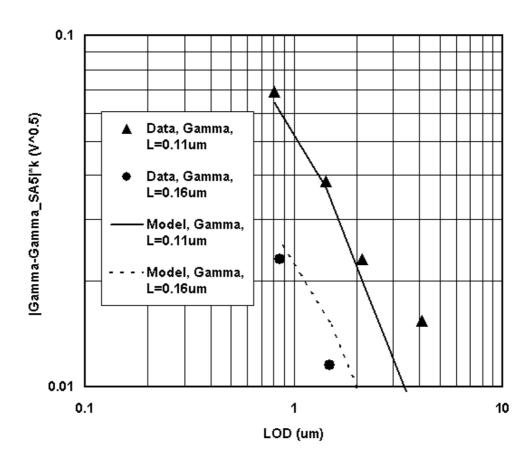

- Fig. 3.21 Gamma shift versus LOD with different channel lengths. Gamma increases as LOD decreases because of higher channel doping concentrations due to diffusion retardations by compressive stress.

- Fig. 3.22 Symmetric and asymmetric irregular layouts under study and the corresponding drain current shift in percentage.

#### Chapter 4

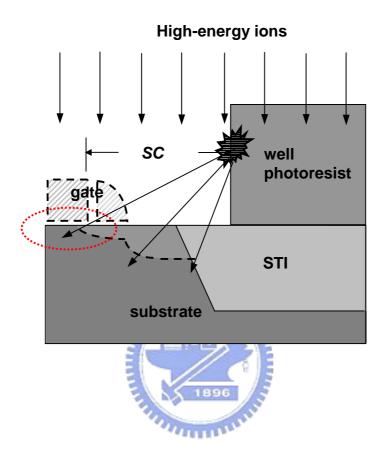

- Fig. 4.1 Origin of well edge proximity effect. High-energy dopant ions scatter at the well photoresist edge during the well ion implantation and the scattered ions are implanted in the MOSFET channel before the gate is formed. *SC* denotes the distance of well-photoresist edge to MOSFET gate edge.

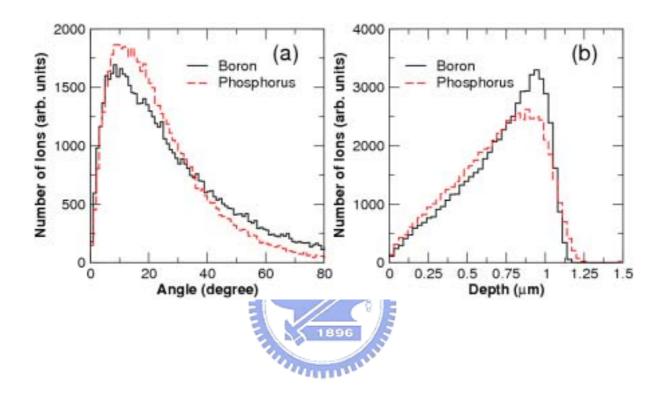

- Fig. 4.2 (a) Angular and (b) depth distributions of the ions scattered out of the photoresist edge for B 300keV and P 625keV implants. The angle is measured from the incident direction, and the depth is the vertical distance from the top surface of the photoresist to the point where the ion exits from the photoresist edge.

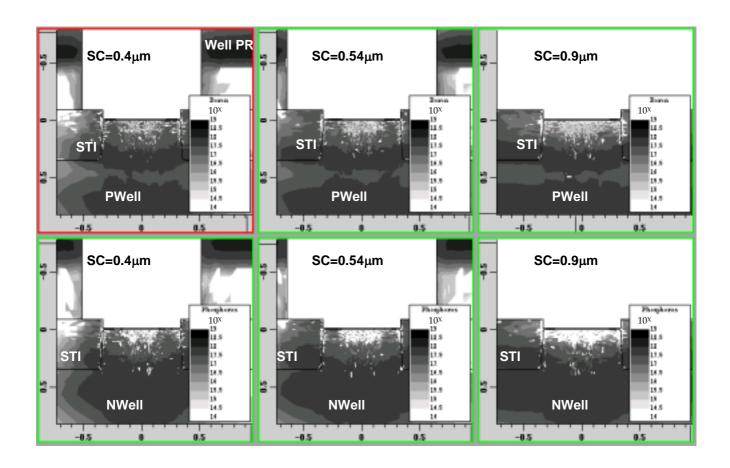

- Fig. 4.3 TCAD simulated dopant distribution versus well to gate edge distance, SC.

- The well dopant distributions are influenced by the SC value. When SC decreases, extra well dopant clusters move toward the center of the active area.

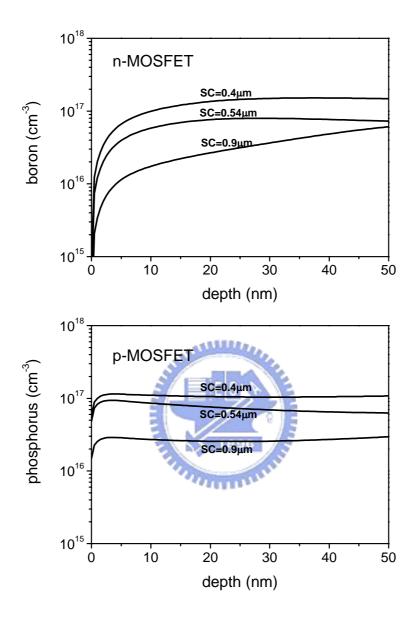

- Fig. 4.4 TCAD simulated vertical channel dopant profile versus well to gate edge distance, SC. The channel dopant concentration increases as the well photoresist edge approaches the MOSFET active area.

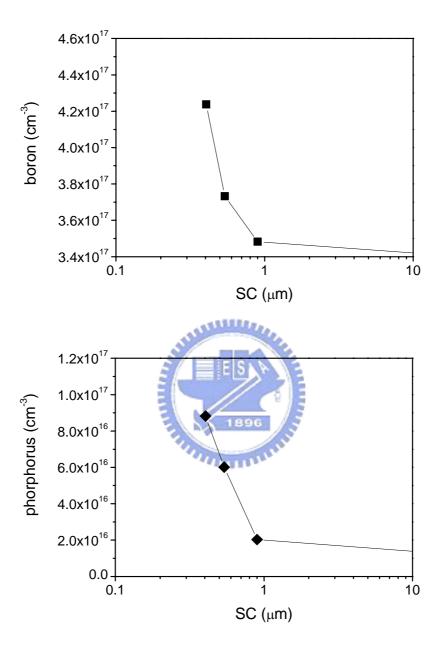

- Fig. 4.5 TCAD simulated average dopant concentration for the area 20nm below the MOSFET gate versus SC.

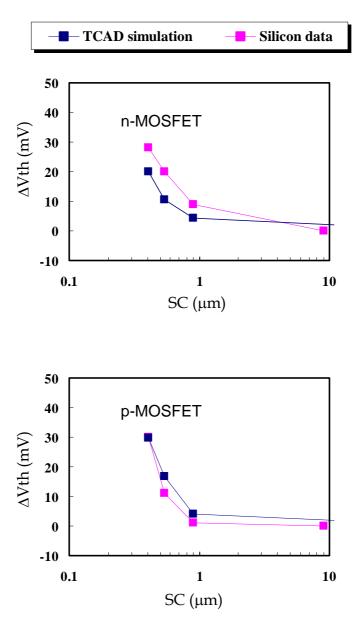

- Fig. 4.6 MOSFET threshold voltage shift versus well to gate edge distance of the silicon experimental and TCAD simulated results for n and pMOSFET. Lg= $0.216\mu m$ .

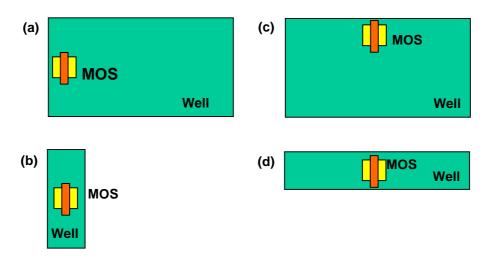

- Fig. 4.7 Typical layouts showing different positions of MOS transistors in a well.

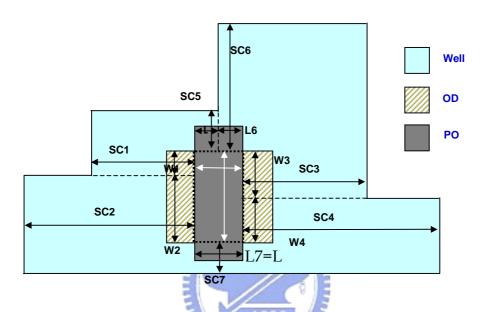

- Fig. 4.8 Schematic presentation of a MOSFET layout and parameters used to establish a well-edge proximity SPICE model.

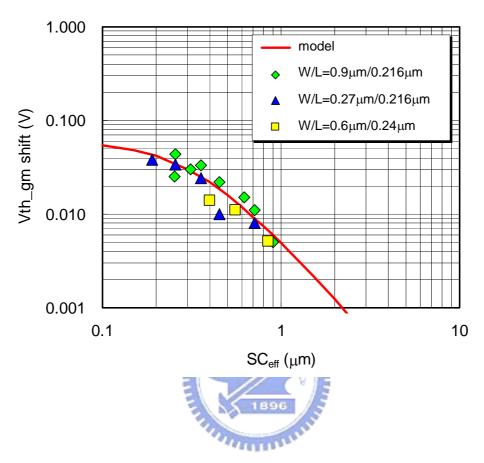

- Fig. 4.9 Model verification results of the MOSFET threshold voltage shift compared to the silicon experiment data.

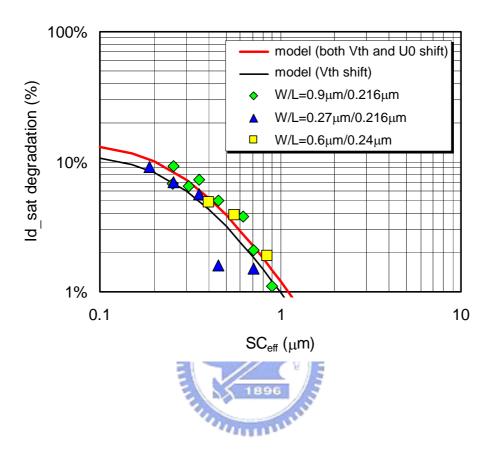

- Fig. 4.10 Model verification results of the MOSFET drive current degradation compared to the silicon experiment data.

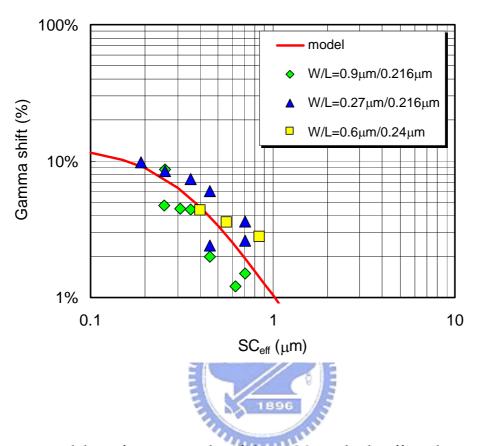

- Fig. 4.11 Model verification results of the MOSFET body effect change compared to the silicon experiment data.

#### **Chapter 1**

#### Introduction

#### 1.1 Overview

During the last half of the previous century, the evolution of semiconductor technology became a major influence in the development of modern electronics. Developing a greater understanding of the function of both the positive and negative aspects of layout dependent effects such as the mechanical stress effect and the boundary ion implantation scattering effect is an essential part of device design and operation, and will no doubt continue to play an increasingly important role in the continuing evolution of the technology.

In Metal-Oxide-Semiconductor-Field-Effect-Transistor (MOSEFT) technology, layout dependent effects are inherently generated through the manufacturing processes, such as shallow trench isolation (STI), thermal oxidation, film deposition, and ion implantation scattering at the photoresist edges, which until recently were considered as a secondary effect. Moore's law states that the number of transistors that can be created in a specific space will approximately double for each successive generation (18~24 months), which means that, as the technology follows the predicted path, the mechanical stress effect becomes more severe and gains more importance and focus. The trend toward increasingly smaller device sizes combined with predictions by the ITRS [1.1], shown in Fig. 1.1, clearly illustrates the past achievements of the industry, and also suggests that this trend is likely to

continue to follow Moore's law for the foreseeable future.

Mechanical stress is the first effect being considered to make MOSFET layout dependent [1.2]-[1.5]. For some technologies, such as piezoresistive sensors and micro-electro-mechanical systems (MEMS), mechanical stress is a major feature of device operation. In the CMOS technologies, as the active area of each device is reduced, device designers are often forced to place the stress-generating sources closer together, with the influence of individual components often being superimposed upon each other, which, in turn, increases the magnitude of the mechanical stress. In addition, scaling rules also require MOSFET channel lengths to be reduced, thereby, accelerating the rate of increase in the average channel stress of the MOSFET, causing a significant impact on device performance that cannot be neglected [1.2]-[1.5]. Another aspect is that MOSFET performance can also be regarded as acting in a similar manner to Moore's law, increasing by ~15% per generation as, in the past, any improvement could be roughly achieved simply by scaling the length, oxide thickness and junction depth. The era of such simplicity has now dissipated as polysilicon gate depletion, gate oxide leakage, the quantum mechanical effect, and carrier scattering became more severe once the technology entered the sub-100nm regime. In this situation, mechanical stress is not only considered to be a by-product of the aggressive downscaling of device feature sizes, but, recently, has also been generated deliberately in order to improve MOSFET performance. Technologies, such as the inclusion of a cap layer with high-level intrinsic stress following the formation of source and drain [1.6], [1.7], strained silicon epitaxy on a strain-relaxed SiGe [1.8], [1.9], and a lattice mis-matched source and drain using selective epitaxy of SiGe [1.10] or SiC [1.11], have been widely used to boost MOSFET drive currents. Fig. 1.2 illustrates a set of recent cross-sectional TEM pictures for a CMOSFET with 35nm gate lengths, which show that the mechanical strain improved the mobility of the NMOSFET by 40% and the PMOSFET by 100% when compared to the unstrained MOSFETs [1.12].

Any analysis of the influence of mechanical stress on a MOSFET can be divided into two categories: (1). Physical changes that occur during the device fabrication process and, (2). Energy band structure changes. Of the two most common physical changes, the first, crystal flaws, has been observed since the early stages of semiconductor technology. There are several types of defects that can be commonly observed in silicon crystal, which are usually classified from their dimensionalities, such as interstitial atoms and vacancies (point defects), dislocations (line defects), stacking faults and slip lines (area defects), and voids (volume defects). Point defects always exist in the crystals and are highly mobile, generated and eliminated with low energy barriers as temperature increases. Their distribution plays an important role in dopant diffusion and is also affected by mechanical stress. Line defects and area defects are generally unwanted and are produced under enormous levels of mechanical stress during the manufacturing process. These crystal flaws will induce a large unwanted leakage current, if they are located near the PN junctions (source and drain or wells), or damage the gate oxide of the MOSFET. Several papers [1.13]-[1.16] have reported that the crystal defects generated by the

mechanical stress produced a junction leakage current as a result of the scaling of the devices. Large volume defects in the crystal, such as voids, are detrimental, but are seldom observed nowadays since they are usually well-controlled in modern silicon crystal growth technology and are not easily generated during the CMOS manufacturing process. Instead, dopant clusters and precipitates have become an increasingly important type of volume defect due to high dopant concentration and shorter thermal annealing time.

Dopant diffusion changes under different magnitudes of stress represent the second most common physical change and have become more prominent recently as a result of increases in the magnitude of mechanical stress as the dimensions of the MOSFET are scaled down. Changes in dopant diffusion result in a difference in the final dopant distribution, which will be reflected in the changes in subthreshold behavior and short channel effects (SCE) in the MOSFET. One of the difficulties encountered in stress-dependent dopant diffusion studies is that it is hard to measure the 2-D dopant diffusion directly. Therefore, the methodology of inverse modeling [1.17], which makes use of the sensitivity of the MOSFET subthreshold current-voltage to 2-D dopant profile, is utilized in this dissertation.

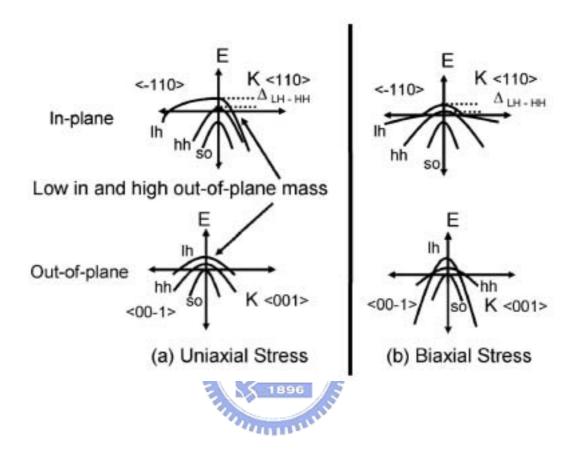

The second category covers the resultant mechanical stress in the MOSFET, inducing a silicon energy band structure change, which, in turn, affects the carrier effective mass of the carrier, together with the mobility and the on-state drive current of the MOSFET [1.18]-[1.25]. Fig. 1.3 and 1.4 shows the simplified band structure changes with the mechanical stress for electrons and holes, respectively, adopted

from Ref.[1.21] and [1.25]. The benefit of improving carrier mobility using mechanical stress, rather than improving the gate dielectric constant, is that the loading capacitance will not increase.

The second effect making the highly scaled MOSFET characteristics layout dependent is the dopant scattering at photo-mask edge during the ion implantations. Recently, strong effects have been observed especially when CMOS wells are formed by using high energy ion implantations [1.26]-[1.30]. The effect of the well-edge proximity to the MOSFET gates was first reported by Hook [1.26] and originates from the lateral scattering of ion implantations at the photoresist edge when forming MOSFET wells, which in turn causes a change in the MOSFET threshold voltage. Fig. 1.5 shows the simulated two-dimensional dopant distribution contours and lateral doping profiles of B and P immediately below the silicon surfaces. The studies on this effect are still preliminary and the effect becomes of increasing importance as CMOS devices continue to shrink further.

#### 1.2 TCAD modeling

Numerical simulation has been widely applied in many scientific and engineering fields. It has been utilized for the physical understanding of semiconductor technology development through physical understanding in semiconductors, and is named as Technology Computer-Aided Design, or TCAD. As the technology continues to be developed, TCAD has become of increasing importance for two main reasons. The first mainly is because both the process and

the device physics have become more and more complex. From the process perspective, except for mechanical stress increases during scaling, novel process flows, including multi-species ion implantations and extremely short thermal process times, cause the dopant diffusion behavior to greatly deviate from traditional diffusion laws. In such cases, it is difficult to predict the dopant distribution in the device simply by using empirical calculations. The dopant profiles can only be obtained by solving complex coupled equations, such as damage production, point defect annihilation, and the cluster effect between point defects and dopants.

The second reason is a result of the need for cost reductions by increasing the wafer size for mass production, so the cost of a single wafer for experimental purposes increases rapidly as the wafer diameter increases. Furthermore, the high process-complexity of nano-scaled CMOS technology makes the cost of a single experiment conditions even higher. Therefore, TCAD is needed to help comprehend the complex physical phenomena inside semiconductor devices, to predict the result from process conditions, and to decide the domain of the wafer experiment. In fact, it not only helps to reduce the cost, but also shortens the time taken to reach the mass production stage, since computer simulation time is generally much shorter than the wafer process times. With the development and addition of some remarkable computer capabilities, researchers are now able to quickly conduct "virtual experiments" using a computer before real experiments in silicon are performed, and they can aim for targets with smaller experiment domains.

One of the features of TCAD is based on numerical methods, such as

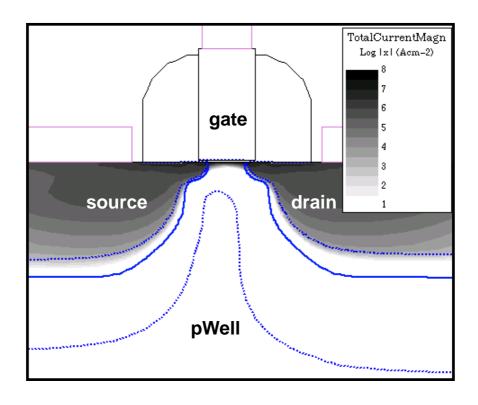

finite-differential and finite-element methods, which first establish the desired simulation structures (continuum) and divide the structures into diminutive elements and nodes using meshes. Then, basic physical equations are implemented and solved for the boundary conditions of each element and node, and a consistent result is obtained for the continuum. For process simulations, basic theories of dopant and defect diffusions, ion implantations, oxidation, and mechanical stress evolutions are solved. Fig. 1.6 shows the simulation results of dopant distribution in a MOSFET. After process simulation, device simulation is desired in order to determine the potential electrical behavior of the device. For device simulation, Poisson's equation, carrier drift-diffusion equations, tunneling equations and quantum effect approximation equations are solved according to terminal bias conditions. Fig. 4 shows the carrier distribution of the MOSFET.

As the rush toward the next generation of semiconductor technology gathers pace, the necessity for conducting experimental work, as well as numerical simulations, in order to realize the impact of layout dependent effects on scaled MOSFETs, has gained focus. The goal of this dissertation is to study the layout dependent effect by conducting experiments using nano-scaled MOSFET technology, and to perform numerical process and device simulations using TCAD tools to investigate the mechanical stress distribution, stress-dependent dopant diffusion, and boundary dopant scattering effects during ion implantations encountered in the MOSFET from a full process point of view, and to explain MOSFET behavior using the proposed physical-based models.

#### 1.3 Dissertation Organization

Chapter two begins with an introduction to the theory and the experiments designed to explore dopant diffusion under mechanical stress. The implementation of the proposed stress-dependent diffusion model into the TCAD simulation tools, TSUPREM4 and MEDICI, is then presented. Three applications, stress dependent diffusion effect on the MOSFETs threshold voltage, stress dependent diffusion effect on the subthreshold leakage of the low dopant concentration well nMOSFET, and anisotropic diffusion under uniaxial strain are introduced in detail.

Chapter three discusses the influence of mechanical stress on the on-state behavior of the MOSFET. The change in structure of the energy-band, and the resulting impact on drive current for both n and pMOSFETs, is discussed. The implementation of a new model into SPICE that accounts for the mechanical stress effect is also proposed for the circuit design.

Chapter four first addresses the dopant scattering effect at well-mask edges on the modern MOSFETs by a designed wafer experiment. In-depth understanding is displayed using full process and device simulations of TCAD tools. Physic-based SPICE models is proposed and is validated with experimental data for better circuit simulation accuracies.

Finally, Chapter five offers a conclusion to the research, together with a summary of the accomplishments, and addresses future work to be extended to the topics of this dissertation.

#### References

- [1.1] International technology roadmap for semiconductors, 2005 edition, executive summary.

- [1.2] G. Scott, J. Lutze, M. Rubin, F. Nouri, and M. Manley, "NMOS drive current reduction caused by transistor layout and trench isolation induced stress," in *IEDM Tech. Dig.*, Dec. 1999, pp. 827-830.

- [1.3] R. A. Bianchi, G. Bouche, and O. Roux-dit-Buisson, "Accurate modeling of trench isolation induced mechanical stress effects on MOSFET electrical performance," in *IEDM Tech. Dig.*, Dec. 2002, pp. 117-120.

- [1.4] Y. M. Sheu, Kelvin Y. Y. Doong, C. H. Lee, M. J. Chen, and C. H. Diaz, "Study on STI mechanical stress induced variations on advanced CMOSFETs," in *Proc. of ICMTS*, Mar. 2003, pp. 205-208.

- [1.5] K. W. Su, Y. M. Sheu, C. K. Lin, S. J. Yang, W. J. Liang, X. Xi, C. S. Chiang, J. K. Her, Y. T. Chia, C. H. Diaz, and C. Hu, "A scaleable model for STI mechanical stress effect on layout dependence of MOS electrical characteristics," in *Proc. of Custom Integrated Circuits Conference*, Sep. 2003, pp. 245-248.

- [1.6] S. Ito, H. Namba, K. Yamaguchi, T. Hirata, K. Ando, S. Koyama, S. Kuroki, N. Ikezawa, T. Suzuki, T. Saitoh, and T. Horiuchi, "Mechanical stress effect of etch-stop nitride and its impact on deep submicron transistor design," in *IEDM Tech. Dig.*, Dec. 2000, pp. 247-250.

- [1.7] C. H. Ge, C. C. Lin, C. H. Ko, C. C. Huang, Y. C. Huang, B. W. Chen, B. C. Perng, C. C. Sheu, P. Y. Tsai, L. G. Yao, C. L. Wu, T. L. Lee, C. J. Chen, C. T.

- Wang, S. C. Lin, Y. C. Yeo, and C. Hu, "Process-strained Si (PSS) CMOS technology featuring 3D strain engineering," in *IEDM Tech. Dig.*, Dec. 2003, pp. 73-76.

- [1.8] K. Rim, J, Chi, H. Chen, K.A. Jenkins, T. Kanarsky, K. Lee, A. Mocuta, H. Zhu, R. Roy, J. Newbury, J. Ott, K. Petrarca, P.M. Mooney, D. Lacey, K. Koester, K. Chan, D. Boyd, M. Ieong, and H.-S. Wong, "Characteristics and device design of sub-100 nm strained Si N- and PMOSFETs," In *VSLI Symp. Tech. Dig.*, Jun. 2002, pp. 98–99.

- [1.9] J. Jung, S. Yu, M. L. Lee, J. L. Hoyt, E. A. Fitzgerald, and D. A. Antoniadis "Mobility Enhancement in Dual-Channel P-MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, pp. 1424-1431, September 2004.

- [1.10] S. E. Thompson, M. Armstrong, C. Auth, M. Alavi, M. Buehler, R. Chau, S. Cea, T. Ghani, G. Glass, T. Hoffman, C. H. Jan, C. Kenyon, J. Klaus, K. Kuhn, Z. Ma, B. Mcintyre, K. Mistry, A. Murthy, B. Obradovic, R. Nagisetty, P. Nguyen, S. Sivakumar, R. Shaheed, L. Shifren, B. Tufts, S. Tyagi, M. Bohr, and Y. El-Mansy, "A 90-nm logic technology featuring strained-silicon," *IEEE Trans. Electron Devices*, vol. 51, pp. 1790-1797, November 2004.

- [1.11] K. W. Ang, K. J. Chui, V. Bliznetsov, A. Du, N. Balasubramanian, M. F. Li, G. Samudra, and Y. C. Yeo, "Enhanced performance in 50 nm N-MOSFETs with silicon-carbon source/drain regions," in *IEDM Tech. Dig.*, Dec. 2004, pp. 1069-1071.

- [1.12] S. Tyagi, C. Auth, P. Bai, G. Curello, H. Deshpande, S. Gannavaram, O.

- Golonzka, R. Heussner, R. James, C. Kenyon, S-H Lee, N. Lindert, M. Liu, R. Nagisetty, S. Natarajan, C. Parker, J. Sebastian, B. Sell, S. Sivakumar, A. St Amour, K. Tone "An advanced low power, high performance, strained channel 65nm technology," in *IEDM Tech. Dig.*, Dec. 2005, pp. 245-248.

- [1.13] J. Damiano, C. K. Subramanian, M. Gibson, Y.-S. Feng, L. Zeng, J. Sebek, E. Deeters, C. Feng, T. McNelly, M. Blackwell, H. Nguyen, H.Tian, J. Scott, J. Zaman, C. Honcik, M. Miscione, K. Cox, and J. D. Hayden, "Characterization and elimination of trench dislocations," in *VSLI Symp. Tech. Dig.*, Jun. 1998, pp. 212–213.

- [1.14] T. K. Kim, D. H. Kim, J. K. Park, T. S. Park, Y. K. Park, H. J. Lee, K. Y. Lee, J. T. Kong, J. W. Park, "Modeling of cumulative thermo-mechanical stress (CTMS) produced by the Shallow trench isolation process for 1Gb. DRAM and beyond" in *IEDM Tech. Dig.*, Dec. 1998, pp. 145-148.

- [1.15] D. Ha, C. Cho, D. Shin, G. H. Koh, T. Y. Chung, and K. Kim, "Anomalous junction leakage current induced by STI dislocations and its impact on dynamic random access memory devices," *IEEE Trans. Electron Devices*, vol. 46, pp. 940-946, May 1999.

- [1.16] J. W. Sleight, C. Lin, and G. J. Grula, "Stress Induced Defects and Transistor Leakage for Shallow Trench Isolated SOI," *IEEE Electron Devices Lett.*, vol. 20, pp. 248-250, Dec. 1999.

- [1.17] Z. K. Lee, M. B. McIlrath, and D. A. Antoniadis, "Two-dimensional doping profile characterization of MOSFET's by inverse modeling using I-V

- characteristics in the subthreshold region," *IEEE Trans. Electron Devices*, vol. 46, pp. 1640-1649, August 1999.

- [1.18] G. Dorda, "Peizoresistance in quantized conduction bands in silicon inversion layers," *J. Appl. Phys.*, vol. 42, pp. 2053-2060, April 1971.

- [1.19] J. Welser, J. L. Hoyt, and J. F. Gibbons, "Electron mobility enhancement in strained-Si N-type metal-oxide-semiconductor field-effect transistors," *IEEE Electron Device Lett.*, vol. 15, pp. 100–102, Feb. 1994.

- [1.20] A. Lochtefeld and D. A. Antoniadis, "Investigating the relationship between electron mobility and velocity in deeply scaled NMOS via mechanical stress," *IEEE Electron Device Lett.*, vol. 22, pp. 591–593, Aug. 2001.

- [1.21] S. Takagi, J. L. Hoyt, J. J. Welser, and J. F. Gibbons, "Comparative study of phonon-limited mobility of two-dimensional electrons in strained and unstrained Si metal-oxide-semiconductor field-effect transistors," *J. Appl. Phys.*, pp. 1567-1577, vol. 80, August 1996.

- [1.22] E. X. Wang, P. Matagne, L. Shifren, B. Obradovic, R. Kotlyar, S. Cea, M. Stettler, and M. D. Giles, "Physics of hole transport in strained silicon MOSFET inversion layers," *IEEE Trans. Electron Devices*, vol. 53, pp. 1840-1851, August 2006.

- [1.23] X. F. Fan, X. Wang, B. Winstead, L. F. Register, U. Ravaioli, and S. K. Banerjee, "MC Simulation of Strained-Si MOSFET With Full-Band Structure and Quantum Correction," *IEEE Trans. Electron Devices*, vol. 51, pp. 962-970, June 2004.

- [1.24] S. E. Thompson, M. Armstrong, C. Auth, M. Alavi, M. Buehler, R. Chau, S. Cea, T. Ghani, G. Glass, T. Hoffman, C. H. Jan, C. Kenyon, J. Klaus, K. Kuhn, Z. Ma, B. Mcintyre, K. Mistry, A. Murthy, B. Obradovic, R. Nagisetty, P. Nguyen, S. Sivakumar, R. Shaheed, L. Shifren, B. Tufts, S. Tyagi, M. Bohr, and Y. El-Mansy, "A 90-nm logic technology featuring strained-silicon," *IEEE Trans. Electron Devices*, vol. 51, pp. 1790-1797, November 2004.

- [1.25] S. Thompson, G. Sun, K. Wu, J. Lim, and T. Nishida, "Key differences for process-induced uniaxial vs. substrate-induced biaxial stressed Si and Ge channel MOSFETs" in *IEDM Tech. Dig.*, Dec. 2004, pp. 221-224.

- [1.26] T. B. Hook, J. Brown, P. Cottrell, E. Adler, D. Hoyniak, J. Johnson, and R. Mann, "Lateral Ion Implant Straggle and Mask Proximity Effect," *IEEE Trans. Electron Devices*, vol. 50, pp. 1946-1951, September 2003.

- [1.27] K. W. Su, Y. M. Sheu, C. K. Lin, S. J. Yang, W. J. Liang, X. Xi, C. S. Chiang, J. K. Her, Y. T. Chia, C. H. Diaz, and C. Hu, "A scaleable model for STI mechanical stress effect on layout dependence of MOS electrical characteristics," in Proc. of Custom Integrated Circuits Conference, Sep. 2003, pp. 245-248.

- [1.28] J. Watts, K. W. Su, and M.Basel, "Netlisting and Modeling Well-Proximity Effects," *IEEE Trans. Electron Devices*, vol. 53, pp. 2179-2186, September 2006.

- [1.29] Y. M. Sheu, K. W. Su, S. Tian, S. J. Yang, C. C. Wang, M. J. Chen, and S. Liu, "Modeling the Well-Edge Proximity Effect in Highly Scaled MOSFETs," *IEEE Trans. Electron Devices*, vol. 53, pp. 2792-2798, November 2006.

Berkeley Short-channel IGFET Model (BSIM) version 4.5.0 manual, chapter 14.

Fig. 1.1 Half pitch and gate length trends predicted by ITRS (adapted from Ref.[1.1]).

Fig. 1.2 TEM images of 35nm-gate-length MOSFETs using mechanical strained technologies (adapted from Ref.[1.12]).

Fig. 1.3 Schematic representation of the constant-energy ellipses for (a) and (b) unstrained Si and (c) and (d) strained Si. (a) and (c) are for a 3DEG in bulk Si. (b) and (d) are those of a 2DEG in a Si inversion layer. (e) and (f) are the schematic diagrams for bulk strained Si and an inversion layer in strained Si, respectively. (adapted from Ref.[1.19]).

Fig. 1.4 Simplified valence band E vs. k diagram for strained Si (adapted from Ref.[1.25]).

(a) 2-D dopant concentration contour plot

(b) Dopant profiles of lateral cut line in the 2D contour plot

Fig. 1.5 (a) Contour plot of simulated doping near resist mask edge. Both boron (intermediate and near-surface) and phosphorus (deep) implantations were simulated. (b) Simulated lateral doping profiles of B and P immediately below the silicon surfaces (adapted from Ref.[1.12]).

Fig. 1.6 Simulated dopant distribution contours of a novel MOSFET using a TCAD tool (TSURPEM4).

Fig. 1.7 Simulated (a) electrical current distribution contours and (b) output current-voltage plot of the MOSFET shown in Fig. 1.6.

## Chapter 2

## **Dopant Diffusion Under Mechanical Stress**

#### 2.1 Preface

Shallow trench isolation (STI) induced mechanical stress increases in magnitude with reduced device active areas of highly scaled CMOS technology, causing a non-negligible impact on device performance [2.1]-[2.4]. Both experimental work and numerical simulations have been conducted to calculate the STI stress magnitude and distribution encountered in scaled MOSFETs [2.5]-[2.9]. The results show that the silicon stress level near the STI region is high. As design rules or layout dimensions scale down, the high-stress region encroaches further into the MOSFET channel. Thus, STI mechanical stress has a significant influence on state-of-the-art device performance.

Earlier work studying the mechanical stress effect has been focused on the MOSFET drive current shift, either in the form of localized or planar stress conditions [2.1]- [2.3], [2.6], [2.10]-[2.14]. Several studies have been performed to link STI mechanical stress to mobility changes while accounting for the observed current shift [2.2], [2.12], [2.13], although no threshold voltage shift mechanism has been investigated. G. Scott, *et al.* [2.14] have investigated both the drive current and threshold voltage shift, suggesting a difference in stress-induced diffusivity as the plausible origin of the threshold voltage shift. So far, however, there has been no further elaboration on this aspect. On the other hand, there has been a great deal of work devoted to dopant diffusion behavior in silicon under the influence of

mechanical stress [2.15]-[2.19]. Cowern, et al. [2.15] proposed a strain-induced dopant diffusivity model of boron diffusion in SiGe. S. T. Ahn, et al. [2.17] concluded that in the presence of high-stress nitride film, phosphorus diffusion in the silicon was retarded, whereas antimony diffusion was enhanced. Aziz [2.18] established a relationship between hydrostatic pressure and biaxial strain via thermodynamic formulation, while accommodating calculation of the activation energy shift due to strain. Based on Aziz's and Cowern's theoretical work [2.15], [2.18], Zangenberg, et al. [2.19] critically reviewed the findings over the past 10 years and further identified the strain effect on boron and phosphorus diffusion in SiGe. However, most studies in the area of mechanical stress induced dopant diffusion changes remain in fundamental research, i.e., at the silicon material level, and have not yet been extended to semiconductor device characterization and modeling.

It is well recognized that the key MOSFET parameters, such as threshold voltage, drain induced barrier lowering, body factor, and subthreshold swing, are all strongly dependent on dopant distribution details. Thus, it is crucial to examine stress-dependent dopant diffusion for scaled MOSFETs under mechanical stress.

In this chapter, a stress-dependent diffusion model and incorporate it into a two-dimensional process simulation environment to assess the doping distribution effect in scaled MOSFETs is presented. The proposed model is corroborated by extensive experimental data in a sub-100nm CMOS technology.

# 2.2 Stress-dependent Diffusion Model and Modeling Methodology

#### 2.2.1 Model Description

The dopant diffusion change due to mechanical stress has been derived from point defect (interstitials and vacancies) changes [2.18]. Mechanical strain influences the point defect formation and migration, while the microscopic volume change and the pressure both contribute to the Gibb's free energy change. Thus, the dopant diffusivity ratio with and without strain can be expressed in an Arrhenius form; and the strain-induced point defect energy change can be translated to the dopant diffusivity change. For example, in the case of a compressively strained SiGe layer where Cowern studied boron diffusion [2.15], the stress condition is regarded as biaxial and the dopant diffusion dependence follows the Arrhenius form

$$D_S = D_A \exp\left[-\frac{sQ'}{kT}\right] \tag{2.1}$$

where  $D_S$  is the dopant diffusivity under strain,  $D_A$  is the dopant diffusivity without strain, s is the biaxial strain in the plane of the SiGe layer, and Q' is the activation energy per strain. The concept of this equation is consistent with experimental data [2.15], [2.18] and theoretical calculations  $^{12}$  showing a linear deffect of the mechanical strain to dopant diffusivity ratios on a log scale. Recently, Diebel [2.20] studied stress-dependent point defect equilibrium concentration and diffusion by means of *ab initio* calculations.

Analogous to equation (2.1), a stress dependent dopant diffusion model for dopant diffusion under STI mechanical stress, named  $\underline{V}$  olume-change-ratio  $\underline{I}$ nduced  $\underline{D}$  iffusion  $\underline{A}$  ctivation  $\underline{E}$  nergy  $\underline{S}$  hift  $\underline{M}$  odel (VIDAESM) is developed. The volume change ratio,  $V_{ct}$ , is a function of position due to non-uniform stress distributions. In this study, the MOSFET width is large enough to allow the three-dimensional stress effect to be reduced to the two-dimensional one. The activation energy involved is the product of a dopant dependent coefficient and volume change ratio, meaning that Eq. (2.1) can be re-written in the case of dopant diffusion under STI mechanical stress

$$D_S(T, x, y) = D_A(T) \exp\left[-\frac{\Delta E_S V_{cr}(T, x, y)}{kT}\right]$$

(2.2)

where  $D_S$  is the dopant diffusivity under strain,  $D_A$  is the dopant diffusivity without strain,  $V_{cr}$  is the volume change ratio due to stress,  $\Delta E_S$  is the activation energy per volume change ratio depending on the dopant species, and T is the temperature. When the strain is small, the volume change ratio can be expressed as

$$V_{cr}(T, x, y) \cong \varepsilon_{t}(T, x, y) \equiv \varepsilon_{xx}(T, x, y) + \varepsilon_{yy}(T, x, y) + \varepsilon_{zz}$$

(2.3)

where  $\varepsilon_{xx}$  is the strain along the channel length direction,  $\varepsilon_{yy}$  is the strain in the direction perpendicular to the silicon surface,  $\varepsilon_{zz}$  is the strain along the channel width direction, and  $\varepsilon_t$  is the strain summation of  $\varepsilon_{xx}$ ,  $\varepsilon_{yy}$ , and  $\varepsilon_{zz}$ . Note that  $\varepsilon_{zz}$  is zero in the two-dimensional simulation due to wide structures adopted. Therefore, Eq. (2.2)

becomes

$$D_{S}(T, x, y) = D_{A}(T) \exp \left[ -\frac{\Delta E_{S} \varepsilon_{t}(T, x, y)}{kT} \right]$$

(2.4)

A two-dimensional numerical process simulator, TSUPREM4, is chosen to perform the process simulation. TSUPREM4 is capable of simulating intrinsic dopant diffusion, three-stream dopant-point defect pairing diffusion, oxidation enhanced diffusion effect, dopant clustering effect, and dislocation loop effect. For assessment of mechanical stress, the simulator also simultaneously solves force balance equations while taking into account thermal expansion, intrinsic stress, geometry re-arrangement after etch and deposition processes, and the thermal oxidation process [2.21]. The stress-dependent diffusion model, VIDAESM, has been incorporated into the simulator through the user-specified equation interface to adaptively calculate stress-dopant diffusivity during the process simulation.

#### 2.2.2 Modeling Methodology

To model stress-dependent dopant diffusion for various stress levels, a series of MOSFETs with various active area sizes are designed and fabricated. Fig. 2.1 schematically shows the cross section view of a test device along the channel direction. The mechanical stress effect was explored here with active area size,  $X_{active}$ , and gate length  $L_g$ , both used as the main structural parameters.

The flow chart of the modeling procedure is shown in Fig. 2.2. Firstly, the

one-dimensional dopant profiles were processed using blanket control wafers, which covered the range of the process conditions of the device wafers. The results were then taken as stress-free dopant profiles and used to calibrate the dopant diffusion parameters without stress-dependent models.

Secondly, two-dimensional MOSFET structures were simulated using the mechanical stress model. Calibrated diffusion parameters were employed to simulate a large X<sub>active</sub> MOSFET, where the stress level is low. All front-end major process steps from the STI to the source/drain anneal were considered. The corresponding simulation geometries were calibrated using TEM cross-sectional images. Some fine-tunings of two-dimensional dopant profile parameters, such as implant lateral straggles and segregation factors, are needed to fit the silicon device I-V characteristics. Fig. 2.3 shows the calibration result of a short channel nMOSFET I-V with a large X<sub>active</sub>.

Next, with the stress distribution known, the stress-dependent diffusion models were introduced to simulate MOSFETs with varying X<sub>active</sub> values. After implementing the stress-dependent diffusion model, process simulation results were used as device simulation inputs. MEDICI was chosen as the numerical device simulator. The device modeling parameters, such as carrier mobility, work function, and silicon/oxide interface charges were calibrated to fit the I-V of large X<sub>active</sub> MOSFETs. Then, device simulations with various X<sub>active</sub> values were performed and compared with silicon device data. The above procedure was iterated from process to device cycle until the current-voltage data was all satisfactorily reproduced in all

cases. The  $\Delta E_S$  values from the previous work [2.15] were employed as the initial guess values. It is worth noting that the numerical convergence and simulation speed were not greatly influenced after implementing VIDAESM. The simulation time incorporating VIDAESM increases by about 7% compared to that without VIDAESM.

#### 2.2.3 Experiment on MOSFET Threshold Voltages and Modeling Results

The silicon wafers were fabricated using novel CMOS processes. The control wafers for one-dimensional SIMS analysis were processed using the same thermal steps as device wafers. Fig. 2.4 displays SIMS results for both n and pMOSFET. The implant conditions were BF<sub>2</sub> 2keV 1×10<sup>15</sup>cm<sup>-3</sup> and As 2keV 1×10<sup>15</sup>cm<sup>-3</sup> for ultra shallow junction calibration and the junction depths are around 260 angstroms for both devices by taking the substrate doping as 2×10<sup>18</sup>cm<sup>-3</sup>. The calibrated simulation profile is also plotted in Fig. 2.4. The calibration procedure included the fine-tuning of implant damage, dopant-point defect pairing diffusion, silicon-oxide dopant segregation, oxidation enhanced diffusion models, dopant clustering models, dopant-defect clustering models, and intrinsic diffusion models.

The stress simulation involved the main process steps, which are STI formation, gate oxidations, and poly-gate formation in sequence. Viscoelastic oxidation model was used to simulate the stress dependent oxide growth. The Young's moduli used were  $1.87 \times 10^{12} \mathrm{dyne/cm^2}$  for the silicon and  $6.6 \times 10^{11} \mathrm{dyne/cm^2}$  for the oxide layers. The intrinsic stress used is  $-1.5 \times 10^9 \mathrm{dyne/cm^2}$  for the STI oxide and  $3.3 \times 10^8 \mathrm{dyne/cm^2}$

for gate spacer oxide. The other parameters follow the default values in the TSUPREM4 manual [2.21]. The stress distribution results for different  $X_{active}$  values are given in Fig. 2.5. It can be seen that the polarity of the strain  $\varepsilon_{xx}$  in the lateral direction is negative, meaning that the MOSFET core area experiences a compressive stress. On the other hand, strain  $\varepsilon_{yy}$  in the vertical direction is tensile with a magnitude much smaller than  $\varepsilon_{xx}$ . In particular, Fig. 2.5(b) reveals that  $\varepsilon_{xx}$  drastically increases in magnitude with decreasing  $X_{active}$  values. Three reference points **A**, **B**, and **C** are chosen to inspect the value of the strain. **A** is at the center of the gate, **B** is 75nm away from the gate center and **C** is 150nm from the gate center. The depth of these points is 20nm from the silicon surface. Fig. 2.6 highlights the magnitude of the strain versus the  $X_{\text{active}}$  value at points **A**, **B**, and **C** in Fig. 2.5. The negative polarity of the strain means that the general strain conditions in the active area are compressive, and the magnitude increases rapidly as value of X<sub>active</sub> decreases. The compressive stress mainly comes from lower thermal expansion rate of the STI oxide compared to silicon, and the thermal gate oxidation induced volume expansion at the STI edge. As X<sub>active</sub> decreases, the STI approaches the MOSFET core region and increases the magnitude of compressive stress. The strain at rapid thermal peak temperature remains compressive and the magnitude is about 0.15% at the MOSFET core region for the minimum  $X_{active}$  case.

The MOSFET channel width in the silicon experiment was fixed at 10µm, large enough to ensure that the stress along the channel width direction is negligible. Simulations were conducted to evaluate the mechanical stress along the channel

width direction. The results showed that the average strain level for channel width W=10 $\mu$ m is around -0.02 %, which is at least two order of magnitude lower than the peak strain level used in this study. The MOSFET design set consisted of  $X_{active}$  values from 0.6 $\mu$ m to 10 $\mu$ m and  $L_g$  from 65nm to 0.42 $\mu$ m. It has been recognized that boron and phosphorus diffusion are retarded by compressive strain [2.15], [2.19], [2.22]. The stress simulation results show that the MOSFET channel stress and strain magnitudes for  $X_{active}$ =10 $\mu$ m are around -1×10 $^8$  dyne/cm $^2$  and -0.04%, respectively. As the  $X_{active}$  value shrinks to 0.6 $\mu$ m, the corresponding stress and strain magnitudes become around -5×10 $^9$  dyne/cm $^2$  and -0.4%, respectively. The compressive strain level in the channel region is quite close to the strain produced by 10% germanium in silicon, which falls within the range of Cowern's and Zangenberg's studies [2.15], [2.19].

In the present work, the impurities introduced to form nMOSFET are boron, indium, arsenic and phosphorus, while pMOSFET employed boron and arsenic. Boron, arsenic and phosphorus were all retarded by STI stress as encountered in fitting the silicon MOSFET I-V data. Indium was not considered as a fitting variable because it was observed to be almost immobile during the thermal process, meaning that dopant profile change due to mechanical stress would hardly be observed. As will be mentioned later, the nMOSFETs threshold voltage was observed to increase as the X<sub>active</sub> value decreases. The subthreshold I-V with a low drain bias is strongly dependent on the accurate doping profile of the MOSFET shallow core region, which is mainly related to arsenic source/drain extension doping and boron halo doping.

In high drain bias cases, the subthreshold I-V depends significantly on the deeper part of the MOSFET doping profile, which is related to phosphorus source/drain, indium halo, and boron halo tail doping profiles. As the gate length varies, the extent of the superposition of tilt-implanted halo doping varies accordingly. Moreover, as the substrate bias increases in magnitude, the depletion region further extends into the substrate from the source, channel and drain regions, considerably influencing subthreshold I-V characteristics. Thus, biasing the MOSFET substrate can serve as a means of verification for the stress-dependent diffusion model. Fig. 2.7 shows the depletion region boundaries of a 65nm nMOSFET for low and high drain voltages.

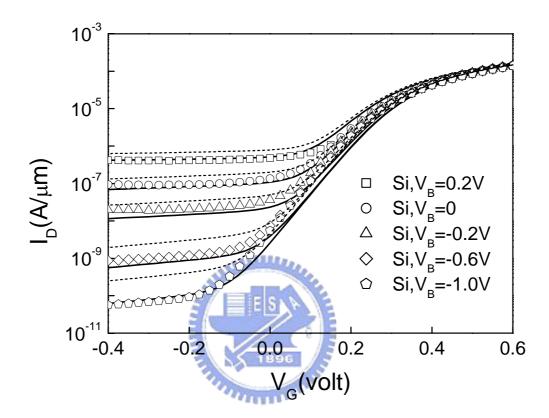

After numerical iterations were completed, the effects of gate lengths, gate voltages, drain voltages, and substrate biases simultaneously matched with the nMOSFET subthreshold I-V data. This is sufficient to claim that the resulting dopant distributions for the whole device core region are correct. To assess the creditability of this model, device I-V simulations with and without VIDAESM were performed and compared. Fig. 2.8 shows the detailed I-V comparison for a small Xactive MOSFET with and without VIDAESM. In the absence of VIDAESM, the simulation fails to correctly describe the I-V dependency on Xactive. Fig. 2.9 displays a series of comparisons with measured gate voltage at different drain current levels for different combinations of gate lengths, active area sizes, drain voltages, and substrate biases. Remarkably, the extracted diffusion parameter set is able to reproduce all the silicon data well. The broad range of gate lengths, active areas,

drain voltages and substrate biases employed in this experiment confirm that the VIDAESM model is indeed suited for modeling the mechanical stress effect on scaled MOSFETs. To further ensure the extracted parameter set also valid for pMOSEFTs, threshold voltage dependence on  $X_{active}$  is simulated and compared with silicon data for both nMOSFETs and pMOSFETs. Fig. 2.10 shows the final results. The threshold voltage is defined by using constant drain current method. The strain effect is estimated to have less 10% drain current variations for  $L_g$ =65nm MOSFETs, which causes less then 4mV variations. It can be seen that the nMOSFET threshold voltage increases with decreasing  $X_{active}$  values while pMOSFET threshold voltage is relatively insensitive to  $X_{active}$ . The trends for both nMOSFETs and pMOSFETs are adequately described by the extracted parameter set.

Finally, Table I lists the extracted  $\Delta E_S$  values for all impurities involved. The  $\Delta E_S$  for phosphorus is -30eV per volume shift ratio and is largest among the impurities. The  $\Delta E_S$  for arsenic is -14eV per volume shift ratio, whereas the  $\Delta E_S$  for boron is -7eV. These coefficients confirm diffusion retardation by the compressive stress in pure silicon, excluding the Ge chemical effect in strained SiGe experiments. Fig. 2.11 illustrates the two-dimensional contour of the nMOSFET net doping concentration for a gate length of 65nm. As shown in the figure, for  $X_{active}$ =10 $\mu$ m, the dopant contours with and without the stress-dependent model are comparable, while the source/drain junction for  $X_{active}$ =0.6 $\mu$ m is significantly shallower and effective gate length is longer in the MOSFET core region when the stress-dependent diffusion model is introduced. To more clearly visualize the effect of the

stress-dependent model, one can inspect the dopant profile along specific cut-lines. Fig. 2.12 and 2.13 displays corresponding vertical and lateral doping profiles for a 65nm gate length nMOSFET with  $X_{active}$  as a parameter. As can be seen, significant dopant diffusion retardation prevails at small  $X_{active}$  values and this explains an increase in threshold voltage as the  $X_{active}$  decreases.

# 2.3 Experiment on MOSFET Subthreshold Leakage with Stress-Dependent Transient-Enhanced-Diffusion Effect Included

This work has been conducted to corroborate the validity of the STI mechanical stress-dependent diffusion model mentioned in section 2.2 using a MOSFET device with an underlying lightly doped well, which exhibits a significant mechanical stress effect on the subthreshold I-V characteristics. The stress-dependent point defect equilibrium concentration and diffusion, which dominates the transient enhanced diffusion (TED), has also been taken into account.

The results of Diebel's study [2.20] also show a linear dependence of both point defect equilibrium concentration and diffusivity in a log scale on the mechanical strain. Thus, it is reasonable to express the point defect equilibrium concentration and diffusion in an Arrhenius form:

$$C_S^*(T, x, y) = C_A^*(T) \exp\left[-\frac{\Delta E_C \varepsilon_t(T, x, y)}{kT}\right]$$

(2.5)

where  $C_s^*$  is the point defect equilibrium concentration under strain. To investigate the transient enhanced diffusion, only strain-dependent interstitial diffusion is needed.  $\Delta E_C$  for the vacancy extracted from calculation results [2.20] is +7.9eV/unit strain. Extracted  $\Delta E_C$  and  $\Delta E_S$  (in Eq. (2.5)) values for the interstitial are -7.0 and +0.99eV/unit strain, respectively. Furthermore, interstitial diffusivity and equilibrium concentration product,  $D_I C_I^*$ , is reduced under the compressive strain conditions. Two-dimensional process/device simulators, TSUPREM4 and MEDICI, were employed. The stress-dependent diffusion models were incorporated into TSUPREM4 through its user-specified equation interface.

A series of n-channel MOSFETs were fabricated using state-of-the-art process technology. Test structures had three active area length ( $X_{active}$  in Fig. 2.1) values: 0.68 $\mu$ m, 1.46 $\mu$ m, and 20.2 $\mu$ m.  $X_{active}$  is the design parameter to modulate mechanical stress. The minimum  $X_{active}$  dimension of 0.68 $\mu$ m takes the presence of one contact window area in the source/drain into account. The gate length and width were 0.17 $\mu$ m and 10 $\mu$ m, respectively. The retrograde well implantations are omitted so as to enhance the sensitivity of the subthreshold characteristics to STI mechanical stress, offering the opportunity to verify the validity of the above mentioned diffusion model. The measured subthreshold I-V characteristics at  $V_D$  = 1.2V are depicted in Fig. 2.13, with the substrate bias as a parameter. Previous work [2.23] revealed that the substrate bias measurement is a suitable verification index of the MOSFET doping profile because of the high sensitivity of carrier diffusion current to the dopant profile. The procedure for obtaining  $\Delta E_S$  values for various impurities began

by calibrating the one-dimensional dopant profiles in blanket control wafers, using processes that covered the range of device wafer process conditions. The results were taken as stress-free dopant profiles and used to calibrate the dopant diffusion parameters without considering stress-dependent diffusion effect. Two-dimensional MOSFET structures were then simulated in conjunction with the mechanical stress model. Calibrated diffusion parameters were employed to simulate a large X<sub>active</sub> case, where the stress level is negligible. All major front-end process steps from the STI to the source/drain anneal were considered. The corresponding simulation geometries were calibrated using TEM cross-sectional images. Device simulations were performed and the device model parameters were calibrated to fit the I-V of the large X<sub>active</sub> MOSFET. Next, the process simulations based on VIDAESM for all  $X_{\text{active}}$  values were conducted with an initial set of  $\Delta E_S$  values. Then, the device simulations with smaller X<sub>active</sub> values were performed and compared with the I-V The above procedure was iterated until a satisfactory reproduction of subthreshold I-V data was achieved in all cases.

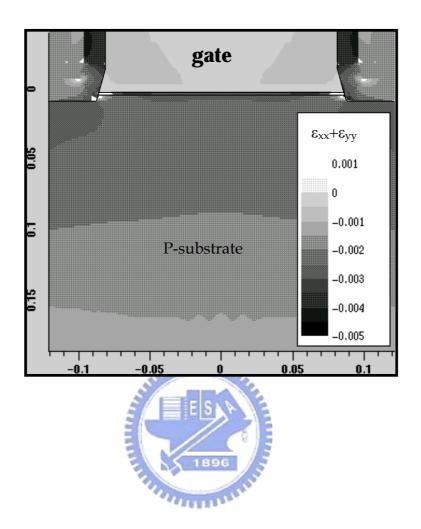

The simulated strain distribution results for  $X_{active} = 0.68\mu m$  are given in Fig. 2.14. It can be seen that the magnitude of the total strain, or volume change ratio,  $(\epsilon_{xx}+\epsilon_{yy})$ , is negative in the MOSFET core area, meaning that the device experiences compressive stresses during the process. In addition, the  $(\epsilon_{xx}+\epsilon_{yy})$  of  $X_{active} = 0.68$  m was found to be much larger in magnitude than  $X_{active} = 20.2\mu m$ . The compressive stress stems mainly from the lower thermal expansion rate of the STI oxide when compared to silicon, as well as the thermal gate oxidation induced

volume expansion at the STI edge. Thus, as  $X_{active}$  decreases, the STI approaching the MOSFET core region increases the magnitude of the compressive stress. The extracted the  $\Delta E_S$  for phosphorus, arsenic and boron in the last section are -30, -14, and -7 eV/unit strain, respectively. The negative sign of  $\Delta E_S$  denotes diffusion retardation caused by the compressive stress in pure silicon for these impurities, and is in agreement with the literature [2.15],[2.19],[2.22]for boron and phosphorus. Note that, so far, no conclusive argument has been reached regarding the arsenic diffusion behavior under a general non-uniformly compressive stress in pure silicon.

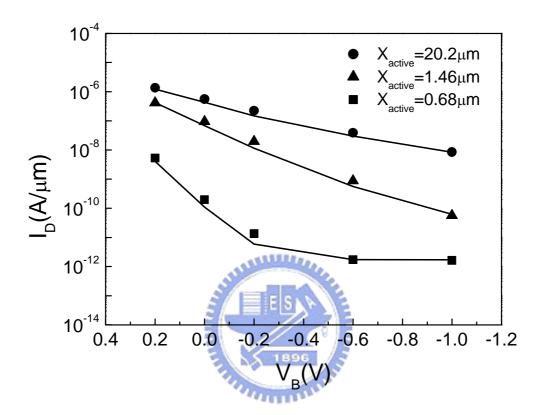

In the MOSFET structure used in this section, source and drain phosphorus diffusion is much more sensitive to the mechanical stress than boron and arsenic because of the absence of the high concentration retrograde P-type doping well. The experimental silicon and simulation results are shown in Fig. 2.13 and Fig. 2.15. In the absence of the VIDAESM, the simulated leakage current (that is, the flat region in Fig. 2.14) was found to be much higher for MOSFETs with smaller  $X_{active}$  values as illustrated in dashed lines in Fig. 2.13. The  $I_D$  value for  $X_{active}$ = 1.46  $\mu$ m at  $V_B$ = –1 V and  $V_G$ = –0.4 V is 2.5×10<sup>-10</sup>A/ $\mu$ m without using VIDAESM, which is much larger than the result obtained using VIDAESM (6.3×10<sup>-11</sup>A/ $\mu$ m). The corresponding silicon experimental data is 5.6 ×10<sup>-11</sup>A/ $\mu$ m. The simulations that incorporated VIDAESM revealed that the punchthrough between the deeper part of the phosphorus source and drain is responsible for the leakage current. This means that the dopant diffusion becomes less as  $X_{active}$  is decreased, and is consistent with the results indicated in Fig. 2.15: a decrease in  $X_{active}$  produces a substantially large reduction in leakage current.

In Fig 2.15, the gate-edge tunneling current of  $X_{active} = 0.68 \mu m$  MOSFET prevails in the background current, regardless of high negative substrate biases.

To investigate the impact of the mechanical stress on transient enhanced diffusion, the stress-dependent point defect diffusion and equilibrium concentration models described in Eqs. (2.4) and (2.5) are applied to the numerical simulator. The simulation results show slightly higher subthreshold leakage current, which implies that the dopant diffusion is the stronger. The  $I_D$  value for  $X_{active}$ = 1.46  $\mu$ m at  $V_B$ = -1  $V_A$  and  $V_A$ = -0.4  $V_A$  increase from  $6.3\times10^{-10}$ A/ $\mu$ m to  $7.1\times10^{-10}$ A/ $\mu$ m. The explanation for this phenomenon is that the interstitial equilibrium concentration  $C_I$ \* decreases under the compressive stress and therefore the interstitial supersaturation factor,  $C_I$  /  $C_I$ \*, increases after impurity ion implantation, which results in the TED enhancement. The effect is not significant because high ramp rate rapid thermal anneals were applied after ion implantations. To further fit the experimental data after taking the stress-dependent TED effect into account, the final value  $\Delta E_S$  of phosphorus is fine tuned from -30 to -33eV/unit strain. Fig 2.15 depicts the corresponding results of experimental data fitting.

# 2.4 Anisotropic Diffusion Derivation for Uniaxial Strain Cases

In this section, a new set of uniaxial-strain-dependent-anisotropic-diffusion equations is derived based on Aziz's theory. The equations will be implemented to the TCAD tool, TSUPREM4, and the simulation work was done to verify the silicon experiment with STI stressed PMOSFETs.

The thermodynamics framework constructed by Aziz (see Ref.[2.25], which is more recent and more thorough than the earlier works cited above), the activation volume ( $\tilde{V}$ ) and the anisotropy of the migration volume ( $\tilde{V}_{||}^m - \tilde{V}_{\perp}^m$ ) exist in nature. The combination of the activation energy, the activation volume, and the anisotropy of the migration volume is remarkable, as demonstrated in a physical model [2.18], [2.25]-[2.27] dedicated to both the hydrostatic pressure experiment and the in-plane biaxial stress experiment:

$$\tilde{V} + \frac{3}{2} \frac{Q'_{33-biax}}{Y_{biax}} = \pm \Omega + (\tilde{V}_{||}^{m} - \tilde{V}_{\perp}^{m})$$

(2.6)

$$\tilde{V} + \frac{3}{2} \frac{Q'_{11-biax}}{Y_{biax}} = \pm \Omega - \frac{1}{2} (\tilde{V}_{||}^{m} - \tilde{V}_{\perp}^{m})$$

(2.7)

where  $Q'_{33-biax}$  is the biaxial strain induced activation energy in the direction normal to the silicon surface,  $Y_{biax}$  is the biaxial modulus,  $\Omega$  is the lattice site volume, and  $Q'_{11-biax}$  is the biaxial strain induced activation energy in the direction parallel to the surface.

On the other hand, in the case of uniaxial stress as encountered while fabricating the MOSFET, without the use of a relaxed SiGe buffer layer, the stress is created through the trench isolation, silicide, or cap layers in a manufacturing process. Therefore, a straightforward extension to the uniaxial strain counterpart is essential. The uniaxial model is derived and its linkage to the case of biaxial strain, Eqs. (2.6) and (2.7), is established. When applied to boron, a process-device coupled simulation is performed on a p-type MOSFET undergoing uniaxial stressing during

the manufacturing process, followed by a systematic assessment of the fundamental material parameters.

According to Aziz [2.18], [2.25], in the case of equilibrium or a quickly equilibrated point defect, the effect of stress on the dopant diffusivity in the direction normal to a (001) surface can be written as:

$$\frac{D_{33}(\sigma)}{D_{33}(0)} = \exp(\frac{\sigma \bullet [V^f + \tilde{V}_{33}^m]}{k_B T})$$

(2.8)

Here the product of the stress tensor  $\sigma$  and the formation strain tensor  $V^f$  is the work done against the stress field in defect formation; the product of the stress tensor  $\sigma$  and the migration strain tensor  $\tilde{V}_{33}^m$  is the work required for the successful transition in the migration path;  $k_B$  is Boltzmann's constant; and T is the diffusion temperature. The tensor  $V^f$  involves the creation or annihilation of a lattice site, followed by a relaxation process [2.18], [2.25]:

wed by a relaxation process [2.18], [2.25]:

$$V^{f} = \pm \Omega \begin{bmatrix} 0 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 1 & 0 \end{bmatrix} + \frac{V^{r}}{3} \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 1 & 0 \end{bmatrix}$$

(2.9)

The + sign denotes vacancy formation and the - sign represents interstitial formation. The relaxation volume propagates elastically to all surfaces, resulting in a change in the volume of the crystal by an amount  $V^r$ .  $\tilde{V}_{33}^m$  is expected to have the form [2.18], [2.25]:

$$\widetilde{V}_{33}^{m} = \begin{bmatrix} \widetilde{V}_{\perp}^{m} & & \\ & \widetilde{V}_{\perp}^{m} & \\ & & \widetilde{V}_{||}^{m} \end{bmatrix}$$

(2.10)

In Eq. (5),  $\tilde{V}_{\perp}^m$  and  $\tilde{V}_{||}^m$ , respectively, reflect the dimension changes perpendicular and parallel to the direction of the net transport when the point defect reaches its saddle point [2.18], [2.25]. Aziz further defined the activation volume as the sum of the three diagonal elements of the formation strain tensor and the migration strain tensor, as expressed by:

$$\widetilde{V} = \pm \Omega + V^{\mathrm{r}} + 2\widetilde{V}_{\perp}^{m} + \widetilde{V}_{\perp}^{m}. \tag{2.11}$$

It is well recognized [2.20] that when applying a uniaxial stress in a certain direction parallel to the silicon surface, the solid will modify its shape in order to minimize the energy of the system. In other words, the solid will deform in such a way that each surface perpendicular to the applied stress direction becomes stress free. The underlying stress tensor therefore is

$$\sigma = \sigma_{uniax} \begin{bmatrix} 1 \\ 0 \\ 0 \end{bmatrix}. \tag{2.12}$$

On the basis of Hooke's law,  $\sigma_{uniax}$  in the linear elastic regime can be related to the uniaxial strain  $\varepsilon_{uniax}$  induced in the same direction:  $\sigma_{uniax} = Y_{uniax}\varepsilon_{uniax}$ , where the uniaxial modulus  $Y_{uniax} = (C_{11} - 2vC_{12})$  with the Poisson's ratio  $v = C_{12}/(C_{11} + C_{12})$ .  $C_{11}$  and  $C_{12}$  are the elasticity constants. Analogous to previous work [2.15], the uniaxial strain induced activation energy in the direction normal to the (001) surface,  $Q_{33-uniax}$ , can be linked to the underlying diffusivity:

$$\frac{D_{33}(\varepsilon_{uniax})}{D_{33}(0)} = \exp\left(-\frac{Q_{33-uniax}^{\prime}\varepsilon_{uniax}}{k_BT}\right) \tag{2.13}$$

By combining Eqs. (2.9), (2.10), and (2.12) and equalizing (2.8) to (2.13), one

obtains  $Q_{33-uniax}$  /  $Y_{uniax} = -V^{4}/3 - \tilde{V}_{\perp}^{m}$ . Again, by incorporating Eq. (2.11), the following expression is produced:

$$\widetilde{V} + 3 \frac{Q_{33-uniax}}{Y_{uniax}} = \pm \Omega + (\widetilde{V}_{||}^m - \widetilde{V}_{\perp}^m)$$

(2.14)

It is then a straightforward task to derive the uniaxial strain induced activation energy  $Q_{11-uniax}^{'}$  in the applied stress direction:  $Q_{11-uniax}^{'}$  /  $Y_{uniax}$  =  $-V^{t}/3$  -  $\tilde{V}_{||}^{m}$ . Consequently, a similar model is achieved:

$$\widetilde{V} + 3 \frac{Q_{11-uniax}^{'}}{Y_{uniax}} = \pm \Omega - 2(\widetilde{V}_{||}^{m} - \widetilde{V}_{\perp}^{m})$$

(2.15)

Obviously, the uniaxial strain version is closely related to its biaxial counterpart: by comparing Eq. (2.6) and (2.14),  $2Q_{33-uniax}^{'} = (Y_{uniax}/Y_{biax})Q_{33-biax}^{'}$  is obtained. Another equation expressing  $Q_{11-uniax}^{'}$  as a function of  $Q_{11-biax}^{'}$  and  $Q_{33-biax}^{'}$  can then be readily derived.

To produce the experimental parameters in terms of the anisotropy of the uniaxial strain induced activation energy, a uniaxial stress experiment was carried out in terms of a p-channel MOSFET in a state-of-the-art manufacturing process [2.24]. The channel length was maintained at 65 nm while changing the spacing in the channel length direction between the two trench isolation sidewalls. The structure schematic is detailed Fig. 2.1. Under such a situation, the channel zone encounters a compressive stress from the nearby trench isolation regions. The devices used are quite wide (10  $\mu$ m), meaning that the stress in the channel width direction can be neglected. The (001) silicon surface is supposed to be stress free. This