# 國立交通大學

# 電子工程學系 電子研究所

# 博士論文

先進互補式金氧半電晶體及氮化矽快閃式記憶元件之可 靠度分析和蒙地卡羅模擬 1896

Reliability and Monte Carlo Analysis in Advanced CMOS and SONOS

Flash Memory

研究生:唐俊榮

指導教授:汪大暉 教授

中華民國九十九年一月

# 先進互補式金氧半電晶體及氮化矽快閃式記憶元件之可 靠度分析和蒙地卡羅模擬

# Reliability and Monte Carlo Analysis in Advanced CMOS and SONOS Flash Memory

研究生:唐俊榮

Student : Chun-Jung Tang

指導教授:汪大暉

Advisor : Tahui Wang

Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering National Chiao Tung University in partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in

**Electronics Engineering**

January 2010 Hsinchu, Taiwan, Republic of China

## 先進互補式金氧半電晶體及氮化矽快閃式記憶元件之可靠度分析和 蒙地卡羅模擬

學生:唐俊榮

#### 指導教授:汪大暉博士

### 國立交通大學 電子工程學系 電子研究所

#### 摘 要

本篇論文主要著重在蒙地卡羅模擬(Monte Carlo simulation)於先進互補式金 氧半電晶體(advanced CMOS)及氮化矽快閃式記憶元件(SONOS flash memory)之 應用。此外,高介電閘極氧化層(high-k)之可靠性議題,如電壓溫度引致不穩定(BTI) 之研究,亦有所探討。

第一章首先描述本論文中蒙地卡羅模擬之三項應用研究成果。前兩項探討 NOR 型氮化矽記憶陣列中,寫入干擾(program disturb)以及電子非平衡傳輸 (non-equilibrium transport)之物理機制。元件基本結構及寫入方法亦有清楚描述。 最後一項應用是研究對於鍺通道(Ge-channel)雙閘極(double gate)電晶體,量子效 應對電洞遷移率(hole mobility)之影響。此外,吾人於此篇論文最後,強調高介電 閘極氧化層中負電壓溫度引致不穩定之重要性。

第二章探討在潛擴散式(buried diffusion)位元線 SONOS 陣列中,當位元線寬 度變窄時所衍生之寫入干擾現象。實驗結果顯示,寫入干擾造成鄰近元件之臨界 電壓有1伏特的增加,使得寫入干擾已成為50 奈米 NOR 型 SONOS 技術開發之 主要問題之一。吾人採用多階式蒙地卡羅模擬來探討寫入干擾之物理機制。研究 結果顯示,在熱電子寫入的過程中,鄰近元件臨界電壓會漂移的原因,是由於撞 擊游離所產生之二次電子,注入至鄰近元件。此種效應對於窄位元線、淺潛擴散 接面以及高摻雜環形佈值濃度之元件,將愈益明顯。此外,吾人發現透過熱電子 寫入電壓以及元件結構之最佳化,可將減低寫入干擾。

i

第三章提出一種在潛擴散式位元線 SONOS 陣列中新的熱電子寫入方法。此 方法是利用在奈米尺度電子呈現之非平衡傳輸現象。與傳統熱電子寫入方法不 同,電子加速是在兩個相鄰元件內完成。因此,汲極至源極電壓(Vds)可降低至 2.5 伏特,以解決閘極長度微縮時所遭遇之貫穿(punch-through)問題。吾人亦利用蒙 地卡羅模擬來探討電子非平衡傳輸行為。研究結果顯示,新的熱電子寫法方式比 傳統熱電子寫入方法具有更高之寫入效率,這是因為電子經過潛擴散區域後,在 寫入單元之源極端具有殘存的能量。此外,當位元線微縮時,新的熱電子寫入方 法將更有效率。

第四章探討對於鍺通道雙閘極電晶體,量子效應對電洞遷移率之影響。低電 場之電洞遷移率是透過蒙地卡羅方法求得。模擬結果得知,對於 (100) /[110] 「矽」通道,電洞遷移率隨著通道厚度變薄而減少。此模擬結果與實驗相符合。 然而對於(100)/[100]「鍺」通道,電洞遷移率在某個通道厚度下具有最大值。此 現象乃因「次能帶內」散射與「次能帶間」散射交互作用下所產生。在(110)/[-110] 「鍺」通道方向上,亦可發現相同情形。此外,吾人發現當單軸壓縮應力施於 (100)/[110]或(110)/[-110]鍺通道上時,電洞遷移率將可進一步提昇。

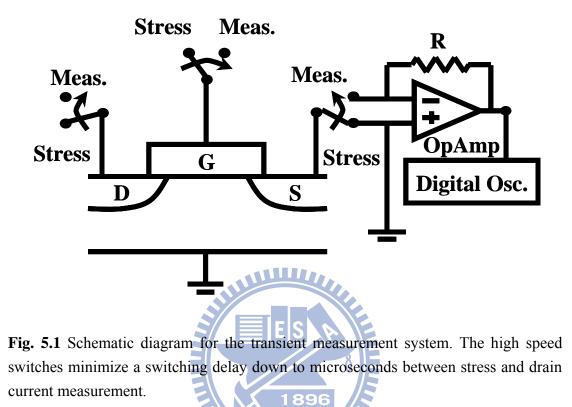

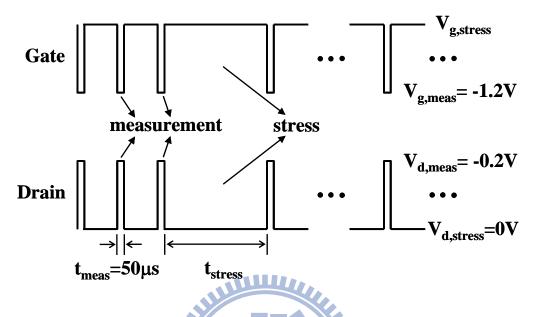

在第五章,吾人利用電腦自動化量測電路系統,研究 HfSiON pMOSFETs 中 負電壓溫度所引致之不穩定性。實驗結果顯示,在某特定加壓條件下,負電壓溫 度加壓所引致之汲極電流,將從增益模式逐漸演變成退化模式,隨著加壓時間或 加壓電壓之呈現奇特的「轉彎現象」(turn around)。此外,對於 pMOSFET 元件 加壓後,汲極電流呈現退化行為。然而,對於 nMOSFET 元件加壓後,汲極電流 呈現恢復行為。吾人提出一「雙極電荷捕捉模型」成功解釋奇特的「轉彎現象」, 並以單電荷散逸量測、電荷幫浦法以及載子分離量測,驗證所提出之物理模型。

最後於第六章,吾人將對本論文做個總結。

關鍵字:蒙地卡羅模擬,先進互補式金氧半電晶體,氮化矽快閃式記憶元件,潛 擴散式,熱電子寫入,寫入干擾,低汲極至源極電壓,貫穿,雙閘極, 鍺通道,電洞遷移率,單軸壓縮應力,高介電閘極氧化層,負電壓溫度 引致不穩定,雙極電荷捕捉模型,單電荷散逸,電荷幫浦量測

ii

# Reliability and Monte Carlo Analysis in Advanced CMOS and SONOS Flash Memory

Student : Chun-Jung Tang

Advisor : Dr. Tahui Wang

Department of Electronics Engineering & Institute of Electronics National Chiao Tung University

# ABSTRACT

This thesis will focus on the Monte Caro simulation and its applications to advanced CMOS and SONOS flash memory. The reliability issue, negative bias temperature instability (NBTI) in advanced gate dielectric (high-k), is studied as well.

In Chapter 1, three applications of Monte Carlo simulation are firstly addressed. The first two are the investigations of program disturb and electron non-equilibrium transport in a NOR-type SONOS array. The device configuration and program methods of the cell are described. The third application is the study of quantum confinement effects on hole mobility in Ge-channel double gate pMOSFETs. The role of NBTI in high-k gate dielectric is also emphasized.

In Chapter 2, the new program disturb in a buried diffusion bit-line SONOS array is investigated. Our characterization shows that the program disturb is 1V, which has been a major issue for the 50nm technology node and beyond. We utilize a multi-step Monte Carlo simulation to explore the disturb mechanism. We find that the threshold voltage shift of a disturbed cell is attributed to impact ionization-generated secondary electrons in a neighboring cell when it is in programming. The disturb is more serious for the small bit-line width, shallow bit-line junction, and high pocket implant dosage. In addition, we find that optimization of program bias conditions and device structure can alleviate the program disturb.

Proposed in Chapter 3 is a novel hot-electron programming method by means of electron non-equilibrium transport in a buried-diffusion bit-line SONOS memory array. In this method, electron acceleration is achieved in two adjacent cells rather than in a single cell. In this way, the drain-to-source voltage ( $V_{ds}$ ) in each cell can be reduced to 2.5V, which is immune to channel punch-through. The Monte Carlo simulation similar to that described in Chapter 2 is employed to explore the non-equilibrium transport behavior. Our study shows that the higher programming efficiency in this method than in the conventional method is attributed to the residual energy at the source of the program cell. Furthermore, this method is more effective as bit-line width reduces.

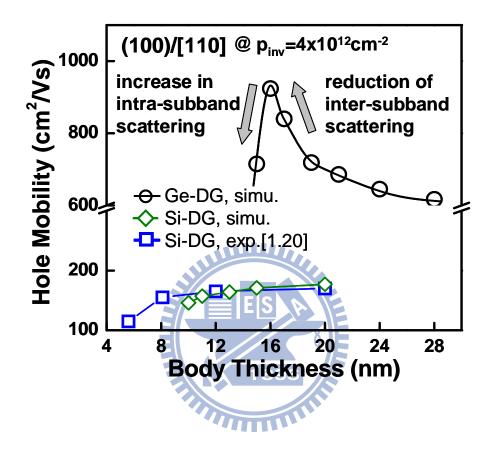

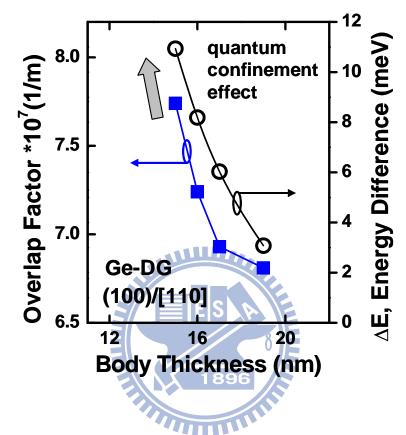

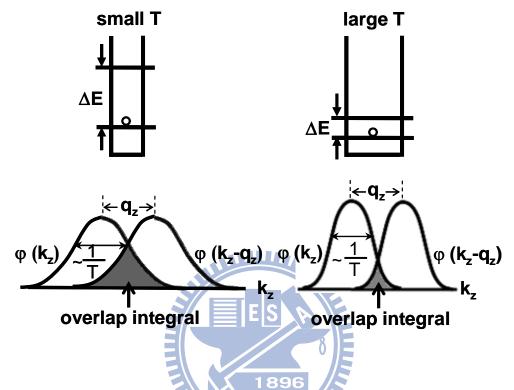

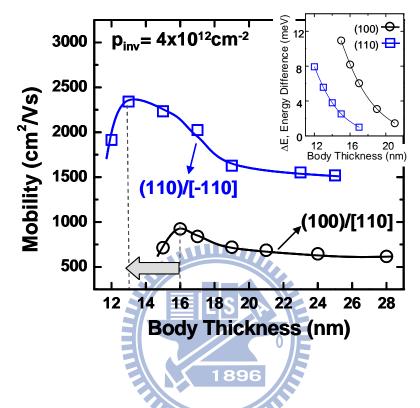

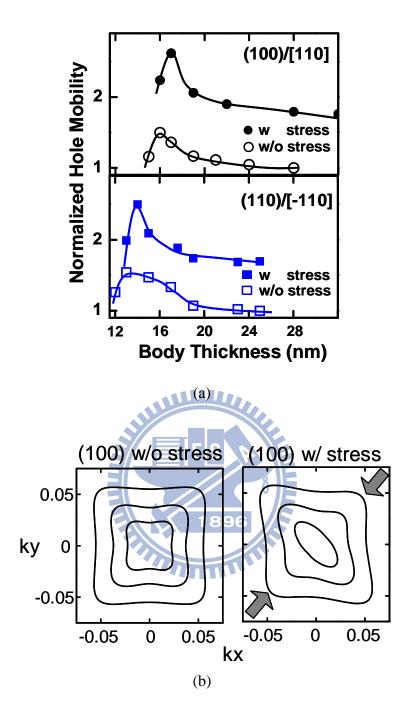

The quantum confinement effects on hole mobility in Ge-channel double gate MOSFETs are studied in Chapter 4. The low-field hole mobility is calculated by a Monte Carlo simulation. Our simulation result shows that the hole mobility in a (100)/[110] silicon well decreases with a decreasing well thickness, which is in agreement with the experimental result. The hole mobility in a Ge-channel pMOSFET, however, exhibits a peak in a sub-20 nm well because of the interplay between intrasubband and intersubband scatterings. The peak mobility in (110)/[-110] channel direction can be also achieved. Moreover, we find that the hole mobility can be further improved when the uniaxial compressive stress is applied to (100)/[110] or (110)/[-110] channel direction.

The characteristic of bipolar charge trapping induced anomalous NBTI in HfSiON gate dielectric pMOSFETs is demonstrated in Chapter 5 by using a fast transient

measurement technique. Our study shows that in certain stress conditions, the NBT-induced current instability evolves from enhancement mode to degradation mode, giving rise to an anomalous turn-around characteristic with stress time and stress gate voltage. Persistent post-stress drain current degradation is found in a pMOSFET, as opposed to drain current recovery in its n-type MOSFET counterpart. A bipolar charge trapping model along with trap generation in a HfSiON gate dielectric is proposed to account for the observed phenomena. Post-stress single charge emissions from trap states in HfSiON are characterized. Charge pumping and carrier separation measurements are performed to support our model.

Conclusions are finally made in Chapter 6.

Keyword: Monte Carlo simulation, Advanced CMOS, SONOS, NOR, Buried diffusion, Hot-electron programming, Program disturb, Low  $V_{ds}$ , Punch-through, Double gate, Ge-channel, Hole mobility, Uniaxial compressive stress, High-*k*, NBTI, Bipolar charge trapping model, Single charge emission, Charge pumping technique

#### ACKNOWLEDGEMENT

I would first like to express my deep gratitude to my advisor, Prof. Tahui Wang. His insightful guidance and encouragement are indispensable to the accomplishment of this dissertation.

I also show my appreciation to all of the committee members for their invaluable comments and suggestions. Moreover, I would like to acknowledge Dr. Chih-Sheng Chang and all the members in ETD3 for their kindly support during my part-time job at TSMC.

During my study, many important people have influenced me. I would like to thank Mr. M. C. Chen, Mr. C. T. Chan, and Mr. S. H. Gu for their guidance during my initial stage of Ph.D. study. Special thanks are also given to Mr. C. C. Cheng and Mr. H. C. Ma for sharing experience. In particular, the assistance in executing routine measurements and simulations from Mr. C. W. Li, Mr. J. Y. Shiu, and Mr. J. P. Chiu is also greatly appreciated. I am also indebted to the Wang and Chung group members of Emerging Device and Technology Lab, who had made life fun.

Scholarship from the department of electronics engineering at NCTU and from ZyXEL is deeply acknowledged for easing my financial pressure. I would also appreciate the National Science Council for providing me the travel grants to present papers in international conferences.

Finally, I would present my deepest love to my parents. Their love is the most important power supporting me. This dissertation is dedicated to them.

#### 謝誌

首先,感謝指導教授汪大暉博士。沒有汪教授的教誨與鼓勵,這本論文將無法完成。

特別感謝論文口試委員在百忙之中給予寶貴的建議與指教。另外,在台灣積 體電路製造公司工讀期間,前瞻技術研發部部經理張智勝博士及所有全體同仁在 研究與工作上的大力協助,在此由衷感謝。

在求學過程中,感謝學長陳旻政博士、詹前泰博士以及古紹泓博士不吝分享 所學,讓我快速進入狀況。感謝鄭志昌先生和馬煥淇先生在實驗室一起討論。此 外,感謝李致維先生、許家源先生、以及邱榮標先生分擔實驗及模擬的工作。因 為有你們的協助,使得這本論文更加充實。同時也感謝前瞻元件與技術實驗室所 有成員,他們為我的博士班生涯增色許多。

感謝國立交通大學電子研究所及朱順一合勤科技提供獎學金,減輕我的經濟 壓力。在此向國科會(National Science Council)致上誠摯的謝意,提供經費補助, 讓我前往國際會議發表論文。

最後,我要感謝長久以來支持我的家人,他們的愛是我的重要支柱。這本論 文,獻給他們。

vii

## CONTENTS

| Chinese Abstract<br>English Abstract<br>Acknowledgement<br>Contents<br>Table Captions<br>Figure Captions<br>List of Symbols |                                                                                                                                                  | i<br>iii<br>vi<br>viii<br>x<br>xi<br>xvi |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| -                                                                                                                           |                                                                                                                                                  |                                          |

| Chapter 1                                                                                                                   | Introduction                                                                                                                                     | 1                                        |

| 1.1                                                                                                                         | Backgrounds                                                                                                                                      | 1                                        |

| 1.2                                                                                                                         | Description of the Problem                                                                                                                       | 2                                        |

| 1.3                                                                                                                         | Organization of this Dissertation                                                                                                                | 4                                        |

| Chapter 2                                                                                                                   | Characterization and Monte Carlo Analysis of Secondary<br>Electrons Induced Program Disturb in a Buried Diffusion<br>Bit-line SONOS Flash Memory | 10                                       |

| 2.1                                                                                                                         | Preface                                                                                                                                          | 10                                       |

| 2.2                                                                                                                         | Experimental                                                                                                                                     | 11                                       |

|                                                                                                                             | 2.2.1 Devices                                                                                                                                    | 11                                       |

|                                                                                                                             | 2.2.2 Program Disturb in a NOR-type SONOS Memory                                                                                                 | 12                                       |

|                                                                                                                             | 2.2.3 Mechanisms for the Program Disturb                                                                                                         | 12                                       |

| 2.3                                                                                                                         | Monte Carlo Model                                                                                                                                | 13                                       |

| 2.4                                                                                                                         | Results and Discussions                                                                                                                          | 14                                       |

|                                                                                                                             | 2.4.1 Spatial Distribution of Secondary Hot Electrons                                                                                            | 14                                       |

|                                                                                                                             | 2.4.2 Energy Distribution of Secondary Hot Electrons                                                                                             | 15                                       |

|                                                                                                                             | 2.4.3 Substrate Bias Effect                                                                                                                      | 17                                       |

|                                                                                                                             | 2.4.4 Bit-line Depth and Width Effects                                                                                                           | 17                                       |

|                                                                                                                             | 2.4.5 Pocket Implant Effect                                                                                                                      | 18                                       |

| 2.5                                                                                                                         | Summary                                                                                                                                          | 18                                       |

| Chapter 3                                                                                                                   | A Novel Hot Electron Programming Method in a Buried<br>Diffusion Bit-line SONOS Memory by Utilizing<br>Non-Equilibrium Charge Transport          | 43                                       |

| 3.1                                                                                                                         | Preface                                                                                                                                          | 43                                       |

| 3.2                                                                                                                         | A Novel Hot Electron Programming Method                                                                                                          | 44                                       |

|                                                                                                                             | 3.2.1 Programming Speed                                                                                                                          | 44                                       |

|                                                                                                                             | 3.2.2 Program Disturb                                                                                                                            | 45                                       |

|                                                                                                                             | 3.2.3 Electron Pre-acceleration Effect                                                                                                           | 45                                       |

| 3.3                                                                                                                         | Monte Carlo Analysis                                                                                                                             | 46                                       |

|                                                                                                                             | 3.3.1 Monte Carlo Model                                                                                                                          | 46                                       |

|                                                                                                                             | 3.3.2 Bit-line Width Effect                                                                                                                      | 46                                       |

| 3.4                                                                                                                         | Summary                                                                                                                                          | 47                                       |

| Chanton 1                                                                                                                   | Study of Quantum Confinament Effects on Hele Mahility in                                                                                         | 60                                       |

# Chapter 4Study of Quantum Confinement Effects on Hole Mobility in60Silicon and Germanium Double Gate MOSFETs

|                                              | Preface                                                                                                               | 60                                |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 4.2                                          | Valence Band Structure in Strained Bulk Materials                                                                     | 60                                |

| 4.3                                          | Valence Subband Structure in pMOSFETs                                                                                 | 66                                |

|                                              | 4.3.1 Schrodinger Equation with a Six-band Luttinger                                                                  | 66                                |

|                                              | Hamiltonian                                                                                                           |                                   |

|                                              | 4.3.2 Poisson Equation                                                                                                | 68                                |

|                                              | 4.3.3 Self-consistent Solution to Poisson and Schrödinger Equations                                                   | 69                                |

| 4.4                                          | Monte Carlo Model                                                                                                     | 70                                |

| 4.5                                          | Hole Mobility in silicon and germanium double-gate                                                                    | 72                                |

| 1.0                                          | MOSFETs                                                                                                               | , 2                               |

|                                              | 4.5.1 Subband Structures in (100) Si- and Ge-channels                                                                 | 72                                |

|                                              | 4.5.2 Hole Mobility in Si- and Ge-channels                                                                            | 73                                |

|                                              | 4.5.3 Substrate Orientation Effect                                                                                    | 75                                |

|                                              | 4.5.4 Uniaxial Compressive Stress Effect                                                                              | 75                                |

| 4.6                                          | Summary                                                                                                               | 76                                |

|                                              | 5                                                                                                                     |                                   |

| Chapter 5                                    | Bipolar Charge Trapping Induced Anomalous Negative                                                                    | 88                                |

|                                              | Bias-Temperature Instability in HfSiON Gate Dielectric                                                                |                                   |

|                                              | pMOSFETs                                                                                                              |                                   |

| 5.1                                          | Preface                                                                                                               | 88                                |

| 5.2                                          | Anomalous Turn-around in Linear Drain Current Evolutions                                                              |                                   |

| U. <b>_</b>                                  | Anomalous Turn-around in Linear Drain Current Evolutions                                                              | 00<br>89                          |

| 5.3                                          | Bipolar Charging Model                                                                                                |                                   |

|                                              |                                                                                                                       | 89                                |

| 5.3                                          | Bipolar Charging Model                                                                                                | 89<br>91                          |

| 5.3<br>5.4                                   | Bipolar Charging Model<br>Single Charge Emission and Charge Pumping                                                   | 89<br>91<br>92                    |

| 5.3<br>5.4<br>5.5                            | Bipolar Charging Model<br>Single Charge Emission and Charge Pumping<br>Carrier Separation Measurement                 | 89<br>91<br>92<br>94              |

| 5.3<br>5.4<br>5.5<br>5.6<br><b>Chapter 6</b> | Bipolar Charging Model<br>Single Charge Emission and Charge Pumping<br>Carrier Separation Measurement<br>Summary 1896 | 89<br>91<br>92<br>94<br>95<br>114 |

| 5.3<br>5.4<br>5.5<br>5.6                     | Bipolar Charging Model<br>Single Charge Emission and Charge Pumping<br>Carrier Separation Measurement<br>Summary 1896 | 89<br>91<br>92<br>94<br>95        |

### TABLE CAPTIONS

#### Chapter 2

Table 2.1 Program bias voltages.  $V_{BL}$  is the bit-line voltage and  $V_{WL}$  is the word-line 22 voltage.

42

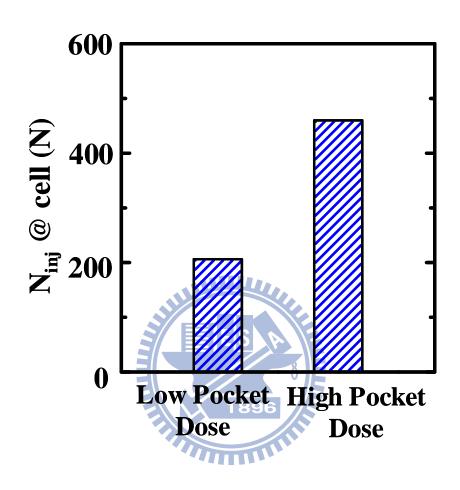

Table 2.2Key factors affecting program disturb.

#### Chapter 3

Table 3.1Program bias voltages used in this method (A) and two conventional hot electrons51methods (B and C).Method B has CHISEL injection while method C dose not<br/>have CHISEL.51

#### **Chapter 4**

Table 4.1 The relevant material parameters and scattering parameters used in the Monte Carlo simulation for both Si and Ge. The  $\gamma_{I_1} \gamma_2$  and  $\gamma_3$  are Luttinger parameters. The  $a_v$ , b, and d are the Bir-Pikus deformation potentials. The  $C_{II}$  and  $C_{I2}$  are elastic constants. The  $\Xi$  and  $D_t K$  are the average acoustic and optical deformation potential, respectively. The  $\hbar \omega$  is the phonon energy. The  $\Delta$  is the average step height, and the  $\Lambda$  is the correlation length.

#### Chapter 5

Table 5.1 Summary of NBT stress caused drain current instability and responsible 113 mechanisms.

#### FIGURE CAPTIONS

#### **Chapter 1**

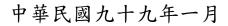

| Fig. 1.1 | Applications of flash memories (source: web research feet inc. 2003).            | 6 |

|----------|----------------------------------------------------------------------------------|---|

| Fig. 1.2 | Charge loss via the oxide trap (a) in a floating gate memory and (b) in a SONOS  | 7 |

|          | memory.                                                                          |   |

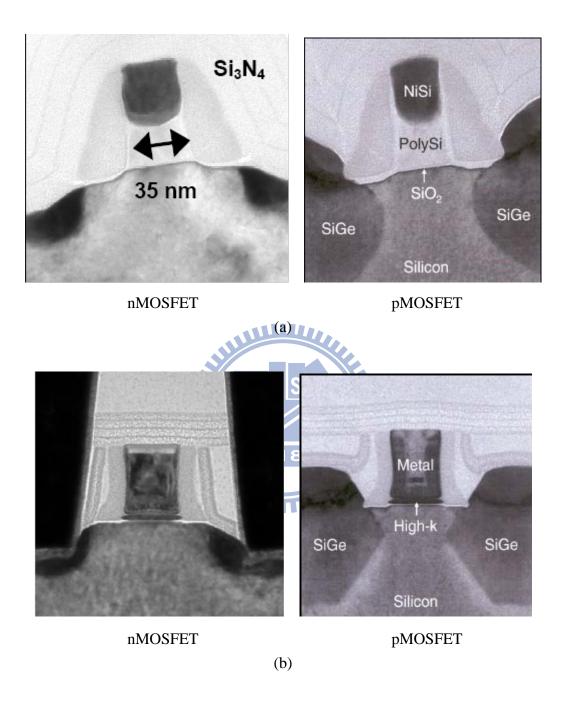

| Fig. 1.3 | Cross sectional TEM images of the state-of-the-art transistors for (a) 65 nm and | 8 |

|          | (b) 45 nm technology nodes.                                                      |   |

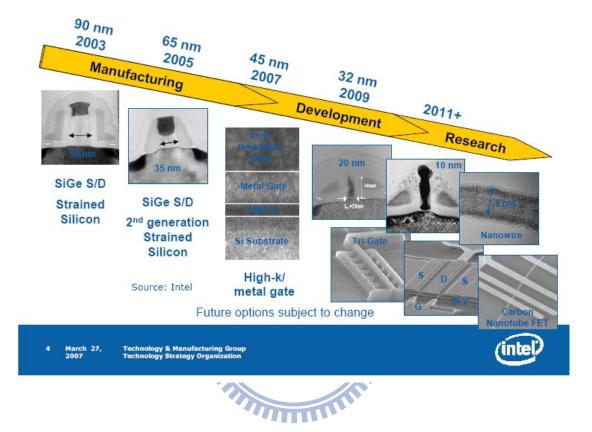

| Fig. 1.4 | The roadmap for the future options (source: Intel).                              | 9 |

|          |                                                                                  |   |

#### Chapter 2

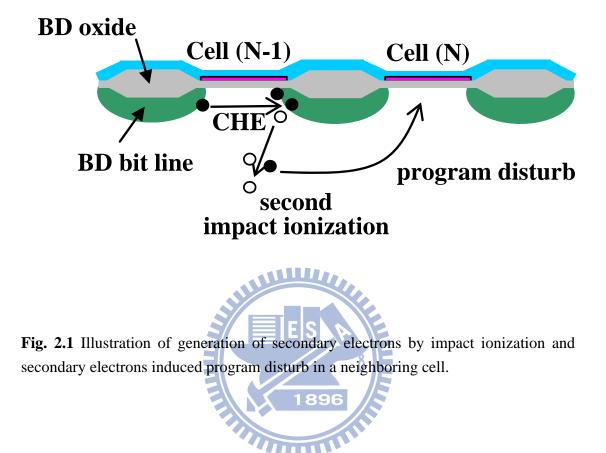

- Fig. 2.1 Illustration of generation of secondary electrons by impact ionization and 20 secondary electrons induced program disturb in a neighboring cell.

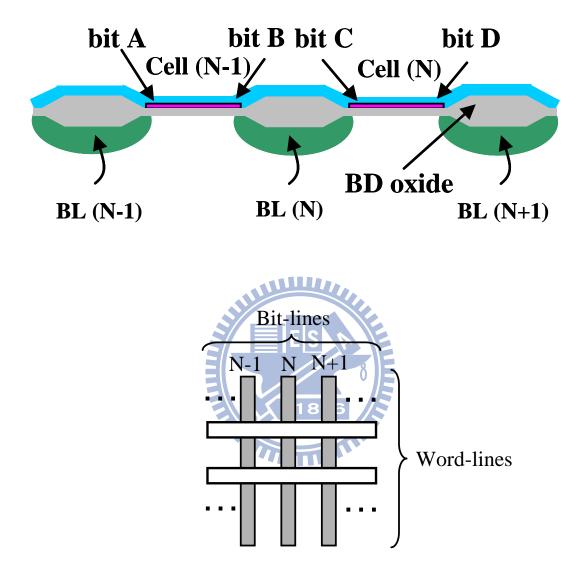

- Fig. 2.2 (a) Top view and (b) cross-section of a buried diffusion bit-line SONOS array. 21

The BD width is 0.12 μm in this work.

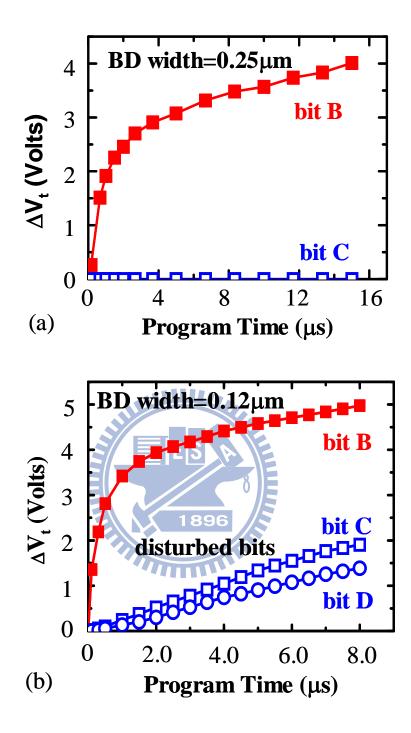

- Fig. 2.3 Threshold voltage shifts versus programming time. Bit B in cell (N-1) is a programmed bit, and bits C and bit D in cell (N) are disturbed bits. A reverse read with a bit-line voltage of 1.6V is employed. The bit-line width splits used in this work are (a) 0.25µm and (b) 0.12µm, respectively.

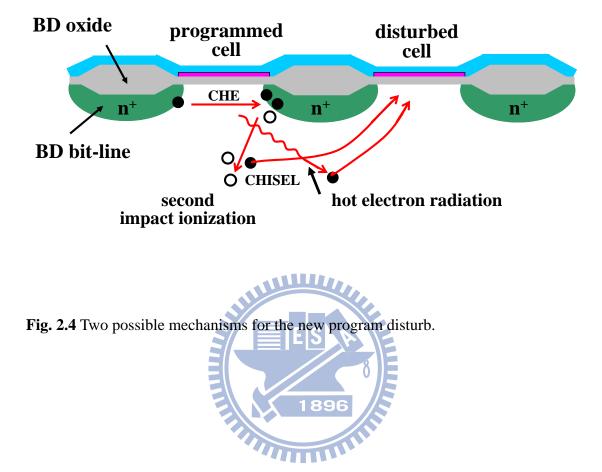

- Fig. 2.4 Two possible mechanisms for the new program disturb.

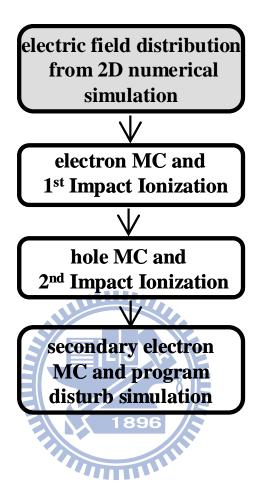

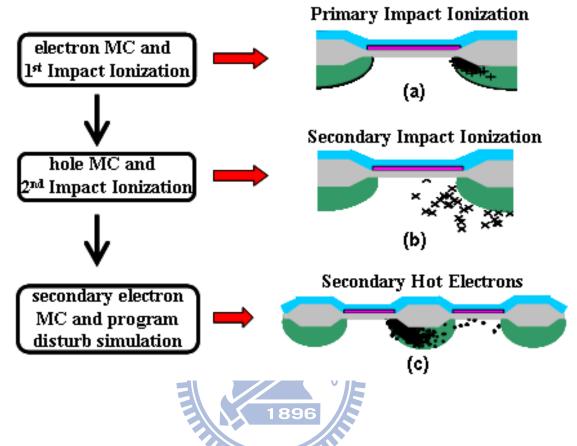

- Fig. 2.5 Three-step Monte Carlo simulation flow using both electron and hole Monte 25 Carlo codes to simulate secondary hot electrons.

24

- Fig. 2.6 (a) E-k relation used in the Monte Carlo simulation. A pseudo-potential model 26 and a bond-orbital model are used to calculate the conduction band and the valence band structure, respectively. (b) Monte Carlo window includes both a programmed cell and a disturbed cell. The electric field distribution during programming is shown.

- Fig. 2.7 (a) A random sample of 50 primary impact ionization events (denoted by +) 27 from the first step MC simulation. (b) A random sample of 50 secondary impact ionization events (denoted by x) from the second step MC simulation (c) A random sample of 500 secondary electrons (denoted by •) with energy above 2.5eV from the third step MC simulation.

- Fig. 2.8Monte-Carlo simulated trajectory of secondary hot electron injection.28

- Fig. 2.9 Electron energy distributions in a programmed cell (a) and in a disturbed cell (b). 29

|           | In a programmed cell, electrons near the drain (bit B) and near the source (bit A)                       |    |

|-----------|----------------------------------------------------------------------------------------------------------|----|

|           | are collected separately. Both primary and secondary electrons are counted. In a                         |    |

|           | disturbed cell, secondary electrons in the entire channel are accumulated.                               |    |

| Fig. 2.10 | Simulation flow of hot electron injection.                                                               | 30 |

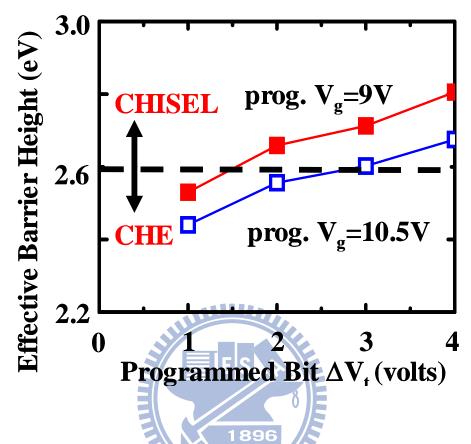

| Fig. 2.11 | Programmed bit $\Delta V_t$ dependence on the effective barrier height. The two program                  | 31 |

|           | word-line voltages are compared. CHISEL is dominant for energy above 2.6eV.                              |    |

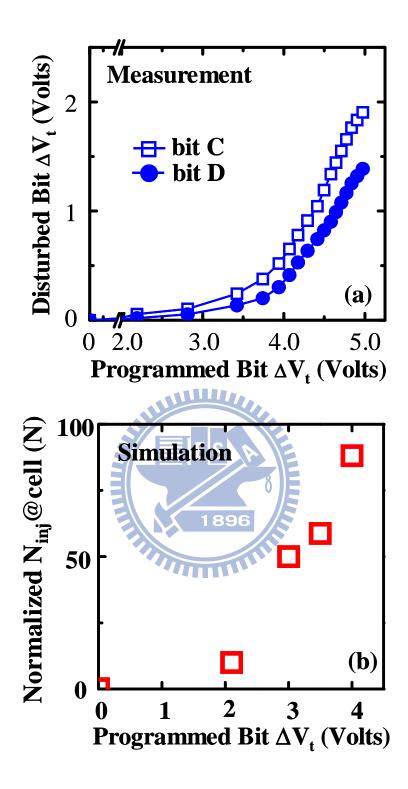

| Fig. 2.12 | (a) Disturbed bit $\Delta V_t$ versus programmed bit $\Delta V_t$ from measurement. (b)                  | 32 |

|           | Normalized charge injection in cell (N) versus programmed bit $\Delta V_t$ from Monte                    |    |

|           | Carlo simulation. Two-stage behavior is observed.                                                        |    |

| Fig. 2.13 | MC-simulated injected charge distributions along the channel in cell (N-1). The                          | 33 |

|           | effective oxide barrier height in cell (N-1) is calculated for $\Delta V_t$ (bit B)=3.0V.                |    |

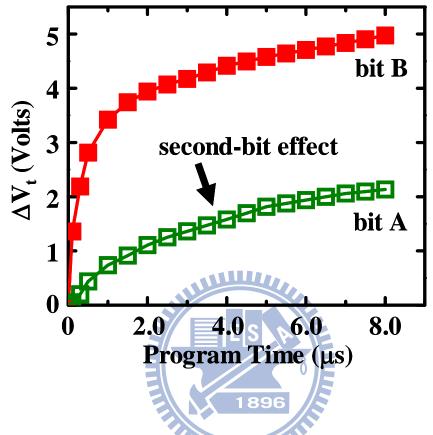

| Fig. 2.14 | $\Delta V_t$ of bit B and bit A during programming.                                                      | 34 |

| Fig. 2.15 | MC-simulated injected charge distributions along the channel in cell (N). The                            | 35 |

|           | effective oxide barrier height in cell (N) is calculated for $\Delta V_t$ (bit B)=3.0V.                  |    |

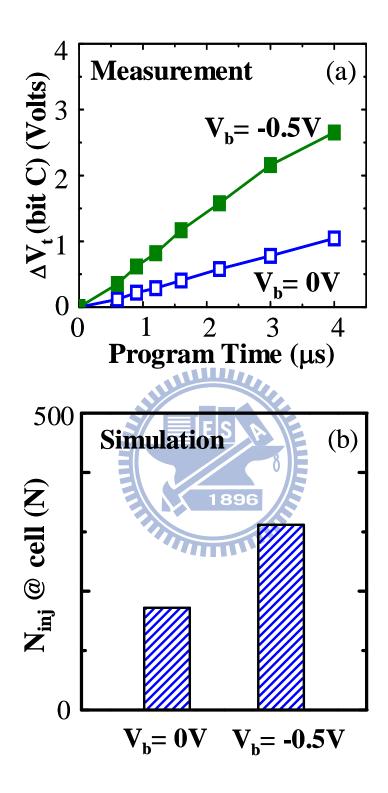

| Fig. 2.16 | (a) Measured substrate bias (V <sub>b</sub> ) effect on the program disturb, $\Delta V_t$ (bit C) versus | 36 |

|           | program time, and (b) simulated $N_{inj}$ in cell (N), for $V_b=0V$ and -0.5V.                           |    |

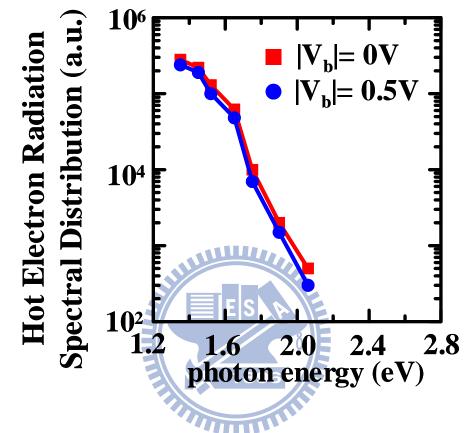

| Fig. 2.17 | Dependence of hot electron light emission spectrum on substrate bias in a                                | 37 |

|           | nMOSFET [2.14].                                                                                          |    |

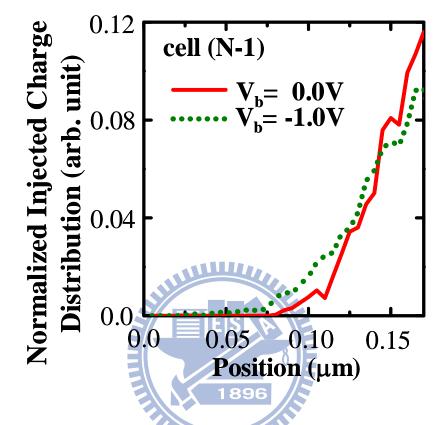

| Fig. 2.18 | Normalized injected charge distributions along the channel for $V_b=0V$ and -1.0V.                       | 38 |

|           | The $V_b$ = -1.0V has a broader distribution due to secondary electron injection.                        |    |

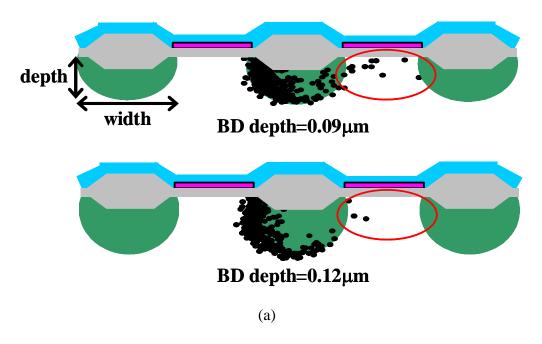

| Fig. 2.19 | (a) Simulated spatial distribution. A random sample of 500 secondary electrons                           | 39 |

|           | with energy above 2.6eV is drawn. (b) Dependence of the program disturb on BD                            |    |

|           | bit-line junction depth, N <sub>inj</sub> (cell (N)) versus bit-line depth.                              |    |

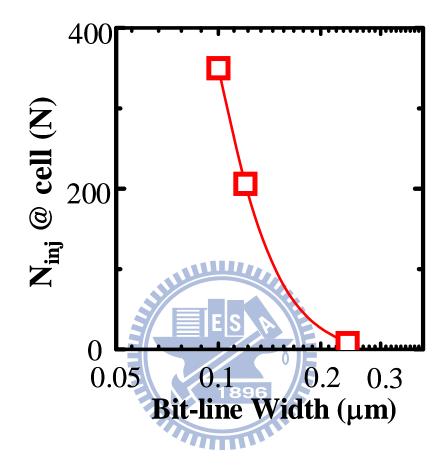

| Fig. 2.20 | Dependence of the program disturb on BD bit-line width, $N_{inj}(\text{cell }(N))$ versus                | 40 |

|           | bit-line width.                                                                                          |    |

| Fig. 2.21 | Pocket implant dosage effect on the program disturb. The dosages of the two                              | 41 |

Fig. 2.21 Pocket implant dosage effect on the program disturb. The dosages of the two 41 pocket implant splits differ by two times.

### Chapter 3

- Fig. 3.1 Illustration of punch-through leakages during conventional hot electron 49 programming in a NOR-type SONOS memory array.

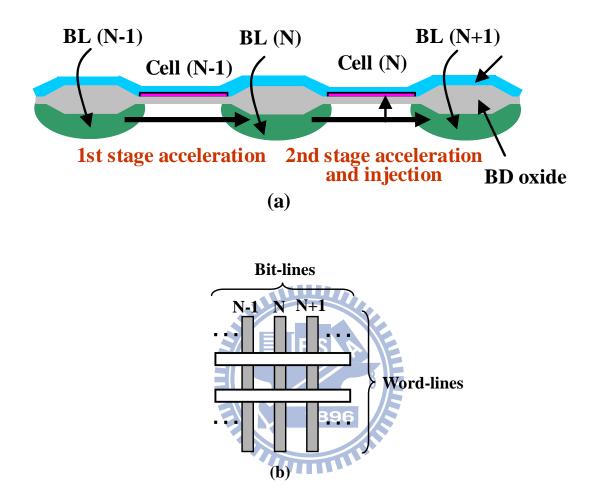

- Fig. 3.2(a) Illustration of a new hot electron programming method and two-stage electron50acceleration in a buried diffusion bit-line SONOS memory array. (b) Top view of

the array. The gate length and the BD width are  $0.1 \mu m$ .

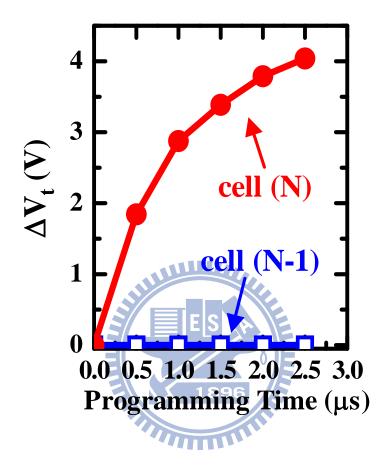

- Fig. 3.3 Threshold voltage shift versus programming time of the three hot electron 52 program methods in Table 3.1. The  $V_{ds}$  of a program cell is fixed at 2.5V.

- Fig. 3.4 Threshold voltage shift versus programming time in cell (N) and cell (N-1). The 53 read voltage is 1.6V.

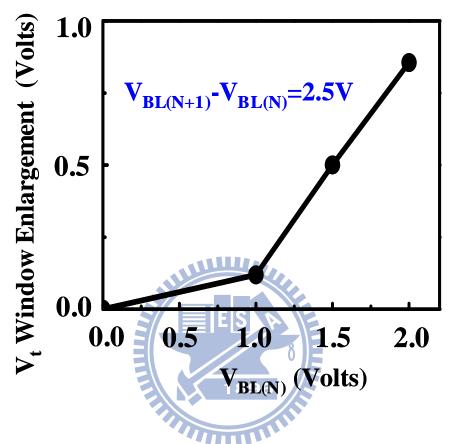

- Fig. 3.5 The dependence of Vt window enlargement on the pre-acceleration voltage VBL(N) 54 in this method. The Vt window enlargement is defined as Vt(this method)-Vt(method B). The Vds of a program cell, i.e. VBL(N+1)-VBL(N), is fixed at 2.5V. The programming time is 2.5µs.

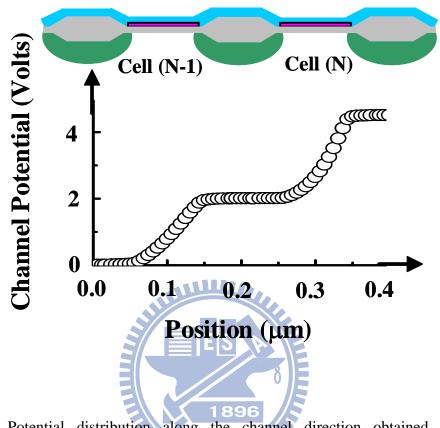

- Fig. 3.6 Potential distribution along the channel direction obtained from a 55 two-dimensional device simulator.

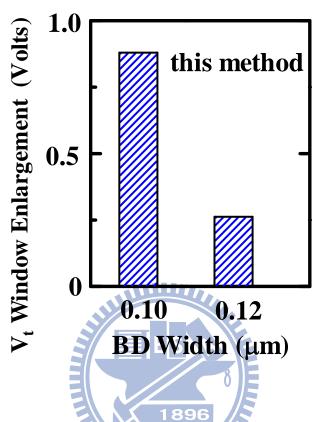

- Fig. 3.7 Comparison of a  $V_t$  window enlargement in two different BD width splits. The 56  $V_{ds}$  of a program cell is fixed at 2.5V. The programming time is 2.5 $\mu$ s.

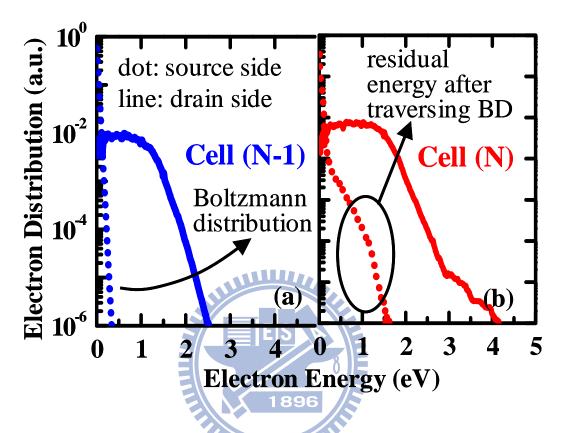

- Fig. 3.8 (a) Electron energy distributions in the source side and in the drain side, 57 respectively, in cell (N-1). (b) Electron energy distributions in cell (N). A high-energy tail near the source is highlighted, which results from electron non-equilibrium transport across the n<sup>+</sup> BD region.

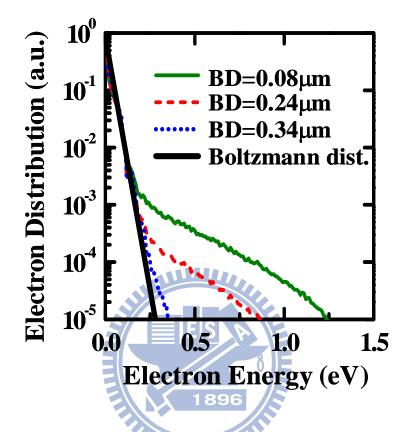

- Fig. 3.9 Monte Carlo simulated electron energy distribution at the source of cell (N) for 58 different BD widths. The bias voltages are given in Table 3.1. The thick solid line represents a Boltzmann distribution.

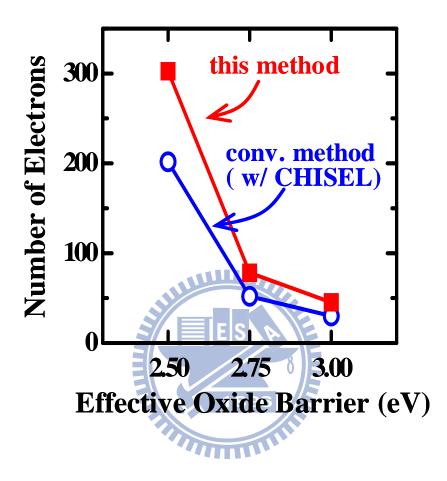

- Fig. 3.10 Total number of simulated electrons with energy above a certain effective oxide 59 barrier in this method and in method B.

#### Chapter 4

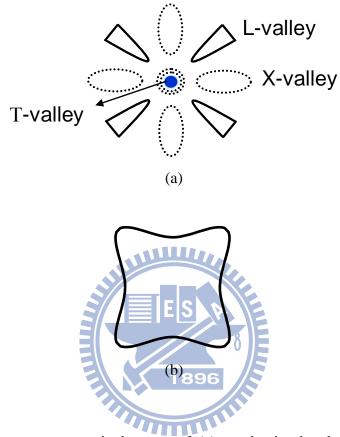

| Fig. 4.1 | Equi-energy contour in k-space of (a) conduction-band structure and (b) valence | 77 |

|----------|---------------------------------------------------------------------------------|----|

|          | band structure (heavy-hole) of bulk Ge (100) substrate.                         |    |

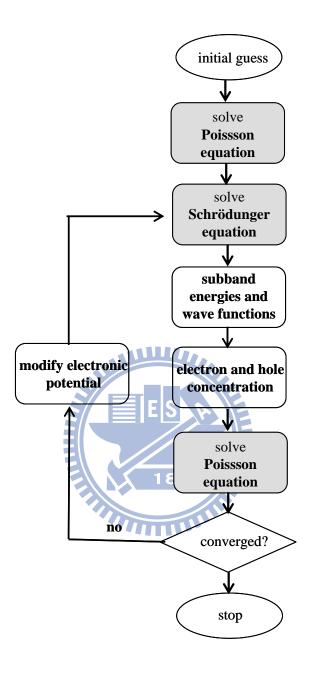

- Fig. 4.2 The simulation flow for the self-consistent solution to Poisson and Schrödinger 78 equations.

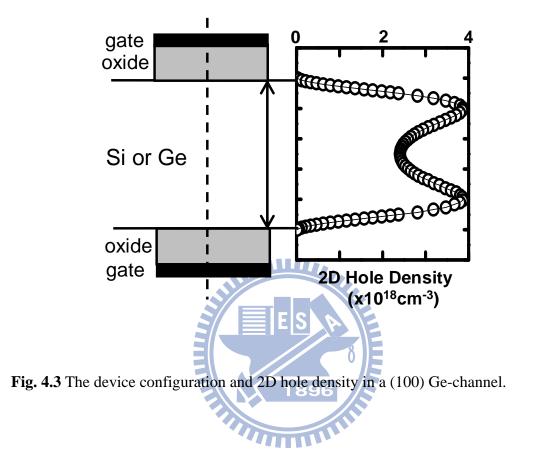

- Fig. 4.3 The device configuration and 2D hole density in a (100) Ge-channel. 79

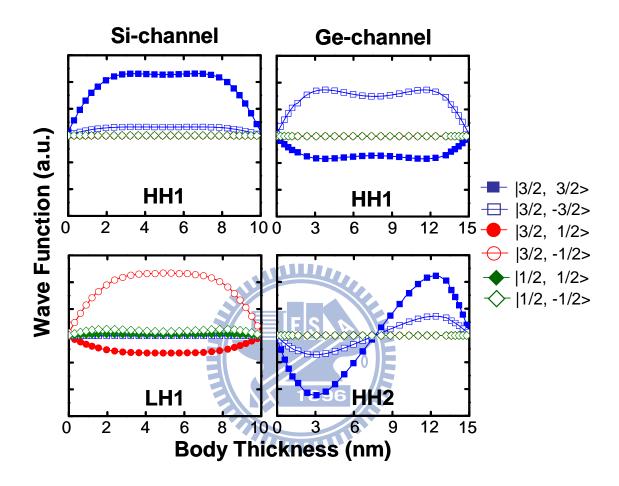

- Fig. 4.4 The wave-functions at the zone center of the lowest two subbands in a Si-channel 80 and Ge-channel

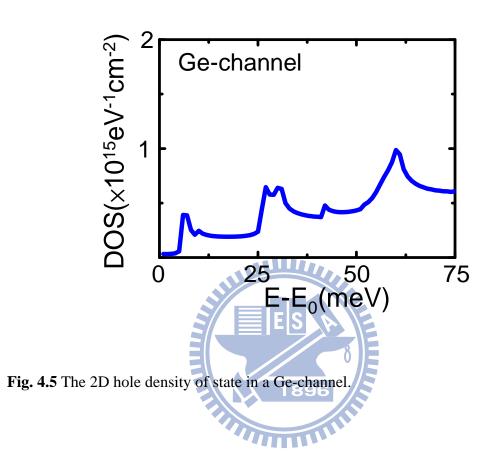

- Fig. 4.5The 2D hole density of state in a Ge-channel.81

- Fig. 4.6Simulated hole mobility as a function of a body thickness in (100)/[110] Si- and83Ge-channel DG-pMOSFETs. The experimental result for Si-channels is plotted

for comparison.

- Fig. 4.7 The body thickness dependence of an overlap factor and an energy difference 84 between the lowest two subbands in (100)/[110] Ge-channel DG-pMOSFETs.

- Fig. 4.8 Illustration of the body thickness dependence of valence subband energy and 85 overlap factor. The shaded region corresponds to an overlap integral. A narrower quantum well has a larger energy separation between subbands and a larger overlap factor.

- Fig. 4.9 Comparisons of the hole mobility and subband energy difference in (100)/[110] 86 and (110)/[-110] Ge-channels.

- Fig. 4.10 (a) Ge hole mobility as a function of a body thickness in (100)/[110] and 87 (110)/[-110] channel directions with and without an uniaxial compressive stress of 0.3GPa. The mobility is normalized to the one without stress effect. (b) The constant energy contours in (100) substrate are plotted. The constant energies are 10, 25 and 50 meV.

# Julie

#### **Chapter 5**

- Fig. 5.1 Schematic diagram for the transient measurement system. The high speed 96 switches minimize a switching delay down to microseconds between stress and drain current measurement.

- Fig. 5.2 The waveforms applied to the gate and drain in the transient measurement. 97

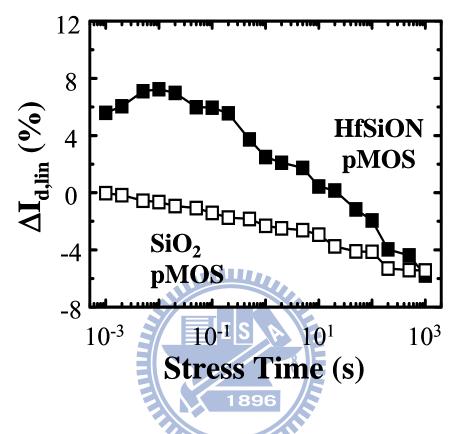

- Fig. 5.3 NBT stress induced linear drain current change ( $\Delta I_{d,lin}$ ) in SiO<sub>2</sub> and HfSiON 98 pMOSFETs. The stress V<sub>g</sub> is -2.8V and the linear drain current ( $I_{d,lin}$ ) is measured at V<sub>g</sub>/V<sub>d</sub>=-1.2V/-0.2V.

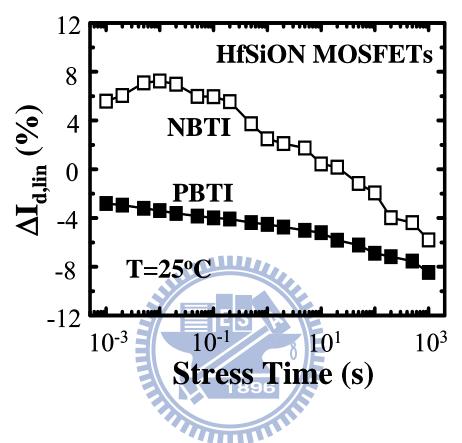

- Fig. 5.4 Linear drain current change ( $\Delta I_{d,lin}$ ) in a pMOSFET (NBTI) and in a nMOSFET 99 (PBTI). The stress V<sub>g</sub> is -2.8V for the pMOSFET and 2.2V for the nMOSFET.

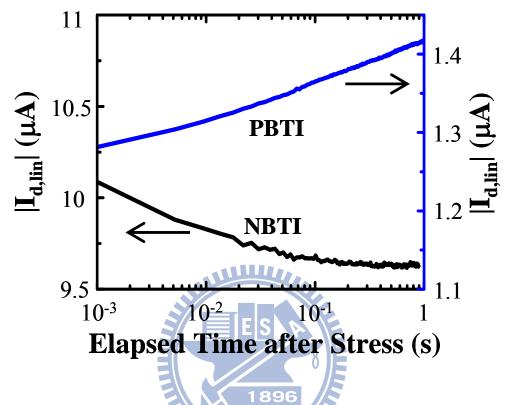

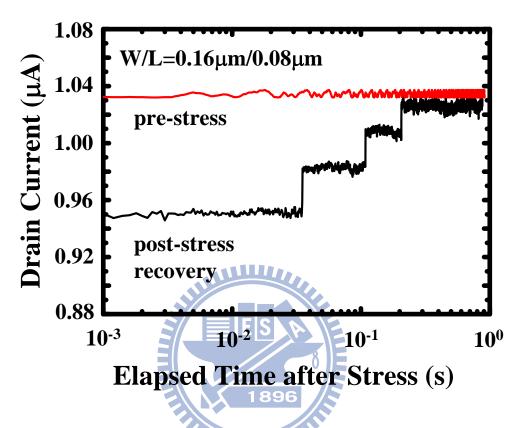

- Fig. 5.5  $|I_{d,lin}|$  as a function of elapsed time after stress. The drain current recovery is 100 observed in a nMOSFET, while the NBTI shows persistent post-stress current degradation.

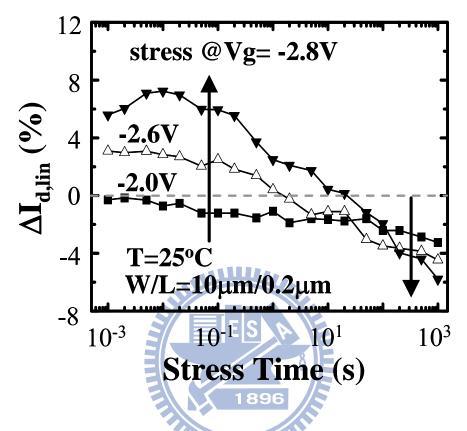

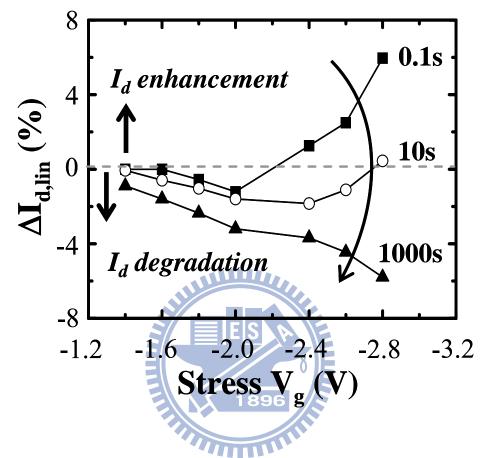

- Fig. 5.6 NBT stress induced drain current evolution for different stress  $V_g$ . Drain current 101 enhancement in an initial stage of stressing is observed for high stress  $V_g$  (-2.6V and -2.8V).

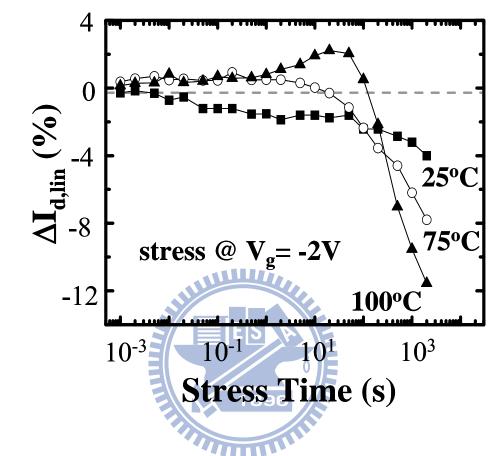

- Fig. 5.7 NBT stress induced drain current evolution for different stress temperatures. 102 Drain current enhancement in an initial stage of stressing is observed for high stress temperatures.

Fig. 5.8 Stress  $V_g$  dependence of  $\Delta I_{d,lin}$  at different stress times. For a short stress time 103 (t=0.1s and 10s),  $\Delta I_{d,lin}$  can be positive or negative, depending on stress  $V_g$ . For a longer stress time (t=1000s), the dependence returns to a normal degradation mode as in SiO<sub>2</sub> gate dielectric transistors.

104

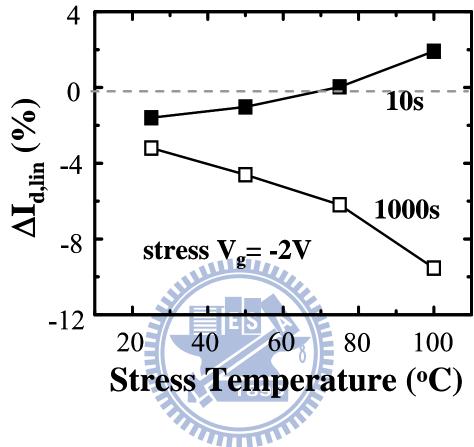

- Fig. 5.9 Stress temperature dependence of  $\Delta I_{d,lin}$ .

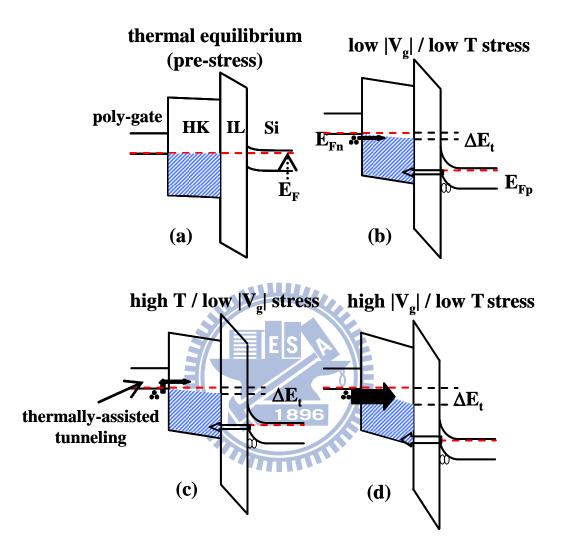

- Fig. 5.10 Schematic representation of an energy band diagram and charge injection 105 processes in (a) thermal equilibrium, (b) low |V<sub>g</sub>|/ low T stress, (c) high T/ low |V<sub>g</sub>| stress, and (d) high |V<sub>g</sub>|/ low T stress. The shaded area represents the occupied trap states in the high-*k* layer. Electron injection from the poly gate and hole injection from the channel are illustrated.

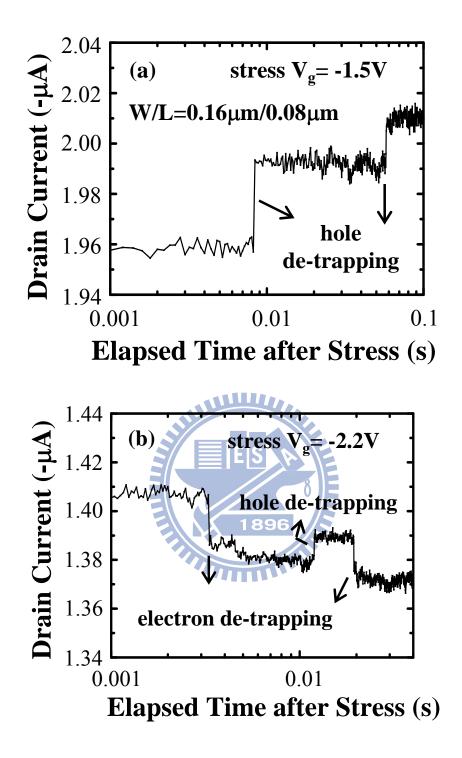

- Fig. 5.11 Post-stress I<sub>d</sub> evolution patterns in small-area devices after (a) a low  $|V_g|$  (-1.5V) 106 stress and (b) a high  $|V_g|$  (-2.2V) stress. The post-stress measurement condition is  $V_g \sim V_t$  and  $V_d$ =-0.2V.

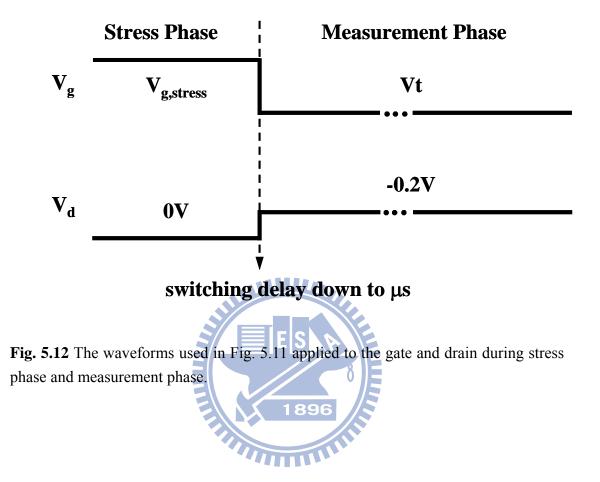

- Fig. 5.12 The waveforms used in Fig. 5.11 applied to the gate and drain during stress phase 107 and measurement phase.

- Fig. 5.13 Post-stress I<sub>d</sub> evolution patterns after stress at  $V_g$ =0.7V for 0.2s in a nMOSFET. 108 The post-stress measurement condition is  $V_g/V_d$ =0.3V/0.2V.

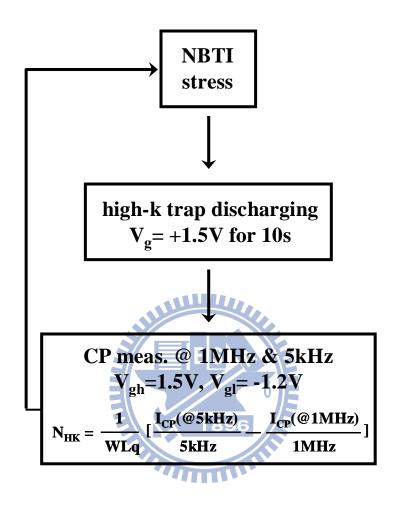

- Fig. 5.14 The characterization procedures of two-frequency charge pumping technique for 109 high-*k* trap density extraction.

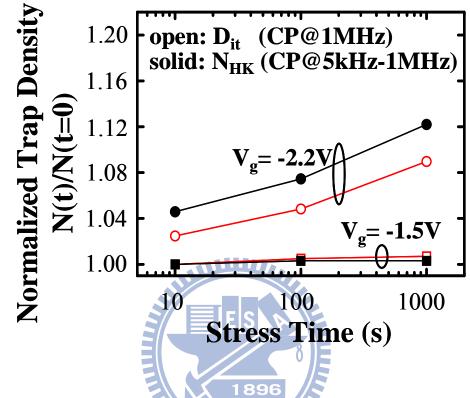

- Fig. 5.15 Interface traps ( $D_{it}$ ) and bulk high-k traps ( $N_{HK}$ ) growth rates in NBT stress at 110  $V_g$ =-1.5V and  $V_g$ =-2.2V.

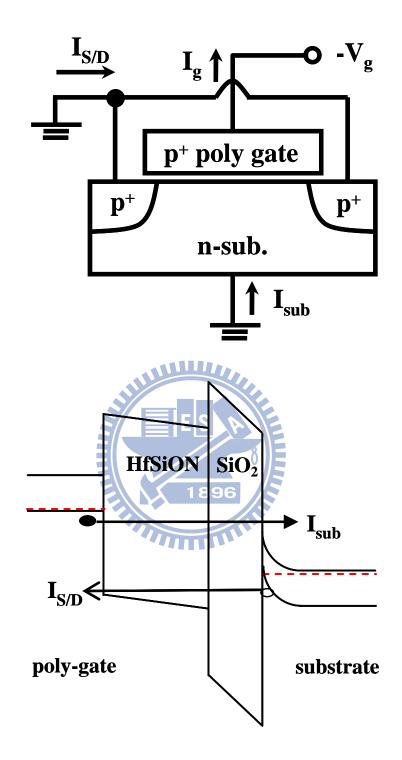

- Fig. 5.16 Illustration of charge separation measurement and carrier flow in a high-k 111 pMOSFET under  $-V_g$  stressing. Isub denotes the electron injection current from the  $p^+$  poly-gate to substrate, and  $I_{S/D}$  stands for hole injection current from the inverted channel. Both can be measured separately through the connected source and drain measurement configuration.

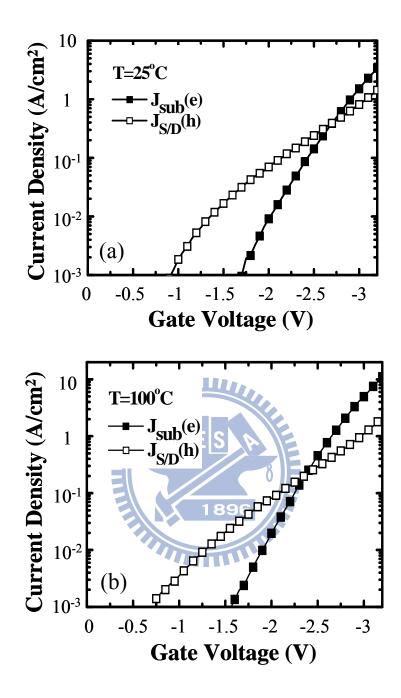

- Fig. 5.17 Gate voltage dependence of hole injection current ( $I_{S/D}$ ) and electron injection 112 current ( $I_{sub}$ ) in a high-*k* pMOSFET, measured at (a) T=25°C and (b) T=100°C.

## LIST OF SYMBOLS

| $a_{v}$               | Bir-Pikus deformation potential                                |

|-----------------------|----------------------------------------------------------------|

| b                     | Bir-Pikus deformation potential                                |

| С                     | Elastic stiffness constant matrix                              |

| D <sub>it</sub>       | Interace trap density                                          |

| $D_n$                 | Two-dimensional density of hole states in <i>n</i> -th subband |

| $D_t K$               | Average optical deformation potential                          |

| d                     | Bir-Pikus deformation potential                                |

| $E_{\rm F}$           | Fermi level                                                    |

| $E_n$                 | <i>n</i> -th subband energy                                    |

| Et                    | Trap energy (from the conduction band)                         |

| $E_{ox}$              | Perpendicular oxide field                                      |

| $f_0$                 | Fermi-Dirac distribution                                       |

| Н                     | 6x6 Hamiltonian                                                |

| $H_k$                 | Luttinger Hamiltonian ES                                       |

| $H_{mn}$              | Overlap factor                                                 |

| $H_{\varepsilon}$     | Bir-Pikus Hamiltonian                                          |

| $h_i$                 | Mesh size between adjacent grid points $x_i$ and $x_{i+1}$     |

| $k_B$                 | Boltzmann constant                                             |

| $k_x$ , $k_y$ , $k_z$ | Wave-vector in x, y, z-direction                               |

| Ι                     | Identity matrix                                                |

| I <sub>cp</sub>       | Charge pumping current                                         |

| Id                    | Drain current                                                  |

| $I_{d,lin}$           | Linear drain current                                           |

| $I_{S/D}$             | Source/Drain current                                           |

| I <sub>sub</sub>      | Substrate current                                              |

| L                     | Channel length                                                 |

| $m_0$                 | Free electron mass                                             |

| $n_{op}$              | Bose-Einstein distribution                                     |

| N <sub>HK</sub>       | High- <i>k</i> trap density                                    |

| N <sub>inj</sub>      | Number of injected hot electrons                               |

| $p_{inv}$             | Inversion hole density                                         |

|                       |                                                                |

|                       | Elamantamy altance                                                 |

|-----------------------|--------------------------------------------------------------------|

| q                     | Elementary charge                                                  |

| $x_i$                 | Mesh point at <i>i</i> -th grid                                    |

| S                     | Elastic compliance constant matrix                                 |

| $S^m_{ac}$            | Acoustic phonon scattering rate in <i>m</i> -th subband            |

| $S^m_{op}$            | Optical phonon scattering rate in <i>m</i> -th subband             |

| Т                     | Lattice temperature                                                |

| T <sub>Ge</sub>       | Body thickness of a Ge-channel                                     |

| t <sub>meas</sub>     | Measurement time                                                   |

| t <sub>stress</sub>   | Stress time                                                        |

| $u_l$                 | Longitudinal sound veloctiy                                        |

| W                     | Channel width                                                      |

| V                     | Potential energy                                                   |

| V <sub>d</sub>        | Drain voltage                                                      |

| V <sub>d,meas</sub>   | Drain voltage<br>Measurement drain voltage<br>Stress drain voltage |

| V <sub>d,stress</sub> | Stress drain voltage                                               |

| $V_{g}$               | Gate voltage                                                       |

| V <sub>g,meas</sub>   | Measurement gate voltage                                           |

| V <sub>g,stress</sub> | Stress gate voltage                                                |

| V <sub>ds</sub>       | Drain-to-source voltage 1896                                       |

| $V_t$                 | Threshold voltage                                                  |

| $V_{T}$               | Thermal voltage                                                    |

| $V_{BL}$              | Bit-line voltage                                                   |

| $V_{WL}$              | Word-line voltage                                                  |

| ħ                     | Reduced Planck constant                                            |

| $\Delta I_{d,lin}$    | Change in linear drain current                                     |

| $\Delta E_t$          | Energy range for available dielectric traps                        |

| $\Delta V_t$          | Change in threshold voltage                                        |

| α                     | Coefficient of effective oxide barrier height                      |

| β                     | Coefficient of effective oxide barrier height                      |

| Е                     | Strain tensor                                                      |

| $\phi_B$              | Effective oxide barrier height                                     |

| $\phi_{SiO2}$         | SiO <sub>2</sub> /Si conduction band offset                        |

| arphi                 | 6×1 wave-vector                                                    |

|                       |                                                                    |

| λ                            | Split-off energy                         |

|------------------------------|------------------------------------------|

| ρ                            | Material density                         |

| $\sigma$                     | Stress tensor                            |

| Y1,Y2,Y2                     | Luttinger parameter                      |

| $\omega_{op}$                | Optical phonon frequency                 |

| Δ                            | Average step height                      |

| Φ                            | Wave-function                            |

| Λ                            | Correlation length                       |

| Ξ                            | Effective acoustic deformation potential |

| $\left J,m_{J}\right\rangle$ | Basis function                           |

| +                            | Operation of complex conjugate           |

## Chapter 1

### Introduction

#### **1.1 Backgrounds**

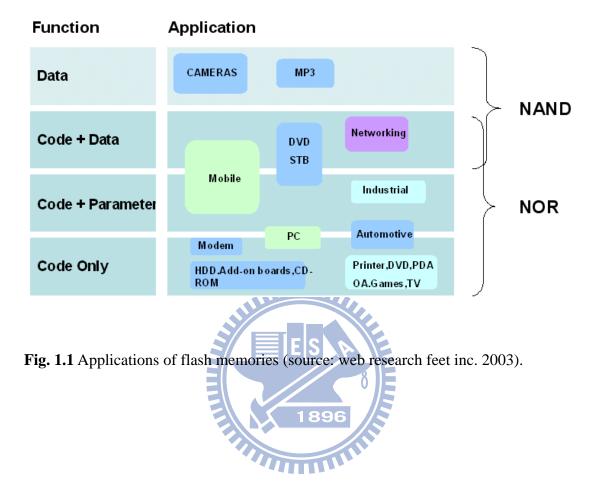

Flash memories play an important role in our VLSI industry with their wide applications (see Fig. 1.1). NOR-type flash memory is suitable for code storage applications, such as personal computers, mobile phones. On the other hand, NAND-type flash memory is suitable for data storage applications, such as digital camera. In terms of charge storage devices, two state-of-the-art structures attract great attention. One is floating gate (FG) flash and the other is charge trapping (CT) flash. The major difference in charge loss mechanisms between FG and CT flash devices is that the charge storage media is conductive in FG flash and is non-conductive in CT flash, as illustrated in Fig. 1.2. Recently, considerable research efforts have been made to study the nitride-based, localized charge trapping storage flash memories for its smaller cell size  $(2.5F^2 \text{ per bit}, \text{ where } F \text{ is the feature size of the process})$ , simpler fabrication process [1.1]-[1.2], the absence of drain turn-on and over-erase [1.3] in comparison with conventional floating gate flash. In a NOR-type SONOS (silicon-oxide-nitride-oxide-silicon) memory, a virtual ground array with  $n^+$  buried diffusion bit-lines is usually implemented to achieve a higher packing density [1.4]. Much attention is particularly paid to its two bits storage capability. The two bits operation can be achieved by placing the programmed charges in the nitride layer locally above the source or drain junction by channel hot electron (CHE) program and band to band hot hole (BTB HH) erase. The reverse-read scheme is used to monitor the threshold voltage window [1.1].

With respect to the advanced CMOS devices, Fig. 1.3 shows the cross sectional images of Intel's state-of-the-art transistors for 65 nm [1.5] and 45 nm technology nodes [1.6], [1.7]. In order to maintain the scaling roadmap, Intel has made a significant breakthrough in solving the gate leakage problem. They replace the SiO<sub>2</sub> with the high permittivity (high-k) material, hafnium-based, and replace the polysilicon gate electrode with new metals for the 45 nm technology node (see Fig. 1.3 (b)). The implementation of the high-k material is to reduce the gate leakage, and metal gate electrode is to eliminate the poly depletion effect, resolve the threshold voltage pinning effect, and screen soft phonons for improved mobility [1.7]. In Fig. 1.3 (b), advanced strained silicon technologies, such as dual-stress liner [1.8] and embedded SiGe source or drain [19], are also incorporated to boost the device performance. Fig. 1.4 shows the roadmap for the future options from Intel's predictions. For the 22 nm technology node and beyond, double-gate field-effect-transistors (MOSFETs) metal-oxide-semiconductor and fin field-effect-transistor have been considered as promising alternatives to bulk MOSFETs [1.0-1.12] due to their immunity to short channel effects. In addition, advanced channel materials with higher carrier mobility than bulk Si, such as Ge [1.13], and III-V materials [1.14], offer potential long term options. The nanowire is under research as well.

#### **1.2 Description of the Problem**

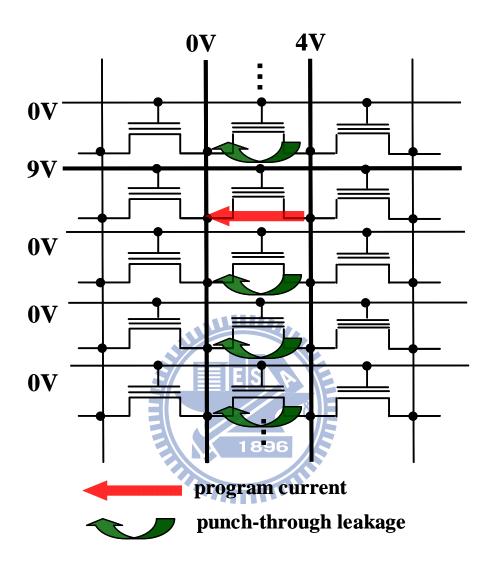

As the technology node is scaled down, three major reliability issues in a NOR-type SONOS memory are identified, which may impose new constraints in cell scaling. The first issue is random telegraph signal (RTS). As bit size aggressively shrinks, the number of programmed charges reduces. A single charge

trapping/detrapping will induce a large fluctuation in read current [1.15]. This current fluctuation, referred to as RTS, has become a serious concern in advanced CMOS technologies [1.16] and will cause retention loss tail bits in a SONOS array. Note that this issue is not studied in this dissertation. The second issue is the program disturb. As the technology node advances, the buried diffusion bit-line width is reduced. Previous works have shown that, in channel hot electron program, channel initiated secondary electrons (CHISEL) play an important role in charge injection [1.17]-[1.19]. As a result, impact ionization-generated secondary electrons may flow to a neighboring cell and cause a program disturb, which results in a threshold voltage shift of a neighboring cell. This program disturb will be a bottleneck in cell scaling. The third issue is the channel punch-through leakage. For hot electron program in a NOR-type SONOS memory, a large drain-to-source voltage is usually required for channel electrons to overcome the tunnel dielectric barrier height. In a SiO<sub>2</sub>/Si system, the barrier height is 3.1 eV for electron. When the memory cell's gate length is shrunk, the punch-through leakage contributed from the un-selected cells sharing the same bit-line voltage will be significant and limit the cell performance.

For the 22 nm technology node and beyond, the multiple gate structures and novel channel materials are appreciated due to their immunity to short channel effect and high carrier mobility than Si, respectively. It is also demonstrated that the carrier mobility can be further improved in quantum structure MOSFETs by a subband modulation [1.20],[1.21]. As a consequence, it is of much importance to investigate the transport properties in a quantum structure MOSFET with an advanced channel material.

The program disturb and channel punch-through in a NOR-type SONOS memory are characterized and evaluated by a Monte Carlo simulation. We use a Monte Carlo method to solve the Boltzmann transport equation (BTE) [1.22], which is a very difficult equation to solve numerically or analytically. The Monte Carlo method has the following attributes. It is a stochastic determination. It can be implemented with band structures and scattering processes. Thus, the quantities of physical interest, such as drift velocity, mean free path, and average carrier energy, can be evaluated. Furthermore, the Monte Carlo method is commonly employed to solve BTE in high-field transport conditions, which is suitable for the simulation of impact ionization, substrate current and hot carrier phenomena [1.23],[1.24]. Furthermore, the applications of Monte Carlo simulation are also widely used to solve BTE for the study of inversion carrier mobility in high-*k* [1.25] and strained-Si devices [1.26].

Finally, we will focus on the negative bias temperature instability (NBTI) in high-*k* devices. NBTI has been recognized as a major reliability concern in ultra-thin gate dielectric pMOSFETs [1,27], which is attributed to the interface generation and hole trapping. Compared to a SiO<sub>2</sub> gate dielectric, however, the NBT instability in high-*k* gate dielectric pMOSFETs has been less explored. As a consequence, we employ the fast transient measurement technique [1.28] to minimize a switching delay between "stress and sense" down to  $\mu$ s, and thus reduce the post-stress transient effect due to charge trapping/detrapping in high-*k* gate dielectric.

#### **1.3 Organization of this dissertation**

This dissertation consists of six chapters. The scope of the dissertation mainly focuses on the applications of Monte Carlo simulation in advanced CMOS and SONOS flash memory. Following the introduction, the characterization and physical mechanisms of the program disturb in a NOR-type SONOS memory are described in Chapter 2. The multi-step Monte Carlo simulation is employed to explore this disturb mechanism. Proposed in Chapter 3 is a novel hot electron programming method with a low drain-to-source voltage in a NOR-type SONOS memory. This method has the merit of immunity to channel punch-through. The concept of this method is verified by means of a Monte Carlo simulation. In Chapter 4, we have developed a Monte Carlo simulation including realistic subband structures to simulate the properties of two-dimensional hole transport in Ge-channel double-gate pMOSFETs. The low field hole mobility is calculated by a Monte Carlo simulation. The effects of substrate/channel orientation effects and uniaxial compressive stress on hole mobility are particularly evaluated. In Chapter 5, the characteristic of bipolar charge trapping induced anomalous negative bias temperature instability in HfSiON gate dielectric pMOSFETs is demonstrated with the use of the computer-automated transient measurement system and the responsible origins are discussed. Finally, conclusions are drawn in Chapter 6.

**Fig. 1.2** Charge loss via the oxide trap (a) in a floating gate memory and (b) in a SONOS memory.

**Fig. 1.3** Cross sectional TEM images of the state-of-the-art transistors for (a) 65 nm and (b) 45 nm technology nodes [1.5]-[1.7].

## **Innovation-Enabled Technology Pipeline**

Fig. 1.4 The roadmap for the future options (source: Intel).

## Chapter 2

# Characterization and Monte Carlo Analysis of Secondary Electrons Induced Program Disturb in a Buried Diffusion Bit-line SONOS Flash Memory

#### 2.1 Preface

Nitride based, localized charge trapping storage flash memory devices have received great interest due to superior performance than conventional floating gate memory devices. Recently, two bits per cell SONOS flash memories by utilizing channel hot electron program and band-to-band tunneling hot hole erase have been demonstrated with good performance and reliability, small die size and low fabrication cost [1.1][1.2]. A virtual ground array with  $n^+$  buried diffusion (BD) bit-lines is implemented to achieve a higher packing density [1.4]. The reliability issues of these memories and their physical mechanisms such as program-state charge loss, erase-state threshold voltage (V<sub>1</sub>) drift and read disturb have been addressed in [1.2][2.1]. As the technology node is scaled beyond 50 nm, two new reliability issues due to number fluctuation of stored charges [1.15][2.2] and bit-line scaling are identified, which may impose a new constraint in cell scaling.

First, as bit size aggressively shrinks, the number of programmed charges reduces. A single charge trapping/detrapping will induce a large fluctuation in read current. This current fluctuation, referred to as random telegraph noise, has become a major concern in advanced CMOS technologies [1.16] and will cause retention loss tail bits in a SONOS flash [2.2]. Second, previous studies have shown that, in channel

hot electron program, channel initiated secondary electrons (CHISEL) play an important role in charge injection [1.17]-[1.19]. As a buried diffusion bit-line width is reduced, we find that impact ionization-generated secondary electrons may flow to a neighboring cell and cause a program disturb, as illustrated in Fig. 2.1.

In this work, we first measure the programming characteristics of the programmed cell, i.e. cell (N-1), and the disturbed cell, i.e. cell (N). Then, a multi-step Monte Carlo (MC) simulation is performed to explore the disturb mechanism. The effect of substrate bias on the program disturb is characterized and evaluated by a Monte Carlo simulation to verify the proposed physical mechanism. Furthermore, the effects of bit-line dimension and pocket implant on the program disturb are also discussed by a Monte Carlo simulation. The possible solutions to alleviate the program disturb are also addressed.

896

#### 2.2 Experimental

#### 2.2.1 Devices

To explore this new failure mode and its impact on bit-line scaling, we fabricate a SONOS mini-array. The SONOS memory cell is fabricated by a standard CMOS process and the gate dielectric is replaced with a nitride trapping layer, sandwiched between two SiO<sub>2</sub> layers. The SONOS cells are processed in a virtual ground array, where bit-lines are  $n^+$  buried diffusions and word-lines are poly stripes. Bit charges are stored in the two sides of a channel to realize two-bit per cell operation. Since there is no field isolation, buried diffusion bit-line array is desirable for a higher packing density. Fig. 2.2 (a) and (b) show the cross section and top view of a buried diffusion bit-line SONOS array, respectively. The BD width in this work is 0.12 µm.

#### 2.2.2 Program Disturb in a NOR-type SONOS Memory

Bit B in cell (N-1) is a programmed bit. Bits C and bit D in cell (N) sharing the same word-line are disturbed bits (see Fig. 2.2 (a)). The program bias voltages are given in Table 2.1, where  $V_{BL}$  is the bit-line voltage and  $V_{WL}$  is the word-line voltage. During channel hot electron programming, the  $V_{WL}$  is 9V, the  $V_{BL(N-1)}$  and  $V_{BL(N)}$  are 0V and 4.2V respectively while  $V_{BL(N+1)}$  is kept floating. Fig. 2.3 measures the  $V_t$  evolutions of two neighboring cells during programming for two different BD width splits. A reverse-read scheme with a bit-line voltage of 1.6V is employed [1.1]. It is obvious that for a larger bit-line width, i.e. 0.25 µm, no program disturb is observed. However, for a 0.12 µm bit-line width, a significant program disturb ( $\Delta V_t$  of bits C and D) is observed. As a consequence, this program disturb will become a new constraint in bit-line scaling. In addition, it is found that the program disturb is apparently more serious for a larger program window.

#### 2.2.3 Mechanisms for the Program Disturb

Two possible mechanisms for the program disturb are illustrated in Fig. 2.4. One is secondary electron generation by impact ionization. In channel hot electron programming, channel electrons gain energy from a large electric field. These high energy electrons induce a first impact ionization near the drain junction and then the generated holes are accelerated by the large drain-to-substrate voltage. The hot holes induce a second impact ionization and generated secondary electrons may flow to a neighboring cell, i.e. disturbed cell, and cause a program disturb. The other possible mechanism is substrate electron generation via re-absorption of channel hot electron emitted light. The main cause of the program disturb will be identified later.

1896

#### 2.3 Monte Carlo Model

A multi-step Monte Carlo simulation similar to that described in [2.3][2.4] is used to explore the program disturb mechanism, as illustrated in Fig. 2.5. The Monte Carlo simulation is performed in the frozen-field approximation [1.23]. The electric field is never updated to reflect the dynamics of the carriers. In other words, the electric field obtained from the two-dimensional device simulator is not calculated self-consistently with the Monte Carlo solution of Boltzmann transport equation. The validity of this nonself-consistent approach has been performed in [2.5], which can be used for hot carrier simulation. This is because the substrate current contributes little to the total current in the channel. It should be noted that the nonself-consistent approach reduces the CPU time without sacrificing too much accuracy.

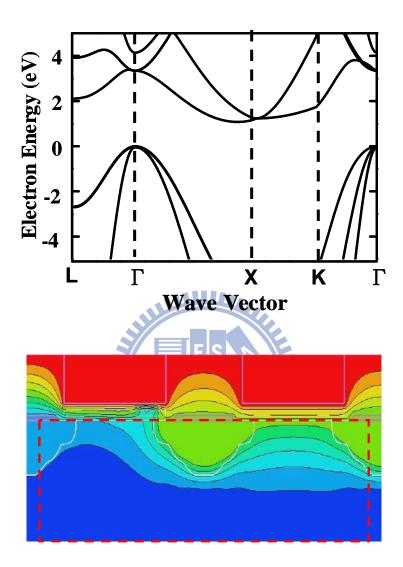

Then, the electric field distribution in cell (N-1) and cell (N) is firstly obtained from a two-dimensional device simulator, Medici [2.6]. The hydrodynamic model, which takes into account the average carrier energy, should be used. The Monte Carlo simulation includes a full band structure for the high energy simulation. A pseudo-potential model [2.7] and a bond-orbital model [2.8] are used to calculate the conduction band-structure and the valence band-structure, respectively. The energy dispersions are drawn in Fig. 2.6 (a). The scattering mechanisms in the simulation include acoustic phonon scattering, optical phonon scattering and impact ionization. The impact ionization rate is calculated by Keldysh's empirical model [2.9]. The band structure and carrier scattering parameters were calibrated in our earlier papers [2.10][2.11]. In a Monte Carlo window, as marked in Fig. 2.6 (b), both electron and hole Monte Carlo simulations are performed. The Monte Carlo window consists of two neighboring cells that both programmed bit and disturbed bits are included. Then, electrons are launched at the source of a programmed cell. The launched electrons have a room temperature and a Maxwell-Boltzmann distribution in energy. The lower and upper surfaces of the Monte Carlo window are treated as reflective boundaries. Each electron or hole is simulated until it either produces an impact ionization event or passes out of the Monte Carlo window. When an impact ionization event takes place, the energy of each electron or hole minus the band-gap energy is shared by the three created secondaries. Moreover, the hot electron injection is simulated by counting the electrons hitting the Si and SiO<sub>2</sub> interface with energy larger than the effective barrier height.

#### 2.4 Results and Discussions

#### 2.4.1 Spatial Distribution of Secondary Hot Electrons

A multi-step Monte Carlo simulation is performed at a program condition of  $V_{WL}$ =9V and  $V_{BL(N)}$ =4.2V. First, electrons are launched at the source in cell (N-1) and primary impact ionization events are simulated (Fig. 2.7 (a)). It is obvious that most of primary impact ionization events take place near the drain junction where the lateral electric field is the largest. In the second step, holes are launched at primary impact ionization sites and secondary impact ionization events are simulated (Fig. 2.7 (b)). It is found that the secondary impact ionization region extends into the substrate. In the third step, electrons are launched at the secondary impact ionization sites and hot electron injection into both cell (N-1) and cell (N) is simulated (Fig. 2.7 (c)). A random sample of 50 impact ionization events is chosen in Fig. 2.7 (a) and (b). A random sample of 500 secondary hot electrons with energy above 2.6 eV is displayed in Fig. 2.7 (c). It is found that Fig. 2.7 (c) confirms the flowing of some secondary electrons into cell (N), which is the cause of the program disturb.

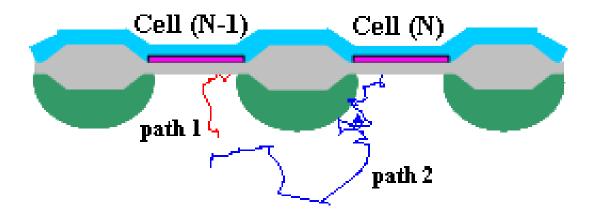

To gain insight into the program disturb path, the Monte Carlo simulated

trajectories of secondary electron injection are shown in Fig. 2.8. For path 1, a generated secondary electron injects into the nitride of cell (N-1), resulting in the increase of V<sub>t</sub> (bit B) in Fig. 2.3 (b). For path 2, a generated secondary electron goes around the  $n^+$  buried diffusion junction and injects into cell (N), resulting in the increase of V<sub>t</sub> (bit C) or V<sub>t</sub> (bit D) in Fig. 2.3 (b).

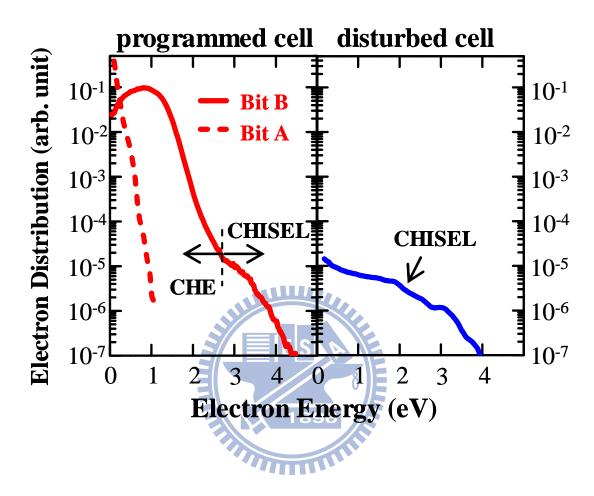

#### 2.4.2 Energy Distribution of Secondary Hot Electrons

Fig. 2.9 shows the simulated electron energy distributions in a programmed cell and a disturbed cell. In a programmed cell, electrons near the drain side (bit B) and near the source side (bit A) are collected separately. As shown in the figure, the bit A follows approximately a Boltzmann distribution. However, the bit B has an apparent high energy tail due to non-equilibrium transport in the high field region. The high energy tail includes both primary hot electrons and secondary hot electrons (see Fig. 2..4). It should be pointed out that the secondary hot electrons (CHISEL) become dominant for energy above 2.6 eV. On the other hand, in a disturbed cell, only secondary hot electrons in the entire channel are accumulated.

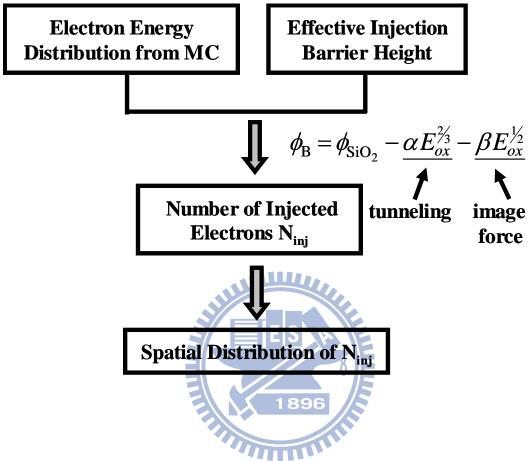

A flow chart for the simulation of hot electron injection is shown in Fig. 2.10. According to [2.12], the effective barrier height,  $\phi_B$ , is expressed as

$$\phi_{B} = \phi_{SiO_{2}} - \alpha E_{ox}^{2/3} - \beta E_{ox}^{1/2}$$

The effective barrier height is lowered after taking into account tunneling  $(\alpha = 1.0 \times 10^{-5} (\text{V cm}^2)^{1/3})$  and image force  $(\beta = 2.59 \times 10^{-4} (\text{V cm})^{1/2})$ .  $E_{ox}$  is the perpendicular oxide field and  $\phi_{SiO2}$  is set to be 3.1 eV. Then, the number of injected hot electrons, N<sub>inj</sub>, can be calculated by counting electrons hitting the SiO<sub>2</sub> and Si

interface with energy above the effective barrier height. Fig. 2.11 shows the effective barrier height as a function of programmed bit  $\Delta V_t$  for two programming word-line voltages. Two points are worth noting. First, as programmed bit  $\Delta V_t$  raises, the effective barrier height increases due to the build-up of program charges in the nitride layer. As a result, in the initial stage of programming, CHE injection is dominant. Then, due to the decrease of CHE significantly during programming, CHISEL injection then becomes dominant. Second, for a larger programming word-line voltage, i.e.  $V_{WL}$ =10.5V, CHE is more dominant in the programming transient and the role of CHISEL is played down, which implies that the program disturb can be alleviated by an appropriate program bias optimization.

We re-plot Fig. 2.3 (b) to Fig. 2.12 (a). Two-stage behavior is observed. In the initial stage of programming, the program disturb is negligible. The charge injection rate in the programmed cell is larger than that in the disturbed cell. The reason is that CHE is dominant in this stage. However, the disturbed bit  $\Delta V_t$  increases drastically for a program bit  $\Delta V_t$  above 3.0V. The reason is that CHISEL becomes dominant in this stage. Fig. 2.12 (b) shows the normalized N<sub>inj</sub> in the disturbed cell during programming from a Monte Carlo simulation. A similar trend from the measurement and simulation is obtained.

After taking into account an electron energy distribution from the Monte Carlo simulation and the effective barrier height, the spatial distribution of N<sub>inj</sub> in the programmed cell and in the disturbed cell is shown in Fig. 2.13 and Fig. 2.15, respectively, at a program level of 3.0V, i.e.  $\Delta V_t$ (bit B)=3.0V. In the programmed cell, the injected charges have a tight distribution near the drain, as shown in Fig. 2.13. The injected charge also affects the threshold voltage of bit A, which is referred to as second bit effect [2.13]. It is found that CHISEL broadens the injected charge

distribution, and thus has an adverse effect on the second bit effect. In other words, the  $\Delta V_t$ (bit A) increases in the programming transient, as shown in Fig. 2.14. Unlike in a programmed cell, however, Fig. 2.15 shows that the injected charges in the disturbed cell spread over the entire channel, that both bits C and D are affected, which is consistent with the experimental result in Fig. 2.12 (a). Furthermore, a larger threshold voltage shift in bit C than in bit D can be realized due to an asymmetrical injected charge distribution towards bit C.

#### 2.4.3 Substrate Bias Effect

The substrate bias effect on the program disturb is characterized in Fig. 2.16 (a). A negative substrate bias in programming enhances the program disturb. The reason is that a negative substrate bias increases the drain-to-substrate voltage drop, which results in an increase of impact ionization events. The trend is also verified by a Monte Carlo simulation in Fig. 2.16 (b). In addition to impact ionization, Fig. 2.17 demonstrates that the substrate bias has a negligible effect on hot electron radiation [2.14], which implies that substrate electron generation via re-absorption of hot electron emitted light should not be a dominant mechanism in the program disturb.

Furthermore, the Monte Carlo simulation shows a broader injected charge distribution in the programmed cell when a negative substrate bias is applied, as shown in Fig. 2.18, which would result in a worsened second bit effect.

#### 2.4.4 Bit-line Depth and Width Effects

The cell or bit-line scaling effects on the program disturb are also evaluated by a Monte Carlo simulation. For cell scaling, a shallower junction depth is required to reduce the short channel effect. A random sample of 500 secondary electrons with energy above 2.6eV is drawn in Fig. 2.19 (a) to represent the spatial distributions for two bit-line depth splits. It is found that a shallower BD junction aggravates the program disturb because the secondary electrons have a larger chance to go around the BD bit-line. The simulated  $N_{inj}$  versus bit-line junction depth is also shown in Fig. 2.19 (b). Nevertheless, it is possible that the program disturb can be reduced in a recessed buried source/drain SONOS memory.

On the other hand, the Monte Carlo simulation shows a strong dependence on a BD bit-line width in Fig. 2.20. The program disturb is more serious in a narrow BD bit-line because secondary electrons have a larger chance to go around the BD bit-line. The  $N_{inj}$  in the disturbed cell increases by two orders as a bit-line width reduces from 0.25µm to 0.1µm. As a consequence, the program disturb becomes a new constraint as the cell/ bit-line scaling advances.

#### 2.4.5 Pocket Implant Effect

In Fig. 2.21, we evaluate the effect of pocket implant on the program disturb. The dosages of two pocket implant splits differ by two times. It is found that, for a higher pocket dose, the secondary impact ionization events increase (i.e. CHISEL increase) due to a larger substrate field, which leads to a larger program disturb. Therefore, it appears that there is a trade-off between the bulk punch-through and the program disturb.

1896

#### 2.5 Summary

In this work, a new program disturb in a scaled BD bit-line SONOS array is demonstrated. Our Monte Carlo simulation confirms that the program disturb is attributed to the impact ionization-generated secondary electrons flowing to a neighboring cell. This program disturb becomes more serious as cell or bit-line scaling advances. The factors affecting the program disturb are summarized in Table 2.2. The characteristics of the program disturb can be well simulated by a Monte Carlo code. Optimization of pocket implant, bit-line geometry and program bias conditions can alleviate this program disturb. The program disturb is one of the main bottlenecks for the scaling of NOR-type flash memory.

**Fig. 2.2** (a) Top view and (b) cross-section of a buried diffusion bit-line SONOS array. The BD width is  $0.12 \ \mu m$  in this work.

Table 2.1 Program bias voltages.  $V_{BL}$  is the bit-line voltage and  $V_{WL}$  is the word-line voltage.

| V <sub>BL(N-1)</sub> | 0V       |  |  |  |

|----------------------|----------|--|--|--|

| V <sub>BL(N)</sub>   | 4.2V     |  |  |  |

| V <sub>BL(N+1)</sub> | Floating |  |  |  |

| VwL                  | 9.0V     |  |  |  |

|                      |          |  |  |  |

**Fig. 2.3** Threshold voltage shifts versus programming time. Bit B in cell (N-1) is a programmed bit, and bits C and bit D in cell (N) are disturbed bits. A reverse read with a bit-line voltage of 1.6V is employed. The bit-line width splits used in this work are (a)  $0.25\mu$ m and (b)  $0.12\mu$ m, respectively.

**Fig. 2.5** Three-step Monte Carlo simulation flow using both electron and hole Monte Carlo codes to simulate secondary hot electrons.

**Fig. 2.6** (a) E-*k* relation used in the Monte Carlo simulation. A pseudo-potential model and a bond-orbital model are used to calculate the conduction band and the valence band structure, respectively. (b) Monte Carlo window includes both a programmed cell and a disturbed cell. The electric field distribution during programming is shown.

**Fig. 2.7** (a) A random sample of 50 primary impact ionization events (denoted by +) from the first step MC simulation. (b) A random sample of 50 secondary impact ionization events (denoted by x) from the second step MC simulation (c) A random sample of 500 secondary electrons (denoted by  $\cdot$ ) with energy above 2.6eV from the third step MC simulation.

Fig. 2.8 Monte-Carlo simulated trajectory of secondary hot electron injection.

**Fig. 2.9** Electron energy distributions in a programmed cell (a) and in a disturbed cell (b). In a programmed cell, electrons near the drain (bit B) and near the source (bit A) are collected separately. Both primary and secondary electrons are counted. In a disturbed cell, secondary electrons in the entire channel are accumulated.

Fig. 2.10 Simulation flow of hot electron injection.

Fig. 2.11 Programmed bit  $\Delta V_t$  dependence on the effective barrier height. The two program word-line voltages are compared. CHISEL is dominant for energy above 2.6eV.

**Fig. 2.12** (a) Disturbed bit  $\Delta V_t$  versus programmed bit  $\Delta V_t$  from measurement. (b) Normalized charge injection in cell (N) versus programmed bit  $\Delta V_t$  from Monte Carlo simulation. Two-stage behavior is observed.

**Fig. 2.13** MC-simulated injected charge distributions along the channel in cell (N-1). The effective oxide barrier height in cell (N-1) is calculated for  $\Delta V_t$  (bit B)=3.0V.

Fig. 2.14  $\Delta V_t$  of bit B and bit A during programming.

Fig. 2.15 MC-simulated injected charge distributions along the channel in cell (N). The effective oxide barrier height in cell (N) is calculated for  $\Delta V_t$ (bit B)=3.0V.

**Fig. 2.16** (a) Measured substrate bias ( $V_b$ ) effect on the program disturb,  $\Delta V_t$ (bit C) versus program time, and (b) simulated  $N_{inj}$  in cell (N), for  $V_b=0V$  and -0.5V.

**Fig. 2.17** Dependence of hot electron light emission spectrum on substrate bias in a nMOSFET [2.14].

**Fig. 2.18** Normalized injected charge distributions along the channel for  $V_b=0V$  and -1.0V. The  $V_b=-1.0V$  has a broader distribution due to secondary electron injection.

$(\mathbf{N}) = (\mathbf{N})^{(1)} (\mathbf{N})^{(2)} (\mathbf{N})^$

**Fig. 2.19** (a) Simulated spatial distribution. A random sample of 500 secondary electrons with energy above 2.6eV is drawn. (b) Dependence of the program disturb on BD bit-line junction depth,  $N_{inj}$ (cell (N)) versus bit-line depth.

Fig. 2.20 Dependence of the program disturb on BD bit-line width,  $N_{inj}$ (cell (N)) versus bit-line width.

Fig. 2.21 Pocket implant dosage effect on the program disturb. The dosages of the two pocket implant splits differ by two times.

## Chapter 3

# A Novel Hot Electron Programming Method in a Buried Diffusion Bit-line SONOS Memory by Utilizing Non-Equilibrium Charge Transport

## 3.1 Preface