# 國立交通大學

電子工程學系 電子研究所碩士班

# 碩士論文

具能量察覺管線化架構可重組混合基底的 快速傅利葉轉換處理器設計

Energy-Aware Pipeline-based Reconfigurable Mixed-Radix FFT/IFFT Processor Design

研 究 生:賴祈成

指導教授:黃 威 教授

中華民國九十五年六月

# 具能量察覺管線化架構可重組混合基底的 快速傅利葉轉換處理器設計

# Energy-Aware Pipeline-based Reconfigurable Mixed-Radix FFT/IFFT Processor Design

研究生:賴祈成 Student:Chi-Chen Lai

指導教授: 黃 威 教授 Advisor: Prof. Wei Hwang

國立交通大學電子工程學系電子研究所項士論文

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical Engineering and Computer Science

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master

in

**Electronics Engineering**

#### **June 2006**

Hsinchu, Taiwan, Republic of China

中華民國九十五年六月

# 具能量察覺管線化架構可重組混合基底的 快速傅利葉轉換處理器設計

學生:賴祈成 指導教授:黃 威 教授

國立交通大學電子工程學系電子研究所碩士班

#### 摘 要

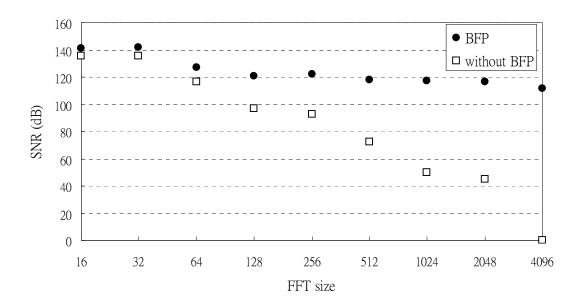

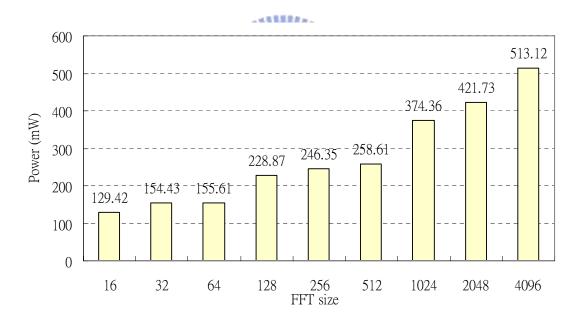

本論文提出一個先進的可重組混合基底的快速傅利葉轉換處理器。該處理器可動態重組為 16 點至 4096 點之快速傅利葉/反向快速傅利葉轉換運算,並且對於不同長度之模式使用不同的混合基底演算法,所提出的架構同時具有能量察覺的特色。不同於一般管線化架構使用較大的內部字長來提高抗雜訊比,我們的架構使用與輸入資料相同的內部字長,並使用區塊浮點的方法來維持抗雜訊比。並且,使用八個平行資料傳輸路徑的管線化架構有效的降低計算週期。

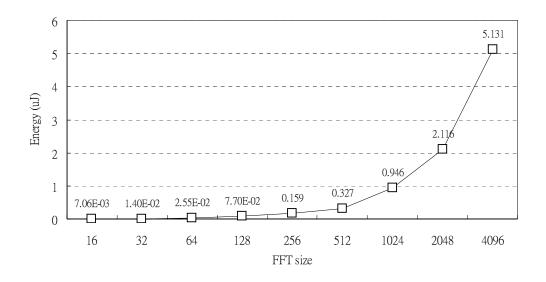

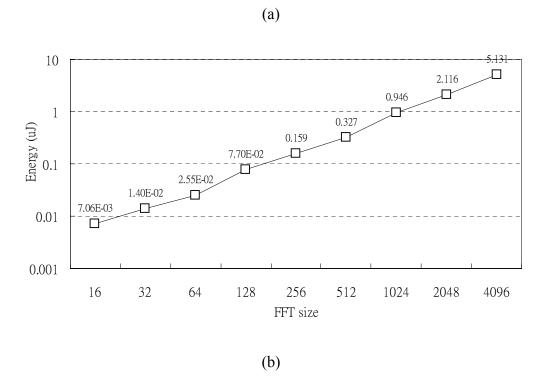

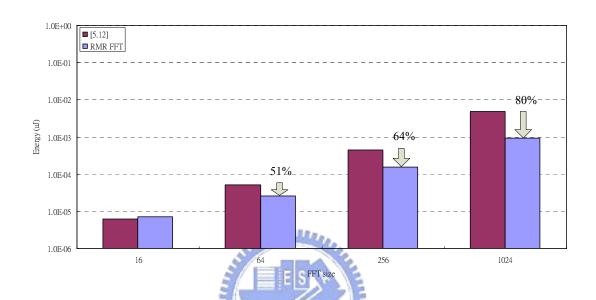

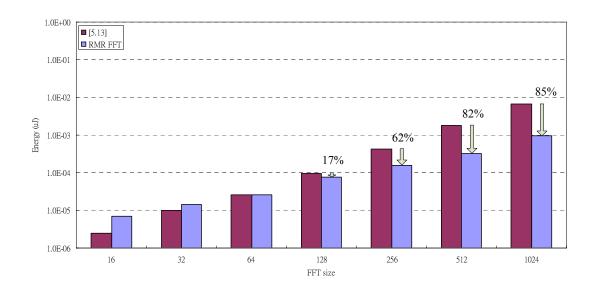

模擬的結果顯示,所提出的快速傅利葉轉換器在不同的資料長度下,能將抗雜訊比維持在 110dB 以上。所提出的快速傅利葉轉換器以 TSMC  $0.13 \mu m$  的技術實現,供應電壓為 1.2V,最高時脈週期為 110MHz,產出率可達四倍時脈週期,亦即 440Msample/s;隨著快速傅利葉轉換運算的長度增加,每筆運算所消耗的能量從 4.34nJ 增加到  $5.115 \mu$ J。

Energy-Aware Pipeline-based Reconfigurable Mixed-Radix FFT/IFFT Processor Design

Student: Chi-Chen Lai

Advisor: Prof. Wei Hwang

Department of Electronics Engineering & Institute of Electronics

National Chiao-Tung University

**ABSTRACT**

In this thesis, we present a novel FFT/IFFT processor, called reconfigurable

mixed-radix (RMR) FFT. It can be easily reconfigured as from 16-point to 4096-point

FFT/IFFT with proper mixed-radix algorithm assigned for each mode. The proposed

architecture is characterized with scalable energy dissipation for different FFT/IFFT

sizes. Unlike general pipeline-based architectures which use a larger internal

wordlength to achieve a high signal-to-noise ratio (SNR), our processor keeps the

internal wordlength the same as the wordlength of the input data while the

block-floating-point (BFP) approach is adopted to maintain the SNR. The

pipeline-based architecture with 8-parallel datapath results in low computation cycles.

The simulation result shows that RMR FFT maintain the SNR above 110dB as

the FFT size varies. The proposed RMR FFT processor is implemented using TSMC

0.13µm technology with a supply voltage of 1.2V. With the maximum clock rate of

110MHz, the throughput rate can reach 440Msample/s, which is 4 times of the input

clock rate. The energy dissipation per FFT ranges from 4.34nJ to 5.115µJ with

increasing FFT sizes.

ii

#### Acknowledgements

I would like to thank my advisor, Prof. Wei Hwang, who has provided me a free research environment for the past two years. He has been supportive all the way, which does help me get rid of the fear of any disturbance in the rear. I was able to think and research independently on interesting topics. I have learned more from these experiences than what books or papers may show.

The fellows of my laboratory also help lot on my study. In addition, they are more helpful on life and many daily events. I have also learned a lot from them and overcome many difficulties with their help.

I would also like to thank my roommates and many schoolmates for the past few years. They have accompanied me a long time and so much has happened. The life in NCTU would be less colorful without them.

## Table of Contents

| Chapte | er 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

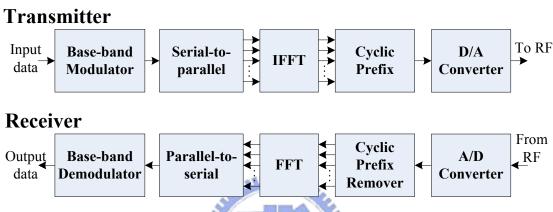

| 1.1    | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1  |

| 1.2    | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1  |

| 1.3    | Organization of Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2  |

| Chapte | er 2 Review of FFT Algorithms and Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4  |

| 2.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4  |

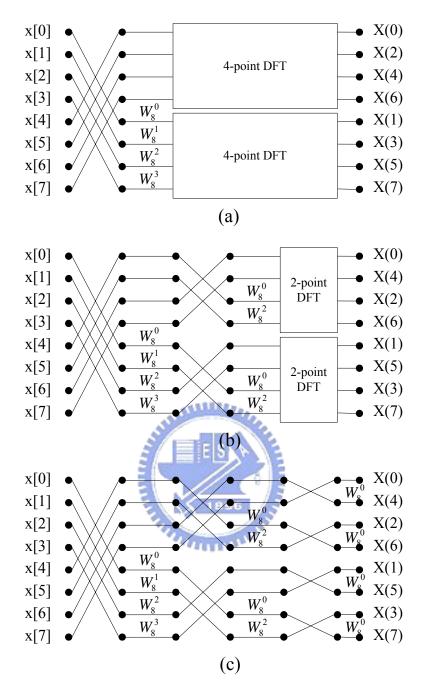

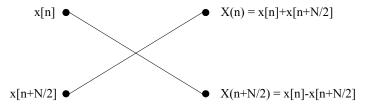

| 2.2    | Basic Concept of FFT Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

| 2.3    | The FFT Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6  |

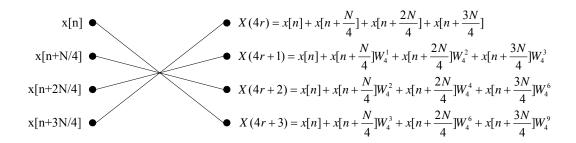

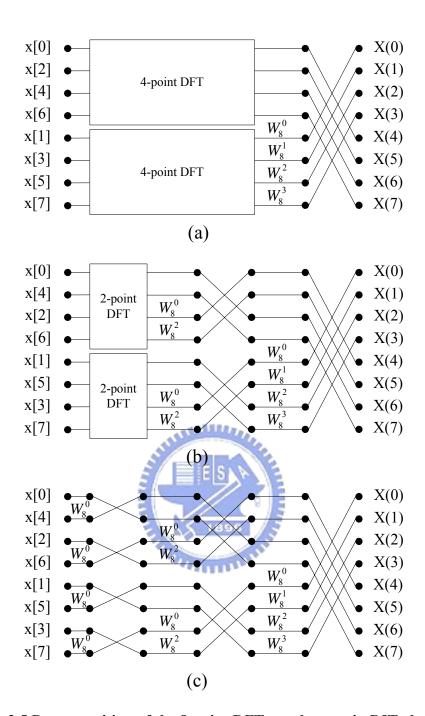

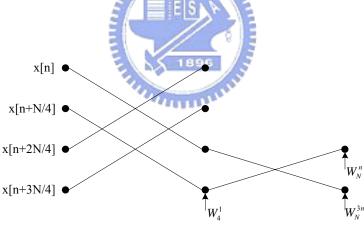

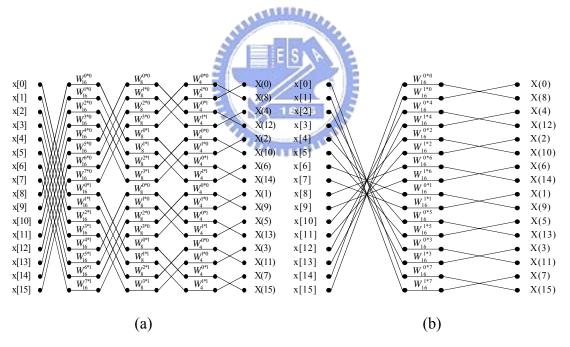

| 2      | .3.1 Decimation-in-Frequency (DIF) Fixed-Radix Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6  |

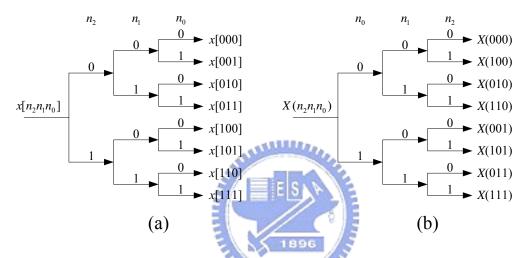

| 2      | .3.2 Decimation-in-Time (DIT) Fixed-Radix Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11 |

| 2      | .3.3 Other FFT Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13 |

| 2.4    | The FFT Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14 |

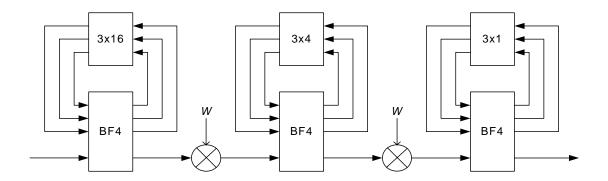

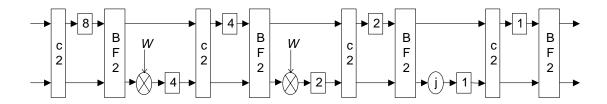

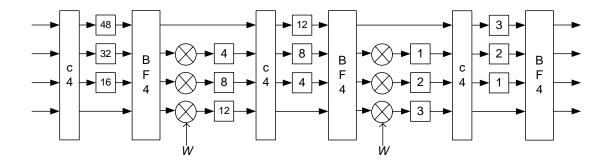

| 2      | .4.1 Pipeline-Based Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15 |

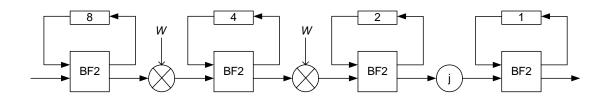

|        | 2.4.1.1 Single-Path Delay Feedback (SDF) Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15 |

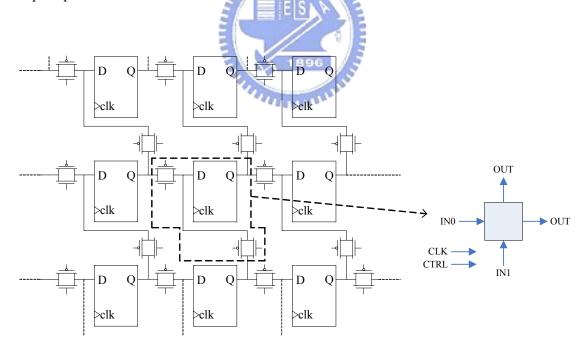

|        | 2.4.1.2 Multiple-Path Delay Commutator (MDC) Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|        | .4.2 Memory-Based Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17 |

| 2      | .4.3 Reconfigurable Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18 |

| 2.5    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20 |

|        | The state of the s |    |

| Chapte | er 3 Algorithm of Reconfigurable Mixed-Radix FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21 |

| 3.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21 |

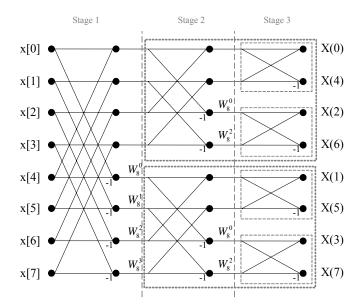

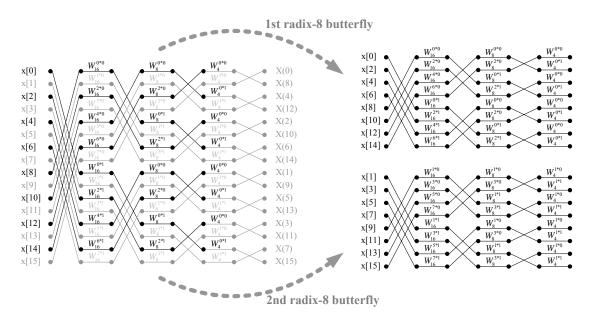

| 3.2    | Reconfigurable Mixed-Radix Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21 |

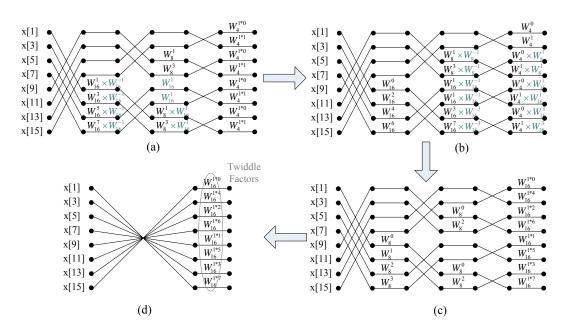

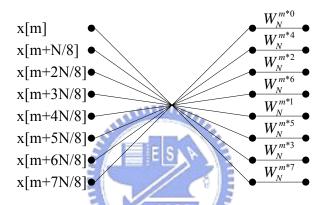

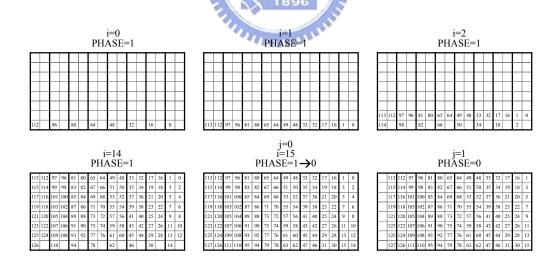

| 3.3    | Data Ordering and Twiddle Factors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25 |

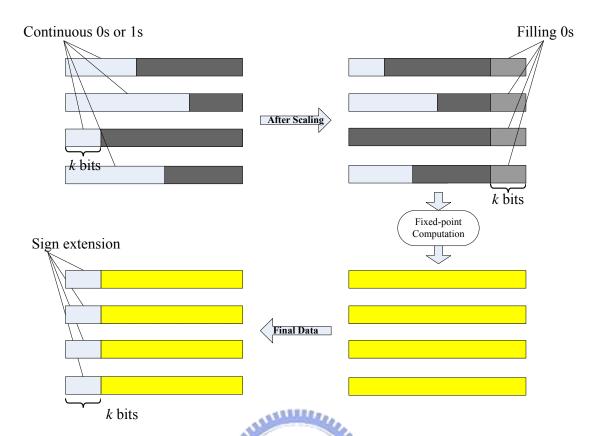

| 3.4    | Finite Register Length Effect and Block-Floating-Point Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30 |

| 3.5    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33 |

| Chapte | er 4 Architecture of Reconfigurable Mixed-Radix FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 4.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

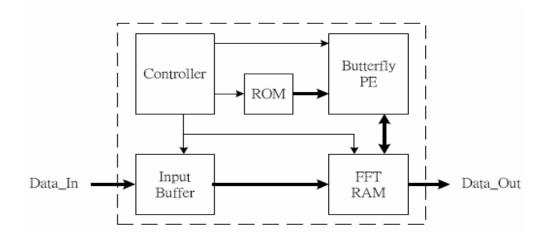

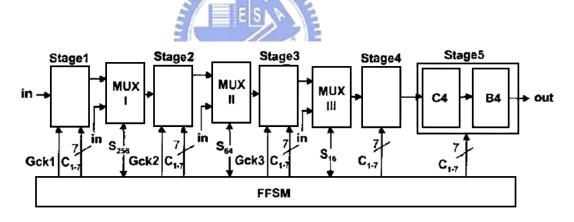

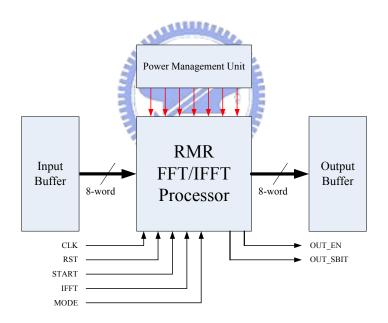

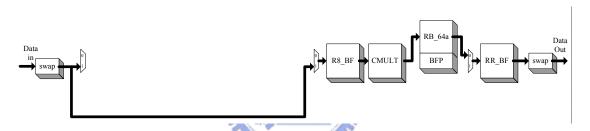

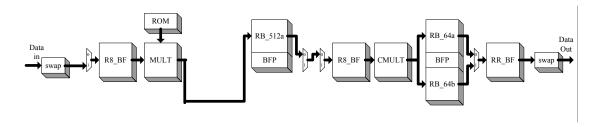

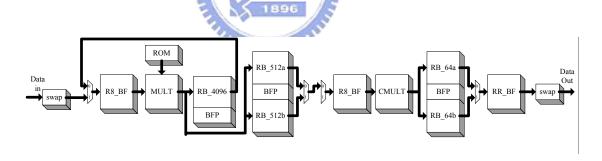

| 4.2    | Overall Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36 |

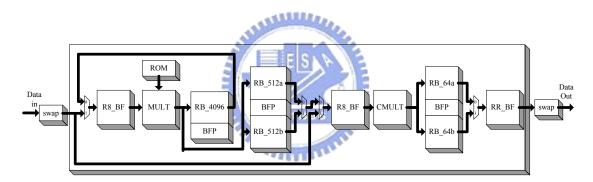

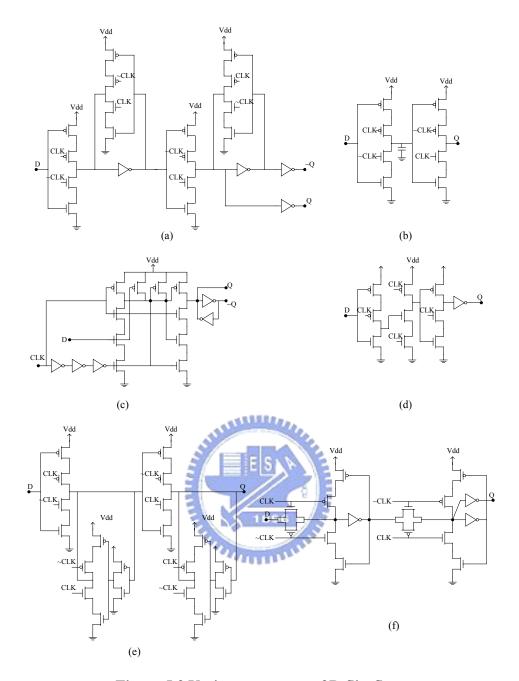

| 4.3    | Architecture Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 37 |

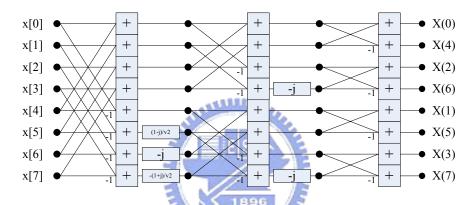

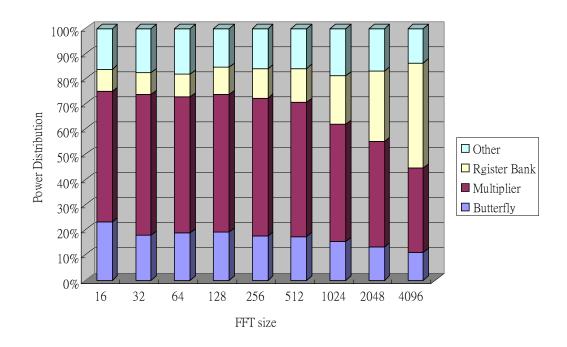

| 4      | .3.1 Butterfly (BF) Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37 |

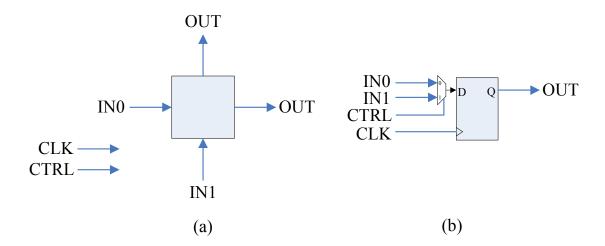

|        | 4.3.1.1 General BF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37 |

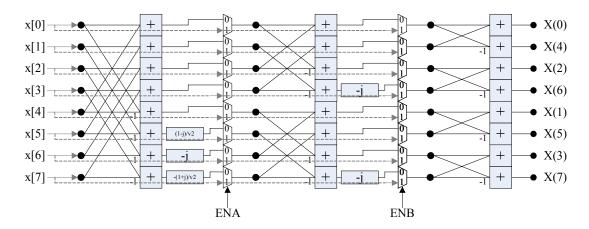

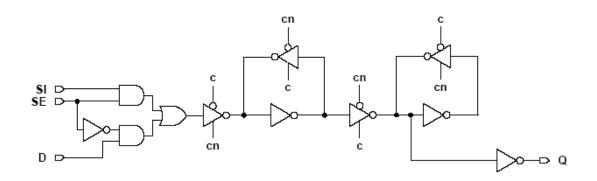

|        | 4.3.1.2 Reconfigurable BF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 38 |

| 4      | -3.2 Multiplier Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

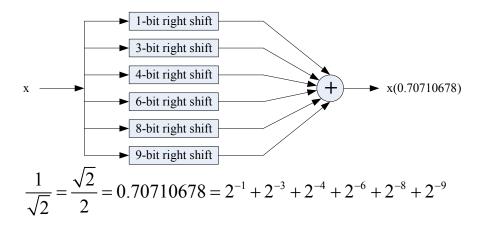

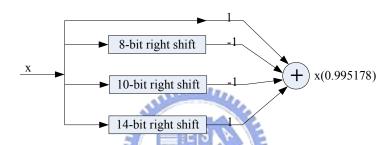

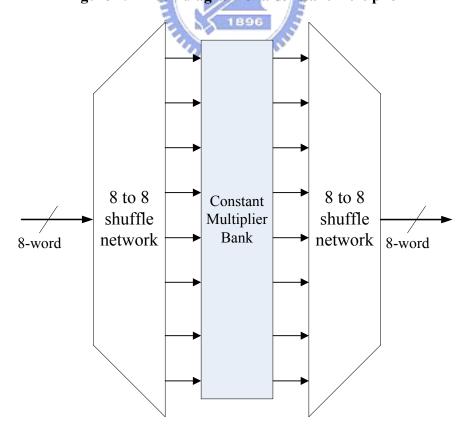

|        | 4.3.2.1 Constant Multiplier Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39 |

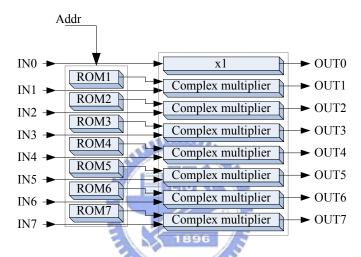

| 4.3.2.2 Complex Multiplier Approach                | 43 |

|----------------------------------------------------|----|

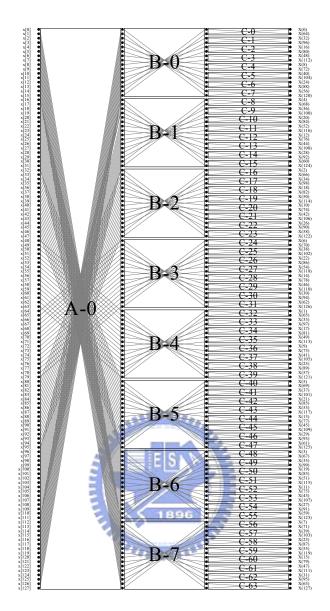

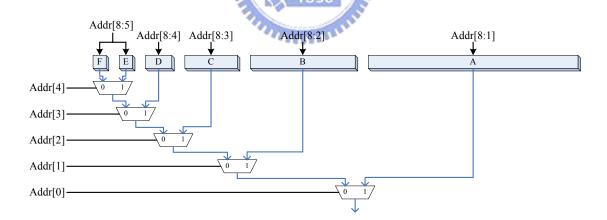

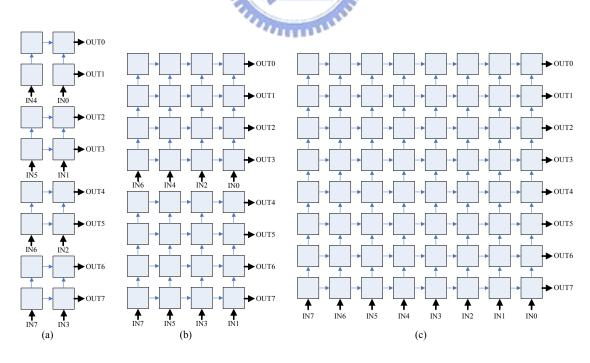

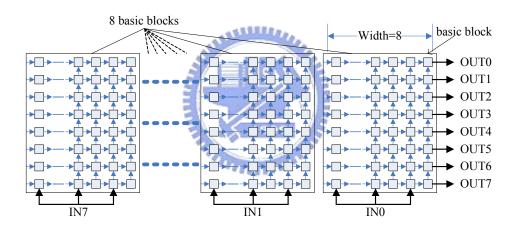

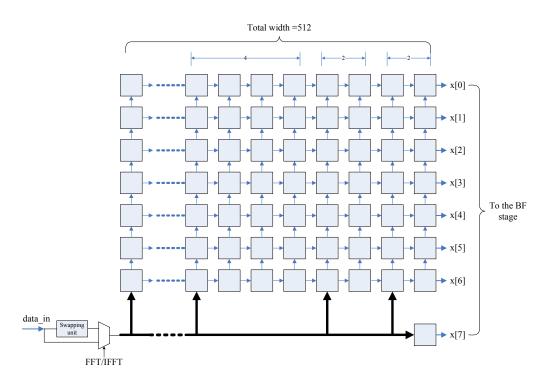

| 4.3.3 Register Banks (RB)                          | 45 |

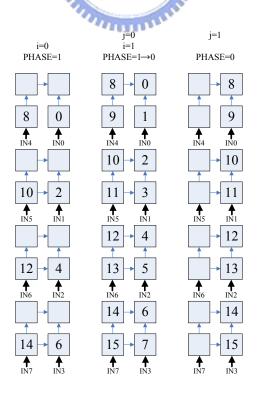

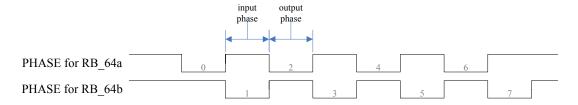

| 4.3.3.1 RB_64                                      | 46 |

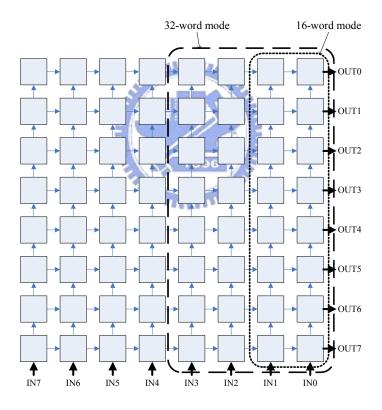

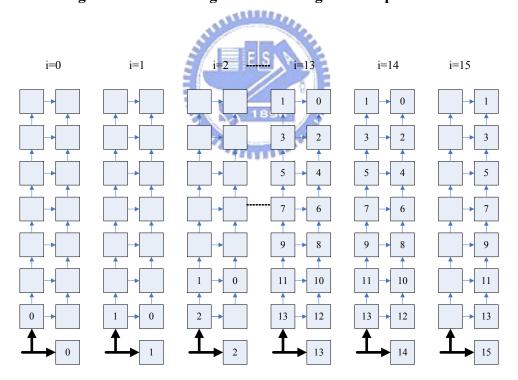

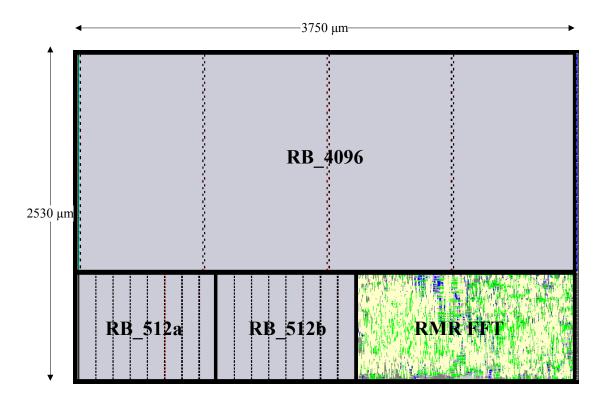

| 4.3.3.2 RB_512 and RB_4096                         | 48 |

| 4.3.3.3 Duplicate Module Insertion                 | 51 |

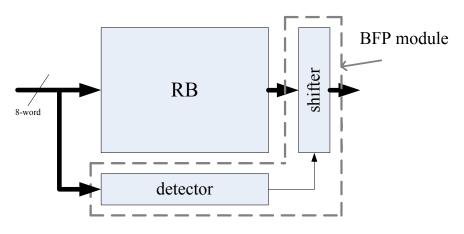

| 4.3.4 BFP                                          | 52 |

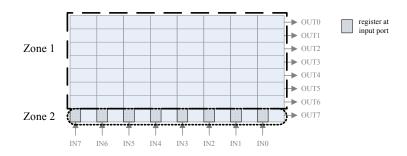

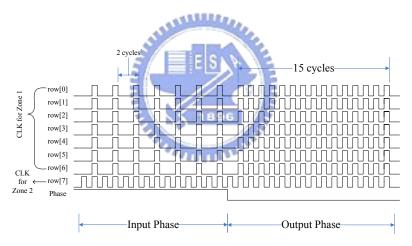

| 4.3.5 Input/Output Buffer                          | 53 |

| 4.4 Data Flow                                      | 55 |

| 4.5 Conclusion                                     | 58 |

|                                                    |    |

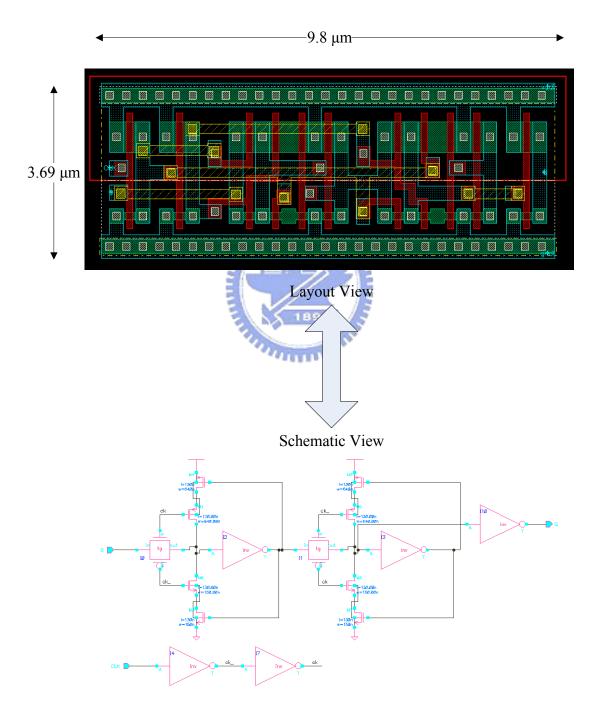

| Chapter 5 Implementation of RMR FFT/IFFT Processor | 59 |

| 5.1 Introduction                                   | 59 |

| 5.2 Implementation Issue on Register Banks         | 59 |

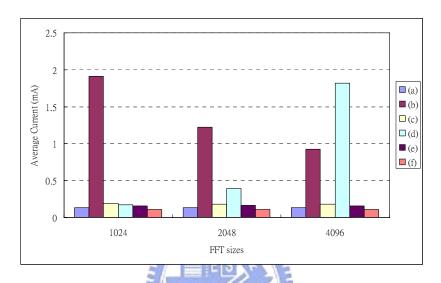

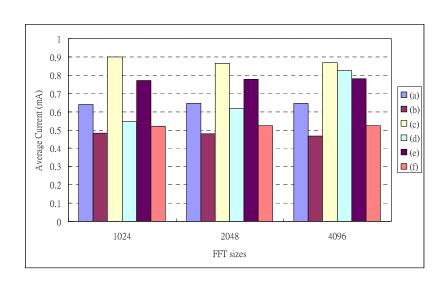

| 5.3 Power Control                                  | 64 |

| 5.4 Simulation Result                              | 66 |

| 5.4.1 Performance of the RMR FFT                   | 66 |

| 5.4.2 Comparison                                   | 69 |

| 5.5 Layout Implementation                          | 72 |

| 5.6 Conclusion ES                                  | 77 |

|                                                    |    |

| Chapter 6 Conclusions and Future Work              | 72 |

| 6.1 Conclusions                                    | 79 |

| 6.2 Future Work                                    | 80 |

|                                                    |    |

| References                                         | 81 |

# List of Tables

| TABLE 3.1 | Mixed-radix algorithms for different FFT sizes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |

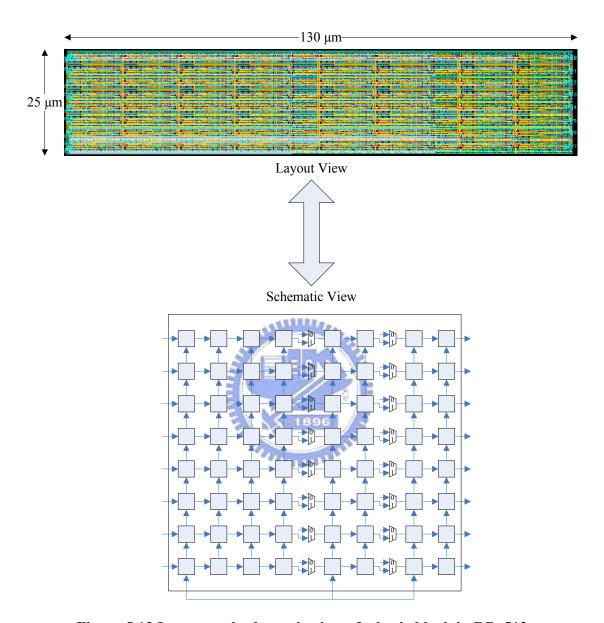

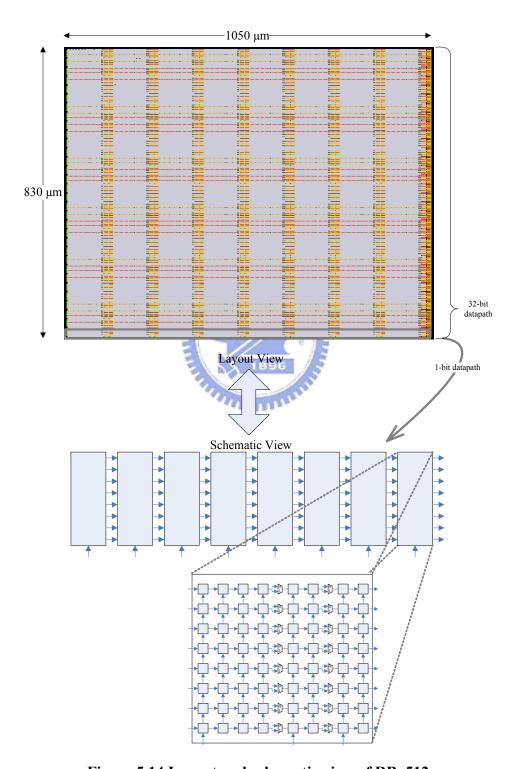

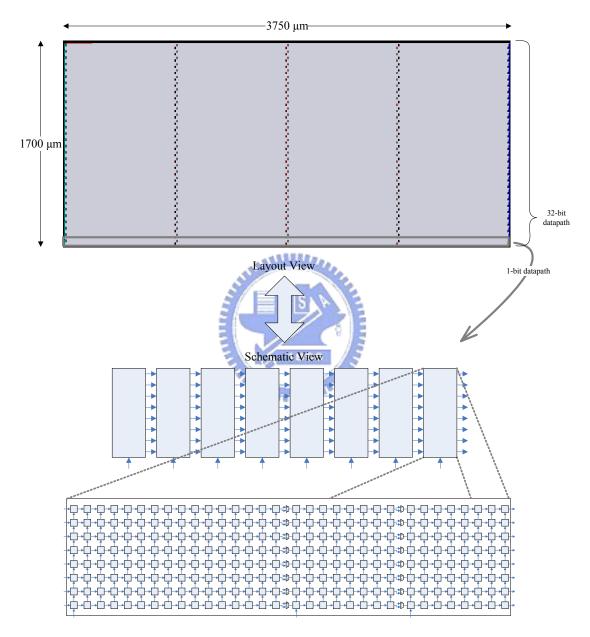

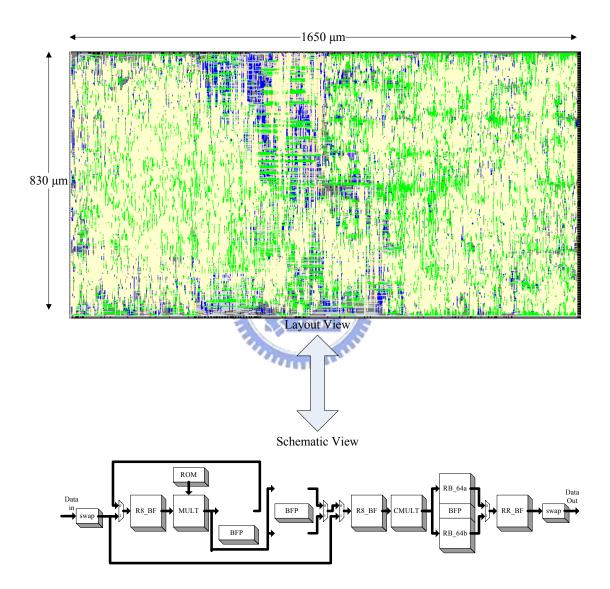

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|