# Charge Storage Characteristics of Mo Nanocrystal Memory Influenced by Ammonia Plasma Treatment

Chao-Cheng Lin,<sup>a</sup> Ting-Chang Chang,<sup>b,\*,z</sup> Chun-Hao Tu,<sup>a</sup> Wei-Ren Chen,<sup>a</sup> Chih-Wei Hu,<sup>a</sup> Simon M. Sze,<sup>a</sup> Tseung-Yuen Tseng,<sup>a</sup> Sheng-Chi Chen,<sup>c</sup> and Jian-Yang Lin<sup>c</sup>

<sup>a</sup>Institute of Electronics, National Chiao Tung University, Hsin-Chu 300, Taiwan

Mo nanocrystal memory was fabricated through annealing the oxygen-incorporated Mo and Si layers. We then investigated the influence an of ammonia plasma treatment on the nonvolatile memory characteristics of a charge storage layer composed of Mo nanocrystal memory embedded in  $SiO_x$ . Transmission electron microscopy revealed the nanostructure of the charge storage layer, and X-ray photoelectron spectra analyses revealed that nitrogen was incorporated into the charge storage layer. Electric analyses indicated that the memory window reduced, and both retention and endurance improved after the treatment. The reduction in the memory window was attributed to the decrease in charge trapping centers in the surrounding oxide after the treatment. The improvement of retention was interpreted in terms of the nitrogen passivation of traps in the oxide around the Mo nanocrystals. The robust endurance characteristic was attributed to the improvement of the quality of the surrounding oxide by nitrogen passivation.

© 2009 The Electrochemical Society. [DOI: 10.1149/1.3155446] All rights reserved.

Manuscript submitted February 27, 2009; revised manuscript received May 8, 2009. Published July 10, 2009.

Nonvolatile memory composed of a floating structure plays an important role in portable devices such as cell phones, notebook computers, and digital cameras. However, conventional floating structure confronts a bottleneck on the reduction in tunnel oxide in the memory structure because carriers stored in an electrical continuously conducting polycrystalline silicon floating gate totally lose if one defect chain exists in the tunnel oxide. 1,2 The nanocrystals embedded in dielectric as charge storage centers in the floating gate structure has attracted much attention for next-generation nonvolatile memory because carriers stored in electrically isolated nanocrystals can suppress carrier loss. 2 Several methods have been investigated to fabricate nanocrystals such as ion implantation, <sup>3,4</sup> sputtering, <sup>5,6</sup> and oxidation. <sup>7,8</sup> It is expected that those processes can induce defects or traps in the dielectric around nanocrystals during the fabrication process. The induced deficiency in the surrounding dielectric can lead to stored charges leaking out of the nanocrystals through trap-assisted tunneling. Therefore, the quality of the surrounding oxide, which electrically isolates the nanocrystals, is an important issue in research on nanocrystal memory. Two possible ways to gain good reliability are improving the surrounding oxide of the nanocrystal by using a hydrogen treatment with a high pressure at high temperature ( > 900°C) and nitrogen annealing at high temperature ( > 1000°C). However, the Si-H bond is weak and easily to be broken during endurance tests. For the nitrogen annealing, a high temperature process (> 1000°C) is required to dissociate the nitrogen to strengthen the surrounding oxide layer. <sup>10,11</sup> Therefore, the process is not appropriate for application in semiconductor industry and for nanocrystal memory in terms of thermal budget.

In this study, Mo nanocrystal memory was fabricated through annealing the oxygen-incorporated Mo silicide layer. We investigated the effect of ammonia (NH<sub>3</sub>) plasma treatment on memory characteristics of the Mo nanocrystal embedded in  $\mathrm{SiO}_x$  as the charge storage layer. The plasma-enhanced process is widely used in the semiconductor industry for its benefit with regard to small thermal budget, which is important for integrated circuit technology because the thermal budget may lead to the redistribution of source/drain dopant or density and size of the nanocrystal. Furthermore, the NH<sub>3</sub> plasma treatment technique has been investigated to improve

the quality of gate dielectric. <sup>13,14</sup> Our experimental results show that the memory characteristics including memory window, retention, and endurance were influenced by the incorporation of nitrogen into the surrounding oxide.

### **Experimental**

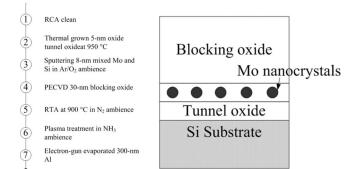

The experimental process flow and memory structure is shown in Fig. 1. The memory cells were fabricated on 6 in. p-type Si substrate. After the substrate was cleaned by a standard RCA process, a 5 nm thick dry oxide layer was grown at 950°C on the substrate in a horizontal furnace. An 8 nm thick Mo silicate layer was then deposited on the oxide layer using cosputtering Mo and Si in Ar (24 sccm)/O (2 sccm) ambience. 30 nm thick Si oxide was deposited on the Mo silicate layer as the blocking oxide by plasmaenhanced chemical vapor deposition (PECVD) at 300°C. The thermal annealing process was performed in N2 ambience at 900°C for 60 s to form Mo nanocrystals embedded in SiO<sub>x</sub>. Cells were subsequently treated with NH<sub>3</sub> plasma in the PECVD chamber for 30 min with an NH<sub>3</sub> gas flow rate of 20 sccm and a chamber pressure of 67 Torr at a power of 50 W. For the electrical characteristic measurement, 500 nm thick Al was thermally evaporated with a shadow mask on the blocking oxide to form the metal-oxide-semiconductor (MOS) structure. The nanostructure of Mo nanocrystals was ana-

## **Process Flow**

Figure 1. Process flow and memory structure of this work.

<sup>&</sup>lt;sup>b</sup>Department of Physics, Center for Nanoscience and Nanotechnology, National Sun Yat-Sen University, Kaohsiung 804, Taiwan

<sup>&</sup>lt;sup>c</sup>Graduate School of Opto-Electronic Engineering, National Yunlin University of Science and Technology, Yunlin 64002, Taiwan

<sup>\*</sup> Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: tcchang@mail.phys.nsysu.edu.tw

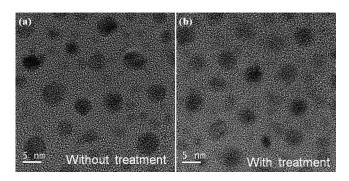

Figure 2. Plane-view TEM image of the sample (a) without and (b) with the plasma treatment.

lyzed through a transmission electron microscope. The chemical bonding and composition of the charge storage layer were analyzed with X-ray photoemission spectroscopy (XPS). Electrical characteristics were measured using a Keithley 4200 and HP 4284 precision LCR meter with a frequency of 1 MHz.

#### **Results and Discussion**

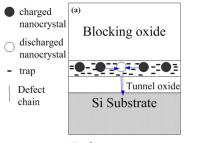

Figure 2a and b shows the transmission electron microscopy (TEM) for the charge storage layer with and without the plasma treatment. The average size and density of both samples are estimated at about 4–5 nm and  $10^{12}$  cm<sup>-2</sup>. A density as high as  $10^{12}$  cm<sup>-2</sup> is a basic requirement for nanocrystal memory to prevent the variation in memory characteristics between cells during reduction in the nonvolatile memory structure. In this case, however, the high density results in the thickness of the surrounding oxide, which electrically isolates nanocrystals, being only 4–5 nm, as shown in Fig. 2. Therefore, if traps exist in the oxide, this can result in a serious tunnel process of the stored carriers between nanocrystals (trap-assisted tunnel mode).

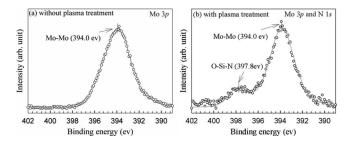

In our previous study, the oxide surrounding the Mo nanocrystal was deficient (oxygen deficiency). <sup>12</sup> Figure 3 shows XPS Mo 3p and N 1s spectra of the charge storage layer (a) without and (b) with the plasma treatment, both performed by using a monochromatic Al K $\alpha$  (1486.6 eV) X-ray. An additional XPS peak (397.8 eV) appears in Mo 3p and N 1s spectra of the charge storage layer after the plasma treatment due to the formation of O–Si–N bonds. This suggests that the incomplete bonds in SiO $_x$  bonded with nitrogen after the plasma treatment, as shown in Fig. 3. <sup>15</sup>

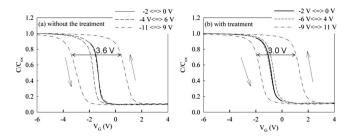

Figure 4a and b shows the *C-V* curves of the MOS structure embedded with the Mo nanocrystal for the sample with and without the plasma treatment, respectively. At the smaller sweeping voltage of 2 V, there is a negligible memory window in Fig. 4a and b corresponding to the quasi-neutral state (i.e., no charge is stored in the charge storage layer under this sweeping range). At the larger sweeping voltages (–11 to 9 V and vice versa), there are counterclockwise memory hystereses, as evident in Fig. 4a and b. The coun-

**Figure 3.** Mo 3p and N 1s core-level spectra of the charge storage layer composed of Mo nanocrystals embedded in  $SiO_x$  (a) without and (b) with the plasma treatment.

Figure 4. C-V curves of the MOS structure without and with the plasma treatment.

terclockwise hystereses are due to carrier transport through tunnel oxide between the charge storage layer and the Si substrate. The memory windows were reduced (0.6 V reduction) for the sample with the plasma treatment. The reduction in the memory window after the treatment was related to the nitrogen passivation in the charge storage layer. It has been suggested that the traps in the oxide around nanocrystals can capture carriers and contribute to the memory window. <sup>12</sup> According to XPS results, nitrogen was incorporated into the oxide around the Mo nanocrystals after the treatment. The incorporated nitrogen can passivate the traps in the oxide, which reduce the charge storage centers in the surrounding oxide, leading to the smaller memory window.

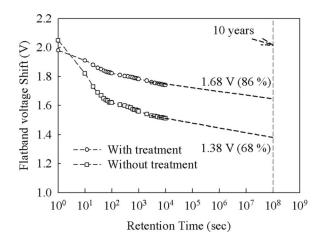

Figure 5 is a comparison of retention behavior for the samples with and without the plasma treatment, respectively. Retention was measured at a stress voltage of  $10\ V$  on the Al gate electrode for  $5\ s$ . The memory window was obtained by comparing the C-V curves between the charged state and the quasi-neutral state. When carriers are stored in the nanocrystals, the stored carriers raise the potential energy of the nanocrystals and increase escape probability of the stored carriers. Furthermore, carriers trapped in the shallow traps are unstable and can easily leak back to the silicon substrate. Figure 5 shows that for retention time before 10<sup>2</sup> s, the charge loss rate is significant, becoming stable over a longer retention time. This result is inconsistent with partial carriers trapping in the shallow trap states of the SiO<sub>x</sub> matrix around the nanocrystals. Because the decline rate of the flatband voltage after 10<sup>2</sup> s retention time is stable, the reduction rate of the flatband voltage has an exponential dependence on retention time according to the one-dimensional direct tunneling Therefore we can extrapolate the retention characteristics to 10 years with a slope of the stable range

Figure 5. The retention behavior of MOS structures with and without the plasma treatment.

Before treatment

After treatment

Figure 6. (Color online) Schematic explanation of the retention behavior for the sample (a) before and (b) after the plasma treatment.

$$m = \frac{V_{\text{FB2}} - V_{\text{FB1}}}{\log t_2 - \log t_1}$$

where  $V_{\rm FB1}$  and  $V_{\rm FB2}$  are the flatband voltage shifts at retention times of  $10^2$  s  $(t_1)$  and  $10^4$  s  $(t_2)$ , respectively. A 1.4 V memory window (charge remaining at 68%) can be obtained after 10 years by analyzing the extrapolation value of retention data. In contrast, the charge loss rate of the sample after the treatment is slower than that without the treatment, with the memory window remaining at 86%. The superior retention of the sample with the treatment can be explained by the nitrogen passivation of the traps in the oxide around Mo nanocrystals, schematically expressed in Fig. 6. When carriers are stored in nanocrystals after programming, if there is a defect chain in the tunnel oxide, the nanocrystal that aligns with the defect chain is discharged immediately. As shown in Fig. 6a for the sample without the plasma treatment, the carriers stored in the neighbor nanocrystals can escape to the discharged nanocrystal by assistance of traps (trap-assisted tunneling) in the surrounding oxide, which results in a faster loss rate of the stored carriers. For the sample with the plasma treatment, the traps in the surrounding oxide were reduced by nitrogen passivation. The trap-assisted lateral migration of the stored carriers was suppressed, which improves the retention of the memory structure, as shown in Fig. 6b.

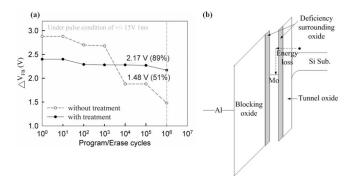

Figure 7a is the comparison of the endurance characteristics of the samples with and without the plasma treatment under pulse conditions of  $V_G = \pm 15 \text{ V}$  for 1 ms, respectively. For the sample without the plasma treatment, the  $\Delta V_{\mathrm{FB}}$  (the difference between programming and erase states) was reduced significantly, remaining 51% after 106 program/erase cycles. However, the plasma-treated sample exhibits a robust endurance characteristic ( $\Delta V_{\rm FB}$  of 89% after 10<sup>6</sup> program/erase cycles). Previously the  $\Delta V_{\rm FB}$  reduction during such an endurance test was due to the degradation of the gate oxide. 13 Carriers tunneling from the substrate into the charge storage layer during the endurance test can release energy to destroy the

Figure 7. (a) Endurance characteristic of the MOS structures without and with the plasma treatment and (b) band diagram of carrier transport during the electron tunnel.

Table I. Comparison of the memory characteristics of our experiment result with those of Si nanocrystal memory in recent

| Reference                               | Memory window (V) | Retention (%) |

|-----------------------------------------|-------------------|---------------|

| This study                              | 3                 | 86            |

| This study<br>Laha et al. <sup>16</sup> | 1.5               | 50            |

| Kuan et al. <sup>17</sup>               | 1                 | < 50          |

| Porti et al. 18                         | 1.4               | 30            |

surrounding dielectric (Fig. 7b), which results in the reduction in the  $\Delta V_{\rm FB}$ . For the sample without the plasma treatment, there are several weak or dangling bonds in the surrounding oxide induced during the formation of nanocrystals. The bonds can easily break during the programming/erase cycles, leading to a faster degradation rate of the surrounding oxide. After the plasma treatment, because the traps were reduced, and the surrounding oxide was strengthened by the nitrogen incorporation, the generation rate of traps reduced, resulting in the better endurance characteristic.

Table I compares the memory characteristics of our experimental result with those of Si nanocrystal memory in recent research. The NH<sub>3</sub> plasma-treated Mo nanocrystal memory has a large memory window and good retention, and is suitable for nonvolatile memory application. <sup>17-19</sup>

#### Conclusion

The nonvolatile memory characteristics of the Mo nanocrystals were influenced by ammonia plasma treatment. The C-V hysteresis reduced from 3.6 to 3.0 V due to a reduction in trapping centers in the surrounding oxide. The retention characteristic improved from 68 to 86% remaining charges after the plasma treatment because the carriers' lateral migration between nanocrystals was suppressed through the nitrogen passivation of the traps in the surrounding oxide. The incorporation of nitrogen into the charge storage layer through the NH3 plasma treatment can strengthen the endurance characteristic of Mo nanocrystal memory. These results suggest the promising usage of NH3 plasma treatment to passivate the surrounding oxide of nanocrystals in the next generation of floating gate flash memory devices.

#### Acknowledgments

This work was performed at National Science Council Core Facilities Laboratory for Nano-Science and Nano-Technology in Kaohsiung-Pingtung area and was supported by the National Science Council of the Republic of China under contract no. NSC-97-3114-M-110-001 and no. NSC 97-2112-M-110-009-MY3.

National Sun Yat-Sen University assisted in meeting the publication costs of this article.

#### References

- 1. D. Kahng and S. M. Sze, Bell Syst. Tech. J., 46, 1288 (1967).

- S. Tiwari, F. Rana, K. Chan, H. Hanafi, W. Chan, and D. Buchanan, *Tech. Dig. Int. Electron Devices Meet.*, **1995**, 521.

- Y. C. King, T.-J. King, and C. Hu, IEEE Trans. Electron Devices, 48, 696 (2001).

- C. Y. Ng, T. P. Chen, L. Ding, M. Yang, J. I. Wong, P. Zhao, X. H. Yang, K. Y. Liu,

- M. S. Tse, A. D. Trigg, et al., *IEEE Trans. Electron Devices*, **53**, 730 (2006). V. Ho, L. W. Teo, W. K. Choi, W. K. Chim, M. S. Tay, D. A. Antoniadis, E. A. Fitzgerald, A. Y. Du, C. H. Tung, R. Liu, et al., *Appl. Phys. Lett.*, **83**, 3558 (2003). K. I. Han, Y. M. Park, S. Kim, S. H. Choi, K. J. Kim, I. H. Park, and B. G. Park,

- IEEE Trans. Electron Devices, 54, 359 (2007) L. W. Teo, W. K. Choi, W. K. Chim, V. Ho, C. M. Moey, M. S. Tay, C. L. Heng,

- Y. Lei, D. A. Antoniadis, and E. A. Fitzgerald, *Appl. Phys. Lett.*, **81**, 3639 (2002). J. K. Kim, H. J. Cheong, Y. Kim, J. Yi, H. J. Bark, S. H. Bang, and J. H. Cho, *Appl.*

- Phys. Lett., 82, 2527 (2003). M. Houssa, M. Tuominen, M. Naili, V. Afanas'ev, A. Stesmans, S. Haukka, and M.

- M. Heyns, J. Appl. Phys., 87, 8615 (2000).

G. Taraschi, S. Saini, W. W. Fan, and L. C. Kimerling, J. Appl. Phys., 93, 9988 (2003).

- 11. C. H. Tu, T. C. Chang, P. T. Liu, H. C. Liu, S. M. Sze, and C. Y. Chang, Appl. Phys. Lett., 89, 162105 (2006).

- C. C. Lin, T. C. Chang, C. H. Tu, W. R. Chen, C. W. Hu, S. M. Sze, T. Y. Tseng, S. C. Chen, and J. Y. Lin, Appl. Phys. Lett., 93, 222101 (2008).

C. Busseret, A. Souifi, T. Baron, S. Monfray, N. Buffet, E. Gautier, and M. N. Semeria, Mater. Sci. Eng., C, 19, 237 (2002).

P. Pavan, R. Bez, P. Olivo, and E. Zanoni, Proc. IEEE, 85, 1248 (1997).

Z. H. Lu, S. P. Tay, R. Cao, and P. Pianetta, Appl. Phys. Lett., 67, 2836 (1995).

W. Guan, S. Long, M. Liu, Q. Liu, Y. Hu, Z. Li, and R. Jia, Solid-State Electron.

- 806 (2007).

A. Laha, D. Kühne, E. Bugiel, A. Fissel, and H. J. Osten, Semicond. Sci. Technol., 23, 085015 (2008).

Y. Kuang, Y. Li, D. Wu, Z. Yu, R. Tang, and R. Huang, in IEEE Nanoelectronics Conference, IEEE, p. 24 (2008).

M. Porti, M. Avidano, M. Nafría, X. Aymerich, J. Carreras, O. Jambois, and B. Garrido, J. Appl. Phys., 101, 064509 (2007).