國立交通大學

工學院半導體材料與製程設備學程

碩士論文

高電場下金原子遷移造成之液晶顯示器

驅動晶片失效之研究

Gold migration under high electrical field

in Liquid Crystal Display Driver Integrated Circuit

研究生：楊宗銘

指導教授：陳 智 博士

中華民國九十八年六月

高電場下金原子遷移造成之液晶顯示器驅動晶片失效之研究

**Gold migration under high electrical field in Liquid Crystal Display

Driver Integrated Circuit**

研究 生：楊宗銘

Student: Tsung-Ming Yang

指 導 教 授：陳 智

Advisor: Chih Chen

國 立 交 通 大 學

工 學 院 半 導 體 材 料 與 製 程 設 備 學 程

Submitted to Institute of Semiconductor Material and Process Equipment

College of Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in

Program of Semiconductor Material and Process Equipment

June 2009

Hsinchu, Taiwan, Republic of China

中 華 民 國 九 十 八 年 六 月

# 高電場下金原子遷移造成之液晶顯示器

## 驅動晶片失效之研究

學生：楊宗銘

指導教授：陳智 博士

國立交通大學

工學院半導體材料與製程設備學程

### 摘要

隨著人類對於聲光影像的娛樂品質需求不斷提升，近年來 Liquid Crystal Display(LCD)顯示面板快速地取代傳統的陰極射線管螢幕，同時對於顯示面板的色彩飽和度、反應速度和解析度等功能性需求快速地提高，使得控制 LCD 面板像素和反應速度的 LCD Driver Integrated Circuit，在內引腳間距上加速地往微間距(Fine pitch)發展，同時對於 LCD Driver IC 在封裝後的可靠性要求更加嚴謹。而在可靠度的議題上，金離子遷移所造成的品質失效問題，因現階段無法完全避免，且生產檢測中無法查覺，須待產品使用一段時間後才會失效，因而更彰顯其重要性。故本實驗主要以模擬 LCD Driver IC 品質失效的真因是由於金離子遷移所造成，同時針對其所發生金離子遷移的必需機制過程做觀察說明，以利後續預防對策的提出。

# **Gold migration under high electrical field in Liquid Crystal Display Driver Integrated Circuit**

Student: Tsung-Ming Yang

Advisor: Dr. Chen Chih

National Chiao Tung University

## **Abstract**

As the demand of audio/video entertainment quality rising rapidly, Liquid Crystal Display panel speedily replace the traditional Cathode Ray Tube screens in recent years simultaneously the functional demands of display panel for the color saturation, reaction speed and resolution enhance quickly makes the Inner Lead Bonding pin spacing development on accelerated manner to micro pitch (Fine pitch) through its control of LCD panel pixels and the reaction speed of LCD Driver Integrated Circuit; at the same time the requirement of LCD Driver IC package became more strictly.

In the reliability issues, since the Gold migration caused by failure of quality problem cannot be totally avoided at this stage; and cannot be detected on time in the productive detection until the production be used for a period then became failure, it demonstrates the important of reliability.

Therefore, the experiment is based on the realistic LCD Driver IC quality failures caused by Gold migration, and for the process to do the necessary observation shows the follow-up prevention.

## 致 謝

細細分析一份論文完成，從物理學的觀點來說，每一個成份，每一個擷取出的元素盡是充滿感謝；從化學的觀點來看，文中的字字句句都是希冀能將畢生的所學盡一已所能地升華成造福人群的知識。四年前，在出社會將近5年；累積了些半導體的實務經驗後，工作上仍是遇到了瓶頸；除了有感於自身現有的知識的不足，亦希望能透過在職專班師資及各界同學的交流，更進一步了解半導體產業的現況。

我首先要感謝交通大學、半導體專班的各授課老師，最重要地更要感謝指導教授陳智博士的悉心教導，經由幾次的訪談，讓我從原本毫無進展的論文；慢慢地理出頭緒，找到方向。這中間也曾因工作調至大陸的緣故，論文一度中斷萌生放棄的念頭；要再次感謝陳智教授的鼓勵與提點，讓我有繼續的原動力。

再來要感謝我在工作上的夥伴，周崇銘、陳國禎、孔祥林等，有了他們工作上的協助與分擔，讓我在百忙的瑣事之中可以抽空靜下心來撰寫論文。

最後要感謝我的太太、家人及朋友，他們默默的陪伴與支持成了最佳的推手，推著我不斷向前，直至終點。

# 目 錄

|                                                                  |      |

|------------------------------------------------------------------|------|

| 摘要.....                                                          | I    |

| Abstract.....                                                    | II   |

| 誌謝.....                                                          | III  |

| 目錄.....                                                          | IV   |

| 圖目錄.....                                                         | VI   |

| 表目錄.....                                                         | VIII |

| <br>                                                             |      |

| 第一章 緒論.....                                                      | 1    |

| 1-1 Liquid Crystal Display Driver Integrated Circuit 封裝技術簡介..... | 1    |

| 1-1.1 TCP(Tape Carrier Package)捲帶式封裝.....                        | 1    |

| 1-1.2 COF(Chip on Film)薄膜覆晶式封裝.....                              | 10   |

| 1-1.3 COG(Chip on Glass)玻璃基板晶片接合技術.....                          | 15   |

| 1-2 研究動機.....                                                    | 20   |

| 第二章 文獻回顧.....                                                    | 21   |

| 2-1 電遷移理論.....                                                   | 21   |

| 2-2 電遷移的驅動力與通量方程式.....                                           | 21   |

| 2-3 純金屬的電遷移效應.....                                               | 23   |

| 第三章 實驗方法與步驟.....                                                 | 25   |

| 3-1 實驗材料.....                                                    | 25   |

| 3-1.1 COF基板材料.....                                               | 25   |

| 3-1.2 完成金凸塊之晶片.....                                              | 29   |

| 3-1.3 覆晶填充膠材.....                                                | 30   |

| 3-2 實驗方法與步驟.....                                                 | 31   |

| 3-2.1 試片製備.....                                                  | 33   |

|                                                     |    |

|-----------------------------------------------------|----|

| 3-2.2 金離子遷移的加速測試.....                               | 34 |

| 3-2.3 試片加速測試後外觀分析.....                              | 36 |

| 3-2.4 Mini-probe和I-V characteristic curve 量測分析..... | 37 |

| 3-2.5 試片破壞分析.....                                   | 38 |

| 第四章 實驗結果與討論.....                                    | 41 |

| 4-1 試片加速測試後外觀分析結果.....                              | 41 |

| 4-2 Mini-probe和I-V characteristic curve 量測分析結果..... | 47 |

| 4-3 試片的微結構分析.....                                   | 51 |

| 4-4 金離子遷移造成產品失效機制之探討.....                           | 62 |

| 第五章 結論.....                                         | 65 |

| 參考文獻.....                                           | 66 |

## 圖 目 錄

|                                                                    |    |

|--------------------------------------------------------------------|----|

| 圖 1-1 TCP&COF 軟性基板底材結構圖.....                                       | 2  |

| 圖 1-2 TCP&COF 軟性捲帶式基板制程流程圖.....                                    | 5  |

| 圖 1-3 金凸塊制程流程圖.....                                                | 7  |

| 圖 1-4 TCP Inner Lead Bonding 分解示意圖.....                            | 8  |

| 圖 1-5 TCP 產品塗膠示意圖.....                                             | 9  |

| 圖 1-6 TCP vs COF 產品剖面結構圖.....                                      | 12 |

| 圖 1-7 COF Inner Lead Bonding 分解示意圖.....                            | 14 |

| 圖 1-8 COF 產品填膠示意圖.....                                             | 15 |

| 圖 1-9 COG 成品示意圖.....                                               | 17 |

| 圖 1-10 ACF 導電粒子結構圖.....                                            | 17 |

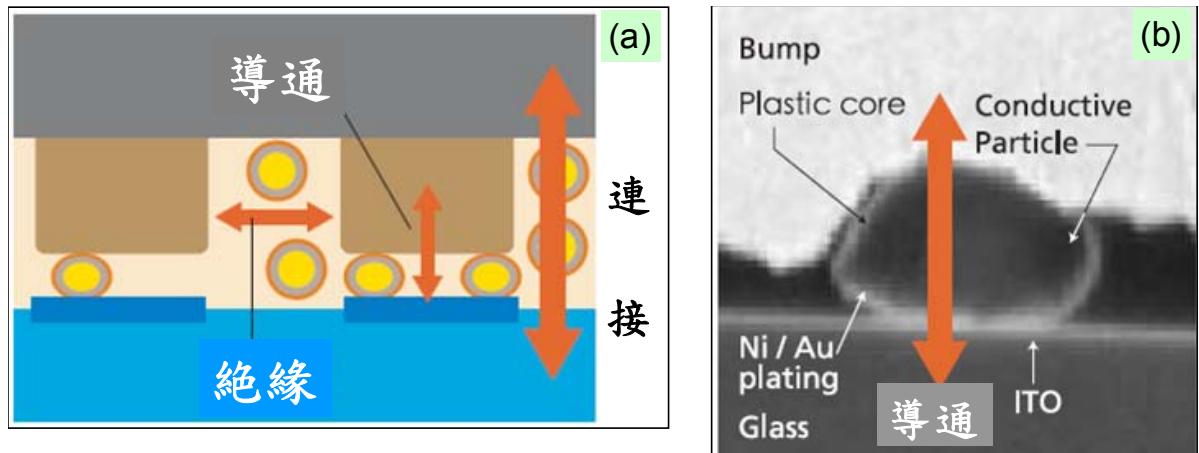

| 圖 1-11(a)導電粒子導通示意圖(b)導電粒子受壓破裂導通圖.....                              | 18 |

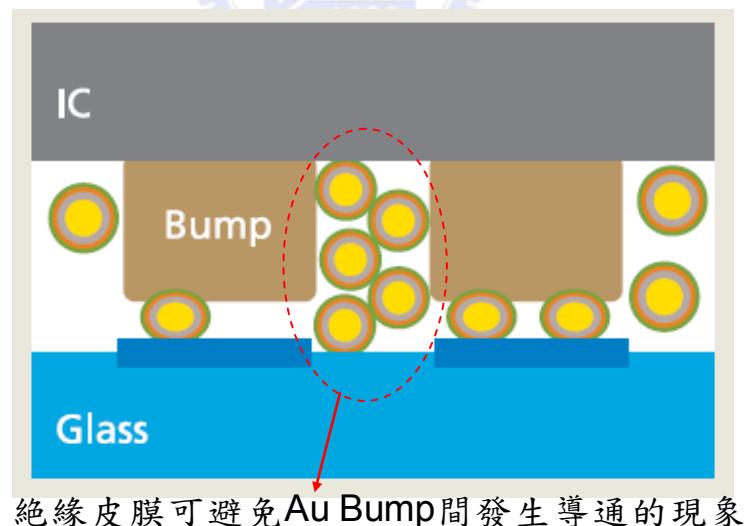

| 圖 1-12 導電粒子中絕緣皮膜效能圖.....                                           | 18 |

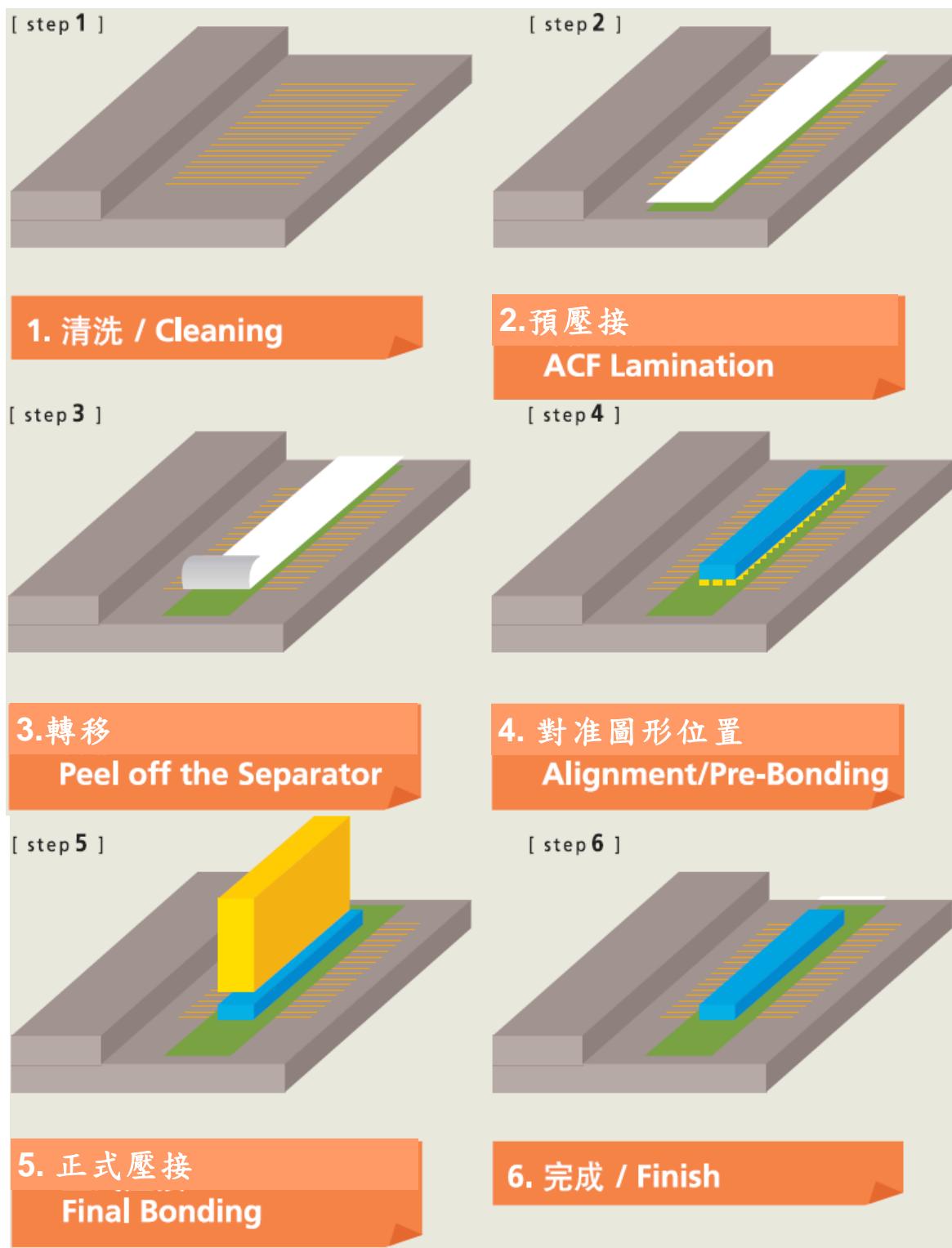

| 圖 1-13 COG 封裝技術流程圖.....                                            | 19 |

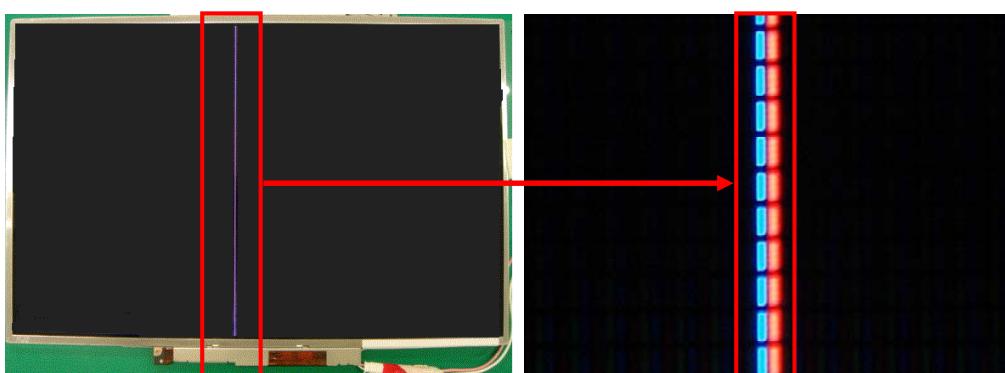

| 圖 1-14 LCD 面板亮線失效模式.....                                           | 20 |

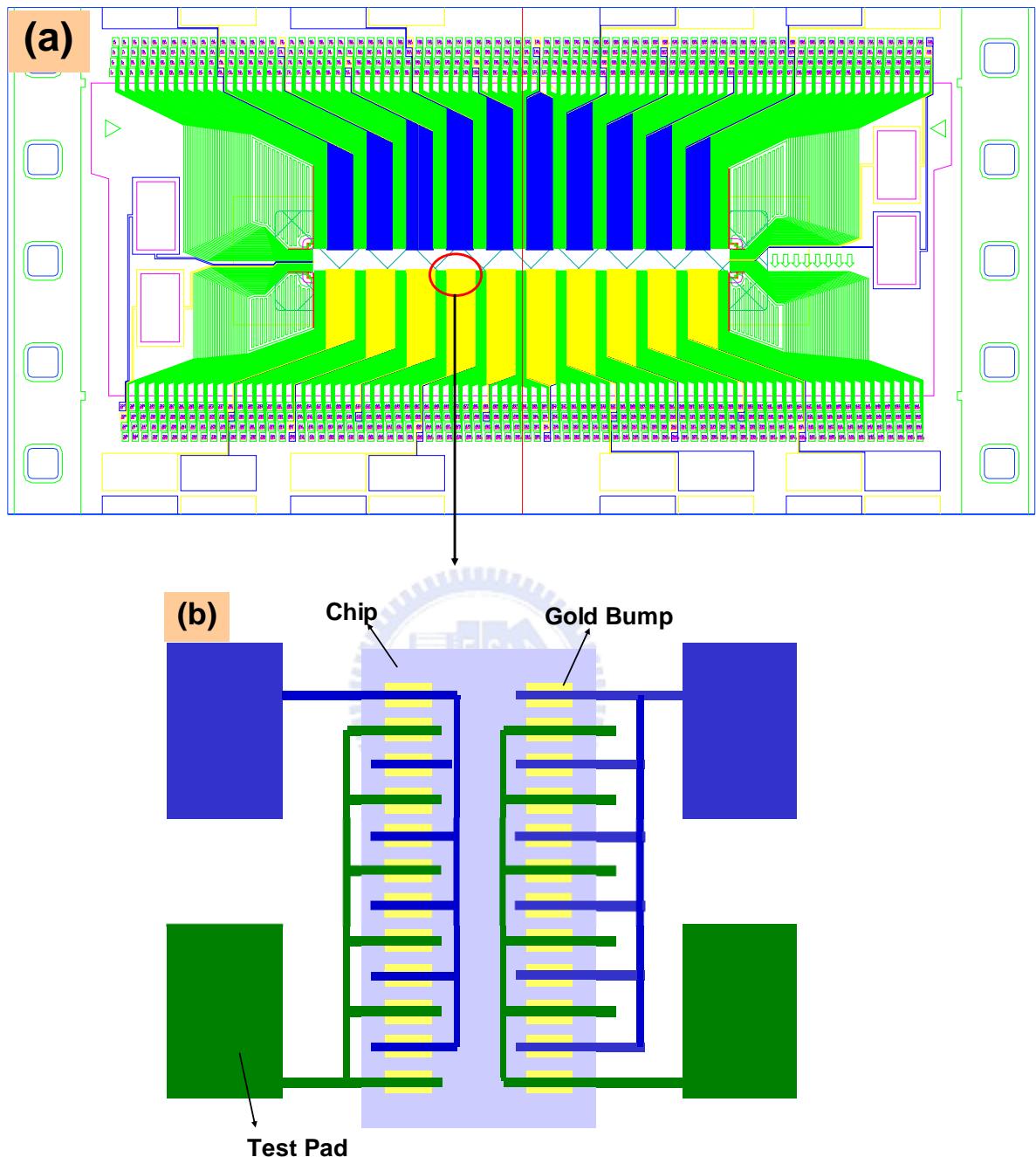

| 圖 3-1 (a) COF tape layout drawing (b) COF tape layout drawing..... | 27 |

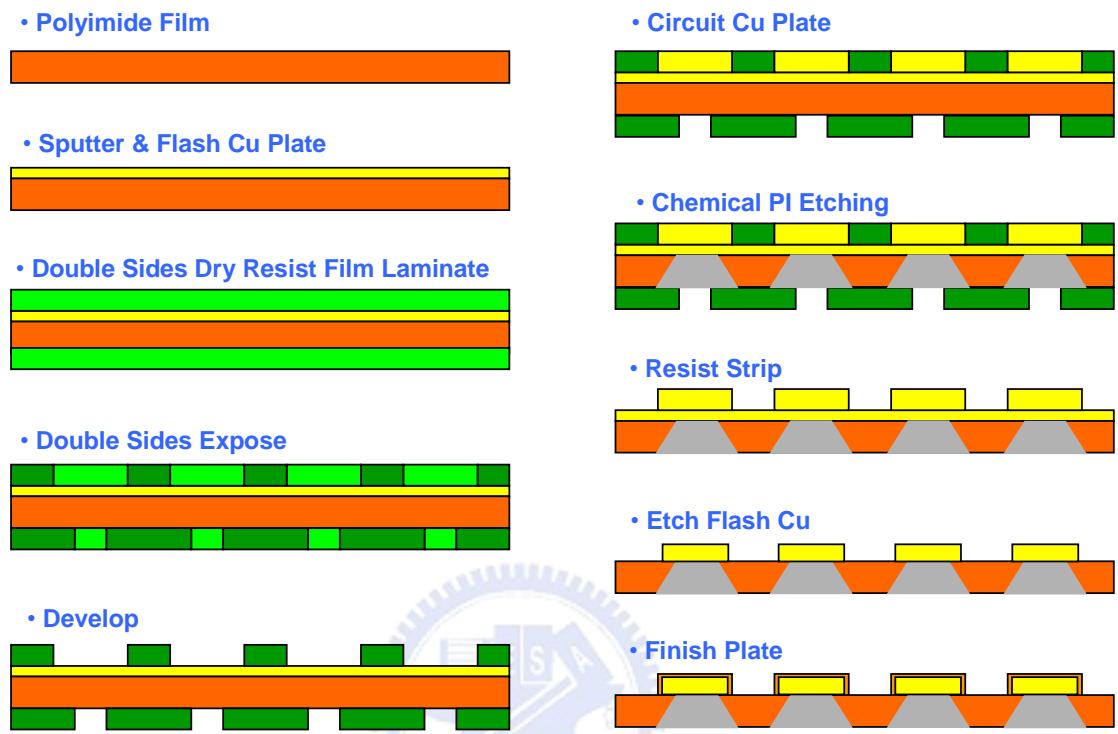

| 圖 3-2 COF 基板半成加法製作流程圖.....                                         | 28 |

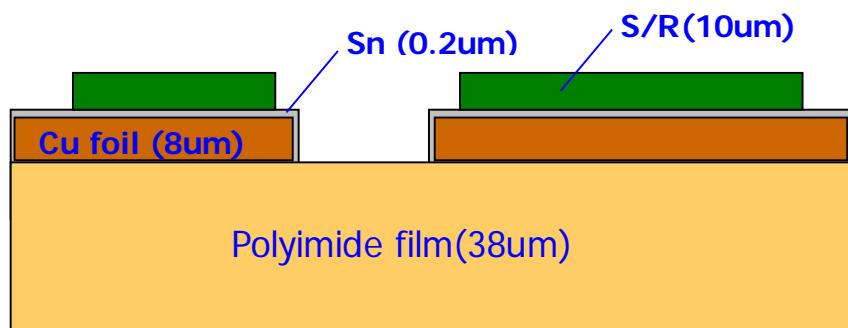

| 圖 3-3 COF 基板結構圖.....                                               | 28 |

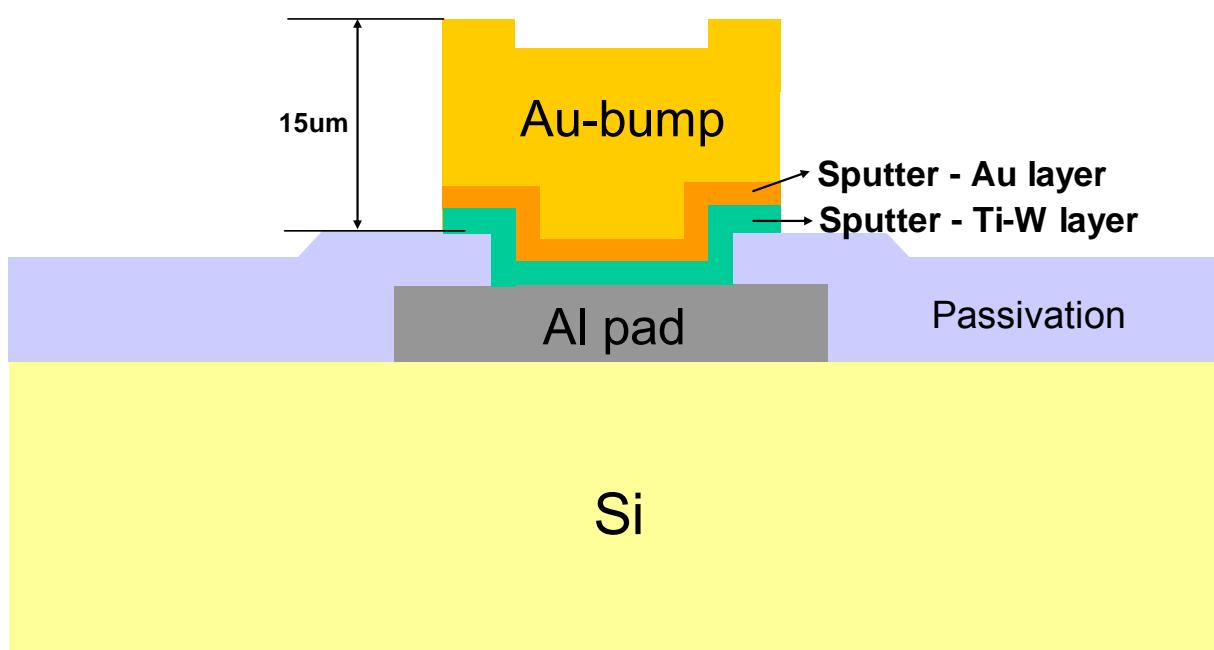

| 圖 3-4 金凸塊結構示意圖.....                                                | 29 |

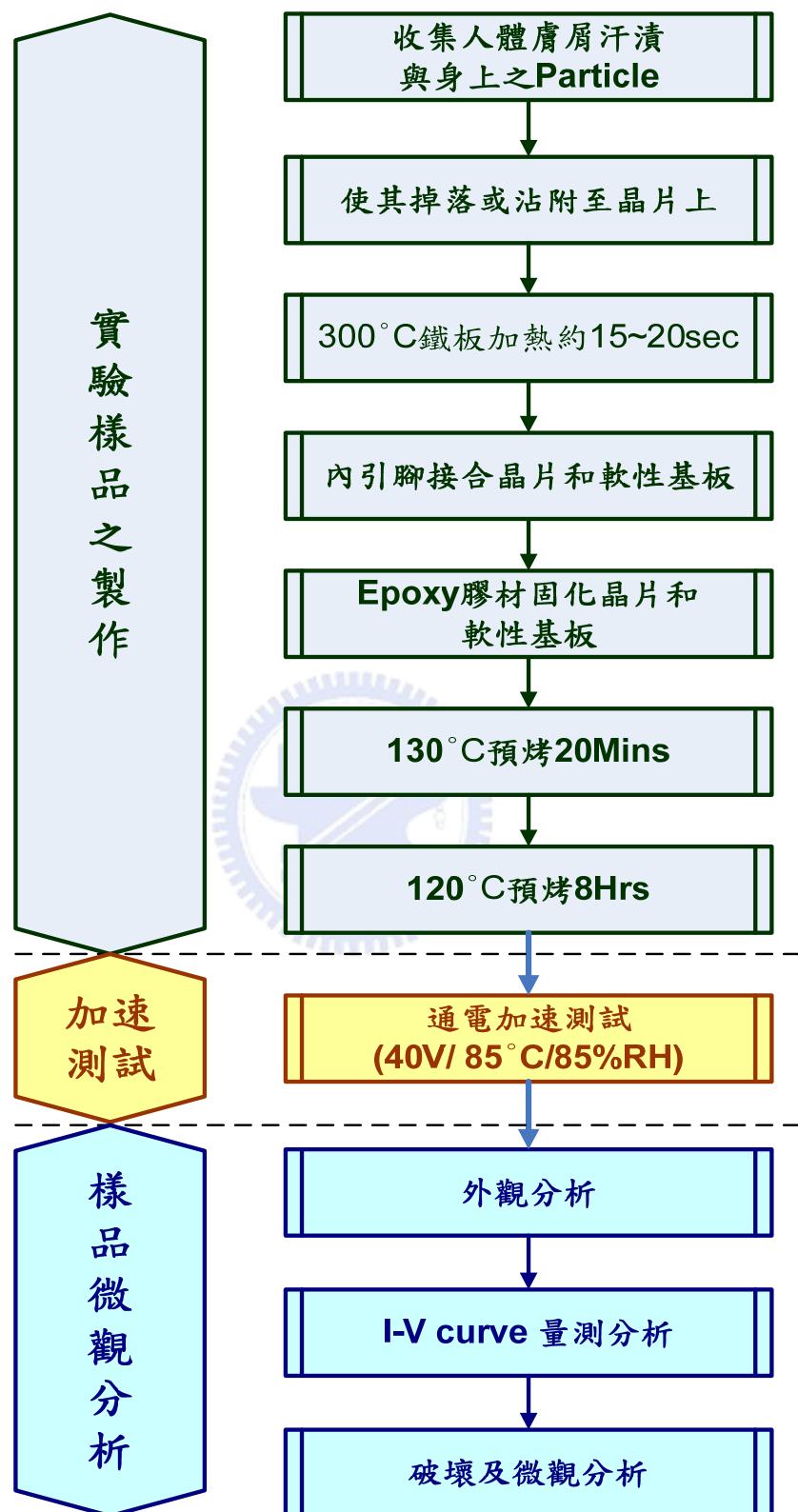

| 圖 3-5 金離子遷移實驗流程圖.....                                              | 32 |

| 圖 3-6 實驗試片通電示意圖.....                                               | 34 |

| 圖 3-7 Temperature & Humidity Storage Test Machine.....             | 35 |

| 圖 3-8 COF 封裝完成結構圖.....                                             | 36 |

| 圖 3-9 NIKON MM-800 工具顯微鏡.....                                      | 36 |

| 圖 3-10 Mini-probe & I-V curve machine photo.....                   | 37 |

|                                                                                                                     |    |

|---------------------------------------------------------------------------------------------------------------------|----|

| 圖 3-11 試片研磨方向圖 .....                                                                                                | 39 |

| 圖 3-12 SEM machine photo.....                                                                                       | 39 |

| 圖 3-13 TEM machine photo.....                                                                                       | 40 |

| 圖4-1 (a) Before HTST 之工具顯微鏡照片 (b)HTST 168hrs後晶片與封膠樹脂分層圖(c) HTST 336hrs 後晶片與封膠樹脂分層圖 (d)HTST 168hrs 後晶片與封膠樹脂分層圖 ..... | 43 |

| 圖 4-2 COF 電腦模擬應力分佈圖 .....                                                                                           | 44 |

| 圖 4-3 環氧樹脂與晶片表面分層過程示意圖 .....                                                                                        | 45 |

| 圖 4-4 1008Hrs 後金凸塊間表面異常圖 .....                                                                                      | 46 |

| 圖4-5 金離子遷移實驗樣品之HP4155分析結果(a)P-P (b)S-S (c)N-N (d)P-S (e)P-N .....                                                   | 50 |

| 圖 4-6 (a)異常樣品研磨至 5um 厚度後金凸塊間表面物質狀況(b)正面研磨後 TEM 取樣位置圖 .....                                                          | 53 |

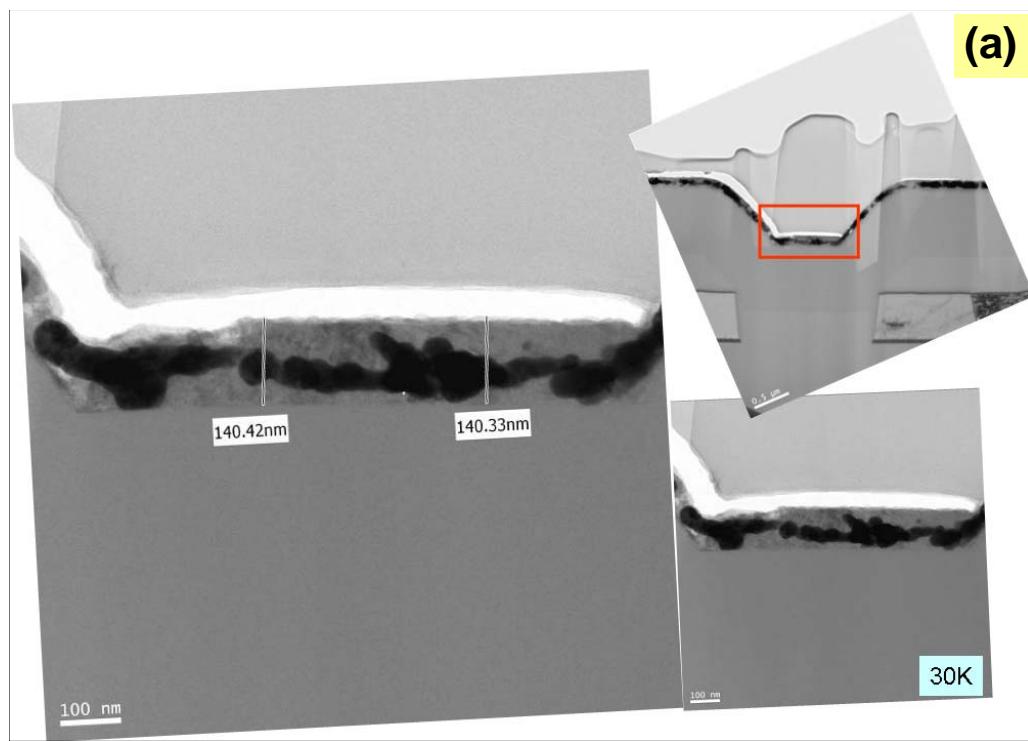

| 圖 4-7 TEM 取樣之試片圖 .....                                                                                              | 54 |

| 圖 4-8 實驗樣品金離子遷移 SEM image .....                                                                                     | 55 |

| 圖 4-9 金離子遷移靠近 Gold bump#A 分層位置放大圖 .....                                                                             | 56 |

| 圖 4-10 金離子遷移靠近 Gold bump#B 分層位置放大圖 .....                                                                            | 57 |

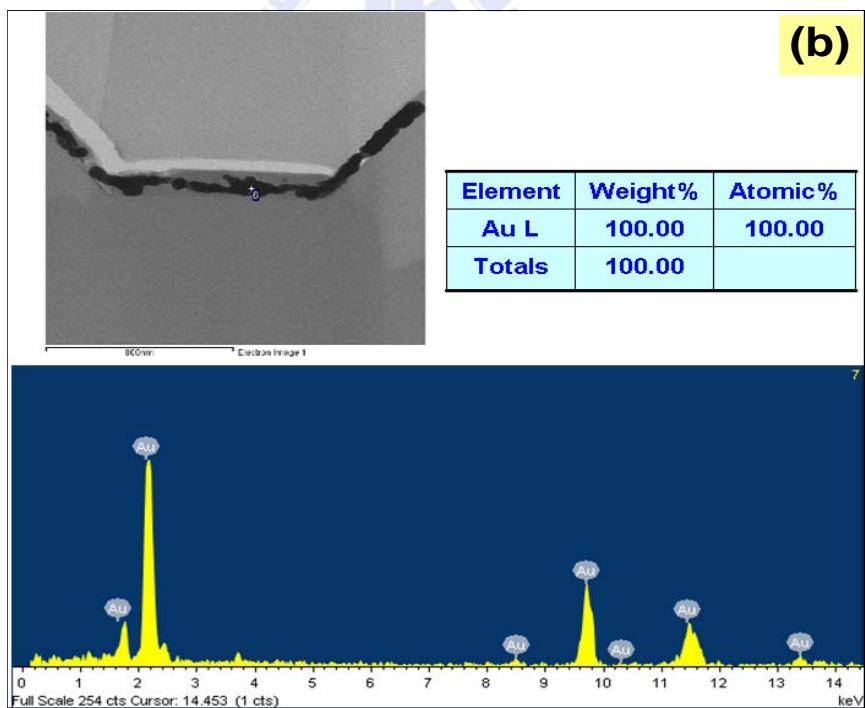

| 圖 4-11 (a)金凸塊邊緣放大 SEM 30K image(b)金凸塊 EDS 分析圖 .....                                                                 | 58 |

| 圖4-12 (a)分層放大SEM 30K image(b)分層中深灰色物質EDS分析圖 .....                                                                   | 59 |

| 圖4-13 (a)分層放大SEM 30K image(b)分層中深黑色物質EDS分析圖 .....                                                                   | 60 |

| 圖 4-14 金離子遷移之金原子移動示意圖 .....                                                                                         | 61 |

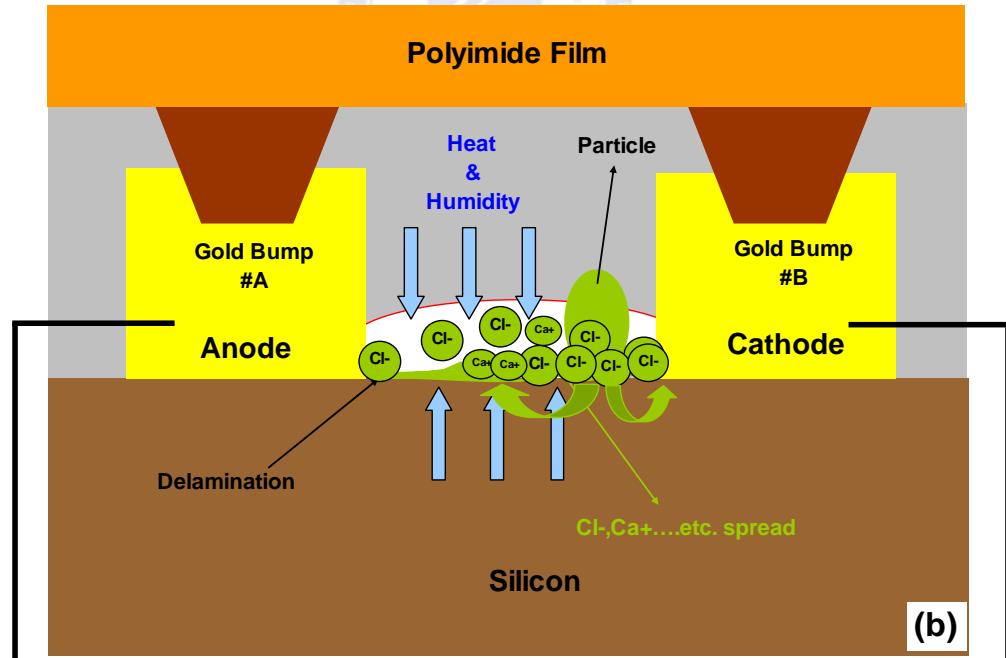

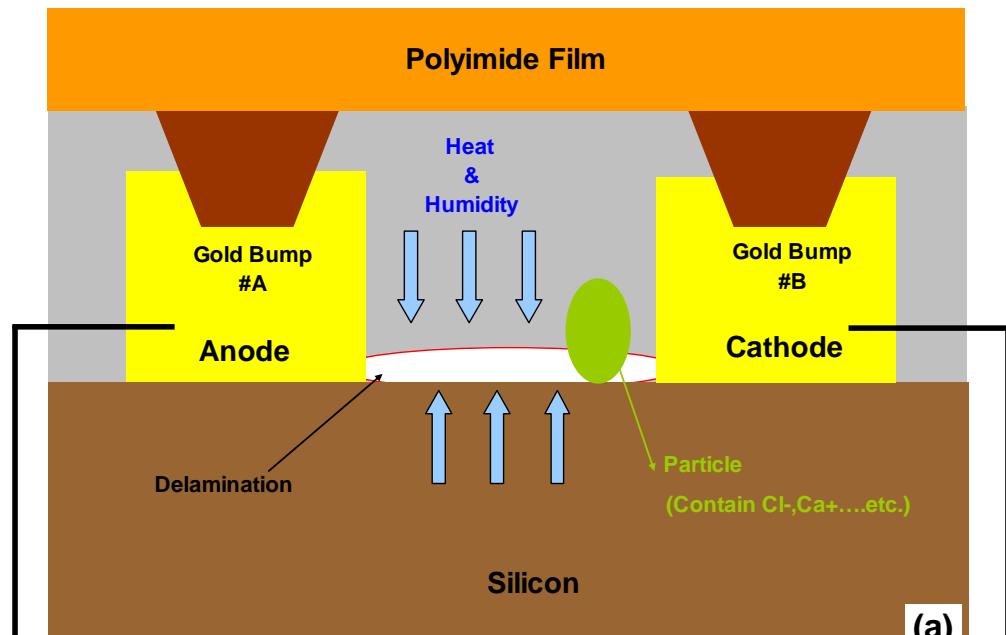

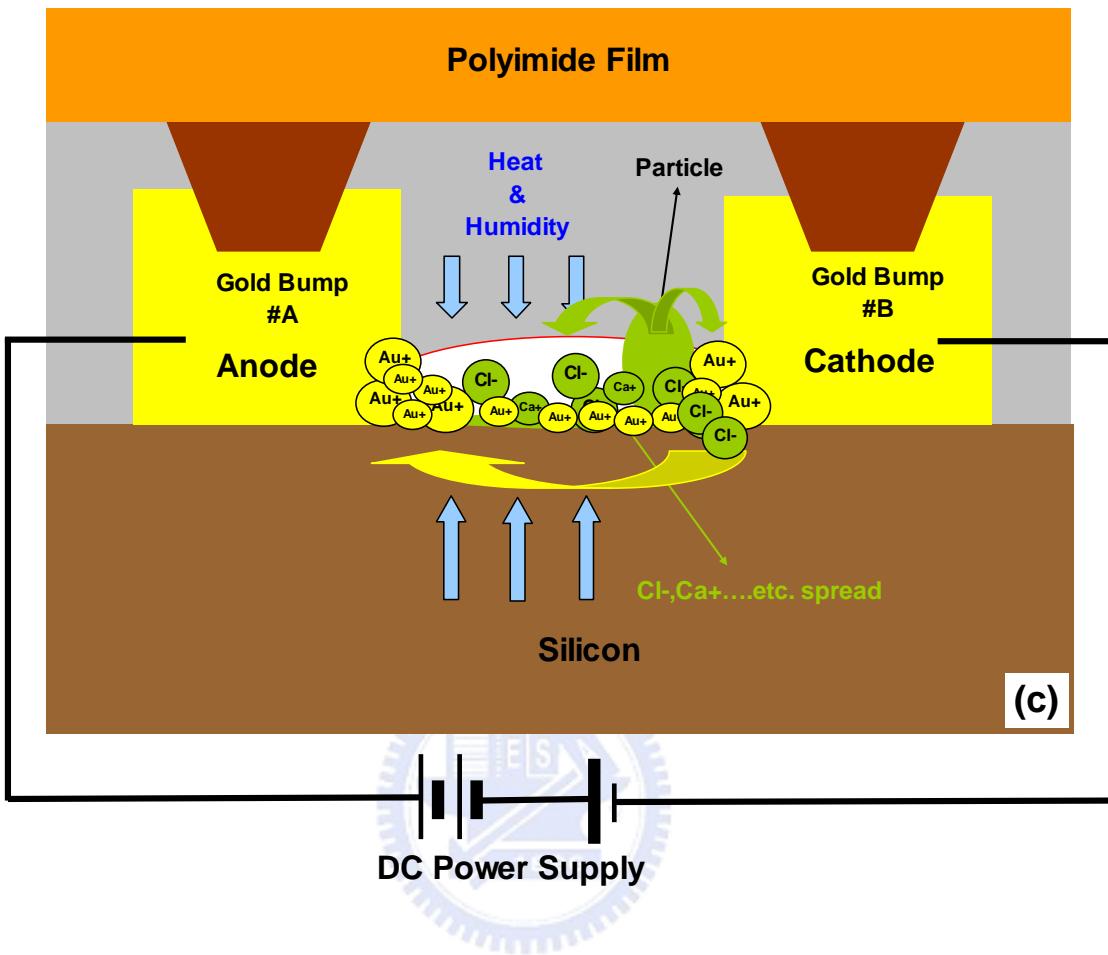

| 圖4-15金離子遷移失效機制發生過程示意圖(a) 金凸塊間有含Cl離子之Particle且在溼氣及溫度的影響下出現分層(b) Cl離子解離至整個分層(c) Cl離子使Gold Bump#A的金                    |    |

離子產生解離現象後金離子持續地往Gold Bump#B移動至接觸到Gold Bump#B則產生

Short失效現象.....64

## 表 目 錄

|                           |    |

|---------------------------|----|

| 表 2-1 純金屬的 $Z^*/f$ 值..... | 24 |

| 表 3-1 覆晶填充膠材規格表.....      | 30 |

| 表 4-1 金離子遷移樣品阻抗量測表.....   | 47 |

## 第一章 緒論

### 1-1 Liquid Crystal Display Driver Integrated Circuit封裝技術簡介

Liquid Crystal Display Driver Integrated Circuit(LCD Driver IC)的構裝方式依使用的構裝結構不同而區分為：捲帶式封裝(Tape Carrier Package)、覆晶式薄膜封裝(Chip on Film)和玻璃基板晶片接合技術(Chip on Glass)三種主要的接合方式。捲帶式封裝(TCP)為LCD Driver IC封裝最早之技術，然隨著消費性電子產品輕、薄、短、小的發展趨勢，使得Integrated Circuit(IC)的間距愈做愈小且腳數愈來愈多，色彩飽合度、反應速度等功能性需求增加，因而發展出新一代LCD Driver IC封裝技術—覆晶式薄膜封裝(COF)，同時間由於某些電子消費產品成本的不斷下降，因而發展出不需要軟性載板的玻璃基板晶片接合封裝技術(COG)，可直接和LCD面板做接合，以節省軟性載板和印刷電路版(Printed Circuit Board)費用。以下針對此三種LCD Driver IC 封裝技術做說明。

#### 1-1-1 TCP(Tape Carrier Package) 捲帶式封裝

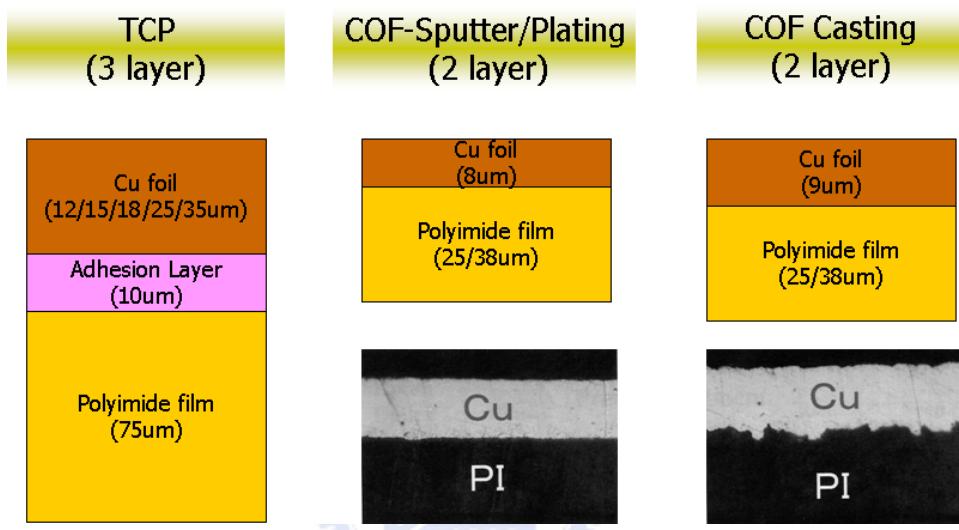

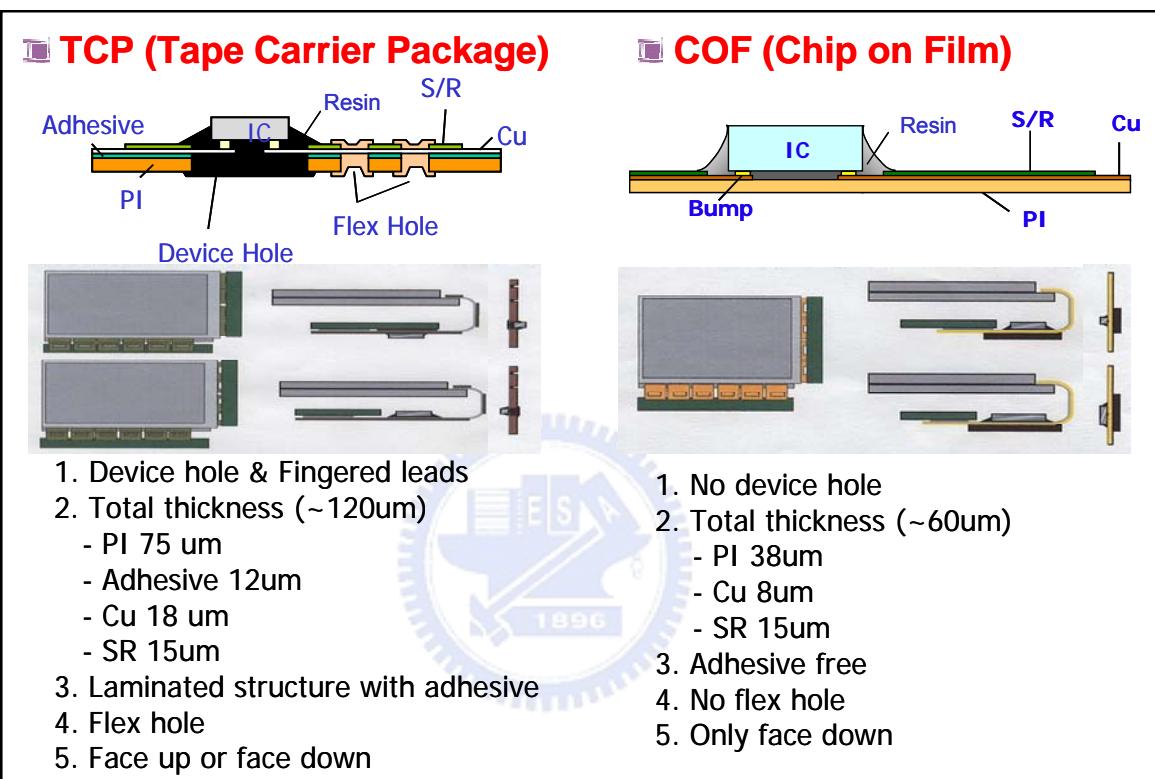

捲帶式封裝(TCP)源於 1968 年美國奇異公司利用捲帶自動粘合技術發展出的一種 IC 封裝方式。目前 TCP 的軟性捲帶式基板底材使用上是以三層結構為主-包含聚亞醯胺(Polyimide)、接著層(Adhesion Layer)和銅箔(Copper

Foil)，如圖 1-1 TCP 和 COF 軟性捲帶式基板底材結構圖，其軟性捲帶式基板底材作法為利用聚亞醯胺當作基材，使用接著劑(Adhesion)將銅箔和聚亞醯胺經由高壓貼合而成。

圖 1-1 TCP&COF軟性基板底材結構圖[1]

1. TCP 的原材料主要有兩部份：(1) 軟性捲帶式基板 (2) 完成金凸塊制程的 IC。

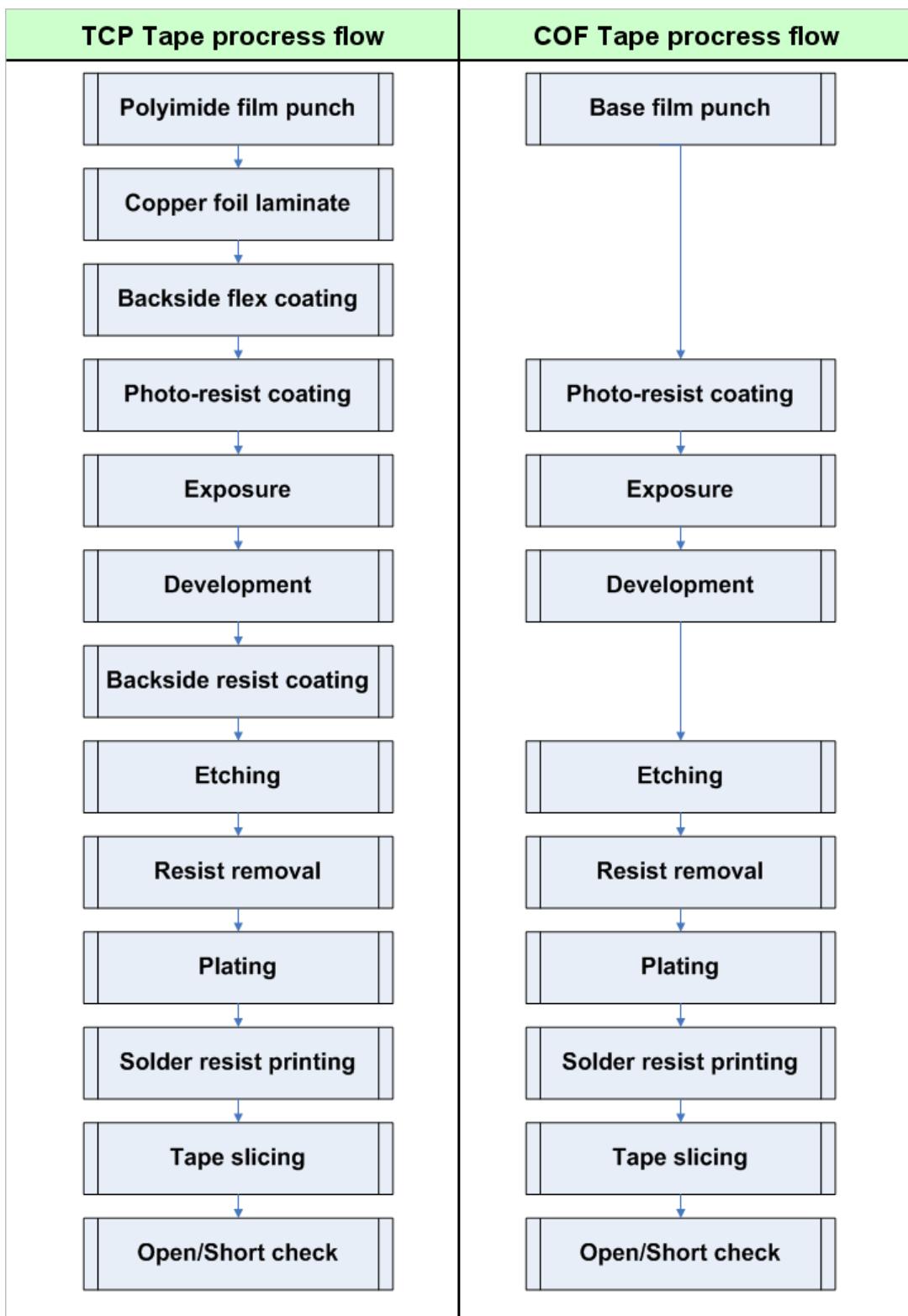

(1)軟性捲帶式基板 – 為一種具搭載電路引腳圖的軟性捲帶式印刷電路版板，其形狀與照相機底片帶十分相似，宽度有 35mm、48mm、70mm 等三種規格。其制作流程可參考圖 1-2 TCP&COF 軟性捲帶式基板制程流程圖。

①Polyimide film punch – 主要是於 Polyimide film 上將傳送用的傳送孔、對位孔、彎曲折孔及放 IC 的元件孔，以衝孔的方式 punch 出來。

②Copper foil laminate – 將銅箔和 Polyimide film 以接著劑粘著後做高溫壓合並烘烤硬化。

③Backside flex coating – 將彎曲折孔背面部分填滿彈性膠。

④Photo-resist coating – 以滾輪塗佈方式於料帶上塗上一層液態感光光阻。

⑤Exposure – 以玻璃光罩繪製高解度的線路做為影像轉移的治具，然後利用 UV 光透過玻璃光罩將欲蝕刻處的光阻進行光裂解反應。

⑥Development – 將已經經過 UV 光裂解的光阻部份以 NaOH 溶解去除並保留未裂解的光阻。

⑦Backside resist coating – 在進行蝕刻前先將元件孔和其它裸露銅箔的孔使用填保護以免受到蝕刻液侵蝕。

⑧Etching – 以蝕刻液將銅箔溶解後蝕刻出線路圖形。

⑨Resist removal – 將不要的光阻及背膠以強鹼藥液剝除。

⑩Plating – 將經蝕刻後的線路以化學鍍錫方式於表面鍍上純錫層。

⑪Solder resist printing – 使用網版印刷方式將非用於焊接的線路

部份以防焊漆覆蓋後進行烘硬化。

⑫Tape slicing – 將完成以上制程的料帶以產品寬度 35mm、48mm

或 70mm 需求做裁切。

⑬Open/Short check – 將裁切好的產品進行最終的 Open 或 Short

的品質測試。

圖 1-2 TCP&COF 軟性捲帶式基板制程流程圖

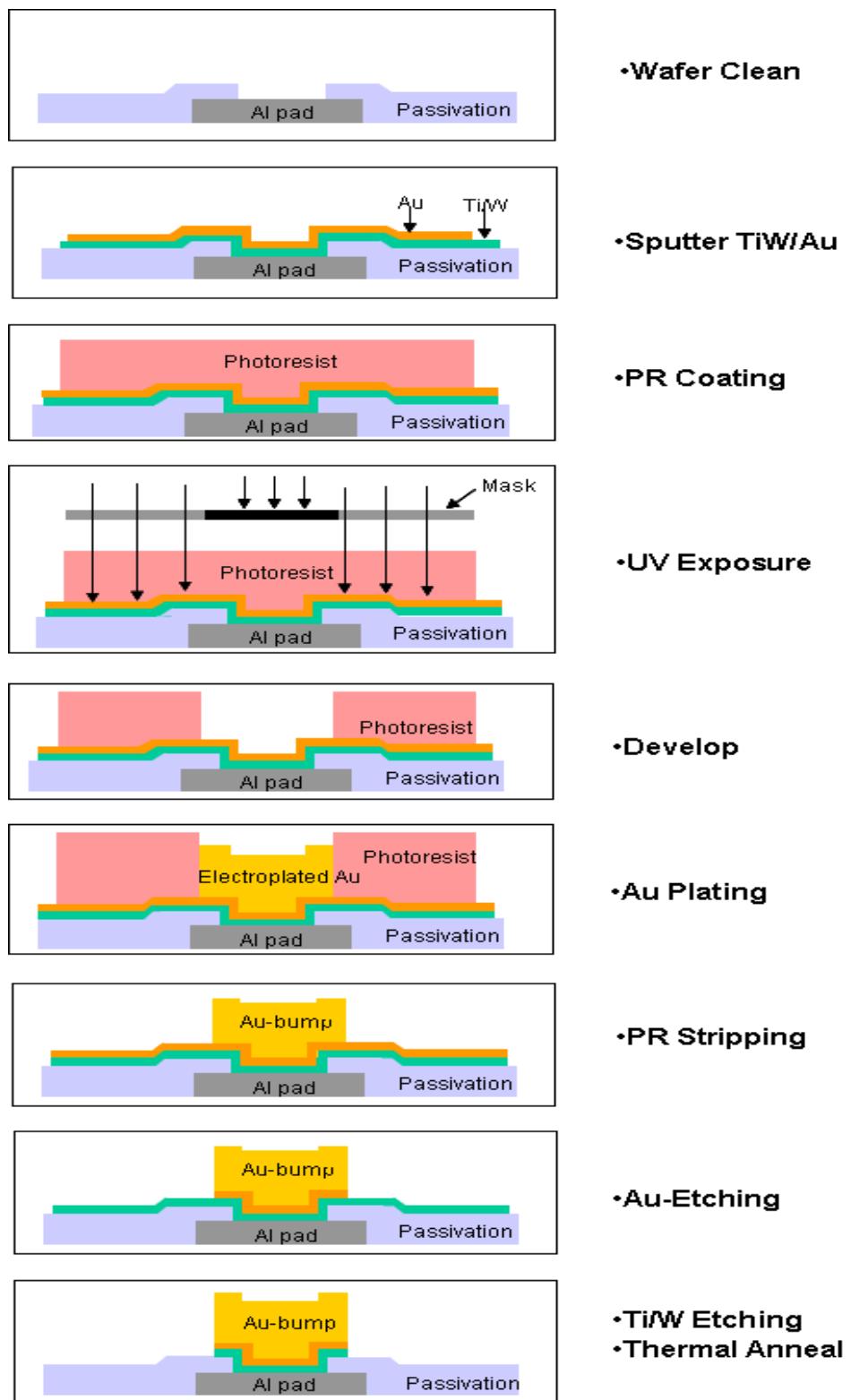

(2) 完成金凸塊制程的 IC – 在 LCD Driver IC 的 TCP、COF 或 COG 的封裝過程中，IC 上的金凸塊為 IC 與軟性捲帶式基板上的電路引腳連接的橋樑。其製作流程可參考圖 1-3 金凸塊制程流程圖。

- ①Wafer clean – 主要是將 wafer 鋁墊上的氧化層做去除的動作。

- ②Sputter 鈦鎢/Gold – 以濺鍍方式於 wafer 上鍍上一層薄薄的鈦鎢層做為阻障層，再鍍上一層薄薄的金做為種子層。

- ③Photo resist coating – 以旋轉塗佈方式於 wafer 上塗上一層液態感光光阻。

- ④Exposure – 以玻璃光罩繪製高解析度線路做為影像轉移的治具，然後利用 UV 光透過玻璃光罩將欲蝕刻處的光阻進行光裂解反應。

- ⑤Development – 將已經經過 UV 光裂的光阻部份以溶劑溶解去除並保留未裂解的光阻。

- ⑥Gold plating – 利用電解電鍍的方式於 wafer 鋁墊上，電鍍上約 15um 厚的金。

- ⑦Photo resist stripping – 將不要的光阻以強鹼藥液剝除。

- ⑧Gold etching – 以蝕刻液將位於 wafer 上做為種子層的金去除。

- ⑨鈦鎢 etching – 以蝕刻液將位於 wafer 上做為阻障層的鈦鎢去除。

- ⑩Thermal anneal – 以高溫退火的方式調整金凸塊的硬度。

圖1-3 金凸塊制程流程圖

## 2. TCP 的封裝流程

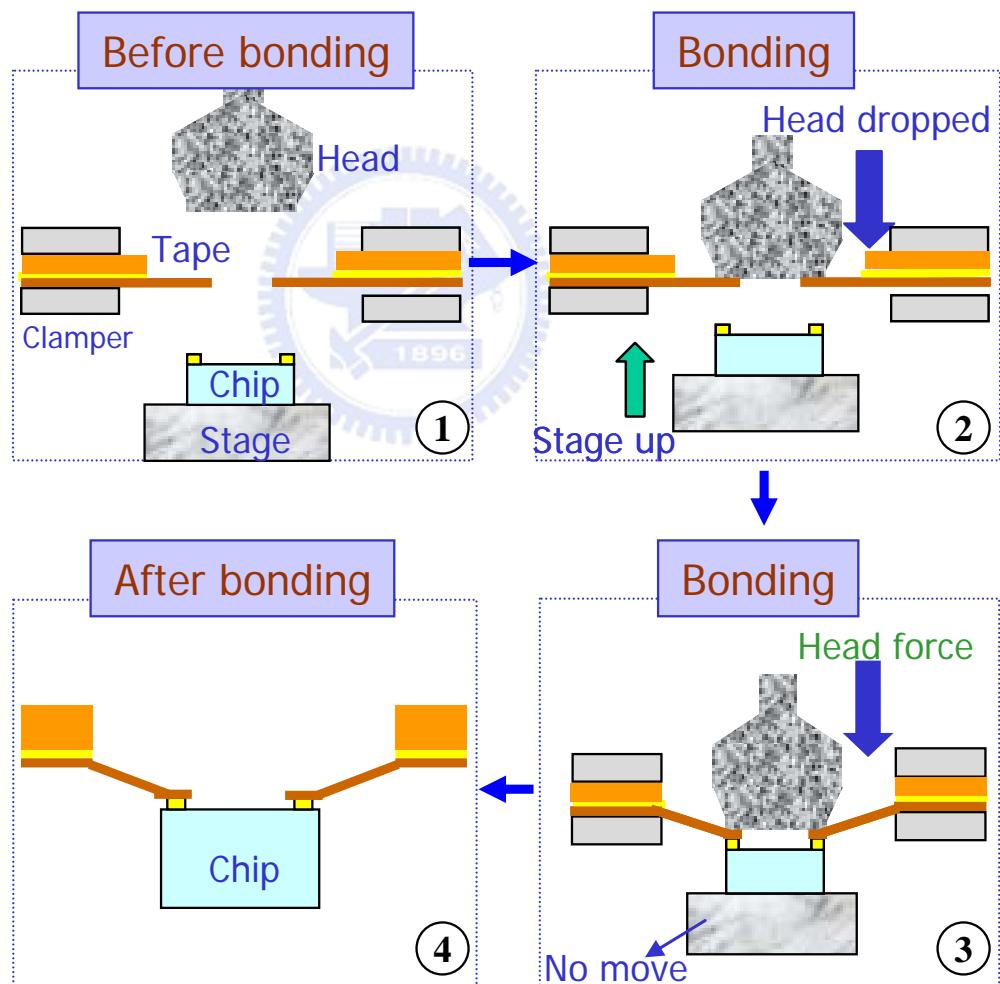

### (1) 內引腳接合(Inner Lead Bonding) – 使用 CVD Diamond Tooling

以高溫 500°C、高壓下，接合時間約為 0.3~0.5sec，使得軟性捲帶

式基板內引腳上的錫融熔，同時和 IC 上的金凸塊形成金錫共晶，

以完成內引腳和金凸塊接合。詳細的內引腳接合步驟，如圖 1-4 TCP

Inner Lead Bonding 分解圖所示。

圖 1-4 TCP Inner Lead Bonding 分解示意圖

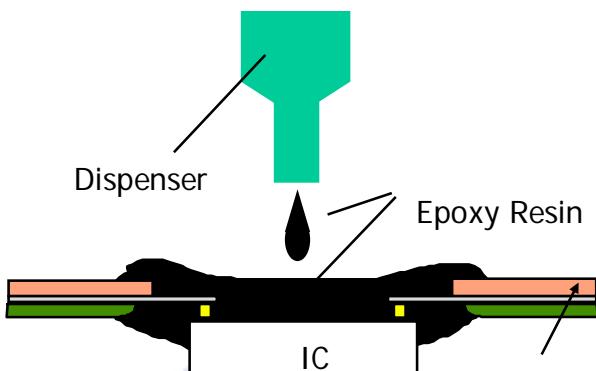

(2)塗膠&烘烤(Potting&Curing) – 將已完成 ILB 制程的產品，使用環氧樹脂以針頭塗膠的方式，將內引腳的位置封膠後再經過高溫烘烤固化，以達到保護產品的效果。

圖 1-5 TCP 產品塗膠示意圖

(3)雷射蓋印(Laser Marking) – 將已完成 Potting&Curing 制程的產品，以 Laser 光將所需之蓋印碼打在晶片背面，以方便產品在客戶端出問題時可追溯產品之生產記錄。

(4)產品最終測試(Final Test) – 將封裝完成之產品進行品質功能上的測試，使用客戶提供之測試程式，經由測試機台及探針卡給產品一定的電壓和電流，依照測試程式中的測試程序，完成產品品質測試，以確保提供至用戶端的產品品質。

(5)外觀檢驗(Inspection) – 以人員使用光學顯微鏡約10X~180X，將完成品質功能測試的產品，做最終產品外觀的100%目檢。

(6)編輯&出貨(Edit&Package) – 將已完成之產品，依客戶的要求，編輯成用戶端所要之方向後，再經過包裝即可出貨。

### 1-1.2 COF(Chip on Film) 覆晶式薄膜封裝

LCD Driver IC 的市場主要可以分成小尺寸 LCD 面板，及中大尺寸 LCD 面板的應用。小尺寸面板主要的應用為手機，手機為高整合性之產品，LCD 模組需整合許多元件且與系統的連接需具有高撓曲、輕量化特性，COF 可滿足此一需求，且可支持越來越複雜的機構設計，針對較高階的手機產品，使得 LCD 模組型態於 2004 年逐漸往 COF 發展。中大尺寸 LCD 面板的應用有筆記型電腦、桌上型螢幕及電視等，其中由於高腳數的要求，快速的反應時間，色彩解析度和飽合度的要求，及產品輕薄短小的趨勢下，COF 的封裝技術已逐漸取代 TCP 封裝技術，成為現今及未來的技術主流。

目前 COF 的軟性捲帶式基板底材使用上是以二層結構為主-包含聚亞醯胺(Polyimide)和銅箔(Copper foil)，如圖 1-1 TCP 和 COF 軟性捲帶式基板底

材結構圖，其軟性捲帶式基板底材作法有兩種，一種為利用 Polyimide 當作基材，經由表面處理後，以濺鍍加電鍍的方式形成銅箔層，此做法稱為 Sputter/Plating method。另一種則是以壓延好的銅箔，經由表面處理後，coating 上一層液態的 Polyimide Layer，最後再經過烘烤後完成，稱為 Casting method。具體結構如圖1-1 TCP和COF軟性基板底材結構圖。

1. COF 原材料同樣包含: (1)軟性捲帶式基板 (2)完成金凸塊制程的 IC。

基本上 TCP 與 COF 所使用的原材料是一樣的，其中的差異是在 COF 使用的軟性捲帶式基板的結構為 2 層材，沒有 Adhesion Layer，其基板的總厚度約只有 60um，而 TCP 約 120um，COF 基板上的 Inner Lead 不是懸空的，沒有 Flex hole，只有 Face down type 等特性。如圖 1-6 TCP vs COF 產品剖面結構圖。至於 COF 用之軟性捲帶式基板的制作流程基本上和 TCP 大同小異，主要少掉 Copper foil laminate、Backside flex coating 和 Backside resist coating 三道制程。如圖 1-2 TCP 和 COF 軟性捲帶式基板制程流程圖所示。

圖 1-6 TCP vs COF 產品剖面結構圖

## 2. COF 的封裝流程

COF 封裝流程與 TCP 封裝流程完全一樣，以下主要針對其中異常在 ILB 和 Potting 站點的封裝方式有些許的不同做說明。

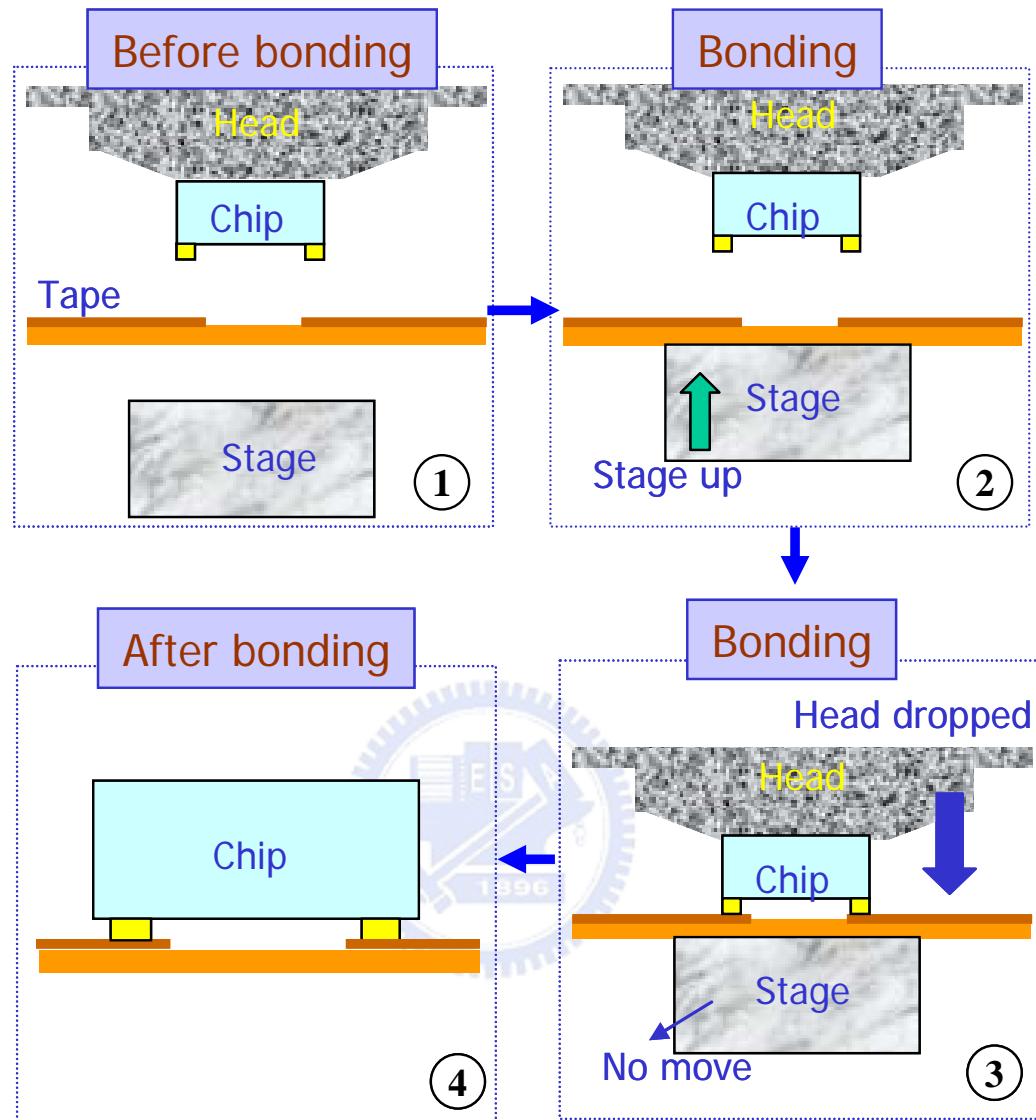

(1) 覆晶式內引腳接合(Flip Chip Inner Lead Bonding) – 特徵為 IC 會翻轉 180 度後承接於 Bonding 用之 CVD Diamond Tooling 上，再以高溫 400°C、高壓下，接合時間約為 0.3~0.5sec，使得軟性捲帶式基板內引腳上的錫融熔，同時和 IC 上的金凸塊形成金錫共晶，以完成內引腳和金凸塊接合。詳細的內引腳接步驟，如圖 1-7 COF Inner Lead Bonding 分解圖所示。

圖 1-7 COF Inner Lead Bonding 分解示意圖

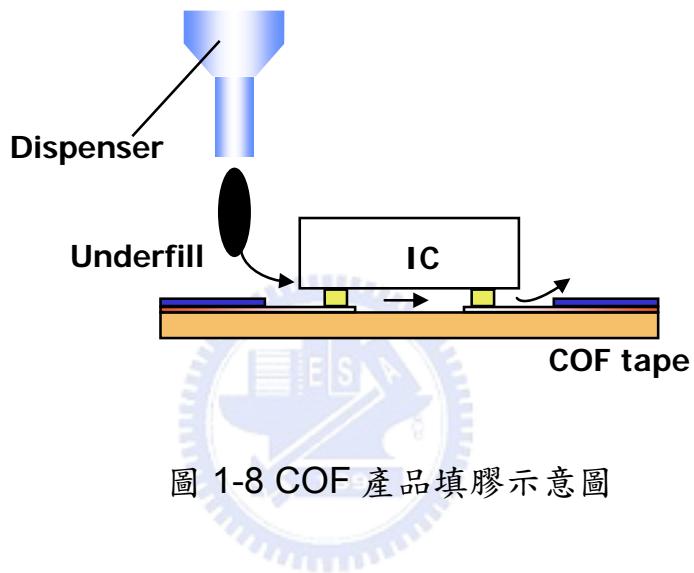

(2) 填膠&烘烤(Underfill&Curing) – 將已完成 ILB 制程的產品，以針頭於 IC 的邊緣填充環氧樹脂膠材，利用毛細現象之虹吸原理，圖 1-8 COF 產品填膠示意圖，使得環氧樹脂膠材自然地填充整個 IC 內部及周圍，再經過高溫烘烤固化，以達到保護產品的效果。

### 1-1.3 COG(Chip on Glass) 玻璃基板晶片接合技術

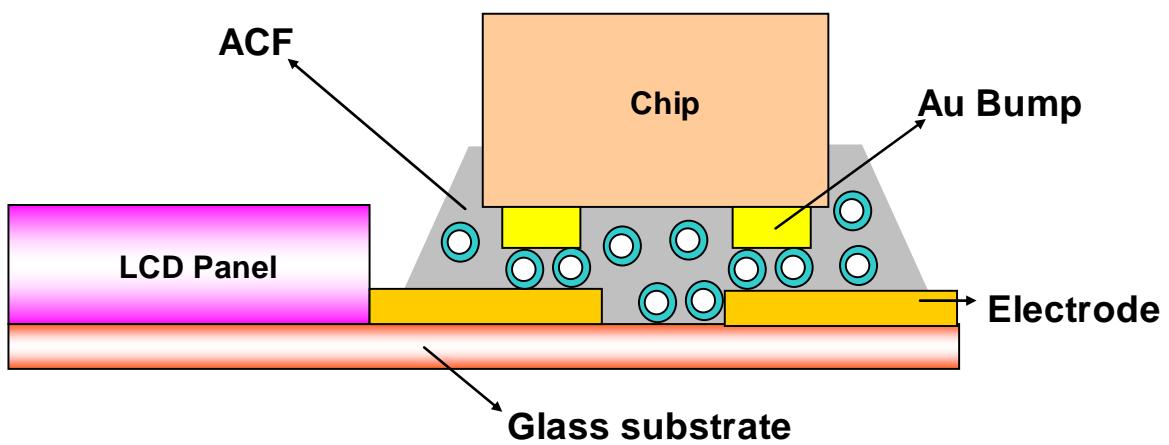

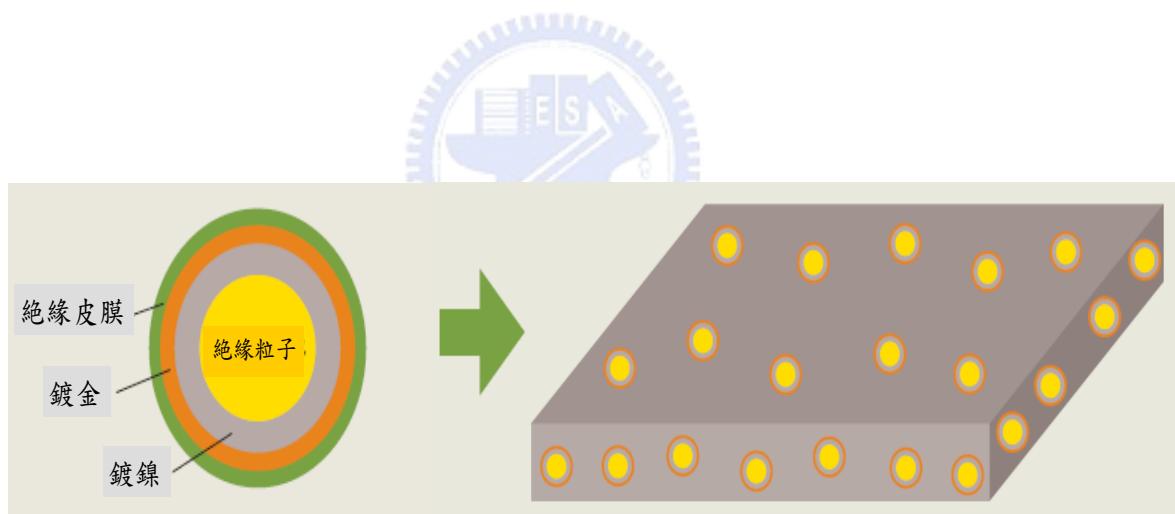

COG 是一種將 IC 與基板相互連接的先進封裝技術，利用覆晶(Flip Chip)技術將長有金凸塊的 IC 晶片，以異方性導電膠(ACF)為中間介面，接合在 LCD 的氧化銻錫(Indium Tin Oxide)端；應用於液晶顯示器上時，由於基板是玻璃，故被稱為玻璃基板晶片接合技術(Chip on Glass)，如圖 1-9 所示。其中異方性導電膠(Anisotropic Conductive Film)是一種將導電粒子分散於熱硬

化性樹脂中 Film 的產品，如圖 1-10，導電粒子的結構為樹脂表面 coating 上一層鎳(Nickel)再加上一層金(Gold)，最後再於最外面 coating 一層絕緣膜。鍍鎳/金的目的為當 ACF 中的導電粒子受一定的壓力破裂變形後，導電粒子中的鎳/金層則扮演起導通晶片中金凸塊和面板中 ITO 端的角色。如圖 1-11(a)導電粒子導通示意圖(b)導電粒子受壓破裂導通圖。而導電粒子中最外面的絕緣層則扮演位於金凸塊中間的導電粒子不產生導通的狀況，以確保產品的可靠性。如圖 1-12 所示。至於 COG 的封裝流程請參考圖 1-13。

- (1) 清洗 – 先將玻璃基板的 Bonding area 做清洗的動作。

- (2) 預壓接 – 將 ACF 貼合於玻璃基板上的 Bonding area。

- (3) 轉移 – 將 ACF 上的保護層撕除。

- (4) 對準圖形位置 – 將 IC 翻轉 180 度後放置於玻璃基板 ACF 上後，做圖形對位及預接合的動作。

- (5) 正式壓接 – 以高溫高壓的方式做接合

- (6) 完成

COG 特點為成本低、制程簡化、低導通阻值等，但其最大的問題是不易重工，若使用於大尺寸之 LCD 面板上，整片基板因一顆 IC 報廢的風險較高，故 COG 大多使用於 IC 使用量不多的小尺寸面板上。

圖 1-9 COG 成品示意圖

圖 1-10 ACF 導電粒子結構圖[2]

圖 1-11 (a)導電粒子導通示意圖(b)導電粒子受壓破裂導通圖[2]

圖 1-12 導電粒子中絕緣皮膜效能圖[2]

圖 1-13 COG 封裝技術流程圖[2]

## 1-2 研究動機

隨著LCD面板功能性需求的快速提升，如色彩飽和度、反應速度、解析度等，再加上成本的快速下跌，使得LCD Driver IC的封裝技術快速地由TCP轉換為COF，且更走向Fine Pitch的產品設計，也因此開始產生產品品質上可靠度的問題。其可靠度失效的模式主要是Pin to Pin Short，從LCD面板上所呈現的現象為亮線，如圖1-14 LCD面板亮線失效模式，而循著該亮線的位置可以對照出負責該訊號位置的LCD Driver IC，從而發現該顆Driver IC的某兩隻Pin腳發生Short的現象。經由外觀的觀察及微觀分析，使用電子顯微鏡SEM和EDS，判斷應為金離子遷移所造成之Pin to Pin Short。然因其發生機率非常地低，約小於1ppm，故一直無法真正了解金離子遷移發生的真因或條件，更不用談如何預防，而本研究的動機主要是先以重現金離子遷移的發生，以了解金離子遷移發生過程中所必需的條件，做為以後預防金離子遷移發生的基礎。

圖1-14 LCD面板亮線失效模式

## 第二章 文獻回顧

### 2-1 電遷移理論

所謂電遷移(Electromigration)效應是指金屬材料中的原子在施加電場的作用下產生擴散的現象。電遷移現象早於1861年Gerardin針對熔融的錫鉛與汞鈉合金中發現。而開始被廣泛地討論則是在1970年代，因發現於積體電路的導線上發生電遷移損壞現象，主因為在高電流密度下，電子的流動會造成金屬導線中的原子上陽極移動並且堆積形成凸起物(Hilllock)，並在另一端陰極留下孔洞，進而迫使線路斷路或短路，造成元件失效[3,4]，從而開啟電遷移學術上的研究。當時之研究主要著眼於純金屬或是合金中電遷移的觀察，而研究觀察的參數主要是以原子漂移速率(Drift velocity)為主[5,6]。原子漂移速率法是指導線中的金屬原子，藉由電子顯微鏡(Scanning Electron Microscope)觀察在電子風(Electron wind)作用下，直接得到原子擴散漂移的情形，量出原子漂移速度，以做為電遷移研究的數據。

### 2.2 電遷移的驅動力與通量方程式

電遷移的驅動力主要由兩種作用力所組成，一種為電子風力 (Electron wind force)，另一種為電場靜電力(Electrostatic field force)。電子風力是指

對一金屬材料施加電流的作用下，電流中的電子不斷的與原子相互摩擦或碰撞所造成的動量轉移[7]，此動量轉移即摩擦力，亦即牽引力（Drag force）。而電場靜電力是單純的離子原子受到電場的作用所產的驅動力。

經由相關的文獻中[4,8-10]，受電遷移影響的固態金屬原子在反應過程中的擴散通量（J）可寫成表示如下：

$$J = J_{cp} + J_{em}$$

$$= -D \frac{\partial C}{\partial X} + \sum_i CM_i F_i \quad (2.1)$$

其中第一項為 $J_{cp}$ 是化學能梯度(Chemical potential gradient)產生的擴散通量，如下式所示。

$$J_{cp} = -D \frac{\partial C}{\partial X} \quad (2.2)$$

對於純金屬而言，原子間沒有化學式能梯度的存在，所以可以忽略此項。

而 $J_{em}$ 則是指受電子流所影響產生的外加作用力的總和，導致原子擴散之通量。 $J_{em}$ 可分成二種不同作用力，分別為靜電力(Electrostatic force,  $F_{el}$ )、電子風力(Electron wind force,  $F_{wd}$ )和，此二種作用力產生的通量如下式。

$$J_{em} = \sum_i CM_i F_i = F_{el} + F_{wd} \quad (2.3)$$

$$= EZ^* e$$

其中E為電場， $Z^*$ 為有效價數 (effective charge)，e為電子電荷。 $eE$ 的乘積代表一個電子在電場E的作用下所具有的力量。另其中 $Z^*$ 是表示受到電遷移作用力的參數值，對於不同金屬會有不同的值，若為正值，原子受到之作用力會朝向陰極，若為負值，則作用力會朝向陽極。故一般認為靜電力大小會正比於原子本身價電數。

### 2.3 純金屬的電遷移效應

從Huntington的理論中，定義了一個非常重要的物理參數  $Z^*/f$  值[11]。表2.1列出一些純金屬電遷移的 $Z^*/f$ 值與其適用之溫度範圍，由此表可看出，絕大部份的金屬 $Z^*/f$  值為負值，其意義表示為金屬原子是順電子流方向由陰極朝向陽極移動，亦即電子風效應大於靜電力的影響為主要之主宰因子。另外可以發現溫度會影響 $Z^*/f$  值的大小，而金屬本身價數似乎有規率的影響電遷移效應。由表中可以發現金銀銅系列，其原子量越大， $Z^*/f$  越負的趨勢。

表2-1 純金屬的 $Z^*/f$  值[11]

| Metal                      | $Z^*/f$                  | Temp. range (C°)     |

|----------------------------|--------------------------|----------------------|

| <b>Noble metals</b>        |                          |                      |

| Gold                       | -9.5 to -7.5<br>-8.0     | 850-1000             |

| Silver                     | -21 ± 5<br>-8.3 ± 1.8    | 830-890<br>795-900   |

| Copper                     | -5.5 ± 1.5<br>-4.8 ± 1.5 | 845-1030<br>870-1005 |

| <b>Alkali metals</b>       |                          |                      |

| Lithium                    | -2.5 to -1.6             | 90-160               |

| Sodium                     | -3.3 ± 0.7               | 45-80                |

| <b>Divalent metals</b>     |                          |                      |

| Zinc                       |                          |                      |

| to c axis                  | -2.5 ± 0.2               | 366-400              |

| ⊥ to c axis                | -5.5 ± 0.6               |                      |

| Cadmium                    | -2.0 ± 0.2               | 215-290              |

| ⊥                          | -4.1 ± 0.4               |                      |

| Magnesium                  | 2.0 ± 0.3                | 500-580              |

| <b>Trivalent metals</b>    |                          |                      |

| Aluminum                   | -30 to -12               | 480-640              |

|                            | Comparable               | 450-610              |

| Indium                     | -11.5                    | 115-150              |

| Gallium<br>(liquid)        | -1.3                     | 18-312               |

| Thallium                   | -4.0 ± 0.5               | 233-303              |

| <b>Transition metals</b>   |                          |                      |

| Nickel                     | -3.5                     | 1000-1400            |

| Iron                       | +2 ± 1                   | 700-1300             |

| Cobalt                     | +1.6 ± 0.3               | 1260-1360            |

| Platinum                   | +0.28 ± 0.04             | 1480-1670            |

| <b>Refractory metals</b>   |                          |                      |

| Zirconium                  | +0.3                     | 930-1730             |

| Uranium                    | -1.6 ± 0.1               | 830-1100             |

| <b>Quadrivalent metals</b> |                          |                      |

| Lead                       | -47/f                    | 250                  |

| Tin                        | -80/f                    | 190                  |

| Tin                        | -18                      | 180-213              |

## 第三章 實驗方法與步驟

### 3-1 實驗材料

本實驗的主要材料包含COF基板、已完成金凸塊之晶片和覆晶填充膠材。

#### 3-1.1 COF基板材料

本實驗之COF基板之設計，如圖3-1(a)COF Tape layout drawing (b)為COF Tape 內引腳局部放大示意圖，於內引腳間距達到業界目前最小間距25um pitch，同時以梳狀結構設計為主架構，連接外部線路部份則以大面積之銅箔連接，做為接通電源接點。製作廠商為日本住礦公司，製作方法為半加成法(Semi-additive)，如圖3-2 所示。

- (1) Polyimide film – 以Polyimide Film 38um為底材。

- (2) Sputter & flash Cu plate - 以濺鍍方式鍍上一層薄薄的銅做為種子層。

- (3) Double side dry resist film laminate – 於料帶的上下兩面都貼上一層乾式的光阻。

- (4) Double sides expose –以玻璃光罩繪製高解度的線路做為影像轉移的治具，然後利用UV光透過玻璃光罩將欲蝕刻處的光阻進行光裂解反應。

- (5) Develop - 將已經經過UV光裂解的光阻部份以溶劑溶解去除並保留未裂解的光阻。

- (6) Circuit Cu Plate - 以化學鍍方式於種子層銅表面鍍上約8um純銅。

- (7) Chemical PI etching - 以化學藥劑將欲開孔的位置蝕刻出來。

- (8) Resist strip - 將不要的光阻以化學藥液剝除。

- (9) Etch flash Cu - 將料帶上多餘的種子層銅以化學藥液去除。

- (10) Finish Plate - 已形成線路之銅線路再以化學鍍鍍上錫約0.2um，最後再塗佈上一層日保麗公司的NPR-3300綠漆，做為保護層。其結構圖，如圖3-3所示。

圖3-1 (a)COF Tape layout drawing

(b)COF Tape 內引腳局部放大示意圖

圖 3-2 COF 基板半成加法製作流程圖[10]

圖 3-3 COF 基板結構圖

### 3-1.2 完成金凸塊之晶片

將實驗樣品之wafer，使用Sputter/Plating的方式，於鋁墊上長成約15um高的金凸塊，做為COF接合時使用。如圖3-4所示。

圖3-4 金凸塊結構示意圖

### 3-1.3 覆晶填充膠材

本次實驗用的覆晶填充膠材為日本Namics 8462-21, 其膠材規格特性, 如表3-1所示。

| Item                                  | Unit            | 8462-21 | Notes                     |

|---------------------------------------|-----------------|---------|---------------------------|

| Viscosity                             | mPa.s           | 530     | 10rpm,1 min@25°C          |

| Leveling propaty(means contact angle) | mm              | 5       | 5mg Potting diameter@25°C |

| Penetration speed@70°C                | sec.            | 44      | G50um,L20mm               |

| Gel time@150°C                        | sec.            | 124     | @150C                     |

| Volume resistivity                    | Init.           | 4.4E+16 | 500V,1min                 |

|                                       | after PCT 20Hrs | 1.7E+16 |                           |

| Dielectric constant                   |                 | 3       |                           |

| Dielectric loss tangent               | %               | 0.8     |                           |

| Electrical conductivity               | µS/cm           | 17      | after PCT 20Hrs           |

| Sodium content                        | mg/l            | 0.01    | after PCT 20Hrs           |

| Chloride ion content                  | mg/l            | 0.1     | after PCT 20Hrs           |

| Coefficient of linear expansion       | ppm/°C          | 71      | at TMA                    |

| Glass transition                      | °C              | 118     |                           |

| Bending modulus                       | GPa             | 2.9     |                           |

| Bending strength                      | Mpa             | 60      |                           |

表 3-1 覆晶填充膠材規格表[11]

### 3-2 實驗方法與步驟

本實驗的重點為驗証金離子遷移之發生，故實驗的流程主要可區分為三大部份，第一部份為實驗試片之製作，第二部份為實驗試片的加速測試方式，第三為實驗試片之微觀分析。參考圖3-5 金離子遷移實驗流程圖。

圖3-5 金離子遷移實驗流程圖

### 3-2.1 試片製備

收集人體皮膚所掉落之膚屑與身體上之汗漬，使其不規則掉落或沾附至已長完金凸塊的晶片表面上，然後將這些實驗用晶片，放於可升溫至約300°C鐵板上以300°C高溫加熱約15~20sec，目的是使這些晶片表面上的Particle可以稍微融化且完全附著於晶片表面上，然後使用日本新川公司的覆晶式內引腳接合機(COF-1000)將這些已沾附上Particle的晶片與COF基板，以高溫400°C高壓100N的方式，使COF基板銅引腳上的錫轉變成熔融狀態後，可與已沾附上Particle晶片上的金凸塊達到金錫共晶的狀態，形成所謂的內引腳接合。再接下來是使用台灣翔勝公司的四軸四頭封膠機將日本Namics公司的覆晶填充膠材8462-21以虹吸原理將這些已完成內引腳接合的樣本完成膠材填充，再經由130°C的預烘烤20分鐘先達到初步的固化，最後再經過一道完整8個小時烘烤120°C，完成整個實驗樣品的制作。

### 3-2.2 金離子遷移的加速測試

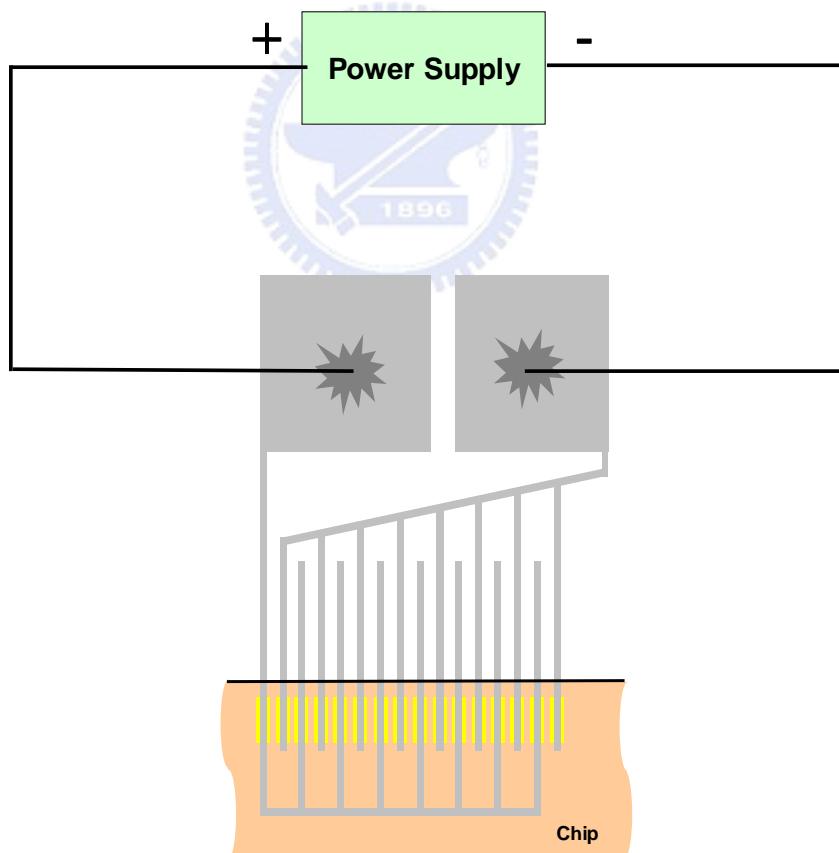

將已完成之實驗樣品，裁剪成類似可Bonding於面板上之單一顆成品，再以鍍接的方式將電源線鍍接於軟性基板的測試墊上，為了減少此鍍接點之異常發生，再於鍍接點上加塗環氧樹脂膠材，以達到保護及固定效果。然後，再接上可提供40V電壓之電源供應器。如圖3-6實驗試片通電示意圖。同時將實驗樣品置放於85°C 85%RH的恆溫恆溼機中，如圖3-7，使其加速發生金離子遷移現象。

圖3-6 實驗試片通電示意圖

圖3-7 Temperature & Humidity Storage Test Machine

### 3-2.3 試片加速測試後外觀分析

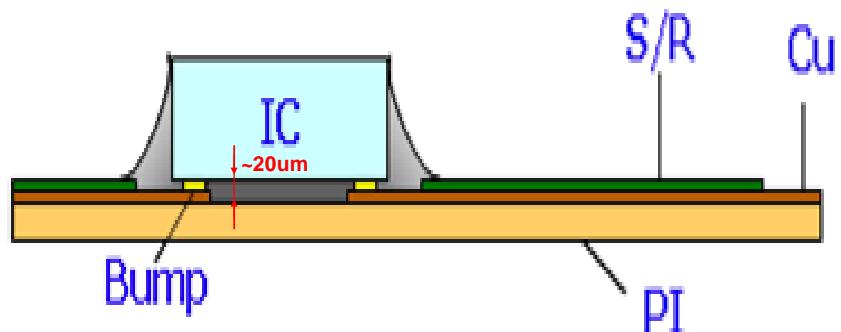

由於實驗試片之軟性基板為Polyimide 材質且透高率約70~80%，且經過 Bonding 後軟性基板和IC表面間距只有~20um(如圖3-8)，使得塗佈於實驗試片上之環氧樹脂呈現透明之淡灰色。因此，可以直接使用NIKON MM-800工具顯微鏡經由正面打光後，由正面可觀察到(1)膠材和PI及IC表面的結合狀態(2)Gold Bump與Gold Bump間的狀況。工具顯微鏡放大倍率由25X~500X，如圖3-9，同時其觀察結果再經由顯微鏡附屬的照相系統拍照取像。

圖3-8 COF封裝完成結構圖

圖3-9 NIKON MM-800工具顯微鏡

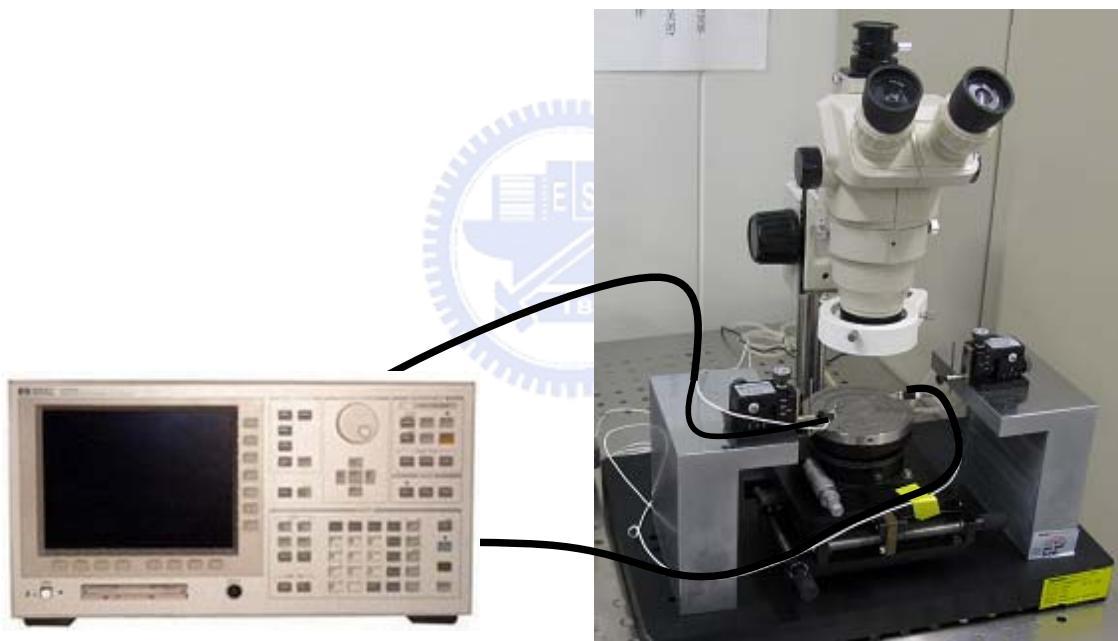

### 3-2-4 Mini- probe和I-V characteristic curve 量測分析

為觀察實驗試片發生金離子遷移後之失效模式，先以萬用表量測有發生金離子遷移的腳位之間的阻抗與正常的腳位是否有差異，另外將碳粉堆積於Gold Bump間故意製作確定Pin to Pin Short的標準樣品，最後再以Mini-Probe和I-V characteristic curve HP4155儀器量測該實驗樣品之電流-電壓曲線，做為正常品和異常品之比較參考。

圖 3-10 Mini-probe & I-V curve machine photo

### 3-2.5 試片的破壞分析

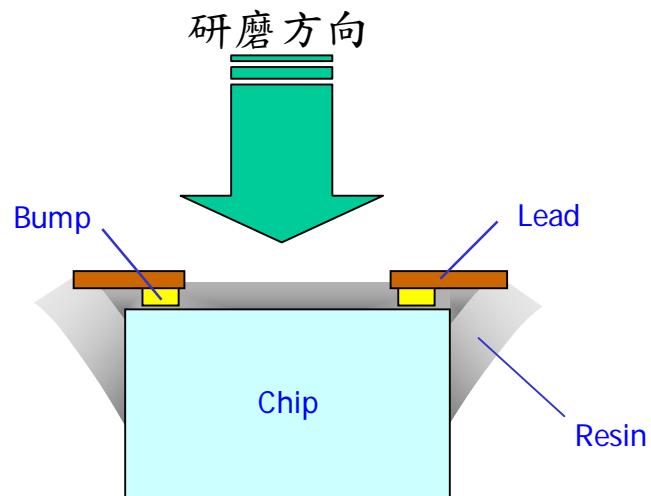

將實驗試片中，經由工具顯微鏡觀察後，已可初步判定為具有金離子遷移的樣品進行破壞模式的分析。首先將樣品上的軟性基板用手將其撕除，再將撕除後的晶片，放置於灌膠模具中，填充入熱融性塑膠，待放置一段時間固化後，再依序以不同號數600、1200、2500、4000的SiC砂紙做研磨，研磨的方式是由晶片的金凸塊正面朝晶片線路面研磨，如圖3-11 試片研磨方向圖，再依續以1um、0.3um、0.05um的氧化鋁粉進行拋光，使得晶片線路上的環氣樹脂和凸塊距離晶片線路面小於5um，以便後續的進階微觀分析。

最後將拋光好的試片濺鍍上一層鉑膜，除了防此試片氧化外，同時增加Scanning electron microscope(SEM)觀測的導電性，如圖3-12。為了確保試片觀察的精確性，決定以Transmission electron microscopy(TEM)的方式，如圖3-12，做該可能發生金離子遷移的位置點做切片取樣分析，再以SEM做微觀分析，另外再以Energy Dispersive Spectrometer (EDS)做為鑑定試片特定區域成分組成的比例。

圖3-11 試片研磨方向圖

JOEL JSM-6701F

**Resolution:**

1 nm@15 kV ; 2.2 nm@1 kV

**Magnification:**

25 X To 650,000 X

**Acc. Voltage:**

0.5 kV To 30 kV( in 0.1 kV step )

**Sample Size:**

40mm(diameter) x 30mm(height)

**Movement Range:**

X / Y / Z = 70mm / 50mm / 1.5~25mm

**Tile:**

-50 ~ 600 / Rotation : 0o ~ 360o

圖 3-12 SEM machine photo[15]

## JOEL JEM-2100F

**Resolution:**

lattice image 0.1nm,

point image 0.19nm

**Magnification:**

50X To 1,500,000 X

**Acc. Voltage:**

80 kV To 200 kV

Camera Length

80-2000mm

**Sample Size:**

3mm in diameter

**Movement Range:**

X / Y / Z = 2mm / 2mm /  $\pm$ 0.1mm

**Tile:**

$\pm$ 250

圖 3-13 TEM machine photo[15]

## 第四章 實驗結果與討論

### 4-1 試片加速測試後外觀分析結果

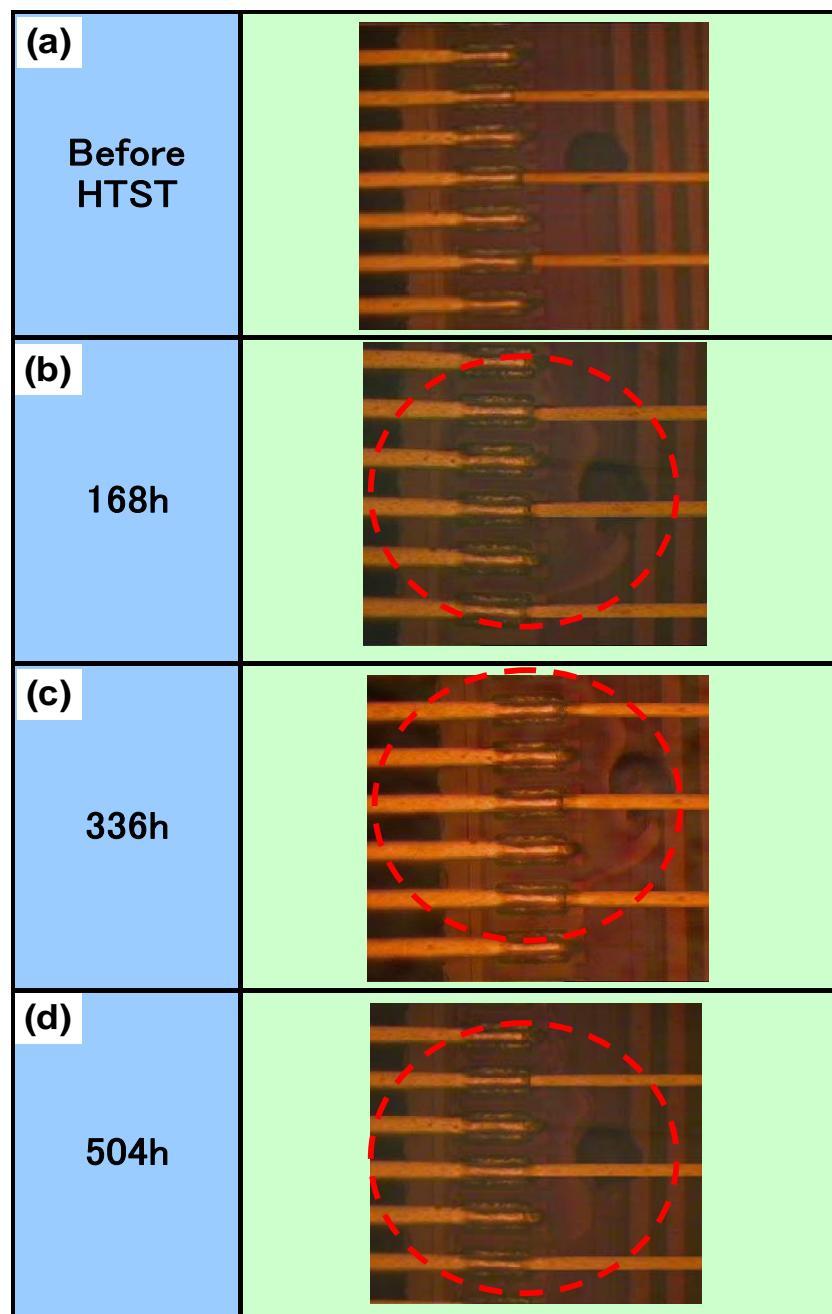

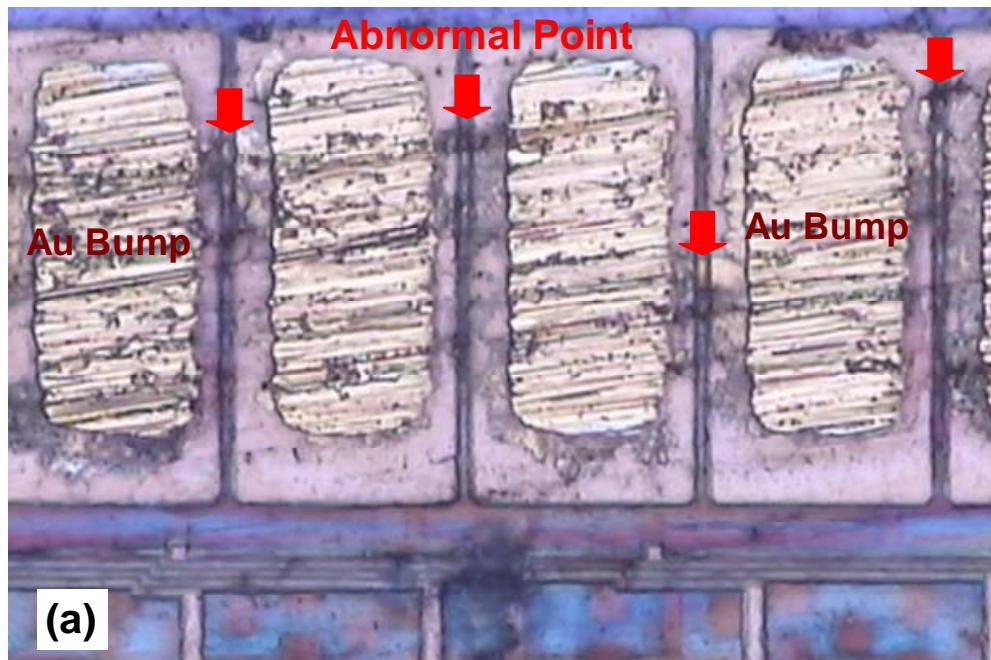

實驗試片經由通電40V後放置於85°C 85%RH的環境中，進行Temperature & Humidity Storage Test(THST)分別於經過96Hrs、168Hrs、336Hrs、504hrs後，以工具顯微鏡觀察其晶片表面狀況，由圖4-1晶片與封膠樹脂分層圖可以得知當試片經過環境測試96Hrs至168Hrs之間，晶片表面與封膠樹脂間產生了分層(Delamination)現象。

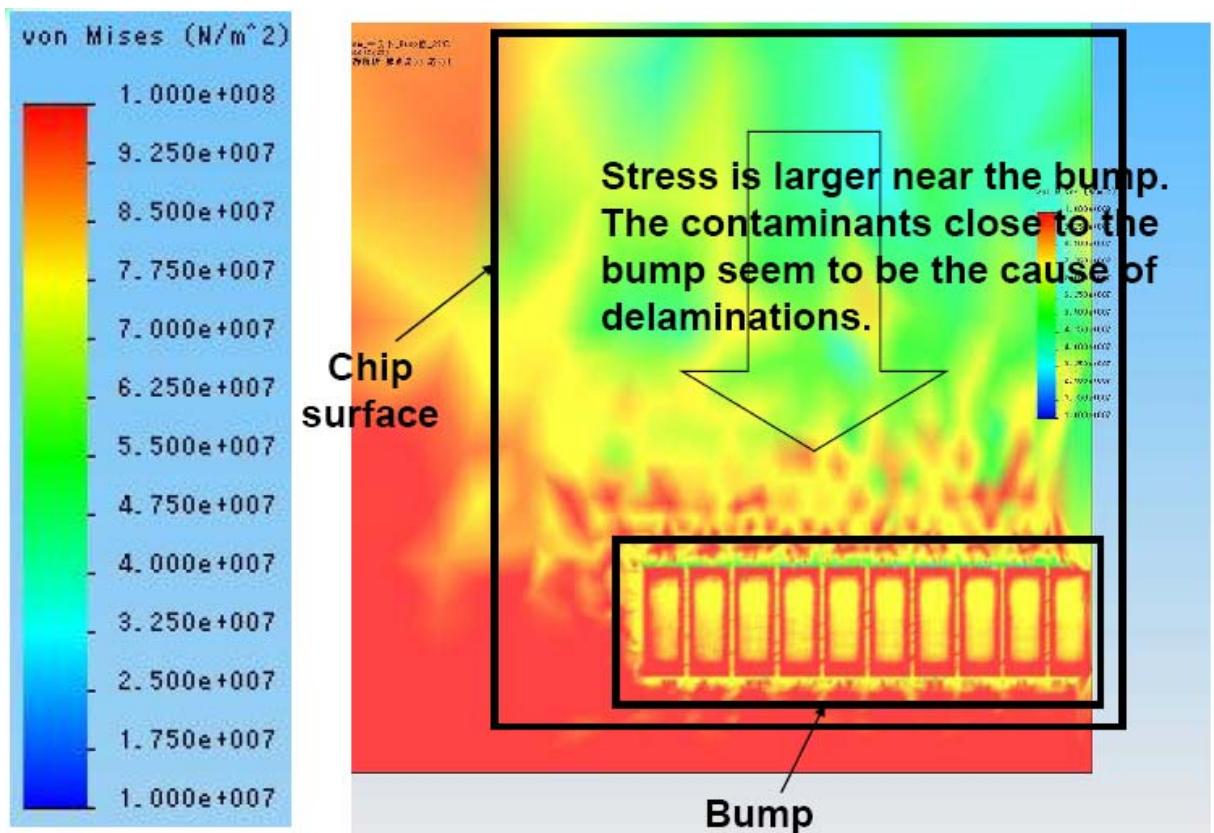

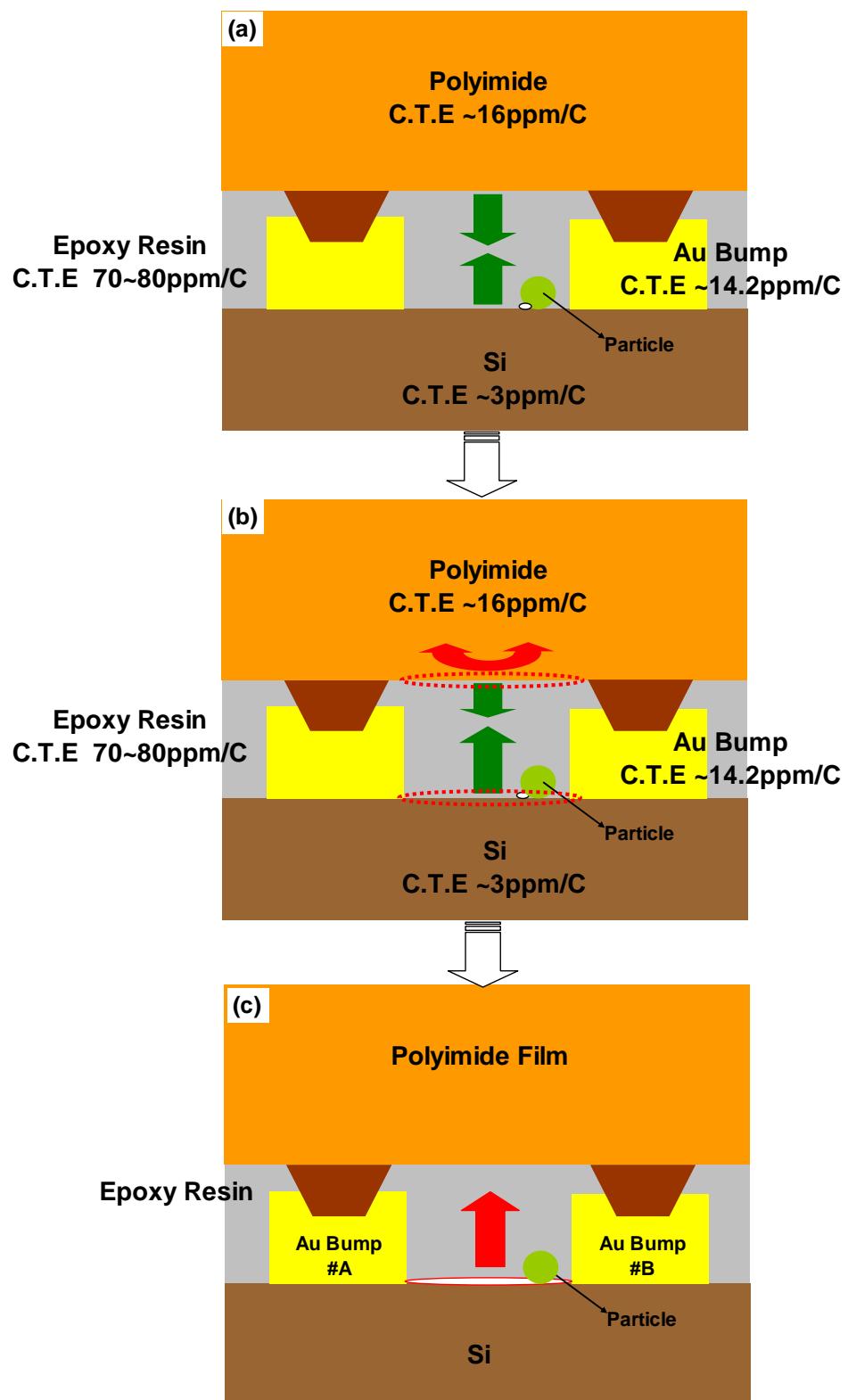

至於晶片表面與封膠樹脂間分層(Delamination)的主要原因為，有異物掉落於晶片上凸金塊的邊緣，經由受熱後完成附著於晶片表面上，且因COF的封膠方式是以虹吸原理將環氧樹脂以毛細現象填滿晶片表面，而由於晶片表面上沾附著異物，使得膠材無法完全填充滿，異物與晶片表面上有微小的間隙，造成膠材的黏合強度變弱，當試片經過環境高溫高溼的作用下，試片封裝過程中所產生的應力，以電腦模擬的方式，可以發現應力主要集中於金凸塊的邊緣，如圖4-2 COF電腦模擬應力分佈圖，再加上各材料間的膨脹係數的差異，軟性捲帶基板的Coefficient of Thermal Expansion(CTE)約為16ppm/°C，環氧樹脂的CTE約為70~80ppm/°C，金凸塊的CTE約為14.2ppm/°C，晶片本身的CTE約為3ppm/°C，因而使得環氧樹脂與晶片表面產生分層(Delamination)的現象。如圖4-3 環氧樹脂與晶片表面分層過程示意圖。

當可靠度測試進行至1008Hrs後，發現於污染物附近的金凸塊與金凸塊中間，經由工具顯微鏡可以隱約看到好像有一層物質產生於晶片的保護層上，如圖4-4 所示。

圖4-1 (a) Before HTST 之工具顯微鏡照片

(b) HTST 168hrs後晶片與封膠樹脂分層圖

(c) HTST 336hrs後晶片與封膠樹脂分層圖

(d) HTST 504hrs後晶片與封膠樹脂分層圖

圖4-2 COF電腦模擬應力分佈圖 [12]

圖4-3 環氧樹脂與晶片表面分層過程示意圖

圖4-4 1008Hrs後金凸塊間表面異常圖

## 4-2 Mini-probe和I-V characteristic curve 量測分析結果

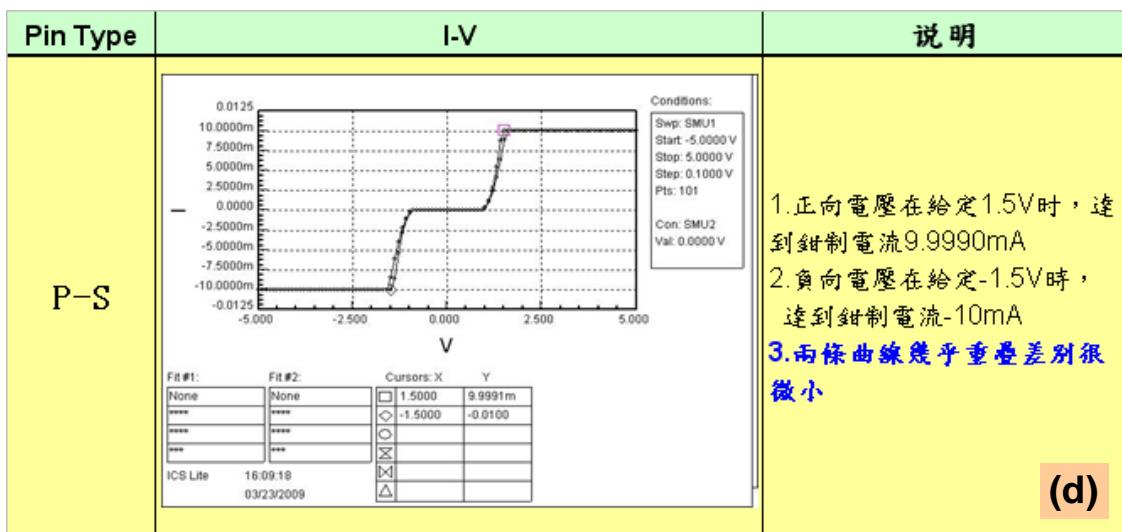

將實驗樣品中的腳位做明確定義與區分，分別定義如下：正常的腳位以P代表Pass pin，以S代表異常金離子遷移的腳位，以N代表故意用碳粉制造不良的Pin to Pin short 脚位。首先使用萬用表量測不同腳位間的阻值，從表4-1中可以得知不管是正常腳位P-P間，正常腳位與金離子遷移的腳位P-S，正常腳位與碳粉不良的腳位P-N，還是金離子遷移的腳位S-S在阻值的量測上看不到明顯的差異，只有於故意用碳粉制造不良的Pin to Pin short 脚位間可以測試到明顯的阻值差異，故無法以量測阻抗的方式來判定金離子遷移失效模式的發生。

表4-1 金離子遷移樣品阻抗量測表

| Sample | Pin Type | 阻值     |

|--------|----------|--------|

| 1      | P-P      | 18.46M |

|        | S-S      | 19.15M |

|        | N-N      | 4.15K  |

|        | P-S      | 18.60M |

|        | P-N      | 17.47M |

| 2      | P-P      | 11.42M |

|        | S-S      | 10.78M |

|        | N-N      | 0.86K  |

|        | P-S      | 11.50M |

|        | P-N      | 8.82M  |

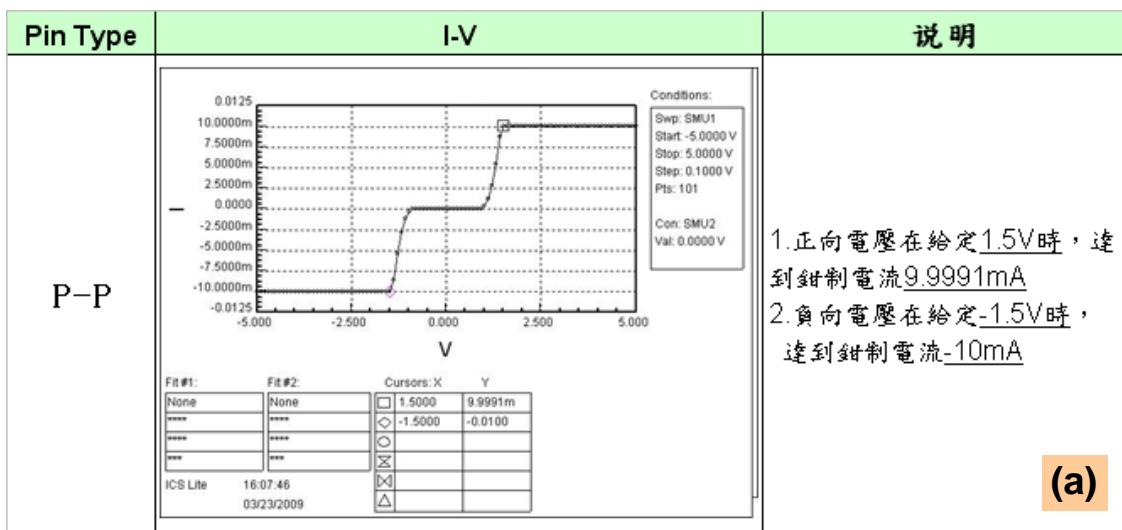

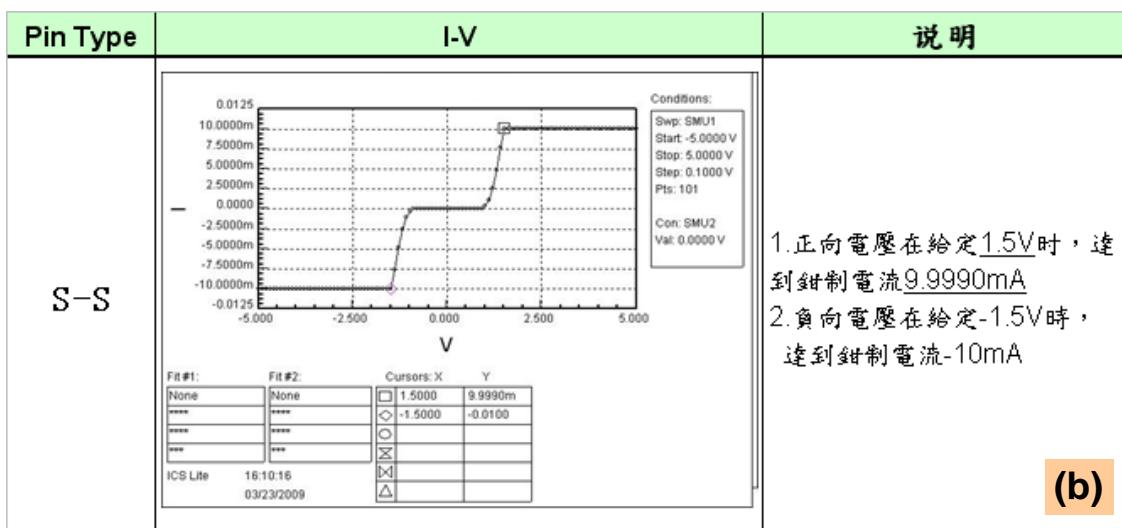

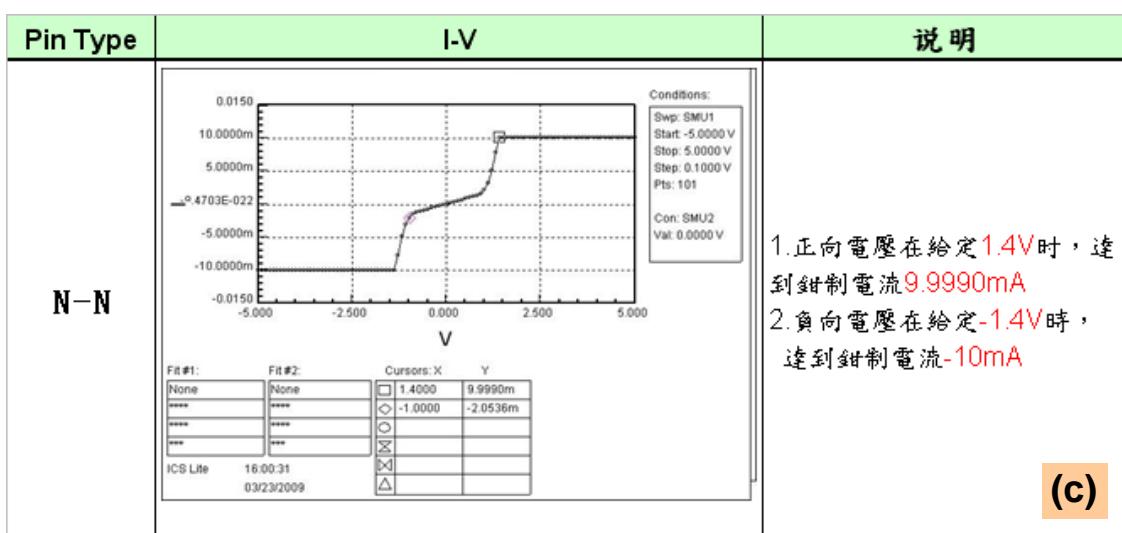

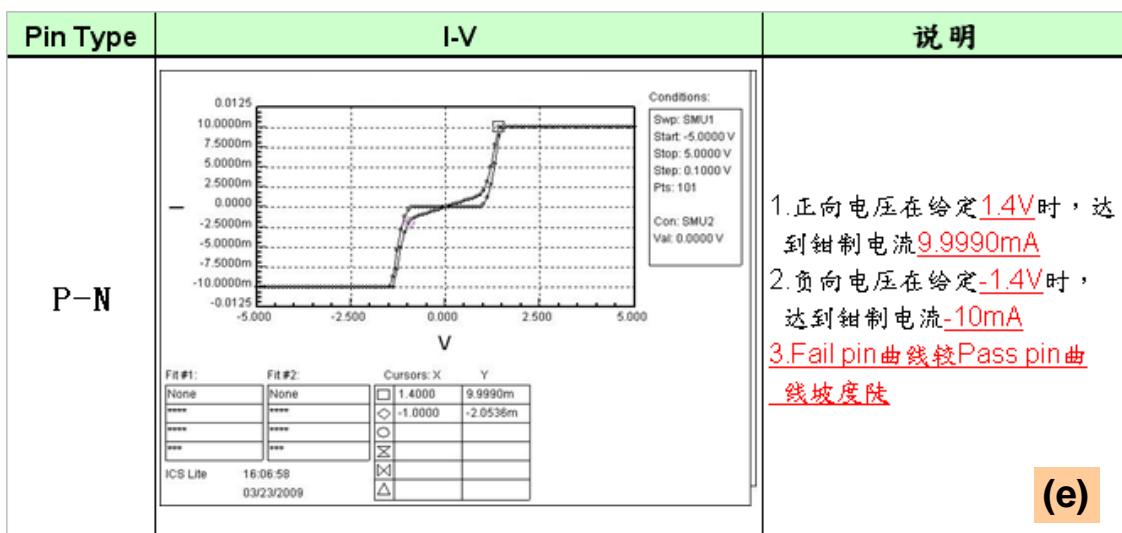

使用半導體參數量測儀HP4155，以給定電壓測電流的方式，量測金離子遷移實驗樣品之I-V curve是否有異常，將第一顆sample分別從P-P、S-S、N-N、P-S、P-N量測I-V curve，從圖4-5(a)中可看到P-P正向電壓在給定1.5V時，達到鉗制電流9.9991mA；負向電壓在給定-1.5V時，達到鉗制電流-10mA。圖4-5(b)中可看到金離子遷移的S-S腳位正向電壓在給定1.5V時，達到鉗制電流9.9990mA；負向電壓在給定-1.5V時，達到鉗制電流-10mA。從圖4-5(d)中可以看到圖4-5(a)與(b)的重疊後，發現正常腳位與有金離子遷移的腳位兩條曲線幾乎重疊，差別很微小。而比對故意以碳粉造成short fail的腳位N-N，可從圖4-5(c)看到正向電壓在給定1.4V時，達到鉗制電流9.9990mA；負向電壓在給定-1.4V時，達到鉗制電流-10mA。將圖4-5(a)與(c)重疊後，可以發現正常腳位與故意制造Fail的腳位有明顯的差異，故意制造Fail的腳位給定電壓只要1.4V即可達到相同的鉗制電流，同時其Fail腳位的曲線較正常腳位Pass pin的曲線坡度陡。

從HP4155的量測結果來看，同樣無法以I-V curve量測方式來做為監控或確認金離子遷移失效模式發生與否的依據。

(a)

(b)

(c)

圖4-5 金離子遷移實驗樣品之HP4155分析結果

(a)P-P (b)S-S (c)N-N (d)P-S (e)P-N

### 4-3 試片的微結構分析

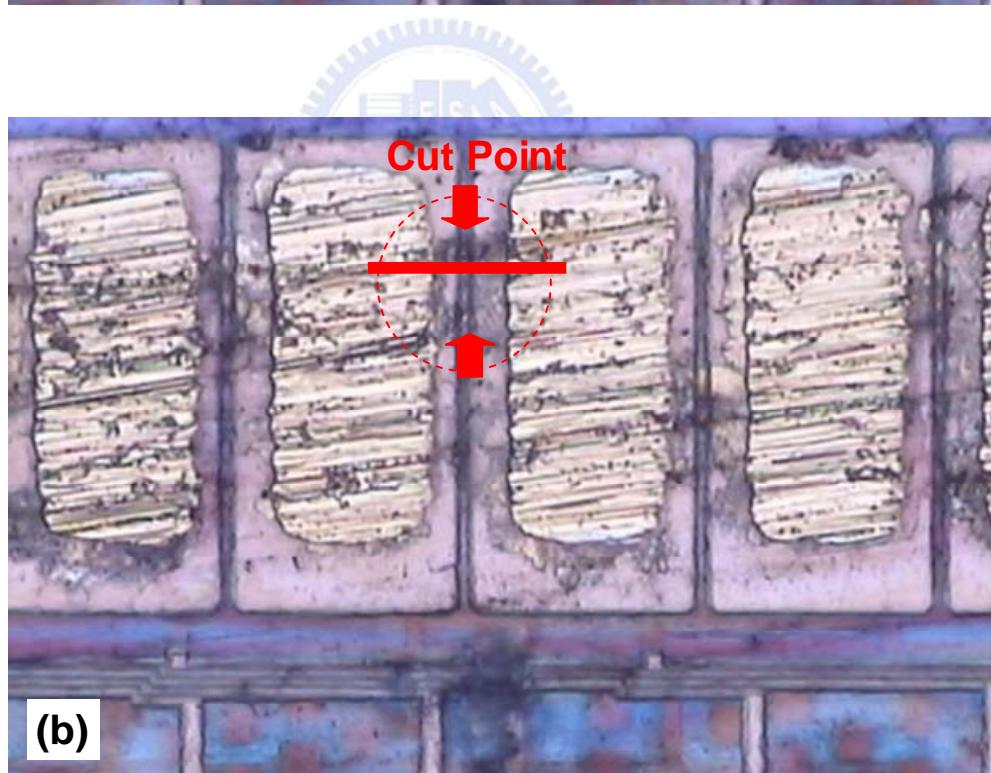

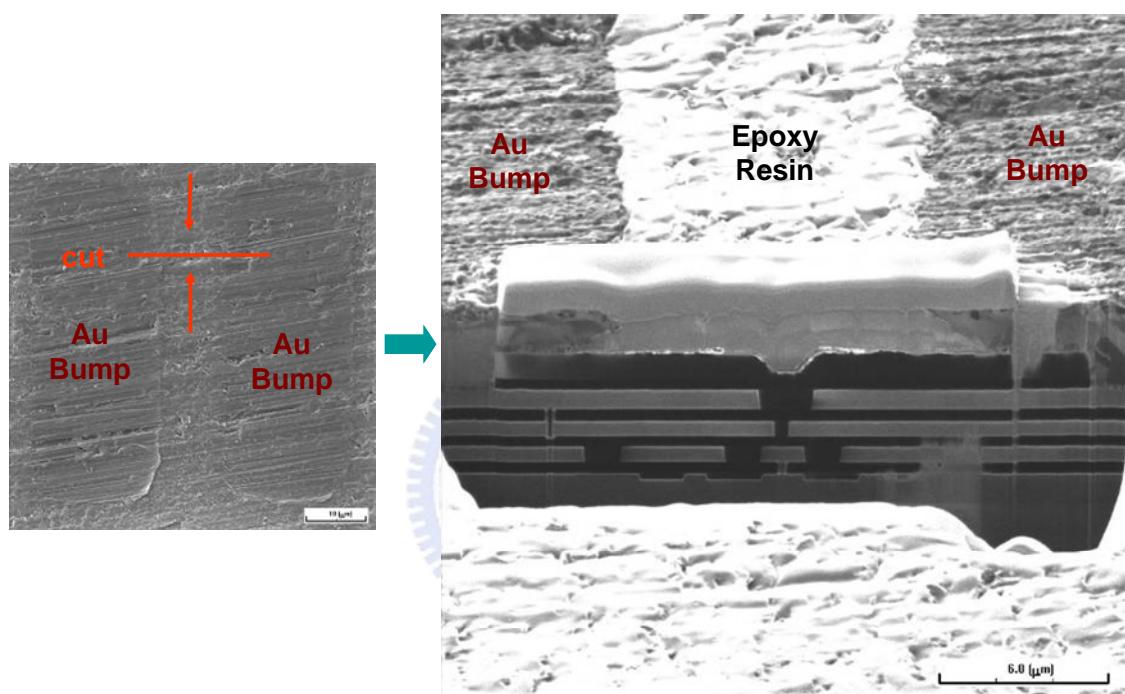

將經由加高壓40V且經可靠度測試1008hrs後，發現有異常的樣品經由正面研磨至約5um的厚度後，經由工具顯微鏡可明確觀察到位於金凸塊與金凸塊中間，確實有一層類似於金屬的物質，如圖4-6(a)中紅色箭號所示的異常位置，同時以4-6(b)紅色虛線該異常位置做為Transmission Electron Microscopy (TEM)取樣試片的位置，TEM取樣後的試片如圖4-7所示。

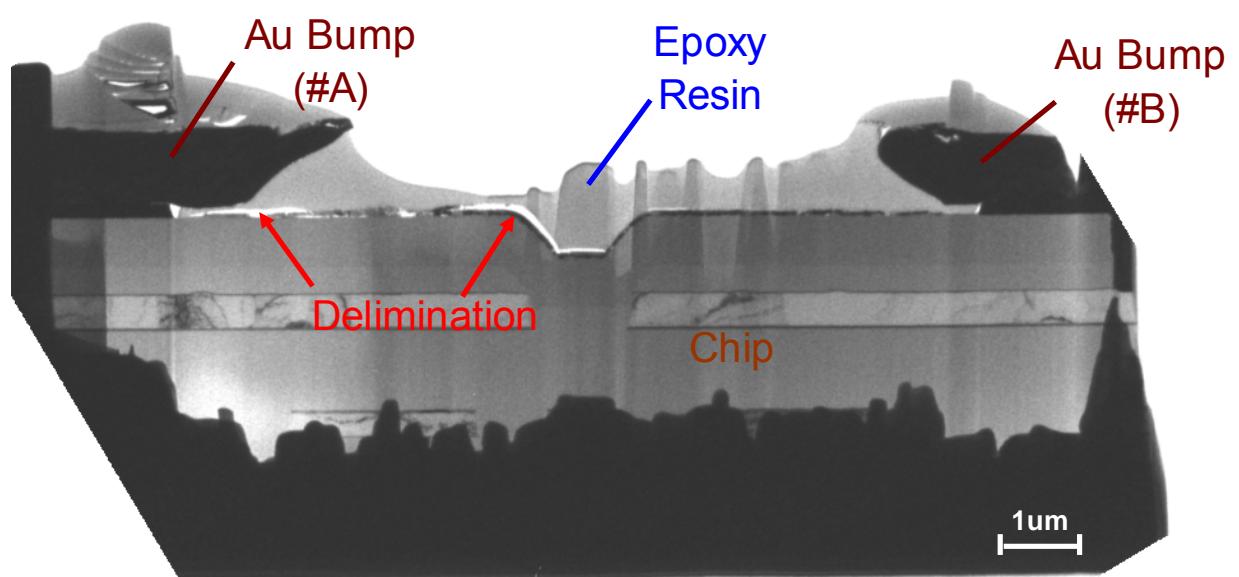

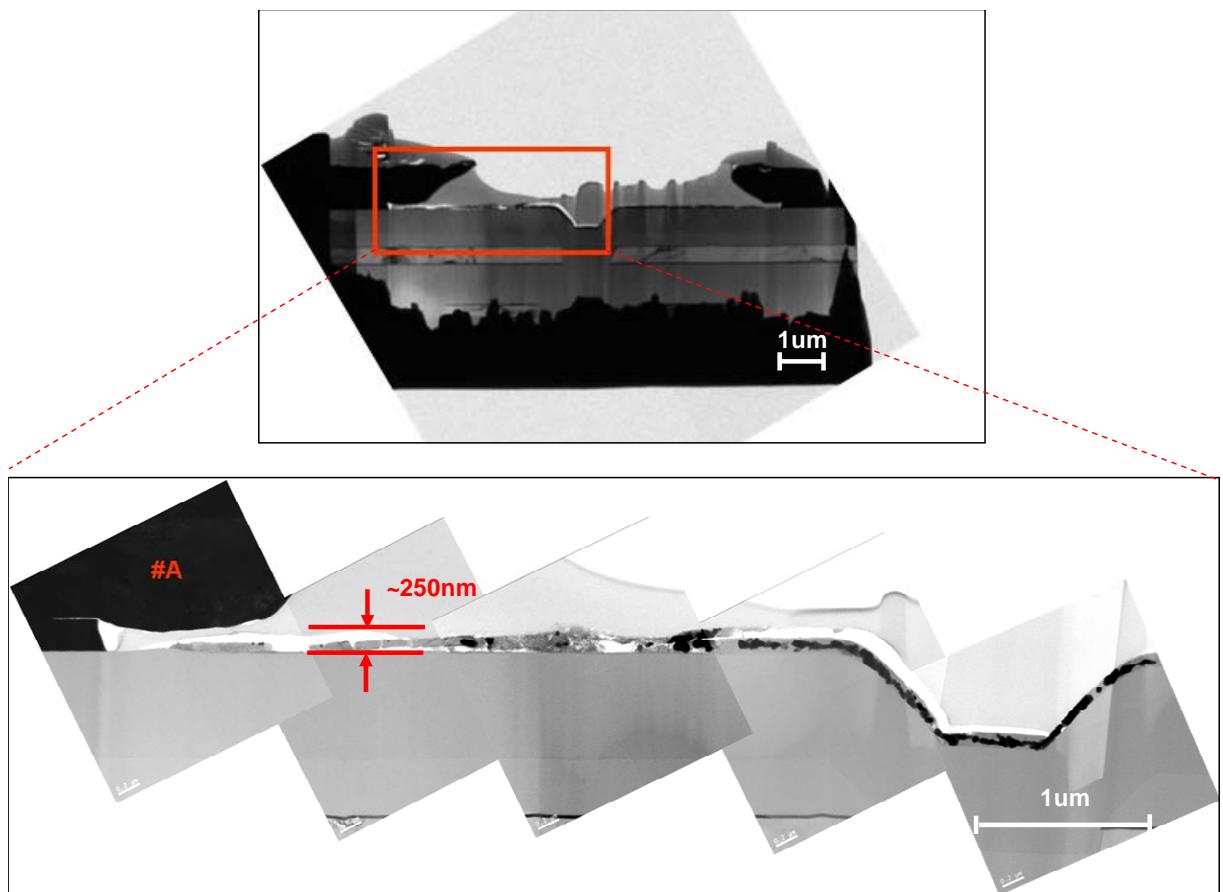

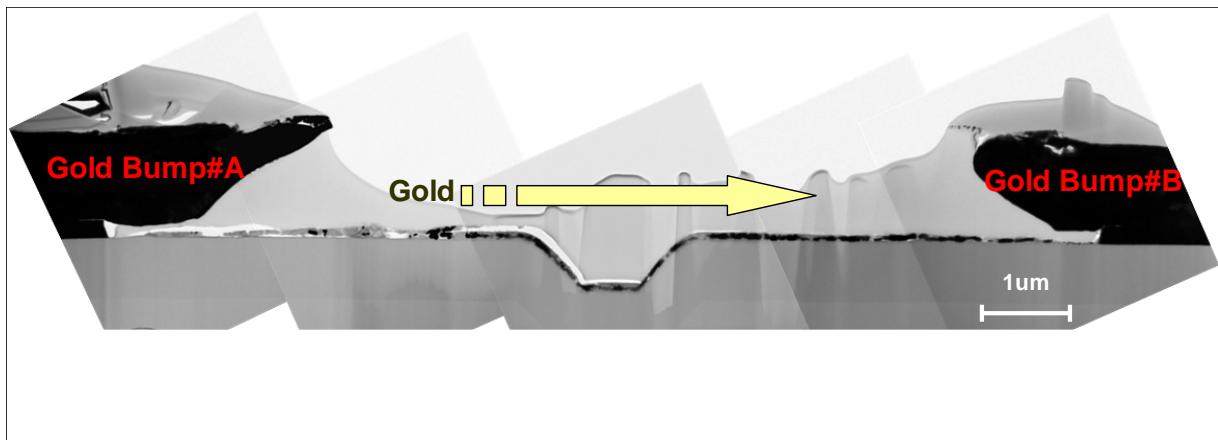

從圖4-8中可以看到確實在金凸塊#A與#B之間的Epoxy Resin和晶片保護層間發生分層(Delamination)現象。位於此分層上有薄薄的深黑色和深灰色物質的東西連接著Gold Bump#A 和 Gold Bump#B，且靠近Gold Bump#A的分層間隙較大，其中以深灰色的物質居多，伴隨著少部份的深黑色物質，如圖4-9(a)所示，而靠近Gold Bump#B的分層則看不到間隙，其中卻是深黑色物質為主，如圖4-10(a)所示。

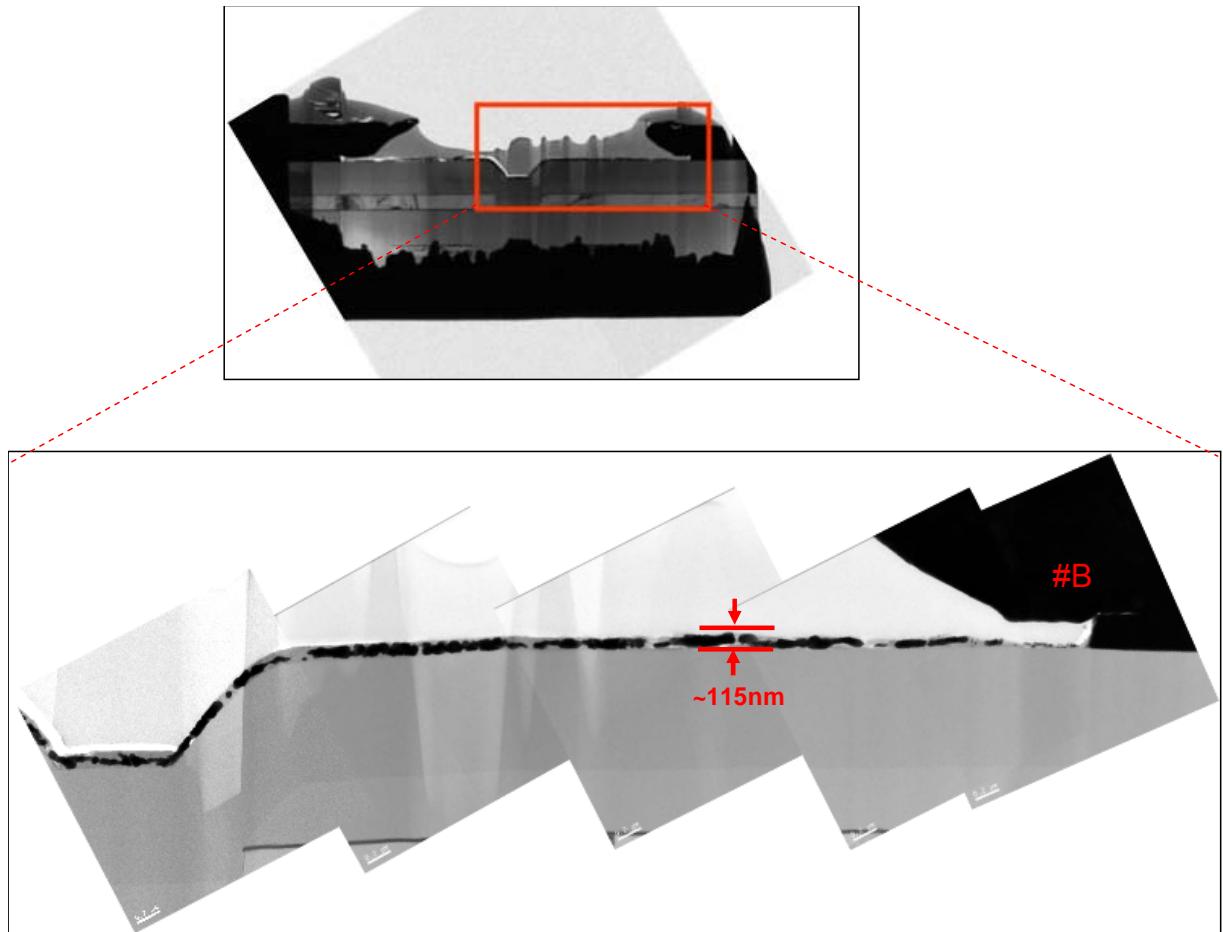

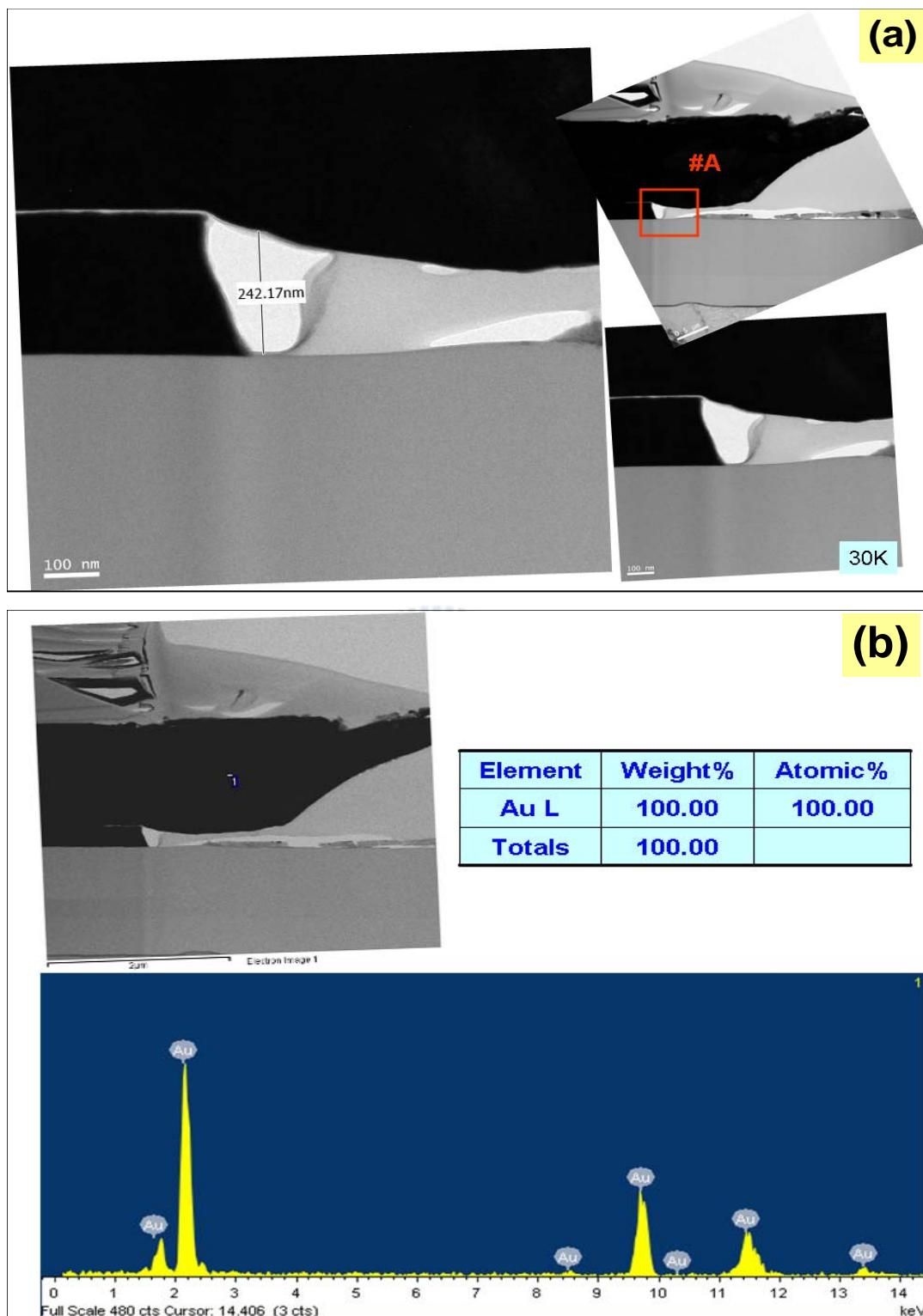

從圖4-11(a)放大至30K的SEM照片中可以發現其分層的間隙約只有250nm，深黑色的部份為金凸塊，以EDX做元素分析確認，打出的成分即為100%金原子，如圖4-11(b)所示。依金凸塊#A至#B下的分層，逐一做元素分析，從圖4-12(b)的元素分析，可得知分層間深灰色的物質元素中，包含了Oxygen(Atomic 42.65%)、Silicon(Atomic 28.4%)、Chlorine(Atomic 3.86%)、Calcium(Atomic 16.18%) 和Copper(Atomic 8.92%)，其中Oxygen、Silicon、

Copper佔總Atomic 79.97%應為該晶片本身所自帶之元素，另外發現的 Chlorine和Calcium佔總Atomic 20.03%，則應該是從實驗樣品中所製造的 Particle，因吸溼再加上高溫的環境中逐漸地解離出來的元素，完整地分散於 整個分層間。另外，分層間深黑色物質則為金原子，如圖4-13(b)中所示。金 原子的分佈狀況，則是由Gold Bump#A中逐漸地往Gold Bump#B中累積增 加，此種現象可從圖4-13中得知。

圖4-6 (a)異常樣品研磨至5um厚度後金凸塊間表面物質狀況

(b)正面研磨後TEM取樣位置圖

圖4-7 TEM取樣之試片圖

圖4-8 實驗樣品金離子遷移SEM image

圖4-9 金離子遷移靠近Gold bump#A分層位置放大圖

圖4-10 金離子遷移靠近Gold bump#B分層位置放大圖

圖4-11 (a)金凸塊邊緣放大SEM 30K image(b)金凸塊EDS分析圖

圖4-12 (a)分層放大SEM 30K image(b)分層中深灰色物質EDS分析圖

圖4-13 (a)分層放大SEM 30K image(b)分層中深黑色物質EDS分析圖

圖4-14 金離子遷移之金原子移動示意圖

#### 4-4 金離子遷移造成產品失效機制之探討

彙總4-1至4-3的觀察分析，金離子遷移發生而造成產品失效的機制可歸納為以下幾個因素：

- (1) 位於晶片金凸塊附近具有Cl離子的Particle。

- (2) 因各材料層之間的熱脹冷縮不一造成封膠層與晶片表面的分層。

- (3) 產品於正常的使用環境中吸收一定的溼氣，且於高溫的環境下，Particle中的Cl離子開始游離於分層間。

- (4) 產品走向Fine Pitch，金凸塊間的間距從45um朝著25um和20um前進使得金凸塊間高電場的持續作用，更趨明顯。

- (5) 當金凸塊的金離子受Cl離子及高電場的影響而持續地解離出來往另一端的金凸塊方向移動，當金離子一接觸到另一端的金凸塊時，則立即產生Short的現象。

其中含Cl離子的Particle與溼氣的殘留為發生金離子遷移的主要關鍵因素，其可能發生的機制過程表示如下：如圖4-15所示。

圖4-15 金離子遷移失效機制發生過程示意圖

(a) 金凸塊間有含Cl離子之Particle且在溼氣及溫度的影響下

出現分層

(b) Cl離子解離至整個分層

(c) Cl離子使Gold Bump#A的金離子產生解離現象後金離子

持續地往Gold Bump#B移動至接觸到Gold Bump#B則產

生Short失效現象

## 第五章 結論

由於金離子遷移失效模式並無法於產品的生產過程中，經由檢測或觀察的方式來攔截，即使是消費者使用後所發生的失效現象，也只能用破壞性的分析來做確認，因此失效現象只是非常微小的Leak現象，不易使用I-V curve或量測阻抗的方式做為判斷的依據，故而至目前為止金離子遷移一直為LCD Driver IC封裝業者間的一個非常困擾且無法徹底解決的問題。經由此次模擬實驗的結果，可以證明LCD Driver IC中金離子遷移失效模式的存在，同時其發生的必要條件為具有氯離子附著於產品晶片表面上，當產品經過一段時間的使用，隨著使用環境的吸溼，溫度的升降衝擊，晶片上金凸塊的金離子受到氯離子的催化，再加上電場的效應，使用金離子不斷地遷移往陽極的金凸塊堆積，當金離子接觸到當陽極的金凸塊後，即造成Short的可靠度失效模式。

## 參考文獻

1. Toyo Metallizing Co., “Non-Adhesive,2 Layer-Type FPC Materials ”METALOYAL””, pp5(2002)

2. Sony Chemicals, “ACP\_Chinese”,pp2-pp5(2004)

3. V.B. Fiks, Sov. Phys.,Solid state., 1, pp.14-28(1959).

4. H. B. Huntington and A. R. Grone, J. Phys. Chem. Solids, 20, pp.76-87(1961).

5. I.A. Blech, and C. Herring, Appl. Phys. Lett., 29, 131(1976).

6. I.A. Blech, J. Appl. Phys., 47, 1203(1976).

7. H. B. H and A. R. Grone, J. Phy. & Chem. Solids, Vol. 20, Issue1-2, pp.76-87(1961).

8. K. N. Tu, J. W. Mayer, and L.C. Feldman, Pearson Education POD, 355 (1996)

9. K. N. Tu, Physical Review B, 45, 3, 1409 (1992)

10. I. A. Blech, and C. Herring, Appl. Phys. Lett., 29, 131 (1976)

11. H. B. Huntington, “Diffusion in Solids : Recent Developments”, edited by A. S. Nowick and J. J. Burton, Academic Press, New York, 1975, pp.303~352.

12. 3M, “TFT COF to customer presentation” , pp15(2002)

13. Namics, “COF/Capillary Flow type Underfill Resin Materials” , pp6(2004)

14. Namics, “Namics COF resin 8462-220A1” , pp13(2008)

15. 關於泛銓科技公司TEM&SEM相關資訊請參閱其官方網站，網址：

<http://www.msscorps.com/>