國立交通大學

電子工程學系 電子研究所碩士班

碩士論文

實現於標準金氧半製程之單晶整合光接收器設計

Design of Monolithically Integrated Optical Receiver

in Standard CMOS Process

研究 生：邱珣益

Hsiang-Yi Chiu

指導教授：蔡嘉明 教授

Prof. Chia-Ming Tsai

中華民國九十七年一月

# 實現於標準金氧半製程之單晶整合光接收器設計

## Design of Monolithically Integrated Optical Receiver in Standard CMOS Process

研究 生：邱 瑪 益

指 導 教 授：蔡 嘉 明 教 授

Student : Hsiang-Yi Chiu

Advisor : Prof. Chia-Ming Tsai

### A Thesis

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical Engineering and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Electronics Engineering

January 2008

Hsinchu, Taiwan, Republic of China

中華民國九十七年一月

---

# 實現於標準金氧半製程之單晶整合光接收器設計

學生：邱珣益

指導教授：蔡嘉明 教授

國立交通大學

電子工程學系 電子工程研究所 碩士班

## 摘要

本論文設計單晶整合光接收器，在標準金氧半製程裡整合檢光二極體與接收器前端電路。為了補償緩慢基版載子的效應，本論文使用等化器補償檢光二極體的本質響應，並使用負阻抗與主動式電感的技術，其頻寬的提升大於 400 倍。第一顆晶片使用  $0.18\mu m$  金氧半製程實現一個  $3.125Gb/s$  的單晶整合光接收器，在  $850nm$  光波長下量測出  $69 dB\Omega$  的差動轉阻增益、 $-8.1dBm$  的靈敏度與  $2.5GHz$  的頻寬，在  $1.8V$  供應電壓下消耗  $36mW$  的功率。在本論文裡，光纖聚光點大於所設計的檢光二極體面積，加上介電層的反射折射，故響應率只有原先預期的一半，造成  $3dB$  的靈敏度下降。此外，光發射器在亮暗比為  $6dB$  時約衰減  $2.2dB$  的靈敏度。第二顆晶片以  $0.13\mu m$  金氧半製程實現一個  $5Gb/s$  的單晶整合光接收器，其設計目標為  $600nm-1000nm$  的光波長可適性。不同波長的光因其入射深度不同，造成不同程度的緩慢增益下降，此接收器因而包含一可調式等化器與一可變增益放大器，確保補償能適當執行。在  $850nm$  光波長下量測出  $60-91 dB\Omega$  的差動

---

轉阻增益與-1.7dBm 的靈敏度，在 1.5V 供應電壓下消耗 112mW 的功率。

---

# **Design of Monolithically Integrated Optical Receiver in Standard CMOS Process**

Student : Hsiang-Yi Chiu

Advisor : Prof. Chia-Ming Tsai

Department of Electronics Engineering & Institute of Electronics

National Chiao Tung University

This thesis presents monolithically integrated optical receivers, consisting of integrated photodiodes and receiver front-end circuits in standard CMOS process. To eliminate the slow substrate carriers effect without sacrificing responsivity, an equalizer is used to compensate the poor intrinsic response of photodiode. Negative impedance and active inductive peaking are adopted to improve the bandwidth further. The compensatory factor is more than 400. The first chip implements a 3.125Gb/s monolithically integrated optical receiver in  $0.18\mu\text{m}$  CMOS process. Measurement result achieves 69dB total differential transimpedance gain, -8.1dBm sensitivity and 2.5GHz optical bandwidth at 850nm light wavelength. This chip dissipates 36mW from a 1.8V supply. In this thesis, because the fiber spot size is larger than the area of photodiode and the reflection is caused by dielectric layers,

---

the responsitivity is only half of the expected one. It therefore causes 3dB sensitivity degradation. Besides, finite extinction ratio of lightwave transmitter impacts the sensitivity. When the extinction is 6dB, the sensitivity degrades about 2.2dB. The second chip implements a 5Gb/s monolithically integrated optical receiver in 0.13 $\mu$ m CMOS technology. This chip is designed for adaptability of 600nm-1000nm light wavelength. Light of different wavelength causes different penetration depth, leading to roll-off in various degree. Therefore, this receiver incorporates a tunable equalizer and a variable gain amplifier for appropriate compensation. Measurement result achieves 60-91dB total differential transimpedance gain and -1.7dBm sensitivity at 850nm light wavelength. This chip dissipates 112mW from a 1.5V supply.

---

## 誌 謝

碩士生涯在完成這份論文時即將劃下句點，兩年多來有笑有淚，一路上衷心感激許多人的成就。

首先，想先感謝指導教授蔡嘉明博士。遇到這麼認真的好老師是我的幸運，老師在研究上的嚴謹和創新創立了典範，而在做人處事應有的態度也不時叮嚀，言教和身教都讓我受益良多。謝謝老師花那麼多時間在每位同學身上，感佩老師的包容和耐心。

此外，感謝郭建男教授、黃國展博士及黃立仁博士對於本論文的建議及指正，讓論文能更加充實。同時感謝郭治群教授在元件模型方面的教導，也感謝信品公司的老闆和蔚華科技的工程師們所給予的協助，感謝國家晶片中心及工業技術研究院提供的先進半導體製程。

感謝實驗室裡一起同甘共苦的伙伴，謝謝宜興在冬夜裡三四點和我一起爬起來量測，謝謝茂成學長和我討論許多高頻的問題，謝謝建君分享的種種經驗和技巧。也感謝學弟提供許多研究及實驗室事務上的協助，秉威，昭安、承暉、勗哲、致煌，研究的路上難免會有挫折和瓶頸，堅定信念、莫忘初衷，你們會做得比我們好。

最後感謝我的家人和朋友，謝謝你們的鼓勵和陪伴。謝謝父母的養育和教導，離家求學的我每次返家都感覺得出您們的欣喜，想起來會掉淚的。謝謝淑婷，妳的笑容和蚪蚪人讓我每一天都過得充實而勇敢，有妳真好。

僅以此論文獻給我最愛的家人以及關心我的師友們。

邱珣益

2008/1/31

---

# 目錄

|                                   |      |

|-----------------------------------|------|

| 中文摘要 .....                        | i    |

| 英文摘要 .....                        | iii  |

| 誌謝 .....                          | v    |

| 目錄 .....                          | vi   |

| 表目錄 .....                         | viii |

| 圖目錄 .....                         | ix   |

| 第一章 簡介 .....                      | 1    |

| 1.1 研究背景 .....                    | 1    |

| 1.2 論文大綱 .....                    | 1    |

| 第二章 單晶整合光接收器相關背景 .....            | 3    |

| 2.1 光纖通訊系統 .....                  | 3    |

| 2.2 互補式金氧半檢光二極體元件物理 .....         | 4    |

| 2.2.1 光偵測原理 .....                 | 4    |

| 2.2.2 金氧半檢光二級體結構 .....            | 5    |

| 2.2.3 數學模型 .....                  | 5    |

| 2.2.4 檢光二極體頻率響應 .....             | 8    |

| 2.3 相關研究發展現況 .....                | 9    |

| 第三章 互補式金氧半檢光二極體設計、模擬與建模 .....     | 11   |

| 3.1 檢光二極體設計考量 .....               | 11   |

| 3.2 Medici模擬 .....                | 12   |

| 3.3 製程飄移考量 .....                  | 14   |

| 3.4 參數萃取與等效電路建模 .....             | 15   |

| 第四章 一個 3.125Gb/s的單晶整合光接收器設計 ..... | 18   |

| 4.1 研究動機 .....                    | 18   |

| 4.2 架構簡介與設計概念 .....               | 19   |

| 4.3 電路設計 .....                    | 20   |

| 4.3.1 轉阻放大器 .....                 | 20   |

| 4.3.2 多頻帶補償式源極退化級 .....           | 22   |

---

|                                 |    |

|---------------------------------|----|

| 4.3.3 電感頂峰 .....                | 25 |

| 4.3.4 增益放大級.....                | 27 |

| 4.3.5 輸出緩衝級.....                | 28 |

| 4.3.6 檢光二極體製程飄移補償機制 .....       | 28 |

| 4.4 模擬結果與佈局考量 .....             | 30 |

| 4.5 量測結果 .....                  | 32 |

| 4.5.1 量測環境 .....                | 32 |

| 4.5.2 檢光二極體量測 .....             | 33 |

| 4.5.3 單晶整合光接收器量測.....           | 37 |

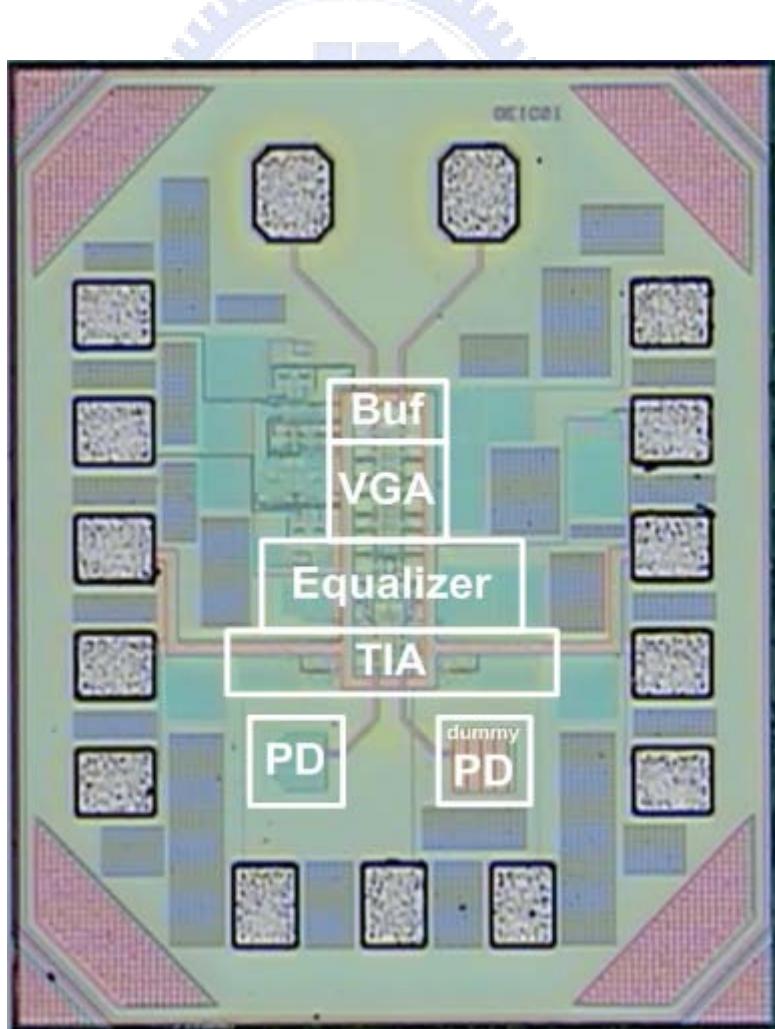

| 4.5.4 晶片照相圖與量測規格列表.....         | 39 |

| 第五章 一個 5Gb/s的寬頻單晶整合光接收器設計 ..... | 41 |

| 5.1 研究動機 .....                  | 41 |

| 5.2 架構簡介與設計概念 .....             | 41 |

| 5.3 電路設計 .....                  | 43 |

| 5.3.1 轉阻放大器 .....               | 43 |

| 5.3.2 加成等化級.....                | 44 |

| 5.3.3 可變增益放大器 .....             | 45 |

| 5.4 模擬結果與佈局考量 .....             | 46 |

| 5.5 量測結果 .....                  | 51 |

| 第六章 結論與未來展望 .....               | 56 |

| 參考文獻 .....                      | 57 |

| 附錄 .....                        | 60 |

| 簡歷 .....                        | 64 |

---

## 表目錄

|       |                 |    |

|-------|-----------------|----|

| 表 2.1 | 相關研究發展現況總結..... | 10 |

| 表 3.1 | 製程參數估計表 .....   | 13 |

| 表 3.2 | 製程參數飄移估計表 ..... | 15 |

| 表 4.1 | 預計規格列表.....     | 32 |

| 表 4.2 | 檢光二極體響應率量測..... | 35 |

| 表 4.3 | 量測規格列表與比較 ..... | 40 |

| 表 5.1 | 預計規格列表.....     | 50 |

| 表 5.2 | 量測結果列表與比較 ..... | 55 |

---

# 圖 目 錄

|        |                                     |    |

|--------|-------------------------------------|----|

| 圖 2.1  | 光纖通訊系統 .....                        | 3  |

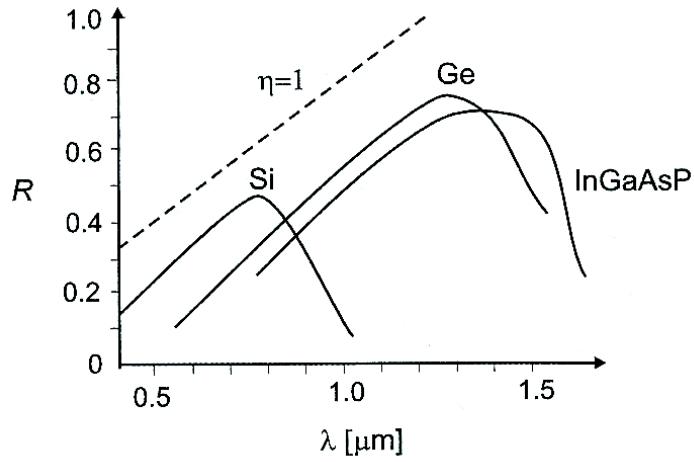

| 圖 2.2  | 不同材料對波長之響應率 .....                   | 5  |

| 圖 2.3  | 金氧化半導光二級體結構 .....                   | 5  |

| 圖 2.4  | 檢光二極體一維模型 .....                     | 6  |

| 圖 2.5  | 檢光二極體各成分之頻率響應 .....                 | 8  |

| 圖 2.6  | (a) 空間調變光偵測器 (b) 暫態響應 .....         | 9  |

| 圖 2.7  | (a) 類比等化器 (b) 眼圖 .....              | 10 |

| 圖 3.1  | 本質與外質頻寬 .....                       | 11 |

| 圖 3.2  | 多指N-well/P-substrate型檢光二極體結構圖 ..... | 12 |

| 圖 3.3  | 不同逆偏狀況下的暫態響應 .....                  | 14 |

| 圖 3.4  | 不同逆偏狀況下的頻率響應 .....                  | 14 |

| 圖 3.5  | 檢光二極體製程飄移的極端狀況 .....                | 15 |

| 圖 3.6  | 檢光二極體本質響應等效模型 .....                 | 16 |

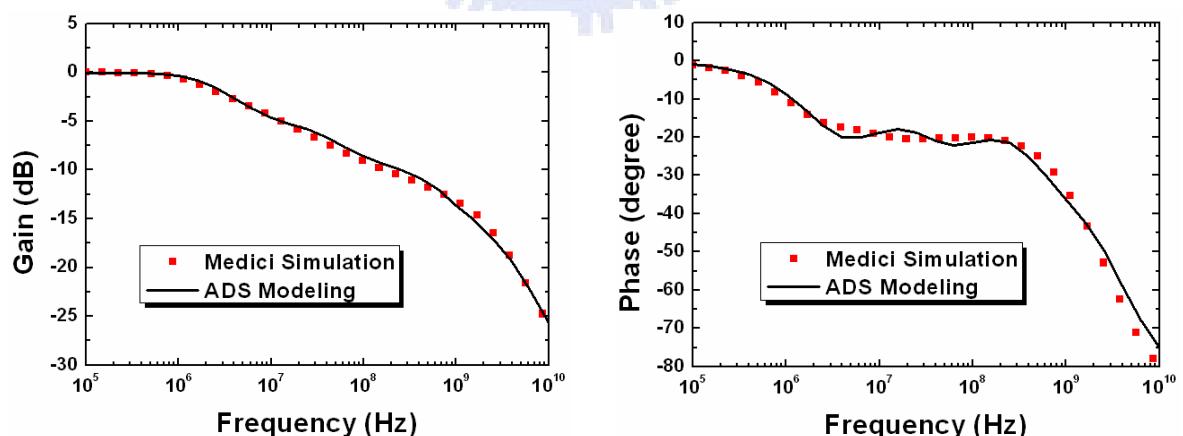

| 圖 3.7  | Medici模擬與ADS模型對應圖 .....             | 16 |

| 圖 3.8  | 檢光二極體寄生效應等效電路 .....                 | 17 |

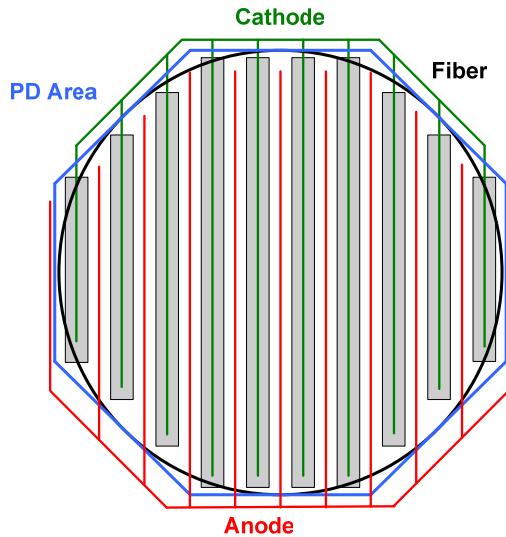

| 圖 3.9  | 檢光二極體佈局示意圖 .....                    | 17 |

| 圖 4.1  | 單晶整合光接收器架構圖 .....                   | 19 |

| 圖 4.2  | 共源極轉阻放大器一階等效模型 .....                | 20 |

| 圖 4.3  | 兩級式偽差動轉阻放大器 .....                   | 21 |

| 圖 4.4  | 轉阻放大器雜訊等效半電路 .....                  | 21 |

| 圖 4.5  | 轉阻放大器頻率響應與眼圖模擬 .....                | 22 |

| 圖 4.6  | 多頻帶補償式源極退化級 .....                   | 23 |

| 圖 4.7  | 源極退化級頻率響應示意圖 .....                  | 24 |

| 圖 4.8  | 差動式源極退化級 .....                      | 25 |

| 圖 4.9  | 鎊線效應對源極退化級之影響 .....                 | 25 |

| 圖 4.10 | 主動式電感示意圖 .....                      | 26 |

| 圖 4.11 | 主動式電感等效電路 .....                     | 26 |

| 圖 4.12 | 差動式主動電感 .....                       | 26 |

| 圖 4.13 | 傳統與改良之Cherry-Hooper放大器 .....        | 27 |

---

|        |                                        |    |

|--------|----------------------------------------|----|

| 圖 4.14 | 具源極隨耦器回授之Cherry-Hooper放大器 .....        | 28 |

| 圖 4.15 | 輸出緩衝級 .....                            | 28 |

| 圖 4.16 | 檢光二極體製程飄移補償機制 .....                    | 29 |

| 圖 4.17 | 檢光二極體製程飄移補償模擬 .....                    | 30 |

| 圖 4.18 | 單晶整合光接收器頻率響應模擬 .....                   | 30 |

| 圖 4.19 | 光接收眼圖模擬 .....                          | 30 |

| 圖 4.20 | 佈局圖 .....                              | 31 |

| 圖 4.21 | 暫態響應量測環境 .....                         | 32 |

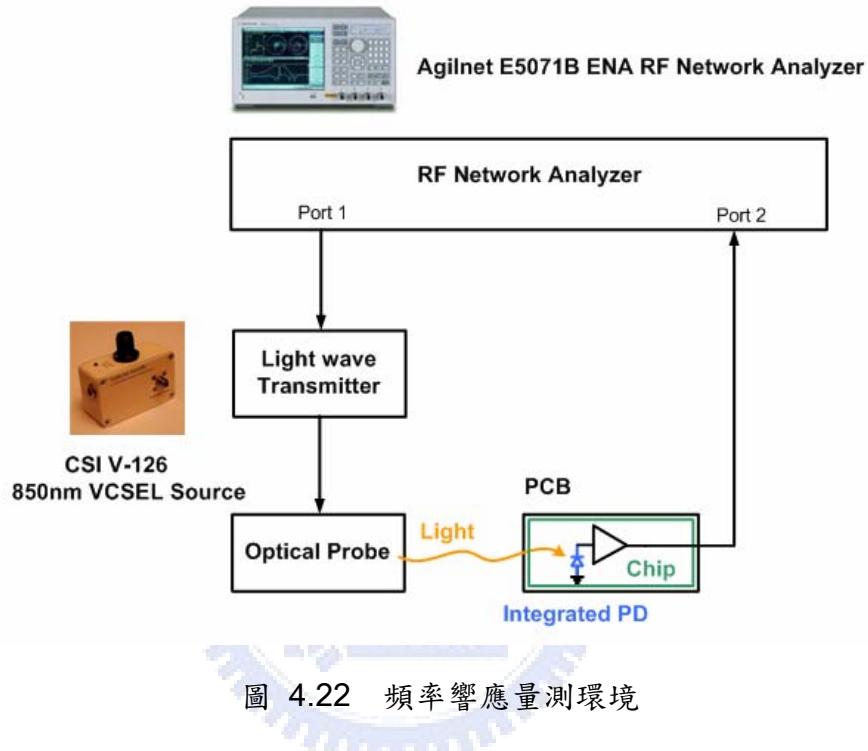

| 圖 4.22 | 頻率響應量測環境 .....                         | 33 |

| 圖 4.23 | 檢光二極體量測設定 .....                        | 34 |

| 圖 4.24 | 檢光二極體C-V圖量測 .....                      | 34 |

| 圖 4.25 | 檢光二極體頻率響應量測 .....                      | 35 |

| 圖 4.26 | 雜散電阻造成的外質響應變化 .....                    | 36 |

| 圖 4.27 | 不同逆偏下的檢光二極體響應量測 .....                  | 36 |

| 圖 4.28 | 檢光二極體暫態響應與眼圖量測（速度為 622Mb/s） .....      | 37 |

| 圖 4.29 | 光接收器頻率響應量測 .....                       | 37 |

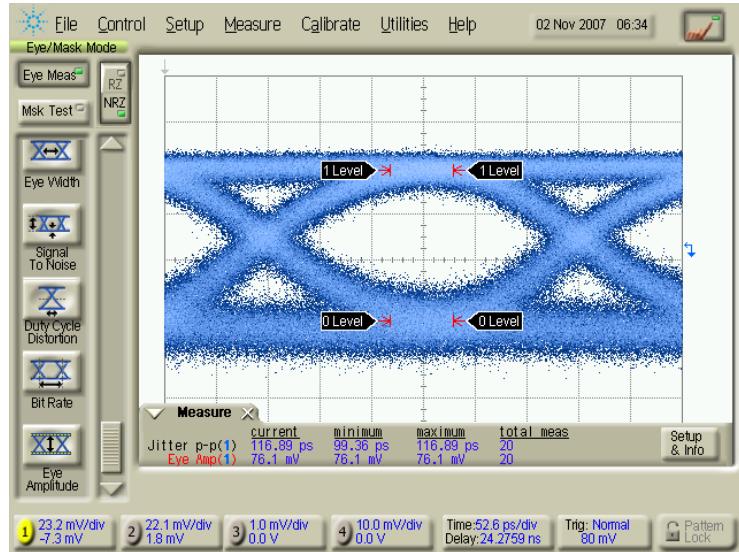

| 圖 4.30 | 光接收器眼圖量測 (-8.5dBm，速度為 3.125Gb/s) ..... | 38 |

| 圖 4.31 | 雜訊功率頻譜量測和雜訊推估 .....                    | 38 |

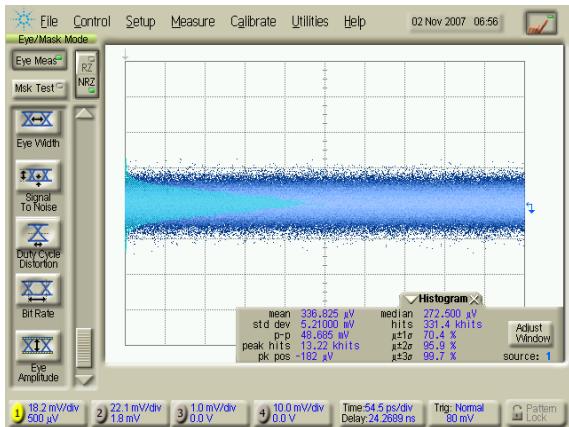

| 圖 4.32 | 直方圖量測和雜訊推估 .....                       | 39 |

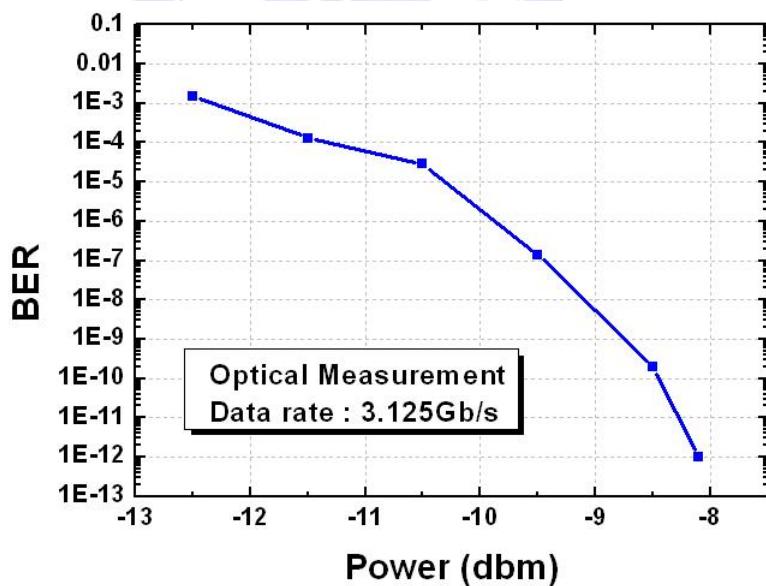

| 圖 4.33 | 光接收器在不同光功率下的誤碼率量測 .....                | 39 |

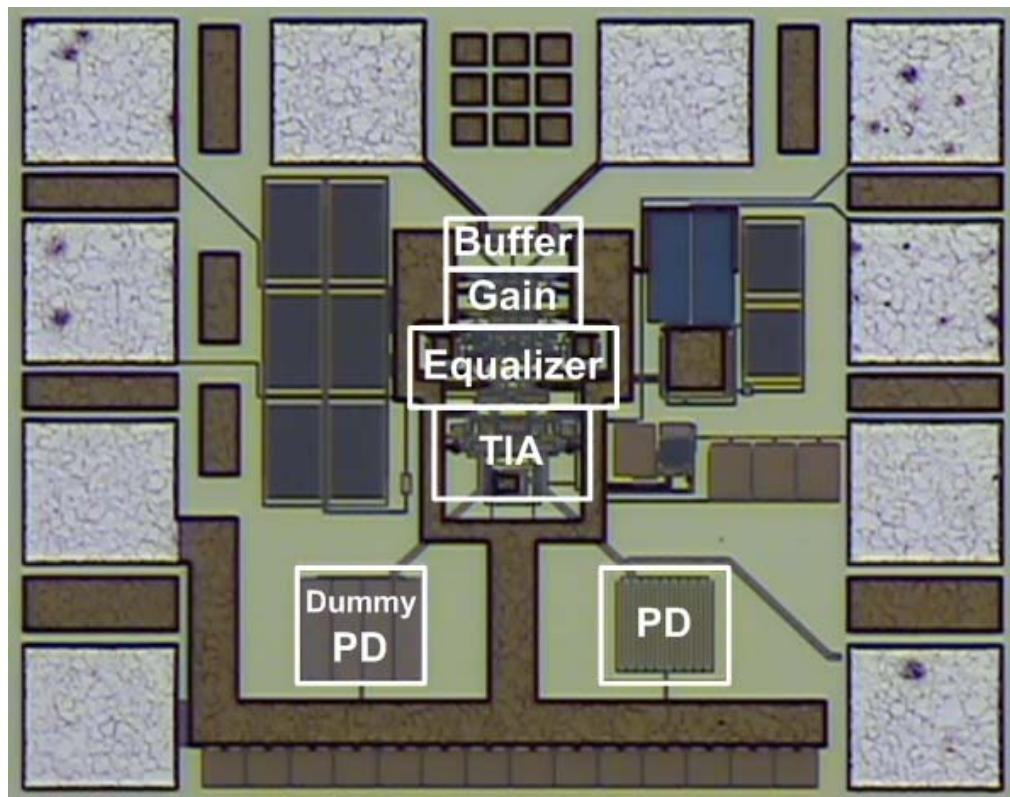

| 圖 4.34 | 晶片照相圖 .....                            | 40 |

| 圖 5.1  | 設計概念 .....                             | 41 |

| 圖 5.2  | 限幅器前後的頻譜關係圖 .....                      | 42 |

| 圖 5.3  | 光接收器架構圖 .....                          | 43 |

| 圖 5.4  | 轉阻放大器 .....                            | 43 |

| 圖 5.5  | 可變源極退化級與加成電路 .....                     | 44 |

| 圖 5.6  | 加成等化級頻率響應模擬 .....                      | 45 |

| 圖 5.7  | 可變增益放大器 .....                          | 46 |

| 圖 5.8  | 可變增益放大器之頻寬與增益關係圖模擬 .....               | 46 |

| 圖 5.9  | 不同波長入射光下的Medici模擬結果 .....              | 47 |

| 圖 5.10 | 不同波長入射光下的ADS模型化結果 .....                | 47 |

| 圖 5.11 | 光接收器不同波長入射光下的頻率響應模擬 .....              | 48 |

---

---

|                                              |    |

|----------------------------------------------|----|

| 圖 5.12 等化器開關時的暫態響應 .....                     | 48 |

| 圖 5.13 八角形檢光二極體佈局圖 .....                     | 49 |

| 圖 5.14 光接收器佈局圖 .....                         | 50 |

| 圖 5.15 頻率響應圖量測 (a) 等化器變動 (b) 可變增益放大器變動 ..... | 51 |

| 圖 5.16 等化器關閉時的暫態響應與眼圖量測 .....                | 51 |

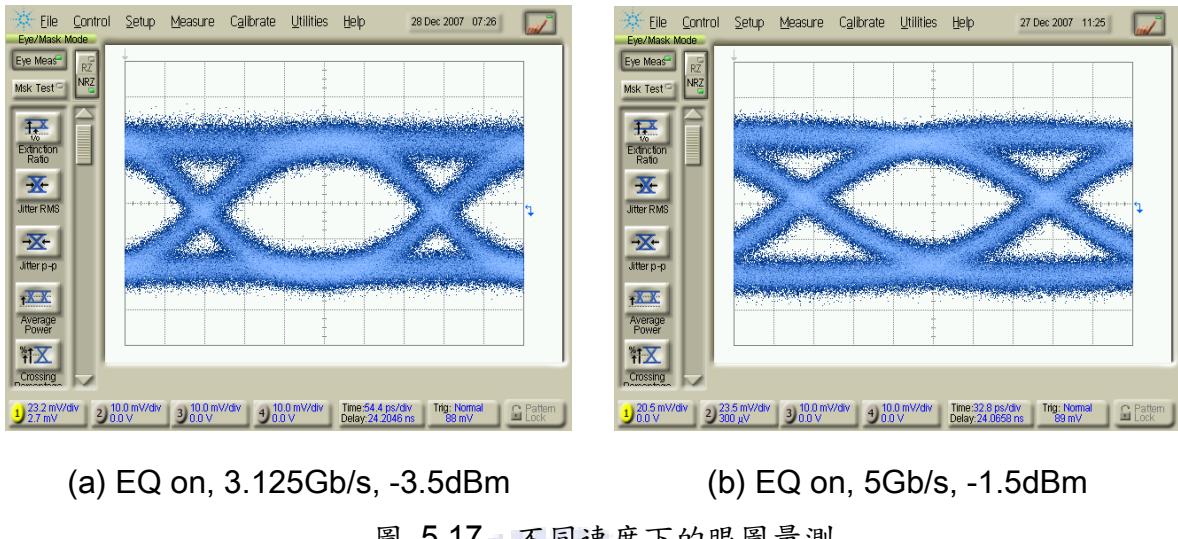

| 圖 5.17 不同速度下的眼圖量測 .....                      | 52 |

| 圖 5.18 頻率響應量測 .....                          | 52 |

| 圖 5.19 雜訊功率頻譜量測和雜訊推估 .....                   | 53 |

| 圖 5.20 直方圖量測和雜訊推估 .....                      | 53 |

| 圖 5.21 光接收器誤碼率量測 .....                       | 54 |

| 圖 5.22 光接收器晶片照相圖 .....                       | 54 |

# 第一章 簡介

## 1.1 研究背景

目前數位化光纖通訊系統已廣泛的應用在長途電信(telecommunication)及資料通訊(data communication)上。其中，長途電信系統以單模光纖(single-mode fiber)為主，其光源多操作於 1310 nm/1550 nm 的波長，應用於數十公里至數百公里的距離；資料通訊屬於短距離通訊，以多模光纖(Multi-Mode Fiber)為主，多採用 850 nm 波長，應用在區域性的網路交換或晶片間的連接上。

現有的光通訊傳輸標準有 SONET (synchronous optical network) 及 SDH (synchronous digital hierarchy) 兩種，其中訂定了階層式的資料交換格式及傳輸位元率 (bit rate)。另在物理層的傳輸標準，是由國際電信標準 ITU (International Telecommunication Unity) 所制定的，其中提出了短中長距離不同位元率下所需的傳送／接收、通道、光波長及量測的規範。

過去，高速光通訊的相關元件和研究侷限於長距離的電信資訊交換。然而，隨著半導體製程的進步，元件及電路的設計製造成本大幅的降低，中距離和短距離的應用規格於是產生。於是，如何將光電元件與電路整合於廉價的 CMOS 製程裡，便是一值得探究的課題。

## 1.2 論文大綱

本論文由六個章節所構成。第二章介紹單晶整合光接收器的相關背景，先概述光纖通訊系統，而後討論檢光二極體元件物理，包含光偵測原理、數學模型和頻率響應等，最後再討論相關的研究發展現況。

第三章談及檢光二極體的設計、模擬與建模。先從物理特性討論可實行於標準 CMOS 製程的檢光二極體，考量其元件結構上的優劣，然後以元件模擬軟體模擬檢光二極體在入射光前後的各項特性，並萃取雜散阻抗以便後端電路模擬。此外，我們還考量了檢光二極體的製程飄移變異，並在後端電路設計相應的補償。

第四章以 0.18 $\mu\text{m}$  CMOS 製程設計出一個適用於 3.125Gb/s 的單晶整合光接收器，

---

包含了整合進 CMOS 的檢光二極體和接收器前端電路。我們設計一多頻帶補償的等化器補償檢光二極體緩慢的增益下降，並使用主動式電感、主動式負阻抗等技巧進一步提升頻寬。量測結果驗證了此設計的可行性。

第五章以  $0.13\mu\text{m}$  CMOS 製程設計出一個  $5\text{Gb/s}$  的寬頻單晶整合光接收器。我們先研究 CMOS 檢光二極體對不同光波長的響應，並構思設計一可適性等化器，使整合的光接收器可在多種波長下達到高速操作。這次的設計包含可適性等化器裡的前饋路徑，除了整合進 CMOS 的檢光二極體和接收器前端電路外，並設計了加成式等化器與高線性度可變增益放大器，以達日後可適性判斷的要求。量測結果驗證了此設計的可行性。

第六章為結論與未來可以改進的地方。

## 第二章 單晶整合光接收器相關背景

### 2.1 光纖通訊系統

圖 2.1 光纖通訊系統

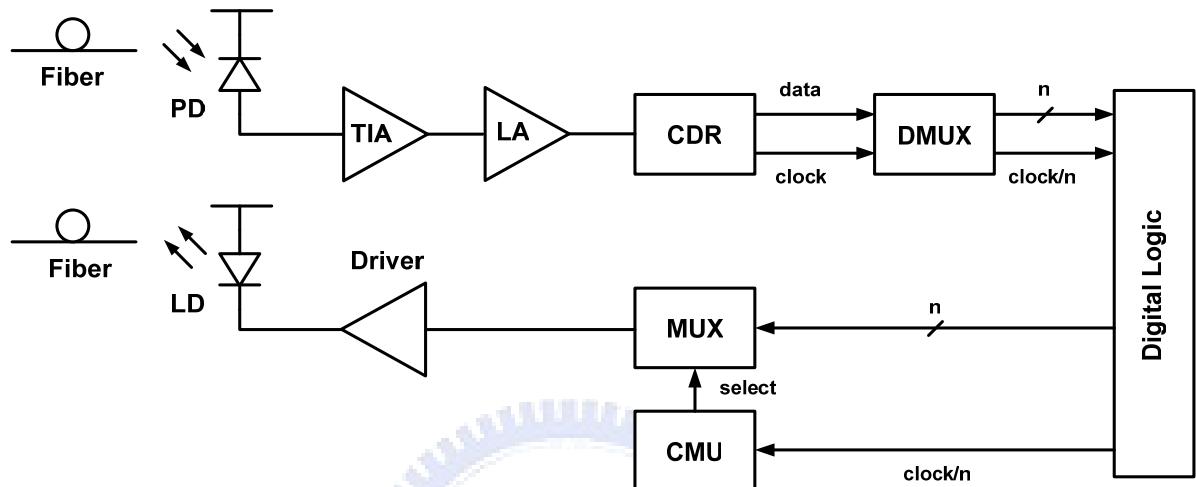

圖 2.1 為一個光纖通訊系統的架構圖

[1]。光信號經由光纖傳遞，在接收端由一個檢光二極體（photodiode, PD）產生正比於光功率的電流信號，經由轉阻放大器（transimpedance amplifier, TIA）將電流轉為電壓，再由限幅放大器（limiting amplifier, LA）放大至數百毫伏特後，送入時脈資料回復電路（clock and data recovery, CDR）取出時脈並重新定位信號，再經解多工器（demultiplexer, DMUX）將信號切為n等分送入數位邏輯（digital logic）做數位信號處理，此為接收端的部分。

在傳送端，信號從數位邏輯送出，經由多工器（multiplexer, MUX）合併為一高速的資料串流，而多工器的信號選擇由時脈合成單元（clock multiplication unit, CMU）執行。最後，一個雷射驅動器（laser driver）藉由調變雷射二極體（laser diode, LD）的電流將電信號轉為光訊號，經由光纖送出。

本研究要設計的部分為接收器前端電路，包含了一整合進 CMOS 的檢光二極體、轉阻放大器和增益放大器，此外並為特定應用加入額外電路，如後文所描述。

---

## 2.2 互補式金氧半檢光二極體元件物理

### 2.2.1 光偵測原理

光打入半導體時，其強度會隨入射深度有著指數性的衰減， $I \propto e^{-\alpha x}$ ，其中  $\alpha$  定義為吸收係數 (absorption coefficient)，是一個隨著入射光頻率而變的值，其倒數定義為入射深度 (penetration depth)。對CMOS而言，在可偵測光訊號的波長下，其入射深度的差異會大到三個數量級[2]。

檢光二極體為一個操作於逆偏的 PN 接面。當光打入檢光二極體時，在能量大於矽能隙 (bandgap) 的條件下，位於價帶的電子會躍升至導帶，產生一對電子電洞對。在空乏區內產生的載子藉由較快的飄移 (drift) 機制所收集，在空乏區外的少數載子則由較慢的擴散 (diffusion) 機制傳輸，光電流即為這兩種載子流動的總和。緩慢的擴散載子在暫態響應上產生一尾狀響應 (tail response)，限制了檢光二極體的速度。於是，增加逆偏電壓或調整 PN 接面摻雜輪廓使空乏區變大，便可有較高速的響應。

最後，我們定義兩個重要的參數：

$$\text{Quantum efficiency } \eta_{ph} = \frac{\text{number of induced electrons}}{\text{number of photons}} = \frac{I_{photo}/q}{P_{inc}/h\nu}$$

$$\text{Responsivity} = \frac{\text{Photocurrent}}{\text{Incident Power}} = \frac{q\eta_{ph}}{h\nu} = \frac{\eta_{ph}\lambda(\mu\text{m})}{1.24}$$

量子效率 (quantum efficiency) 定義為入射光子和受激發電子電動對的比例。理想上一個光子可產生一組電子電動對，但因表面反射或材料吸收發熱，故在一般的 CMOS 檢光二極體裡這個值約只有 40%~70%。

響應率 (responsivity) 則定義成單位入射光能量所能產生的電流比例。若我們假設量子效率最大 ( $=1$ ) 的話，則對於  $400\text{nm} < \lambda < 850\text{nm}$  的入射光而言，其響應率約為  $0.32\text{A/W} \sim 0.64\text{A/W}$ 。圖 2.2 為不同材料對光波長的響應率，我們可以看到對矽而言，其響應率的最大值約在光波長為  $850\text{nm}$  時，故後面將在此波長下做最佳化。

圖 2.2 不同材料對波長之響應率

### 2.2.2 金氧半檢光二級體結構

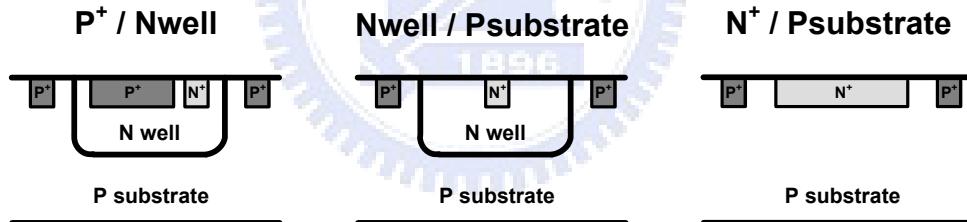

檢光二級體為一逆偏的 PN 接面，因而在 CMOS 製程裡可實現的結構有 P<sup>+</sup>/N-well、N-well/P-substrate 和 N<sup>+</sup>/P-substrate，如圖 2.3 所示。

圖 2.3 金氧半檢光二級體結構

P<sup>+</sup>/N-well 與 N<sup>+</sup>/P-substrate 的檢光二級體其接面深度較淺，故接收效率較差。由於前者接收光時並無牽扯到基版深處的緩慢擴散載子，因而有較快的速度；然而，後者雖然速度較慢，卻因大量的基版擴散載子而有較大的信號成分。N-well/P-substrate 有最深的接面，且其摻雜濃度較淺故空乏區較大，因而接收效率最好。最後，我們選擇有最大信號成分但速度較慢的 N-well/P-substrate 檢光二級體，原因是信號小的話其差的信雜比無法改善，然而速度慢卻可以電路技巧補償。

### 2.2.3 數學模型

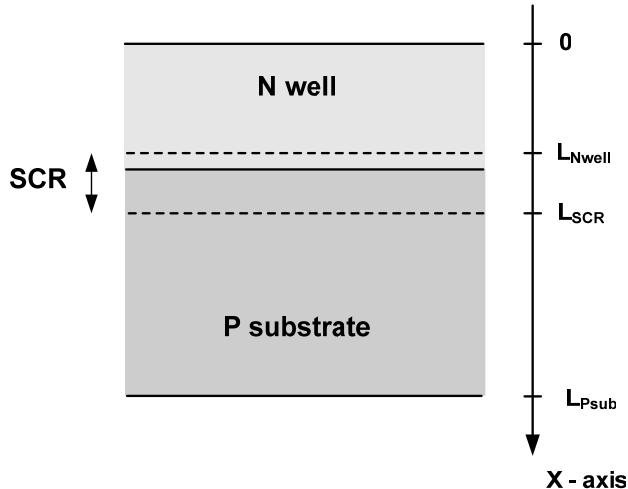

我們從一維模型開始，探究檢光二極體的本質響應[3]。Nwell-Psubstrate檢光二極體一維模型如圖 2.4 所示，其中 SCR 代表存在一逆偏壓時的空乏區（space charge region）。

圖 2.4 檢光二極體一維模型

當能量大於矽能隙的光射入 N-well / P-substrate 檢光二極體時，在 N-well 、P-substrate 和空乏區分別產生電子電洞對，光電流即為這三股電流的總和。

$$I_{\text{photo}} = I_{\text{diff}, \text{Nwell}} + I_{\text{drift}, \text{SCR}} + I_{\text{diff}, \text{Psub}}$$

對於 Nwell 裡的少數載子電洞，其載子傳輸方程式如下：

$$\frac{\partial p(x,t)}{\partial t} = D_p \frac{\partial^2 p(x,t)}{\partial x^2} - \frac{p(x,t) - p_0}{\tau_p} + \alpha \Phi e^{-\alpha x}$$

其中  $p(x,t)$  為 N-well 裡的電洞濃度， $p_0$  為 N-well 裡電洞的初始濃度， $D_p$  為電洞的擴散係數， $\tau_p$  為少數載子生命週期， $\alpha$  為光在矽裡的吸收係數， $\Phi$  為光通量。這式子描述單位體積的載子濃度在以下三種影響下會改變：流進和流出的擴散載子通量差異（第一項）、淨復合（net recombination，第二項）與光產生的載子增量（第三項）。其邊界條件為：

$$\begin{aligned} p(x=0,t) &= p_0 \\ p(x=L_{\text{Nwell}},t) &= 0 \\ p(x,t=0) &= p_0 \end{aligned}$$

第一個邊界條件假設矽表面的的復合為零，第二個邊界條件是因為空乏區邊緣其少數載子濃度為零，第三個邊界條件敘述在沒有光的時候載子濃度為平衡濃度  $p_0$ 。

我們將此非齊次偏微分方程式分解為一齊次偏微分和一非齊次常微分方程。因此，我們可以把解分解為：

$$p(x,t) = v(x) + w(x,t)$$

於是，我們可以求得解為：

$$\begin{aligned} p(x,t) = & p_0 - \frac{\alpha\Phi}{D_p\alpha^2 - 1/\tau_p} e^{-\alpha x} + A_p \exp\left(\frac{x}{\sqrt{D_p\tau_p}}\right) + B_p \exp\left(\frac{-x}{\sqrt{D_p\tau_p}}\right) \\ & + \sum_{k=1}^{\infty} C_p(k) \sin\left(\frac{k\pi x}{L_{Nwell}}\right) \exp\left[-\left(\frac{k^2\pi^2 D_p}{L_{Nwell}^2} + \frac{1}{\tau_p}\right)t\right] \end{aligned}$$

我們再利用邊界條件將  $A_p$ 、 $B_p$  和  $C_p(k)$  這三個常數求出。最後，我們可以得出電洞擴散電流為：

$$J_{\text{diff},p} = -qD_p \frac{\partial p}{\partial x} \Big|_{x=L_{Nwell}}$$

另一方面，在 P-substrate 裡的載子傳輸方程式如下：

$$\frac{\partial n(x,t)}{\partial t} = D_n \frac{\partial^2 n(x,t)}{\partial x^2} - \frac{n(x,t) - n_0}{\tau_n} + \alpha\Phi e^{-\alpha x}$$

其中  $n(x,t)$  為 P-substrate 裡的電子濃度， $n_0$  為 P-substrate 裡電子的初始濃度， $D_n$  為電子的擴散係數， $\tau_n$  為少數載子生命週期， $\alpha$  為光在矽裡的吸收係數， $\Phi$  為光通量。其邊界條件為：

$$\begin{aligned} n(x = L_{SCR}, t) &= 0 \\ n(x = L_{Psub}, t) &= n_0 \\ n(x, t = 0) &= n_0 \end{aligned}$$

第一個邊界因為空乏區邊緣其少數載子濃度為零，第二個邊界條件敘述在  $L_{Psub}$  遠大於少數載子擴散長度 (diffusion length) 時其濃度為平衡濃度  $n_0$ ，第三個邊界條件敘述在沒有光的時候載子濃度為平衡濃度  $n_0$ 。

方法如前，在 P-substrate 裡的電子濃度分佈如下式：

$$\begin{aligned} n(x,t) = & n_0 - \frac{\alpha\Phi}{D_n\alpha^2 - 1/\tau_n} e^{-\alpha x} + A_n \exp\left(\frac{x}{\sqrt{D_n\tau_n}}\right) + B_n \exp\left(\frac{-x}{\sqrt{D_n\tau_n}}\right) \\ & + \sum_{k=1}^{\infty} C_n(k) \sin\left(\frac{k\pi(x - L_{SCR})}{L_{Psub} - L_{SCR}}\right) \exp\left[-\left(\frac{k^2\pi^2 D_n}{(L_{Psub} - L_{SCR})^2} + \frac{1}{\tau_n}\right)t\right] \end{aligned}$$

我們再利用邊界條件將  $A_n$ 、 $B_n$  和  $C_n(k)$  這三個常數求出。最後，我們可以得出電子擴散電流為：

$$J_{\text{diff},n} = -qD_n \frac{\partial n}{\partial x} \Big|_{x=L_{\text{SCR}}}$$

飄移電流的部分，考慮在空乏區內光產生的載子：

$$J_{\text{drift}} = q \int_{x=L_{\text{Nwell}}}^{x=L_{\text{SCR}}} G(x) dx = q \int_{x=L_{\text{Nwell}}}^{x=L_{\text{SCR}}} \alpha \Phi e^{-\alpha x} dx$$

其中  $L_{\text{NWLL}}$  和  $L_{\text{SCR}}$  的差距即為空乏區寬度，其值約為：

$$L_{\text{SCR}} - L_{\text{Nwell}} = \sqrt{\frac{2\epsilon}{q} \left( \frac{1}{N_A} + \frac{1}{N_D} \right) (V_{\text{bi}} - V_R)}$$

$N_A$  為 P-substrate 內的受體摻雜濃度， $N_D$  為 N-well 內的施體摻雜濃度， $\epsilon$  為矽的介電常數 (permittivity)， $V_{\text{bi}}$  為內建電壓 (built-in voltage)， $V_R$  為逆偏電壓。

## 2.2.4 檢光二極體頻率響應

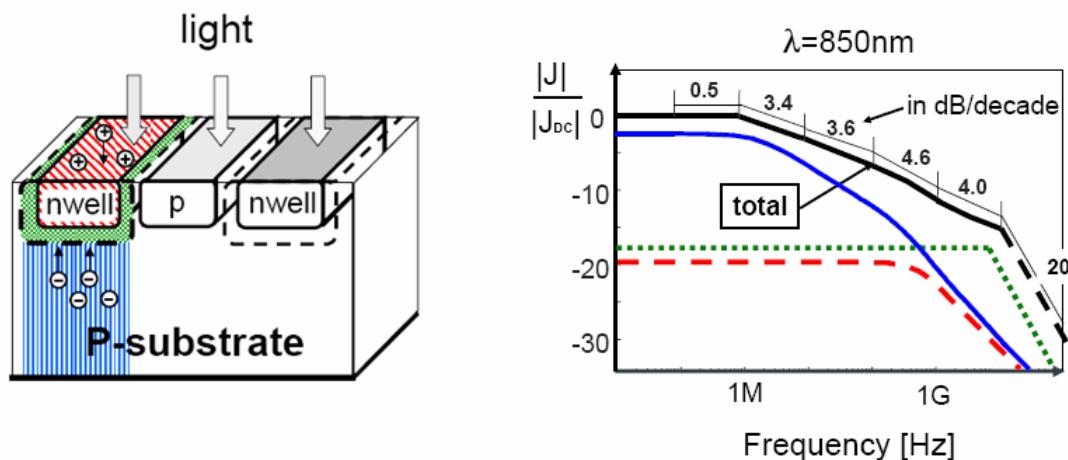

考慮元件的二維效應，從[4]的結果可以看出在CMOS檢光二極體內不同成分電流的頻率響應，如圖 2.5 所示。我們可看出高速的飄移載子有最高的頻寬，N-well 擴散載子因為離接面較近所以有次之的頻寬。由於 850nm 的光入射進矽時其入射深度約為十幾  $\mu\text{m}$ ，在接面擴散長度 (diffusion length) 內的少數載子會被收集，故在基版產生的 P-substrate 擴散載子佔光電流最多的成分，且因擴散距離長故速度最慢。三個成分加起來後，得出一從 MHz 就開始的緩慢增益下降響應，其幅度約為每一個數量級下降 3.5~4.5 個分貝。

圖 2.5 檢光二極體各成分之頻率響應

## 2.3 相關研究發展現況

在上一節的討論已經提及，金氧半檢光二極體主要的速度限制是來自基版深處的擴散載子所造成。因此，若是能抵銷或補償此緩慢擴散載子的響應，便能改善原先速度的限制。

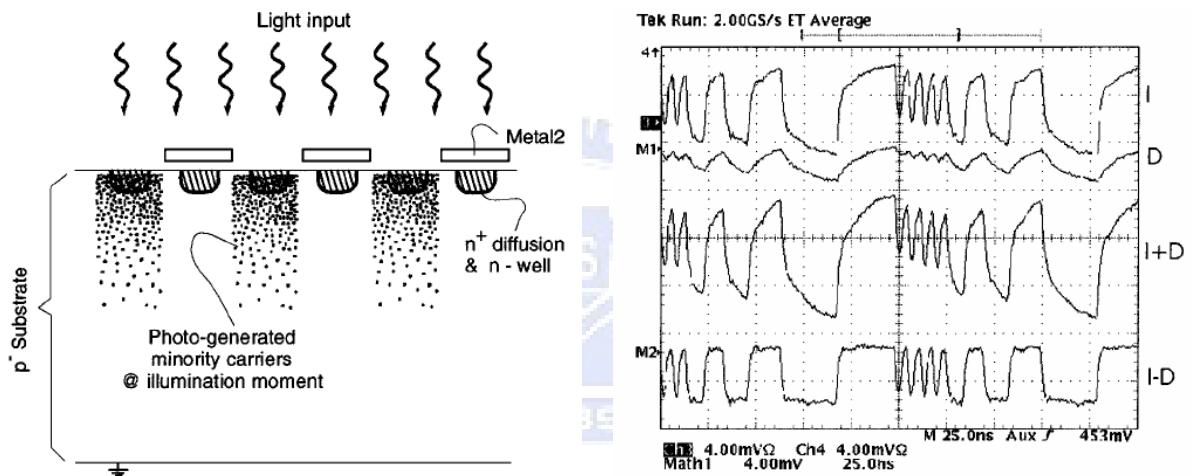

從抵銷擴散載子的觀念出發，提出了空間調變光偵測器（spatially modulated light, SML）的方法[5]。首先是實現一差動的多指（multi-finger）檢光二極體，將感光區域交錯地以金屬遮蔽，如圖 2.6(a)所示。

圖 2.6 (a) 空間調變光偵測器 (b) 暫態響應

光打入空間調變光偵測器後，照到光的部分產生擴散載子，金屬遮蔽的部分反之。在基版深處產生的載子會同時擴散至照光與金屬遮蔽的區域，因此這兩部分的信號都包含了擴散載子的響應。如圖 2.6(b)所示，I 代表照光（illuminated）區域，D 代表遲緩（deferred）區域，我們看到兩個信號的暫態響應都有尾狀延遲。而後，將這兩部分的信號送進後端電路相減（I-D），可以看到消去擴散載子後信號變得更高速，尾狀延遲也不復見。然而，這種消去擴散載子的架構雖然高速，但卻以犧牲響應率為代價，使電路整體的靈敏度下降。

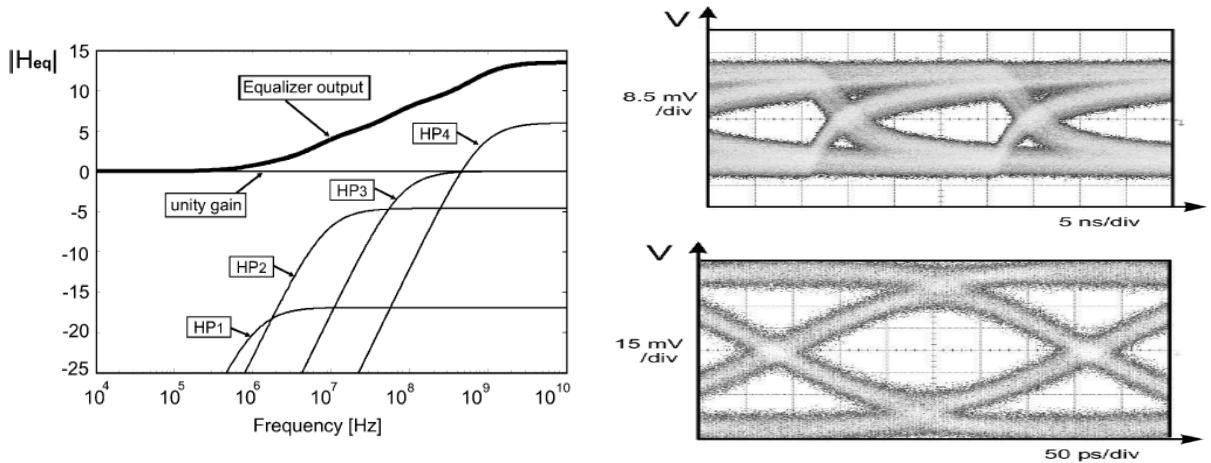

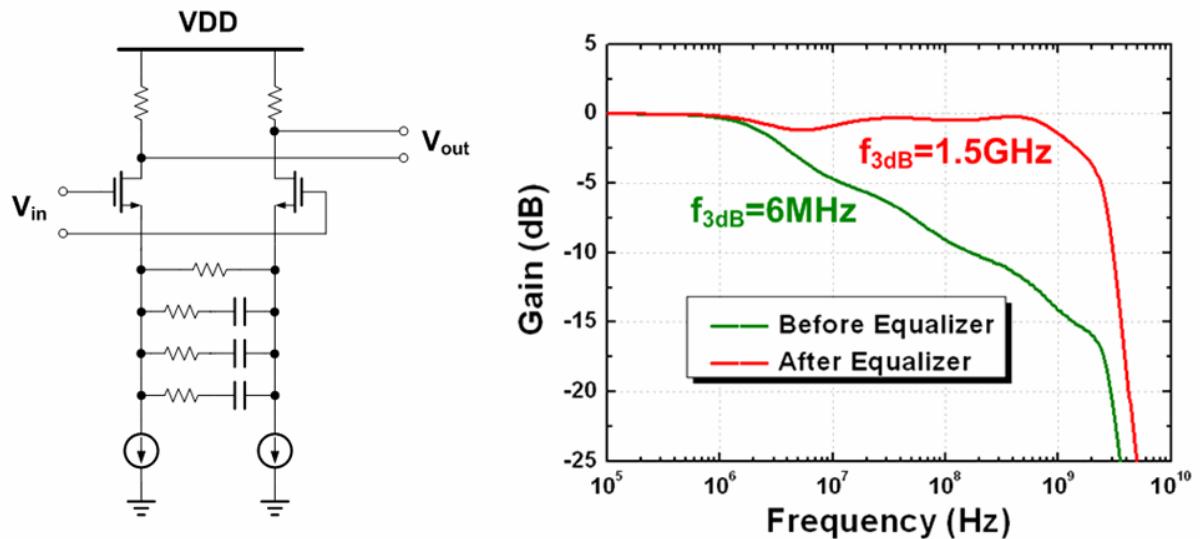

另一方面，從補償擴散載子的觀念來看，設計一個類比等化器（equalizer）增加速度是另一種思考[6]。如圖 2.7(a)所示，使用數個高通濾波器近似一個緩慢上升的響應，以補償擴散載子的緩慢下降響應，理論上便可得到一個沒有尾狀延遲的高速響應。

圖 2.7 (a) 類比等化器 (b) 眼圖

如圖 2.7(b)所示，上圖為等化器關掉的響應，下圖為等化器打開的響應。我們觀察到頻寬有極顯著的增加，因此改善了符號間干擾 (inter-symbol interference, ISI)，進而增加靈敏度。這種補償擴散載子的架構保留了所有的信號成分，故沒有犧牲響應度的問題，但對檢光二極體的模擬和模型建立與等化器的補償等皆需要精準的掌握。

表 2.1 是相關研究發展現況總結，可以發現使用等化器的方法同時兼具較高的速度和靈敏度，並和前述檢光二極體的選擇考量相合，故我們將以此為基礎再做進一步的研究。

|             | B. Nauta<br>2005 JSSC [6]      | M. Steyaert<br>2006 JSSC [7]   |

|-------------|--------------------------------|--------------------------------|

| Process     | 0.18μm CMOS                    | 0.18μm CMOS                    |

| Wavelength  | 850nm                          | 850nm                          |

| Method      | Equalizer                      | SML                            |

| Data rate   | 3Gb/s                          | 500Mb/s                        |

| Sensitivity | -19dBm @ BER=10 <sup>-11</sup> | -8dBm@ BER=3x10 <sup>-10</sup> |

表 2.1 相關研究發展現況總結

# 第三章 互補式金氧半檢光二極體設計、模擬與建模

## 3.1 檢光二極體設計考量

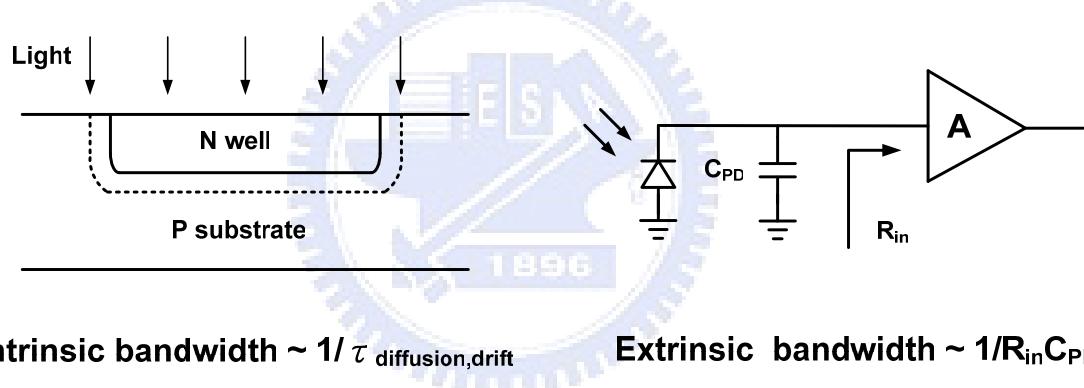

當能量大於材料能隙的光照入金氧半檢光二極體時，產生電子電洞對，並以飄移或擴散的機制被收集，有著一緩慢下降的頻率響應。我們定義此頻寬為本質頻寬 (intrinsic bandwidth)，由較慢的載子生命週期倒數決定。當檢光二極體被放置進電路裡時，因為本身有著數百fF的寄生電容，因此在電路輸入端將造成一較低頻的極點限制頻寬。我們定義此頻寬為外質頻寬 (extrinsic bandwidth)，其值約為電路輸入端的RC時間常數倒數。單晶整合光接收器的頻寬由本質頻寬和外質頻寬中較小的一個所主導[8]，如圖 3.1 所示。

圖 3.1 本質與外質頻寬

在本質頻寬的部分，可做的改善不外乎是減少緩慢擴散載子、增加高速飄移載子的比例。在不使用額外製程且製程參數固定的條件下，可改善的方法有：

- 一、使用較淺的N<sup>+</sup>/P-substrate檢光二極體，並在周圍以氧化層圍住以阻絕基版擴散至接面的緩慢載子[9]。

- 二、使用空間調變光偵測器，再經後端電路消去擴散載子[5]。

- 三、使用等化的技巧補償擴散載子緩慢下降的本質響應[6]。

- 四、加大逆偏電壓增加空乏區面積，以增加高速飄移載子的比例[10]。

- 五、使用多指的結構增加空乏區面積，以增加高速飄移載子的比例。

- 六、使用接面較深且摻雜濃度較淺的 N-well/P-substrate 檢光二極體，可收集較多擴散載子並有較大的空乏區面積。

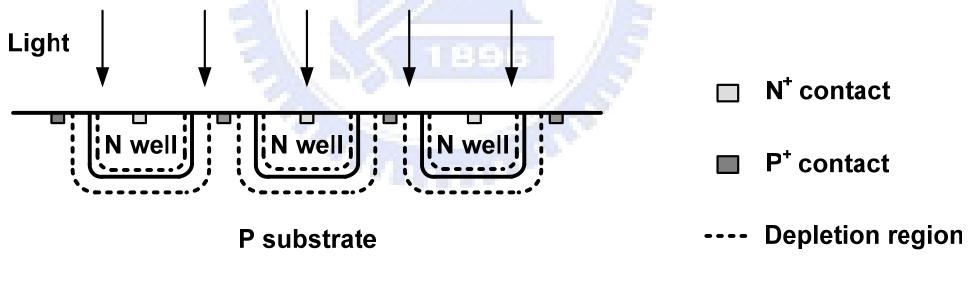

第一、二個方法都以犧牲響應度為高速的代價，然而對一個接收器最重要的靈敏度也跟著降低，因而在本研究中並不採用。為兼顧速度和靈敏度，本研究主要以第三種方法補償緩慢擴散載子響應，並使用多指設計的 N-well/P-substrate 檢光二極體使空乏區的面積變大，其指數由製程容許的最小 N-well 寬度和相隔間距所決定。此外，在先進製程裡其供應電壓有其限制，故增加逆偏的方法並不適合。

在外質頻寬的部分，我們希望有較小的寄生電容使 RC 時間常數變小。檢光二極體的結構固定後，主要改善寄生電容的方法為佈局上的考量，例如使用面積較小的八邊形取代傳統的四方形以近似光纖的孔徑等。

對一般的 N-well / P-substrate 檢光二極體而言，其本質頻寬約為 MHz 級，而高速電路 RC 時間常數約為 GHz 級，因此整體頻寬由本質頻寬決定。然而，當我們使用等化的技術補償緩慢擴散載子的響應後，外質頻寬的影響便顯得更重要，故在設計時需同時最佳化此兩種頻寬。

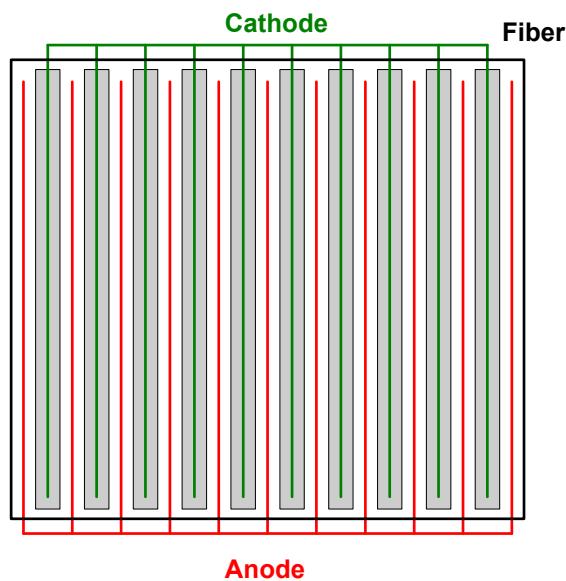

總結來說，本研究的檢光二極體將採用多指的 N-well / P-substrate 型，使用等化的技巧補償擴散載子，面積為  $50\mu\text{m} \times 50\mu\text{m}$ ，因為這是多模光纖的直徑。此外，我們將在相鄰的 N-well 間打上基版連結 (substrate contact)，以減少基版電阻並增加載子收集效率。最後的結構如圖 3.2 所示。

圖 3.2 多指 N-well/P-substrate 型檢光二極體結構圖

## 3.2 Medici 模擬

在這次的設計裡使用標準的 CMOS 製程製作檢光二極體，故應先萃取出設計所需的相關參數，再使用 Synopsys 的製程及元件模擬軟體 TCAD 模擬檢光二極體的特性。首先，使用 TSMC 的二極體模型並觀察其空乏電容的變化，反推出摻雜的濃度；再者，查閱 TSMC 文件裡的片電阻值，反推求出摻雜的深度。詳細的推導步驟如下：

一、使用 TSMC spice 元件庫裡的二極體參數，提供逆偏電壓並得出空乏電容。在

此只考慮底部的電容。

二、我們可由模擬出的接面電容求出  $C_{j0}$ 。而後，因 P+/N-well 和 N-well/P-substrate 兩種二極體，其個別的 P 和 N 濃度都相差一個數量級以上，故可經由下述公式推導出 N-well 和 P-substrate 的摻雜濃度：

$$C_j = \frac{C_{j0}}{\sqrt{1 + \frac{V_R}{V_{bi}}}} \Rightarrow C_{j0} = A \cdot \sqrt{\frac{\epsilon q}{2} \left( \frac{1}{N_A} + \frac{1}{N_D} \right)^{-1} \left( \frac{1}{V_{bi}} \right)}$$

**For P+/N-well diode,  $[P+] \gg [N\text{-well}]$**

$$\Rightarrow [N\text{-well}] = \left( \frac{C_{j0}}{A} \right)^2 \cdot \frac{2}{\epsilon q} \cdot V_{bi}$$

**For N-well/P-substrate diode,  $[N\text{-well}] \gg [P\text{-substrate}]$**

$$\Rightarrow [P\text{-substrate}] = \left( \frac{C_{j0}}{A} \right)^2 \cdot \frac{2}{\epsilon q} \cdot V_{bi}$$

三、利用 N-well under OD 的電阻值，並使用導電率 (conductivity) 的公式估計出 N-well 的摻雜深度。

$$\text{sheet resistance } R_s = \frac{1}{\sigma} \cdot \frac{1}{t}$$

$$\text{conductivity } \sigma = q(\mu_n n + \mu_p p)$$

計算出的主要製程參數如表 3.1 所示。

|                                  | Value  | Unit              |

|----------------------------------|--------|-------------------|

| Temperature                      | 25     | °C                |

| N-well doping concentration      | 1.5E17 | 1/cm <sup>3</sup> |

| P-substrate doping concentration | 1.8E15 | 1/cm <sup>3</sup> |

| Number of finger                 | 10     | N/A               |

| N-well width                     | 2      | μm                |

| N-well depth                     | 1.9    | μm                |

表 3.1 製程參數估計表

決定元件結構並求出模擬所需的主要製程參數後，我們模擬暫態響應和頻率響應。

圖 3.3 為不同逆偏狀況下的暫態響應。我們發現逆偏越大時有越好的響應率，但在合理範圍內其效應並不顯著。這是因為對 N-well/P-substrate 檢光二極體而言，主要的電流

成分是基版生成的擴散載子。因此，逆偏電壓主要由電路規格所決定。

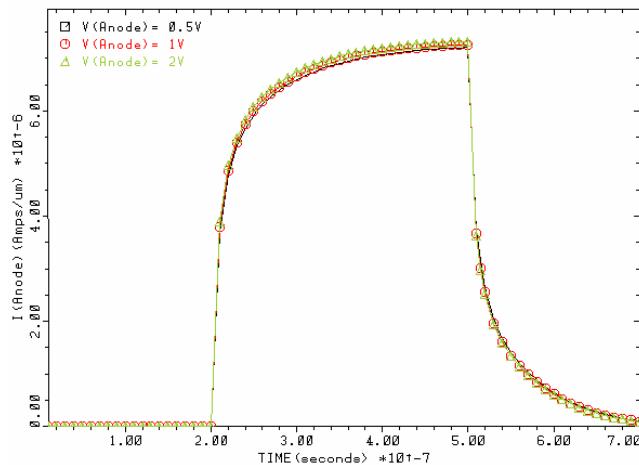

圖 3.3 不同逆偏狀況下的暫態響應

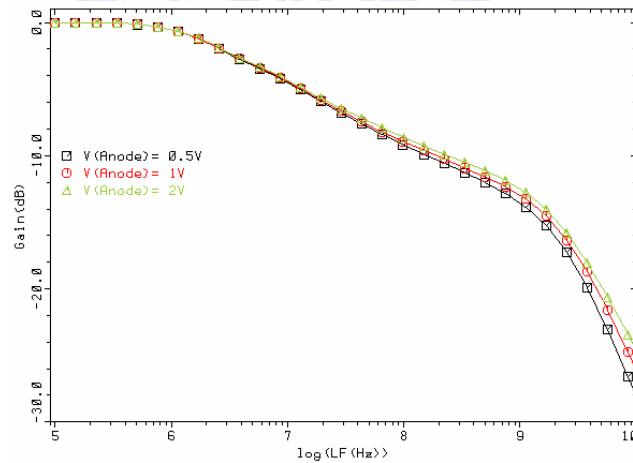

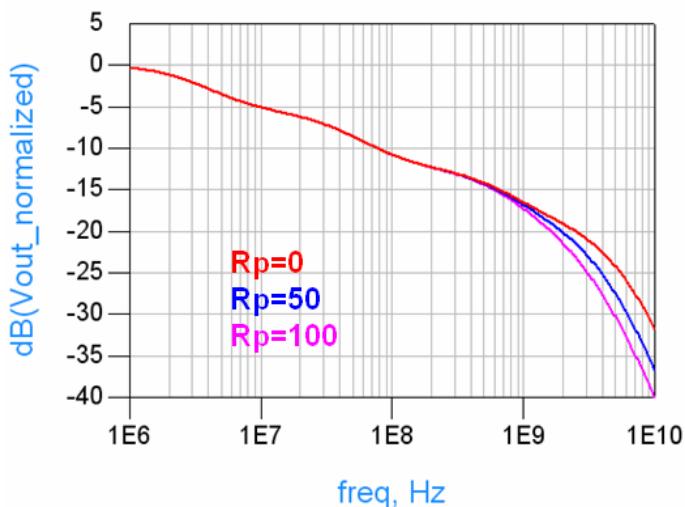

圖 3.4 為不同逆偏狀況下的頻率響應。如之前所預期，檢光二極體的增益在 MHz 的頻段就開始因擴散載子的效應而緩慢下降，其頻寬約為 6MHz。

圖 3.4 不同逆偏狀況下的頻率響應

### 3.3 製程飄移考量

因為使用等化的方式補償擴散載子需要有精準的模擬，故我們在推估製程參數時考慮一可能變動的範圍，並在後端電路加入可變化的補償。推估的範圍如表 3.2 所示。

|                                                      | Minimum | Typical | Maximum |

|------------------------------------------------------|---------|---------|---------|

| Temperature                                          | 0       | 25      | 80      |

| N-well doping concentration ( $1/\text{cm}^3$ )      | 1.2E17  | 1.5E17  | 1.8E17  |

| P-substrate doping concentration ( $1/\text{cm}^3$ ) | 1.4E15  | 1.8E15  | 2.2E15  |

| N-well depth ( $\mu\text{m}$ )                       | 0.9     | 1.9     | 2.9     |

表 3.2 製程參數飄移估計表

當溫度上升時，載子遷移率（mobility）下降，故高頻的飄移載子響應將會變慢，即有較多的衰減。當摻雜深度減少時，表示 N-well 區域變小而基版載子的比例變多，故在低頻部分的緩慢下降變得更嚴重。圖 3.5 為檢光二極體製程飄移的極端狀況，也是後面電路裡設計可調補償的範圍。模擬證實製程濃度的變異較不顯著，故在此忽略其偏移。

圖 3.5 檢光二極體製程飄移的極端狀況

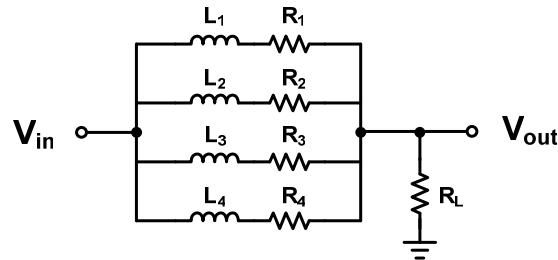

### 3.4 參數萃取與等效電路建模

為了建立檢光二極體頻率響應的模型，我們使用四組串聯的電感電阻實現一低通濾

波器，如圖 3.6 所示。電感的阻抗隨頻率上升而增加，故我們可以適當選擇電感電阻的值，近似出橫互三個數量級的緩慢增益下降。

圖 3.6 檢光二極體本質響應等效模型

$$\frac{V_{out}}{V_{in}} = \frac{R_L}{R_L + [(R_1 + j\omega L_1) \parallel (R_2 + j\omega L_2) \parallel (R_3 + j\omega L_3) \parallel (R_4 + j\omega L_4)]}$$

當信號頻率很低時，

$$\left| \frac{V_{out}}{V_{in}} \right| \approx \frac{R_L}{R_L + [R_1 \parallel R_2 \parallel R_3 \parallel R_4]}$$

當信號頻率很高時，

$$\left| \frac{V_{out}}{V_{in}} \right| \approx \frac{R_L}{\omega^2 (L_1 \parallel L_2 \parallel L_3 \parallel L_4)^2} \approx 0$$

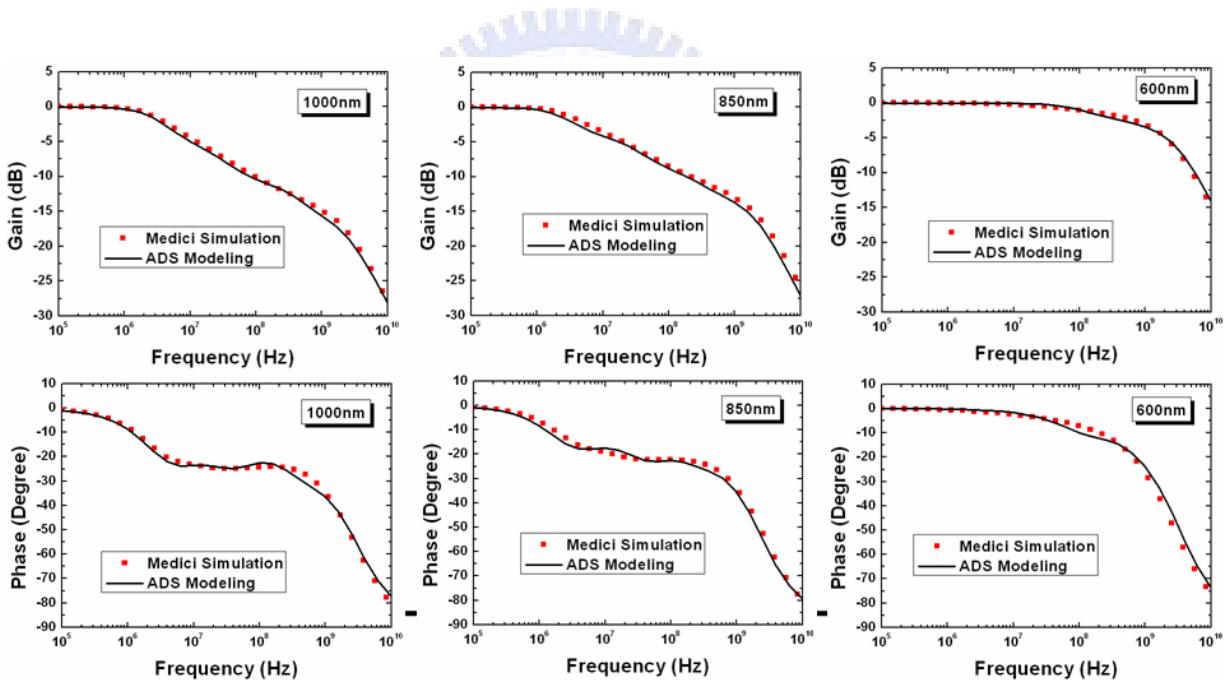

經由適當的選擇，中間的頻段就會有緩慢的增益下降，以模擬檢光二極體的頻率響應。模擬和模型化的比較如圖 3.7 所示。

圖 3.7 Medici 模擬與 ADS 模型對應圖

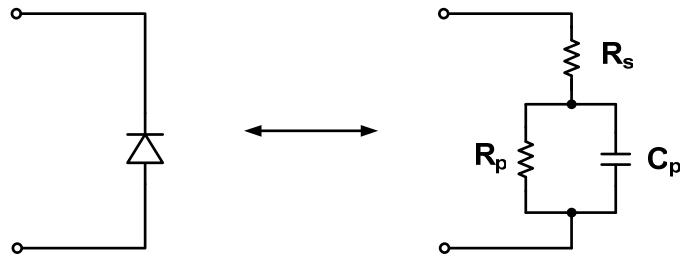

檢光二極體的寄生效應等效電路如圖 3.8 所示。 $R_p$  模擬逆偏時的漏電流（數百 k 或 M 歐姆以上的等級，通常很大而可以忽略）， $R_s$  模擬連接（contact）和未空乏的基版電阻， $C_D$  模擬逆偏時的空乏電容。

圖 3.8 檢光二極體寄生效應等效電路

在參數萃取的部分，我們使用 Y 參數的概念，分別由 Y 參數高頻和低頻的實部虛部做萃取：

$$\text{At LF} \Rightarrow R_s \text{ is neglected} \Rightarrow \text{Im}(Y) = C_p$$

$$\text{At LF} \Rightarrow C_p \text{ open} \Rightarrow \text{Re}(Y) = \frac{1}{R_s + R_p} \approx \frac{1}{R_p}$$

$$\text{At HF} \Rightarrow C_p \text{ short} \Rightarrow \text{Re}(Y) = \frac{1}{R_s}$$

| Cp (fF) | Rp (kohm) | Rs (kohm) |

|---------|-----------|-----------|

| 580     | 230       | 8         |

檢光二極體佈局如圖 3.9，面積為  $50\mu\text{m} \times 50\mu\text{m}$ ，有十個並排的 N-well 以增加空乏區面積，其寬度為  $2\mu\text{m}$ 。依照實際的佈局規則考量，金屬遮蔽住光的面積約為 11%，其響應率為  $0.55\text{A/W}$ 。

圖 3.9 檢光二極體佈局示意圖

# 第四章 一個 3.125Gb/s的單晶整合光接收器設計

## 4.1 研究動機

在長距離的資料傳輸上，高速的光纖通訊序列逐漸取代傳統的電子連接，光偵測器（optical detector）多以 GaAs 或 InP-InGaAs 實現，其昂貴的價格由各個通道上的使用者共同分擔。然而，在短距離的應用裡（如區域網路、晶片間的連線），因為通道無法被共用，因此對單一使用者而言其花費相當高昂。

為了降低短距資料傳輸的花費，我們傾向使用低成本的塑膠光纖、雷射和標準製程 [6]。在這樣的條件下，此光纖系統的許多條件便已被限制：

一、低成本的塑膠光纖其直徑為  $50\mu\text{m}$ ，因而檢光二極體的面積被限制為  $50\mu\text{m} \times 50\mu\text{m}$ 。

二、在高速的資料傳輸時，用於矽製檢光二極體的雷射操作在相當長的波長，現代高速的雷射波長其下限約為  $850\text{nm}$ ，在這次的專題裡即針對此波長做最佳化。

三、在製程方面，為了降低成本，將整個光偵測器整合進主流的 CMOS 製程裡。

除了降低成本的好處外，將檢光二極體和電路整合於同一顆晶片上還有其他的優勢。因為不需要連接到外部的市售檢光二極體，原本多出的鏽線、腳位（pad）、印刷版路徑等所造成的雜散電容電感可以消除；電路的輸入端 RC 時間常數決定了系統的主極點（dominant pole），而整合進晶片裡的檢光二極體其電容已知且固定，故增進了系統的穩定度；電路輸入端減少了額外的對外連結，原先路徑上所耦合進的環境雜訊都可以避免。而上述優點不需要犧牲太多額外面積，因為檢光二極體的面積和原本連結至外的腳位大小約相當。

然而，標準 CMOS 製程並未為光電元件最佳化，因而有下缺點：一、接面的摻雜濃度、寬度和深度已決定，無法因應光的入射深度做調整；二、逆偏電壓不能超過供應電壓；三、沒有防止反射的塗佈（anti-reflection coating, ARC）。因此，在此製程下所製造的檢光二極體，其速度和響應率都會小於市售檢光二極體。在現今的 CMOS 技術下所實現的積體光偵測器，其本質傳輸速率約為  $10\text{Mb/s}$  的數量級左右。如此慢的速率是因為矽材料本身的緣故，長波長的光打入檢光二極體時將在矽的深處產生擴散載子，此緩慢擴散至空乏區的載子限制了整體的速率。

在文獻裡我們可以找到幾種增進單晶 CMOS 光偵測器速率的方法，而這些方法都是

為了消除緩慢擴散載子所產生的效應。其中大部分的方法都需要額外的製程，例如增加一層埋藏的氧化層（buried oxide）以防止電荷緩慢地擴散回接面處[9]，又或以矽製作於絕緣層上（SOI）[11]，其他的方法還包括了加一大電壓以增加空乏區厚度[10]或是使用較輕的摻雜。然而，這些方法都和我們因降低成本因素而想在標準CMOS製程下實現的理想相違。

在這次的專題裡，我們將以現今標準的 CMOS 製程實現一整合了檢光二極體的光接收器，並使用等化的技巧補償 CMOS 檢光二極體先天的緩慢速率，如此一來可兼顧低成本和高速率、高整合性的諸優點。

## 4.2 架構簡介與設計概念

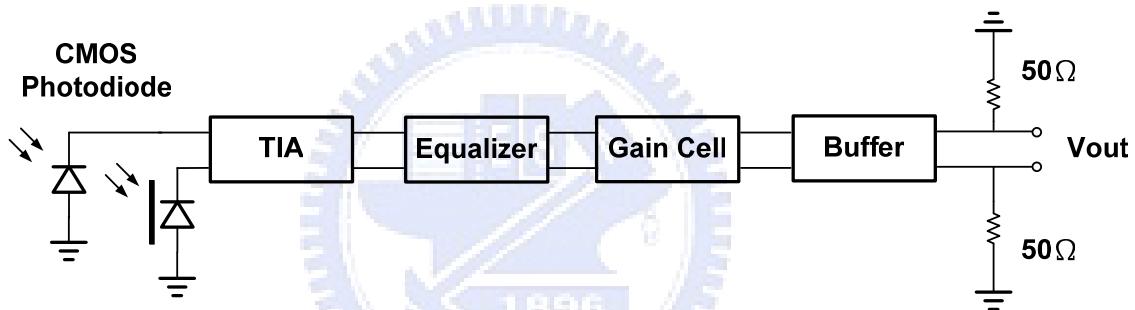

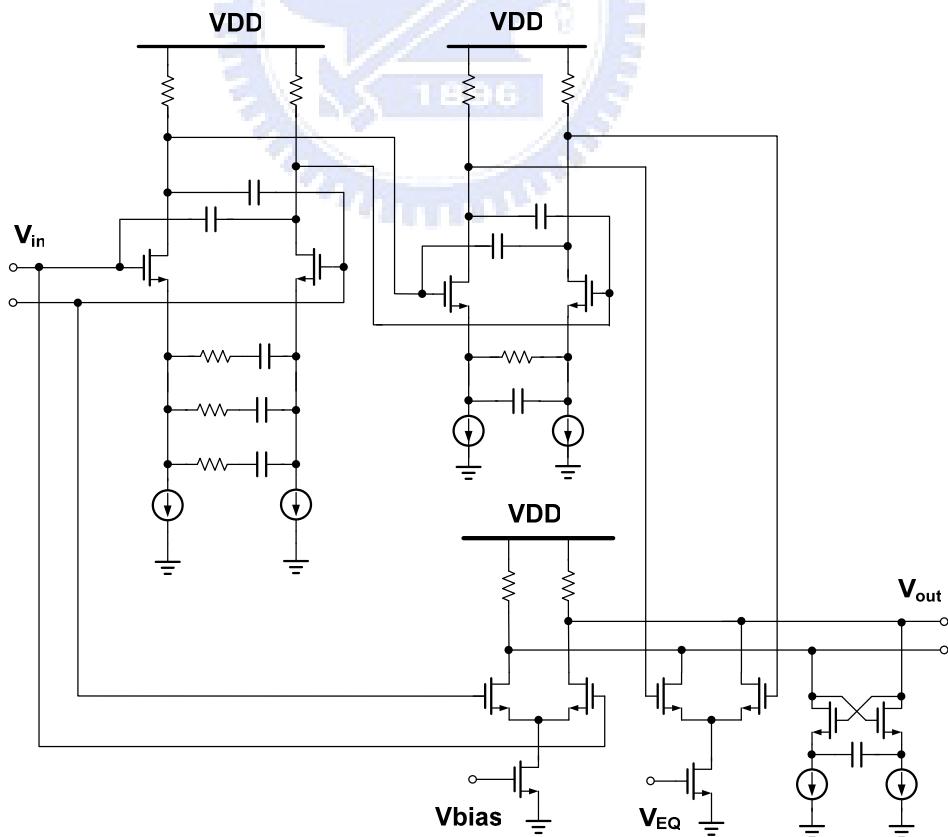

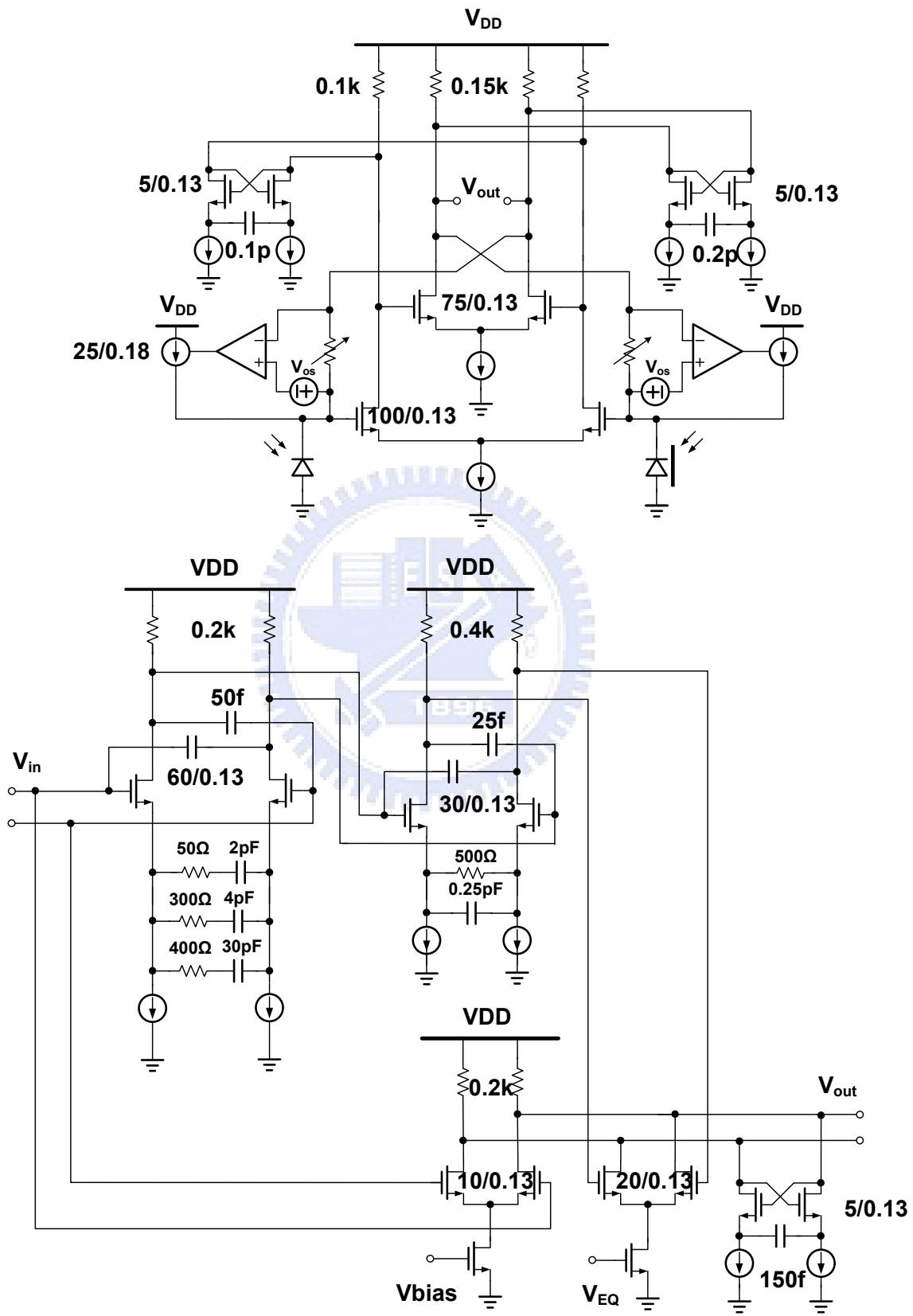

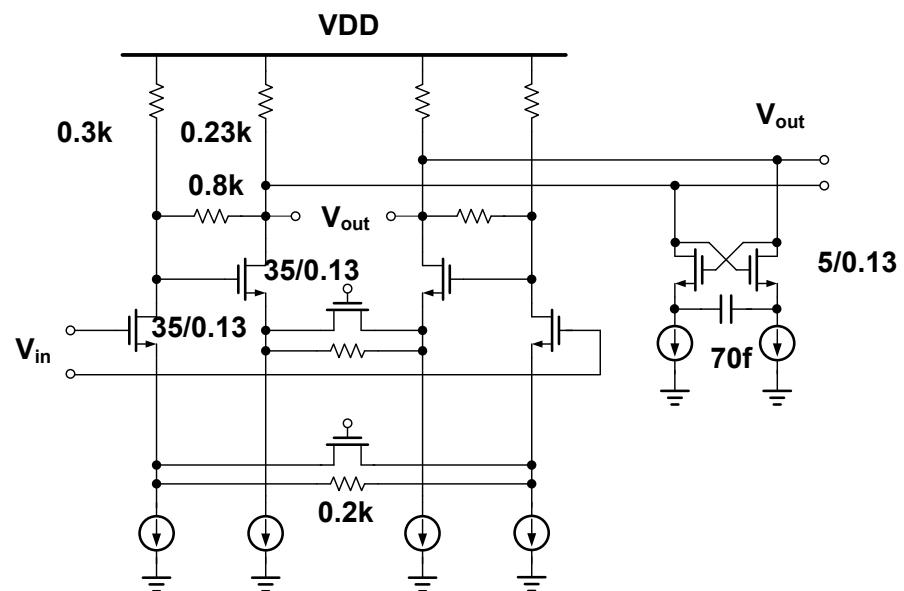

圖 4.1 單晶整合光接收器架構圖

這次的光接收器如圖 4.1 所示，最前端為一整合進 CMOS 的檢光二極體，在此並有另一個多餘的 PD (dummy PD) 以平衡後端的差動轉阻放大器。這樣的架構稱為平衡式轉阻放大器 (balanced TIA)，以其較優異的雜訊免疫力著稱，從電源或基版所耦合的雜訊將被後端電路視為共模 (common-mode) 擾動而被抑制[12]。

下一級為補償 CMOS 檢光二極體本質響應的等化器級，並使用電感頂峰 (inductive peaking) 更進一步增加系統頻寬，藉由改善符號間干擾以提升誤碼率。後級再經過增益放大級 (gain stage) 放大，最後經過一緩衝級 (buffer) 接到輸出的量測儀器。這樣安排的順序主要是為了在信號仍保留小信號線性特性時用等化級補償，並避免放大後級電路的高頻雜訊，降低整體系統的靈敏度。

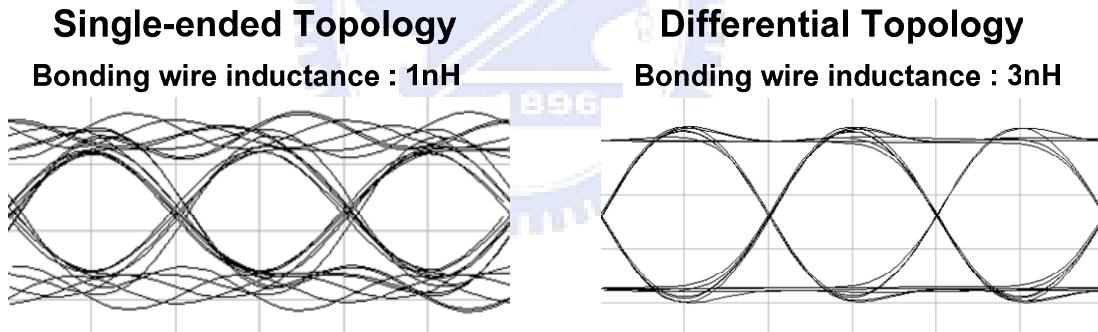

此外，使用差動架構的另一個原因是因為等化級使用可變源極退化 (variable source degeneration) 的技巧補償，但在單端設計時會因鎍線的電感和接地電容產生共振，使系統不穩定甚而震盪。我們將在後面的章節更進一步討論這個問題。

## 4.3 電路設計

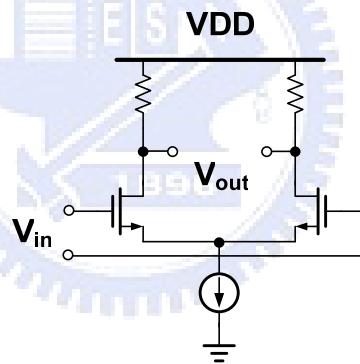

### 4.3.1 轉阻放大器

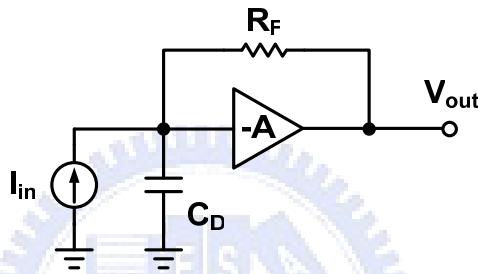

我們設計一轉阻放大器將光電流轉為電壓訊號。轉阻放大器常見的架構有兩種，分別為開迴路[13]與閉迴路[14]。開迴路多以共閘極實現，有較小的輸入阻抗，因而可以有較高的速度，但其雜訊表現較差；閉迴路以共源極採電壓-電流負回授實現，其回授電阻沒有直流偏壓電流流過，故可以有較大的轉阻值，且雜訊表現較佳，但有穩定度的問題。為了增益與雜訊的考量，我們使用電壓-電流負回授的架構，其一階模型如圖 4.2 所示[15]。

圖 4.2 共源極轉阻放大器一階等效模型

$$T_z = -\frac{A}{A+1} \frac{R_F}{1 + \frac{R_F C_D}{A+1} s}$$

$$f_{3dB} = \frac{1}{2\pi} \frac{A+1}{R_F C_D}$$

由於電壓-電流回授的緣故，輸入和輸出阻抗同時減少；前者的好處是提高輸入端的極點使頻寬增加，後者的好處是增加對後級的驅動能力。我們同時發現電路的轉阻約等於  $R_F$ ，頻寬隨著放大器的開迴路增益增加。

為了使供應電壓 (supply noise) 不會干擾信號（尤其是源極退化級的接地 RC 網路），造成不正常的補償甚至振盪，我們以差動方式實現後級電路。然而，由於有效的光信號只會進入電路的其中一端，故我們在沒有信號的一側加上一個多餘檢光二極體 (dummy PD) 以求較好的平衡。

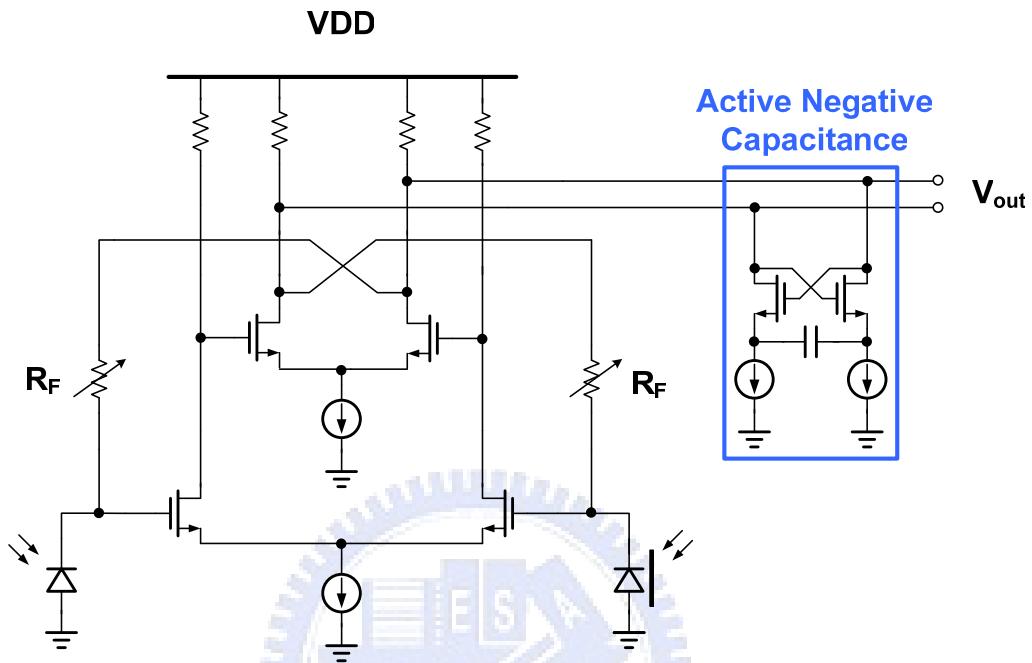

為增加速度，我們希望轉阻放大器的增益加大以增加頻寬。一般常見的實現方法為串接三級放大器，然而相位邊界 (phase margin) 的不足卻讓穩定度成為一重要考量，使設計的彈性不足；單極放大器有很好的穩定度，然而其增益卻不夠大。差動架構在這

裡提供了一個好處，就是放大器的級數不必受限於單數級，因而可採用兩級的架構在高增益和穩定度間達到平衡，並使用主動式負電容補償輸出端的電容效應[16]，使頻寬更為提升。此外，我們將回授電阻  $R_F$  設計為可調，以避免輸入為大電流時造成非線性失真，增進電路過載的能力。最後的轉阻放大器電路如圖 4.3 所示。

圖 4.3 兩級式偽差動轉阻放大器

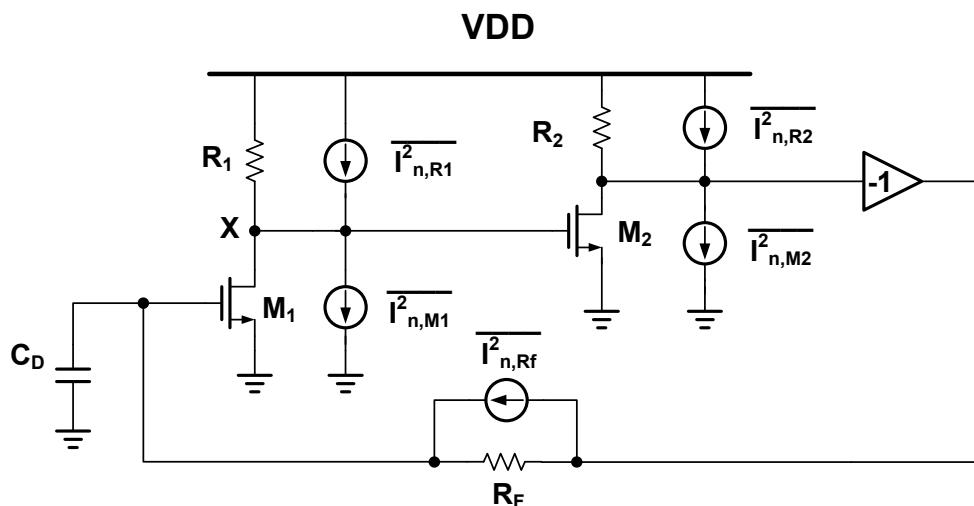

轉阻放大器位於接收端的第一級，除了要兼顧速度和增益外，雜訊也是很重要的考量。我們將轉阻放大器化為等效半電路，如圖 4.4 所示。推導出的輸入等效雜訊電流如式 (4.1)，這個重要的參數決定了系統的靈敏度。

圖 4.4 轉阻放大器雜訊等效半電路

$$\overline{I_{n,in}^2} = \frac{4kT}{R_F} + \frac{1}{g_{m1}^2} \left( \frac{1}{R_F^2} + \omega^2 C_D^2 \right) \left( \frac{4kT}{R_1} + 4kT\Gamma g_{m1} \right) \\ + \frac{1}{g_{m1}^2 g_{m2}^2} \left( \frac{1}{R_F^2} + \omega^2 C_D^2 \right) \left( \frac{1}{R_1^2} + \omega^2 C_X^2 \right) \left( \frac{4kT}{R_2} + \frac{4kT}{R_F} + 4kT\Gamma g_{m2} \right)$$

為增加靈敏度，我們希望轉阻放大器的增益加大，以降低後級雜訊對電路輸入端的影響。我們注意到若希望降低輸入等效雜訊電流，我們需增加  $R_F$ 、 $g_{m1}$ 、 $g_{m2}$ ，並設法降低檢光二極體的雜散電容  $C_D$ 。根據 Friis 公式，我們傾向將前級的增益放大以降低後端雜訊對輸入端的影響，故  $g_{m1}$  會設計得比  $g_{m2}$  大。

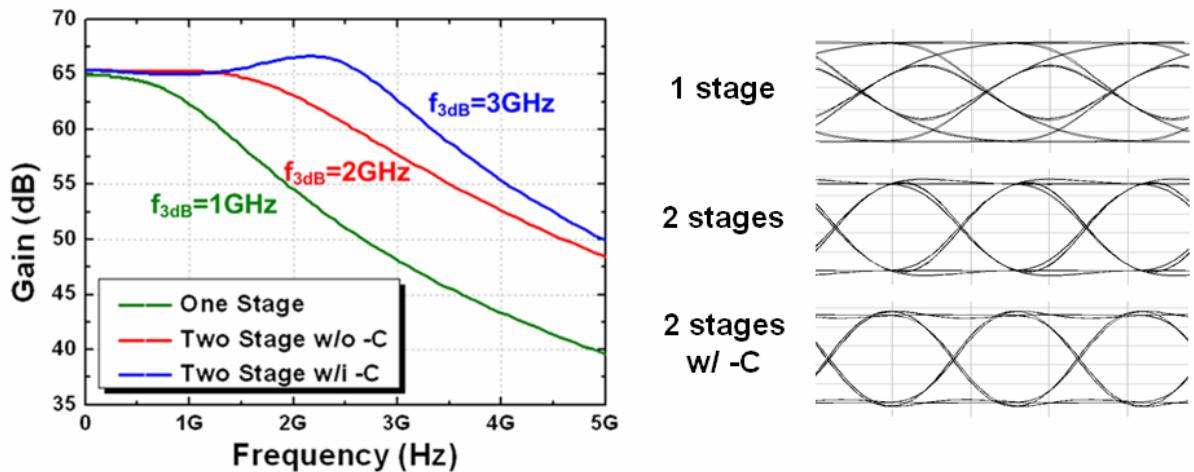

圖 4.5 是轉阻放大器的頻率響應圖。我們看到兩級的架構因為有較大的開迴路增益，故大大地提升了電路頻寬，再加上主動式負電容補償輸出極點，使整體頻寬增進為原先一級架構的三倍。

圖 4.5 轉阻放大器頻率響應與眼圖模擬

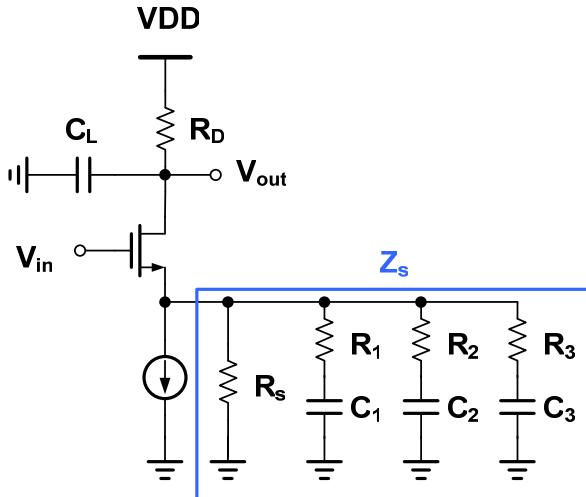

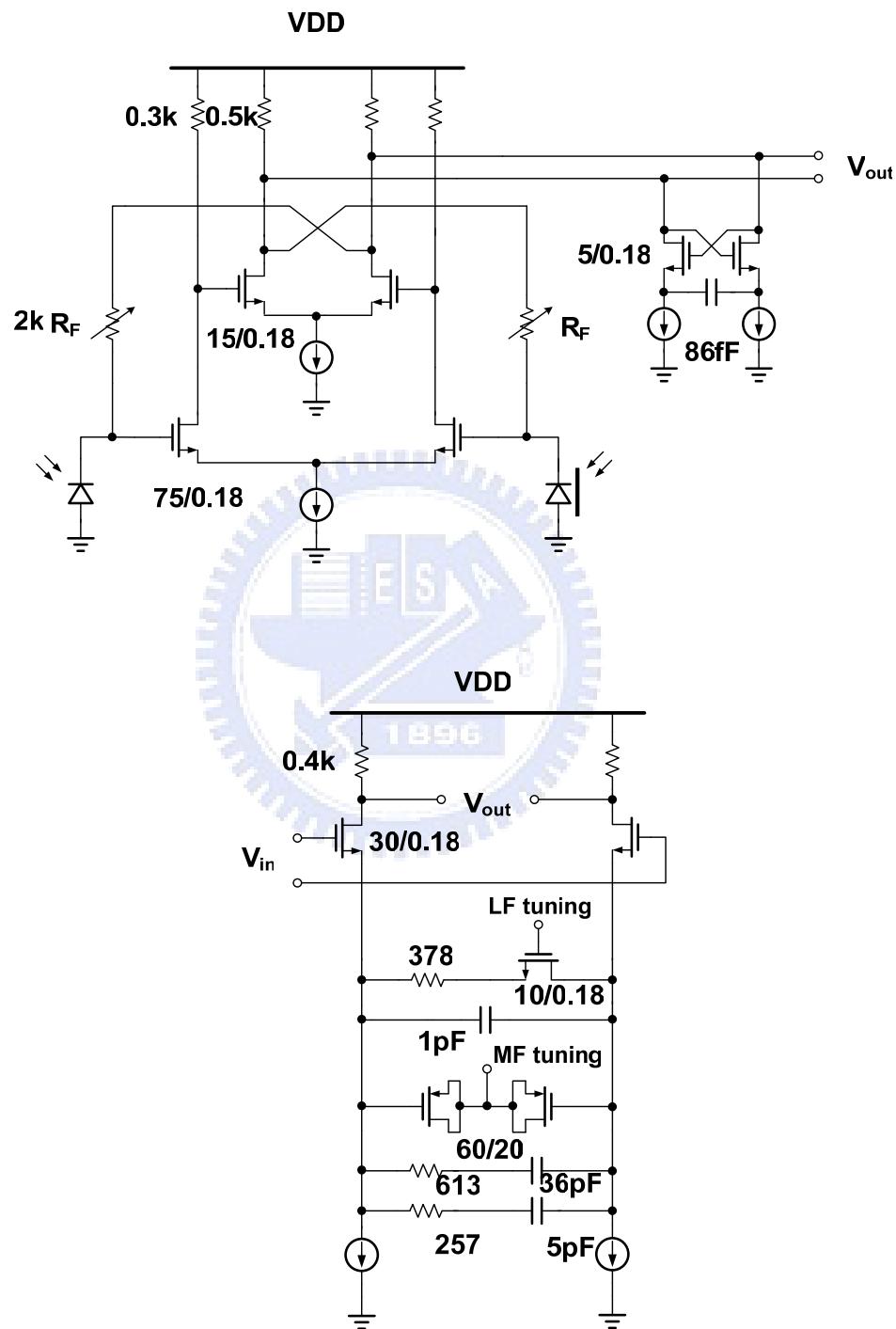

### 4.3.2 多頻帶補償式源極退化級

為了使增益隨頻率增加時上升，我們實現一源極退化級，製造實數零點 (real zero) 補償檢光二極體的緩慢增益下降。這樣的技巧有優異的線性度，具很大的補償範圍，在調整時不至影響資料路徑 (data path)，且零點提供額外的相位補償能使抖動減少。不同於一般纜線等化器 (cable equalizer) [20]~[23] 將源極退化級分數級實現不同頻帶的補償，CMOS 檢光二極體的增益下降因為有著緩慢而跨越幾個數量級的特性，故可將不同頻帶的補償整合進一級實現 [6]。如此一來，不但有助於降低面積和複雜度，更可避免額外的雜訊貢獻。如圖 4.6 所示。

圖 4.6 多頻帶補償式源極退化級

$$|A_v| = \frac{V_{out}}{V_{in}} \approx \frac{R_D}{\frac{1}{g_m} + Z_s \parallel r_o}$$

因為電容的阻抗和頻率成反比，故我們可將  $Z_s$  網路裡的電容視為低頻時阻絕信號的元件，經由適當設計可使頻率上升時依序開啟， $R_s$  便依序其他電阻並聯。若我們設計  $C_1 > C_2 > C_3$  且  $R_1 > R_2 > R_3$ ，則  $R_s$  便會在頻率較大時和較小的電阻並聯，因而  $Z_s$  的阻抗會隨頻率增加而減少，使整體電路的增益隨頻率增加時緩慢上升。

我們假設  $g_m$  很大且  $R_s = R_D$ ，則：

$$\begin{aligned} \frac{V_{out}}{V_{in}} &\approx - \left( 1 + \frac{sR_D C_1}{1 + sR_1 C_1} + \frac{sR_D C_2}{1 + sR_2 C_2} + \frac{sR_D C_3}{1 + sR_3 C_3} \right) \\ \Rightarrow \left| \frac{V_{out}}{V_{in}} \right| &= 1 \quad \text{at low frequency} \\ \left| \frac{V_{out}}{V_{in}} \right| &= 1 + \frac{R_D}{R_1} + \frac{R_D}{R_2} + \frac{R_D}{R_3} \quad \text{at high frequency} \\ \Rightarrow &\text{with a low roll-up behavior for intermediate frequency} \end{aligned}$$

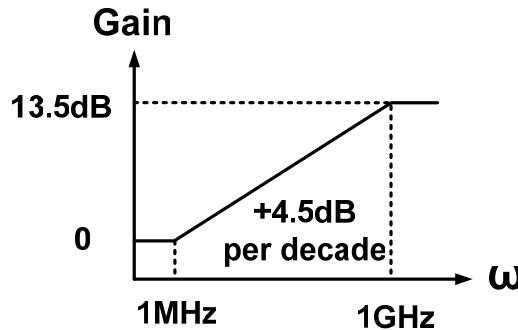

在我們的 Medici 模擬裡，檢光二級體的本質響應從 1MHz 到 1GHz 緩慢下降了大約 13.5dB，於是我們將等化器裡高通濾波器的時間常數分別設定為對數座標上 1MHz 到 1GHz 間三個等距的頻率，每極補償 4.5dB，如圖 4.7 所示。

圖 4.7 源極退化級頻率響應示意圖

等化器裡電阻電容值的一階估計如下：

$$R_n = \frac{R_D}{10^{\frac{\Delta dB \cdot n}{20}} - 10^{\frac{\Delta dB \cdot (n-1)}{20}}} \quad C_n = \frac{1}{2\pi \cdot f_n \cdot R_n}$$

$$f_n = f_{\min} \cdot \left( \frac{f_{\max}}{f_{\min}} \right)^{\frac{n-1}{3}} \quad n=1,2,3$$

先以每極補償 4.5dB 的條件決定出電阻值，而後再決定出三個在對數座標上等距的頻率，最後以此時間常數決定出電容值。

我們推導可補償的最大範圍為：

$$\begin{aligned} \text{Maximum boosting} \Rightarrow \Delta |A_v| &= 20 \log \left| \frac{A_{v,Max}}{A_{v,min}} \right| \\ &= 20 \log |g_m R_D| - 20 \log \left| \frac{R_D}{1/g_m + R_s \parallel r_o} \right| \\ &= 20 \log |1 + g_m (R_s \parallel r_o)| \end{aligned}$$

然而，當  $R_s$  增加時代表直流增益下降，而且會降低整個系統的信號雜訊比 (Signal to Noise Ratio, SNR)，故補償有其限度。

此外，源極退化級因為有接地的電阻電容網路，故對鎧線所提供的雜散電感效應特別敏感。於是，我們選擇採用差動的架構實現此多頻帶補償式源極退化電路，以隔絕 RC 網路對地的直接連接，避免鎧線效應對補償網路造成非預期的影響。最後的電路如圖 4.8 所示，頻寬由 6MHz 跳進至 1.5GHz 且增益相當平坦，表示此一等化電路可補償擴散載子的緩慢增益下降效應。

圖 4.8 差動式源極退化級

鎊線效應對源極退化級之影響如圖 4.9 所示，單端的架構在鎊線電感為  $1\text{nH}$  時就有顯著的震盪和不穩定的情況，然而差動的架構卻可忍受  $3\text{nH}$  的鎊線電感，大幅提昇電路的可行性與穩定度。

圖 4.9 鎊線效應對源極退化級之影響

在源極退化級裡，主要的面積是由電容所佔據。為了補償低頻的響應，我們需要比較大的時間常數，因而需要比較大的電容值，其值約為數十  $\text{pF}$ 。這裡凸顯了差動源極退化級的另一個優點，由於差動電路的特性，故所需的電容值僅為單端電路的一半，大幅減少佈局的面積。

### 4.3.3 電感頂峰

此外，我們可以使用電感，以複數極點（complex pole）補償高頻響應。傳統的被

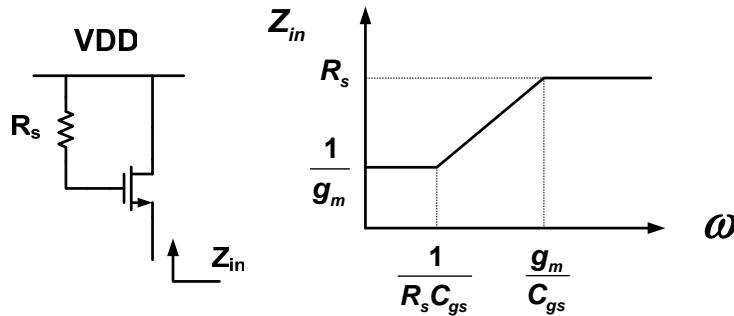

動電感因為面積較大，且在晶片製造後缺乏可調整的空間，故我們使用主動式電感實現高頻補償[17]，以更進一步增加系統頻寬。在這裡使用主動式電感主要原因是它提供了高頻補償的調整彈性，以確保在製程偏移時仍可正確補償。主動式電感的原理如圖 4.10 所示，在 $g_m$ 大於 $R_s$ 的條件下，圖中的 $Z_{in}$ 阻抗會隨著頻率增加而增加，等效上可用以補償高頻的衰減。等效電路如圖 4.11 所示。

圖 4.10 主動式電感示意圖

圖 4.11 主動式電感等效電路

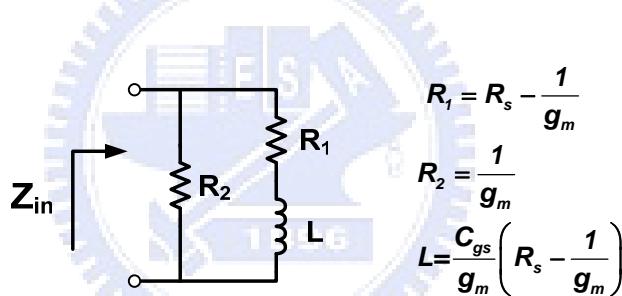

實際的電路如圖 4.12 所示，頻寬由 1.5GHz 增進至 2.5GHz，約為 1.67 倍的增量。

圖 4.12 差動式主動電感

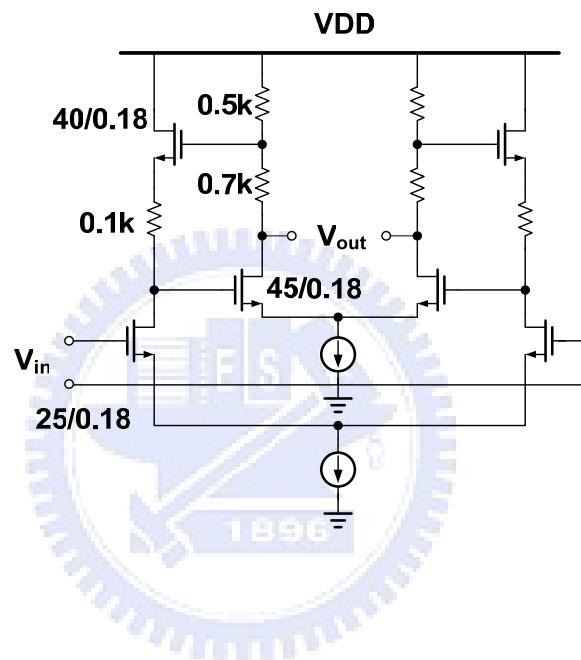

#### 4.3.4 增益放大級

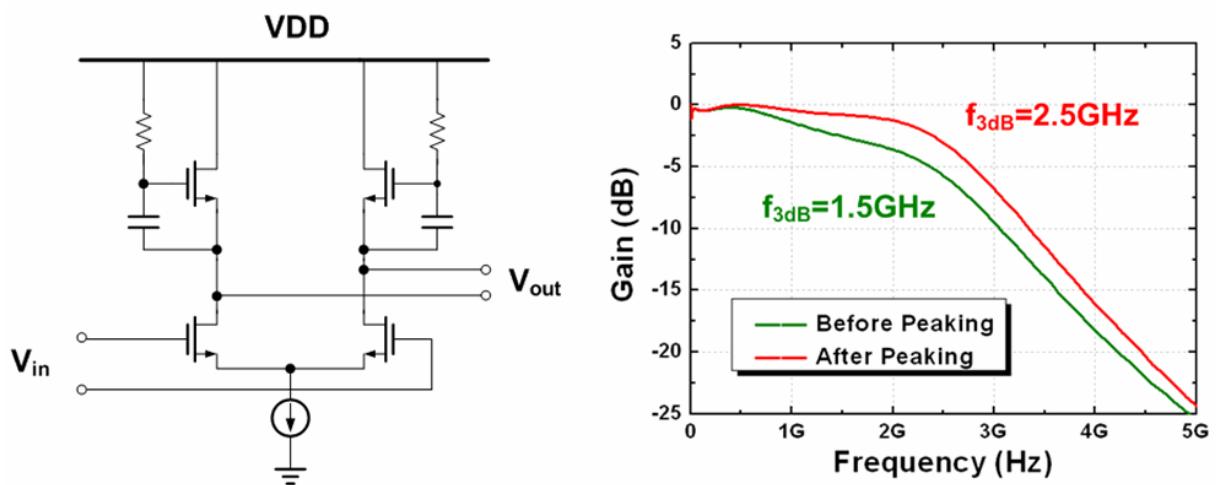

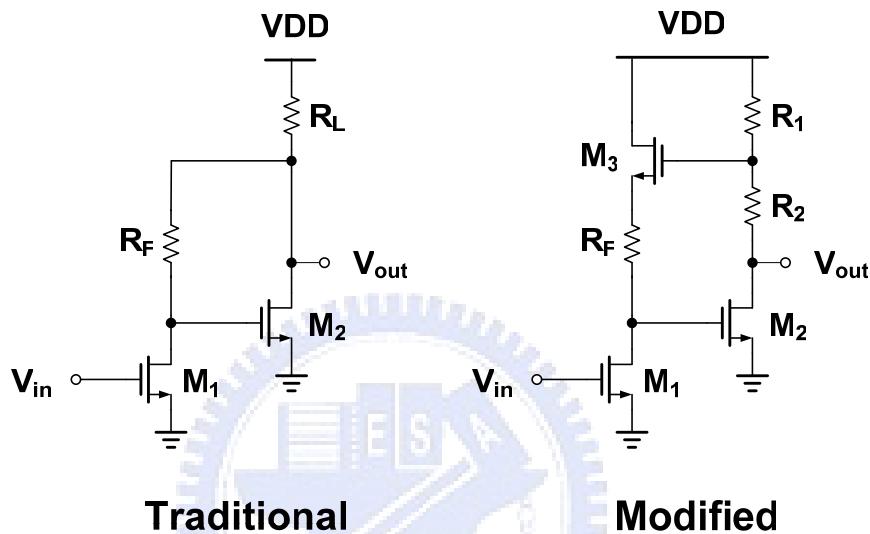

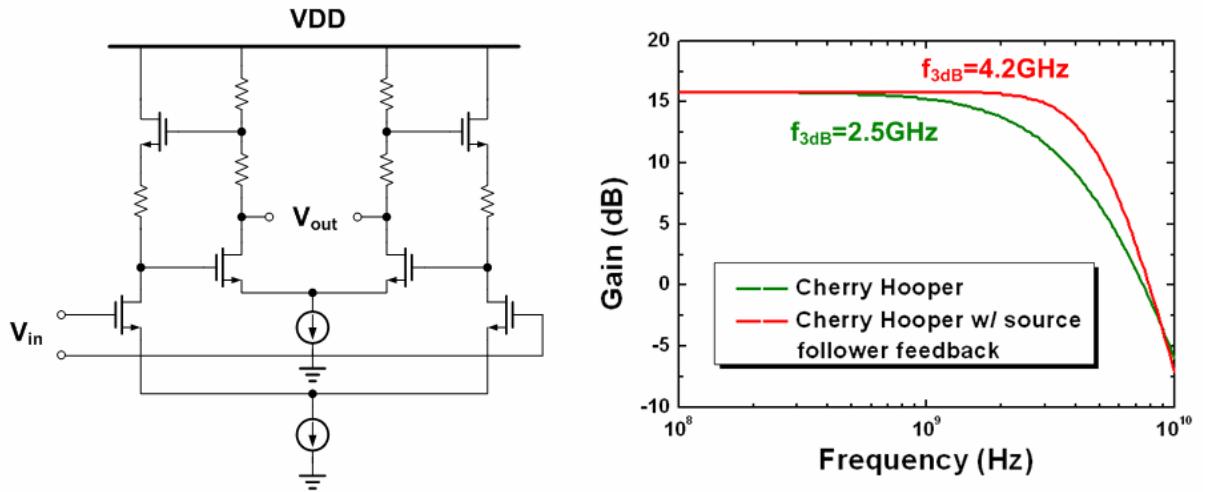

為了高增益和高頻寬的需求，這裡的增益放大器使用Cherry-Hooper的架構。傳統的Cherry-Hooper放大器是由一轉導放大器和一轉阻放大器所組成，利用後者電壓-電流負回授的特性提高中間的極點和輸出的極點，以達成高速的應用。改良式的Cherry-Hooper放大器則在回授路徑上多加一個源極隨耦器，**M<sub>3</sub>**，在頻寬相當的情況下額外提升增益[18][19]。如圖 4.13 所示。

圖 4.13 傳統與改良之 Cherry-Hooper 放大器

我們推導出兩者的直流增益約為：

$$|A_v| = g_{m1} R_F \quad \text{for traditional Cherry-Hooper}$$

$$|A_v| = g_{m1} R_F \left( 1 + \frac{R_2}{R_1} \right) \quad \text{for modified Cherry-Hooper}$$

為了高增益和高頻寬的需求，這裡的增益放大器使用改良式 Cherry-Hooper 的架構，如圖 4.14 所示，其增益上升量為  $(1+R_2/R_1)$  倍。在這裡我們將多增進的增益以頻寬增進的方式呈現，其增進量為 17.倍。串接兩級增益放大器約可提供 16dB 的增益，中間沒有安插額外的源極隨耦器，不需要其他補償技巧便可達到 4.2GHz 的頻寬。

圖 4.14 具源極隨耦器回授之 Cherry-Hooper 放大器

#### 4.3.5 輸出緩衝級

輸出緩衝級以一個電流模邏輯 (current mode logic, CML) 電路實現。

圖 4.15 輸出緩衝級

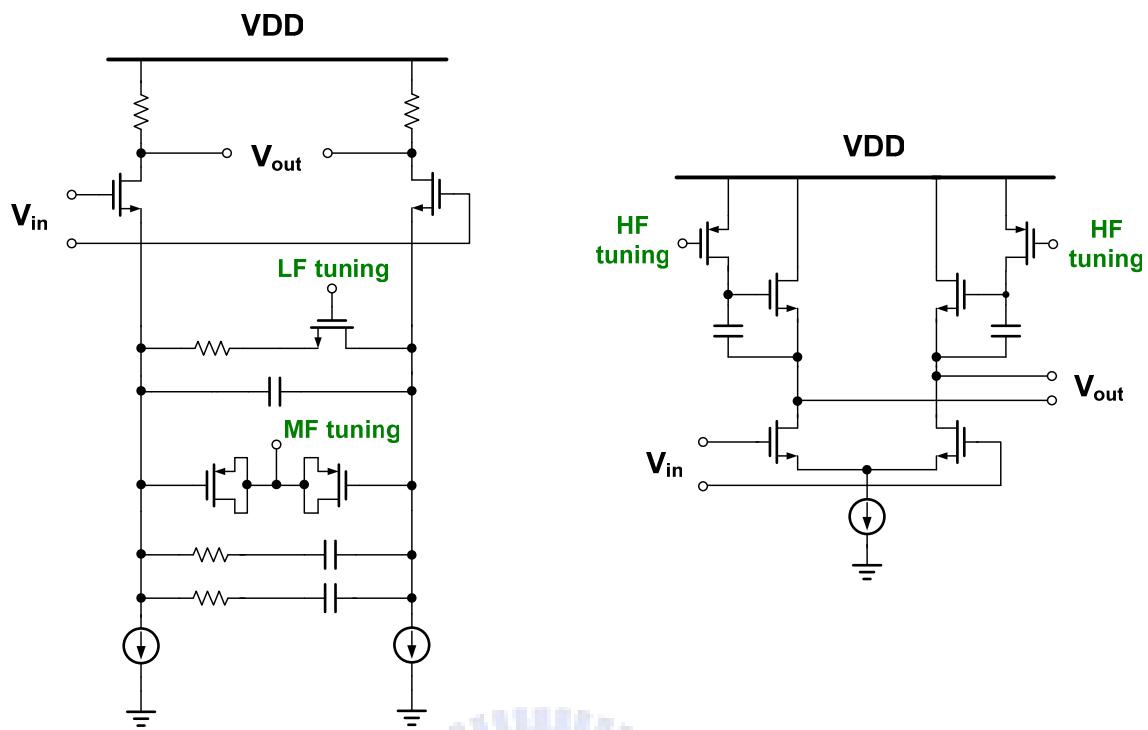

#### 4.3.6 檢光二極體製程飄移補償機制

檢光二極體為此電路裡所欲補償的對象，若是因為製程變動而使響應有所變化，後端的電路可能會補償不足或過份補償，前者造成符號間干擾，後者使雜訊增加。因此，我們以元件模擬軟體 TCAD 模擬檢光二極體的飄移，並在等化器級裡保留不同頻段微調的彈性。

圖 4.16 檢光二極體製程飄移補償機制

圖 4.17 是考慮到檢光二極體製程飄移時的模擬結果，其變異量如第三章所述。此外，電路的溫度也和檢光二級體同時變異。

圖 4.17 檢光二極體製程飄移補償模擬

#### 4.4 模擬結果與佈局考量

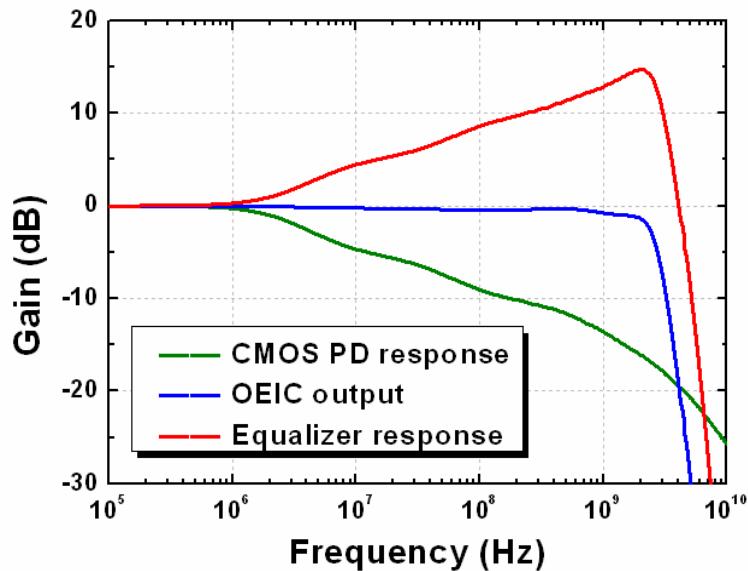

圖 4.18 為單晶整合光接收器的頻率響應，等化器約補了 15dB 的衰減，最後整體的頻寬達到 2.5GHz，且增益相當平坦，適合高速的應用。

圖 4.18 單晶整合光接收器頻率響應模擬

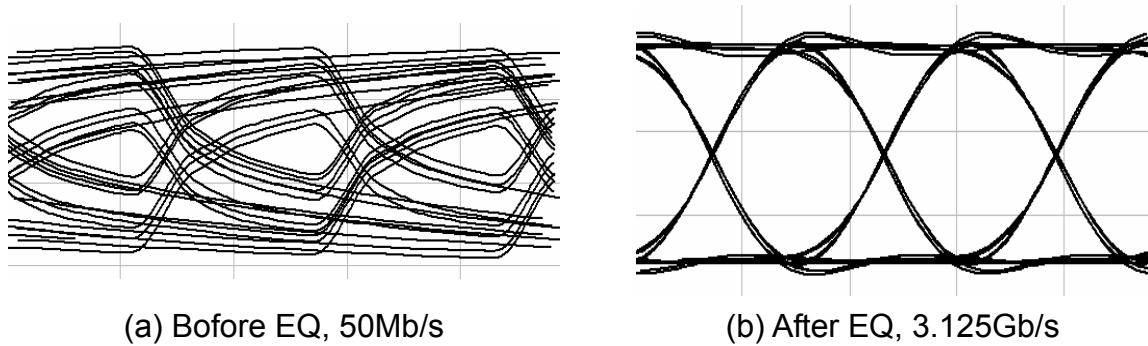

圖 4.19 為等化器前後的眼圖。我們可以看到因為 CMOS 檢光二極體本質響應的緣故，在等化前即使打進 50Mb/s 的信號其符號間干擾仍非常嚴重，而且存在顯著的尾狀響應。然而，在等化後補償了擴散載子的效應，大幅提昇頻寬並消去符號間干擾，因此在 3.125Gb/s 的信號下仍有具高誤碼率的眼圖。

圖 4.19 光接收眼圖模擬

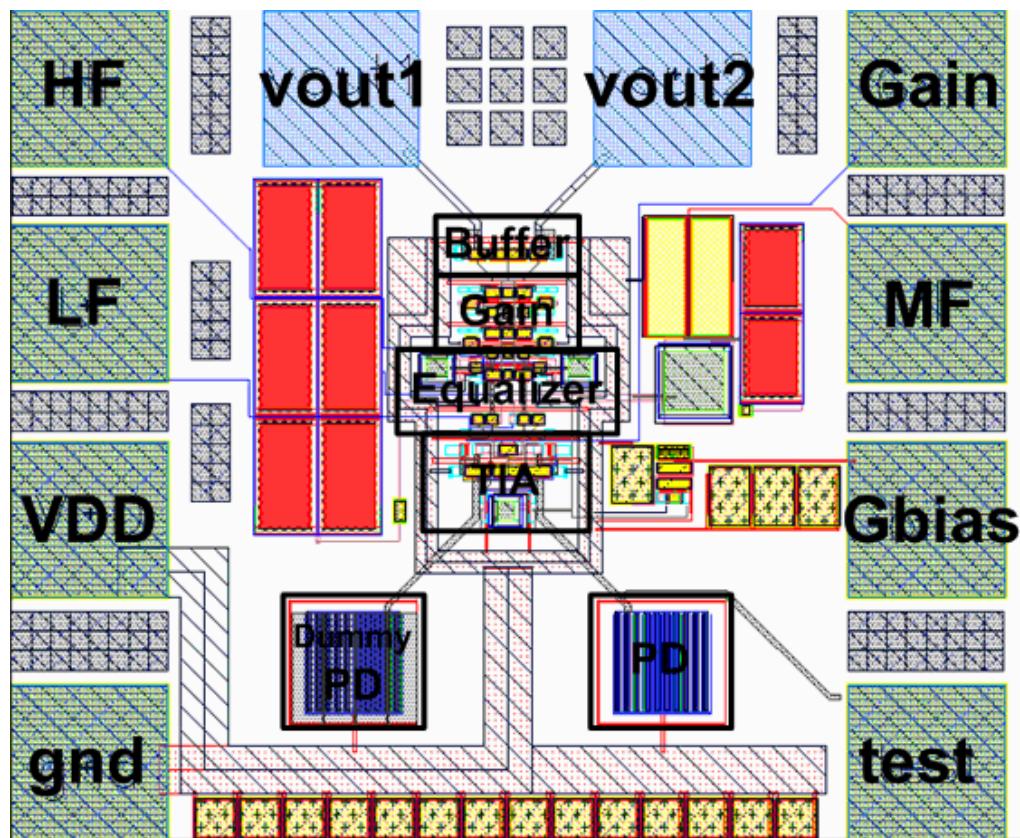

在佈局方面，我們以對稱性為優先考量。電路裡所有差動的部分皆為對稱，信號走線選擇較高層的金屬以減少基版雜訊的耦合，且盡量縮短信號走線的長度。多餘的檢光二極體和接收光的檢光二極體佈局相同，但在最上層鋪設金屬以隔絕光的進入。為單獨量測檢光二極體，電路輸入端拉出一條浮接的金屬，並預留一個空的腳位做測試用。電源及直流控制電壓都有對地的去耦（decoupling）電容，除了穩壓的功能外，也可濾去高頻雜訊。此晶片面積為  $510\mu\text{m} \times 430\mu\text{m}$ 。

圖 4.20 佈局圖

|                            | <b>Design Target</b> | <b>Simulation Result</b> |

|----------------------------|----------------------|--------------------------|

| <b>Technology</b>          | 0.18μm CMOS          | 0.18μm CMOS              |

| <b>Optical Wavelength</b>  | 850nm                | 850nm                    |

| <b>Bandwidth</b>           | 2.2GHz               | 2.5GHz                   |

| <b>Data rate</b>           | 3.125Gb/s            | 3.125Gb/s                |

| <b>Transimpedance Gain</b> | 66dBΩ                | 69dBΩ                    |

| <b>DC Responsivity</b>     | 0.5A/W               | 0.55A/W                  |

|                          |                                |                                |

|--------------------------|--------------------------------|--------------------------------|

| <b>Sensitivity</b>       | -15dBm @ BER=10 <sup>-12</sup> | -14dBm @ BER=10 <sup>-12</sup> |

| <b>Chip Size</b>         | NA                             | 510μm × 426μm                  |

| <b>Power Dissipation</b> | NA                             | 38mW                           |

表 4.1 預計規格列表

## 4.5 量測結果

### 4.5.1 量測環境

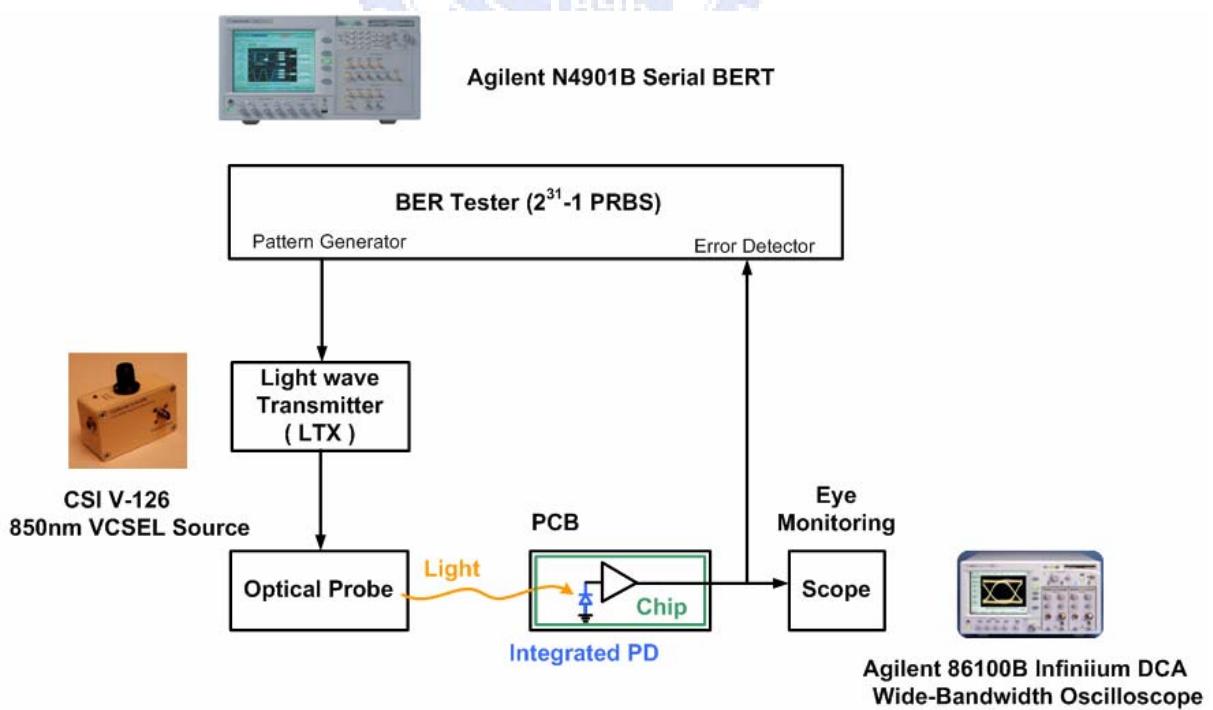

在這次的量測裡主要分兩部分，分別為暫態響應和頻率響應。暫態響應量測的部分如圖 4.21 所示，我們利用 Agilent N4901B 誤碼率測試儀 (Bit Error Rate Tester, BERT) 送出偽隨機位元串流 (Psuedo Random Bit Stream, PRBS)，而後以 CSI V-126 光發射器將電訊號轉成波長為 850nm 的光訊號，經由光針將光聚在整合於晶片裡的檢光二極體上。晶片輸出的信號送入 Agilent 86100B 示波器觀察眼圖，並送回 Agilent N4901B 量測誤碼率。光功率的大小由 AFL OVA5 可變光衰減器 (Variable Fiber Optic Attenuator) 調整，並由 AFL OPM4 光功率量測器 (Optical Power Meter) 量測從光發射器送出的光功率。

圖 4.21 暫態響應量測環境

頻率響應量測的部分如圖 4.22 所示，我們利用 Agilnet E5071B 網路分析儀（Network Analyzer）送出信號，而後以 CSI V-126 光發射器將電訊號轉成波長為 850nm 的光訊號，經由光針將光聚在整合於晶片裡的檢光二極體上。晶片輸出的信號送回 Agilnet E5071B 量測頻率響應，並用 CSI P-101 高速光接收器作為一理想的對照組，將雷射和射頻（Radio Frequency, RF）電纜的響應校正掉。

圖 4.22 頻率響應量測環境

#### 4.5.2 檢光二極體量測

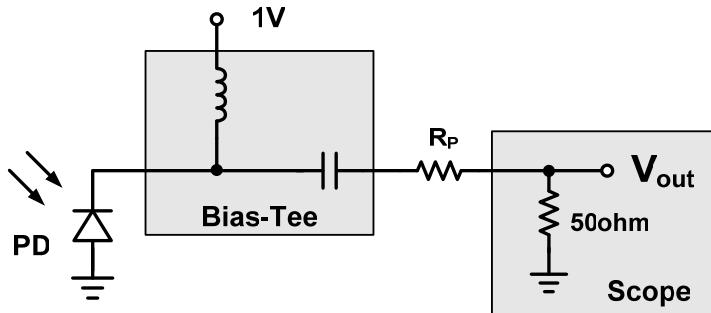

檢光二極體的量測藉由聚焦離子束（Focused Ion Beam, FIB）的方法將檢光二極體往電路的走線切斷避免額外干擾，並將檢光二極體陰極接到原本預留測試的空腳位上。而後，利用電源隔離器（Bias-Tee）提供直流逆偏壓，並將射頻端的電流信號信號送進儀器，藉由儀器裡的 50ohm 阻抗轉換成電壓，如圖 4.23 所示。這是因為檢光二極體本身有一個 pF 級的雜散電容，故僅用儀器的 50ohm 電阻做電流-電壓的轉換，以免產生太低的極點而影響低頻本質響應的觀察。

圖 4.23 檢光二極體量測設定

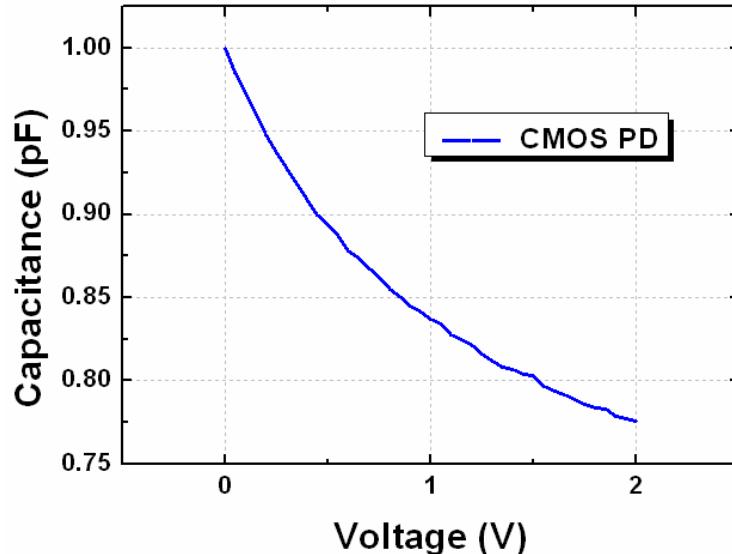

為減少額外的寄生效應，檢光二極體的特性 (characteristic) 藉由下針的方式量測。我們利用 Agilent 4284A (Precision LCR Meters) 量測 CV 特性，由圖 4.24 所示。我們可以觀察在 1V 時的寄生電容約為  $0.84\text{pF}$ ，比所預估的值大了  $0.26\text{pF}$ 。主要的原因是因為此檢光二極體直接整合進電路，沒有浪費額外的面積製造測試元件，因此無法將 pad 和走線等的效應去嵌化 (de-embedding)。

圖 4.24 檢光二極體 C-V 圖量測

檢光二極體的響應率如表 4.2 所示，在平均光功率為  $0\text{dBm}$  時期響應率約為  $0.272\text{A/W}$ ，約為之前模擬的一半 ( $0.55\text{A/W}$ )。這是因為多模光纖的直徑雖然為  $50\mu\text{m}$ ，但其聚光點 (spot size) 的直徑卻大於  $50\mu\text{m}$ ，致使無法將所有的光都送進面積為  $50\mu\text{m} \times 50\mu\text{m}$  的檢光二極體內。此外，整合進 CMOS 的檢光二極體沒有額外的防反射塗佈，加上標準 CMOS 製程有多層的介質 (dielectric layer)，多餘的反射折射這也是響應率比之前預期來得低的原因之一。

| Average Power |      | Meas. I | Cal. R |

|---------------|------|---------|--------|

| (dBm)         | (mW) | (uA)    | (A/W)  |

| 0             | 1.0  | 272     | 0.272  |

表 4.2 檢光二極體響應率量測

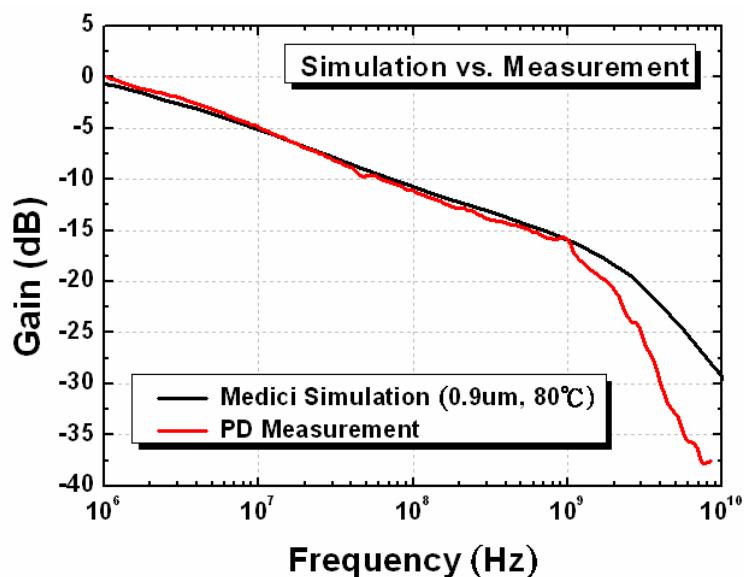

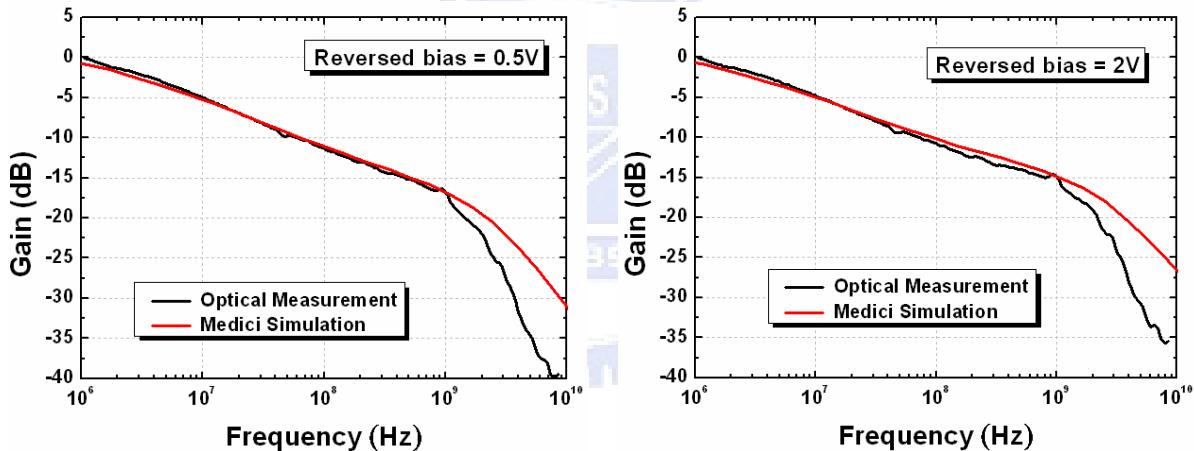

檢光二極體的頻率響應如圖 4.25 所示，逆偏壓為 1V。在 GHz 之前的緩慢增益下降符合之前 Medici 模擬的預期，這部分為檢光二極體的本質響應，頻率每跨過一個數量級增益就約下降 5dB。雖然檢光二極體的響應落於模擬時的某一個極端，但因為電路裡有為此變異預留的可調設計，故後面與電路整合時仍能量出有品質的信號。

圖 4.25 檢光二極體頻率響應量測

然而，GHz 以上的響應除了是因為高速的飄移載子造成外，也和 RC 時間常數造成的外質響應有關，因此我們看到在 GHz 以上有不相符的現象。我們在 ADS 的模擬裡加入一個雜散電阻的效應，如圖 4.26 所示，發現此電阻變化可改變 GHz 以上增益下降的狀況，於是可解釋檢光二極體的量測結果。等效上改變雜散電容也有相同的效應。

圖 4.26 雜散電阻造成的外質響應變化

此外，我們也提供檢光二極體不同大小的逆偏電壓，分別為 0.5V 和 2V，其量測與模擬的本質響應皆符合，如圖 4.27 所示。

圖 4.27 不同逆偏下的檢光二極體響應量測

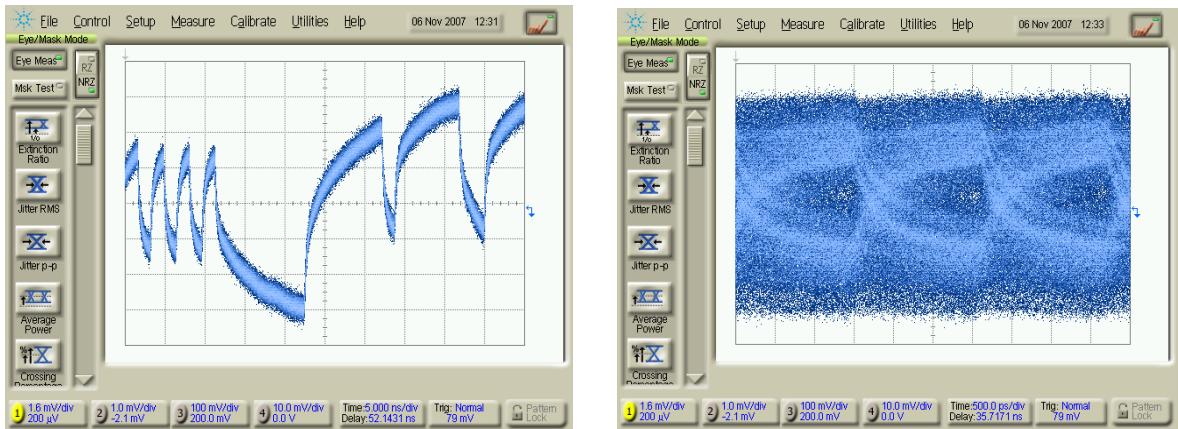

最後，我們量測檢光二極體的暫態響應，如圖 4.28 所示。送入信號速率為 622Mb/s，此為儀器可提供的最低速度。我們觀察到即使在此相對低速的信號下仍有顯著的符號間干擾，並存在擴散載子所造成的尾狀響應。此外，由於嚴重的符號間干擾，因此無法量得高品質的眼圖，誤碼率也大於  $10^{-1}$ 。

圖 4.28 檢光二極體暫態響應與眼圖量測（速度為 622Mb/s）

### 4.5.3 單晶整合光接收器量測

我們把檢光二極體接上後端電路後，測量所得頻率響應如圖 4.29 所示，經由等化器補償檢光二極體本質響應後，整體頻寬提升為 2.5GHz。

圖 4.29 光接收器頻率響應量測

眼圖量測如圖 4.30 所示。我們發現由於等化級補償了緩慢擴散載子的效應，故能得到一個消去符號間干擾的眼圖。然而，由於偽差動的架構存在一先天的直流偏移，故眼圖看起來有些許非線性。此效應在輸入高功率的光信號時會更明顯，因為過載 (overload) 的緣故產生明顯的失真。這部分可由調整轉阻放大器的  $R_F$  改善。

圖 4.30 光接收器眼圖量測 (-8.5dBm, 速度為 3.125Gb/s)

圖 4.31 為雜訊功率頻譜 (noise power spectrum) 量測和雜訊推估。我們將光關掉，僅量測電路本身的雜訊功率，將之積分至資料速度 (3.125GHz)，利用增益、響應率、亮暗比 (extinction ratio) 等參數推出靈敏度為-8.16dBm。

$$P_{in} = -10.5 \text{ dBm} \quad \rho = 1.04 \quad R = 0.272$$

$$I_{p-p} (\mu A) = [10^{(-10.5/10)}] \times \rho \times R = 25.2 (\mu A)$$

$$V_{p-p} (mV) = 52 mV$$

$$\text{gain} = \frac{52 mV}{25.2 \mu A} = 2.06 k(\text{single end})$$

$$dBmV = 47 + (\text{value dBm}) \quad \text{for } 50\Omega \text{ system}$$

$$I_N = \frac{10^{\left(\frac{-31+47}{20}\right)} (mV)}{\text{gain}} = \frac{6.31 m}{2.06 k} = 3.06 \times 10^{-6}$$

$$\begin{aligned} \text{Sensitivity} &= 10 \times \log(14.1 \times I_N \times \frac{1}{\rho} \times \frac{1}{R} \times 1000) \\ &= 10 \times \log(14.1 \times 3.06 \times 10^{-6} \times \frac{1}{1.04} \times \frac{1}{0.272} \times 1000) = -8.16 \text{ dBm} \end{aligned}$$

圖 4.31 雜訊功率頻譜量測和雜訊推估

圖 4.32 為直方圖 (histogram) 量測和雜訊推估，我們將光關掉，僅量測電路本身的雜訊分佈，以標準差 (standard deviation) 和其他參數推出靈敏度為-8.99dBm。

$$I_N = \frac{5.21}{2.06} \times 10^{-6} = 2.53 \times 10^{-6}$$

$$\begin{aligned} \text{Sensitivity} &= 10 \times \log \left[ \frac{14.1 \times I_N}{R \times \rho} \times 1000 \right] \\ &= 10 \times \log \left[ \frac{14.1 \times 2.53 \times 10^{-6}}{0.272 \times 1.04} \times 1000 \right] \\ &= -8.99 \text{ dBm} \end{aligned}$$

圖 4.32 直方圖量測和雜訊推估

光學量測的誤碼率如圖 4.33 所示，在平均光功率大於-8.1dBm 時能達到小於  $10^{-12}$  的誤碼率。模擬與量測的靈敏度差異是因為光纖聚光點大於所設計的檢光二極體面積，加上介電層的反射折射，故響應率只有原先預期的一半，造成 3dB 的靈敏度下降；此外，光發射器非無窮大的亮暗比也對靈敏度造成影響，在亮暗比為 6dB 時約衰減 2.2dB 的靈敏度。

圖 4.33 光接收器在不同光功率下的誤碼率量測

#### 4.5.4 晶片照相圖與量測規格列表

圖 4.34 晶片照相圖

|                           | B. Nauta<br>2005 JSCC             | M. Steyaert<br>2006 JSSC           | This work                          |

|---------------------------|-----------------------------------|------------------------------------|------------------------------------|

| <b>Technology</b>         | 0.18μm CMOS                       | 0.18μm CMOS                        | 0.18μm CMOS                        |

| <b>Optical Wavelength</b> | 850nm                             | 850nm                              | 850nm                              |

| <b>Photodiode Area</b>    | 50μm×50μm                         | 80μm×80μm                          | 50μm×50μm                          |

| <b>Bandwidth</b>          | 1.5GHz                            | N/A                                | 2.5GHz                             |

| <b>Data rate</b>          | 3Gb/s                             | 500Mb/s                            | 3.125Gb/s                          |

| <b>DC Responsivity</b>    | N/A                               | N/A                                | 0.272A/W                           |

| <b>Sensitivity</b>        | -19dBm<br>@ BER=10 <sup>-11</sup> | -8dBm<br>@ BER=3×10 <sup>-10</sup> | -8.1dBm<br>@ BER=10 <sup>-12</sup> |

| <b>Chip Size</b>          | 700μm×400μm                       | 1000μm×570μm                       | 510μm×430μm                        |

| <b>Measurement Method</b> | On Wafer                          | On Board                           | On Board                           |

| <b>Power Dissipation</b>  | 50mW                              | 17mW                               | 36mW                               |

表 4.3 量測規格列表與比較

# 第五章 一個 5Gb/s 的寬頻單晶整合光接收器設計

## 5.1 研究動機

由於材料吸收的緣故，光的強度會和入射深度成指數的衰減關係，我們定義衰減至  $1/e$  時的深度為入射深度，是一個和波長相關的值。光波長越短時其能量越大，入射時有較多的光子被吸收而激發出電子電洞對，故入射深度較淺。CMOS 檢光二極體可接收的光波長有一定範圍：當入射光的波長太長時，其能量小於能隙故無法激發出電子電洞對，上限約為 1100nm；當入射光的波長太短時，在檢光二極體表面會產生超額載子，其很高的表面復合速率 (surface recombination rate) 使最後流出檢光二極體的光電流很小，下限約為 400nm。

不同光波長的穿透深度不同，產生基版緩慢擴散載子的數量也不同，故造成不同的頻率響應，其差異主要在基版載子所造成的低頻緩慢下降。因此，我們構思實現一可適性等化器 (adaptive equalizer) 以補償不同光波長的不同緩慢載子響應，在不需犧牲響應率的情況下，使此系統在一寬頻的光波長內都能達到高速的應用。

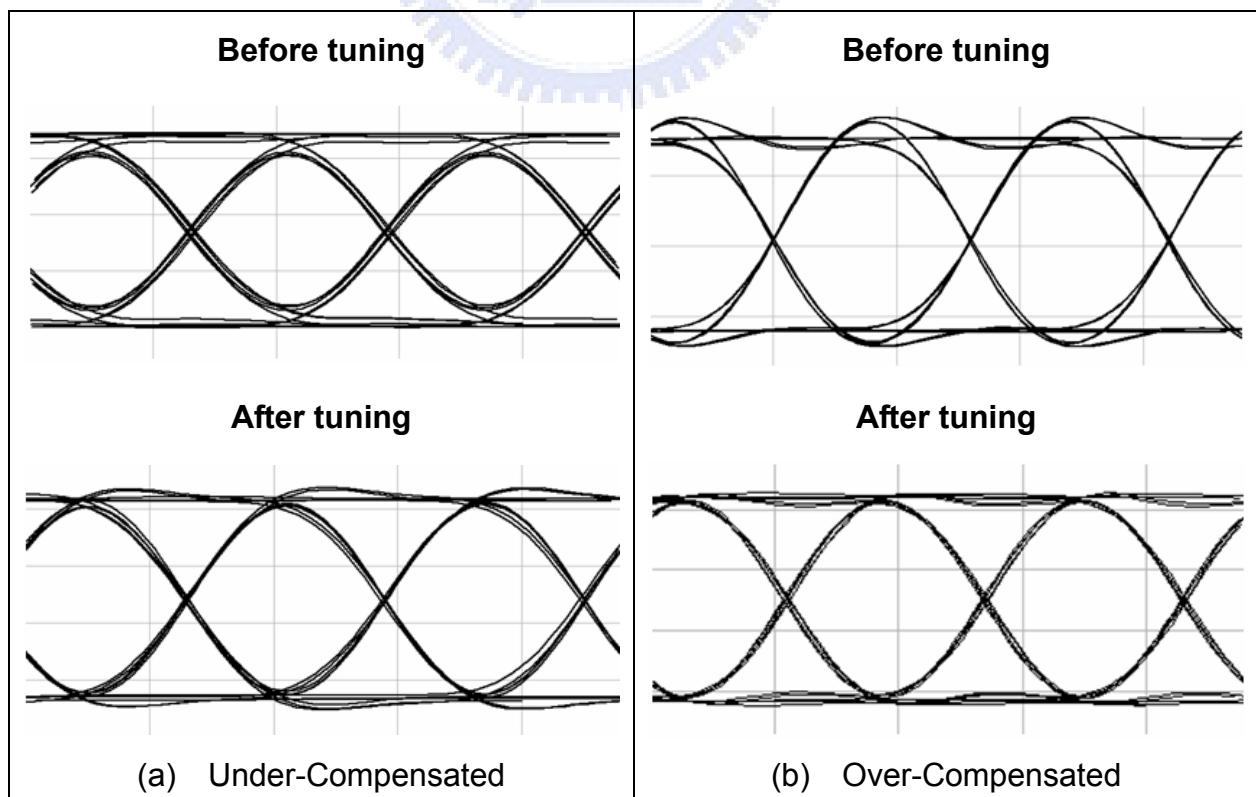

## 5.2 架構簡介與設計概念

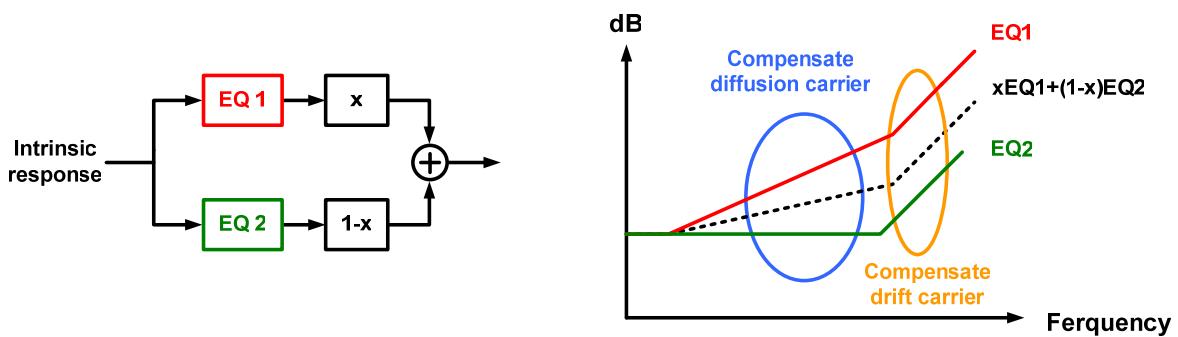

不同波長的入射光因為入射深度不同，故有不同的頻率響應，主要的差別在生成於基板的緩慢擴散載子響應，較高速的飄移載子和後端電路的 RC 時間常數限制對不同光波長影響並不顯著，此想法並經元件模擬軟體 Medici 驗證。於是如圖 5.1 所示，我們實現一可調整比率的等化器以補償不同光波長入射時的緩慢增益下降。

圖 5.1 設計概念

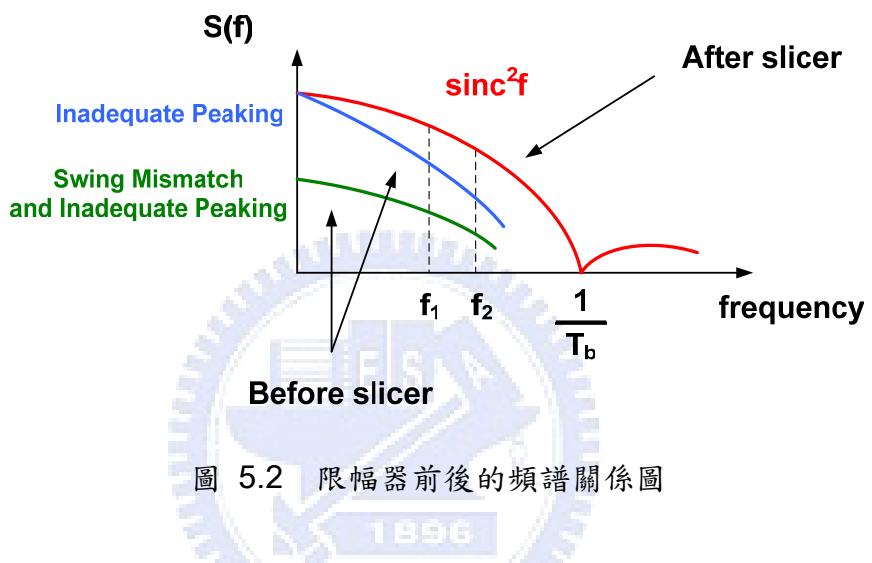

傳統的可適性架構比較高頻的能量以調整補償的程度[21]。信號經過限幅器(slicer)後近似一理想的方波訊號，而後藉由一個控制迴路去損益經過限幅器前信號的高頻響應，使之頻譜近似一理想方波的sinc函數(sinc function)。然而圖 5.2 所示為限幅器前後的頻譜，當我們在比較信號能量時，如果限幅器前後的信號能量(即低頻的部分)不一樣大，即使頻譜已是sinc函數(意即近似方波)，其等化迴路仍會執行過多或過少的補償[22][23]。因此，我們加入一個可變增益放大器維持限幅器前後信號能量，使等化過程中可以執行適當的補償。此外，可變增益級使不同功率大小的光打進檢光二極體時，都能有一足夠的輸出信號能量，以確保決策電路的正確執行。

圖 5.2 限幅器前後的頻譜關係圖

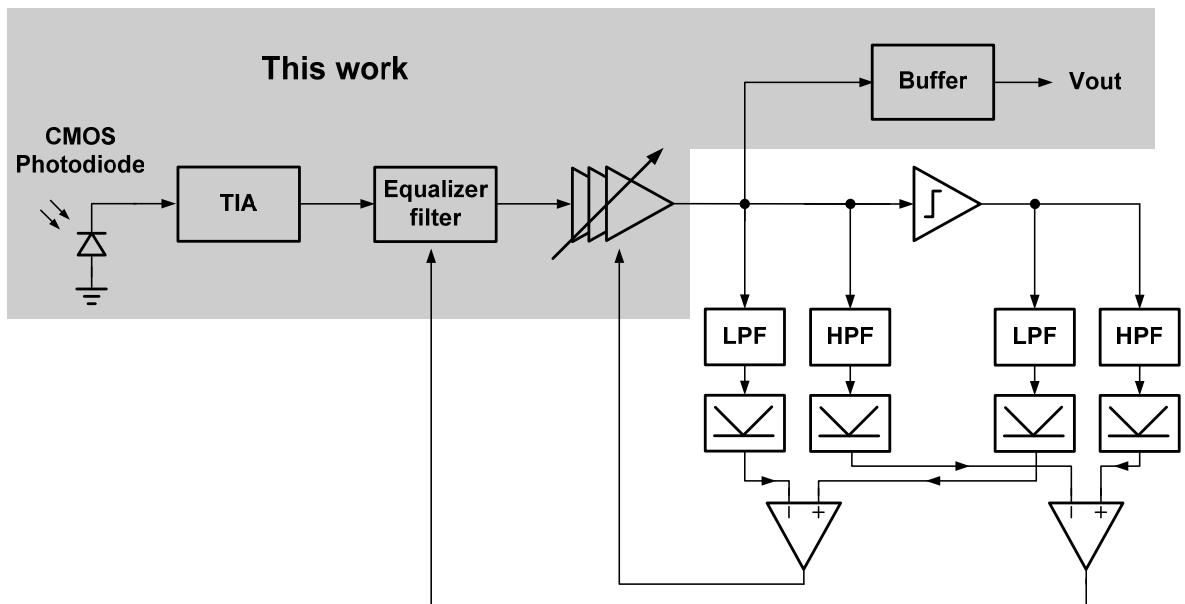

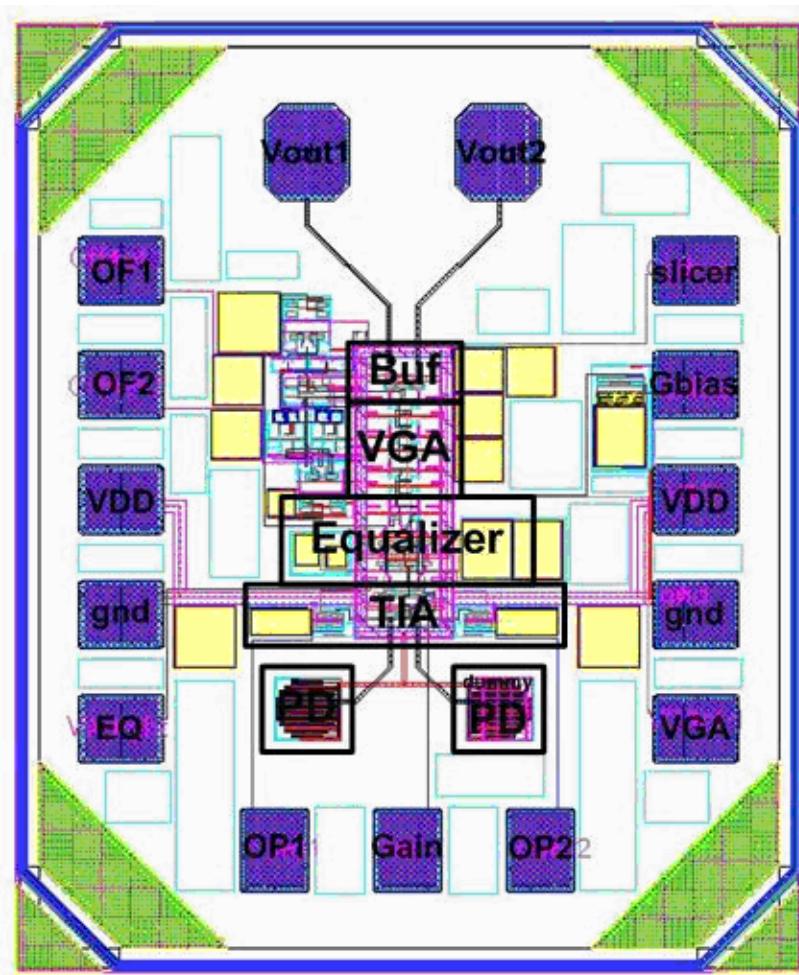

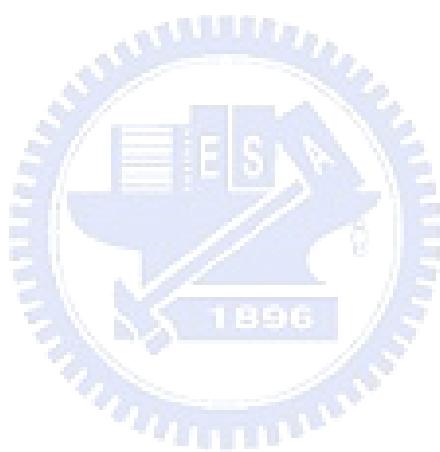

我們提出的可適性光接收器架構如圖 5.3 所示。最前端為一整合進 CMOS 的檢光二極體，經轉阻放大器將電流信號轉成電壓信號，再經由等化器補償。後面接著一個可控制增益的放大器(variable gain amplifier, VGA)，確保在不同大小的入射光下信號都有足夠的輸出振幅及正確的可適性判斷(adaptive decision)，信號至此經過一緩衝級到輸出的量測儀器。此外，信號在緩衝級前有另一路徑決定可適性的判斷，藉由比較限幅器前後信號能量決定可變增益大小，比較限幅器前後信號能量決定等化器的補償量。在這次的設計裡包含了前饋(feed-forward)路徑的電路，包含整合進 CMOS 的檢光二極體、轉阻放大器、加成式等化器、可變增益放大器與輸出緩衝級。

圖 5.3 光接收器架構圖

## 5.3 電路設計

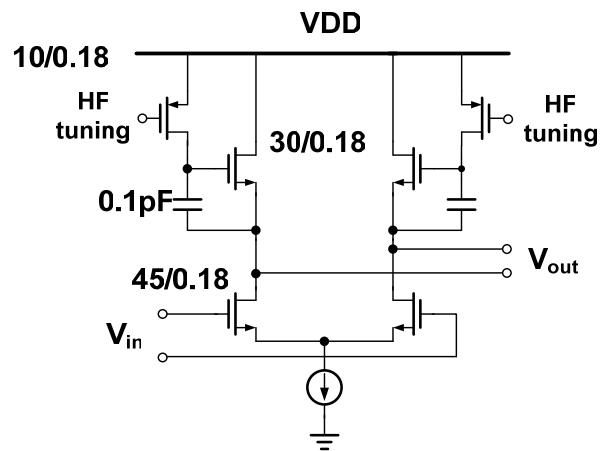

### 5.3.1 轉阻放大器

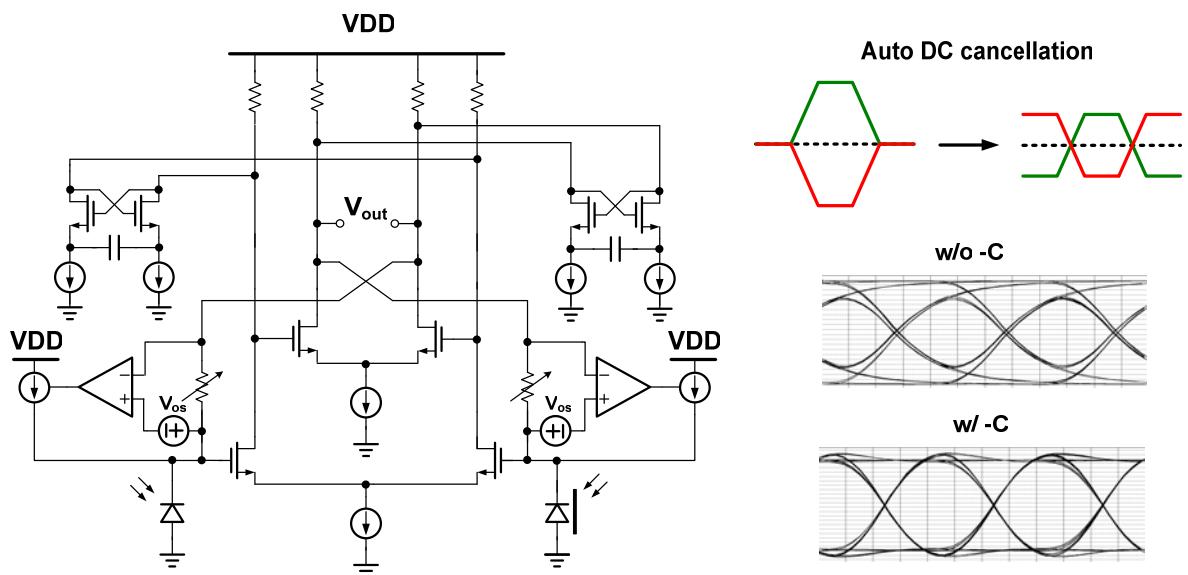

我們採用兩級的架構提升增益，並使用主動式負電容補償輸出端的電容效應，使頻寬提升為原本的 1.7 倍。此電路並包含了兩個直流消除（DC cancellation）的迴圈以增進動態範圍，並使後面的判斷能正確執行。此外，運算放大器內建的偏移電壓為 0.25V，使得轉阻放大器輸出的頭部空間更為提升。電路如圖 5.4 所示。

圖 5.4 轉阻放大器

### 5.3.2 加成等化級

在這次的應用裡，我們因為掌握了檢光二極體對不同光波長的不同斜率的增益下降響應，故捨棄傳統同時改變極點和零點的補償方式，以加成的方式做補償調整。

除了之前的多頻帶補償式源極退化級外，我們再用另一個可變源極退化級取代電感做更高頻的補償，以避免被動電感面積過大和主動電感耗損頭部空間（headroom）的缺點。這兩級同時使用了逆向縮放（inverse scaling）[24]和中性化（neutralization）[1]的技巧進一步增進頻寬，並使補償後的頻率響應盡量平整以減少抖動（jitter）。

加成電路的部分以電流模式（current mode）實現，控制流經輸出電阻上高速和低速信號的比例做出不同程度的緩慢增益上升，並使用主動式負電容補償輸出極點的頻寬限制。傳統以折疊式電流源形成的加成電路[25]，在加成時輸出端流經固定的電流，故其輸出直流準位固定，然而在加成的過程中兩個路徑的增益會同時變化，在此系統中代表在調整高頻增益時，低頻的增益也會變化。為避免等化迴路和可變增益迴路相互耦合造成系統收斂錯誤，我們去除多頻帶補償式源極退化級原有的源極電阻使低頻增益極小，並將低頻路徑的電流固定，使得等化器加成時僅改變高頻補償路徑的電流，在變動低頻增益最小的狀況下達到加成的目的。整體電路如圖 5.5 所示。

圖 5.5 可變源極退化級與加成電路

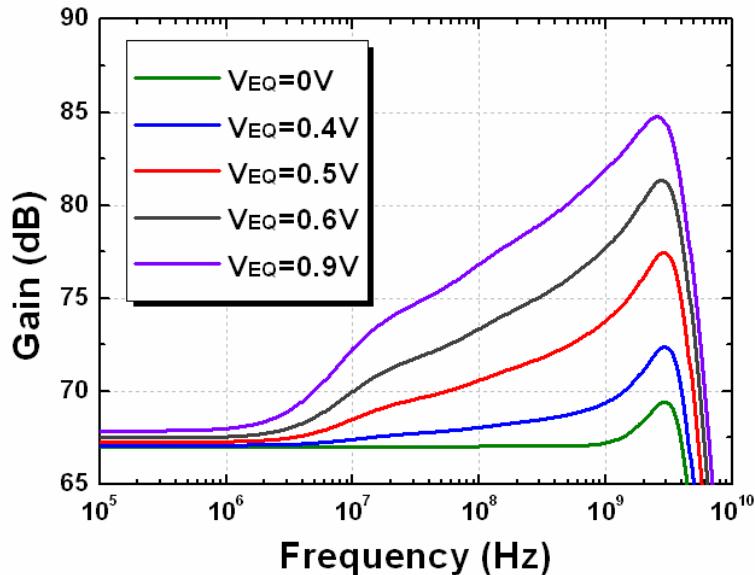

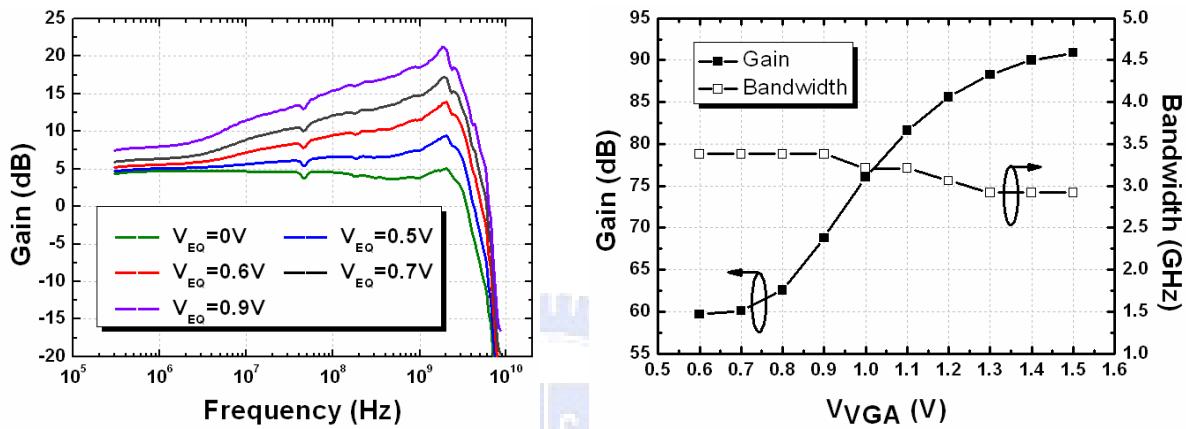

圖 5.6 為加成等化級的頻率響應模擬，入射光波長為 850nm。直流增益的變動在 1dB 以內，等化器如預期地補償了不同程度的低頻緩慢下降，而高頻增益最多可補償 17dB。

圖 5.6 加成等化級頻率響應模擬

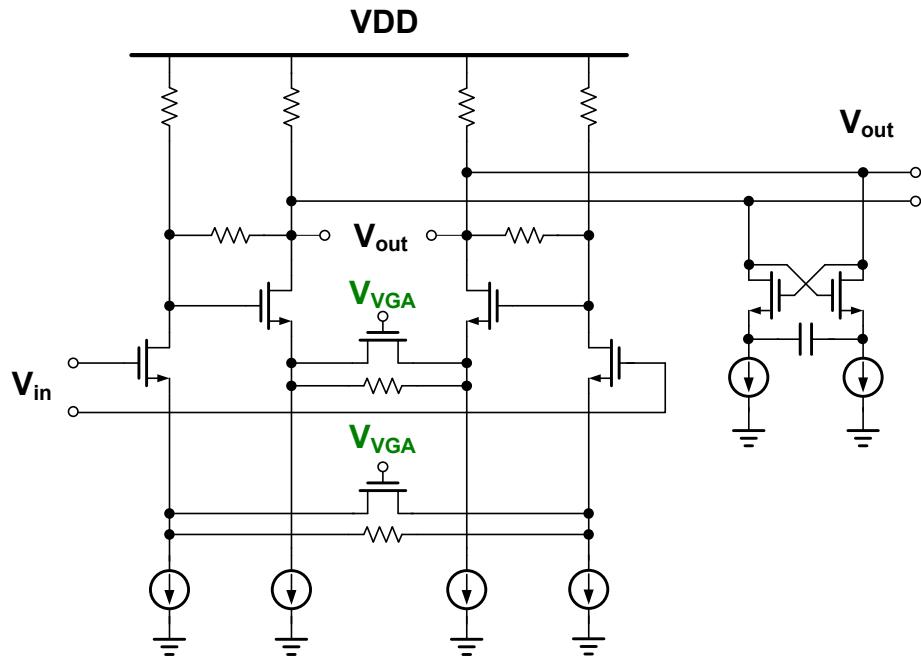

### 5.3.3 可變增益放大器

實現可變增益放大器有幾種方法，如變化偏壓電流[26]、變化負載電阻等[27]。然而，由於本電路設計目標為適用於可適性光接收器，我們希望在增益變化時高頻信號的部分不要變化以避免干擾等化迴路的判斷，故使用源極迴授（source feedback）的放大器增加電路線性度，藉由改變源極電阻以達到增益變化的目的。此種增益變化機制不影響信號路徑上的RC時間常數，故能保持頻寬，且因其優良的線性度，可使增益迴路在鎖定時不會影響等化迴路。

我們以 Cherry-Hooper 的架構實現高速放大器，此架構以一個轉導放大器和一個轉阻放大器所組成，藉由轉阻放大器降低阻抗以拉遠內部極點。因為米勒負電容的值隨放大器增益而改變，但在此架構增益變化時其輸出極點並不會改變，故以主動式負電容補償輸出極點，避免增益變動時的高頻響應變異。各級間免除源極隨耦器的雜散效應隔離，故適用於低供應電壓。此外，在  $g_m$  很大的前提下，電路增益約為回授電阻  $R_f$  和源極電阻  $R_s$  的比例，故對製程和溫度的飄移有較大的免疫力。

最後完成的電路以差動形式呈現，如圖 5.7 所示。

圖 5.7 可變增益放大器

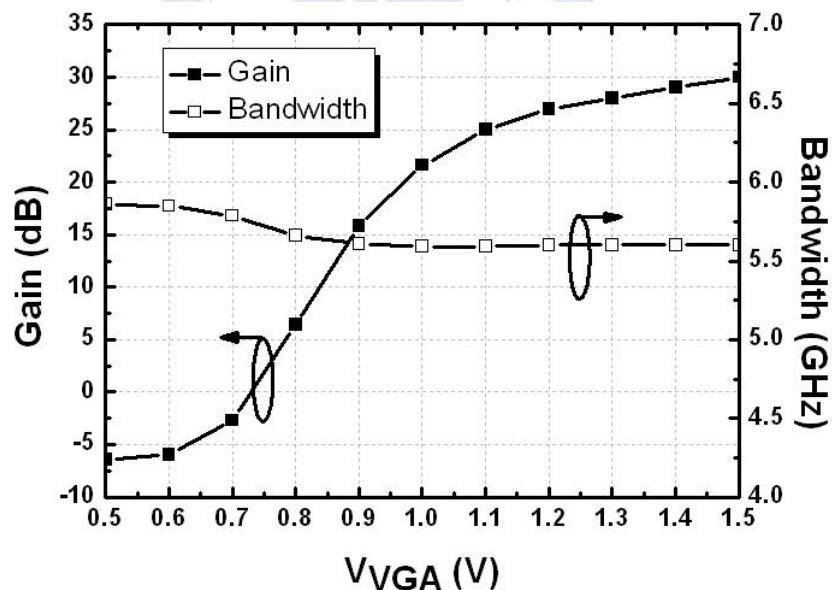

圖 5.8 為可變增益放大器的頻寬與增益關係圖。我們實現三級可變增益放大器，可調增益範圍為-7~+30dB，頻寬變異只有 260MHz。

圖 5.8 可變增益放大器之頻寬與增益關係圖模擬

## 5.4 模擬結果與佈局考量

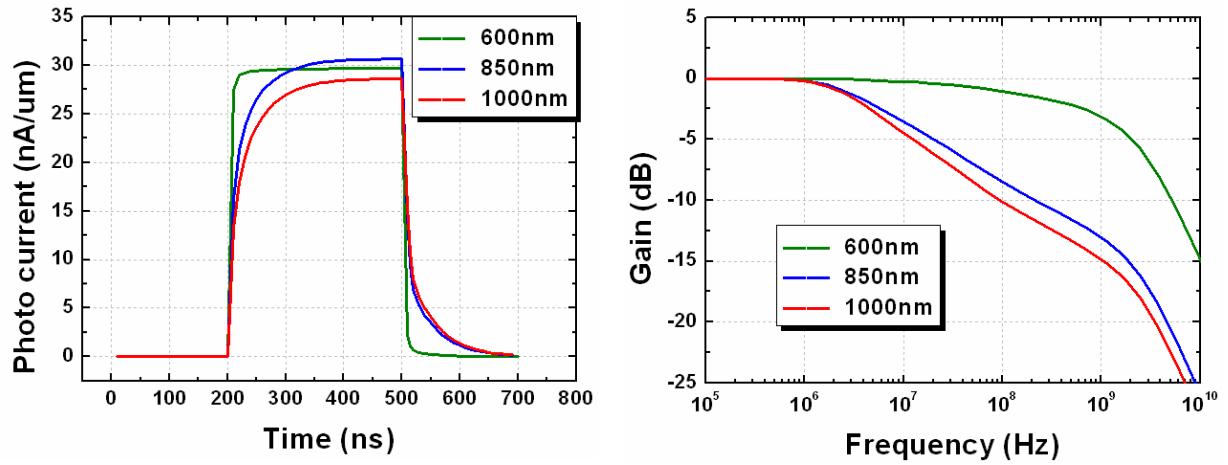

圖 5.9 為檢光二極體在不同波長入射光時的 Medici 模擬結果，其不同光波長所造成

的低頻增益衰減趨勢符合之前所預期。圖 5.10 為不同波長入射光下的 ADS 模型化結果。

圖 5.9 不同波長入射光下的 Medici 模擬結果

圖 5.10 不同波長入射光下的 ADS 模型化結果

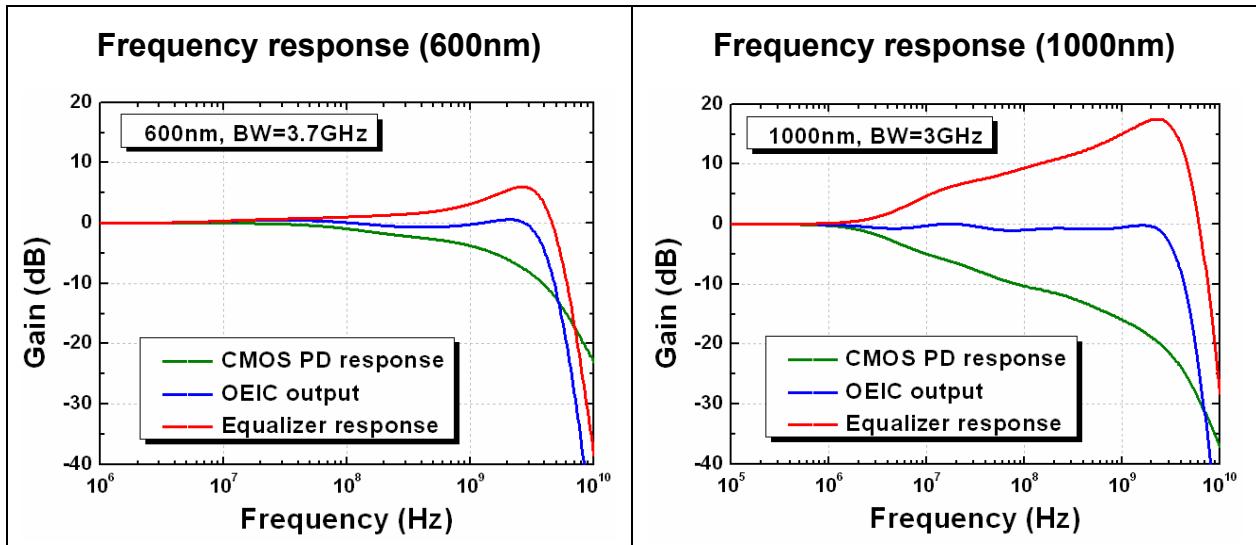

圖 5.11 為整個光接收器的頻率響應。在 600nm 波長的光入射下，等化器補償了

6dB，整體頻寬為 3.7GHz；在 1000nm 波長的光入射下，等化器補償了 17dB，整體頻

寬為 3GHz。增益相當平坦，因而可以有較小的抖動。

圖 5.11 光接收器不同波長入射光下的頻率響應模擬

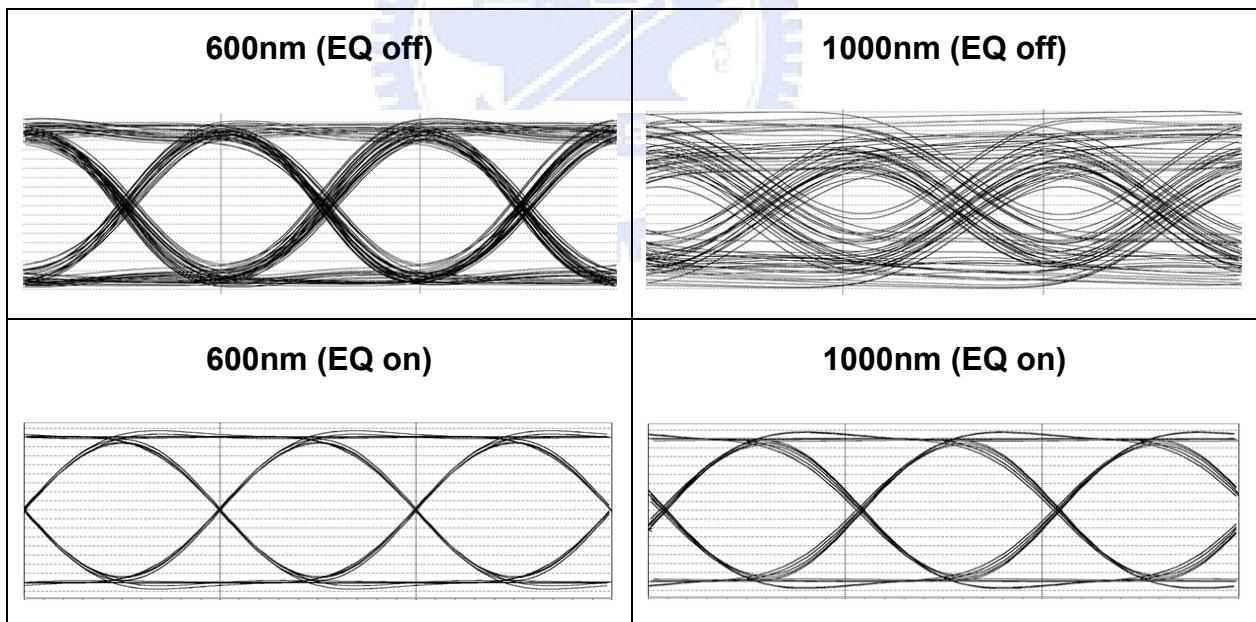

圖 5.12 為光接收器的暫態響應，可以看出在等化器關閉時，不同波長造成的符號間干擾程度不同，但在經過等化器補償及可變增益放大器調整後皆得到高誤碼率的信號。

圖 5.12 等化器開關時的暫態響應

在佈局的部分，光二極體採用八角形取代傳統的正方形，如圖 5.13 所示。經 Medici 驗證其頻率響應仍符合預期，但此舉會大幅降低雜散的電容效應，進而增加後端電路設計的彈性。這樣的改良約可減少 22% 的雜散電容。

圖 5.13 八角形檢光二極體佈局圖

在佈局考量的部分，電路裡所有差動的部分皆為對稱，信號走線選擇較高層的金屬以減少基版雜訊的耦合，且盡量縮短信號走線的長度。多餘的檢光二極體和接收光的檢光二極體佈局相同，但在最上層鋪設金屬以隔絕光的進入。各個電路皆圍上一保護環 (guard ring)，以阻絕基版雜訊的耦合。晶片內部的 VDD 和 gnd 各圍成一電源環 (power ring) 使電源更均勻，並在晶片兩側各放置一組電源，除了減低鎊線的效應外，也可以使電源更穩定。電源及所有直流控制電壓都有對地的去耦 (decoupling) 電容，除了穩壓的功能外，也可濾去高頻雜訊。晶片周圍圍了一圈密封環 (seal ring)，其用處是避免在晶圓 (wafer) 切割時產生的應力損害晶片。晶片佈局如圖 5.14 所示，面積為  $650\mu\text{m} \times 790\mu\text{m}$ 。

圖 5.14 光接收器佈局圖

|                            | <b>Design Target</b>           | <b>Simulation Result</b>        |

|----------------------------|--------------------------------|---------------------------------|

| <b>Technology</b>          | 0.13μm CMOS                    | 0.13μm CMOS                     |

| <b>Optical Wavelength</b>  | 600nm~1000nm                   | 600nm~1000nm                    |

| <b>Bandwidth</b>           | 3.5GHz                         | 600nm : 3.7GHz<br>1000nm : 3GHz |

| <b>Data rate</b>           | 5Gb/s                          | 5Gb/s                           |

| <b>Transimpedance Gain</b> | 66dBΩ ~ 86dBΩ                  | 61dBΩ ~ 97dBΩ                   |

| <b>DC Responsivity</b>     | 0.5A/W                         | 0.55A/W                         |

| <b>Sensitivity (850nm)</b> | -10dBm @ BER=10 <sup>-12</sup> | -9.8dBm @ BER=10 <sup>-12</sup> |

| <b>Chip Size</b>           | NA                             | 650μm×790μm                     |

| <b>Power Dissipation</b>   | NA                             | 117mW                           |

表 5.1 預計規格列表

## 5.5 量測結果

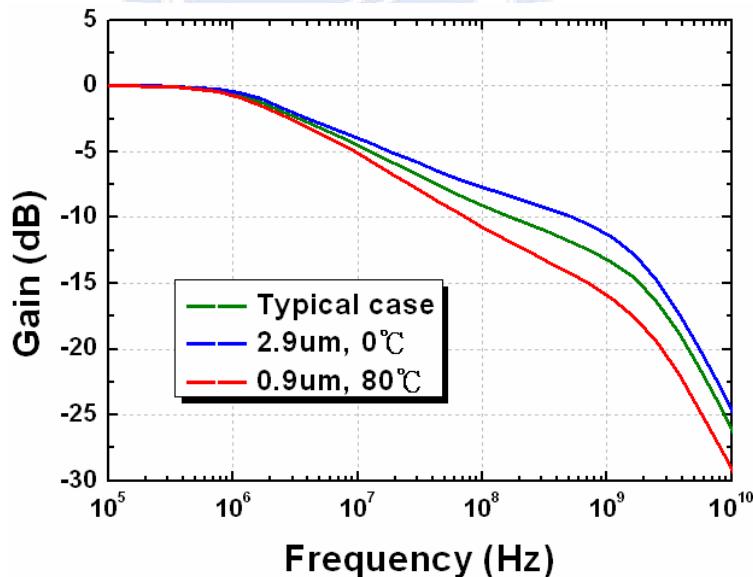

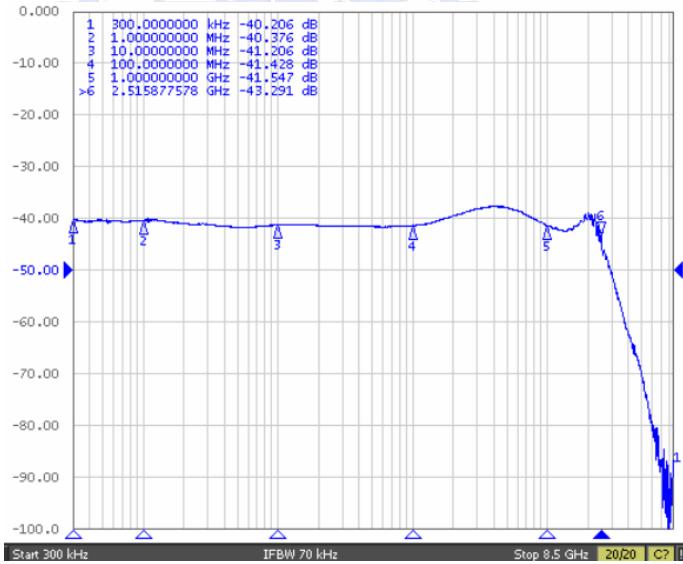

圖 5.15 為加成等化級和可變增益級變化時的頻率響應圖，在此直接輸入電訊號觀察純電路響應。加成等化級可在 MHz~GHz 的範圍內變動 14dB 以補償不同程度緩慢增益下降的響應，可變增益級則提供了 31dB 的增益變化範圍，且其頻寬隨增益的變化相當小，符合之前提過的可適性需求。

圖 5.15 頻率響應圖量測 (a) 等化器變動 (b) 可變增益放大器變動

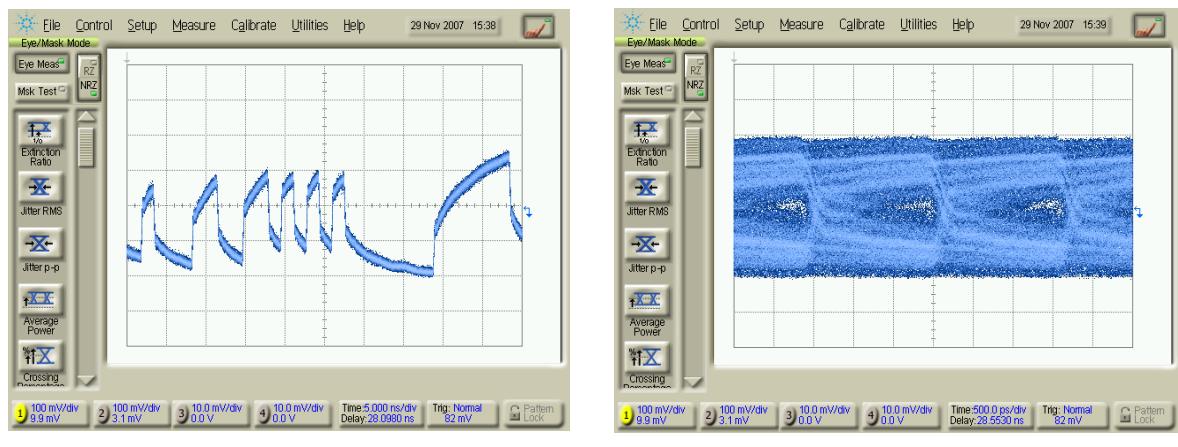

因為實驗室所購買的 650nm 和 980nm 波長雷射無法達到高速調變的應用，故在這裡的量測皆使用 CSI 高速 850nm 光發射器。圖 5.16 為等化器關閉時的暫態響應與眼圖，其符號間干擾相當嚴重。

圖 5.16 等化器關閉時的暫態響應與眼圖量測

圖 5.17 為等化器打開後不同速度下的眼圖量測，可發現符號間干擾已被等化器消除，故有較好品質的信號。

圖 5.17 不同速度下的眼圖量測

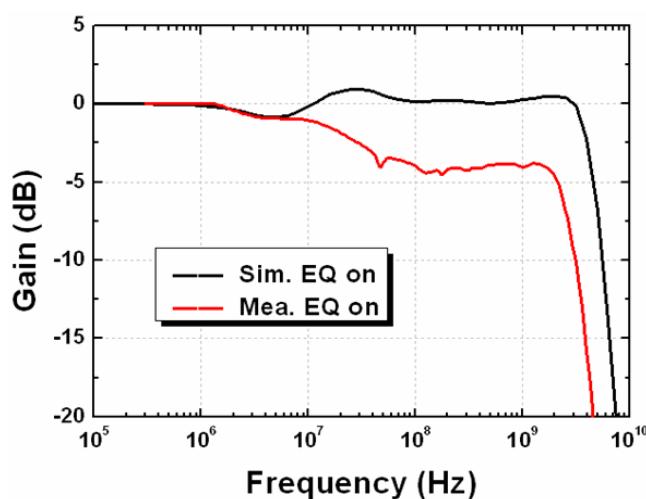

圖 5.18 為等化器在 850nm 波長的光照射下的頻率響應量測。從 100MHz 開始，高頻約有 4dB 沒被等化器補償，而後維持一平穩增益大小，在 2.6GHz 時掉至-7dB。這主要是因為在 Medici 模擬時沒有考慮到光纖聚光點的問題，以致有多餘的光照射到檢光二極體旁的基版，造成 2dB 的差異。此外，等化器的高頻補償不如模擬預期，約少了 2dB 的補償量。在注入高速的信號時，由於高頻的增益大小直接影響到信號的振幅，故這 4dB 將直接衰減靈敏度。

圖 5.18 頻率響應量測

圖 5.19 為雜訊功率頻譜量測和雜訊推估。我們將光關掉，僅量測電路本身的雜訊

功率，將之積分至資料速度 (5GHz)，利用增益、響應率、亮暗比等參數推出靈敏度為 -4.7dBm。

圖 5.19 雜訊功率頻譜量測和雜訊推估

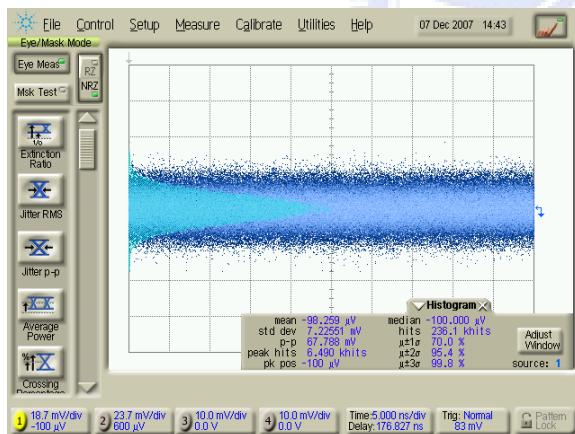

圖 5.20 為直方圖量測和雜訊推估，我們將光關掉，僅量測電路本身的雜訊分佈，以標準差和其他參數推出靈敏度為-5.07dBm。

$$\begin{aligned} I_N &= \frac{7.23}{3.16} \times 10^{-6} = 2.28 \times 10^{-6} \\ \text{Sensitivity} &= 10 \times \log \left[ \frac{14.1 \times I_N}{R \times \rho} \times 1000 \right] \\ &= 10 \times \log \left[ \frac{14.1 \times 2.28 \times 10^{-6}}{0.25 \times 1.04} \times 1000 \right] \\ &= -9.07 \text{dBm} \xrightarrow{\text{incomplete compensation}} -5.07 \text{dBm} \end{aligned}$$

圖 5.20 直方圖量測和雜訊推估

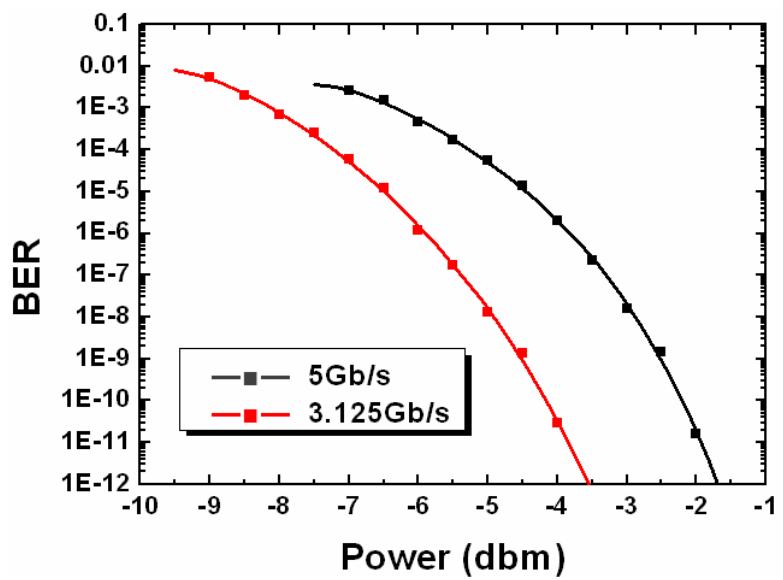

圖 5.21 為光接收器誤碼率量測，在 5Gb/s 時其靈敏度為-1.7dBm。由於此時仍有許多符號間干擾，故打入較慢速的信號，以觀察單純因雜訊所造成的誤碼率。在 3.125Gb/s 輸入信號時，其靈敏度為-3.6dBm。

圖 5.21 光接收器誤碼率量測

圖 5.22 為光接收器晶片照相圖，表 5.2 為量測結果列表與比較。

圖 5.22 光接收器晶片照相圖

|                             | <b>B. Nauta<br/>2005 JSCC</b>     | <b>M. Steyaert<br/>2006 JSSC</b>   | <b>This work</b>                   |

|-----------------------------|-----------------------------------|------------------------------------|------------------------------------|

| <b>Technology</b>           | 0.18μm CMOS                       | 0.18μm CMOS                        | 0.13μm CMOS                        |

| <b>Optical Wavelength</b>   | 850nm                             | 850nm                              | 850nm                              |

| <b>Photodiode Area</b>      | 50μm×50μm                         | 80μm×80μm                          | 50μm×50μm                          |

| <b>Bandwidth / roll off</b> | 1.5GHz                            | N/A                                | -4dB @ 200MHz<br>-7dB @ 2.6GHz     |

| <b>Data rate</b>            | 3Gb/s                             | 500Mb/s                            | 5Gb/s                              |

| <b>DC Responsivity</b>      | N/A                               | N/A                                | 0.25A/W                            |

| <b>Sensitivity</b>          | -19dBm<br>@ BER=10 <sup>-11</sup> | -8dBm<br>@ BER=3×10 <sup>-10</sup> | -1.7dBm<br>@ BER=10 <sup>-12</sup> |

| <b>Chip Size</b>            | 700μm×400μm                       | 1000μm×570μm                       | 650μm×790μm                        |

| <b>Measurement Method</b>   | On Wafer                          | On Board                           | On Board                           |

| <b>Power Dissipation</b>    | 50mW                              | 17mW                               | 112mW                              |

表 5.2 量測結果列表與比較

## 第六章 結論與未來展望

在這次的研究中，我們從製程文件的資料推估相關製程參數，利用元件模擬軟體設計出適用於標準 CMOS 製程的檢光二極體，並將之建模於電路階層，利用電路模擬軟體設計出完整的單晶整合光接收器。量測提供了從檢光二級體到電路的模擬驗證，和日後設計的改良方向。

第一顆晶片使用  $0.18\mu\text{m}$  金氧半製程實現一個  $3.125\text{Gb/s}$  的單晶整合光接收器，在  $850\text{nm}$  光波長下量測出  $69 \text{ dB}\Omega$  的差動轉阻增益、 $-8.1\text{dBm}$  的靈敏度與  $2.5\text{GHz}$  的頻寬，在  $1.8\text{V}$  供應電壓下消耗  $36\text{mW}$  的功率。第二顆晶片以  $0.13\mu\text{m}$  金氧半製程實現一個  $5\text{Gb/s}$  的單晶整合光接收器，在  $850\text{nm}$  光波長下量測出  $60\text{-}91 \text{ dB}\Omega$  的差動轉阻增益與  $-1.7\text{dBm}$  的靈敏度，在  $1.5\text{V}$  供應電壓下消耗  $112\text{mW}$  的功率。

在檢光二級體的部分，由於多模光纖聚光的問題，我們未來傾向用較大的面積以收集較多的光，或使用聚焦光纖以增進量測的響應率。此外，我們將把檢光二級體上高介電係數的護層撥除，以減少非理想的反射折射效應。檢光二級體的結構也可由原先連續的多指 N 型井改為方塊狀排列，增加空乏區面積以減緩高頻的增益下降，使信雜比更為提升。

在電路的部分，我們將在等化器前至入適當的增益級，在信號未失真、等化器仍能完成補償的前提下，降低後端電路雜訊對輸入端的影響。此外，並分析可適性等化器的閉迴路與穩定度分析，將之與單晶整合光接收器結合，實現一可接收寬頻波長的高速光接收器。

---

## 參考文獻

- [1] E. Säckinger, *Broadband Circuits for Optical Fiber Communication*, John Wiley & Sons, 2005

- [2] M. Fukuda, *Optical Semiconductor Devices*, John Wiley & Sons, 1998

- [3] C. Hermans, P. Leroux, and M. Steyaert, "Gigabit Photodiodes in Standard Digital nanometer CMOS Technologies," Proc. Eur. Solid-State Device Research Conf., pp. 51–54, 2003.

- [4] S. Radovanović, A. J. Annema, and B. Nauta, "Physical and electrical bandwidths of integrated photodiodes in standard CMOS technology," Proc. Eur. Solid-State Device Research Conf., pp. 95–98, 2003.

- [5] J. Genoe, D. Coppee, J. H. Stiens, R. A. Vounckx, and M. Kuijk, "Calculation of the current response of the spatially modulated light CMOS detectors," IEEE Trans. Electron Devices, vol. 48, no. 9, pp. 1892–1902, 2001.

- [6] S. Radovanović, A. J. Annema and B. Nauta, "A 3-Gb/s Optical Detector in Standard CMOS for 850-nm Optical Communication," IEEE J. Solid-State Circuits, vol. 40, pp. 1706-1717, 2005.

- [7] C. Hermans and M. Steyaert, "A high-speed 850-nm optical receiver front-end in 0.18 $\mu$ m CMOS," IEEE J. Solid-State Circuits, vol. 41, pp. 1606-1614, 2006.

- [8] S. Radovanović, A. J. Annema, and B. Nauta, "3 Gb/s monolithically integrated photodiode and pre-amplifier in standard 0.18  $\mu$ m," in IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp. 472–472, 2004.

- [9] M. Ghioni, F. Zappa, V. P. Kesan, and J. Warnock, "A VLSI-compatible high speed silicon photodetector for optical datalink applications," IEEE Trans. Electron Devices, vol. 43, no. 7, pp. 1054-1060, Jul. 1996.

- [10] R. Swoboda, J. Knorr, and H. Zimmermann, "A 5-Gb/s OEIC with voltage-up-converter," IEEE J. Solid-State Circuits, vol. 40, no. 7, pp. 1521–1526, Jul. 2005.

- [11] S. M. Csutak, J. D. Schaub, W. E. Wu, R. Shimer, and J. C. Campbell, "High-speed monolithically integrated silicon photoreceivers fabricated in 130-nm

-

- CMOS technology," J. Lightwave Technol., vol. 20, no. 9, pp. 1724-1729, Sep. 2002.

- [12] A. Maxim, "A 3 V 10 Gb/s SiGe limiting transimpedance amplifier using a pseudo-differential transimpedance stage and a cross-coupled Cherry-Hooper limiting stage," in IEEE Symp. Radio Frequency Integrated Circuits Dig. Tech. Papers, pp. 313–316, 2005.

- [13] S. M. Park and H.-J. Yoo, "1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications," IEEE J. Solid- State Circuits, vol. 39, pp. -112–121, Jan. 2004.

- [14] C. M. Tsai and L. R. Huang, "A 21mW 2.5Gb/s 15k Self-Compensated Differential Transimpedance Amplifier," IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp. 234-235, Feb. 2005.

- [15] B. Razavi, *Design of integrated circuits for optical communications*, McGraw Hill, 2003.

- [16] C. M. Tsai and L. R. Huang, "A 24mW 1.25Gb/s 13k Transimpedance Amplifier Using Active Compensation," IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp. 894-903, Feb. 2006

- [17] C. H. Lu and W. Z. Chen, "Bandwidth enhancement techniques for transimpedance amplifier in CMOS technologies," Proc. Eur. Solid-State Circuits Conf., pp. 174-177, Sep. 2001.

- [18] C. D. Holdenried, M. W. Lynch, and J. W. Haslett, "Modified CMOS Cherry-Hooper amplifiers with source follower feedback in 0.35  $\mu\text{m}$  technology," Proc. Eur. Solid-State Circuits Conf., pp. 553-556, Sep. 2003.

- [19] C. D. Holdecried, J. W. Haslett and M. W. Lynch, "Analysis and design of HBT Cherry-Hooper amplifiers with emitter-follower feedback for optical communications," IEEE J. Solid-State Circuits, vol. 39, pp. 1959-1967, 2004.

- [20] J. LEE, "A 20-Gb/s adaptive equalizer in 0.13- $\mu\text{m}$  CMOS technology," IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp. 273–282, Feb. 2006

- [21] J. N. Babanezhad, "A 3.3-V analog adaptive line-equalizer for fast Ethernet data connection," in Proc. IEEE Custom Integrated Circuit Conf., pp. 343–346, May 1998.

- [22] S. Gondi, J. Lee, D. Takeuchi and B. Razavi, "A 10Gb/s CMOS adaptive equalizer

-

-

- for backplane applications," IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp. 328–329, Feb. 2005.

- [23] J. S. Choi, M. S. Hwang and D. K. Jeong, "A  $0.18\mu\text{m}$  CMOS 3.5-gb/s continuous-time adaptive cable equalizer using enhanced low-frequency gain control method," IEEE J. Solid-State Circuits, vol. 39, pp. 419-425, 2004.

- [24] E. Säckinger and W.C. Fischer, "A 3-GHz 32-dB CMOS limiting amplifier for SONET OC-48 receivers," IEEE J. Solid-State Circuits, vol. 35, pp. 1884-1888, 2000.

- [25] B. Razavi, *Design of Analog CMOS Integrated Circuits*, McGraw Hill, 2000.

- [26] C. F. Liao and S. I. Liu, "A 10Gb/s CMOS AGC Amplifier with 35dB Dynamic Range for 10Gb Ethernet," IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, pp. 2092–2101, Feb. 2006.

- [27] S. Yamashita, S. Ide, K. Mori, N. Ueno, and K. Tanaka, "Novel cell AGC technique for burst-mode CMOS preamplifier with wide dynamic range and high sensitivity for ATM-PON system," IEEE J. Solid-State Circuits, vol. 37, no. 7, pp. 881-886, Jul. 2002.

## 附錄

### 第四章 一個 3.125Gb/s 的單晶整合光接收器設計

## 第五章 一個 5Gb/s 的寬頻單晶整合光接收器設計

---

## 簡歷

姓名：邱珣益

出生地：台灣台北市

學歷：

1995.09 ~ 1998.06 台北縣中和國中

1998.09 ~ 2001.06 台北縣立永平中學

2001.09 ~ 2005.06 國立中央大學 電機工程學系

2005.09 ~ 2008.01 國立交通大學 電子研究所