## 國立交通大學

電信工程學系

碩士論文

具多齊質性處理器核心之多媒體串流處理架構

Media Streaming Architecture with Homogeneous Processor Cores

研究生:劉嘉儀

指導教授:關河鳴博士

中華民國九十六年七月

## 具多齊質性處理器核心之 多媒體串流處理架構

## Media Streaming Architecture with Homogeneous Processor Cores

研究生:劉嘉儀 Student: Chia-Yi Liou

指導教授:闕河鳴 博士 Advisor:Dr. Herming Chiueh

#### A Thesis

Submitted to Department of Communication Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

for the Degree of Master of Science

in

Communication Engineering

July 2007

Hsinchu, Taiwan.

中華民國九十六年七月

## 具多齊質性處理器核心之 多媒體串流處理架構

研究生:劉嘉儀 指導教授:闕河鳴 博士

國立交通大學 電信工程學系碩士班

#### 摘要

ES

隨著科技的發展與進步,在現今的生活中應用於多媒體運算之可攜式嵌入式 系統的重要性與日俱增。然而由於傳統運算模型中之記憶體存取模型與處理核心 和記憶體間的效能間隙落差,導致多媒體運算無法有效率的對應並且實現在傳統 的處理器架構模型上。另外在硬體實現的系統架構上亦是產生效能無法提升的重 要因素之一。因此所提出的多媒體處理架構採用史丹佛大學提出之串流處理模型 配合上多種硬體實現的系統架構來克服傳統處理器架構所造成效率低落。並且提 供一具高平行度和有效率運算速率的多媒體運算平台。

在本論文中,設計並下線製作一個與 AMBA 介面相容之多媒體處理單元作為構成具多齊質性處理核心之多媒體串流處理架構的核心運算單元。除此之外亦設計實做浮點運算處理器,利用此浮點運算處理器提供此一與 AMBA 介面相容之多媒體處理單元有效率的浮點運算處理能力,使其可以更廣泛的應用於各種多媒體處理運算中。透過不同運算單元與架構間的效能評估與比較,證實了僅需要

些許的硬體成本即可提供更有效率且更廣泛的多媒體運算處理能力。另外此效能 評估與比較亦證實了具多齊質性處理核心之多媒體串流處理架構在擁有不同數 目之處理核心時,在合理的硬體成本之下其效能可以有效的提升。

#### Media Streaming Architecture with

#### Homogeneous Processor Cores

Student: Chia-Yi Liou Advisor: Dr. Herming Chiueh

Department of Communication Engineering

National Chiao Tung University

Hsinchu, Taiwan

#### **Abstract**

As the evolution of information technology, embedded systems with media applications for portable devices are more and more important in modern life. However, the conventional processor architecture does not handle the processing requirement of media applications very well since the characteristics of media applications and other inheritance disability from conventional microprocessor architecture's memory accessing model and processor-memory performance gap.

Recent research shows that the stream processing model and stream processor architecture are suitable for media applications. However, software implementations for a streaming processor are not a trivial job since it evolves a lot of hand and manual optimization in memory exchange and tread deployment to different processor element or functional unit.

In this thesis, a processing element for reconfigurable homogenous ALU cluster and its Advanced Microcontroller Bus Architecture (AMBA) platform interface has been designed and implemented. The proposed design integrated platform based design methodology and stream processing model to overcome the challenge of media applications. The proposed homogenous ALU cluster is utilized as a reconfigurable hardware accelerator for specific and different functions in media applications. The chosen AMBA interface provides an integration platform for embedded operating system and programming development environment. The combination of these methodologies provides a turnkey solution for media applications development in modern portable devices.

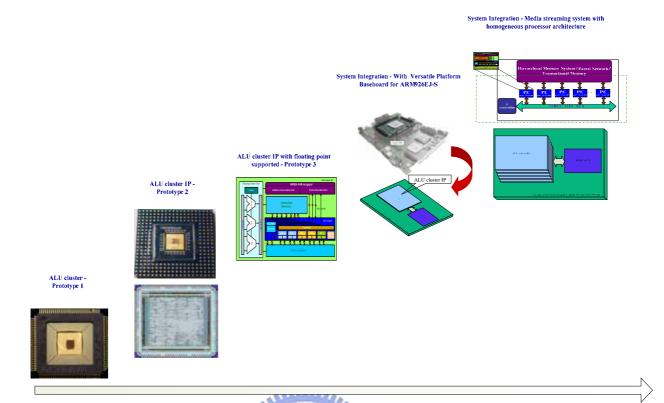

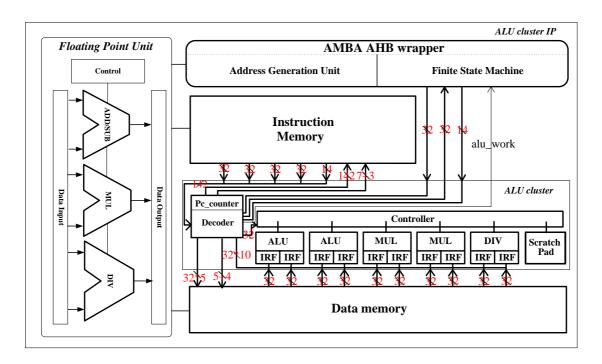

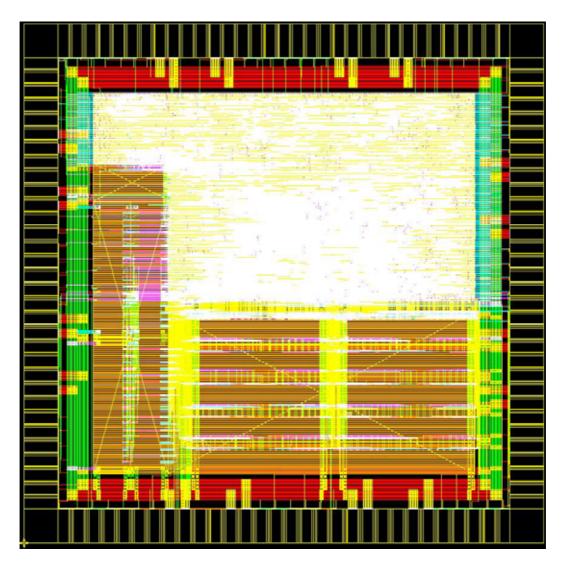

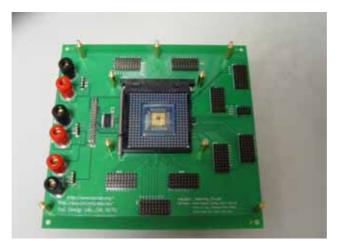

The ALU cluster IP with AMBA interface is taped out using TSMC 0.15um technology and operates at 100MHz. The chip area is 3.9\*3.9 mm² and gate count is 0.2 million. A 4-layer FRP printed circuit board is designed and fabricated as the daughter card for system integration. The daughter card carries the designed chip is integrated to ARM versatile platform board as the system integration and application development environment. In addition, a floating point operation unit for ALU cluster IP is proposed and implemented and it will be integrated with ALU cluster IP as the future revision of the hardware accelerator. The hard macro of the floating point unit operates at 75MHz, its area and gate count is 0.415mm² and 0.02 million respectively. The performance evaluation and comparison in floating point operation benchmark between different proposed architectures are presented. Media applications can be developed for proposed reconfigurable homogenous processing elements in the future using the chips and systems build in this thesis.

## Acknowledgement

本篇碩士論文得以順利完成,首先要感謝我的指導教授 闕河鳴博士。老師擁有淵博的學識,總能讓學生在研究遇到瓶頸的時候給予實貴的指導及建議,使我能夠突破與進步。更由於老師在平日培養學生獨立思考與分析、解決問題的能力,使我對於研究的領域建立正確的態度及觀念。

再者要感謝晶片系統設計實驗室的學長姐、同學以及學弟妹們, 在我的研究上及生活上给與諸多的指教及幫助。因為你們的支持,才 讓我得以擁有一段快樂充實的碩士班研究生活,謝謝大家。

THE PERSON NAMED IN

最後,我要感謝父母的栽培與養育之恩、所有關心我的家人與朋 友、以及我生長的這塊土地、社會與國家。

誠心感謝並祝福所有提攜幫助我和支持鼓勵我的大家,謝謝各位並祝福各位。

劉嘉儀

## **CONTENTS**

#### 中文摘要

| Engl | ish Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Ackı | nowledgment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| Cont | tent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| List | of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| List | of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | The state of the s |    |

| Cha  | pter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1  |

| 1.1  | Motivation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1  |

| 1.2  | Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3  |

| Cha  | pter 2 Background and Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4  |

| 2.1  | Issues of Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4  |

|      | Issues of System Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| Cha  | pter 3 Development Roadmap and Proposed Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 |

| 3.1  | Developmental Roadmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11 |

| 3.   | 1.1 Motivation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 |

| 3.   | <b>1.2</b> Roadmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

|      | <b>3.1.2.1</b> Stream Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11 |

|      | 3.1.2.2 Developmental Roadmap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14 |

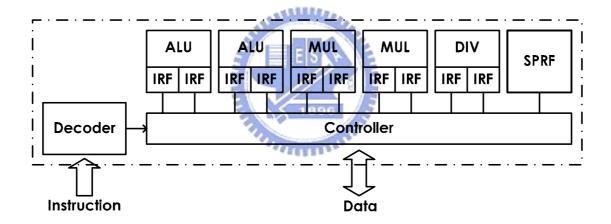

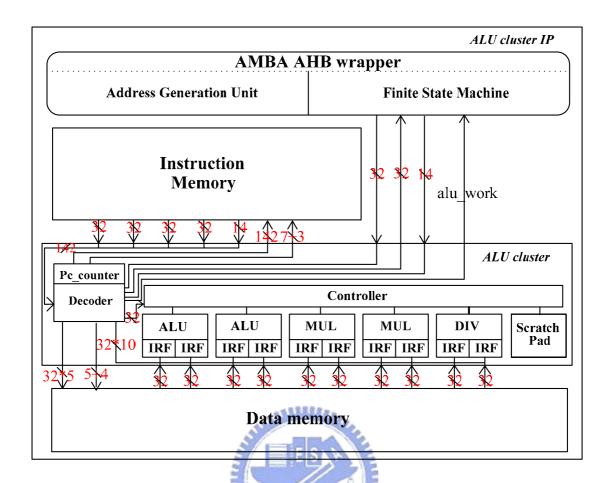

| 3.2  | An ALU cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17 |

| 3.   | 2.1 Micro-Architecture of an ALU cluster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17 |

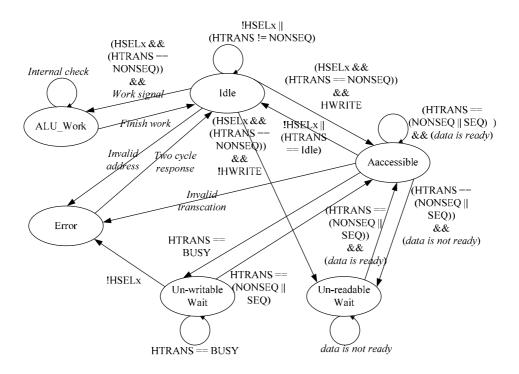

| 3.3  | An ALU cluster Intellectual Property                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

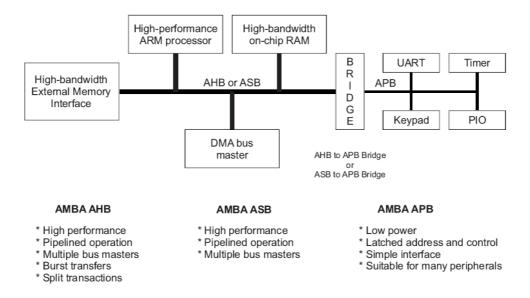

| 3.   | <b>3.1</b> Overview of AMBA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

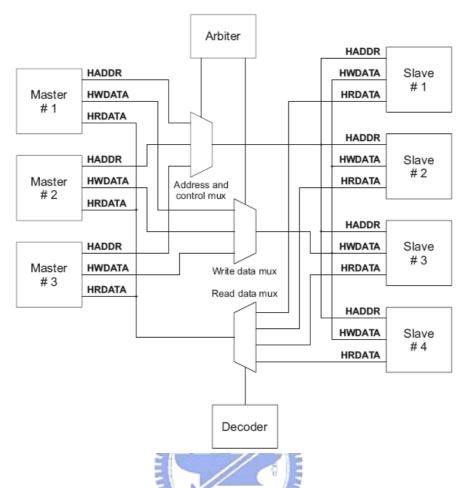

| <b>3.3.1.1</b> Introduction of AMBA AHB                                           | <b>20</b> |

|-----------------------------------------------------------------------------------|-----------|

| <b>3.3.1.2</b> Bus Interconnection                                                | 21        |

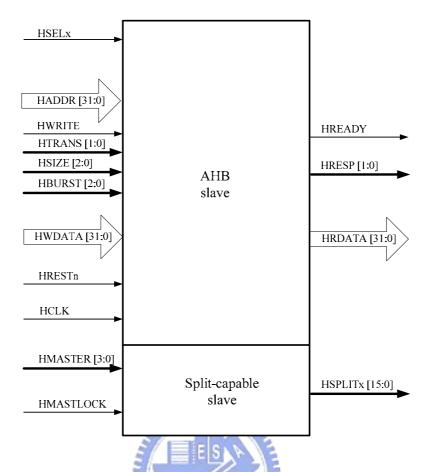

| <b>3.3.1.3</b> Signals for the protocol of AMBA AHB slave                         | 22        |

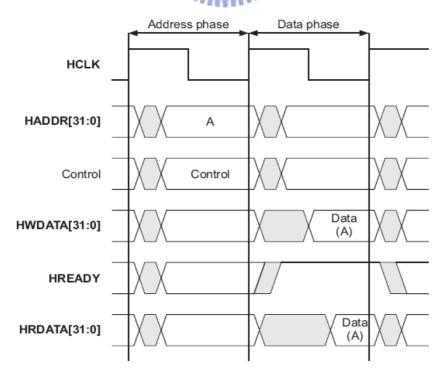

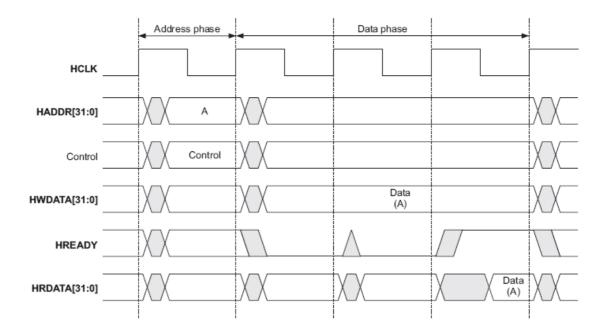

| 3.3.1.4 Basic Transfer                                                            | 24        |

| <b>3.3.1.5</b> Transfer Type                                                      | 25        |

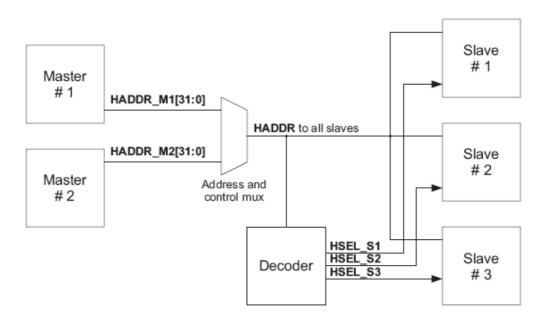

| <b>3.3.1.6</b> Address Decoding                                                   | 26        |

| <b>3.3.1.7</b> Burst Operation                                                    | 27        |

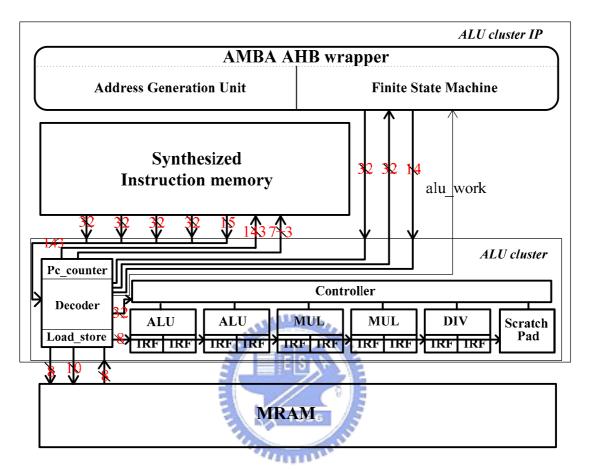

| <b>3.3.2</b> Micro-Architecture of an ALU cluster Intellectual Property           | 28        |

| <b>3.4</b> Floating Point Units for the ALU cluster IP                            | 32        |

| 3.4.1 Design Consideration.                                                       | 33        |

| Chapter 4 Implementation Results and Performance Evaluation                       | 37        |

| Chapter 4 Implementation Results and Performance Evaluation                       | 31        |

| <b>4.1</b> Implementation and Testing Results of An ALU cluster                   | 38        |

| <b>4.2</b> Verification and Implementation Results of An ALU cluster Intellectual |           |

| Property                                                                          | 43        |

| 4.2.1 An ALU cluster IP with Magnetic RAM                                         | 43        |

| 4.2.1.1 Introduction of Magnetic RAM                                              | 44        |

| 4.2.1.2 Modified ALU cluster IP for Magnetic RAM                                  | 44        |

| 4.2.2 Implementation Results                                                      | 45        |

| 4.2.3 Circuit Verification                                                        | 50        |

| <b>4.2.4</b> Chip Testing                                                         | 55        |

| 4.3 Circuit Implementation and Results of Floating Point Units for the            |           |

| ALU cluster IP                                                                    | 57        |

| <b>4.4</b> Performance Evaluation and Comparison                                  | 62        |

| 4.4.1 Selected Benchmark                                                          | 63        |

| <b>4.4.2</b> Evaluation and Comparison Results                                    | 64        |

| Chapter 5 Conclusion and Future Work                                              | 80        |

| <b>5.1</b> Conclusion                                                             | 80        |

| <b>5.2</b> Future Work                                                            | 81        |

| Bibliography                                                                      | 82        |

## **LIST of TABLES**

| Table 2.1                                                                | System Architecture vs. media application              |    |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------|----|--|--|

| Table 3.1                                                                | Comparison between programming models 14               |    |  |  |

| Table 3.2                                                                | Burst Signal Encoding                                  | 27 |  |  |

| Table 3.3                                                                | Active Byte Lanes for a 32 bits big endian data bus    | 28 |  |  |

| Table 3.4                                                                | Active Byte Lanes for a 32 bits little endian data bus |    |  |  |

| Table 3.5         Format of single and double precision IEEE 754 floa    |                                                        |    |  |  |

|                                                                          | point number                                           | 34 |  |  |

| Table 3.6                                                                | -                                                      |    |  |  |

| Table 4.1                                                                | Implementation Results Summary of ALU cluster          | 38 |  |  |

| Table 4.2                                                                | Testing results summaries of ALU cluster 4.            |    |  |  |

| Table 4.3                                                                | Summary of Implementation Characteristics 4            |    |  |  |

| Table 4.4                                                                | The Definitions of I/O the ports                       |    |  |  |

| Table 4.5                                                                | Summary of the Implementation Results 59               |    |  |  |

| Table 4.6                                                                | Performance Evaluation Results for Original Integer    |    |  |  |

|                                                                          | Architecture                                           | 66 |  |  |

| Table 4.7         Performance Evaluation Results for Floating Point Unit |                                                        |    |  |  |

| Original Integer Architecture Mixed                                      |                                                        |    |  |  |

| Table 4.8                                                                | Performance Evaluation Results in Execution Time       |    |  |  |

## LIST OF FIGURES

| Fig 2.1     | Conventional Programming Model                               | 5  |

|-------------|--------------------------------------------------------------|----|

| Fig 2.2     | Processor-Memory Performance Gap                             | 5  |

| Fig 2.3     | Application Specified Integrated Circuit Design              | 6  |

| Fig 2.4     | An Example of Platform-Based Architecture                    | 7  |

| Fig 2.5     | A Diagram of Reconfigurable Architecture                     | 8  |

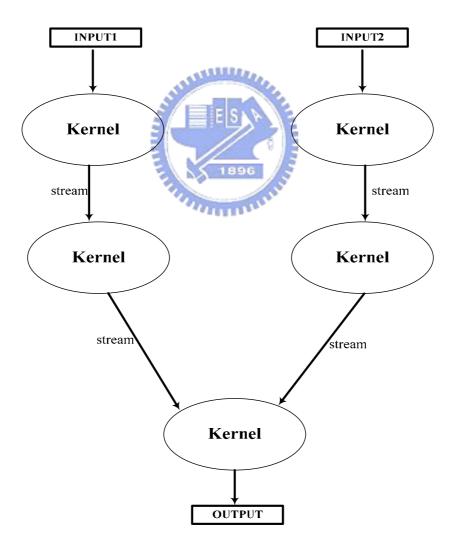

| Fig 3.1     | Stream Programming model                                     | 12 |

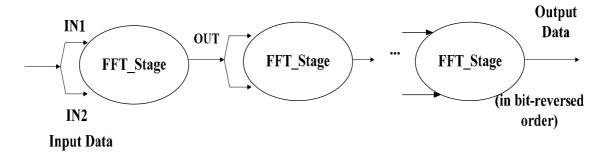

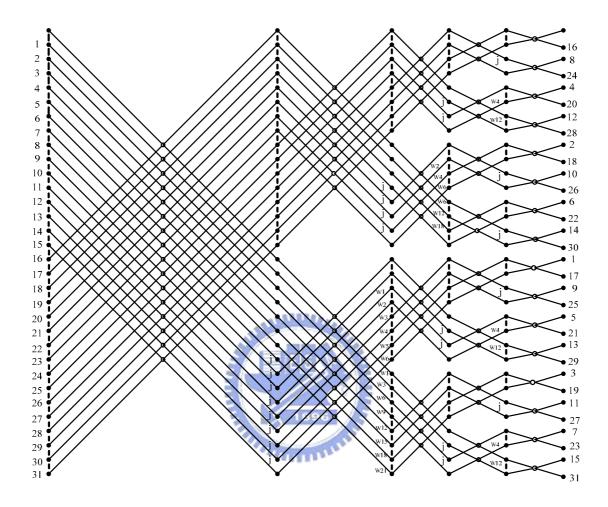

| Fig 3.1     | Example of 1024-points radix-2 Fast Fourier Transform        | 13 |

| C           | -                                                            | 13 |

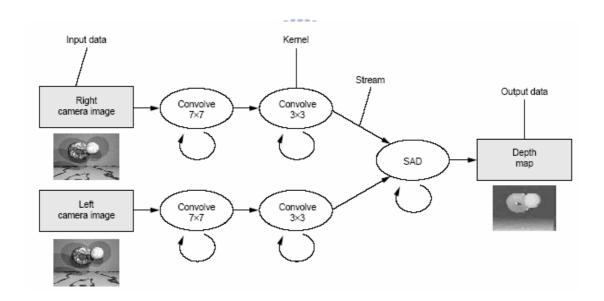

| Fig 3.3     | Example of Stereo Depth Extraction                           |    |

| Fig 3.4     | Development roadmap                                          | 15 |

| Fig 3.5     | Micro-Architecture of ALU cluster                            | 17 |

| Fig 3.6     | Diagram of AMBA-based system                                 | 20 |

| Fig 3.7     | Diagram of AMBA AHB interconnection                          | 22 |

| Fig 3.8     | Diagram of AHB slave interface                               | 23 |

| Fig 3.9     | An example of simple transfer                                | 24 |

| Fig 3.10    | The example of the transfer extended                         | 25 |

| Fig 3.11    | Slave Selected Signal                                        | 26 |

| Fig 3.12    | The Proposed ALU Cluster IP Architecture                     | 29 |

| Fig 3.13    | The state diagram of the finite state machine                | 31 |

| Fig 3.14    | An ALU cluster IP with Floating Point Unit Supported         |    |

|             | Architecture                                                 | 36 |

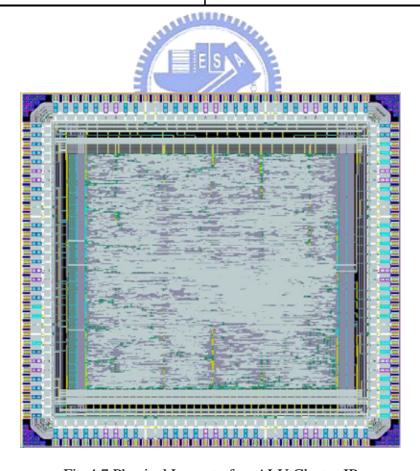

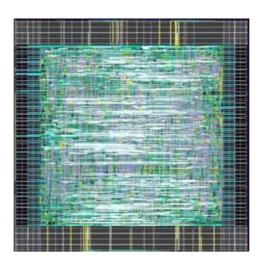

| Fig 4.1     | Physical Layout of an ALU cluster                            | 39 |

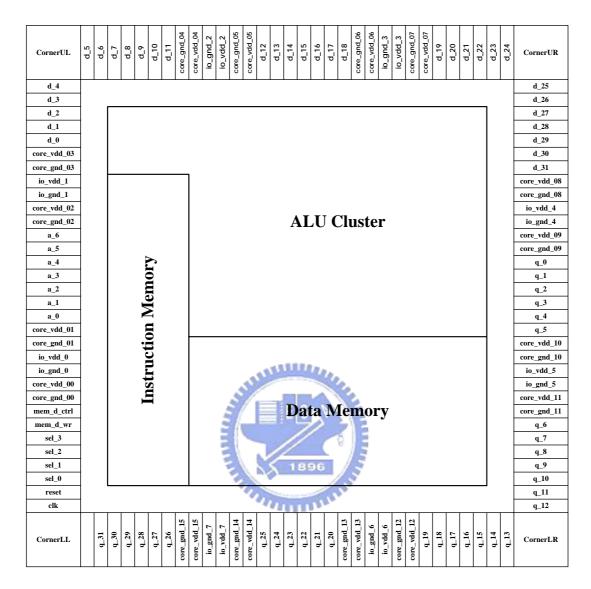

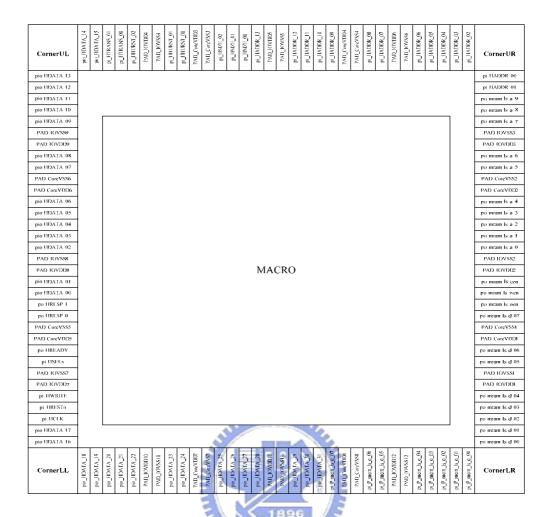

| Fig 4.2     | Floorplan and Pad Assignment of an ALU cluster               | 40 |

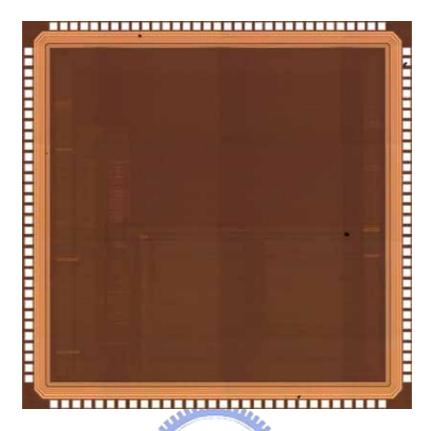

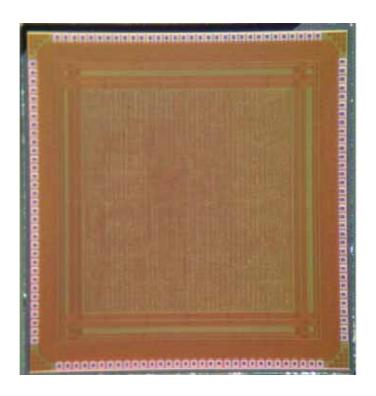

| Fig 4.3     | Microphotograph of taped out ALU cluster                     | 41 |

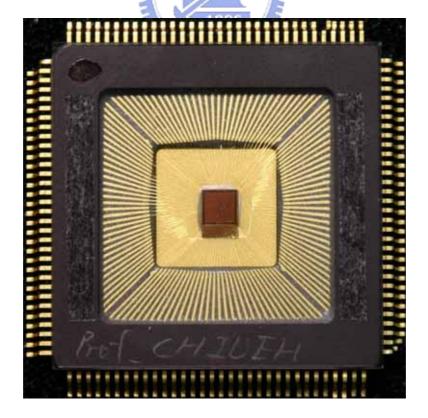

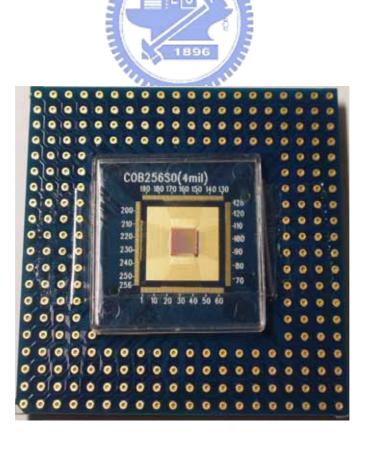

| Fig 4.4     | An ALU cluster with CQFP128 package                          | 41 |

| Fig 4.5     | An ALU cluster with PCB board                                | 42 |

| Fig 4.6     | Modified ALU cluster IP architecture for MRAM                | 45 |

| Fig 4.7     | Physical Layout of an ALU Cluster IP                         | 46 |

| Fig 4.8     | Pads Assignment of an ALU Cluster IP                         | 47 |

| Fig 4.9     | Die Microphotograph of Taped Out Chip                        | 48 |

| Fig 4.10    | Photograph of Prototype with Package                         | 48 |

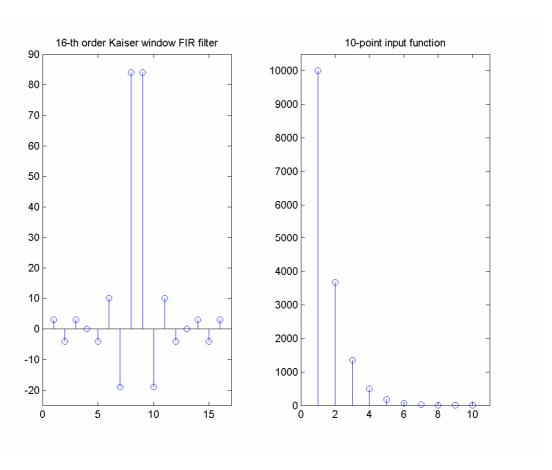

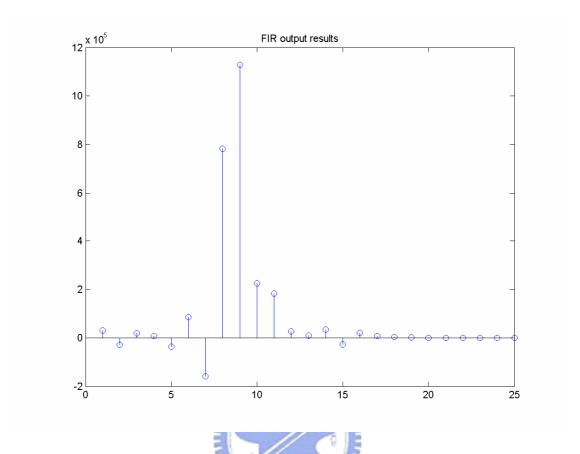

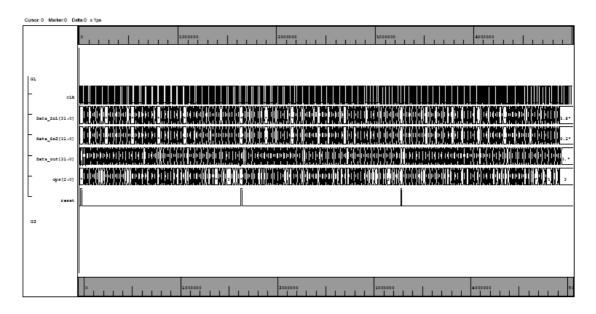

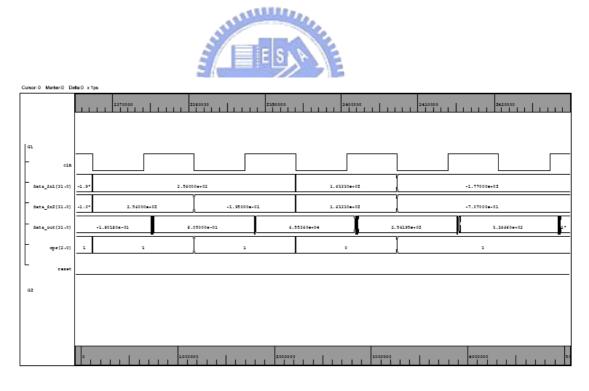

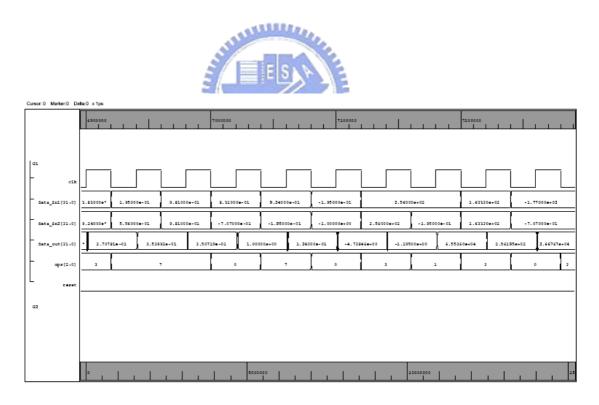

| Fig 4.11    | The input function and coefficients of the FIR filter system | 51 |

| Fig 4.12    | Output results of the FIR filter system                      | 52 |

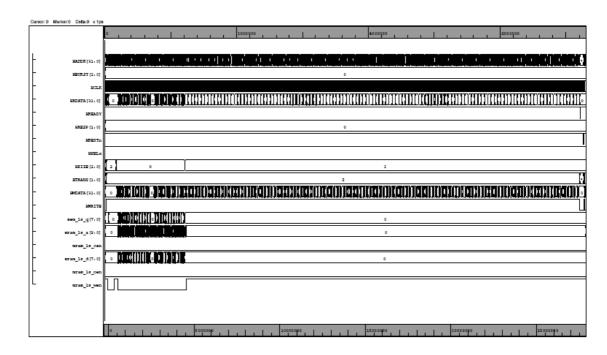

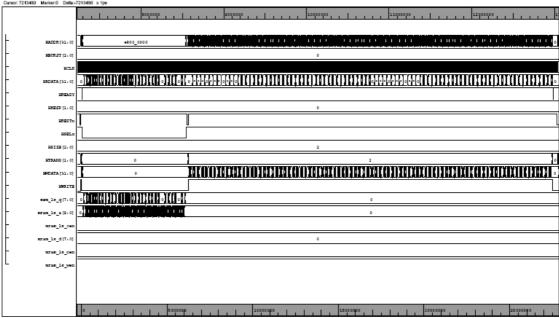

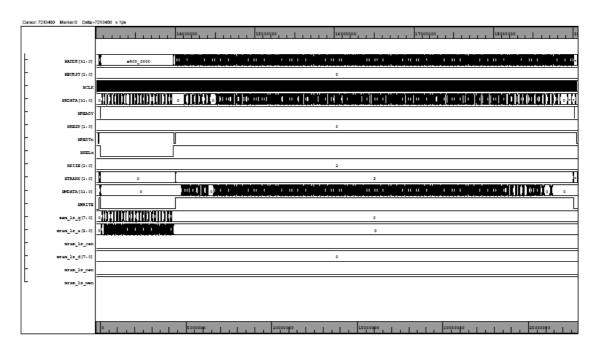

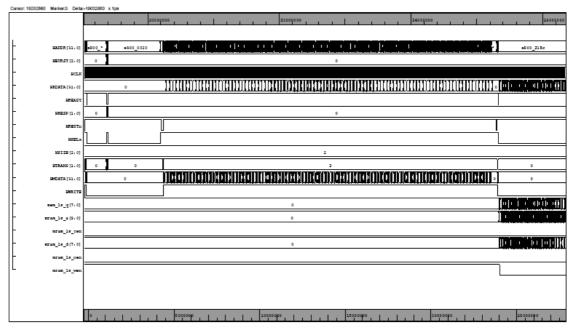

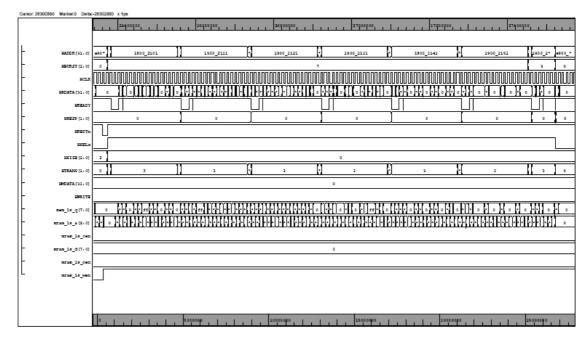

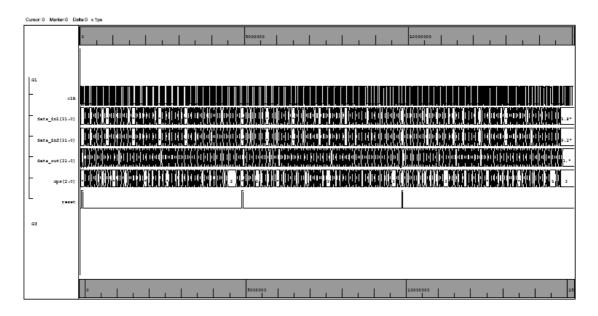

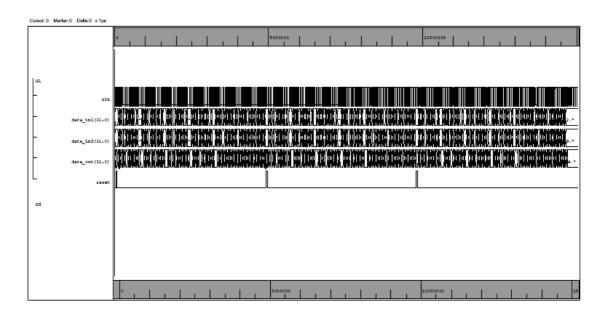

| Fig 4.13(a) | Post-Layout Simulation Results of an ALU cluster IP ( )      | 53 |

| Fig 4.13(b) | Post-Layout Simulation Results of an ALU cluster IP ( ) 53   |            |  |  |

|-------------|--------------------------------------------------------------|------------|--|--|

| Fig 4.13(c) | Post-Layout Simulation Results of an ALU cluster IP ( ) 54   |            |  |  |

| Fig 4.13(d) | Post-Layout Simulation Results of an ALU cluster IP ( ) 54   |            |  |  |

| Fig 4.13(e) | Post-Layout Simulation Results of an ALU cluster IP ( ) 55   |            |  |  |

| Fig 4.14    | The Printed Circuit Board (PCB) for the manufactured chip 55 |            |  |  |

| Fig 4.15    | Testing Equipments – Logic Analyzer System 56                |            |  |  |

| Fig 4.16    | Connection between the Chip and Testing Equipments 56        |            |  |  |

| Fig 4.17    | Physical Layout of the Type 1 FPU macro 58                   |            |  |  |

| Fig 4.18    | Physical Layout of the Type 2 FPU macro                      |            |  |  |

| Fig 4.19    | Physical Layout of the Type 3 FPU macro 59                   |            |  |  |

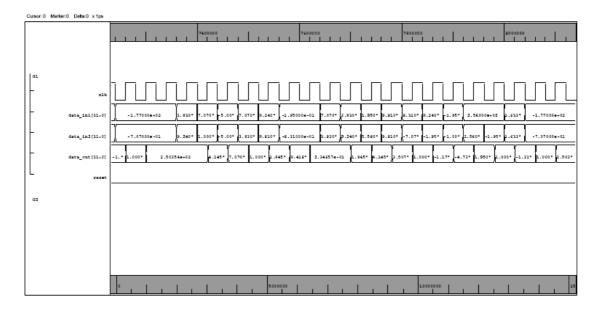

| Fig 4.20    | Full View of Post-Layout Simulation Results for Type 1       |            |  |  |

|             | FPU                                                          | 60         |  |  |

| Fig 4.21    | Interception of Post-Layout Simulation Results for Type 1    |            |  |  |

|             | FPU                                                          | 60         |  |  |

| Fig 4.22    | Full View of Post-Layout Simulation Results for Type 2       |            |  |  |

|             | FPU                                                          | 61         |  |  |

| Fig 4.23    | Interception of Post-Layout Simulation Results for Type 2    |            |  |  |

|             | FPU                                                          | 61         |  |  |

| Fig 4.24    | Full View of Post-Layout Simulation Results for Type 3       |            |  |  |

|             | FPU.                                                         | 62         |  |  |

| Fig 4.25    | Interception of Post-Layout Simulation Results for Type 3    |            |  |  |

|             | FPU                                                          | 62         |  |  |

| Fig 4.26    | Flowchart of the length 32 Split-Radix FFT algorithm         | 64         |  |  |

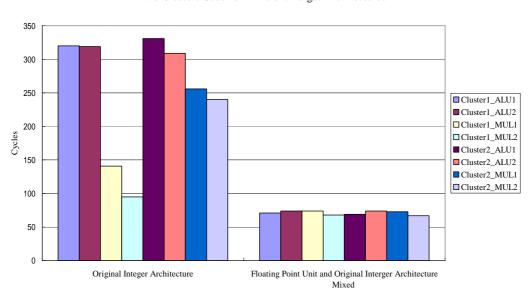

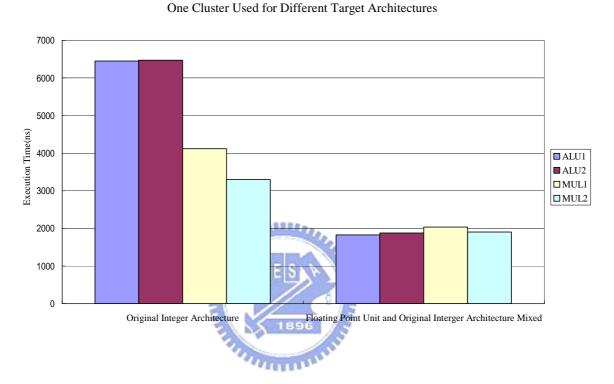

| Fig 4.27    | Performance Evaluation of one cluster included in these      |            |  |  |

|             | architectures                                                | 68         |  |  |

| Fig 4.28    | Performance Evaluation of two clusters included in these     |            |  |  |

|             | architectures                                                | 69         |  |  |

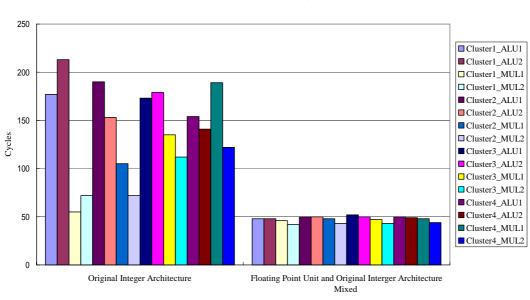

| Fig 4.29    | Performance Evaluation of four clusters included in these    |            |  |  |

|             | architectures                                                | 69         |  |  |

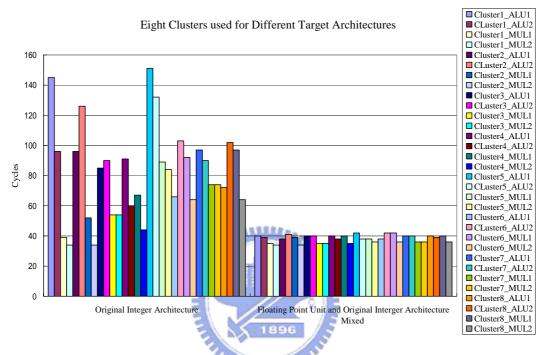

| Fig 4.30    | Performance Evaluation of eight clusters included in these   |            |  |  |

|             | architectures                                                | <b>7</b> 0 |  |  |

| Fig 4.31    | Performance Evaluation of one cluster included in execution  |            |  |  |

|             | time                                                         | 72         |  |  |

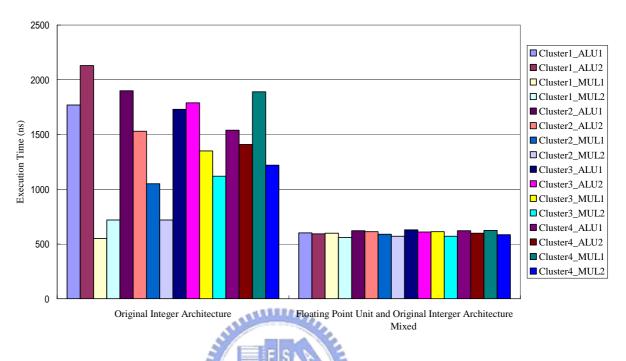

| Fig 4.32    | Performance Evaluation of two clusters included in           |            |  |  |

|             | execution time                                               | 73         |  |  |

| Fig 4.33    | Performance Evaluation of four clusters included in          |            |  |  |

|             | execution time                                               | 74         |  |  |

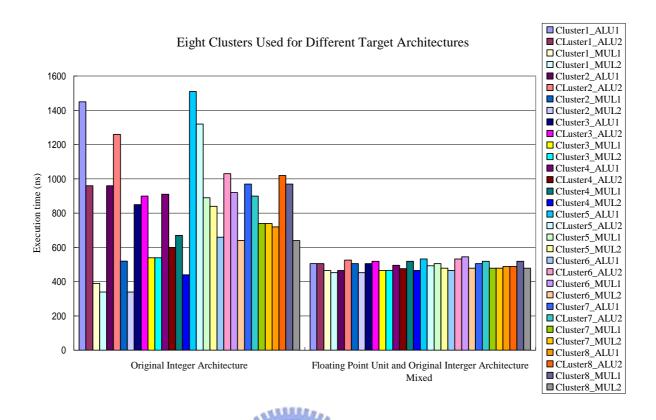

| Fig 4.34 | Performance Evaluation of eight clusters included in     |            |

|----------|----------------------------------------------------------|------------|

|          | execution time                                           | 75         |

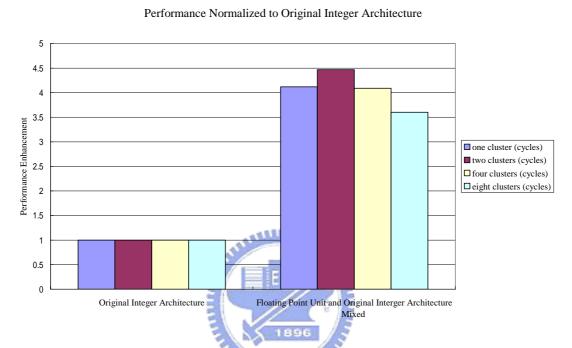

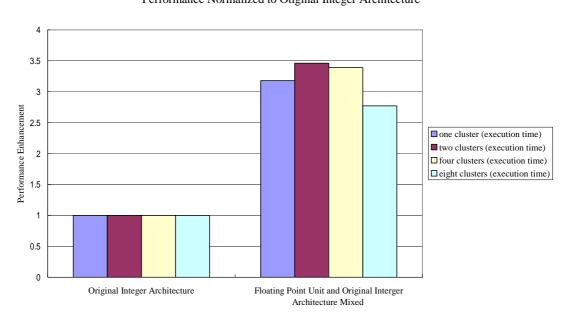

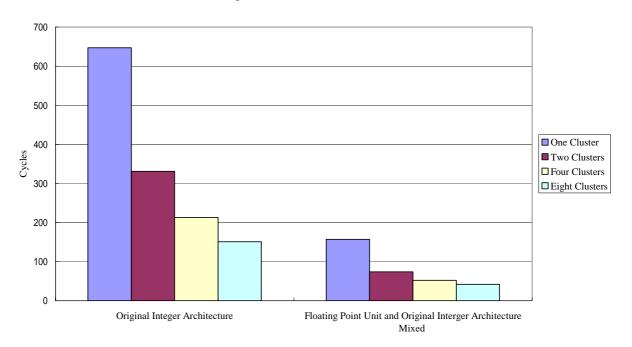

| Fig 4.35 | Comparison of Performance Normalized in execution cycles | <b>7</b> 6 |

| Fig 4.36 | Comparison of Performance Normalized in execution time   | 76         |

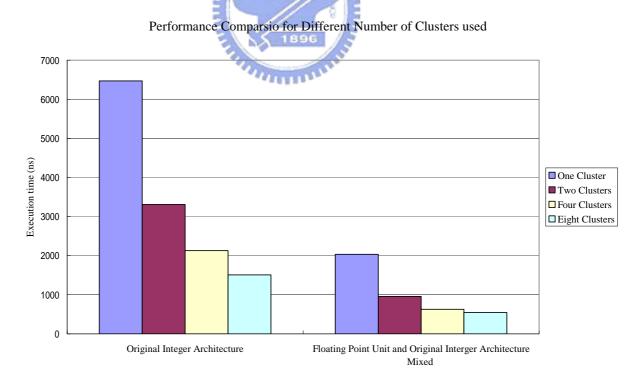

| Fig 4.37 | Performance Comparison for Different Number of Clusters  |            |

|          | used in cycles                                           | 78         |

| Fig 4.38 | Performance Comparison for Different Number of Clusters  |            |

|          | used in execution time                                   | <b>78</b>  |

|          |                                                          |            |

| Fig 5.1  | RealView Versatile Platform Baseboard for ARM926EJ-S     | 81         |

# CHAPTER 1 Introduction

#### 1.1 Motivation

Portable systems are more and more important. They become essentials of our life. Furthermore, media applications are becoming a dominant portion of processing for portable entertainment system in modern life.

Multimedia processing applications are characterized by large available parallelism, little data reuse and high computation to memory access ratio. Large available parallelism due to each data stream is independent to others, so each stream is possible to be operated concurrently. The reason for the characteristic of little data reuse is that typical data reference in media applications require a single read and write per global data element. High computation to memory access ratio is needed because of large amount of data operations [1 - 4]. Thus these characteristics poorly match conventional general purpose processor architecture. The conventional programming model and processor architecture dealt with media applications traditionally are not efficient because of the characteristics of media applications, its memory accessing model and processor-memory performance gap [5].

In addition to programming models, system architectures used to implement the whole media processing system are also key factors to affect the efficiency of processing. System architectures such as application specific integrated circuits (ASIC), platform-based architecture and reconfigurable architecture are used to implement the hardware for media applications. However, these architectures for media processing have their own drawbacks separately. They suffer from lacking of flexibility, programmability, and inefficient communication bandwidth. The issues of programming model and system architecture mentioned above limit the processing requirement needed for modern media application in mobile system.

However, streaming programming model has been suggested as an efficient programming model for both media applications and base-band architecture for software defined radios [6] [7]. In order to build next generation media processing system, advantages from different system architectures are integrated. The pros of reconfigurable architecture and platform-based architecture will overcome the drawbacks of using above-mentioned architecture separately.

This thesis presented a processing element for reconfigurable homogenous ALU cluster and its Advanced Microcontroller Bus Architecture (AMBA) platform interface has been designed and implemented. The proposed design provides enough processing requirement for media applications and utilized as a reconfigurable hardware accelerator for specific and different functions in media applications. AMBA AHB interface in this design provides an integration platform for embedded operating system and programming development environment. The combination of these design methodologies will be a suitable solution in development applications for portable devices.

All design and verification of the proposed architecture are finished with cell-based design flow. The chip is taped out using TSMC 0.15um CMOS technology and operates at 100MHz. The die size and gate count are 15.2 mm² and 0.2 million respectively. Utilize COB (PGA256) as package material. The pad number of proposed chip is 130. The designed chip with daughter card will be integrated with ARM926EJ-S versatile baseboard to form a media streaming system and as the development environment for applications.

Furthermore, a floating point operation unit is critical in the majority of media application and makes the applications efficient. A floating point operation unit for ALU cluster IP is proposed and implemented in this thesis as a modified version of the hardware accelerator. The hard macro of three different type floating point unit operates at 75MHz, 25MHz and 25MHz, its area and gate count is 0.415 mm², 0.529mm², 0.396mm² and 0.02million, 0.03 million, 0.02 million respectively. Then the performance evaluation and comparison between two different target architectures are presented and shows the results that the floating point unit is efficient and critical for the proposed architecture.

#### 1.2 Organization

In the beginning of Chapter 2, the background and challenges about this thesis are introduced. Issues of programming models and system architectures for media applications are discussed.

Next come the details of the development roadmap and the proposed design is described. The development roadmap and micro-architectures of an ALU cluster, an ALU cluster Intellectual Property and Floating point units for the ALU cluster IP and the overview of the AMBA AHB protocol are described in Chapter 3.

In Chapter 4, implementation results of proposed designs are described. The verification and testing results are also introduced in this chapter. Then the performance evaluation and comparison are discussed in the last part of the chapter. In the last chapter of this thesis, Chapter 5, the conclusion and future work are summarized.

## CHAPTER 2

### **Background and Challenges**

This chapter begins with the discussion of conventional programming model for media application. Therefore two kinds of programming model are used to deal with data while the comparison between programming models will be introduced in next chapter. Meanwhile, different system architectures of implementing the design are presented and discussed. These issues discussed of the programming models and system architectures are the background of current research. This thesis is motivated from these issues of the background.

#### 2.1 Issues of Programming Model

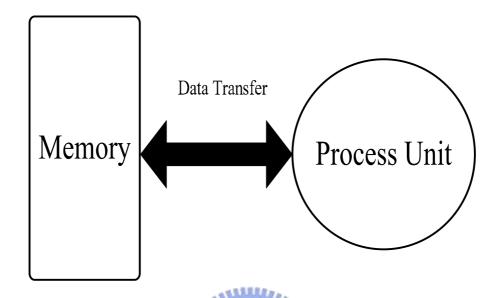

Traditionally, the media applications are processed by conventional programming model implemented in conventional general purpose processor architecture. As shown in Fig 2.1, conventional programming model read data from memory system for computation and write results back into memory system. The memory system of this processing model depends on caches, which is optimized for latency and data reuse. Remind the characteristics of media processing applications. First, every stream is read exactly once, resulting in poor cache performance. Second, operating one data element is largely independent to others. It results in a large amount of data parallelism and high latency tolerance. Finally it can not support high ratio of computation to memory access. Above-mentioned issues show that large available parallelism, little data reuse and high computation to memory access ratio are cramped by the attributes of caches.

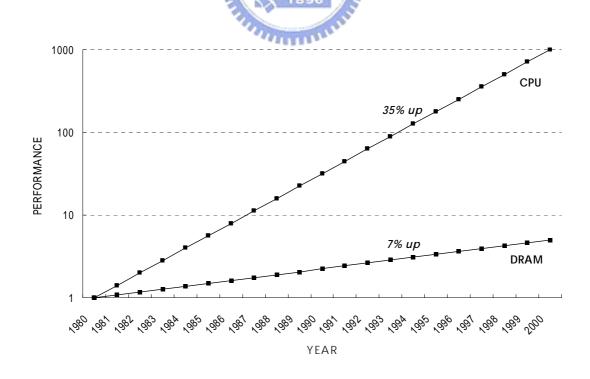

Another clincher is memory-processor communication bandwidth gap. As shown in Fig 2.2, the processor-memory performance gap reveals that the performance growth of memory is much slower than processor [8]. The phenomenon will cause more latency for memory access and communication between processor and memory

is more critical. And traditional memory system utilizes global structures to provide data bandwidth. It means that it cannot scale to multiple arithmetic logic units for high performance rates in media applications.

Fig 2.1 Conventional Programming Model

Fig 2.2 Processor-Memory Performance Gap

#### 2.2 Issues of System Architecture

Generally speaking, there are many different system architectures when implementing a design. Three main system architectures of design methodology, such as application specified integrated circuit(ASIC), platform-based architecture and reconfigurable architecture will be briefly introduced in this section on the basis of time to market demands, programmability, flexibility and physical area, etc. Following, the pros and cons of these system architectures are discussed. [9 - 11]

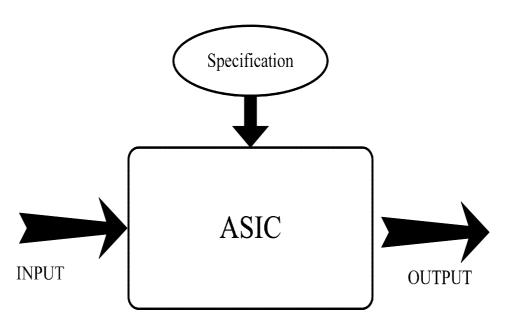

The application specified integrated circuit is the most commonly used in these architectures. The ASIC design principle is shown in Fig 2.3. The chip implementation could be finished very quickly as long as the well-defined specification is given. Overall function and performance, such like area, power consumption and operating frequency, are optimized for the specification required. Thus long design cycles which include circuit design and the manufacture increase the investment risk. And design verifications and corrections also take a large amount of design effort. It raises investment risk also. In addition, the waste of logic resources and power dissipation for non-active hardware is another issue for the design methodology. Besides, let us consider the situation that the specifications are changed. In this situation, it reveals the lack of flexibility for ASIC design. It also shows the lack of programmability and non-reusable in the architecture.

Fig 2.3 Application Specified Integrated Circuit Design

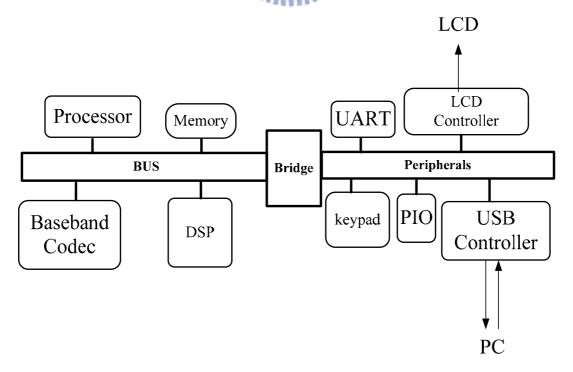

The platform-based architecture includes a processor, memory, communication bus and multiple functional hardware accelerators. It gains more flexibility than ASIC architecture from reusing existence intellectual property (IP), such as digital signal processor (DSP), baseband codec, audio applications accelerator and other functional blocks. The example of platform-based architecture is shown in Fig 2.4. Different IP blocks are added or removed to meet different application. The platform-based architecture provides a common communication bus for convenience to integrated different IP macros quickly. Different systems will be set up as fast as possible. It reduces the design and re-develops effort significantly. One more attractive thing is that these platforms have been set up with a developing baseboard. Many common IP and peripherals on the baseboard will benefit to fast prototyping. The existent OS of the baseboard can reduce the effort of connecting the real applications to development design. Current research such as [12], [13] and [14] are listed in the reference.

Thus there are some drawbacks in this architecture. The interface communicate each functional macro increases the overhead of whole system. Besides, the memory bandwidth is limited by the communication bus. These factors decrease the efficiency seriously. In the meantime, the power consumption should be increased when more IP blocks are included. The idle IP macros waste unnecessary power dissipation, too. As discussed above, the platform-based architecture is more flexible and programmable than ASIC design. Thus this architecture is still a task-oriented system. It can not be applied to any application using the same framework.

Fig 2.4 An Example of Platform-Based Architecture

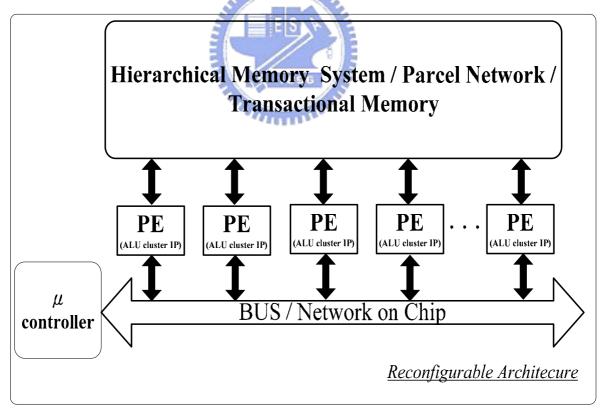

The reconfigurable architecture, the third design methodology, is similar to platform-based architecture. As shown in Fig 2.5, there are multiple general processing elements in this architecture. These processing elements, or ALU cluster IP blocks, play the key role of operating data stream. A system of reconfigurable architecture is built up with a micro controller, a bus or a network on chip system and a well-hierarchical memory system. One advantage of this kind of architecture is the usages of hardware accelerator IP are reconfigurable. It provides a significant flexibility and programmability for different applications. Another advantage is the applications can be operated concurrently. It means that it provides the ability for parallel operation. Nevertheless, there exist some potential drawbacks in using the design methodology. First, without power management system the power dissipation of unused process elements can not be saved. Second, the reconfigurable architecture could not match the above-introduced characteristic very well since the bandwidth of communication bus is insufficient and data transfer bottleneck encounters between process elements and memory system. The efficient memory hierarchy system is needed to solve the performance degradation. Current research such as [15], [16] and [17] are referenced in the bibliography.

Fig 2.5 A Diagram of Reconfigurable Architecture

In conclusion, one of these system architectures can be selected to implement the design trading off between pros and cons addressed above. These pros and cons corresponding to characteristics of media applications are summarized in the Table 2.1 listed below. Thus, any one of them adopted alone suffers from some drawbacks and can not meet the application of media processing very well. Consequently, the proposed design will be addressed and discussed in later section. It must resolves these issues.

Table 2.1 System Architecture vs. media application

|                                           | ASIC                                                                                         | Platform-Based Architecture                                                                                  | Reconfigurable Architecture                                                                        |

|-------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                           | THE REAL PROPERTY.                                                                           | Weintecture                                                                                                  | Tucintecture                                                                                       |

|                                           | <b>3</b>                                                                                     | S A                                                                                                          | Flexibility and                                                                                    |

|                                           | Lack of hardware                                                                             | Memory bandwidth                                                                                             | programmability                                                                                    |

|                                           | flexibility                                                                                  | will be limited by                                                                                           | Parallelism                                                                                        |

|                                           | Lack of                                                                                      | bus                                                                                                          | Data transfer                                                                                      |

| G .                                       | programmability                                                                              | Immediate data                                                                                               | bottleneck between                                                                                 |