國立交通大學

光電工程研究所

碩士論文

介面修飾對有機薄膜電晶體元件特性之影響

**Effect of Surface Treatments on the Device

Properties of Organic Thin-Film Transistors**

研究生：蔡紓婷

指導教授：陳方中 博士

中華民國九十六年八月

介面修飾對有機薄膜電晶體元件特性之影響

**Effect of Surface Treatments on the Device

Properties of Organic Thin-Film Transistors**

研究生：蔡紓婷

Student : Shu-Ting Tsai

指導教授：陳方中 博士

Advisor : Dr. Fang-Chung Chen

A Thesis

Submitted to Institute of Electro-Optical Engineering

College of Electrical and Computer Engineering

Nation Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of Master

In

Electro-Optical Engineering

July 2006

Hsinchu, Taiwan, Republic of China

中華民國九十六年八月

# 介面修飾對有機薄膜電晶體元件特性之影響

碩士研究生：蔡紓婷

指導教授：陳方中

國立交通大學光電工程研究所碩士班

## 中文摘要

本論文探討五環素(pentacene)與絕緣層間的介面修飾對薄膜電晶體啟動電壓(turn-on voltage,  $V_{to}$ )的影響。我們以PMMA、PVP以及HMDS處理絕緣層( $\text{SiN}_x$ )表面，分別測量電流電壓曲線與電容電壓曲線，發現啟動電壓( $V_{to}$ )和平帶電壓( $V_{FB}$ )的點並不一致，推測這可能是由於修飾材料的特性造成了捕捉陷阱密度有差異。為了分析捕捉陷阱的來源，我們分為晶粒內部和晶粒邊界(grain boundary)兩部份來探討，我們發現五環素的排列整齊度是影響元件捕捉陷阱密度的主要因素，而造成啟動電壓位移則是由晶粒邊界數目多寡決定。由實驗結果可知，不同的介面修飾可導致元件的開啟電壓與平帶電壓偏移，如此便可利用簡單的旋塗製程調變啟動電壓。

# Effect of surface treatments on the Device Properties of Organic Thin-Film Transistors

**Student : Shu-Ting Tsai**

**Advisor : Dr. Fang-Chung Chen**

Electro-Optical Engineering

National Chiao Tung University

## Abstract

The effect of surface treatments on the performance of organic thin-film transistors(OTFTs) has been investigated using pentacene as the active material. With poly-methyl-meth-acrylate(PMMA), poly-4-vinylphenol(PVP) or 1,1,1,3,3,3-hexamethyldisilazane(HMDS) on  $\text{SiN}_x$  dielectric layers, the mismatch between the turn-on voltages and the flat-band voltages were observed, which were obtained from current-voltage and capacitance-voltage characteristics, respectively. This is probably due to different trap density in the channel of the devices. The traps probably distribute inside the grains and in the grain boundaries. It is found that the arrangement of the pentacene molecules determines the trap density of devices and the turn-on voltage shift is mainly affected by the density of grain boundaries. Using different polymers can modulate the device turn-on voltage and flatband voltage. As a result, a simple fabrication process of devices with various turn on voltage is achieved.

## 誌謝

研究所兩年的時光在做實驗中快速飛逝而過，能夠完成這份碩士論文要感謝大家的幫忙。首先要感謝陳方中老師提供我非常好的研究環境，指導我做學問的正確觀念，讓我不但在專業領域上擴充新知外，也改變了作事情該有的態度，同時感謝朱治偉博士、劉柏村老師、戴亞祥老師提供的意見，讓本文更完善。

接著，我要感謝我的老大舜哥總是耐心的教我做實驗，指引我正確的思考方向，每每與我討論時總是傾囊相授。謝謝祖榮哥在實驗方面的大力相挺，也謝謝永昇、立仁、東賢在實驗儀器與基本觀念的指導，讓我可以很快就進入狀況。更感謝映頻在我實驗或是心情陷入低潮時，總會適時伸出援手拉我一把，讓我又可以重新出發。也感謝思芳、惠君、文生、瑞祥、奎哥、志平學長在實驗觀念上的指教，讓我的視野可以更寬廣。

謝謝實驗室共同奮戰的同學：尹婷、泰元、志力、上傑、浩偉、義凱，還好這一路走來有大家的陪伴，共同面臨畢業壓力，讓壓力減輕不少。感謝實驗室學弟妹：太獅、曉芬、呈祥、昱仁、永軒、政豪、安琪，沒有妳們實驗室就少了歡笑，也感謝你們在實驗上也都會適當的給於我協助、意見，讓我實驗數據不至於會難產。感謝從大學一路上來一起念研究所的同學們潤琪、宛芳、秀娟、家軒、亞諭…與研究所的同學們政丹、明容、馨文、芸嘉…，還有產專的朋友們俞文、家峰、子怡、枝福…，因為有妳們讓苦悶的碩士生活更添光采，碩士兩年將是我永遠會記得的回憶，感謝大家帶給我美好的回憶。

謝謝校隊的大家，雖然很晚才認識你們，但是卻有了永難磨滅的奮戰經驗，一起拿到了女子團體總冠軍，也感謝教練願意給我上梅竹賽的機會，感謝你們。

最後，我要感謝我的父母親，即使家裡經濟狀況並不是很好，但是對於我的唸書生涯妳們從不打算中斷，反倒是無怨無悔的提供我良好的求學環境，也始終陪伴在我身邊關心我，現在終於畢業了，也正式結束了我的求學生涯。接下來換成是我回報妳們了，謝謝你們總是在背後默默支持我。

## 目 錄

|       |                  |     |

|-------|------------------|-----|

| 中文摘要  | .....            | i   |

| 英文摘要  | .....            | ii  |

| 誌謝    | .....            | iii |

| 目錄    | .....            | iv  |

| 表目錄   | .....            | vi  |

| 圖目錄   | .....            | vii |

| 第一章   | 序論               | 1   |

| 1.1   | 前言               | 1   |

| 1.2   | 有機薄膜電晶體與相關元件特性   | 3   |

| 1.2.1 | 金氧半場效電晶體之結構與元件特性 | 3   |

| 1.2.2 | 薄膜電晶體之結構與元件特性    | 7   |

| 1.2.3 | 有機薄膜電晶體發展史       | 8   |

| 1.2.4 | 有機薄膜電晶體之相關製程     | 11  |

| 1.3   | 有機半導體材料簡介        | 14  |

| 1.3.1 | 高分子(polymer)     | 15  |

| 1.3.2 | 寡分子(oligomer)    | 15  |

| 1.3.3 | 小分子              | 15  |

| 第二章   | 動機與原理            | 16  |

| 2.1   | 研究動機與目的          | 16  |

| 2.2   | 有機材料的導電機制        | 17  |

| 2.2.1 | 偏極子(polaron)的形成  | 17  |

| 2.2.2 | 傳輸模型             | 18  |

| 2.3   | 五環素材料之簡介         | 20  |

| 2.4   | 有機薄膜電晶體的載子移動率    | 22  |

| 2.5   | 有機薄膜電晶體的操作模式     | 23  |

| 2.5.1 | MOSFET(金氧半場效電晶體) | 23  |

| 2.5.2 | 有機電晶體            | 24  |

| 2.6   | 各項重要參數           | 25  |

| 2.6.1 | 載子遷移率            | 25  |

| 2.6.2 | 臨限電壓             | 27  |

| 2.6.3 | 電流開關比            | 28  |

| 2.6.4 | 次臨界擺幅            | 28  |

| 2.6.5 | 啟動電壓             | 28  |

| 2.6.6 | 平帶電壓             | 29  |

| 第三章   | 實驗架構             | 30  |

| 3.1   | 實驗流程             | 30  |

| 3.1.1 | 基板               | 30  |

| 3.1.2 | 基板清洗             | 30  |

|             |                                      |           |

|-------------|--------------------------------------|-----------|

| 3.1.3       | 表面處理.....                            | 31        |

| 3.1.4       | 主動層及電極的蒸鍍.....                       | 32        |

| 3.1.5       | 元件流程.....                            | 33        |

| 3.2         | 實驗儀器.....                            | 36        |

| 3.3         | 原子力顯微鏡操作步驟與原理.....                   | 37        |

| <b>第四章</b>  | <b>實驗結果與討論.....</b>                  | <b>40</b> |

| 4.1         | 介面修飾對元件 $V_{to}$ 和 $V_{FB}$ 的影響..... | 40        |

| 4.2         | 陷阱捕捉.....                            | 43        |

| 4.3         | 晶粒內部.....                            | 45        |

| 4.4         | 晶粒邊界.....                            | 47        |

| 4.4.1       | Z 軸方向.....                           | 47        |

| 4.4.2       | X-Y 平面-五環素厚度 100Å.....               | 48        |

| 4.4.3       | X-Y 平面-五環素厚度 600Å.....               | 50        |

| 4.5         | 影響晶粒邊界的因素.....                       | 52        |

| 4.5.1       | 接觸角.....                             | 52        |

| 4.5.2       | 修飾層表面粗燥度.....                        | 54        |

| <b>第五章</b>  | <b>結論.....</b>                       | <b>56</b> |

| <b>參考文獻</b> | <b>.....</b>                         | <b>57</b> |

## 表 目 錄

|       |                                      |    |

|-------|--------------------------------------|----|

| 表 4.1 | 不同修飾的元件 $V_{to}$ 和 $V_{FB}$ 的數值..... | 42 |

| 表 4.2 | 不同修飾的元件參數值.....                      | 44 |

| 表 4.3 | X 光繞射強度與捕捉陷阱數目整理.....                | 46 |

| 表 4.4 | 不同修飾 Z 方向晶粒大小.....                   | 48 |

| 表 4.5 | 五環素厚度 $100 \text{ \AA}$ 的邊界長度.....   | 48 |

| 表 4.6 | 五環素厚度 $600 \text{ \AA}$ 的邊界長度.....   | 50 |

| 表 4.7 | 將不同修飾的表面特性整理成表.....                  | 52 |

| 表 4.8 | 接觸角量測儀三種液滴的特性.....                   | 53 |

| 表 4.9 | 不同修飾的表面形貌粗糙度與介面的最大捕捉陷阱數目關係表          | 55 |

## 圖 目 錄

|        |                                                                                                                                               |    |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 圖 1.1  | MOSFET 的元件結構圖(a)p 型半導體基板、(b)n 型半導體基板                                                                                                          | 3  |

| 圖 1.2  | 傳統pMOS的電流電壓圖，(a) $I_D$ - $V_{GS}$ 、(b)改變 $V_{GS}$ 的 $I_D$ - $V_{DS}$ 圖                                                                        | 4  |

| 圖 1.3  | 當 $V_{GS} > V_T$ ，(a)小 $V_{DS}$ 值、(b)較大的 $V_{DS}$ 值、(c) $V_{DS} > V_{DS(sat)}$ 的值、(d) $V_{DS} > V_{DS(sat)}$ 的值時的截面及 $I_D$ - $V_{DS}$ 圖。..... | 6  |

| 圖 1.4  | 薄膜電晶體結構圖.....                                                                                                                                 | 7  |

| 圖 1.5  | 1983 年發表在國際期刊的第一顆 OTFT 電性圖.....                                                                                                               | 8  |

| 圖 1.6  | 1988 年 A. Assadi 等人使用 P3HT 製作的 OTFT 元件.....                                                                                                   | 9  |

| 圖 1.7  | Mobily 達 $7 \text{ cm}^2/\text{Vs}$ 的OTFT元件電性圖.....                                                                                           | 10 |

| 圖 1.8  | Mobily在室溫高達 $35\text{cm}^2/\text{Vs}$ 的載子遷移率對溫度關係圖.....                                                                                       | 10 |

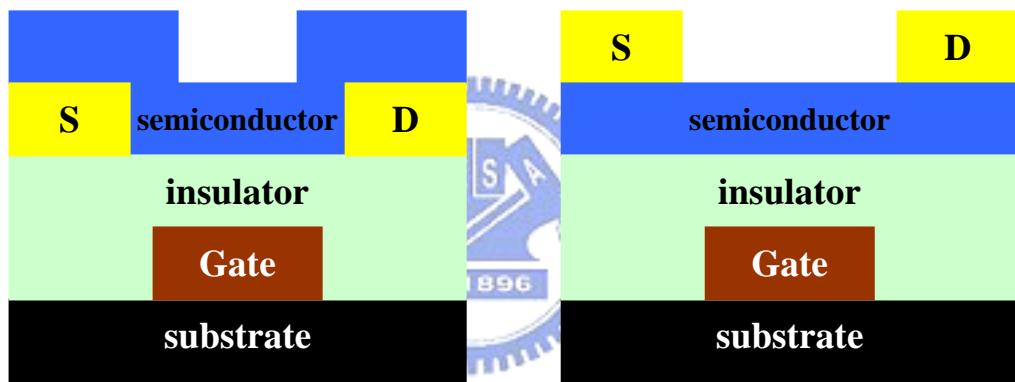

| 圖 1.9  | (a)底電極(Bottom Contact)與(b)頂電極(Top Contact) .....                                                                                              | 11 |

| 圖 1.10 | 用 contact printing 的方式製作小線寬 top contact OTFT.....                                                                                             | 12 |

| 圖 1.11 | 有機半導體材料(a)高分子(b)寡分子(c)小分子.....                                                                                                                | 14 |

| 圖 2.1  | 能帶中 polaron 的產生機制示意圖.....                                                                                                                     | 17 |

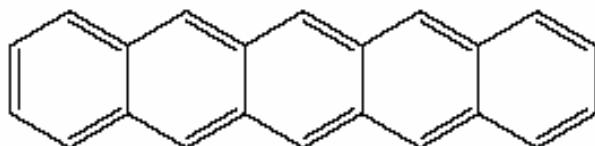

| 圖 2.2  | Pentacene 的化學結構圖，由五個苯環所組成，又稱五環素.....                                                                                                          | 20 |

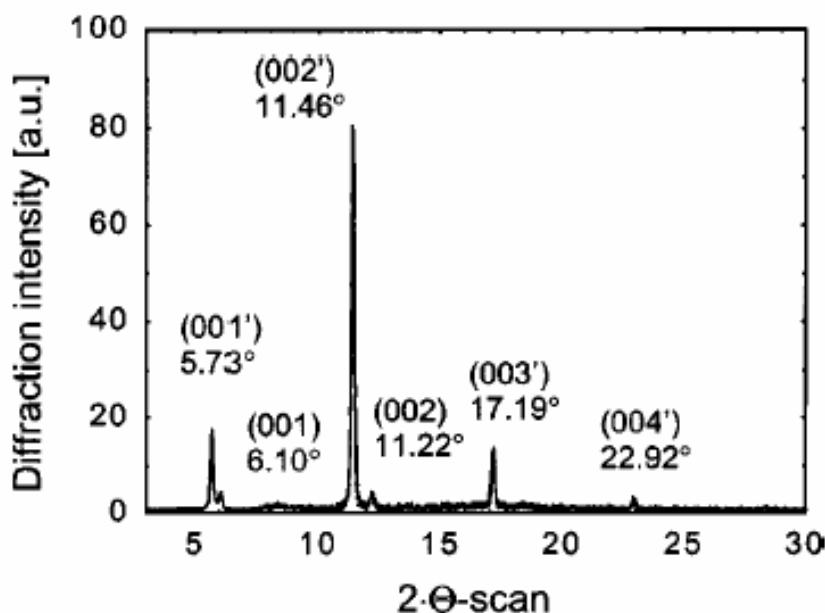

| 圖 2.3  | pentacene 之 X-ray 相關繞射峰.....                                                                                                                  | 20 |

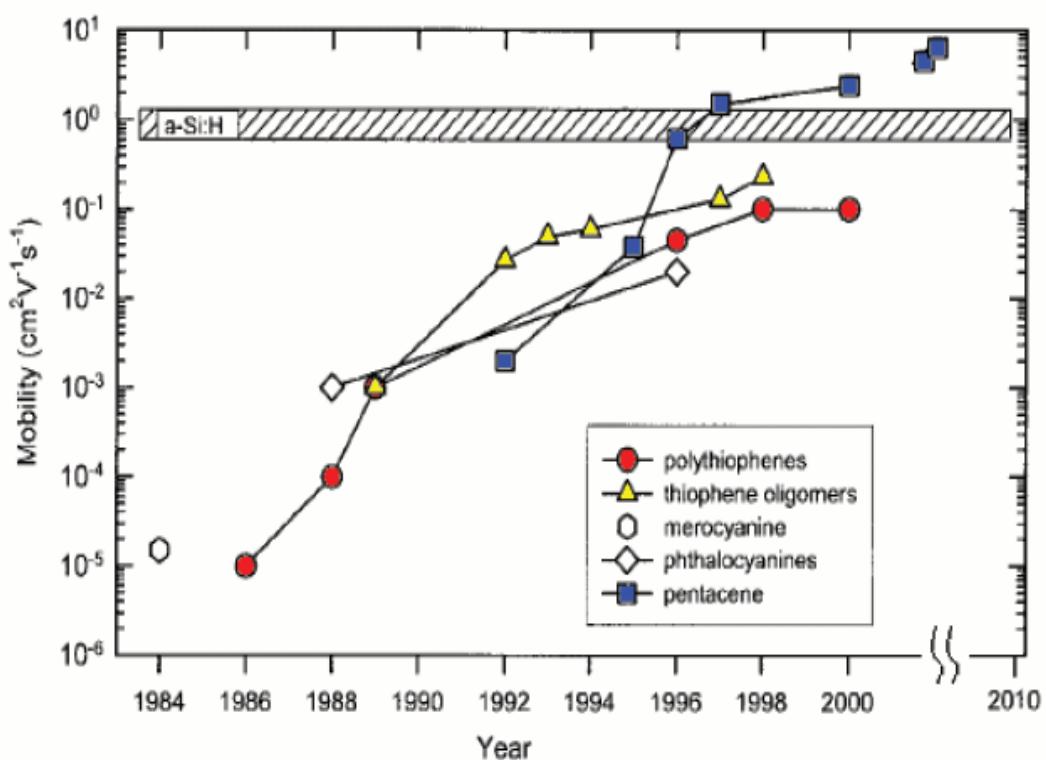

| 圖 2.4  | 從 1984 年至今的 OTFT mobility 進展趨勢.....                                                                                                           | 22 |

| 圖 2.5  | 金氧半接面能階隨閘極電壓的變化.....                                                                                                                          | 23 |

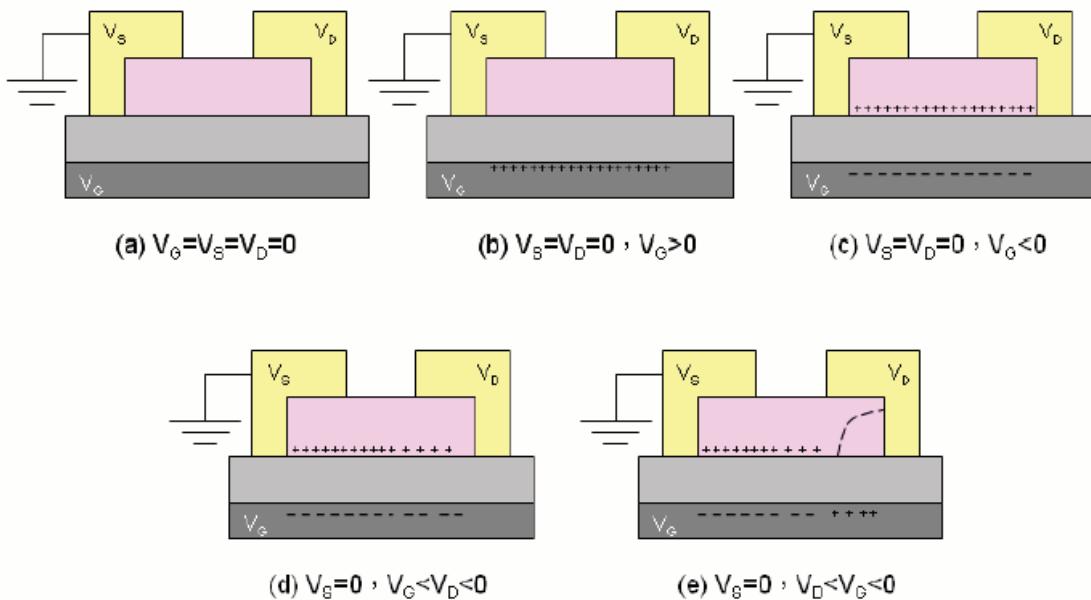

| 圖 2.6  | 有機場效電晶體操作機制示意圖.....                                                                                                                           | 24 |

| 圖 2.7  | OTFT 元件參數萃取示意圖.....                                                                                                                           | 26 |

| 圖 2.8  | C-V 示意圖.....                                                                                                                                  | 29 |

| 圖 3.1  | (a)步驟 4 和(b)步驟 5 的示意圖.....                                                                                                                    | 30 |

| 圖 3.2  | 實驗流程示意圖.....                                                                                                                                  | 34 |

| 圖 3.3  | 原子力顯微鏡的雷射模組.....                                                                                                                              | 37 |

| 圖 3.4  | 雷射光點位置示意圖.....                                                                                                                                | 37 |

| 圖 4.1  | $I_D$ - $V_g$ 曲線圖， $V_D = -30\text{V}$ 、 $V_g = +20\text{V} \sim -60\text{V}$ .....                                                           | 40 |

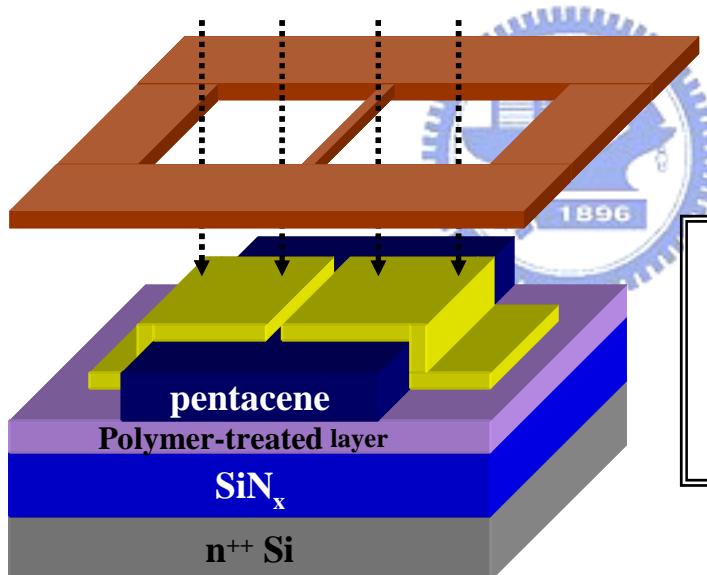

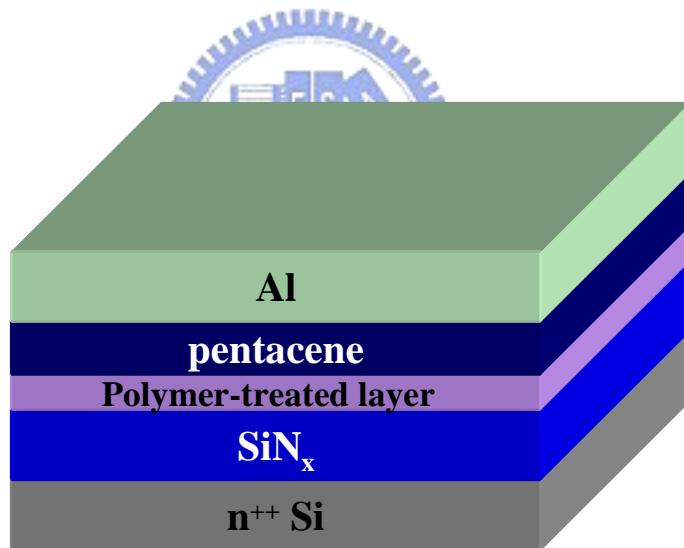

| 圖 4.2  | 量測 $I_D$ - $V_g$ 的元件結構圖.....                                                                                                                  | 41 |

| 圖 4.3  | 量測 C-V 的 MIS 結構圖.....                                                                                                                         | 41 |

| 圖 4.4  | C-V 曲線圖， $V_D = 0\text{V}$ 、 $V_g = +20\text{V} \sim -20\text{V}$ .....                                                                       | 4  |

|        |                                                                                                                                               | 2  |

| 圖 4.5  | C-V 示意圖.....                                                                                                                                  | 4  |

|        |                                                                                                                                               | 3  |

| 圖 4.6  | 五環素成長在不同修飾層的 X 光繞射圖，五環素厚度 $600\text{ \AA}$ .....                                                                                              | 4  |

|        |                                                                                                                                               | 5  |

| 圖 4.7  | 第二根繞射峰放大的圖形.....                                                                                                                              | 4  |

|        |                                                                                                                                               | 6  |

| 圖 4.8  | 厚度 $100\text{ \AA}$ 的五環素表面形貌。 (a) $\text{SiN}_x$ 的元件、(b)經HMDS修飾、(c)經PMMA修飾、(d)經PVP修飾。[面積大小                                                    | 4  |

|        |                                                                                                                                               | 9  |

|                |                                                                                           |        |

|----------------|-------------------------------------------------------------------------------------------|--------|

| 1.67um*1.67um] | .....                                                                                     | .....  |

| 圖 4.9          | 厚度 600 Å 的五環素表面形貌。(a) SiN <sub>x</sub> 的元件、(b)經HMDS修飾、(c)經PMMA修飾、(d)經PVP修飾。[面積大小 5um*5um] | 5<br>1 |

| 圖 4.10         | (a)經HMDS和PMMA修飾的晶粒類似島狀結構、(b)SiN <sub>x</sub> 和經PVP修飾的晶粒類似層狀結構。                            | 5<br>3 |

| 圖 4.11         | (a) SiN <sub>x</sub> 的元件、(b)經HMDS修飾、(c)經PMMA修飾、(d)經 PVP 修飾。[面積大小 5um*5um]                 | 5<br>4 |

# 第一章 序論

## 1.1 前言：

過去數十年來大都使用 Polycrystalline-Si(Poly-Si) 或 Amorphous-Si(a-Si) 等無機物來製作薄膜電晶體，並已廣泛地應用在主動式平面顯示器(Active Matrix Flat Panel Display, AMPLDs)上。在1977年Macdiarmid等人發現以碘蒸氣摻雜聚乙炔(Polyacetylene)可使其導電度大幅提昇，此後導電高分子引起了熱烈的研究與討論，近年來有機半導體材料已被應用在電子元件上成為熱門的研究題材。目前有機半導體已被應用於有機薄膜電晶體(Organic Thin Film Transistors, OTFTs)[1]、有機電激發光元件(Organic/Polymer Light Emitting Diode, OLED/PLED) [2]、有機太陽能電池(Organic Solar Cells) [3]等有機電子元件。

近年來有機薄膜電晶體(OTFTs)的電性和各方面的表現，在大家積極的研究討論中逐步追上非晶矽薄膜電晶體(amorphous silicon thin film transistor)，製程的方法也不斷的改進和嘗試，如低溫製程、大面積製作、成本低廉、具延展性等優點，使得有機薄膜電晶體有機會可以取代非晶矽薄膜電晶體，成為未來平面顯示器的趨動元件，例如主動式矩陣液晶顯示器(active-matrix liquid crystal displays, AMLCDs)[4]和主動式矩陣有機發光二極體(active-matrix organic light-emitting diodes, AMOLEDs)等 [5]。除了在顯示器方面的應用外，也可應用於無線射頻識別系統(radio frequency identification, RFID)中的電路元件[6]，或是濕度感測計[7]等電子產品。也就是說目前OTFTs在低階電子元件方面有機會被廣泛應用。

有機化合物大多包含氫和碳兩種元素，可經由提煉或人工合成之方式產生，也因此有機物的種類非常的多，較常被應用來作為有機半導體材料的可分成高分子和小分子兩種，製程也因此而有差異。高分子通常以旋轉塗佈的方式，而小分子多半以熱蒸鍍的方式進行。

比較有機和無機薄膜電晶體(TFT)，其中利用有機材料來製作電子元件的優點有(1)成本低廉，(2)溶液製程(Solution Process)，包括旋轉塗佈(Spin coating)、噴

墨(Ink-jet Printing)等簡單的製程程序，(3)低溫製程，(4)重量輕、體積小、耐衝擊，(5)在可撓性基板上製作，(6)大面積容易製作等優點。然而，無機電晶體，雖然製程溫度高、成本高，但由於它的載子遷移率高、元件穩定度又高，所以目前在應用上仍是比較成熟，所以如何提昇OTFTs載子移動率、元件穩定度等，是非常重要的課題，也唯有如此才能使有機元件的應用更廣泛。

## 1.2 有機薄膜電晶體與相關元件特性：

### 1.2.1 金氧半場效電晶體之結構與元件特性：

場效電晶體的結構通常是金屬-絕緣層-半導體，金氧半場效電晶體(Metal-Oxide-Semiconductor Field Effect Transistors, MOSFETs)即是一個常見的場效電晶體，基底是經過摻雜的矽，而絕緣層部分是選用氧化層(Oxide)，電極部分則是使用重度摻雜的矽。

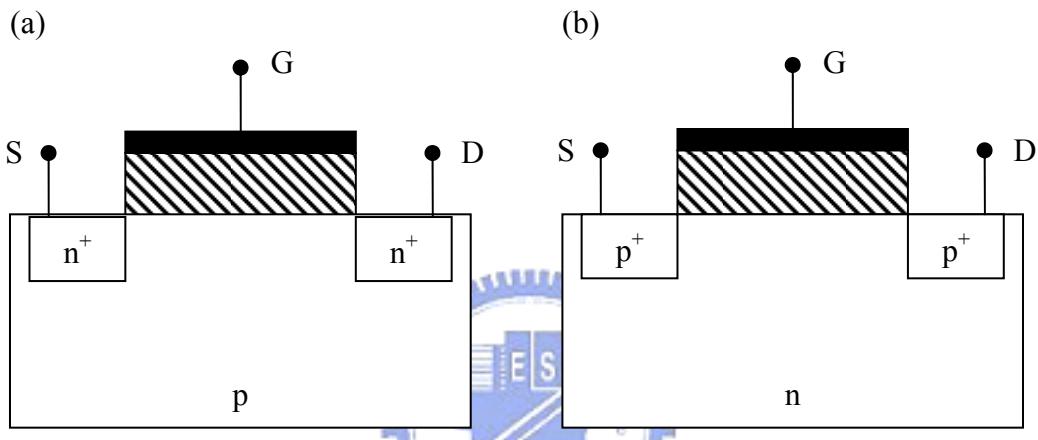

圖1.1 MOSFET的元件結構圖(a)p型半導體基板、(b)n型半導體基板

選用不同摻雜的矽來當作半導體就會有n型和p型之分，如圖1.1所示，p型半導體基版主要是矽經由硼(B)或氟化硼(BF<sub>3</sub>)的摻雜後，增加了可移動電洞的數目，而n型基版則是經由砷(As)和磷(P)摻雜後，多了可移動的電子，而提升了導電度成為半導體層。矽經重度摻雜後變成了MOS元件裡面的電極，也就是在圖1.1中有n<sup>+</sup>或p<sup>+</sup>的部份。

我們會在閘極(G)加一偏壓，在外加偏壓不大的情況下，會形成空乏層，在外加偏壓持續加大後，就會在半導體跟絕緣體的介面形成反轉層，如此我們即可以閘極外加的偏壓來控制通道的大小，而當通道形成且開始導通時，我們稱此電壓值為起始電壓(Threshold Voltage, V<sub>th</sub>)，而此時電晶體的狀態稱為線性區(Linear Region)，若我們繼續加大偏壓，則電流會不斷增大到一個定值後不再增加，此時

的電壓稱為臨界電壓，而電流稱為飽和電流(Saturation Current)，而此時電晶體是操作在飽和區(Saturation Region)，圖1.2 即是一個傳統pMOS的電流電壓曲線。

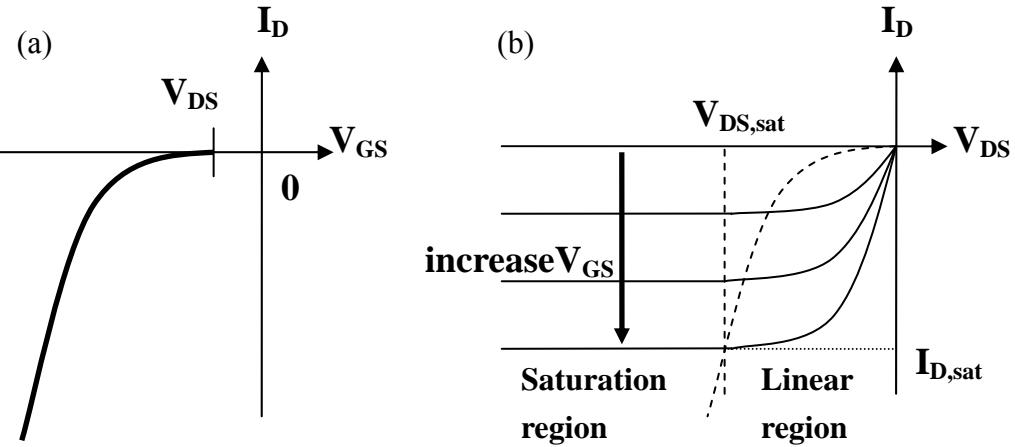

圖1.2 傳統pMOS的電流電壓圖，(a) $I_D$ - $V_{GS}$ 、(b)改變 $V_{GS}$ 的 $I_D$ - $V_{DS}$ 圖

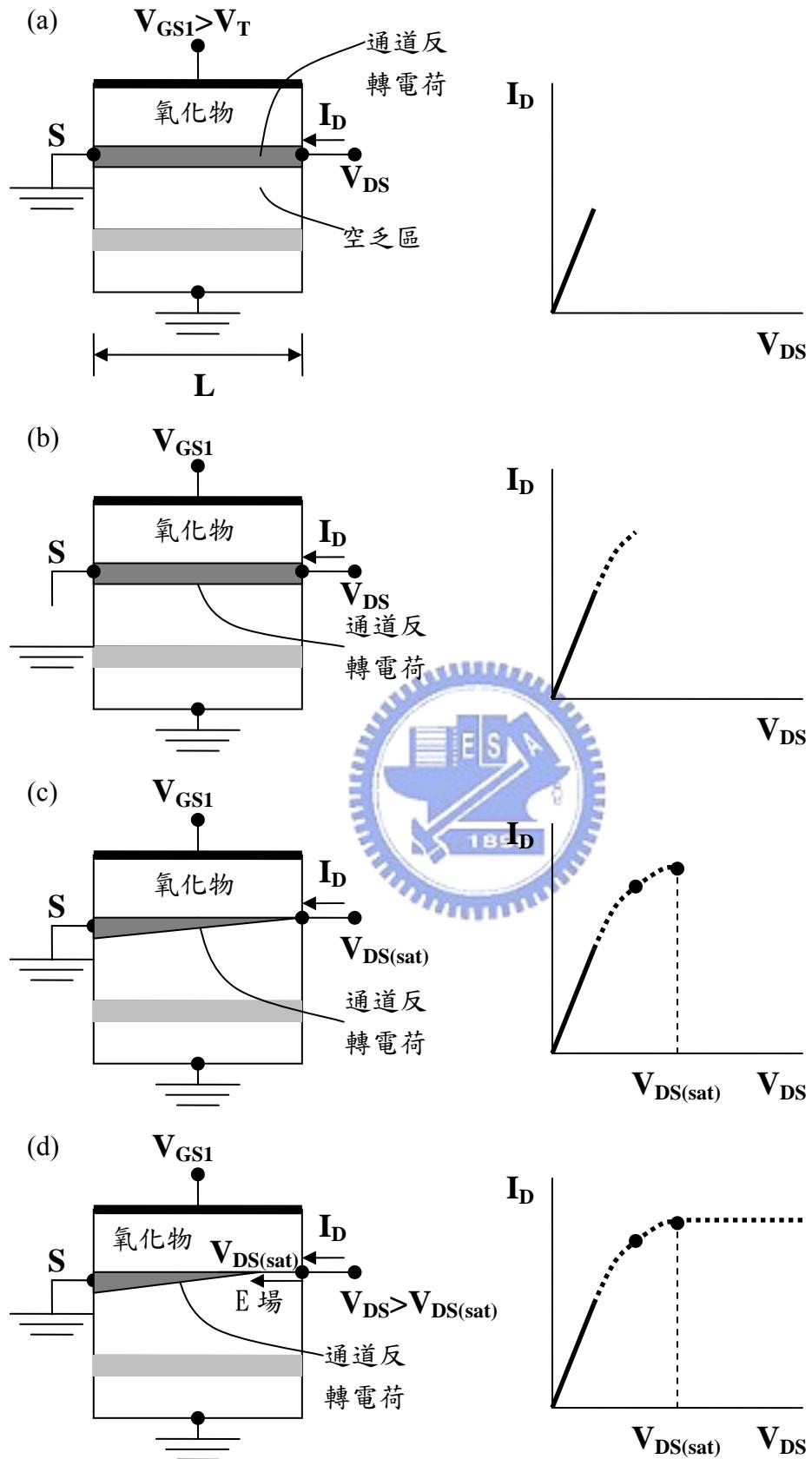

圖1.2是描述改變 $V_{GS}$ (閘極、源極之間的電壓差)對 $I_D$ (從汲極端到源極端的電流)- $V_{DS}$ (汲極、源極之間的電壓差)圖的影響，緊接著我們探討不同的 $V_{DS}$ 在相同的 $V_{GS}$ 對 $I_D$ - $V_{DS}$ 圖的影響，圖1.3(a)是表示當 $V_{GS} > V_T$ 時， $V_{DS}$ 很微小的情況下的MOS結構圖。圖中反轉層的厚度在整個通道都是固定不變的，由此可知整個通道的電荷密度是不變的，而對應的 $I_D$ - $V_{DS}$ 圖顯示在右側。

圖1.3(b)是表示當 $V_{DS}$ 值持續增大，靠近汲極(D)端點處跨降在氧化物上的電壓會下降，這表示反轉電荷密度減少，通道的增量電導也會下降， $I_D$ 對 $V_{DS}$ 曲線的斜率將會隨著降低，從圖中可以看出電流上升的趨勢隨著汲極加的偏壓越大而越來越慢。

圖1.3(c)則是當 $V_{DS}$ 增加到跨降在氧化物上的電壓等於 $V_T$ 時，在汲極附近反轉層的電荷密度剛好為零，增量電導也為零，由此可知 $I_D$ 對 $V_{DS}$ 曲線的斜率也是零，由此現象我們可以推導出 $V_{DS}(sat)$ 的關係式， $V_{DS}(sat)$ 就是在汲極端產生零反轉電荷密度的汲極(D)至源極(S)偏壓。

$$V_{GS} - V_{DS}(sat) = V_T \Rightarrow V_{DS}(sat) = V_{GS} - V_T \quad (1.1)$$

而當  $V_{DS}$  超過  $V_{DS}(\text{sat})$  時，不僅靠近汲極處的反轉電荷為零，等於零的這個點持續朝源極端移動，如圖 1.4(d) 所示。在此時電子從源極注入後進入通道往汲極移動，到達反轉電荷為零的點時，電子被注入空乏區中，在此處是經由電場掃除而到達汲極端，此時的通道長度已比原本的短，而電流將會固定不變，這個  $I_D$  對  $V_{DS}$  的特性區稱為飽和區域。

以下是 MOS 元件的電壓-電流公式：

$$I_D = \frac{WC_i}{L} \mu \left( V_G - V_T - \frac{V_D}{2} \right) V_D \quad (1.2)$$

L：通道長度(channel length)

W：通道寬度(channel width)

$C_i$ ：單位面積的絕緣層電容值(capacitance per unit area of the insulating layer)

$V_T$ ：臨界電壓(threshold voltage)

$\mu$ ：場效載子遷移率(field-effect mobility)

當  $V_{GS} - V_T = V_{DS}$  時，電晶體會進入飽和區，我們將  $V_{GS} - V_T = V_{DS}$  帶入公式(1.2)，可得到在飽和區的電流公式：

$$I_D = \frac{WC_i}{2L} \mu (V_G - V_T)^2 \quad (1.3)$$

從公式可以看出當我們將  $|I_D|^{1/2}$  對閘極電壓  $V_{GS}$  做圖，取曲線的斜率經過計算可求得電晶體在飽和區中的場效載子遷移率  $\mu$  值，將此線延伸對  $V_{GS}$  軸交的截距即為  $V_T$ 。

圖1.3 當 $V_{GS} > V_T$ ，(a)小 $V_{DS}$ 值、(b)較大的 $V_{DS}$ 值、(c)  $V_{DS} > V_{DS(sat)}$ 的值、(d)  $V_{DS} > V_{DS(sat)}$ 的值時的截面及 $I_D$ - $V_{DS}$ 圖。[44]

### 1.2.2 薄膜電晶體之結構與元件特性：

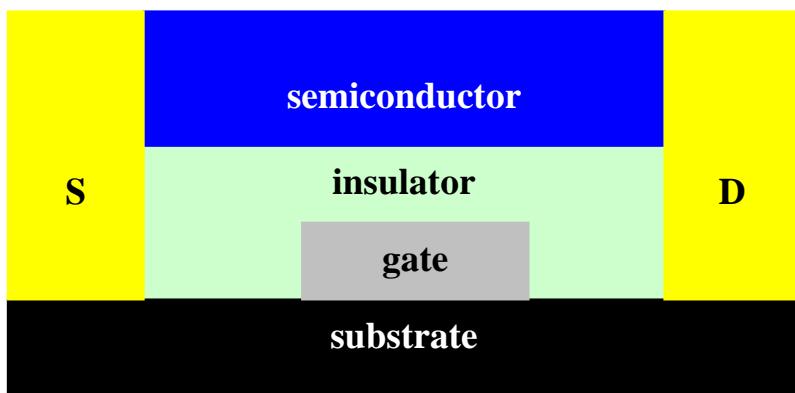

薄膜電晶體(Thin Film Transistors, TFTs)跟場效電晶體的電流特性和驅動方式非常的類似，比較大的差異在於元件的結構，圖1.4是薄膜電晶體結構圖。跟傳統MOS場效電晶體比較的話，可發現多了基板的部份，因為多了基板的部份，所以我們可以選擇想要的材料來做為基板，例如：為了透光性，所以選擇透明玻璃當做基板；為了可撓性，可以選擇塑膠材料當做基板。無機薄膜電晶體通常應用在主動式矩陣液晶平面顯示器的開關電路，基板通常都是選擇透明玻璃，以薄膜的方式製作在玻璃基板上。

圖1.4 薄膜電晶體結構圖

製程上的差異更加明顯、重要，MOSFET的基底需要經由摻雜三族跟五族的元素，才可以提升其導電性，摻雜的方式有兩種：(1)熱擴散(Thermal Diffusion)，缺點是製程溫度會高達900°C；(2)離子佈值(Ion Implantation)，缺點是製作成本會相對的提高，在製程上需要更多道光罩(Mask)以黃光微影(Photolithography)的方式來定義圖案(Pattern)；TFTs在製作上不需要太多道光罩，製程明顯比MOSFET簡單，半導體層通常是選用低溫製作的多晶矽和非晶矽，因為低溫製作所以在基板的選擇就更少限制，可以選塑膠來當可撓性元件的基板。MOSFET在載子遷移率方面，以本質Si當做基板的 $\mu_n$ 通常高達 $1350\text{cm}^2/\text{Vs}$ ，而 $\mu_p$ 也有 $480\text{cm}^2/\text{Vs}$ ，若經

過摻雜則遷移率更高；而TFTs常使用的主動層有多晶矽與非晶矽兩種，前者載子移動率可達 $200\text{-}300\text{cm}^2/\text{Vs}$ ，後者大概只有 $1\text{cm}^2/\text{Vs}$ ，因為遷移率不高，限制了TFTs的應用，目前多應用在平面顯示器。

### 1.2.3 有機薄膜電晶體發展史：

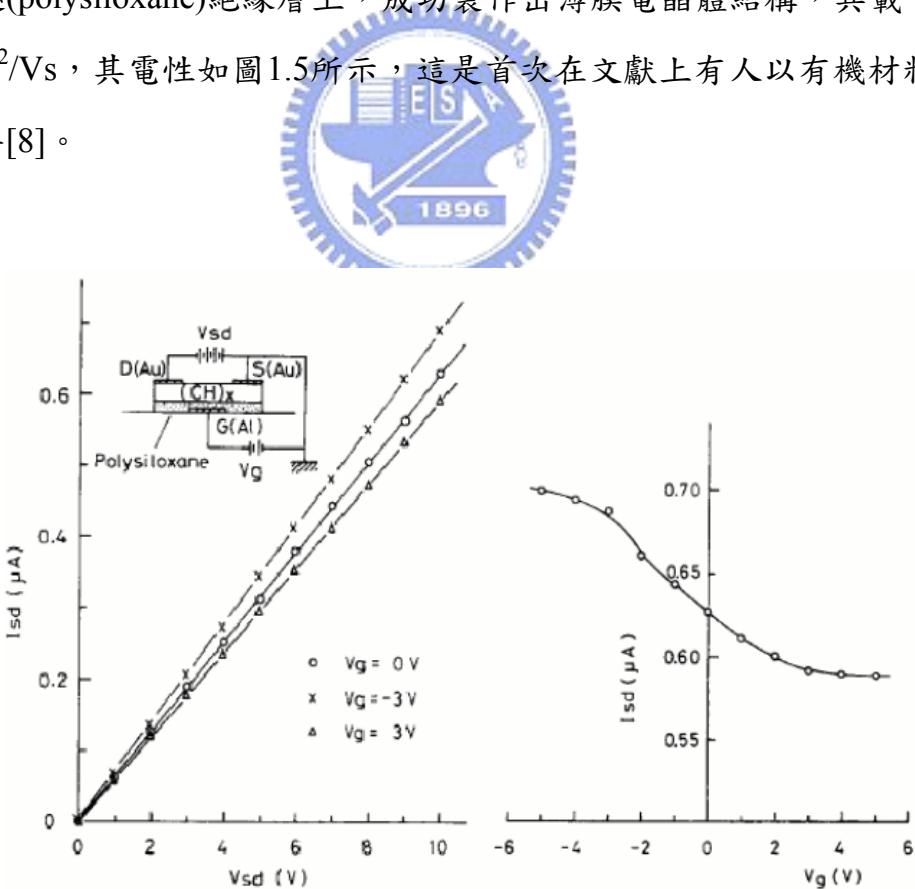

在1977年Macdiarmid等人發現以碘蒸氣摻雜聚乙炔(Polyacetylene)可使其導電度大幅提昇後，開始了有機材料的研究，也因此有了以有機半導體取代無機半導體的想法，以有機材料當作半導體層的元件稱為有機薄膜電晶體(Organic Thin Film Transistors, OTFTs)。第一顆OTFTs在1983年由F. Ebisawa等人發表在國際期刊Journal of Applied Physics中，將聚乙炔(polyacetylene)半導體高分子層直接成長在聚矽醚(polysiloxane)絕緣層上，成功製作出薄膜電晶體結構，其載子遷移率小於 $10^{-5}\text{cm}^2/\text{Vs}$ ，其電性如圖1.5所示，這是首次在文獻上有人以有機材料作為主動層的元件[8]。

圖1.5 1983年發表在國際期刊的第一顆OTFT電性圖[8]

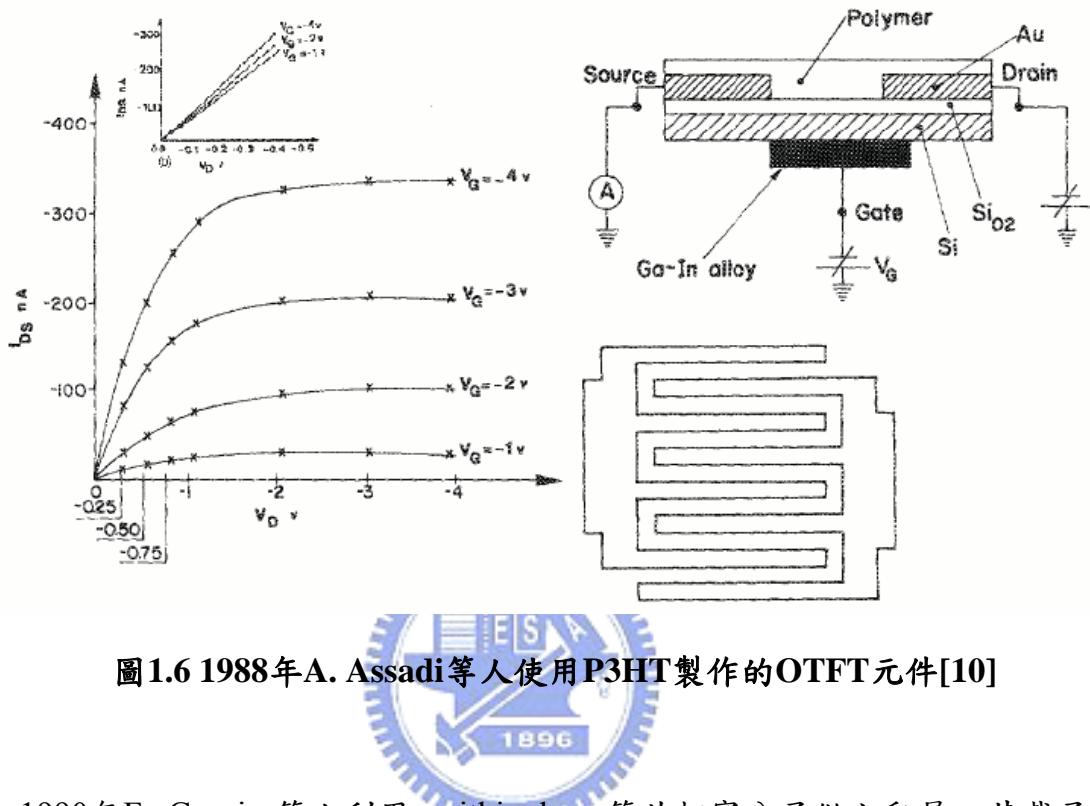

1986年的A. Tsumura等人率先使用polythiophene作為電晶體的主動層，其載子遷移率為 $10^{-5}\text{cm}^2/\text{Vs}$ [9]。1988年A. Assadi等人使用高分子poly(3-hexylthiophene)作為OTFT的主動層[10]，其元件結構與電性如圖1.6所示。

圖1.6 1988年A. Assadi等人使用P3HT製作的OTFT元件[10]

1990年F. Garnier等人利用sexithiophene等共軛寡分子做主動層，其載子遷移率可達 $10^{-1}\text{cm}^2/\text{Vs}$ [11]，這已經可以和非晶矽TFT互相比較了。

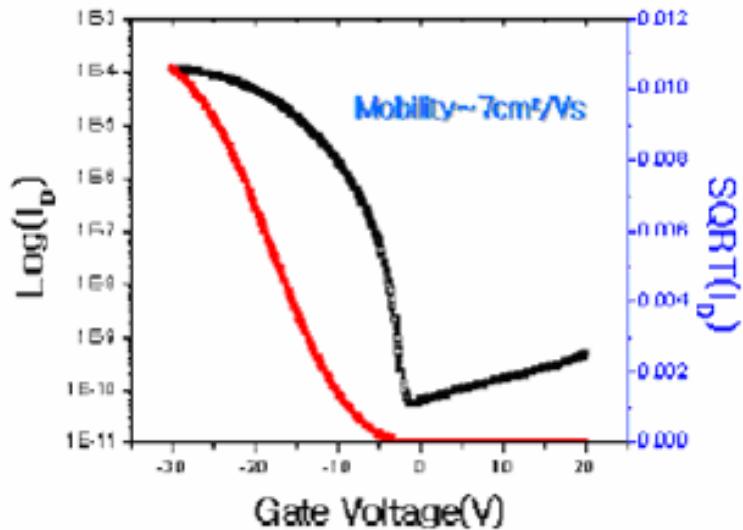

在1992年小分子五環素(pentacene)開始被應用於OTFTs[12]，第一顆以pentacene作為主動層的元件，其載子遷移率為 $2 \times 10^{-3} \text{ cm}^2/\text{Vs}$ 。pentacene是藉由熱蒸鍍的方式沉積，電流傳輸是靠電洞，是目前眾多有機分子中最受矚目的材料，製作的電晶體特性也是所有有機分子中表現最佳的，其載子遷移率比高分子還要大十倍以上，例如1997年Y.-Y. Lin等人[13]利用兩段式基板溫度的條件蒸鍍pentacene，並得到 $1.5\text{cm}^2/\text{Vs}$ 的載子牽移率以及相當高的電流開關比(on-off ratio)等優異的元件特性，此文章的發表也意謂著pentacene TFT在載子遷移率方面已開始超越了a-Si:H TFT。到2005年M. P. Hong等人在SID研討會上發表的top-contact OTFT，利用新合成的絕緣層材料S4(polysilicon-acrylate with titanium complex)，

以 pentacene 作為主動層材料，電極則是使用金，其載子遷移率已高達  $7\text{cm}^2/\text{Vs}$ [14]，如圖1.7所示。

圖1.7 Mobily達 $7\text{cm}^2/\text{Vs}$ 的OTFT元件電性圖[14]

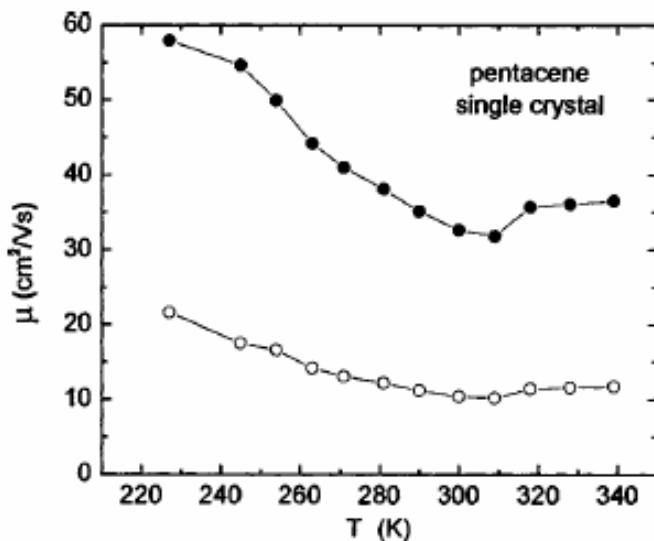

在2004年由Oana D. Jurchescu等人發表在Appl. Phys. Lett.的期刊，經由真空昇華(vacuum sublimation)去除6,13-pentacenequinone，降低了捕捉的陷阱數，在室溫載子遷移率已可達到 $35\text{cm}^2/\text{Vs}$ ，在225K時載子遷移率已可達到 $58\text{cm}^2/\text{Vs}$ ，如圖1.8所示。[15]

圖1.8 Mobily在室溫高達 $35\text{cm}^2/\text{Vs}$ 的載子遷移率對溫度關係圖[15]

#### 1.2.4 有機薄膜電晶體之相關製程：

從一開始介紹的金氧化半場效電晶體到無機薄膜電晶體，緊接著有機薄膜電晶體，這趨勢是成本減少、製程溫度降低以及製程步驟簡易，但載子遷移率也隨著降低、操作電壓上升以及電流開關比不高，這都顯示著必須尋找有更高載子遷移率的主動層、絕緣特性更佳的絕緣層以及利用合成的新材料，來提升元件特性。在新材料被發現以前，許多研究與技術的改良都可以使pentacene TFT在電性上獲得提升。

在製程方面的變化，以半導體跟電極沉積順序的不同分成兩種：底電極(Bottom Contact)與頂電極(Top Contact)，如圖1.9所示。

圖1.9(a)底電極(Bottom Contact)與(b)頂電極(Top Contact)

Bottom Contact的結構，由圖可以看出在製作元件時是先成長電極的部份，之後再上半導體層，Top Contact剛好相反，是先半導體層再後上電極的部份。這兩種結構不管是在電性上的表現或是製程方面都是不同的。以電性來說，top contact的元件特性會比bottom contact好，因為bottom contact先成長電極，而靠近電極附近是一個直角，因為沉積的介面不好而影響了pentacene的成長，此時接面電阻會變大，進而影響元件特性。若經由製程不同來探討此兩種結構差異性，top contact因為先成長了有機材料，所以很難使用微影蝕刻的方式來定義圖案，會因此破壞有機層，因此top contact多是利用shadow mask來定義通道長度，但若經由shadow

mask的方式很難達到小線寬(上限為40um)，因此如果希望元件尺寸做小的話，則需要使用 bottom contact的結構，可以利用微影蝕刻的方式定義我們電極的圖案，之後再將有機層沈積上去，如此就可以達到小線寬又不會破壞有機層。

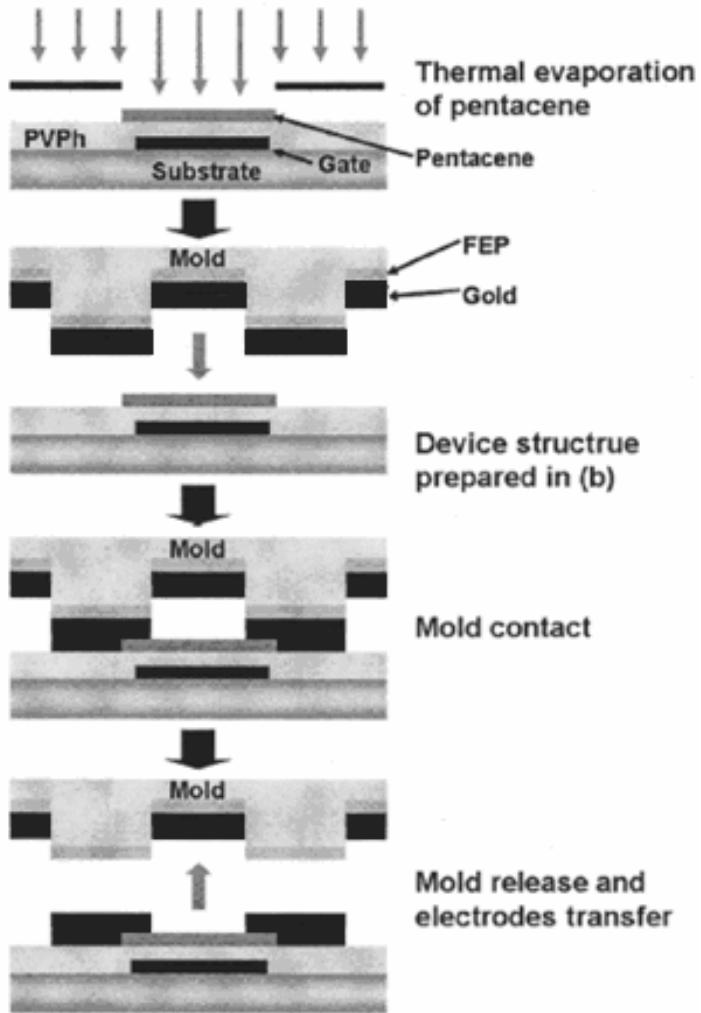

除了這兩種方式，最近幾年有人研究出利用接觸轉印(contact printing)的方式來製作出小通道長度的OTFTs[16]。如圖1.10所示。

圖1.10 用contact printing的方式製作小線寬top contact OTFT

轉印方法簡述如下：(1)先蒸鍍pentacene，(2)在poly(dimethyl siloxane)(PDMS)上製作出圖形(上面的圖形可使線寬小至10um以下)，接著沈積fluorinated ethylene propylene(FEP)在PDMS的模型上，作為PDMS和金屬間的緩衝層，之後再沈積金屬於FEP上面，(3)接著再將整個PDMS的模型壓印在元件上面，隨後經由加熱，

就可有效將PDMS模型和金屬電極分離完成我們的元件，如圖1.9所示。利用contact printing可以製作出小通道長度的元件，又保有top conatct的結構，如此可得到較好的元件特性，又達到小線寬的目的。

### 1.3 有機半導體材料簡介：

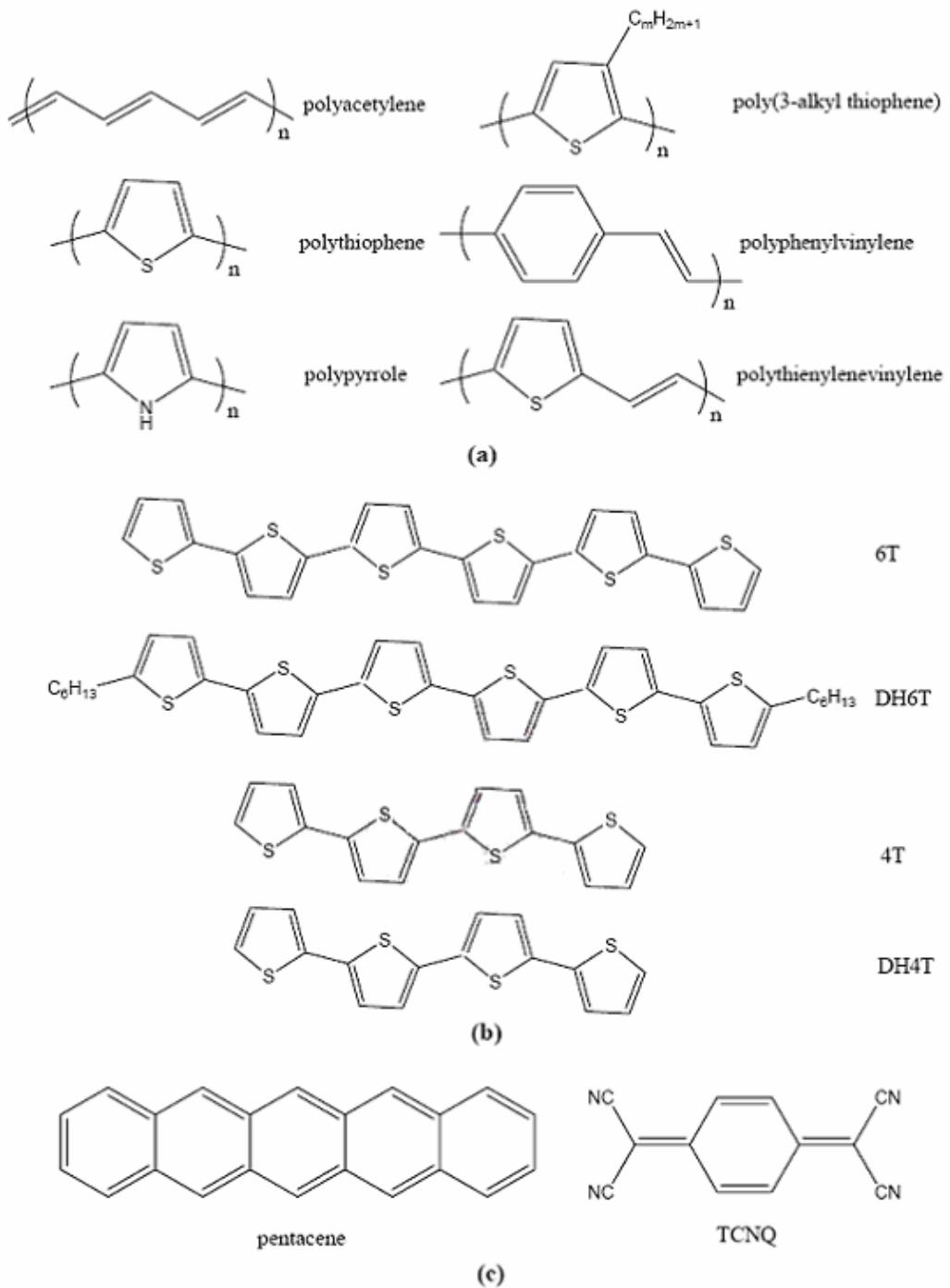

較常被應用於OTFT當作有機半導體的材料有：高分子(polymer)、寡分子(oligomer)和小分子，如圖1.11所示。

圖1.11 有機半導體材料 (a) 高分子 (b) 寡分子 (c) 小分子。

### 1.3.1 高分子(polymer)：

共軛高分子最早被應用於薄膜電晶體製程的有機材料，是以旋轉塗佈的方式來製作半導體層，例如polythiophene[17、18、19、20]、polyacetylene[21、22]等。因為高分子具有較高的黏度，所以比小分子更適用於旋轉塗佈的方式。由於是經由旋轉塗佈的方式，所以溶解度不可以太差，為了提升溶解度，可以在高分子主鏈上加入取代基。例如：poly(3-alkyl thiophene)其烷基側鏈的目的在於使高分子本身具有更好的溶解度。最近利用浸泡(dip-coating)的方式讓厚度維持在2-4nm，載子遷移率已可達 $0.2\text{cm}^2/\text{Vs}$ [23]。使用高分子當主動層的優點是可使用噴印(ink-jet printing)和旋轉塗佈(spin-coating)的方式，但是材料的純度將會增加捕捉載子的陷阱的數目(charge-trapping sites)，使得元件載子遷移率下降。

### 1.3.2 寡分子(oligomer)：

從3T(terthiophene)到8T(octithiophene)，而其中以4T(quaterthiophene)與6T(sexithiophene)及它們末端 $\alpha$ ， $\beta$ -二己基衍生物的表現最好。但由於溶解度並不佳，因此在製程上多採用真空蒸鍍。

### 1.3.3 小分子：

高分子利用旋轉塗佈的方式會扭曲結構降低元件特性，而小分子藉由熱蒸鍍的方式使得分子間排列更為整齊。也由於小分子在電性上的表現最好，所以相關的研究也越來越多，近年來小分子新材料陸續被發表；除了最受歡迎的pentacene[24-28]，還有C<sub>60</sub>[29、30]、phthalocyanine、金屬錯合物(ScPc2、LuPc2、TmPc2、NiPc、ZnPc等)[31-33]以及TCNQ(tetracyanoquinodimethane)[34、35]等。

## 第二章 動機與原理

### 2.1研究動機與目的：

目前對於有機元件的探討往往著重在載子遷移率，對於元件臨限電壓(threshold voltage,  $V_T$ )與啟動電壓 (turn-on voltage,  $V_{to}$ )的相關探討相對的比較少。因此本篇論文利用不同的聚合物經由旋轉塗佈的方式修飾無機的基板( $\text{SiN}_x$ )，發現基板經由一層薄薄的有機聚合物修飾後，元件的特性就會有明顯的改變，除了電流-電壓特性曲線以外，也引入了電容-電壓特性曲線。在電容-電壓的探討大部分的文獻還是利用無機的觀念解釋，但事實上在有機的電容-電壓曲線代表的意義已經跟無機不同，而臨限電壓在有機電晶體中也不具任何意義，這也是這篇論文探討的重點。此篇論文的探討，將可以更了解在不同修飾的情況下，表面狀態是否會影響五環素的排列方式，進而影響電荷的填補、累積與傳輸，導致電晶體啟動電壓位移。藉由這篇研究的結果，除了可以更了解電晶體的傳輸機制，進一步利用控制介面特性來調變電晶體的啟動電壓。

## 2.2 有機材料的導電機制：

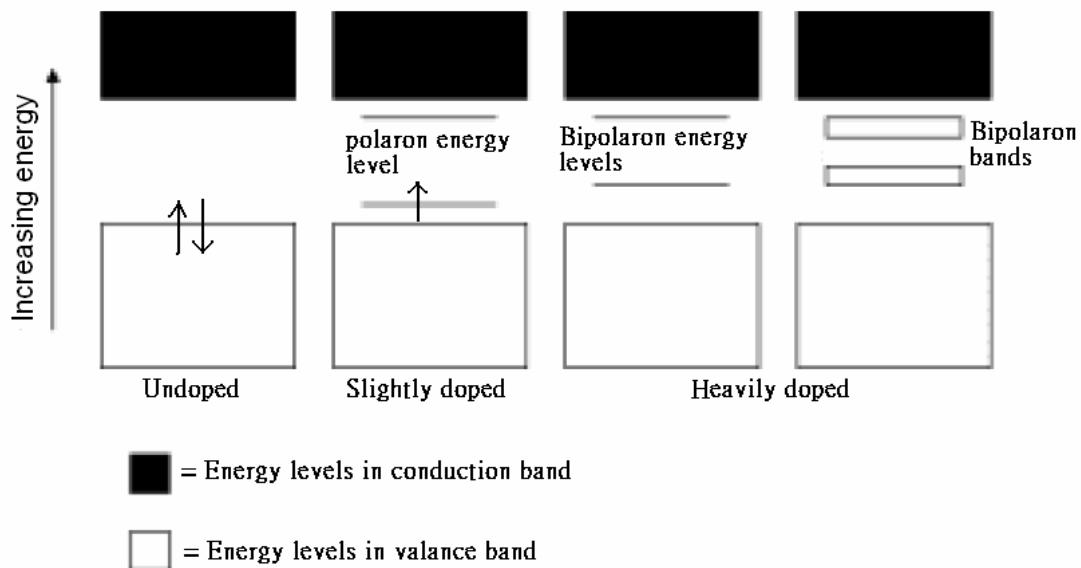

### 2.2.1 偏極子(polaron)的形成[36]

有機材料中分子與分子之間的作用力是以微弱的凡德瓦力(Van der Walls forces)束縛在一起，這與無機半導體分子間的共價鍵是不同的，所以有機的導電機制與無機半導體是有很大的差異。一般有機半導體的導電機制可用偏極子(polaron)的理論來解釋，如圖2.1所示。當一個電子從共軛高分子中移走時，相當於產生一個電洞，此電荷會與週遭晶格產生劇烈的耦合，此耦合效應使得能階產生變化，這個與週圍晶格有強大作用的電荷，我們即稱為偏極子(polaron)。此時若再將另一電子移走，則可能在分子鏈上產生另一個偏極子，也可能從原先的偏極子再次移走電子而形成雙偏極子(bipolaron)，雙偏極子所形成的能階(bipolaron energy level)較偏極子所形成的能階(polaron energy level)來的高，若形成較多的雙偏極子就有如高度摻雜一樣，則其能量在能帶邊緣處重疊使在導帶與價帶之間形成狹窄的雙偏極子能帶(bipolaron bands)，且 polaron 與 bipolaron 皆可藉由外加電場於能帶之間移動而傳導電荷。

圖 2.1 能帶中 polaron 的產生機制示意圖

## 2.2.2 傳輸模型

### **Hopping Model[36]**

電子的分佈可分成局部狀態（Localized States）和非局部狀態（Delocalized States）。局部狀態的定義是指電子只專屬於某一特定的原子，相反的則稱為非局部狀態。以 $\pi$ 鍵來說明局部狀態跟非局部狀態， $\pi$ 鍵是原子之間分享電子的一種鍵結，如果從原子和原子之間的 $\pi$ 鍵找出額外之電子，而此電子和鍵結並沒有直接關係，我們就稱此電子處於非局部狀態。

在金屬和一般的半導體中，載子的傳輸都是非局部狀態，少部分是靠聲子的散射，而熱引起晶格變形，但這樣的理論不再適用於低導電度材料。以有機半導體和非晶矽半導體來說，載子的平均自由路徑會比平均分子距離短。在這些材料中載子的傳輸是藉由在局部和非局部狀態之間hopping。局部和非局部在傳輸上最大的差異在於非局部是有限的聲子散射；反之，局部的是藉由聲子促進。在一般的半導體材料，載子遷移率隨著溫度降低，但相反的狀況卻發生在大部分的有機材料，在許多的例子裡面，載子遷移率和溫度的關係式如下：

$$\mu = \mu_0 \exp\left[\left(-\frac{T_0}{T}\right)^{\frac{1}{\alpha}}\right] \quad (2-1)$$

其中 $\alpha$ 是介於1~4中間的整數。介於非局部和局部狀態的過程，載子遷移率在 $0.1\sim 1\text{cm}^2\text{V}^{-1}\text{s}^{-1}$ 之間，排列的很整齊的分子晶格的載子遷移率是很接近這個值。不管這些材料的導電度如何，應該要用局部性或非局部性傳輸來描述仍是有爭議的。

### Multiple Trapping and Release Model (MTR) [36] :

在MTR模型中假設有一條窄小的非局部之能帶，而此能帶的產生是跟高密度的局部能階有相關連，其功用就像是陷阱捕捉(Traps)。當傳輸過程經過非局部能階時，電荷載子會跟局部能階互相影響藉由捕捉和熱釋放的方式。通常我們會有以下的假設：第一，當載子傳達到一個缺陷時會有機率接近為1的機會被捕捉住，第二，捕捉住的載子釋放是由一個熱活化的過程(Thermally Activated Process)所控制。而所造成的漂移率(Drift Mobility,  $\mu_D$ )會跟非局部能階的載子移動率( $\mu_0$ )有關，可以表示成方程式2-2：

$$\mu_D = \mu_0 \alpha \exp\left(-\frac{E_T}{kT}\right) \quad (2-2)$$

$E_T$ 為缺陷能階，如果發生在單一個缺陷能階， $E_T$ 缺陷能階和非局部化能帶的邊緣距離有關，而 $\alpha$ 是在非局化邊緣有效之狀態密度和缺陷濃度的比率。MTR模型目前最常被使用來計算在非晶矽裡面的電荷傳導。

## 2.3 五環素(Pentacene)材料之簡介：

在小分子有機材料裡面最受重視的半導體材料五環素(pentacene)，其分子結構如圖 2.2 所示，在 1961 年 Campbell 和 coworkers 確定了 pentacene 的結構 [37]。pentacene 基本上是一種 p 型有機半導體材料，化學式為  $C_{22}H_{14}$ ，密度  $1.2\text{g/cm}^3$ ，分子量為 278.35，一個 cell 的體積大概是  $705\text{ \AA}^3$ ，介電常數是 4 [38]，電子親和力大概是 2.49eV，熔點大約在  $300^\circ\text{C}$  左右 [39]，外觀為深藍色的粉末，必須保存在封閉乾燥陰暗的空間下，避免受水氣、氧氣以及光的影響與破壞。

圖 2.2 Pentacene 的化學結構圖，由五個苯環所組成，又稱五環素。

以 X 光繞射圖來分析 pentacene 於基板上的結晶情況，Pentacene 具有兩種相 (phase)，第一種稱為 thin film phase，第二種為 bulk phase 或是 single crystal phase，如圖 2.3 所示。

圖 2.3 pentacene 之 X-ray 相關繞射峰。[40]

Pentacene具有兩種排列方式，第一種稱為thin film phase，第一根繞射峰位於 $5.83^\circ$ ，之後每隔 $5.83^\circ$ 就會有peak，分別位於 $5.83^\circ$ 、 $11.7^\circ$ 、 $17.6^\circ$ 等，定義為 $(001)'$ 、 $(002)'$ 、 $(003)'$ ；第二種稱為bulk phase或是single crystal phase，第一根peak位於 $6.2^\circ$ ，之後每隔 $6.2^\circ$ 就會有peak，分別位於 $6.2^\circ$ 、 $12.4^\circ$ 、 $18.6^\circ$ 等，定義為 $(001)$ 、 $(002)$ 、 $(003)$ 。藉由公式的計算，可以知道在thin film phase中層與層的間距(d-spacing)為 $14.5\text{ \AA}$ ，而bulk phase的d-spacing為 $15.4\text{ \AA}$ ，由計算結果可知thin film phase的pentacene傾向於垂直基板表面排列，而bulk phase相較之下則較為傾斜。除此之外還有另外兩種比較不常見的排列方式，層與層的間距為 $14.1\text{ \AA}$ 和 $15.0\text{ \AA}$ ，排列方式主要是由基板的條件決定。[41、42]

## 2.4 有機薄膜電晶體的載子移動率：

在有機材料中載子是處於局部化的狀態，電子與電洞不能夠自由移動，所以有機薄膜電晶體的載子遷移率並不高，這也限制了它的應用。近幾年由於學者盡力的研究與討論，累積出來的經驗與製作技術不斷的改進，有機材料的載子移動率已經有相當大的改進，如圖2.4所示。

圖2.4 從1984年至今的OTFT mobility進展趨勢[43]

由圖2.4可以觀察到有機材料的載子遷移率在近幾年來有快速成長的趨勢，利用pentacene這個有機材料當作半導體層所做出來的元件載子遷移率已經可以跟非晶矽相提並論，未來隨著製程技術的進步，學者預測在2008年後，其載子移動率可以和多晶矽達到同一等級，相對的這也提高了有機薄膜電晶體的應用層面。

## 2.5 有機薄膜電晶體的操作模式：

### 2.5.1 MOSFET (金氧半場效電晶體)：

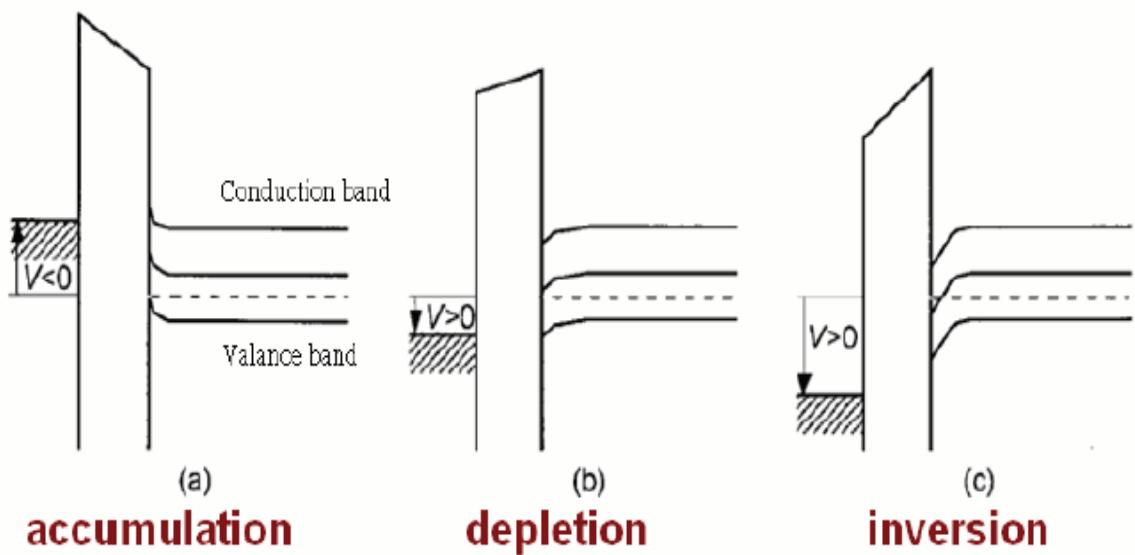

P型半導體金氧半導體(metal-oxide-semiconductor)電晶體的能帶示意圖，如圖2.5所示[43]。在閘極(Gate)外加足夠大的正偏壓時，P型半導體在與絕緣層介面處形成反轉層(inversion layer)即為N型的通道，此時電晶體開啟，當閘極不施加電壓或施加一負偏壓時，在介面處則是形成空乏區呈現關閉狀態。

圖2.5 金氧半接面能階隨閘極電壓的變化[36]

## 2.5.2 有機電晶體：

不同於矽電晶體的操作模式，有機電晶體是利用有機半導體中多數載子，在絕緣層介面處形成累積層(accumulation layer)，以利於載子的傳輸。若我們選用 pentacene 作為有機半導體層，則介面處是累積一層以正電荷為主要的通道。圖 2.6 顯示以電洞為傳輸載子的有機電晶體元件在各種操作電壓下的電荷分佈，當  $V_D$  、  $V_G$  、  $V_S$  均不加偏壓時圖 2.6(a) 並未有載子累積現象，而圖 2.6(b) 中當  $V_G$  外加正偏壓時半導體/介電層介面處形成空乏區。

圖 2.6 有機場效電晶體操作機制示意圖[44]

圖 2.6(c) 中  $V_G$  外加負偏壓使半導體/介電層之間有電洞累積形成累積層，此時若  $V_D$  外加負偏壓則載子便由源極注入半導體流至汲極，當  $V_D$  小於  $V_G$  的時候，電晶體操作在線性區，此時由於累積電荷的累積形式好比一方塊形電阻，故元件電流-電壓關係符合歐姆定律。圖 2.6(d) 當中的  $V_D$  負偏壓逐漸增強，汲極端的累積電荷量變少，電壓與電流之間不再是線性關係，直至  $V_D$  的負偏壓加至大於  $V_G$  時，汲極區便形成如圖 2.6(e) 所示的空乏區，電流則不再隨  $V_D$  的增加而變大，即為進入飽和區。

## 2.6 各項重要參數：

有機薄膜電晶體的重要參數在多數文獻上仍延用p型場效電晶體公式來求得，計算方式依序如下：

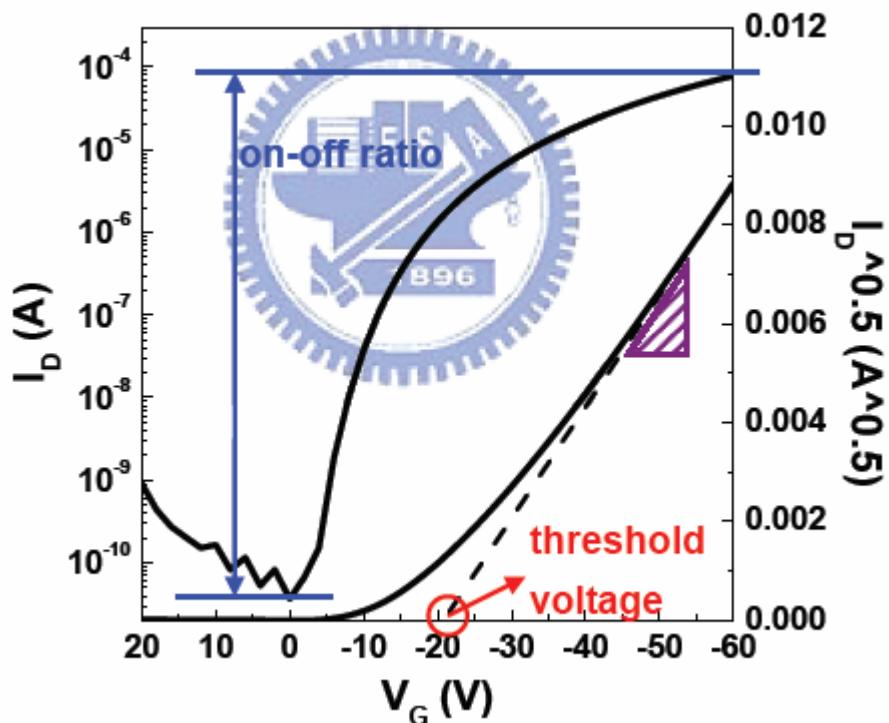

### 2.6.1 輽子遷移率 (mobility)：

在外加電場的影響下，電子或電洞在導體或半導體中傳輸的速度，稱為載子遷移率(mobility)。一般有機薄膜電晶體仍是採用標準的p型場效電晶體公式來描述，取得mobility值的方式分成線性區和飽和區兩種：

#### 線性區

線性區就是在汲極電壓 $V_D$ 很低時，汲極電流 $I_D$ 是隨著 $V_D$ 呈線性的增加，其電流值可用式2-3來表示：

$$I_D = \frac{WC_i}{L} \mu \left( V_G - V_T - \frac{V_D}{2} \right) V_D \quad (2-3)$$

$V_D$ 很小，所以 $V_D^2$ 可以忽略，得到2-4式

$$I_D = \frac{WC_i}{L} \mu (V_G - V_T) V_D \quad (2-4)$$

將 $I_D$ 對 $V_D$ 微分得到

$$\frac{\partial I_D}{\partial V_D} = \frac{WC_i}{L} \mu (V_G - V_T) \quad (2-5)$$

2-5式所得到的微分值即為在一固定 $V_G$ 下電流線性區的斜率，將此斜率再對 $V_G$ 微分，可得

$$\frac{\partial}{\partial V_G} \left( \frac{\partial I_D}{\partial V_D} \right) = \frac{WC_i}{L} \mu \quad (2-6)$$

將斜率對 $V_G$ 作關係圖，可由圖中得到另一線性的斜率，將已知的參數帶入，即可求得線性區的載子遷移率。

## 飽和區

當  $V_D$  大於  $V_G$  時，在累積層的汲極端會產生夾止(pinch-off)的現象，此時電流趨於飽和，即進入飽和區，電流公式如下：

$$I_D = \frac{WC_i}{2L} \mu (V_G - V_T)^2 \quad (2-7)$$

所以取  $|I_D|^{\frac{1}{2}}$  對  $V_G$  關係圖的斜率，即是將 2-7 是兩邊取平方根，得到 2-8 式

$$\sqrt{I_D} = \sqrt{\frac{WC_i}{2L} \mu} (V_G - V_T) \quad (2-8)$$

之後將  $|I_D|^{\frac{1}{2}}$  對  $V_G$  微分，得到 2-9 式

$$\frac{\partial \sqrt{I_D}}{\partial V_G} = \sqrt{\frac{WC_i}{2L} \mu} \quad (2-9)$$

2-9 式的值可由圖 2.7 求得，之後將各項參數代入，即可得到飽和區的場效載子遷移率。

圖 2.7 OTFT 元件參數萃取示意圖

## 2.6.2 臨限電壓(Threshold voltage, $V_T$ )：

在主動層與絕緣層介面間常會存在缺陷，導致載子在傳輸時容易被缺陷所捕獲，此時需要一個較大的電壓( $V_G$ )來將其釋放(或填滿)，直到開始有自由載子流動時，此時的電壓稱為臨限電壓，所以說有較大的缺陷電荷密度，就必須有較大的啟動電壓[45]，此時的電壓亦可視為電晶體開啟的最小電壓值。臨限電壓也分成線性區跟飽和區兩種：

理論上有幾種得到臨限電壓的方式：

1. 當電晶體操作於線性區時，對  $I_D$ - $V_G$  圖形作微分，便可得到  $g_m$  圖形，在  $I_D$ - $V_G$  圖中，在  $g_m$  最大值時的  $V_G$  作切線，找出  $y=0$  相交，便可推出交點  $V_G=V_T+V_D/2$ 。

$$I_D = \frac{WC_i}{L} \mu \left( V_G - V_T - \frac{V_D}{2} \right) V_D \quad (2-10)$$

$$g_m = \left( \frac{\partial I_D}{\partial V_G} \right)_{V_D=\text{const}} = \frac{WC_i}{L} \mu V_D \quad (2-11)$$

2. 當電晶體操作在飽和區(saturation region)時，電流公式為式2-7，對其開根號，即成為式2-8，此時可發現  $I_D^{\frac{1}{2}}$  跟對X軸( $V_G$ )交點即是臨限電壓。

$$\sqrt{I_D} = \sqrt{\frac{WC_i}{2L} \mu (V_G - V_T)} \quad (2-12)$$

### 2.6.3 電流開關比(on-off ratio, $I_{on}/I_{off}$ )比：

在累積模式中，有高濃度的載子累積在元件通道，比較小的通道電阻，因而有最大的電流稱之為”on state”；而在空乏模式中，通道附近的載子被排開形成空乏區，造成較大的通道電阻，因而有最小的電流稱之為”off state”，而最大電流和最小電流比我們稱之為on / off ratio。由圖2.7可看出on-off ratio的定義，on-off ratio值越大代表對比愈明顯，當有較小的漏電流( $I_{off}$ )時，也可獲得較大的on-off ratio，所以此值是有機薄膜電晶體可不可以應用於電子產品的一項重要依據。

### 2.6.4 次臨界擺幅 (Subthreshold swing (s.s.))：

次臨界擺幅的定義為在形成通道時，元件啟動(turn on)的速度，值可由下式得到：

$$S.S. = \left( \frac{\partial(\log(I_D))}{\partial V_G} \right)_{V_D=\text{const}} \quad \text{when } V_G > V_T$$

此值越大代表電壓變化一點，電流就可以大幅的提升，也代表從off狀態到on的狀態可以很明確快速。

### 2.6.5 啟動電壓(turn on voltage, $V_{to}$ )：

此值是代表在元件打開後，電流呈現指數上升時的閘極電壓值，由於無機是操作在反轉區，而有機是操作在累積區，所以臨限電壓在有機並沒有特別的意義，於是我們定義了新的名詞 $V_{to}$ 代表電晶體的啟動電壓。

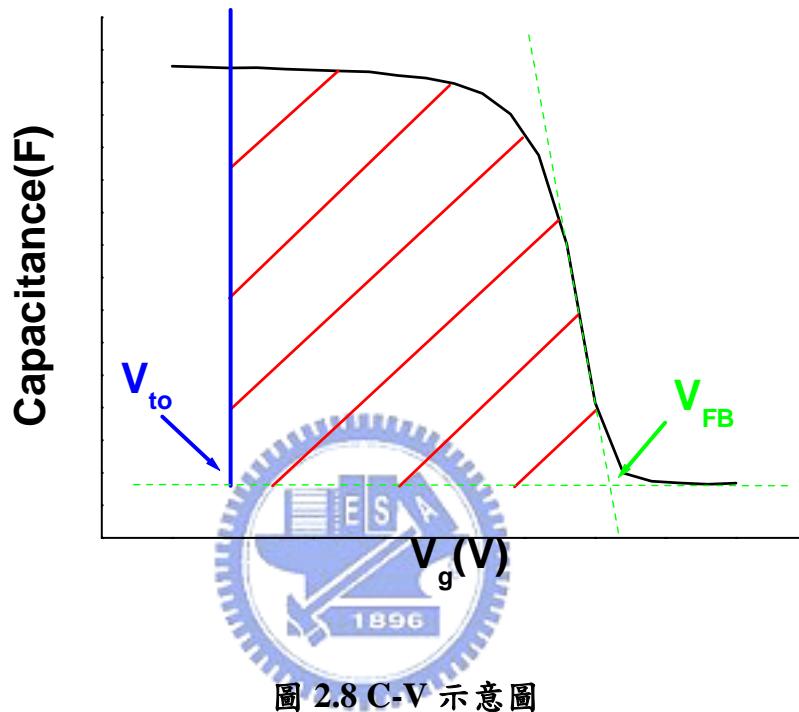

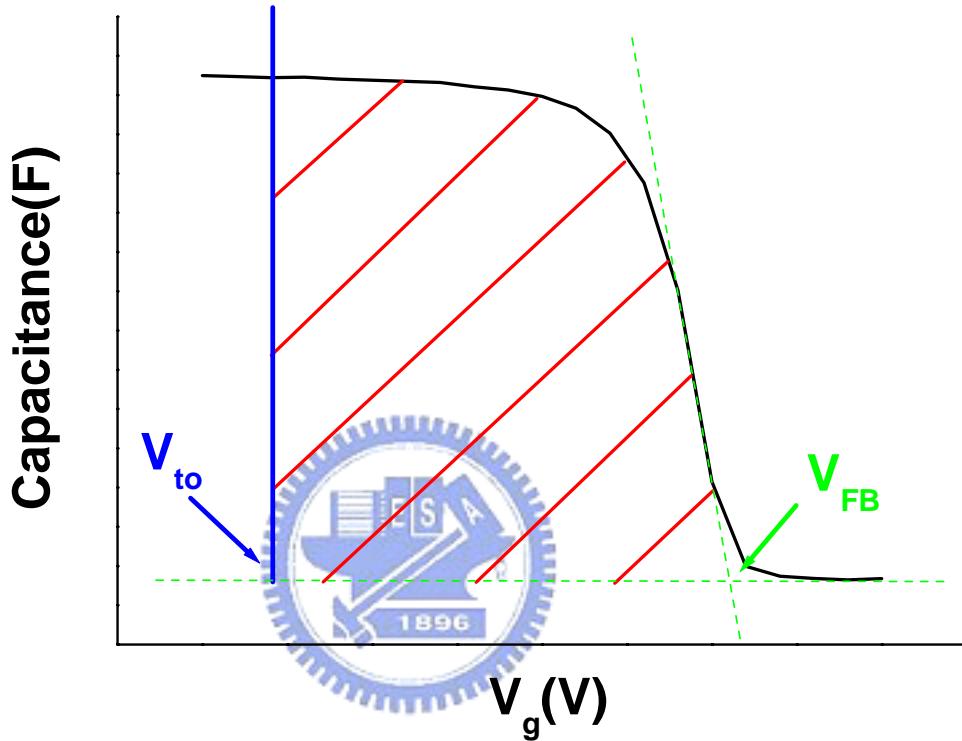

## 2.6.6 平帶電壓( $V_{FB}$ )[46]：

載子受到絕緣層內部捕捉住的電子吸引，而開始填補捕捉陷阱的電壓值，從圖2.8可以看到 $V_{FB}$ 的定義。有文獻定義 $V_g > V_{FB}$ 稱為空乏區(depletion mode)，而 $V_g < V_{FB}$ 稱為累積區(accumulation mode)。[47]

圖 2.8 C-V 示意圖

## 第三章 實驗架構

### 3.1 實驗流程：

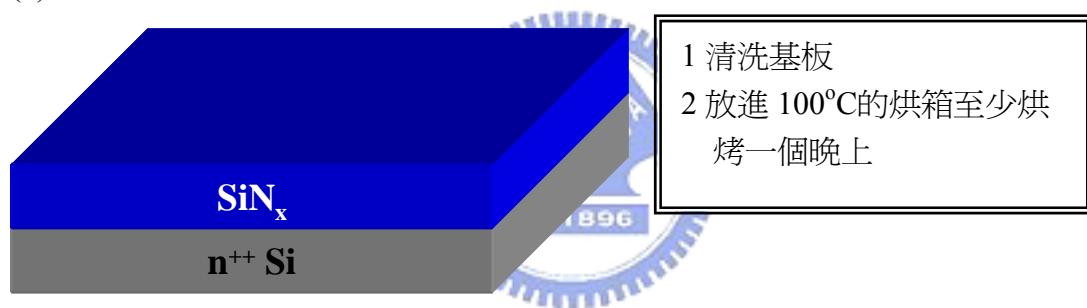

#### 3.1.1 基板

在這篇論文當中所使用的基板包含兩部分

第一部分：經重摻雜的矽(Si<sup>+</sup>)晶圓。經摻雜後變成了高導電度材料，將它使用為元件中的閘極。

第二部份：經熱成長在晶圓上的氮化矽(SiN<sub>x</sub>)，主要的作用是當作無機絕緣層，阻絕漏電流的產生。

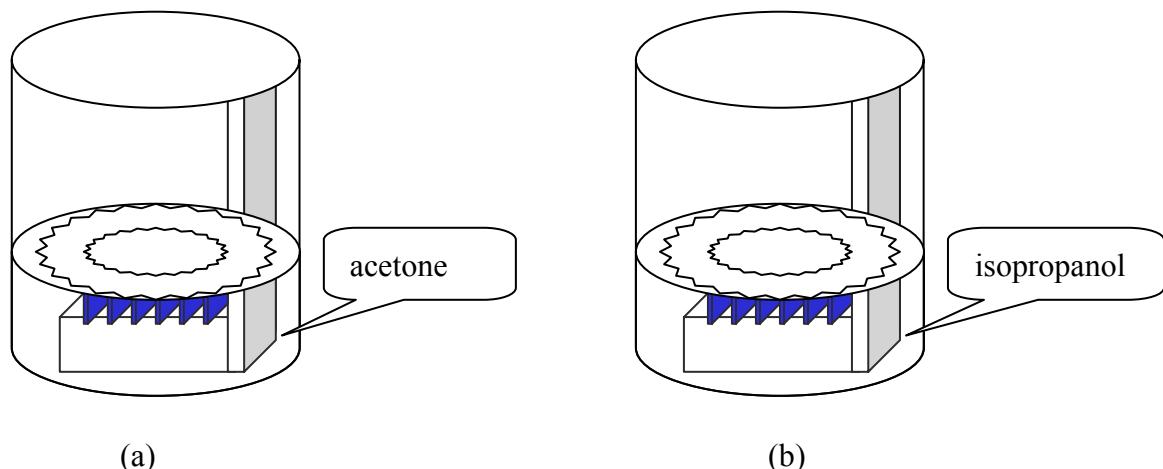

#### 3.1.2 基板清洗：

步驟 1、用清潔劑搓洗基板

步驟 2、用去離子水清洗乾淨

步驟 3、重複上述步驟 1 和步驟 2

步驟 4、將基板整齊排列在鐵氟龍holder上，將holder放入裝有丙酮溶劑的燒杯中，然後將燒杯置入超音波震盪器震盪 20 分鐘，這步驟是為了去除黏附在基板的水與有機物。

圖 3.1 (a)步驟 4 和(b)步驟 5 的示意圖

**步驟5**、將holder取出，將燒杯內溶劑換成isopropanol(IPA)，放置在超音波震盪器震盪20分鐘，此步驟是為了去除丙酮。

**步驟6**、用氮氣槍將基板吹乾，放置在乾淨的玻璃培養皿中。

**步驟7**、將玻璃培養皿放入溫度為100°C的烤箱，直到使用前，以確保基板的乾淨度。

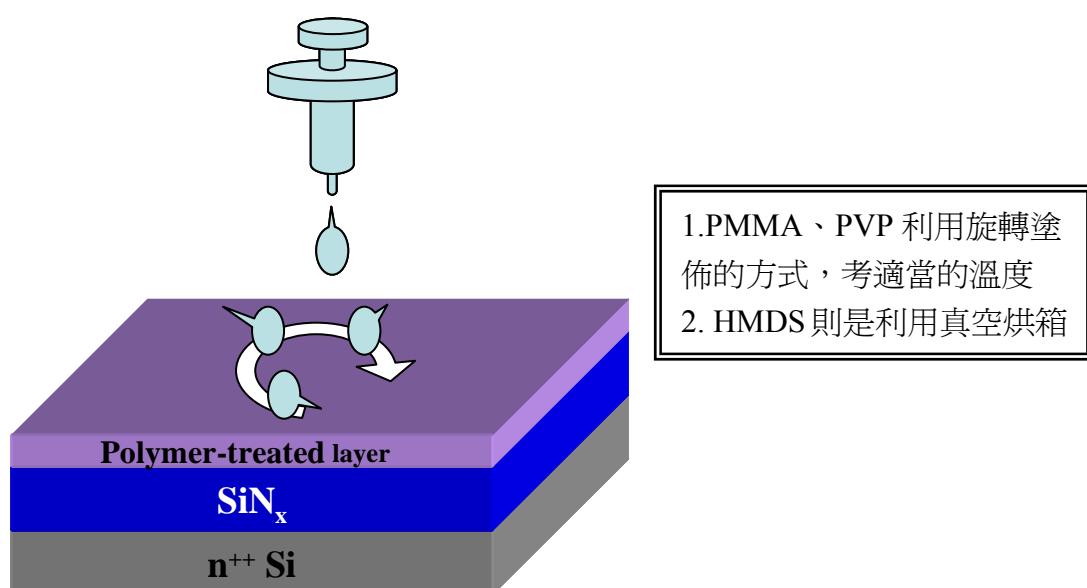

### 3.1.3表面處理：

**材料1：poly-4-vinylphenol (PVP)**

濃度：1wt%、0.4wt%、0.1wt%

溶劑：propylene glycol monomethyl ether acetate (PGMEA)

Cross-linker：poly(melamine-co-formaldehyde) methlated(4wt%)

將溶液弄在基板上的方法：旋轉塗佈(spin-coating)

烤的溫度：120°C，5分鐘；200°C，20分鐘

厚度：20nm、13nm、2~3nm

**材料2：1,1,1,3,3,3-hexamethyldisilazane (HMDS)**

置入HMDS烤箱中，將程式按開啟即可。程式步驟是先抽真空灌氮氣三次，之後抽到高真空的狀態，噴灑HMDS蒸氣，接著烤150°C，然後抽真空，灌氮氣破真空，HMDS成功吸附在基板上。

**材料3：poly-methyl-meth-acrylate (PMMA)**

濃度：1wt%、0.1wt%

溶劑：Toluene(甲苯)

將溶液弄在基板上的方法：旋轉塗佈(spin-coating)

烤的溫度：100°C，30分鐘。

厚度：70nm、7.2nm

上述 3 種材料PVP、HMDS、PMMA 以及未經過修飾的SiN<sub>x</sub>剛好形成 4 種表面特性，藉此來探討有無修飾層對於元件的影響。修飾層的厚度都是藉由原子力顯微鏡(Atomic Force Microscope，AFM)所量測得到之數據。

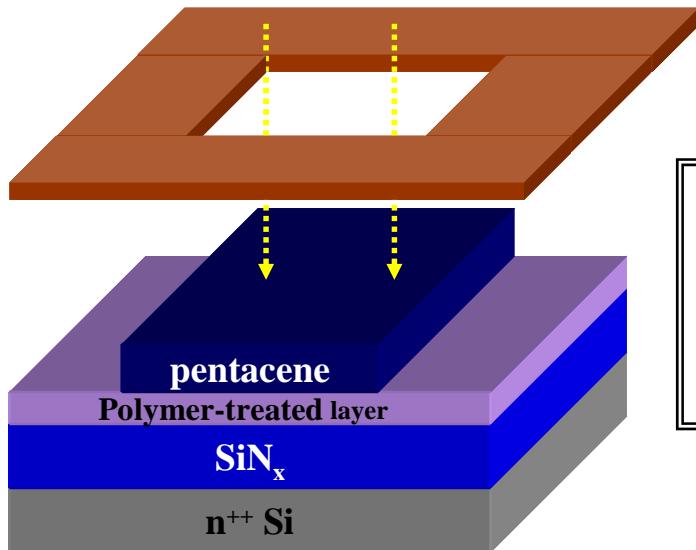

### 3.1.4 主動層及電極的蒸鍍

選用的機台：ULVAC thermal evaporator

主動層材料：99.9% Fluck pentacene

鍍率：0.5 Å /sec (由 quartz oscillator 測得)

真空度： $2.5 \times 10^{-6}$  torr

基板溫度：25°C (由機台內部的 Al-Cr thermocouple 量測)

厚度：60nm

蒸鍍源：將 pentacene 放入特製 BN 坩鍋中

電極材料：金(Au)

鍍率：2~3 Å /sec (由 quartz oscillator 測得)

真空度： $3 \times 10^{-6}$  torr

基板溫度：25°C (由機台內部的 Al-Cr thermocouple 量測)

厚度：40nm

蒸鍍源：將金置於鎢舟上

選金作為電極的理由是金的功函數(5eV)和 pentacene 的 HOMO(5.1eV)比較匹配，蒸鍍主動層和電極是用不同的 mask 來定義圖案，通道寬度(channel width，W)是 2mm，而通道長度(channel lengths，L)分別是 75、100、130 和 160um。然而在蒸鍍過程中，mask 和基板的貼合緊密度造成 Shadow effect 程度大小不一，將會改變通道寬度和長度，故在元件製作後可用光學顯微鏡(Optical Microscope，OM)量測正確的通道長度和寬度。

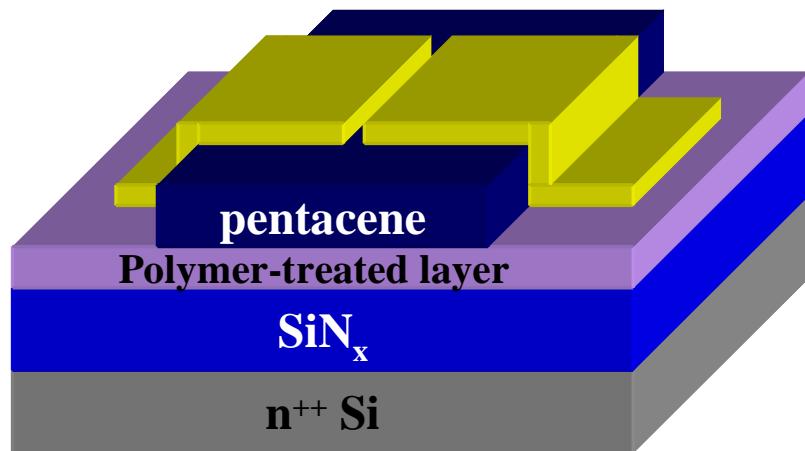

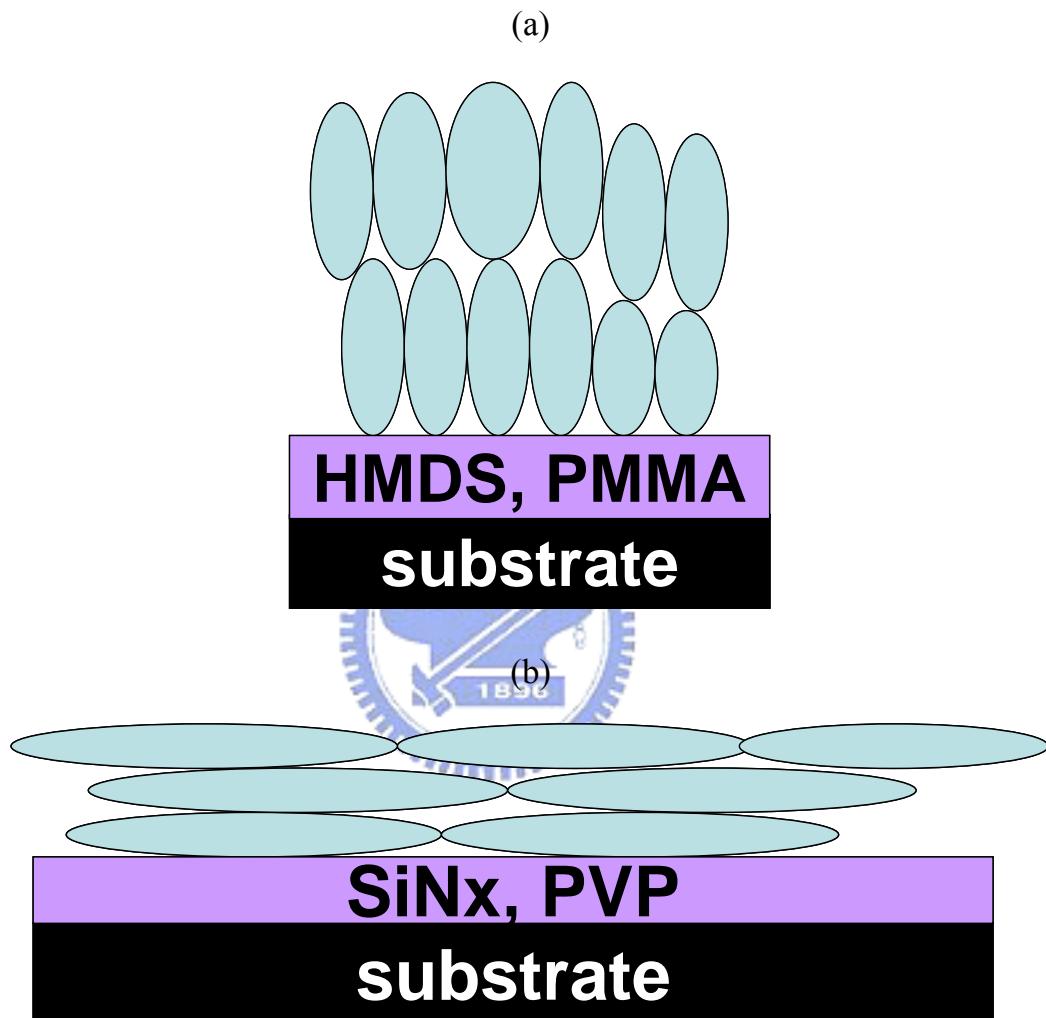

### 3.1.5 元件流程

如圖 3.2 所示，購買n型參雜的矽晶圓來當作元件閘極，再經由高溫爐管成長  $\text{SiN}_x$  作為閘極絕緣層，之後經過切割成實驗必須的元件大小  $2\text{ cm} \times 2\text{ cm}$  的晶片，然後經過清潔劑、丙酮以及IPA的清洗，結構如圖 2.3(a)所示。

清洗結束之後放入溫度設定為  $100^\circ\text{C}$  的烘箱，製作元件之前將基板從烘箱取出放涼，在成長主動層之前，先對  $\text{SiN}_x$  作表面處理，本實驗使用 3 種有機材料來作為修飾層，有PMMA、PVP和HMDS，選用適當溶劑和濃度，經由蒸鍍和旋轉塗佈等方法均勻的鋪在基板上，經過適當溫度的烘烤，去除溶劑的殘留，結構如圖 3.2(b)所示。

(a)

(b)

(c)

利用熱蒸鍍的方式，選取適當的 mask 定義出 pentacene 的區域

腔體壓力： $2.5 \times 10^{-6}$  torr

鍍率： $0.5 \text{ \AA/sec}$

(d)

利用熱蒸鍍的方式，選取適當的 mask 定義出 Au 的區域

腔體壓力： $3 \times 10^{-6}$  torr

鍍率： $2\sim3 \text{ \AA/sec}$

圖 3.2 實驗流程示意圖

接著將烘烤結束的基板放涼，貼在不鏽鋼所製的 mask 上，藉此來定義蒸鍍後 pentacene 的圖案，我們選用的 pentacene 是 Fluck 所製的 P 型有機半導體，取適量放置在坩鍋中，利用 ULVAC 的熱蒸鍍機來蒸鍍，藉由控制環繞在坩鍋外圍的鎢絲電流來調整加熱溫度，進而控制蒸鍍的鍍率，在調整好鍍率穩定在  $0.5 \text{ \AA}$

/sec 之前都可用遮版來阻擋，等到鍍率穩定後開遮版，以鍍率  $0.5 \text{ \AA/sec}$  蒸鍍到厚度為 60nm。

蒸鍍主動層結束後冷卻 10 分鐘後破真空取出元件，將元件貼在電極的 mask 上，將金錠放置在鎢舟上，控制在鎢舟兩端電極的電壓來控制蒸鍍速率，鍍率控制在  $2\text{--}3 \text{ \AA/sec}$  蒸鍍到厚度為 40nm。

### 3.2 實驗儀器：

| 中文名稱<br>(英文名稱)                        | 廠牌型號                                                                                                    | 用途               |

|---------------------------------------|---------------------------------------------------------------------------------------------------------|------------------|

| 真空烘箱(Vacuum Oven)                     | Yield Engineering Systems, YES - 5                                                                      | 蒸鍍 HMDS          |

| 旋轉塗佈機(Spin coater)                    | Chemat Technology, KW-4A                                                                                | 修飾層之旋轉塗佈         |

| 熱蒸鍍機<br>(Thermal coater)              | ULVAC, CRTM-6000                                                                                        | 蒸鍍 pentacene、金和鋁 |

| 電流-電壓量測機台<br>(I-V parameter analyzer) | Keithley 4200                                                                                           | 量測元件基本電性         |

| 原子力顯微鏡<br>(Atomic Force Microscope)   |  DI3100              | 量測薄膜表面形貌、厚度      |

| X 光繞射儀<br>(XRD)                       |  M18 XHF, MacScience | 分析半導體結晶狀況        |

| 接觸角量測儀<br>(Contact angle)             | Kruss Universal Surface Tester, GH100                                                                   | 量測薄膜表面的接觸角與表面能   |

| 電容-電壓量測機台                             | HP4284A                                                                                                 | 量測元件電容值和電容電壓特性曲線 |

### 3.3 原子力顯微鏡操作步驟及原理：

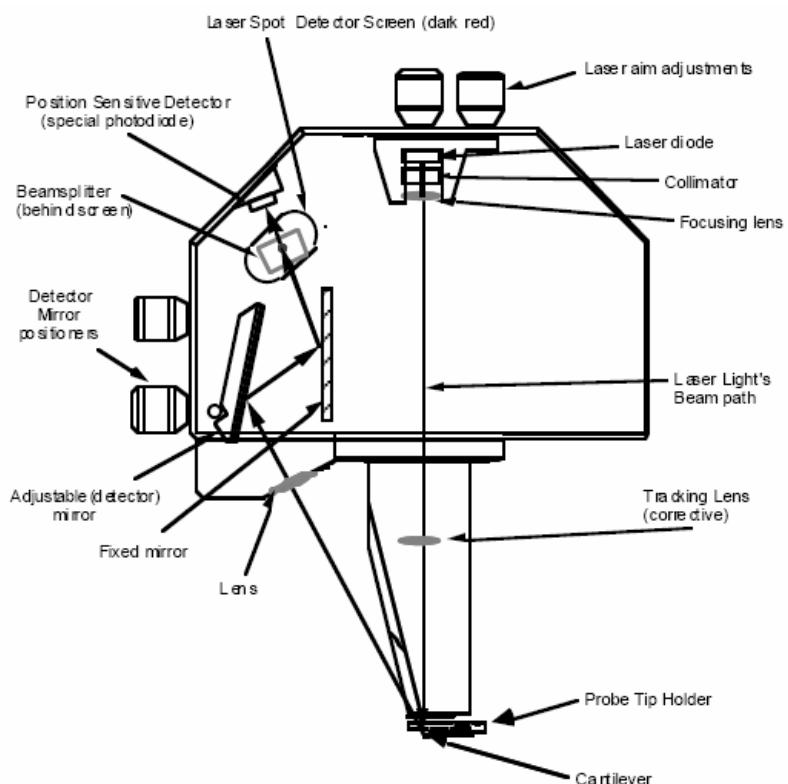

#### 一、雷射光束對位：

旋轉雷射模組(圖 3.3)上方的兩顆旋鈕，改變雷射光源的位置，使雷射光點照射於懸臂頂點 (如圖 3.4 中橢圓紅色光點的位置)。此動作會直接影響 SUM 值，當光點落在懸臂頂點時，理論上應有最大的 SUM 值。Tapping mode 的 SUM 值只須大於 2 即可。

圖 3.3 原子力顯微鏡的雷射模組

圖 3.4 雷射光點位置示意圖

## 二、樣品放置、防震系統、載台移動：

1、樣品放置：可用雙面膠黏樣品，或貼兩條膠帶於樣品兩側。

2、防震系統：開氮氣使載台浮起，避免外界震動而使儀器共振，影響 AFM 量測精確。

3、載台移動：( surface focusing )

將雷射光點對到樣品上欲量測的位置，注意移動時樣品的高度，不能撞到鏡頭。接著將鏡頭降落（注意移動滾輪時只能用掌心動）。

## 三、光學顯微鏡對位：( tip focusing )

首先把針對清楚，接著將十字的中心對到針的前端中央。（此舉為將 CCD 所看到的位置調到針所掃的位置，使得 CCD 看到的跟掃的位置是相同的。）

四、樣品表面或探針反射影像對位：( surface focusing )

## 五、震動頻率校正：

按 Auto tune 白色曲線為震動頻率曲線，黃色曲線表示相位，中間值表示共振頻率。

## 六、下針前的參數還原：

|               |      |                   |      |

|---------------|------|-------------------|------|

| scan size     | 1um  | aspec ratio       | 1:1  |

| x offset      | 0 nm | y offset          | 0 nm |

| scan angle    | 0    | scan rate         | 1 Hz |

| samples/line  | 256  | Lines             | 256  |

| Integral gain | 0.6  | Proportional gain | 0.6  |

Scan size 最大不要超過 30um。

儀器最佳的 resolution 為 100nm~800、900nm。

Drive amplitude(給針的驅動電壓)最好小於 200mV。否則當表面起伏很小時，則表面形貌會模糊掉。

## 七、下針後的注意事項：

- 1、scan size 越大則 scan rate 要越慢。

- 2、將 trace 和 retrace 的線重合，這樣量到的圖形才是正確的，可以調的值為：IG、PG、Amplitude setpoint、scan rate、scan size。

- 3、Amplitude setpoint 值越小表示針壓越大(tapping mode 適用)

- 4、Integral gain and Proportional gain:對於樣品距離的回饋，如果樣品側示圖有很多的小 peak 代表太靈敏則 IG and PG 的值要調小，假如曲線很平緩則代表太不靈敏則 IG and PG 的值要調大。

## 第四章 實驗結果與討論

### 4.1 介面修飾對元件 $V_{to}$ 和 $V_{FB}$ 的影響

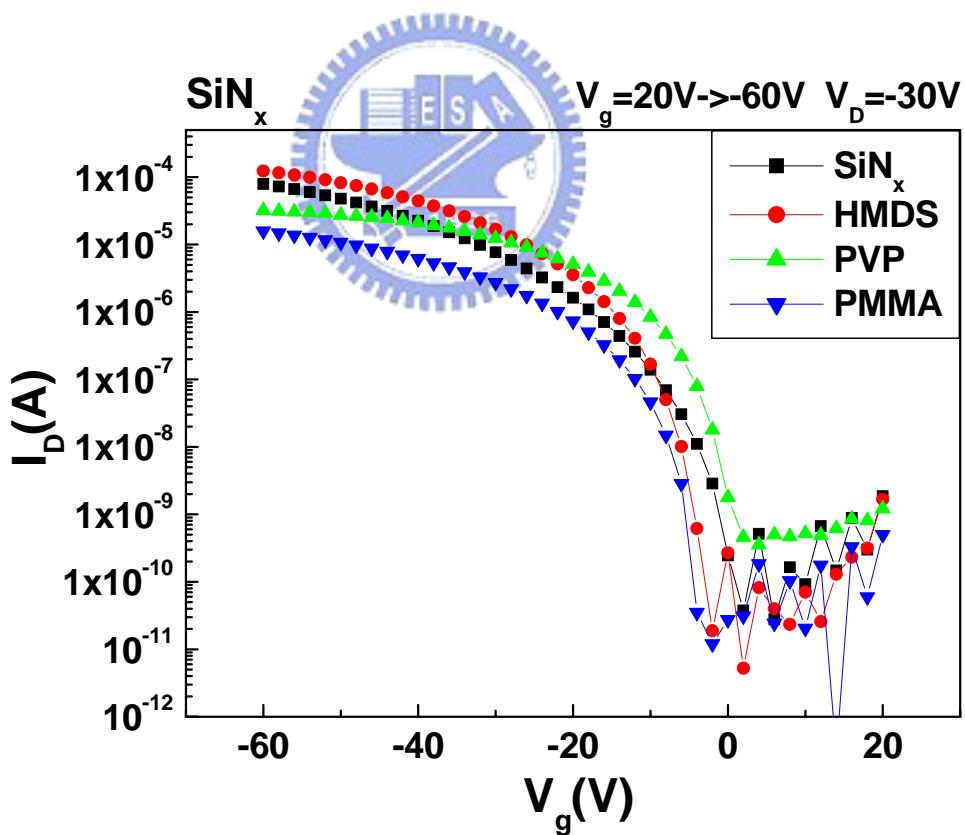

本實驗是利用不同的有機材料修飾基板，包含PVP、PMMA和HMDS三種，利用介面修飾改變基板表面的特性，進而影響了元件(device)的特性曲線( $I_D-V_g$ )，如圖 4.1 所示。由圖我們可以發現經過不同修飾的元件，電晶體啟動的電壓不同(turn-on voltage， $V_{to}$ )， $V_{to}$ 即是指電流呈指數上升時外加的閘極電壓值。元件開啟順序分別是PVP、 $\text{SiN}_x$ 、HMDS，最後開啟的是經由PMMA修飾的元件。 $I_D-V_g$ 的曲線是閘極( $V_g$ )從+20V掃到-60V，而集極端( $V_D$ )是維持施加-30V的偏壓，圖中正方形的符號是未修飾的元件，圓形則是HMDS修飾的元件，三角形是經PVP修飾，而倒三角形是經PMMA修飾的元件特性曲線。

圖 4.1  $I_D-V_g$ 曲線圖， $V_D=-30\text{V}$ 、 $V_g = +20\text{V} \sim -60\text{V}$

圖 4.2 量測 $I_D$ - $V_g$ 的元件結構圖

量測電容的結構是使用金屬-絕緣層-半導體的結構，此結構稱為 MIS 結構 (metal insulator semiconductor)，如圖 4.3 所示。

圖 4.3 量測 C-V 的 MIS 結構圖

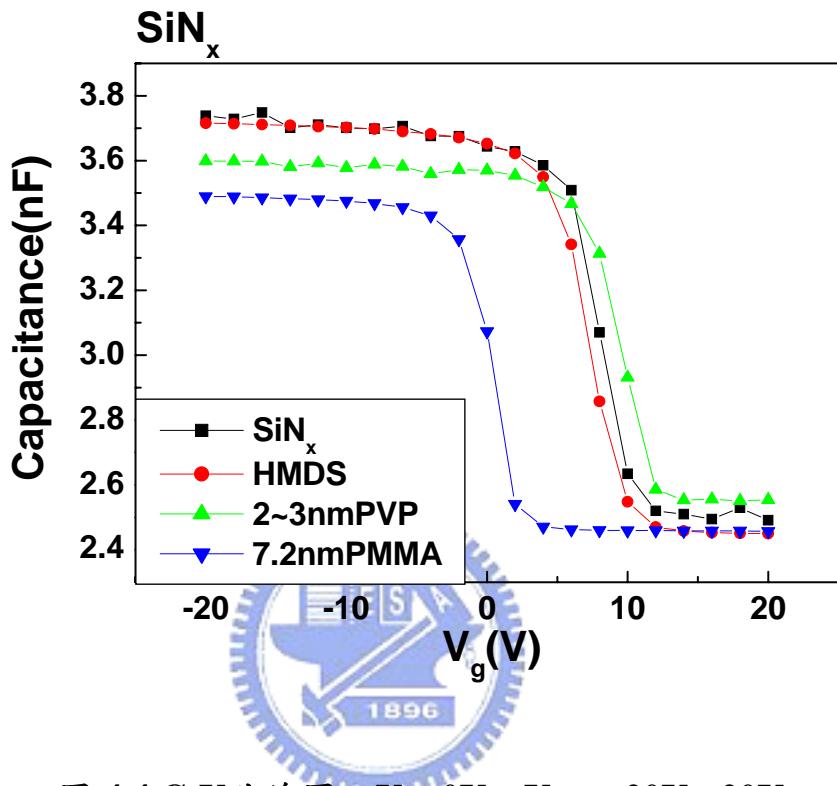

電容的特性曲線(C-V)，如圖 4.4 所示，我們定義 $V_{FB}$ (flat band voltage)為電荷受到吸引開始填補捕捉陷阱的電壓值，隨著基板表面修飾材料不同， $V_{FB}$ 也隨著改變。由圖 4.4 可觀察出 $V_{FB}$ 的變化趨勢跟 $V_{to}$ 是一樣的，但是元件 $V_{FB}$ 和 $V_{to}$ 值的差值是不同的。C-V的曲線是閘極( $V_g$ )從+20V掃到-20V，而集極端( $V_D$ )是維持接地的狀態，頻率是 1kHz，交流電壓是 25mV，由於C-V曲線在-20V時電容已沒有變化，所以沒有繼續增加偏壓。

我們將不同修飾元件的 $V_{FB}$ 、 $V_{to}$ 值以及差值整理在表 4.1 中，推測造成此現象的原因是陷阱捕捉(trap density)密度的改變。

圖 4.4 C-V曲線圖， $V_D=0V$ 、 $V_g = +20V \sim -20V$

表 4.1 不同修飾的元件 $V_{to}$ 和 $V_{FB}$ 的數值

|                                    | $V_{to}$ (V) | $V_{FB}$ (V) | $V_{FB}-V_{to}$ |

|------------------------------------|--------------|--------------|-----------------|

| $\text{SiN}_x$                     | 0            | 10.55        | 10.55           |

| $\text{SiN}_x+\text{HMDS}$         | -2           | 9.43         | 11.43           |

| $\text{SiN}_x+7\text{nmPMMA}$      | -4           | 2.29         | 6.29            |

| $\text{SiN}_x+2\sim 3\text{nmPVP}$ | 2            | 12.14        | 10.14           |

## 4.2 陷阱捕捉(trap density)

由圖 4.4 我們可以計算出從載子開始被吸引填補捕捉陷阱到元件可以啟動所需要的電荷總量，計算方式如圖 4.5 所示。圖中兩條虛線相交的點即為  $V_{FB}$ ，此篇論文中的  $V_{FB}$  都是利用相同的方法定義出來的。

圖 4.5 C-V 示意圖

圖 4.5 中的粗實線是代表  $V_g = V_{to}$  的直線，由這三條線在加上 C-V 曲線，所圍起來的區域大小定義為電晶體開啟之前所必須填滿捕捉陷阱的總電量，也就是圖上畫斜線的面積。計算的結果整理在表 4.2 中，表中  $V_{to}$  即是由 I-V 曲線定義出來的，而不可以移動的電量則是利用圖 4.5 所表示的斜線區域面積大小計算得到的結果，因為載子是填補捕捉陷阱，所以我們稱呼為被捕陷電量(trapped charges)。 $V_{FB}$  在圖 4.5 當中也有描述， $V_{FB} - V_{to}$  是電荷從開始填補捕捉陷阱到電晶體開啟的電壓差值。因此  $V_{FB}$  與  $V_{to}$  之間的差異越大，則被捕陷的電荷越多，這表示基板經由不

同材料修飾後，整體捕捉陷阱數目改變。

表 4.2 不同修飾的元件參數值

|                     | $V_{to}(V)$ | 被捕陷的電荷<br>(庫倫)        | $V_{FB}(V)$ | $V_{FB}-V_{to}$ |

|---------------------|-------------|-----------------------|-------------|-----------------|

| $SiN_x$             | 0           | $8.91 \times 10^{-9}$ | 10.55       | 10.55           |

| $SiN_x+HMDS$        | -2          | $1.08 \times 10^{-8}$ | 9.43        | 11.43           |

| $SiN_x+7nmPMMA$     | -4          | $4.16 \times 10^{-9}$ | 2.29        | 6.29            |

| $SiN_x+2\sim3nmPVP$ | 2           | $7.00 \times 10^{-9}$ | 12.14       | 10.14           |

由圖 4.5 計算出陷阱捕捉的總電量後，我們必須更詳細的定義出捕捉陷阱所在的區域。捕捉陷阱可以分成晶粒內部和晶粒邊界(grain boundary)兩部份來探討。

### 4.3 晶粒內部

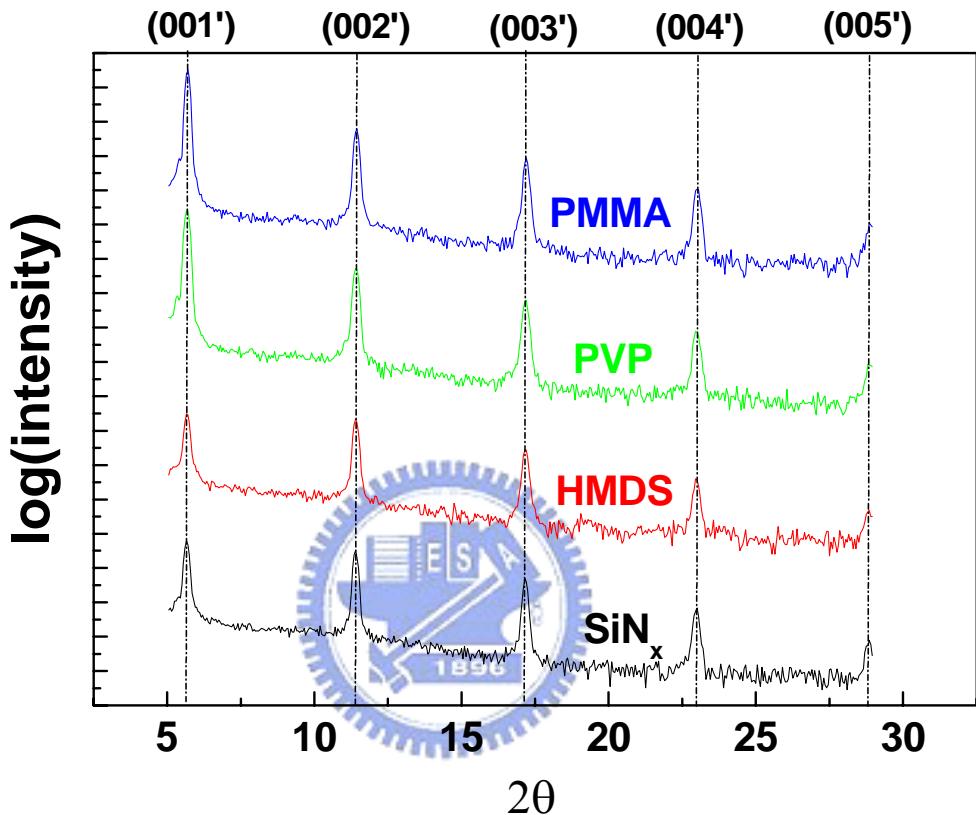

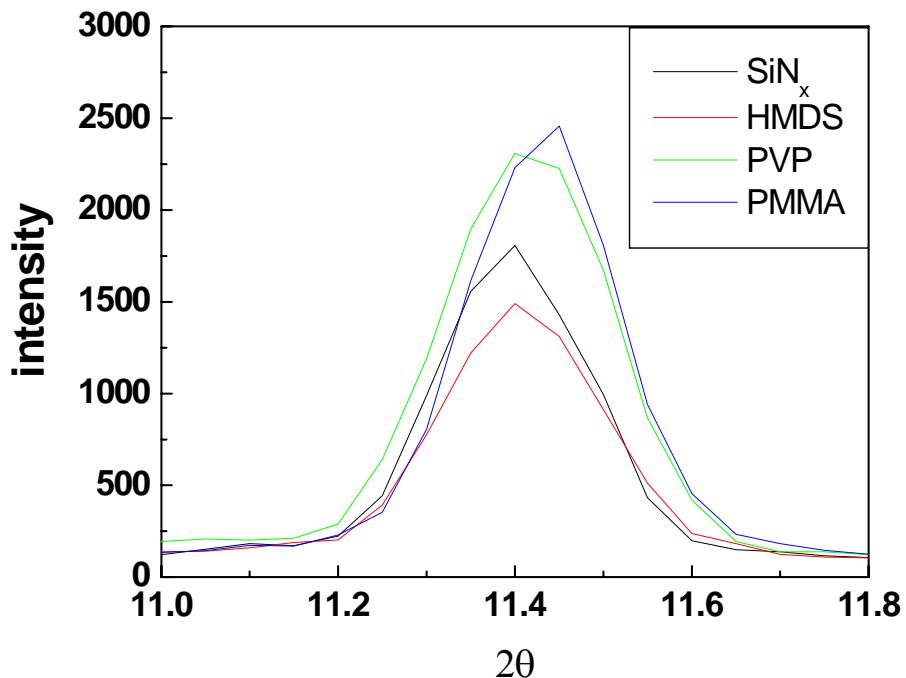

我們利用 X 光晶格繞射來判定五環素成長在不同修飾層的晶格排列的狀態，蒸鍍厚度  $600\text{ \AA}$ ，結果如圖 4.6 所示。

圖 4.6 五環素成長在不同修飾層的 X 光繞射圖，五環素厚度  $600\text{ \AA}$ 。

五環素成長在不同修飾的介面上厚度  $600\text{ \AA}$ ，經 X 光晶格繞射的結果，由圖 4.6 可以發現在這四種介面上成長的五環素都只有單一種相就是 thin-film phase[40]。在強度上的表現，由圖 4.7 可以發現第二繞射峰強度上的表現以 PMMA 最強，PVP 次之，緊接著是未修飾的，強度最弱的是經 HMDS 修飾的元件，而選擇第二繞射峰的原因是由於掃描角度在十度內會包含儀器造成的誤差。

圖 4.7 第二根繞射峰放大的圖形

我們推測五環素的排列整齊度較差，會導致陷阱捕捉的數量變的較多，我們將 X 光晶格繞射第二根繞射峰的強度與表 4.2 陷阱捕捉數量對照，將數據整理在表 4.3，可發現 X 光繞射結果強度越弱的，五環素排列越混亂，捕捉陷阱也越多。

表 4.3 X 光繞射強度與捕捉陷阱數目整理

|                                         | Intensity(強度) | 被捕陷的電荷(庫倫)            |

|-----------------------------------------|---------------|-----------------------|

| $\text{SiN}_x$                          | 1807          | $8.91 \times 10^{-9}$ |

| $\text{SiN}_x + \text{HMDS}$            | 1490          | $1.08 \times 10^{-8}$ |

| $\text{SiN}_x + 7\text{nmPMMA}$         | 2457          | $4.16 \times 10^{-9}$ |

| $\text{SiN}_x + 2\text{~}3\text{nmPVP}$ | 2308          | $7.00 \times 10^{-9}$ |

## 4.4 晶粒邊界

五環素沉積在基板上，平行基板的方向跟垂直方向的成長是互相獨立的，為了進一步了解晶粒邊界對於捕捉陷阱的影響，我們將晶粒邊界分成 X-Y 平面與 Z 方向兩部分來討論

### 4.4.1 Z 軸方向

我們引入 sherrer equation 計算晶粒大小，由公式計算得到的數值是代表 (001') 方向的晶粒高度，也就是 Z 軸方向。

**Sherrer equation :**

$$D_{hkl} = \frac{0.9 \times \lambda}{\beta_{hkl} \cos \theta}$$

其中  $D_{hkl}$  代表晶粒高度(Grain size)

$\beta_{hkl}$  是繞射峰的半高寬(徑度)

$\theta$  是繞射峰所在的角度(徑度)

$\lambda$  是  $1.54 \text{ \AA}$

由 sherrer equation 計算得到的結果整理在表 4.4 中，從表 4.4 的結果可觀察出五環素在 Z 軸方向的晶粒大小(Grain size)最少都有  $300 \text{ \AA}$ ，而半導體層在製作元件時只有蒸鍍  $600 \text{ \AA}$  的厚度，也就是說在五環素內部 Z 軸方面的晶粒邊界只會有一或二次，所以 Z 方向的晶粒邊界陷阱捕捉是可以忽略的。

表 4.4 不同修飾 Z 方向晶粒大小

|                                   | Grain size(Å) |

|-----------------------------------|---------------|

| $\text{SiN}_x$                    | <b>362.94</b> |

| $\text{SiN}_x+\text{HMDS}$        | <b>362.94</b> |

| $\text{SiN}_x+7\text{nmPMMA}$     | <b>385.75</b> |

| $\text{SiN}_x+2\sim3\text{nmPVP}$ | <b>341.22</b> |

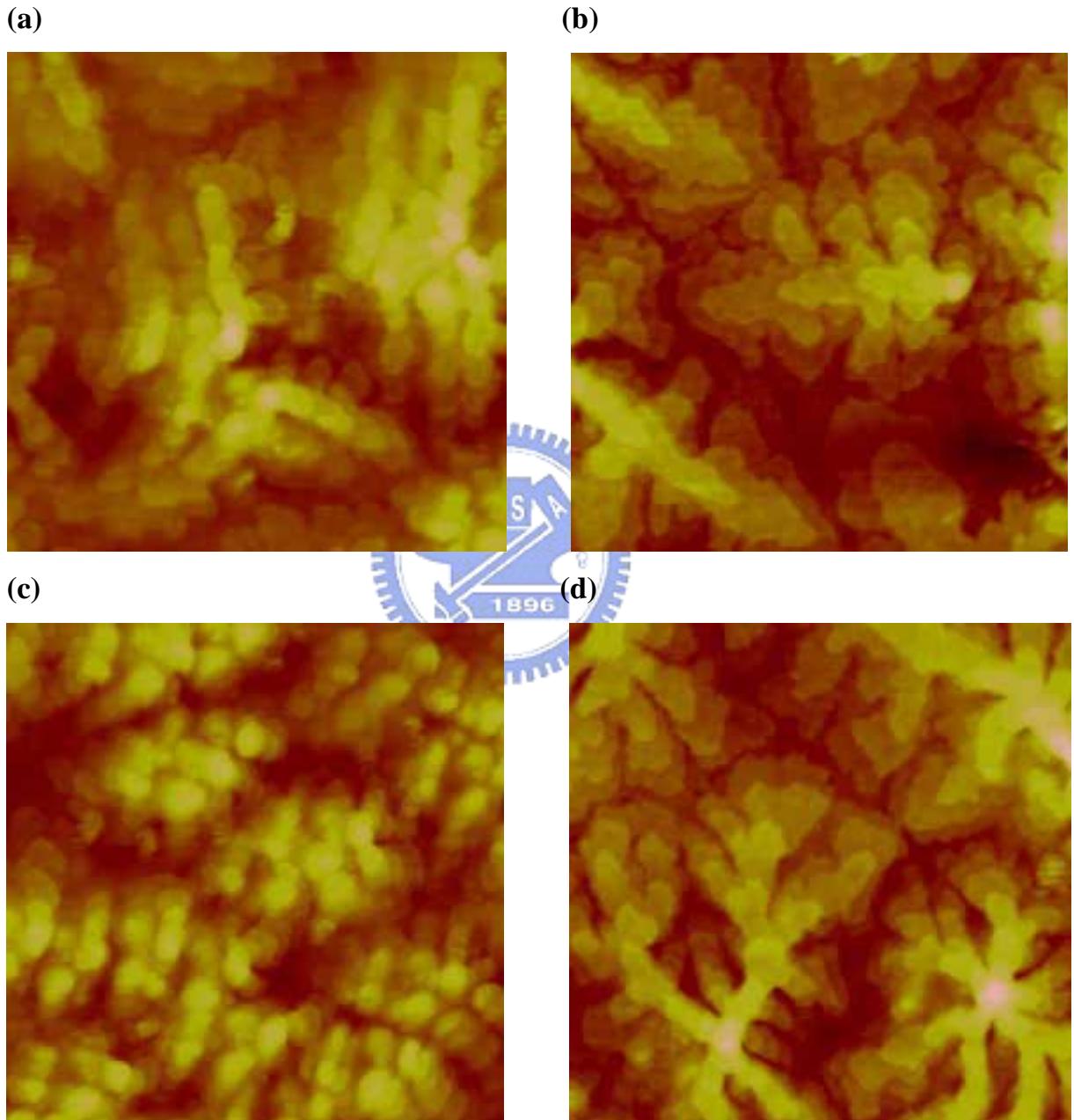

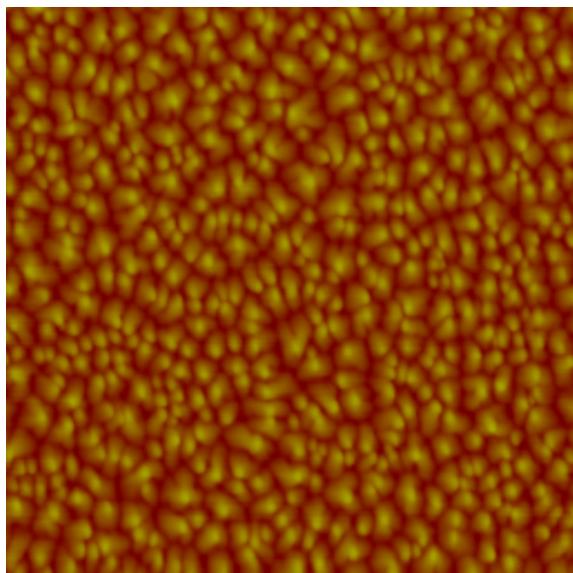

#### 4.4.2 X-Y 平面-五環素厚度 $100\text{ \AA}$

利用原子力顯微鏡量測五環素的表面形貌，五環素厚度是  $100\text{ \AA}$ ，量測結果如圖 4.8 所示，由於目前沒有比較好分析晶粒大小的方式，雖然原子力顯微鏡有內建程式可以計算晶粒大小，但是由於五環素的晶粒形狀較特殊有樹枝狀跟塊狀，程式在分析上明顯有誤差，於是我們仿造內建程式的寫法，設定一個基準面，分析在基準面上的狀況。

我們用來分析的軟體是 MATLAB，利用 MATLAB 程式分析晶粒邊界的長度，將數據整理在表 4.5。

表 4.5 五環素厚度  $100\text{ \AA}$  的邊界長度

|                                   | 啟動電壓(V) | 邊界長度(/um) |

|-----------------------------------|---------|-----------|

| $\text{SiN}_x$                    | 0       | 8.8       |

| $\text{SiN}_x+\text{HMDS}$        | -2      | 9.7       |

| $\text{SiN}_x+7\text{nmPMMA}$     | -4      | 10.1      |

| $\text{SiN}_x+2\sim3\text{nmPVP}$ | 2       | 8.6       |

將邊界長度和啟動電壓做比較，可以發現邊界長度越短的元件會越早開啟，這是因為載子在傳輸的過程當中，通過的晶粒邊界越少，則載子被捕捉的機會也會減少。

圖 4.8 厚度  $100\text{ \AA}$ 的五環素表面形貌。 (a)  $\text{SiN}_x$ 的元件、(b)經HMDS修飾、(c)經PMMA修飾、(d)經PVP修飾。[面積大小  $1.67\text{ }\mu\text{m} \times 1.67\text{ }\mu\text{m}$ ]

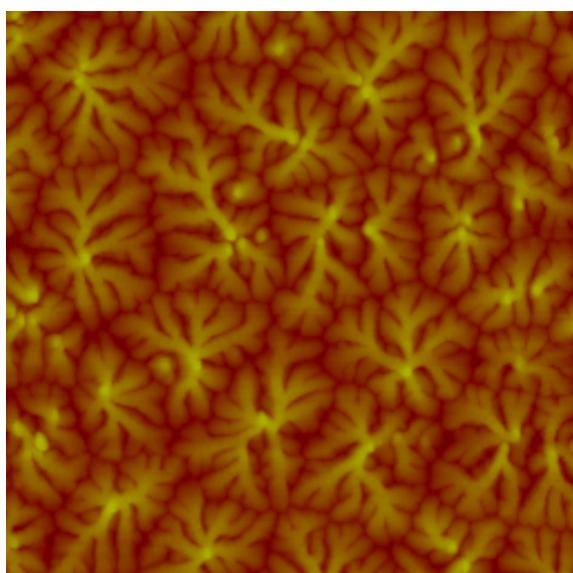

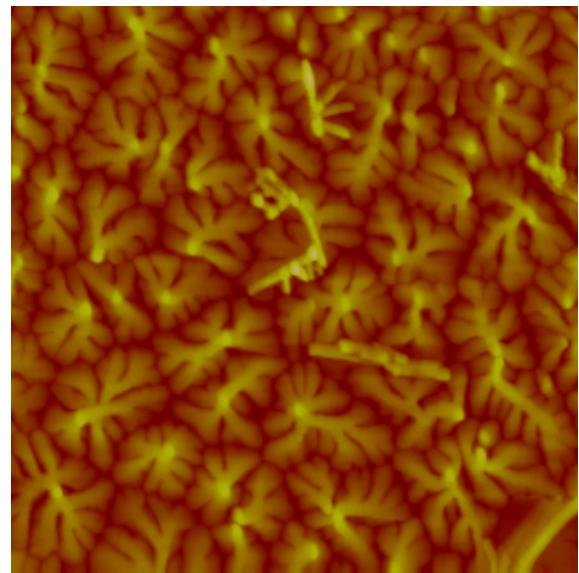

#### 4.4.3 X-Y 平面-五環素厚度 600 Å

利用原子力顯微鏡量測五環素的表面形貌，製作成元件的五環素厚度是 600Å，量測結果如圖 4.9 所示。我們同樣使用 MATLAB 程式分析，將分析結果列在表 4.6 中，發現邊界長度較短的元件，較容易啟動，而邊界長度較長的捕捉陷阱也較多，造成元件啟動較晚，此結果與薄的五環素得到的趨勢是相同的。

**表 4.6 五環素厚度 600 Å 的邊界長度**

|                            | 啟動電壓(V) | 邊界長度(/um) |

|----------------------------|---------|-----------|

| SiN <sub>x</sub>           | 0       | 19.37     |

| SiN <sub>x</sub> +HMDS     | -2      | 21.2      |

| SiN <sub>x</sub> +7nmPMMA  | -4      | 23.44     |

| SiN <sub>x</sub> +2~3nmPVP | 2       | 18.36     |

(a)

(b)

(c)

(d)

圖 4.9 厚度  $600\text{ \AA}$  的五環素表面形貌。 (a)  $\text{SiN}_x$ 的元件、(b)經HMDS修飾、(c)經PMMA修飾、(d)經PVP修飾。[面積大小  $5\text{um} \times 5\text{um}$ ]

## 4.5 影響晶粒邊界的因素

晶粒大小是影響晶粒邊界的主要原因，在X-Y平面，晶粒越大則晶粒邊界是越少的，觀察圖 4.8 與圖 4.9，可以發現五環素沉積在 $\text{SiN}_x$ 與經過PVP修飾的基板，都會得到較大的晶粒；反之，五環素沉積在經過PMMA與HMDS修飾的基板，晶粒都較小。進一步探討影響晶粒大小的原因，主要是利用接觸角實驗與修飾層表面粗糙度來推測成長模型。

### 4.5.1 接觸角

由接觸角量測儀來判定基板經過修飾後的表面特性，接觸角量測儀是基板表面滴三種溶液 (water, diiodo-methane, ethylene glycol)，利用 CCD 鏡頭拍攝畫面，使用 tangent 的方法求得液滴跟基板的夾角，數據列在表 4.7 中，而表 4.8 是列出接觸角量測儀的三種液滴特性。

表 4.7 將不同修飾的表面特性整理成表

|                                   | Diiodo-Methane | Water       | Ethylen glycol | surface tension (mN/m) | 邊界長度 (/um)   |

|-----------------------------------|----------------|-------------|----------------|------------------------|--------------|

| $\text{SiN}_x$                    | <b>35.6</b>    | <b>43.4</b> | <b>17.3</b>    | <b>48.5</b>            | <b>19.37</b> |

| $\text{SiN}_x+\text{HMDS}$        | <b>49.1</b>    | <b>65.2</b> | <b>37.1</b>    | <b>41.6</b>            | <b>21.2</b>  |

| $\text{SiN}_x+7.2\text{nmPMMA}$   | <b>29.8</b>    | <b>68</b>   | <b>46.3</b>    | <b>43.6</b>            | <b>23.44</b> |

| $\text{SiN}_x+2\sim3\text{nmPVP}$ | <b>21.5</b>    | <b>62.4</b> | <b>27</b>      | <b>50.8</b>            | <b>18.36</b> |

由熱力學的角度推測晶粒成長的狀態，當基板的表面能比沉積上去的材料大時，基板傾向於被材料鋪滿，類似層狀結構；相反的，當基板的表面能比沉積的材料小時，則沉積的材料會形成島狀結構。由表 4.7 顯示的實驗數據， $\text{SiN}_x$ 與經

過PVP修飾的基板擁有比五環素大的表面能，所以基板表面會被五環素鋪滿，長成類似層狀的結構，有較大的晶粒，較短的邊界長度；而PMMA和HMDS修飾的基板表面能較小，所以五環素長成類似島狀的結構，晶粒較小，有較長的邊界長度。利用表面能推測五環素成長模型如圖 4.10 所示。

圖 4.10 (a)經HMDS和PMMA修飾的晶粒類似島狀結構、(b)SiNx和經PVP修飾的晶粒類似層狀結構。

表 4.8 接觸角量測儀三種液滴的特性

|                | Density | Viscosity | Surface tension | Disperse part | Polar part |

|----------------|---------|-----------|-----------------|---------------|------------|

| Water          | 1       | 1         | 72.8            | 26            | 46.8       |

| Diiodo-Methane | 3.33    | 2.76      | 50.8            | 44.1          | 6.7        |

| Ethylen glycol | 1.11    | 21.81     | 47.7            | 26.4          | 21.3       |

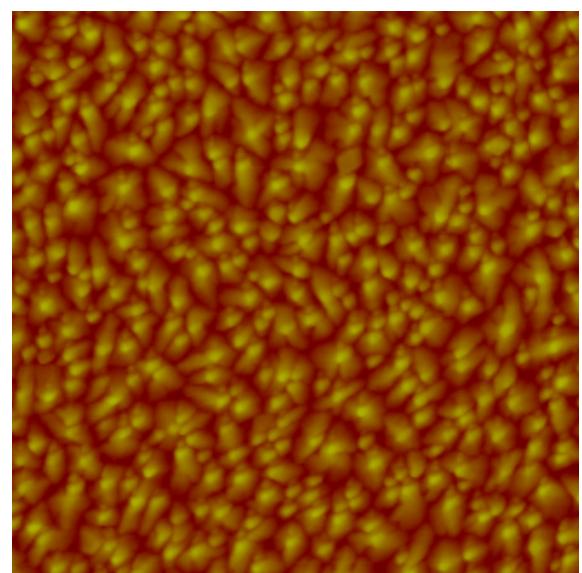

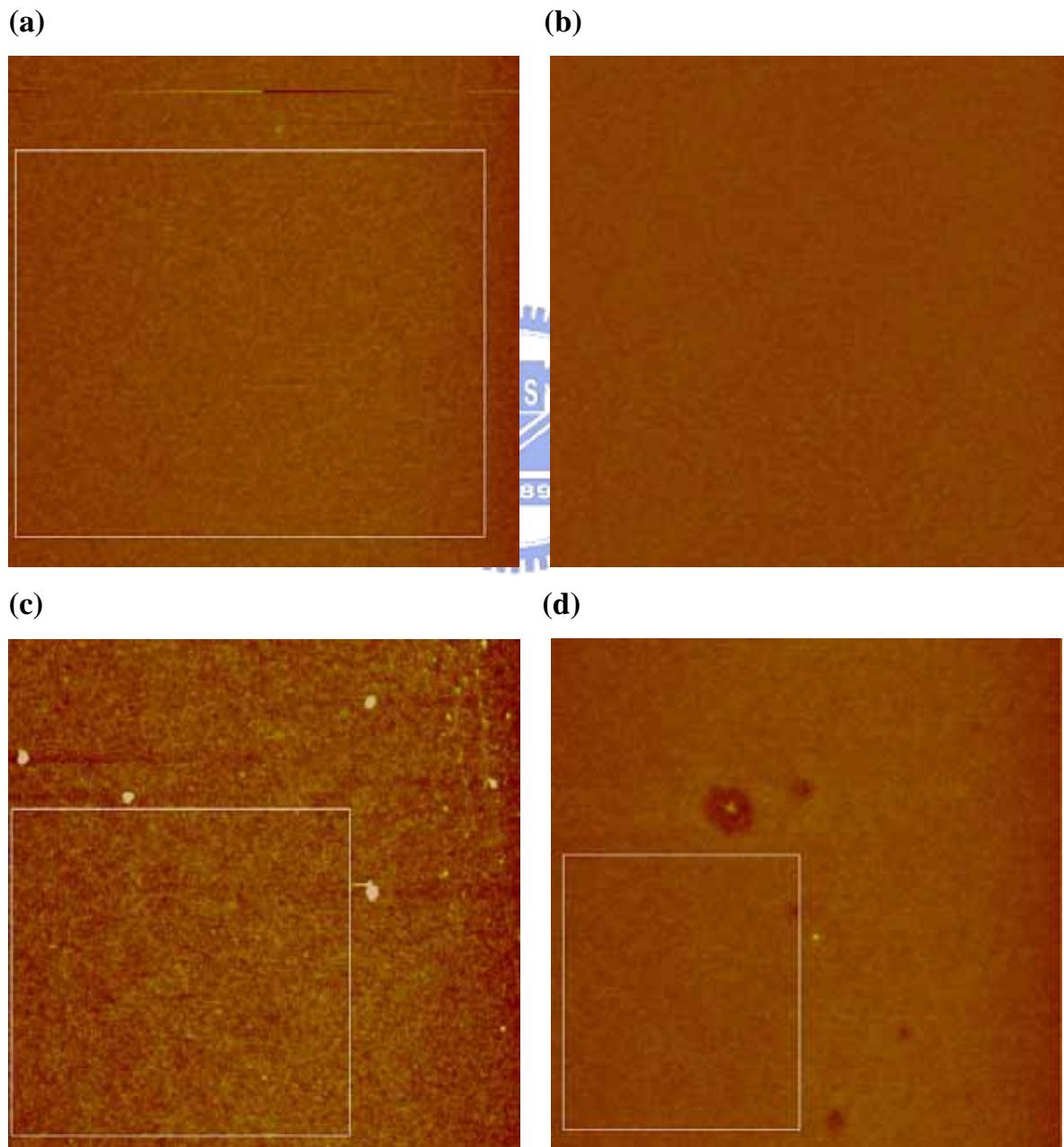

#### 4.5.2 修飾層表面粗燥度

有文獻指出表面粗糙度會影響晶粒大小，表面越粗糙則晶粒會越小。上一節利用表面能判定出五環素成長的方式可分成島狀跟層狀，此節近一步引入表面粗糙度分析。利用原子力顯微鏡掃描修飾層的表面，藉此可看出成長五環素之前的表面形貌，結果如圖 4.11 所示。

圖 4.11 (a)  $\text{SiN}_x$ 的元件、(b)經HMDS修飾、(c)經PMMA修飾、

(d)經 PVP 修飾。[面積大小 5um\*5um]

將圖 4.11 利用原子力顯微鏡內建的程式分析表面粗糙度，將數據列在表 4.9 中，從數據可發現的看到PMMA表面比HMDS粗躁，所以五環素沉積在PMMA的晶粒又比HMDS來的小，也就是說晶粒邊界在PMMA的元件會比HMDS長；而SiN<sub>x</sub>也比經PVP修飾的基板來的粗糙，所以五環素成長在SiN<sub>x</sub>表面的晶粒就比成長在經PVP修飾的表面小，PVP修飾的元件晶粒邊界就會比SiN<sub>x</sub>少。

**表 4.9 不同修飾的表面形貌粗糙度與介面的最大捕捉陷阱數目關係表**

|                            | RMS(nm)      | V <sub>to</sub> (V) | 邊界長度(/um)    |

|----------------------------|--------------|---------------------|--------------|

| SiN <sub>x</sub>           | <b>0.401</b> | <b>0</b>            | <b>19.37</b> |

| SiN <sub>x</sub> +HMDS     | <b>0.321</b> | <b>-2</b>           | <b>21.2</b>  |

| SiN <sub>x</sub> +7nmPMMA  | <b>0.463</b> | <b>-4</b>           | <b>23.44</b> |

| SiN <sub>x</sub> +2~3nmPVP | <b>0.311</b> | <b>2</b>            | <b>18.36</b> |

先使用表面能判定五環素成長的方式，五環素成長在PVP和SiN<sub>x</sub>都是層狀結構，所以在X-Y平面有較大的晶粒，又因為SiN<sub>x</sub>的表面比PVP粗躁導致晶粒比較小，所以PVP的元件有比SiN<sub>x</sub>短的晶粒邊界長度；而五環素成長在PMMA和HMDS是島狀結構，在X-Y平面的晶粒較小，又因為PMMA的表面很粗糙，導致五環素成長在PMMA的表面晶粒更小，所以PMMA的元件有較長的晶粒邊界長度。

## 第五章 結論

用不同材料修飾改變基板表面特性，由 X 光晶格繞射來判定五環素在排列上並無相變化的產生，但在電性上則有明顯的變化。以電流電壓曲線和電容電壓曲線互相比較，發現電晶體開啟順序和電荷開始累積的順序是一樣的，但是數值上的差異是很明顯的，為了更了解這差異的來源，可使用儀器和引入模型來幫助分析。

先利用電容的特性曲線計算被捕陷電量。為了分析捕捉陷阱的來源，我們分為晶粒內部和晶粒邊界(grain boundary)兩部份來探討。晶粒內部可利用X光晶格繞射的強度來觀察排列的情況，發現強度越強排列越整齊的，捕捉的載子是最少的。而晶粒邊界必須分成兩個部份討論，X-Y平面與Z軸方向。X-Y平面則是先使用原子力顯微鏡掃描五環素的表面形貌，之後利用MATLAB程式分析邊界長度，五環素的厚度有  $100\text{ \AA}$  與  $600\text{ \AA}$ ，由程式分析的結果發現不同厚度可得到相同的趨勢，邊界長度越長的元件，會越慢開啟；而Z軸方向晶粒有  $300\text{ \AA}$ ，所以Z方向的晶粒邊界陷阱捕捉是可以忽略的。緊接著利用接觸角量測經修飾之後的表面能，推測五環素成長的模型。五環素的表面能比PVP和 $\text{SiN}_x$ 小，所以會形成層狀結構，晶粒較大，邊界長度較短；而PMMA和HMDS修飾後表面的表面能比五環素小，形成島狀結構，晶粒較小，邊界長度較長。邊界長度越長的元件，會使得載子在傳輸時容易被陷阱捕捉，元件會較慢開啟；反之，邊界長度短的元件，載子傳輸時不易被捕捉，元件開啟的時間就會較早。

元件經過不同材料修飾後改變整體捕捉陷阱密度，主要是因為五環素排列整齊度與晶粒邊界多寡，造成元件特性的差異。元件開啟電壓主要是晶粒邊界多寡決定，由此可知如果想要做出可調變的元件，可以利用不同材料的修飾層來調變  $V_{to}$ 。

〔参考文献〕

[1] G. Horowitz, “Organic Thin Film Transistors: From Theory to Real Devices”, *J. Mat. Res.* 19, pp. 1946, 2004.

[2] T. Dobbertin, M. Kroeger, D. Heithecker, D. Schneider, D. Metzdorf, H. Neuner, E. Becker, H.-H. Johannes, and W. Kowalsky, “Inverted Top-Emitting Organic Diodes Using Sputter-Deposited Anodes”, *Appl. Phys. Lett.* 82, pp. 284, 2003.

[3] C. J. Brabec, N. S. Sariciftci, and J. C. Hummelen, “Plastic Solar Cells”, *Adv. Funct. Mater.* 11, pp. 15, 2001.

[4] K. Nomoto, N. Hirai, N. Yoneya, N. Kawashima, M. Noda, M. Wada, and J. Kasahara, “A High-Performance Short-Channel Bottom-Contact OTFT and Its Application to AM-TN-LCD”, *IEEE T. Electron Dev.* 52, pp. 1519, 2005.

[5] L. Zhou, S. Park, B. Bai, J. Sun, S. C. Wu, T. N. Jackson, S. Nelson, D. Freeman, and Y. Hong, “Pentacene TFT Driven AM OLED Displays”, *IEEE Electron Device Letter.* 26, pp.640, 2005.

[6] V. Subramanian, J. M. J. Frechet, P. C. Chang, and S. K. Volkman, ” Progress Toward Development of All-Printed RFID Tags: Materials, Processes, and Devices”, *Proceeding Of The IEEE*, 93, pp.1330, 2005.

[7] Zheng-Tao Zhu, Jeffery T. Mason, Rudiger Dieckmann, and George G. Malliaras, “Humidity Sensors Based on Pentacene Thin-Film Transistors”, *Appl. Phys. Lett.* 21, pp.4643, 2002.

[8] F. Ebisawa, T. Kurokawa, and S. Nara, “Electrical Properties of Polyacetylene/Polysiloxane Interface”, *J. Appl. Phys.* 54, pp.3255, 1983.

[9] A. Tsumura, H. Koezuka, and T. Ando, ”Macromolecular electronic device : Field-Effect Transistors with a Polythiophene Thin Film”, *Appl. Phys. Lett.* 49, pp. 1210, 1986.

[10] A. Assadi, C. Svensson, M. Willander, and O. Inganas, “Field-Effect Mobility of Poly(3-hexylthiophene)”, *Appl. Phys. Lett.* 53, pp.195, 1988.

[11] F. Garnier, G. Horowitz, X. Z. Peng, D. Fichou. *Adv. Mater.* 2, pp. 592-594, 1990.

[12] G. Horowitz, X. Z. Peng, D. Fichou, and F. Garnier, “Role of Semiconductor/insulator Interface in the Characteristics of -Conjugated-Oligomer-Based Thin-Film Transistors”, *Syn. Met.* 51, pp.419, 1992.

[13] Y.-Y. Lin, D. J. Gundlach, S. F. Nelson, and T. N. Jackson, “Stacked Pentacene Organic Thin-Film Transistors with Improved Characteristics”, *IEEE Electron Device Letters*, 18, pp.606, 1997.

[14] M. P. Hong, B. S. Kim, Y. U. Lee, K. K. Song, J. H. Oh, J. H. Kim, T. Y. Choi, M. S. Ryu, and K. Chung, S. Y. Lee, B. W. Koo, J. H. Shin, E. J. Jeong, and L. S. Pu, “Recent Process in Large Sized & High Performance Organic TFT Array”, *SID 05 DIGEST*, 23, 2005.

[15] Oana D. Jurchescu, Jacob Baas, and Thomas T. M. Palstra, *Appl. Phys. Lett.* 84, pp. 3061, 2004.

[16] A. Tsumura, H. Koezuka, T. Ando, *Appl. Phys. Lett.* 49, pp. 1210, 1986.

[17] A. Assadi, C. Svensson, M. Willander, O. Ingans, *Appl. Phys. Lett.* 1988.

[18] J. Paloheimo, E. Punkka, H. Stubb, P. Kuivalainen, in *Lower Dimensional Systems and Molecular Devices*, Proceedings of NATO ASI, Spetses, Greece (Ed: R. M. Mertzger), Plenum, New York, 1989.

[19] Z. Bao, A. Dodabalapur, A. J. Lovinger, *Appl. Phys. Lett.* 69, pp. 4108, 1996.

[20] H. Sirringhaus, N. Tessler, R. H. Friend, *Science*, 280, pp. 1741, 1998.

[21] F. Ebisawa, T. Kurokawa, S. Nara, *J. Appl. Phys.*, 54, pp. 3255, 1983.

[22] J. H. Burroughes, C. A. Jones, R. H. Friend, *Nature*, 335, pp. 137, 1988.

[23] G. M. Wang, J. Swensen, D. Moses, and A. J. Heeger, “Increased mobility from regioregular poly (3-hexylthiophene) field-effect transistors”, *J. Appl. Phys.*, 93, pp

6137, 2003.

- [24] R. Hajlaoui, G. Horowitz, F. Garnier, A. Arce-Brouchet, L. Laigre, A. Elkassmi, F. Demanze, F. Kouki, *Adv. Mater.* 9, pp. 389, 1997.

- [25] J. H. Schn, C. Kloc, B. Batlogg, *Org. Electron.*, 1, pp. 57, 2000.

- [26] Y. Y. Lin, D. J. Gundlach, S. Nelson, *T. N. Lett.*, 18, pp. 606, 1997.

- [27] C. D. Dimitrakopoulos, A. R. Brown, A. Pomp, *J. Appl. Phys.*, 80, pp. 2501, 1996.

- [28] Y. Y. Lin, D. J. Gundlach, T. N. Jackson, *54th Annual Device Research Conference Digest 1996*, p.80. 1991.

- [29] G. Horowitz, X. Peng, D. Fichou, F. Garnier, *Synth. Met.*, 51, pp. 419, 1992.

- [30] R. C. Haddon, A. S. Perel, R. C. Morris, T. T. M. Palstra, A. F. Hebard, R. M. Fleming, *Appl. Phys. Lett.*, 67, pp. 121, 1995.

- [31] J. Kastner, J. Paloheimo, H. Kuzmany, in *Solid State Sciences*(Eds:H. Huzmany, M. Mehring, J. Fink), Springer, New York, pp. 515-521, 1993.

- [32] G. Guillaud, M. Al Sadoun, M. Maitrot, *Chem. Phys. Lett.*, 167, pp. 503, 1990.

- [33] Z. Bao, A. J. Lovinger, J. Brown, *J. Am. Chem. Soc.*, 120, pp. 207, 1998.

- [34] H. Fuchigami, A. Tsumura, H. Koezuka, *Appl. Phys. Lett.*, 63, pp. 1372, 1993.

- [35] A. R. Brown, D. M. de Leeuw, E. J. Lous, E. E. Havinga, *Synth. Met.*, 66, pp. 257, 1994.

- [36] G. Horowitz, “Organic Field-Effect Transistors”, *Adv. Mater.* 10, pp. 365, 1998.

- [37] R. B. Campbell, J. Monteath Robertson, and J. Trotter, “The crystal and molecular structure of pentacene”, *Acta Cryst.* 14, pp.705, 1961.

- [38] L. Sebastian, G. Weiser, and H. Bassler, “Charge transfer transitions in solid tetracene and pentacene studied by electroabsorption”, *Chemical Physics*, 61, pp 125-135, 1981.

- [39] E. M. Suuberg, *J. Chem. Eng. Data*, 43, pp. 486 – 492, 1998.

[40] D. Knipp,a) R. A. Street,b) A. Vo" lkel, and J. Ho, J. Appl. Phys., vol. 93, pp. 347, 2003.

[41] Christine C. Mattheus, Anne B. Dros, Jacob Baas, Auke Meetsma, Jan L. de Boer and Thomas T. M. Palstra, "Polymorphism in pentacene", Acta Cryst. C57, pp.939 2001.

[42] Christine C. Mattheus, Gilles A. de Wijs, Robert A. de Groot, and Thomas T. M. Palstra, "Modeling the polymorphism of pentacene", J. Am. Chem. Soc. 125, pp. 6323, 2003.

[43] C. D. Dimitrakopoulos, and P. L. Malenfant, "Organic Thin Film Transistors for Large Area Electronics", Adv. Mater. 14, pp.99, 2002.

[44] D. A. Neamen, "Semiconductor Physics and Devices :Basic Principles", 3<sup>rd</sup>, McGraw-Hill, 2003.

[45]M. A. Lampert, Physical Review, 103, pp. 1648-1656, 1956.

[46]D. K. Schroder, "Semiconductor Material and Device Characterization", (Wiley-Interscience, New York, 1998)

[47] A. Wang, I. Kymissis, V. Bulović, and A. I. Akintunde, "Tunable threshold voltage and flatband voltage in pentacene field effect transistors", Appl. Phys. Lett. 89, pp. 112109, (2006).