# 行政院國家科學委員會專題研究計畫 成果報告

## 矽鍺奈米晶體之生長與材料特性之研究

計畫類別：個別型計畫

計畫編號：NSC94-2112-M-009-033-

執行期間：94 年 08 月 01 日至 95 年 07 月 31 日

執行單位：國立交通大學光電工程學系(所)

計畫主持人：張振雄

報告類型：精簡報告

處理方式：本計畫可公開查詢

中 華 民 國 95 年 9 月 19 日

# 行政院國家科學委員會補助專題研究計畫

\* 成果報告

□期中進度報

## 矽 鐵 奈 米 晶 體 之 生 長 與 特 性 之 研 究

計畫類別： 個別型計畫       整合型計畫

計畫編號：NSC94-2112-M-009-033-

執行期間： 94 年 8 月 1 日至 95 年 7 月 31 日

計畫主持人：張 振 雄

成果報告類型(依經費核定清單規定繳交)： 精簡報告

執行單位：交 通 大 學 光 電 工 程 研 究 所

中 華 民 國 95 年 9 月 15 日

## 一、 中文摘要

我們成功的利用快速熱氧化多孔矽(RTO-PS)的方法製作出奈米矽晶體(Silicon nanocrystals , nc-Si)，應用在金氧半結構的記憶體中。我們再利用高解析度穿透式電子顯微鏡(HRTEM)、拉曼散射光譜(Raman)，來觀察奈米矽晶體的存在，且利用電容-電壓(C-V)及電流系統，探討以p型與p<sup>+</sup>型多孔矽基板製作MOS的記憶效應。也討論利用不同退火的氣氛製作氧化層薄膜時，奈米矽晶體內之電荷儲存與釋放之改變。

另在本計劃中，多孔矽晶體也注入鉕元素並研究奈米矽晶體平均尺寸與發光特性光譜之間關係。藉由拉曼散射光譜紅位移及可見光激發光藍位移，可以發現它們位移量隨奈米矽晶體尺寸變小而增大。當將奈米矽晶體之樣品中摻雜鉕原子，發現鉕原子在1.54 μm螢光發光強度隨著奈米矽晶體尺寸變小而增強。如同其它文獻所證實，奈米矽晶體的存在的確可以加強激發鉕原子發光，且發光效益也和奈米矽晶體尺寸有密切關係。

關 鍵 詞：多孔矽晶體,奈米矽晶體,記憶特性,摻鉕發光特性

## 二、 英文摘要

We employed successfully rapid thermal oxidized porous silicon (PS) to fabricate silicon nanocrystals (nc-Si) in the metal - oxide - semiconductor (MOS) structure for novel memory device. The characteristics of the oxidized PS were investigated by high resolution transmission electron microscope (HR-TEM), Capacitance-Voltage (C-V), Current-Voltage (I-V), and Raman scattering (Raman). We observed the charging effects of the RTO-PS MOS made by p-type and p<sup>+</sup>-type silicon substrates under the different operating ambiances while RTA process. The charging effect manifested by the hysteresis in the C-V curve was found to relate the different sizes of the nc-Si embedded in the oxidized PS region.

After that, we doped Er ions into silicon rich SiO<sub>2</sub> (SRSO) structure and successfully observed the infrared photoluminescence at 1.54 μm from Er ions. From the observed red-shift data of Raman scattering and the blue shift of visible photoluminescence, we are able to evaluate the average size of nc-Si. The relations between infrared photoluminescence and average size of nc-Si were discussed. The average intensity of infrared photoluminescence at 1.54 μm from Er ions would increases as the average size of nc-Si decreases. This fact giving evidence that the Er ions were excited by the exciting nc-Si and the process of transferring energy from the excited nc-Si was happened. Hence, the conversion efficiency of light from Er ions is related to the quantity and average size of nc-Si.

### 三、報告內容

#### (a) 前 言

目前常用的記憶元件主要可以分成兩大類：一種是揮發性記憶元件(volatile memory)，另一種是非揮發性記憶元件(non-volatile memory)。揮發性記憶體儲存在記憶體的資料會隨電源關閉而消失，而非揮發性記憶體儲存在記憶體的資料不會隨電源關閉而消失。非揮發性記憶元件主要有三種產品：(1) 抹除式唯讀記憶體(Electrically programmable read-only memory, EPROM)，(2) 電子抹除式唯讀記憶體(Electrically erasable programmable read-only memory, EEPROM)。後來又有Flash 記憶元件的發展，這種記憶元件結構和特性與 EEPROM 很相似，只是 Flash 的容量比 EEPROM 大，所以應用層面較廣。Flash 記憶元件的操作速度比 EEPROM 還要快。

Flash 記憶元件又可細分為兩種不同結構，這兩種記憶元件儲存電荷的機制也大不相同。一種是浮停閘元件(Floating gate device)，另一種是捕捉電荷元件(Charge-trapping device)。浮停閘元件主要是將載子儲存在floating gate中，電荷可以在塊材內流動，因此儲存位置是屬於連續性的。捕捉電荷元件的儲存位置是不連續性的。兩種代表性的元件：(1) 砂氧化氮氧化矽(SONOS)記憶元件，(2) 量子點(Quantum dots)記憶元件。矽氧化氮記憶元件，儲存電荷的媒介是氮化矽( $\text{Si}_3\text{N}_4$ )，夾在雙層氧化層中間，捕捉電荷的機制是靠氮化矽中的traps。而量子點記憶元件，這種元件儲存位置是量子點(Quantum dots) 或稱作奈米晶體。量子點快閃記憶體，電荷必須要穿過薄的氧化層進入到儲存位置被捕，也就是本計劃所要探討的結構。<sup>[1]</sup>

#### (b) 研究目的與文獻考

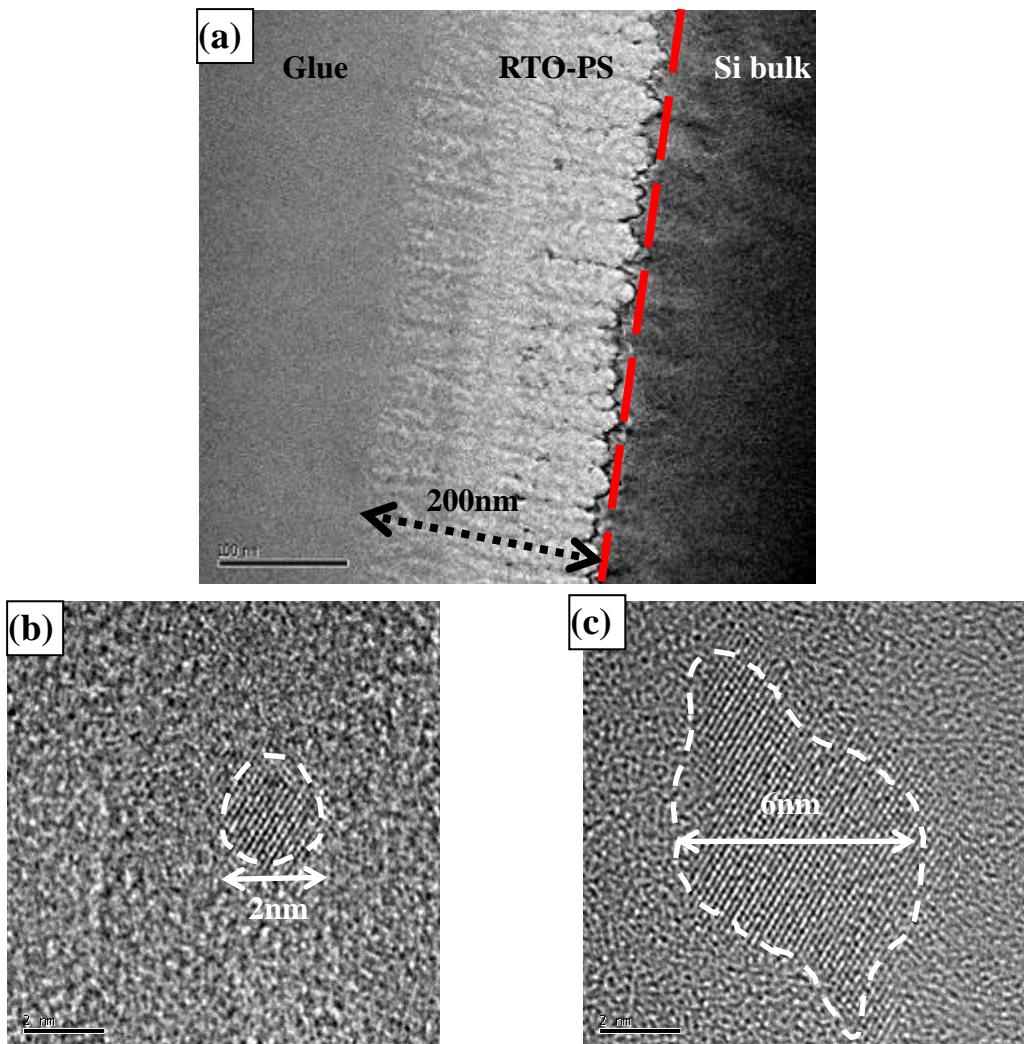

在MOS結構中，氧化層中含有奈米矽晶體，這種結構最近被廣泛運用在記憶元件。記憶元件裡只要含有奈米矽晶體就稱為『奈米矽晶體記憶元件』。1996年，Tiwari<sup>[2]</sup>發表一篇論文是關於奈米矽晶體的記憶元件，在這種記憶元件中，電荷儲存在奈米矽晶體中(見圖 1)。在本計劃中，我們主要是要探討快速熱氧化的多孔矽所製作的奈米矽晶體。這種奈米矽晶體的記憶元件中，儲存電荷將有可能發生在下列四個位置：(1) 矽基板與 $\text{SiO}_2$ 的介面處(interface states)，(2) 在 $\text{SiO}_2$ 裡面缺陷處，(3) 奈米矽晶體內，(4) 奈米矽晶體與周圍的 $\text{SiO}_2$ 的介面處。

在1999年Koki Ueno<sup>[3,4]</sup>利用快速熱氧化的方法製作奈米矽晶體，他利用RTO-PS製作發光二極體，主要是探討發光機制，他並沒有估計奈米矽晶體尺寸大小和利用奈米矽晶體在電性方面的研究與探討。

#### (c) 研究方法

我們利用多孔矽當作基板主要是元件可應用在矽基材料上面，由於多孔矽表面有許多的孔洞，因此多孔矽比一般的矽基板更容易被氧化，且多孔矽經過氧化

而成的 $\text{SiO}_2$ 的品質比poly-Si經過氧化而成的 $\text{SiO}_2$ 的品質好。所以，利用此種方法製作出來 $\text{SiO}_2$ 的漏電流較小，非常適合做成MOS結構中的控制氧化層(control oxide)。我們利用多孔矽基板經過快速熱氧化(Rapid thermal oxide, RTO)後，在氧化層表面再鍍上一層金屬閘極，這樣就形成標準的MOS結構。在此氧化層中，會殘存許多尚未被氧化成 $\text{SiO}_2$ 之大小不均的奈米矽晶體。我們主要是探討RTO-PS製作MOS的儲存電荷的效果及利用HRTEM證實有奈米矽晶體的存在並用Raman shifts估計奈米矽晶體的尺寸大小。藉由C-V和I-V量測探討此結構奈米矽晶體的記憶效應與電荷傳輸機制。

圖 1

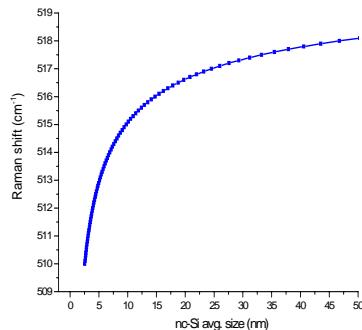

由於拉曼散射實驗的激發光源的光點的直徑一般為10~20微米，因此拉曼散射的訊號是大量奈米晶體的平均，而且奈米晶體不一定是精確的球狀晶體。所以常用到矽材料拉曼橫向光學模式振動頻率<sup>[4]</sup>可以寫成：

$$(\omega_L - \omega_o)^2 + \left( \frac{\Gamma_0}{2} \right)^2 \approx \frac{1}{2L} \exp(-\pi^2) \quad (1)$$

而 $\omega_L$ 是奈米矽晶體尺寸為 $L$ (angstrom)的振動頻率，對矽材料 $\omega_o = 520\text{cm}^{-1}$ ， $\Gamma_0 = 3.5\text{cm}^{-1}$ ， $\omega_L - \omega_o = \Delta\omega = \text{Raman shift} (\text{cm}^{-1})$ 。奈米矽晶體尺寸大小對拉曼位移的理論計算結果。此圖2是由(1)式得到的。我們將用拉曼散射實驗結果來估計奈米矽晶體的平均尺寸。

圖 2

我們是利用電化學陽極氧化的方法來製作多孔矽。我們將選用p型和p<sup>+</sup>型的矽基板，用來製作多孔矽。p型p<sup>+</sup>型矽基板的電阻率(resistivity,  $\rho$ )分別是  $50\Omega\text{-cm}^{-1}$  和  $0.05\Omega\text{-cm}^{-1}$ 。我們使用的矽基板面積是  $1\text{cm}^2$ 。

當我們將多孔矽的基板製作完成，接下來就是要進行快速熱氧化的步驟。我們將多孔矽基板置入快速熱氧化的chamber內，chamber內通入的氣體是氧氣，且在 30 秒內就可以從室溫升溫到  $1000^\circ\text{C}$ ，持溫的時間分別是 30 秒。快速熱退火的裝置與快速熱氧化的裝置相同。只是快速熱退火是通入氮氣( $\text{N}_2$ )或forming gas(氮氣 95%，氬氣 5%)的環境下退火。退火的溫度分別控制在  $400^\circ\text{C}$  和  $350^\circ\text{C}$ ，持溫時間分別是 30 秒和 60 秒。在快速熱氧化的多孔矽表面沉積金屬，這樣就形成金氧半結構 (MOS structure)。我們所使用的金屬電極是鋁(Al)當作我們的電極端，金屬面積是  $3.14 \times 10^{-4}\text{cm}^2$ 。金屬厚度約 300nm左右。之後，再進行RTA的過程，使金屬的contact更好。樣品條件介紹如下表一：

| 試片<br>編號 | 基板<br>種類            | Porous Silicon |       | R T O  |        | R T A |                                     | 金屬 |

|----------|---------------------|----------------|-------|--------|--------|-------|-------------------------------------|----|

|          |                     | 電流             | 時間    | 溫度     | 時間     | 溫度    | 氣體                                  |    |

| NO.1     | P <sup>+</sup> - Si | 300mA          | 1sec  | 1000°C | 30s    | 400°C | N <sub>2</sub>                      | Al |

| NO.2     | P <sup>+</sup> - Si | 300mA          | 1sec  | 1000°C | 30s    | 350°C | 95%N <sub>2</sub> +5%H <sub>2</sub> | Al |

| NO.3     | P <sup>+</sup> - Si | 30mA           | 10sec | 1000°C | 30s    | 400°C | N <sub>2</sub>                      | Al |

| NO.4     | P - Si              | 30mA           | 23sec | 1000°C | 30s    | 400°C | N <sub>2</sub>                      | Al |

| NO.5     | P <sup>+</sup> - Si |                |       | 1000°C | 120sec | 400°C | N <sub>2</sub>                      | Al |

| NO.6     | P - Si              |                |       | 1000°C | 120sec | 400°C | N <sub>2</sub>                      | Al |

#### (d)結果與討論

我們使用國家奈米實驗室 NDL 的電容-電壓量測系統，來量測我們製作的試片。使用的儀器設備是 Keithly 公司的儀器，包括了 590 C-V Analyzer(高頻分析儀)、595 C-V Quasi Meter(低頻分析儀)、230 Voltage Source(電壓供應器)、5951 Remote Input Controller 及 Probe station。我們主要是要量測 C-V 曲線，觀察電滯曲線的表現。

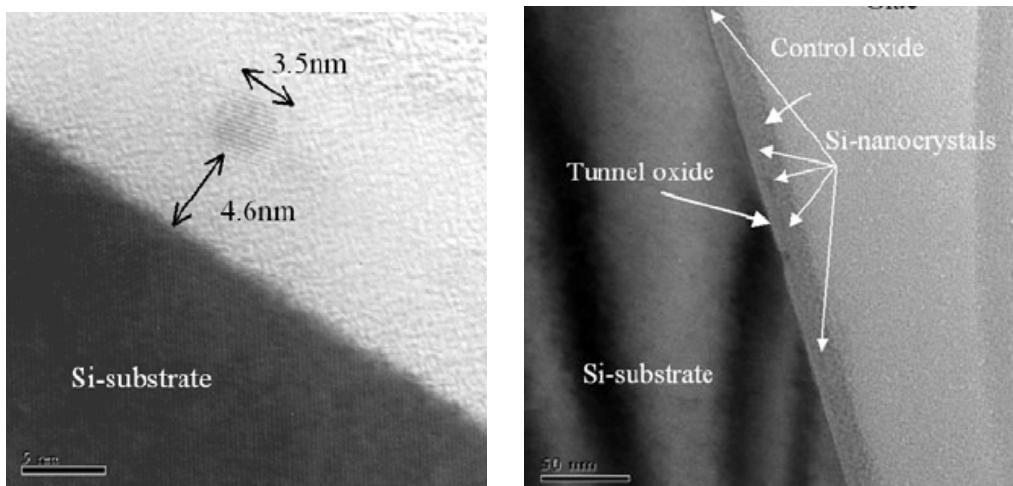

針對試片 NO.1，在這氧化後的多孔矽中含有許多大小不均勻的奈米矽晶體存在。圖 3，就是此種快速熱氧化多孔矽的 HRTEM 橫截面圖和不同尺寸奈米矽晶體的 HRTEM 圖。從圖 3.(a)，快速熱氧化多孔矽的橫截面圖可以得到在 RTO-PS 的表面有一層緻密的氧化層約 50nm。其餘部分的氧化層內因為存在奈米矽晶體，且多孔矽的深度越深氧化的程度越低，所以此種快速熱氧化多孔矽結構的氧化程度不均勻，奈米矽晶體尺寸也不均勻。從圖 3.(b)到(c)，奈米矽晶體尺寸介於 2nm 到 10nm 之間，平均尺寸約為 5nm。

如同試片 NO.1，在其他三種(NO.2- NO.4)不同製作奈米矽晶體的條件下，從 HRTEM 可以判斷只有 p 型 30mA (NO.4) 多孔矽製作的 MOS 沒有奈米矽晶體的存

在，可能是因為p型矽基板易氧化且氧化時間太久，導致於全部的多孔矽層都被氧化形成 $\text{SiO}_2$ 。其他二種製作的條件都可以觀察到奈米矽晶體的存在，且平均尺寸是5nm左右，形狀都不規則。

圖3.  $\text{p}^+$ 型 300mA RTO-PS (a)HRTEM橫截面圖

(b)和(c)不同尺寸的奈米矽晶體的HRTEM圖

我們也利用拉曼散射光譜的結果來估計我們快速熱氧化多孔矽製作的奈米矽晶體的平均尺寸大小。這裡拉曼量測的結果必須利用 peak fit 的軟體，找出兩個 peaks：第一個 peak 是奈米矽晶體的聲子振動頻率，第二個 peak 是矽基板的振動頻率。這裡利用公式(1)來推算出奈米矽晶體的平均尺寸大小，見表二。

這三種快速熱氧化多孔矽的拉曼散射光譜結果得知

| condition                     | Raman shift            | nc-Si  |

|-------------------------------|------------------------|--------|

| $\text{P}^+ 300\text{mA}$     | $512.78\text{cm}^{-1}$ | 4.7 nm |

| $\text{P}^+ 30\text{mA}$      | $512.04\text{cm}^{-1}$ | 4 nm   |

| $\text{P}^+ 300\text{mA H}_2$ | $512.78\text{cm}^{-1}$ | 4.7 nm |

表二

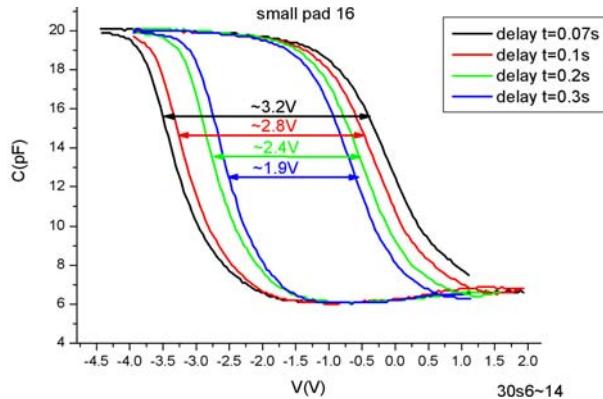

其次我們針對試片NO.1(與試片NO.2雷同)所選用的C-V曲線，電壓掃描範圍-4V到2V之間，以不同掃描速度之電壓下得到的C-V曲線的結果(圖4)。電滯曲線顯示試片確實有電荷儲存的效果，其所儲存之電荷約為 $10^{12}\text{cm}^{-2}$ 左右。

圖4.  $\text{p}^+$ 型 300mA多孔矽製作的MOS，在電壓掃描範圍較小，不同電壓 delay time 對電滯曲線寬度的結果

我們將 $\text{p}^+$ 矽基板經過標準的RCA clean 清洗過程之後，直接進行快速熱氧化，此為試片NO.5。這樣就會在 $\text{p}^+$ 型矽基板表面形成 $\text{SiO}_2$ ，然後在氧化層表面鍍金屬鋁(Al)，這樣就形成標準的MOS結構。此種標準MOS結構的氧化層中，沒有奈米矽晶體，也沒有缺陷的存在。試片NO.5與試片NO.6製作的MOS所量測得到的電容—電壓曲線從-4V往3V掃描，與從3V往-4V掃描，所得到的曲線是重疊的。這代表基本MOS結構是沒有儲存電荷的效果。而試片NO.4製作的MOS是 $\text{p}^+$ 型 30mA多孔矽基板製作的MOS，與試片NO.1兩種結果稍有不同。這是因為NO.4製作的MOS中沒有奈米矽晶體，但在氧化矽層中含有許多的缺陷，因此捕捉電荷主要是靠氧化層中的缺陷及一些界面態，所以它也有電滯曲線產生，不過寬度範圍較小，即儲存之電荷較少。由 I-V量測結果得知，電荷是從閘極端穿遂進入氧化層被氧化層中的奈米矽晶體、缺陷或界面態所捕捉，而呈現電滯曲線。 $\text{p}^+$ 型 30mA RTO-PS的MOS，從I-V曲線結果可以知道缺陷儲存和釋放電荷的時間較短。

另在本計劃中，多孔矽晶體也注入鉗元素並研究奈米矽晶體平均尺寸與發光特性光譜之間關係。藉由拉曼散射光譜紅位移及可見光激發光藍位移，可以發現它們位移量隨奈米矽晶體尺寸變小而增大。當將奈米矽晶體之樣品中摻雜鉗原子，發現鉗原子在  $1.54\mu\text{m}$  螢光發光強度隨著奈米矽晶體尺寸變小而增強。如同其它文獻所證實，奈米矽晶體的存在的確可以加強激發鉗原子發光，且發光效益也和奈米矽晶體尺寸有密切關係。

我們在實驗中主要是採用多孔矽當做基板。因為多孔矽本身就含有微小的奈

米矽晶體存在，且具有許多孔洞，所以比起一般矽基板更容易被氧化形成 SRSO 結構。至於鉀原子摻雜的方式，我們是採用電化學方式摻雜鉀，由於多孔矽具有孔洞的特性，可相對的增加鉀原子接觸矽原子之表面積，當我們藉著電場的力量將電化學溶液中的鉀原子帶入到多孔矽內，就比起使用其它方式更容易一次並大量摻雜鉀原子到多孔矽深層，而且非常有效快速。最後再經過快速熱氧化及快速熱退火的步驟，即可產生含有鉀原子的 SRSO 結構。

當奈米矽晶體尺寸越小，會使矽的光激發光(螢光)發光從原本的紅外光區( $E_g = 1.12 \text{ eV}$ )往藍位移偏，變成在可見光區發光。換句話說，隨著奈米矽晶體的尺寸變小，能隙因量子效應而增加，明顯不同於矽塊材，此效應稱為量子侷限效應 (quantum confinement effects)<sup>[5][6]</sup>。

我們利用電鍍的方式摻雜鉀元素，電鍍溶液是使用純度 99. 99% 的三氯化鉀 ( $\text{ErCl}_3$ )粉末將其浸泡入乙醇( $\text{C}_2\text{H}_5\text{OH}$ )溶液中形成飽和溶液。電鍍完的樣品，再以去離子水沖洗(DI water)數秒。電鍍鉀的電流密度皆固定使用  $35\text{mA/cm}^2$ ，電鍍時間皆為 300 秒。快速熱退火目的是使多孔矽內產生奈米矽晶體的析出。多孔矽電鍍完鉀元素的樣品完成後，接下來要進行快速熱氧化的步驟。將樣品放入腔體內，氣氛使用  $\text{O}_2 : \text{N}_2 = 20\% : 80\%$  的比例。升溫溫度約  $30^\circ\text{C/sec}$ ，設定 30 秒從室溫升到  $1000^\circ\text{C}$ ，持溫時間 30 秒。之後緊接著進行快速熱退火步驟。快速熱退火的溫度皆  $350^\circ\text{C}$ ，持溫時間皆 60 秒，通入氣體為  $\text{H}_2 : \text{N}_2 = 5\% : 95\%$  (forming gas)。

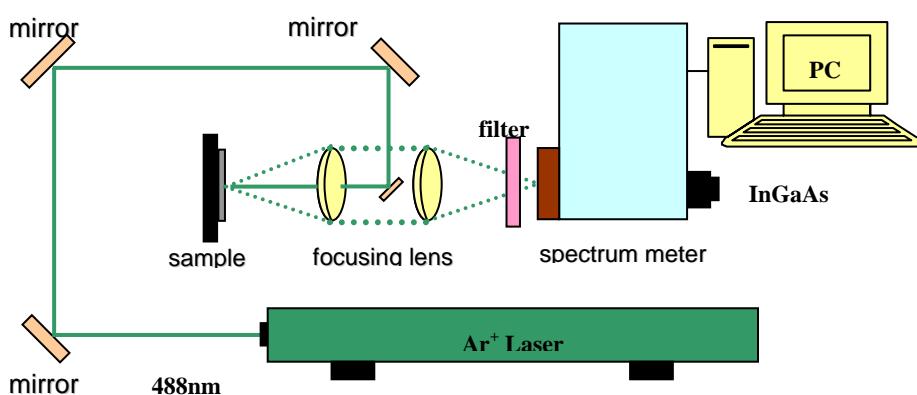

可見光激發光架設和拉曼散射光譜是雷同的系統。因量測範圍必須避開激發光源  $532\text{nm}$ ，以免光強對CCD的直接傷害，所以量測範圍是  $550\sim 900\text{nm}$ 。我們將觀察奈米矽晶體中，因量子侷限效應而有的發光波長的藍位移現象。紅外光激發光是以氬離子雷射( $\text{Ar}^+$  laser)波長  $488\text{nm}$ ，出光功率約  $500\text{mW}$ ，作為激發光源。光束經過四面反射鏡再經聚焦後，將激發光源聚焦在樣品上。最後經由一組收光鏡將樣品發出的螢光收入光譜儀。螢光在進入光譜儀狹縫之前必須放置一個濾波片，將氬離子雷射波長  $488\text{nm}$ 的光濾除。使用的偵測器為InGaAs，此偵測器可以使用範圍約在波長  $0.9\sim 1.6\mu\text{m}$ ，偵測器的溫度設定在  $-18^\circ\text{C}$ 。為了能夠量到鉀在  $1.54\mu\text{m}$ 附近的特徵光譜，我們量測的範圍設定從  $1.4\sim 1.6\mu\text{m}$ ，量測間距為  $10\text{\AA}$ ，信號積分的時間為 1 秒。(見圖 5)

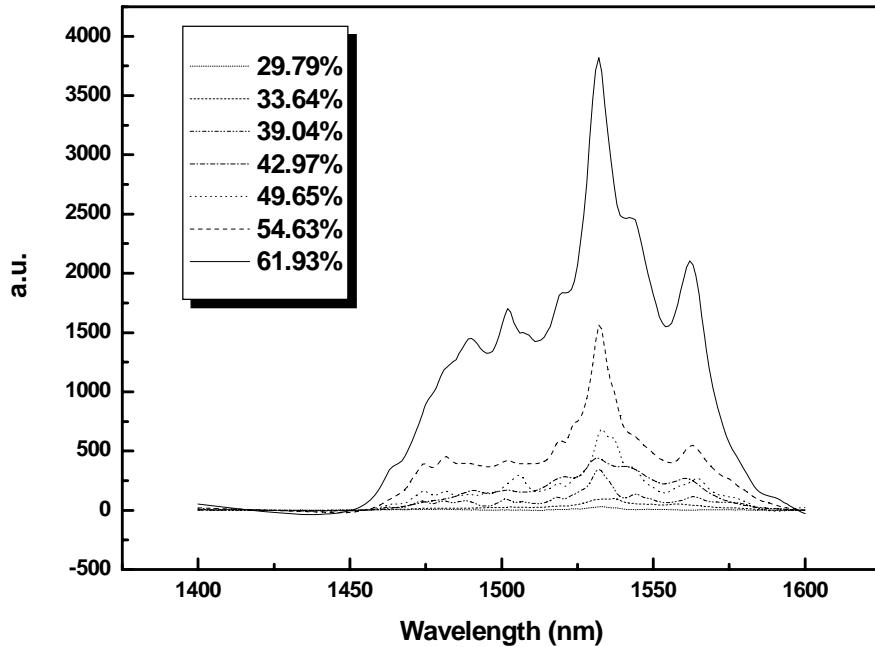

由於矽為非直接能隙且室溫能隙約 1.12eV，因此室溫矽的光激發光除了效率非常差外，發出之波段也在紅外光譜的範圍。但是形成奈米矽晶體後，光激發光會有明顯的改變。由於量子侷限效應，奈米矽晶體隨著尺寸越小，能隙會越大，於是發出之波段從原本的紅外光區，藍位移至可見光區。當奈米晶體大小約為 3.1nm 時，光激發光在能隙 1.8eV。當奈米晶體大小約為 3.3nm 時，光激發光在能隙 1.7eV。針對不同孔隙度的多孔矽摻雜鉿原子後，進行快速熱氧化及快速熱退火後，即形成含有奈米矽晶體並摻雜鉿原子的 SRSO 結構。最後進行紅外光激發光針對鉿原子  $1.54\text{ }\mu\text{m}$  波段量測。圖 6 即為不同孔隙度之 SRSO 之結構摻鉿發光結果，我們發現鉿原子的發光光譜約在  $1.54\text{ }\mu\text{m}$  位置。圖 6 為此系列量測疊合。由圖 6 我們計算出鉿原子發光強度底部積分面積，發現多孔隙試片孔洞率由 29.79% ( 奈米矽晶體平均大小約為 5.5 nm ) 至 61.93% ( 奈米矽晶體平均大小約為 3.1 nm ) 時，在  $1.54\text{ }\mu\text{m}$  波長的發光效率增加了 50 倍。

圖 6 各孔隙度摻鉿紅外光激發光光譜

奈米矽晶體的尺寸大小、數量多寡對鉿原子摻雜發光的信號強弱是非常重要的，奈米矽晶體的尺寸越小，代表整個樣品單位面積所含的奈米矽晶體數量多。若摻雜鉿原子後，能量會由奈米矽晶體吸收後傳遞給鉿原子，若單位面積所含的奈米矽晶體數量較多，鉿原子摻雜後所發出的  $1.54\text{ }\mu\text{m}$  波段強度自然就提昇。由拉曼散射光譜、可見光激發光及 TEM 結果皆顯示蝕刻電流密度越大，所形成的孔隙度越大，奈米矽晶體平均尺寸越小。摻雜鉿後的紅外光激發光實驗結果發現，隨著孔隙度的增加奈米矽晶體尺寸越小，將使得發光強度越大。另一方面也

因為奈米矽晶體越小，猜測在樣品內單位面積的奈米矽晶體數量較多，造成能量傳遞機會增多，使得鉺原子發光強度增加。

#### 四、考文獻

- (1) Sandip Tiwari,Farhan Rana, Hussein Hanafi, Allan Hartstein, Emmanuel F. Crabbe', and Kevin Chan Appl. Phys. Lett. **68** (10), 1996

- (2)"Nonvolatile Semiconductor Memory Technology" ED:William D.Brown, Joe E. Brewer ,1998

- (3) Koki Ueno and Nobuyoshi Koshida, Appl. Phys. Lett. **74**, 93 (1999)

- (4)Koki Ueno and Nobuyoshi Koshida, Phy. Stat. Sol.(a), 579,(2000)

- (5) M. L. Brongersma and A. Polman, Appl. Phys. Lett 72 20 2557 (1998)

- (6)L. Khomenkova, N Korsunskaya, J. Phys: Cond. Matt, 14 13217 (2002)

#### 五、自評部分

研究內容與原計劃部分大致相同，惟有含鍺奈米晶體部分，我們沒有全部完成。不過含鍺奈米晶體此部分的結果，我們與長庚大學電機系的賴朝松教授，有共同合作成果的發表在國際期刊。至於奈米矽晶體，我們的研究成果尚還可以。我們正準備要投稿至在國際期刊。