# 行政院國家科學委員會專題研究計畫 期中進度報告

## 氯化氫氟酸在奈米金氧半電晶體之應用及其設備之開發

(1/3)

計畫類別：個別型計畫

計畫編號：NSC94-2215-E-009-071-

執行期間：94 年 08 月 01 日至 95 年 07 月 31 日

執行單位：國立交通大學電子物理學系(所)

計畫主持人：趙天生

報告類型：精簡報告

報告附件：出席國際會議研究心得報告及發表論文

處理方式：本計畫可公開查詢

中 華 民 國 95 年 6 月 1 日

# 行政院國家科學委員會補助專題研究計畫 期中報告

## 氯化氫氟酸在奈米金氧半電晶體之應用及其設備之開發 (1/3)

計畫類別： 個別型計畫 整合型計畫

計畫編號：NSC 94 - 2215 - E - 009 - 071 -

執行期間：94 年 8 月 01 日至 95 年 7 月 31 日

計畫主持人：趙天生 國立交通大學電子物理系教授

成果報告類型(依經費核定清單規定繳交)： 精簡報告 完整報告

本成果報告包括以下應繳交之附件：

赴國外出差或研習心得報告一份

赴大陸地區出差或研習心得報告一份

出席國際學術會議心得報告及發表之論文各一份

國際合作研究計畫國外研究報告書一份

處理方式：除產學合作研究計畫、提升產業技術及人才培育研究計畫、

列管計畫及下列情形者外，得立即公開查詢

涉及專利或其他智慧財產權，一年二年後可公開查詢

執行單位：國立交通大學電子物理系

中 華 民 國 95 年 05 月 31 日

# 行政院國家科學委員會專題研究計畫成果報告

## 氯化氫氟酸在奈米金氧半電晶體之應用及其設備之開發

### (1/3)

#### Reduction of Donor-like Interface Traps of n-Type Metal-Oxide-Semiconductor Field-Effect-Transistors Using Hydrogen-Annealed Wafer and In-situ HF-Vapor Treatment

計畫編號：NSC 94-2215-E-009-071

執行期限：94 年 8 月 1 日至 95 年 7 月 31 日

主持人：趙天生 國立交通大學電子物理系

#### 一、中文摘要

在本次報告中，我們將 n 型金氧半場效電晶體作在經過氬氣退火處理過的晶圓上，再藉由氯化氫氟酸的處理成功的降低了本試品中具”施體傾向”的介面陷阱。閘極氧化層的品質在此方法的處理下可以獲得相當大幅度的改善，例如汲極電流、在應力惡化下的臨限電壓之不穩定性以及轉換電導。我們發現能有如此大幅度的特性改善是由於降低了具施體傾向的介面陷阱。此外，氯化氫氟酸的處理可以減少元件當中的自生氧化層在生長的情形。而當我們同時使用氬氣退火處理過的晶圓以及氯化氫氟酸的處理可以讓元件有最好的特性改善。

關鍵詞：氯化氫氟酸、自生氧化層、氬氣退火

#### Abstract:

In this paper, the n-type metal-oxide-semiconductor field effect transistors (nMOSFETs) of low donor-like interface traps are fabricated on hydrogen-annealed wafers (Hi-wafer) with an in-situ HF-vapor treatment. The gate oxide integrity will be significantly improved in terms of drain current, threshold-voltage shift under stressing and transconductance. We found that the improvement is due to the significant reduction of donor-like interface trapping densities. Besides, the in-situ HF vapor cleaning process will reduce the re-growth of native oxide. This improvement will become distinguished when both Hi-wafer and in-situ

HF-vapor treatment are utilized.

**Keywords:** Hi-wafer, HF-vapor, native oxide, hydrogen-annealed

#### 二、簡介

當 1991 年有人成功的研發出氮氧化矽絕緣層時[1]，利用一氧化二氮( $N_2O$ ) 或者氧化氮(NO) 所成長的氮氧化矽閘(oxynitride) 極介電層就隨著時代的演進而越來越受到重視。而其原因就是此氮氧化矽閘極介電層可以讓元件操作在高電場時能具有高的驅動電流[1]，而且對於 p 型金氧半場效電晶體來說，此氮氧化矽絕緣層可以有效抑制硼穿隧(boron penetration) 的問題[2-3]。此外，利用此氮氧化矽絕緣層所做出來的元件還有高輻射硬度[4]；而且在熱載子惡化的情形下，此元件可以表現出較一般氧化矽絕緣層有更佳的可靠度[5-6]。在此情形下，唯一需要注意的就是利用此氮氧化矽絕緣層所做出來的元件會有比較低的載子遷移率(mobility)[5]。而之所以會降低了元件載子遷移率的原因是因為氮原子併入所造成較淺的具施體傾向(donor-like) 的陷阱(trap)存在於氮氧化矽絕緣層與矽基板的介面處[7-8]。

近來，閘極氧化層的厚度快速向元件的物理極限厚度(1.3-1.5 nm)來靠近，而此物理極限厚度最主要是受制於當閘極氧化層太薄的時候會產生直接導通的電流穿隧現象，而使得元件產生極大的漏電流。有鑑於此，目前就開始以高介電絕緣材料來取代一般傳統的氧化矽絕緣層[9]。但是當高介電絕緣層材料直接沉積在矽基板上

時，我們卻必須面對載子遷移率大幅降低的問題。不過此載子遷移率降低的問題是可以被克服的，只要我們在沉積高介電絕緣層之前先成長一層較薄的氮氧化矽絕緣層當做緩衝層，就可以有效的抑制載子遷移率降低的問題[10]。但是在製程上，此緩衝層卻非常不容易降低其物理厚度，因此，對於以高速應用為主的元件，其等效氧化層厚度往往都是偏高的。在此情況下，當元件的等效氧化層厚度(equivalent oxide thickness)要小於2奈米的厚度時，每當成長閘極氧化層之前會自然形成的自生氧化層(native oxide)就扮演了一個相當重要的角色。如果我們想要改善高介電絕緣層的元件可靠度以及？雜物的擴散問題，首先，我們就是要去研究如何做出好的氮氧化矽緩衝層。如果說氮氧化矽是一定要做在半導體元件中，那因為氮原子併入所引發的載子遷移率降低的問題是一定要去克服的。近來則是有許多人利用不同晶向的矽基板來改善元件載子遷移率的表現[11-12]。除此之外，與一般傳統的Czochralski(CZ)晶圓比較，利用氫氣退火(hydrogen-annealed)處理過的矽晶圓(Hi-wafer)也可以有相對較低的缺陷的降低，主要的原因就是抑制了因為氧而形成晶圓中的缺陷[13-14]。在本次的報告當中，我們成功的將n型金氧半場效電晶體作在Hi-wafer上，並藉由氯化氫氟酸的處理來去除元件中的自生氧化層。而且我們發現在n型金氧半場效電晶體中載子遷移率降低的問題是可以藉由同時使用Hi-wafer以及氯化氫氟酸處理來加以改善。

### 三、實驗

N型金氧半場效電晶體是製作在6吋p型(100)經過(Hi-wafer)上，而其阻值僅有 $3\text{-}6\Omega\text{ cm}$ 。而整套的垂直爐管一共包含了三套模組，分別是氯化氫氟酸清潔系統、氧化成長系統以及 $n^+$ -?雜之多晶矽沉積系統。所以整套的多晶矽/氧化矽/矽結構之金氧半電容(poly-Si/SiO<sub>2</sub>/Si MOS capacitor)便可以在此垂直爐管中以無氧狀態一次完成所有的電容製程，而此製程步驟就不需要有大氣污染的顧慮。為了達成上述所說之製程步驟，垂直爐管必須充滿著高純度

的氮氣，也就是說爐管內所殘餘的氧氣不可以高於4ppm，如此做法才能使在氯化氫氟酸處理完之後也不會有任何的自生氧化層長出來。而本次實驗中我們一共做了四組不同條件的試品，而其閘極氧化層的厚度則是3奈米，在製程條件上試品會分為一般氯化氫氟酸溶液浸泡以及乾式的氯化氫氟酸清潔，之後再把這兩組試品分別利用垂直爐管中的氮氣以及一氧化二氮氣體來加以氧化以形成閘極氧化層，而此氧化的溫度則是800°C。而此閘極氧化層的均勻度在經過測試後發現，一片6吋的試品其誤差會小於 $\pm 1\text{\AA}$ 。而我們先前即利用了二次離子質譜儀(SIMS)來加以分析氧殘留在矽基板表面上的情形是否會因為做了氯化氫氟酸處理而有所改變[15]。而所有的試品會直接在垂直爐管中沉積多晶矽薄膜來作為元件的閘極。而為了將Hi-wafer與一般傳統CZ晶圓做比較，我們將上述相同的製程步驟分別作在Hi-wafer、CZ Si(100)以及Si(111)晶圓來做比較。

### 四、結果與討論

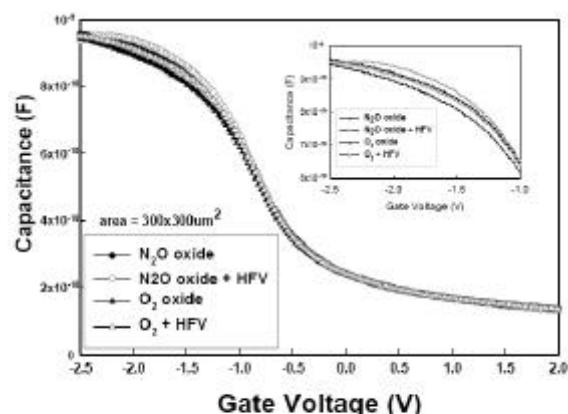

圖一為所有試品之電容-電壓(C-V)特性區線的表現，而我們所量測的試品面積為 $300\times 300\mu\text{m}^2$ 。從此圖中我們可以發現不同試品的電容電壓曲線幾乎都在閘極電壓等於-2.5伏特時重合在一起，此現象表示所有試品的閘極氧化層厚度幾乎是一樣的。

圖一：以Hi-wafer為基板之電容在不同閘極製程方法下之電容-電壓特性曲線。

$\bullet$   $\text{N}_2\text{O}$  oxide；在氯化氫氟酸處理下以 $\text{N}_2\text{O}$ 所成長之氧化層。

$\square$   $\text{N}_2\text{O}$  oxide + HFV；在氯化氫氟酸處理後以 $\text{N}_2\text{O}$ 所成長之氧化層。

$\diamond$   $\text{O}_2$  oxide；在氯化氫氟酸處理下以 $\text{O}_2$ 所成長之氧化層。

$\triangle$   $\text{O}_2$  + HFV；在氯化氫氟酸處理後以 $\text{O}_2$ 所成長之氧化層。此電容面積為 $300\times 300\mu\text{m}^2$ 。插圖為閘極電壓在-2.5到-1.0伏特狀況下之電容-電壓特性曲線。

當閘極電壓從-2.5到-1.0伏(大約在平帶電壓的地方)時，所有的曲線會先分

開，而當閘極電壓大於 -1.0 伏時，所有的曲線又再度的重合在一起。在曲線有分開的區域裡面，其電容值大小依序為  $(N_2O\text{-oxide} + HFV) > (N_2O\text{-oxide}) > (O_2\text{-oxide} + HFV) > (O_2\text{-oxide})$ ，所以我們可以觀察到  $N_2O\text{-oxide}$  電容值是高於  $O_2\text{-oxide}$ ；而經過氯化氫氟酸處理的試品則是大於經過氫氟酸溶液浸泡的試品。此外，我們從圖一中的插圖可以觀察到所有試品在閘極電壓從 -2.5 到 -1.0 伏時的電容電壓放大曲線，電容值從堆積區域(accumulation)往平帶電壓(flat-band)的方向時會減小表示有 trap 存在於介面的地方。而此 trap 是具有 “施體傾向”的陷阱。由此理論來做分析，可以發現到  $N_2O\text{-oxide}$  所擁有的 “施體傾向”的陷阱是小於  $O_2\text{-oxide}$ ；而經過氯化氫氟酸處理的試品則比經過氫氟酸溶液浸泡的試品更容易獲得改善。而且我們可以發現到在所有的試品當中，同時以  $N_2O\text{-oxide}$  來成長且經過氯化氫氟酸處理的試品會擁有最少的 “施體傾向”的陷阱而且具有最大的電容值。

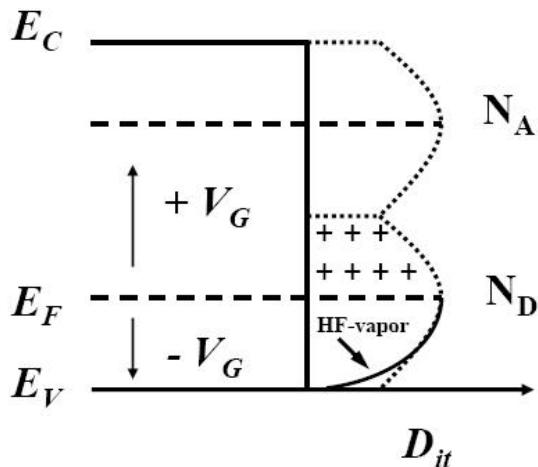

圖二 從能帶圖中可以觀察到費米能階在  $+V_G$  和  $-V_G$  以及有關施體與受體介面缺陷密度的分布情形。 $N_A$  表示為 “受體傾向”的陷阱，而  $N_D$  則為 “施體傾向”的陷阱。實線則代表了 “施體傾向”的陷阱受到抑制。

而  $N_2O\text{-oxide}$  試品經過氯化氫氟酸處理後的能帶圖則表示在圖二，從圖中可以明顯看出具有 “施體傾向”的陷阱在經過氯化氫氟酸處理後會變少(以圖二中實線與虛線作比較)。而當元件操作在負閘極偏壓區時，費米能階(Fermi level)會移向價帶(valance band)，而  $N_2O\text{-oxide}$  試品以及經過氯化氫氟酸處理後的試品因為有較少的 “施體傾向”的陷阱而產生較高的電容值；反觀當閘極電壓處於正偏壓時，所有的介

面陷阱都被電子佔據而使得整體看似中性，因此在電容-電壓量測上面無法看出不同的地方。

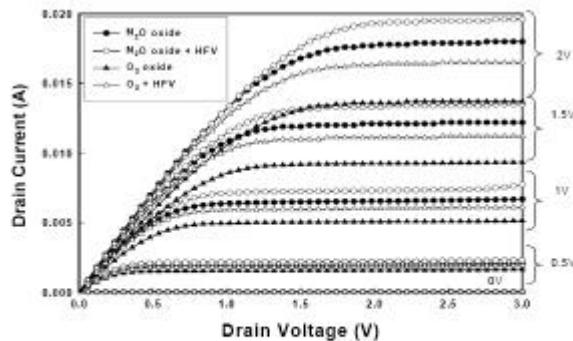

圖三 在不同的閘極電壓下所看到的汲極電流-汲極電壓特性圖。而此張圖的試品為n型半導體製作在氮化矽之上，而其開槽氧化層則分成下列四種情形： $N_2O\text{-oxide} + HFV$ ,  $N_2O\text{-oxide}$ ,  $O_2\text{-oxide} + HFV$ ,  $O_2\text{-oxide}$ 。量測點的長寬比為 100 μm/1μm。

圖三是汲極電流-汲極電壓在不同閘極電壓時的特性曲線。由圖中可以很明顯的觀察到經過氯化氫氟酸處理後的試品會具有較高的汲極電流，而此汲極電流增加的趨勢和先前所提到的電容-電壓特性曲線是一樣的，其汲極電流大小依序為  $(N_2O\text{-oxide} + HFV) > (N_2O\text{-oxide}) > (O_2\text{-oxide} + HFV) > (O_2\text{-oxide})$ ，以  $N_2O\text{-oxide}$  元件來看：有經過氯化氫氟酸處理元件的汲極電流比經過氫氟酸溶液浸泡的元件增加了約 16%；另外一方面來看，有經過氯化氫氟酸處理的  $O_2\text{-oxide}$  元件，其汲極電流會比經過氫氟酸溶液浸泡的  $O_2\text{-oxide}$  元件高了約 20%。在此我們要再度提醒一下， $N_2O\text{-oxide}$  元件的汲極電流是高於  $O_2\text{-oxide}$  元件的汲極電流。而以上所說之有關於  $N_2O\text{-oxide}$  元件的汲極電流在高電場時所獲得的改善與他人先前所做的結果是一致的[16-18]，在高電場時，載子遷移率能獲得改善主要是因為有佔據在傳導帶(conduction-band)的 “受體傾向” 之介面狀(interface states)態受到抑制[16-17]；亦或著是表面散射(surface roughness scattering)與埋設通道(buried-channel)的載子傳輸的結合所造成的結果[18]。此外，也有人曾經提出經過氯化氫氟酸處理的試品的介面會比經過氫氟酸溶液浸泡的試品介面更平滑[19]。而由以上種種效應整合來看，我們就可以知道在本次實驗中的四種元件裡面， $N_2O\text{-oxide}$  的元件再經過氯化氫氟酸的處理會有最高的汲極電流。

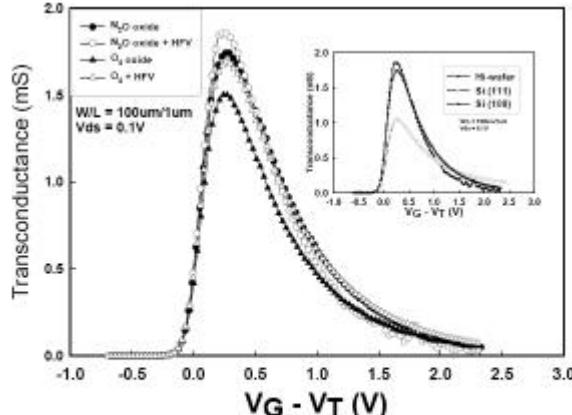

圖四是從元件操作線性區所萃取的轉換電導( $G_M$ )，而  $N_2O\text{-oxide}$  的元件再經過氣

化氫氟酸的處理會有最高的轉換電導，比經過氫氟酸溶液浸泡的O<sub>2</sub>-oxide元件高了約 20%。而此結果與先前他人的研究結果[5]是完全不同的，之前他人所提出的實驗結果說N<sub>2</sub>O-oxide長在CZ Si(100)的G<sub>M</sub>在線性區會小於O<sub>2</sub>-oxide元件的G<sub>M</sub>，而其原因為是因為N<sub>2</sub>O-oxide的元件會有“施體傾向”的陷阱存在於介面處。

圖四 轉換電導在線性區的表現 ( $V_D = 0.1$  V)。而此張圖的試品為n型半導體製作在氮氣過火的晶圓上，而異開槽氧化層則分成下列四種情形： $N_2O$ -oxide + HFV,  $N_2O$ -oxide,  $O_2$ -oxide + HFV,  $O_2$ -oxide。量測點的長寬比為100  $\mu m/1\mu m$ 。插圖比較了經過氯化氫氟酸處理的n型半導體製作在不同的基板上(Hi-wafer, CZ Si(100) and CZ Si(111))的轉換電導。

從我們的實驗結果可以發現此存在於介面處的 trap 可以利用氯化氫氟酸的處理以及使用 Hi-wafer 來加以改善，而且以此方法所製作的元件會有相當好的介面品質。如同先前圖一所看到的，當我們同時使用 Hi-wafer 以及氯化氫氟酸的處理，元件將會有最好的介面品質；這結果與圖三和圖四所得到的實驗結果是相同的。當我們以相同的閘極氧化層並加上氯化氫氟酸的處理方法時，利用不同基板(CZ Si(100)、CZ Si(111)以及 Hi-wafer)所作出來的元件其所顯示出來的轉換電導則呈現於圖四中的插圖。由此圖可以很明顯的觀察到將 n 型半導體製作於 Hi-wafer 上會有最大的轉換電導。即使 Si(111)元件在經過氯化氫氟酸的處理後其轉換電導可以獲得改善[15]，但是其轉換電導仍低於 Si(100)元件。先前曾有人提出在 CZ 晶圓中會有大量的氧，而且會與氮形成氮氧施體傾向的陷阱(nitrogen-oxygen donor-like traps)[7-8]。但是此大量的氧缺陷是可以藉由經過氫退火處理的 Hi-wafer 來獲得有效的改善[13-14]，更因此導致 n 型半導體元件可以有較高的電容值、較高的驅動電流以及較高的轉換電導。在我們先前的研究中[15]可以看到，利用氯化氫氟酸的處理來抑制

自生氧化層時也會更進一步地降低了在介面的氧。由此實驗結果就可以很清楚的理解了為什麼同時使用 Hi-wafer 以及氯化氫氟酸處理可以使元件有最佳的特性表現。

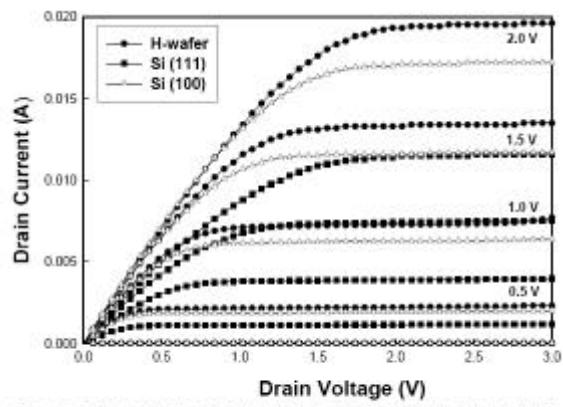

圖五 在不同的閘極電壓下所看到的汲極電流-汲極電壓曲線圖。而此張圖的元件是以  $N_2O$  成長的閘極氧化層並經過氯化氫氟酸處理的 n 型半導體製作在不同的基板之上，而其基板分別為 Hi-wafer、CZ Si(100) 以及 CZ Si(111)。量測點的長寬比為  $100 \mu m/1\mu m$ 。

圖五 在不同的閘極電壓下所看到的汲極電流-汲極電壓曲線圖。而此張圖的元件是以  $N_2O$  成長的閘極氧化層並經過氯化氫氟酸處理的 n 型半導體製作在不同的基板之上，而其基板分別為 Hi-wafer、CZ Si(100) 以及 CZ Si(111)。而此量測元件的長寬比為  $100 \mu m/1\mu m$ 。從此圖中可以清楚地發現利用 Hi-wafer 所製作的元件其汲極電流比 Si(111) 所製作的元件高了 72%；而以 Si(100) 所製作的元件也比 Si(111) 所製作的元件增加了 53%。再將利用 Hi-wafer 所製作的元件與以 Si(100) 所製作的元件來加以比較，可以發現利用 Hi-wafer 所製作的元件其汲極電流比 Si(100) 所製作的元件增加了 12%。綜合以上的實驗結果，將以  $N_2O$  所成長的閘極氧化層並經過氯化氫氟酸處理的 n 型半導體製作在 Hi-wafer 上會是本實驗中所有元件裡面的最佳選擇。

## 五、結論

由本次的報告中可以清楚地觀察到，將 n 型半導體製作在 Hi-wafer 上並以氯化氫氟酸來處理可以在電性表現上獲得大幅度且明顯的改善。同時使用 Hi-wafer 以及氯化氫氟酸處理可以降低使元件中具施體傾向的陷阱密度，而此大幅的改善可使元件有較好的閘極絕緣層，在驅動電流與轉換電導上有更佳的特性表現。

## 參考文獻

- [1] W. Ting, G. Q. Lo, J. Ahn, T. Y. Chu and D. L. Kwong: IEEE Electron Device Lett. **12** (1991) 416.

- [2] L. K. Han, D. Wristers, J. Yan, M. Bhat and D. L. Kwong: IEEE Electron Device Lett. **16** (1995) 319.

- [3] T. S. Chao, C. H. Chu, C. F. Wang, K. J. Ho, T. F. Lei and C. L. Lee: Jpn. J. Appl. Phys. **35** (1996) 6003.

- [4] G. Q. Lo, A. B. Joshi and D. L. Kwong: IEEE Electron Device Lett. **40** (1993) 1565.

- [5] H. Hwang, W. Ting, D. L. Kwong and J. C. Lee: IEEE Electron Device Lett. **12** (1991) 495.

- [6] M. Bhat, J. Kim, J. Yan, G.W. Yoon, L. K. Han and D. L. Kwong: IEEE Electron Device Lett. **15** (1994) 421.

- [7] M. Suezawa, K. Sumino, H. Harada and T. Abe: Jpn. J. Appl. Phys. **25** (1986) L859.

- [8] A. T. Wu, T. Y. Chan, V. Murali, S. W. Lee, J. Nulman and M. Garner: International Electron Devices Meeting (1989) 271.

- [9] Y. Taur: IBM J. Res. Dev. **46** (2002) 213.

- [10] M. Yang, E. P. Gusev, M. Ieong, O. Gluschenkov, D. C. Boyd, K. K. Chan, P. M. Kozlowski, C. P. D'Emic, R. M. Sicina, P. C. Jamison and A. I. Chou: IEEE Electron Device Lett. **24** (2003) 339.

- [11] H. S. Momose, T. Ohguro, S. Makamura, Y. Toyoshima, H. Ishiuchi and H. Iwai: IEEE Trans. Electron Devices **49** (2002) 1597.

- [12] K. Onishi, C. S. Kang, R. Choi, H. J. Cho, Y. H. Kim, S. Krishnan, M. Shahariar and J. C. Lee: IEEE Electron Device Lett. **24** (2003) 254.

- [13] K. Izunome, H. Shirai, K. Kashima, J. Yoshikawa and A. Hojo: Appl. Phys. Lett. **68** (1996) 49.

- [14] Y. Matsushita, S. Samata, M. Miyashita and H. Kubota: International Electron Devices Meeting (1994) 321.

- [15] T. S. Chao, Y. H. Lin and W. L. Yang: IEEE Electron Device Lett. **25** (2004) 625.

- [16] T. Hori: IEEE Trans. Electron Devices **37** (1990) 2058.

- [17] H. Hwang, W. Ting, D. L. Kwong and J. Lee: IEEE Electron Device Lett. **9** (1991) 495.

- [18] J. S. Cable and C. S. Woo: IEEE Trans. Electron Devices **39** (1992) 607.

- [19] A. Chin, B. C. Lin, W. J. Chen, Y. B. Lin and C. Thai: IEEE Electron Device Lett. **19** (1998) 42.