# 行政院國家科學委員會專題研究計畫 成果報告

總計畫(3/3)

計畫類別：整合型計畫

計畫編號：NSC94-2220-E-009-006-

執行期間：94 年 08 月 01 日至 95 年 07 月 31 日

執行單位：國立交通大學電子工程學系及電子研究所

計畫主持人：蔣迪豪

報告類型：完整報告

處理方式：本計畫可公開查詢

中 華 民 國 95 年 10 月 31 日

## 一、計畫簡介(敬請簡要描述)

SOC 整合是未來發展的趨勢其相關研究及產業發展有別於半導體及資訊產業兩者，對於跨研究領域系統整合有高度的要求。本研究計劃之目標在於研究與設計具新世代行動通訊 3G 無線接取(Wireless Access)能力的多媒體高度整合晶片。其中主要研究內容包括：

- MPEG-4/21 SOC 設計及新世代行動通訊之研究

- 應用於多媒體晶片系統之低電壓高頻寬內嵌式記憶體之研究

- 多媒體通訊數位基頻 SOC 加速架構及嵌入式作業系統界面之研究

- 新世代無線通訊系統對異質性服務媒體接取控制之研究

- 結合基頻與視訊處理技術在行動通訊應用之研究

- MPEG-4/21 射頻傳收設計之研究

- MPEG-21 多媒體通用存取架構下數位元件可適性之即時視訊轉碼系統之設計與製作之研究

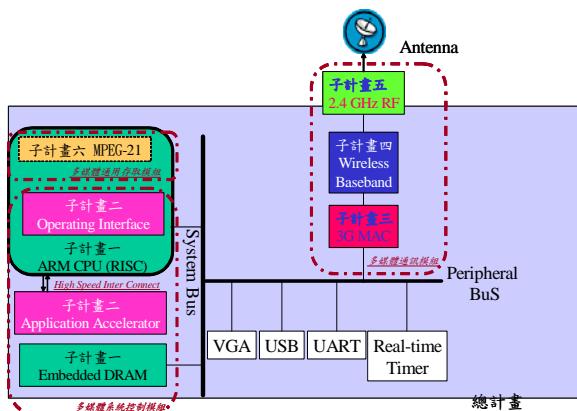

圖一：基於 MPEG-4/21 標準的 3G 無線接取多媒體高度整合晶片系統架構

圖一說明本計劃之系統整合架構圖。目前本計劃主要研究成果包括多媒體系統控制模組和多媒體通訊模組兩部份：

## 二、重要執行成果及價值(計畫產生對國家有最重要價值之影響)

本計劃主要研究成果包括多媒體系統控制模組和多媒體通訊模組兩部份：

### 1. 多媒體系統控制模組

多媒體控制系統設計是以 MPEG 正在發展中的 Reconfigurable Video Coding (RVC) 的架構為主要的設計目標，以期能支援不同視訊壓縮法的解碼器的動態產生。由於 RVC 為目前 MPEG 工作中的項目，所以目前的設計都是以軟體 (C model 或其它 behavioral model 的模擬平台，如 Moses for CAL 來進行研究)。本團隊因為積極參與 MPEG 標準的制訂，所以能隨時根據最新的結果來修正設計這個平台。

多媒體控制系統設計主要的研究內容包含(a)設計多媒體雙核心系統、(b)設計多媒體之硬

體加速 SoC 平台、(c) 設計 MPEG-21 多媒體通用存取系統、以及 (d) 整合 ARM-9 CPU (從國科會國家晶片系統設計中心獲得) 低電壓高頻寬內嵌式記憶體 以及 周邊設備之 IP。主要研究成果如下：

- a. 在 TI OMAP OSK5912 平台上發展一套 Heterogeneous Multi-Processor (HMP) 的動態工作切割排程作業系統核心

- 善用 arm 以及 dsp 雙核心效能，證明 tightly-coupled system 在複雜的多媒體平台效能比 loosely-coupled system 好

- 發展自己的 DSP scheduler 來幫助作 task 的排程。

- Porting eCos 到 TI omap 平台上，並開發雙核心有效的溝通協定。

- 設計一個可以配合 eCos MLQ scheduler 的動態分工模組。

- 設計新的異質多核心的新 Programming model。

- 實作出支援動態分工應用程式的開發工具。

- b. 設計多媒體之硬體加速 SoC 平台，以利軟硬體協同設計，有別以往純硬體佈線的設計。本平台的架構設計是以能直接支援 MPEG 正在發展中的 Reconfigurable Video Coding (RVC) 為主要的目標。

- 在所設計的硬體加速平台開發以 table-driven 的軟體 Finite State，並實作 MPEG RVC Framework 中的 Global Control Unit (GCU) 藉以完成模擬 H.264 和 MPEG-4 SP 的 decoder 的功能。

- 在 ARM 平台上完成 Motion-estimation：計算達到 1/4 pel，參考多個 reference frames 以及所有 sub block 模式

- 在 ARM 平台上完成 Deblocking filter

- 在 ARM 平台上完成 8x8 DCT/IDCT

- 在 ARM 平台上完成 4x4 transform/inverse transform

- 在 ARM 平台上完成 quantizer/de-quantizer

- 在 ARM 平台上完成 intra-prediction unit

- c. 整合靜態及動態記憶體結構提供多媒體系統所需之內嵌式記憶體 (SSM)

- 訂定內嵌式系統階層記憶體之架構架構及介面電路，融合 SRAM+Flash、DRAM+Flash、SRAM+DRAM+Flash

- d. 利用 MPEG-21 多媒體通用存取系統開發可適性之即時視訊轉碼系統

- 發展基於 MPEG4-AVC 標準的數位轉碼功能，主要包含子母畫面之功能結合，可應用於視訊傳輸伺服器端

- 在傳統轉碼技巧外，研發快速轉碼演算法，可將每秒轉碼幅數提高超過50倍

- 研發之快速演算法亦有利於硬體實現，未來可進一步以硬體加速此快速轉碼器

e. 設計軟硬體多媒體之整合介面，方便業界技術轉移

## 2. 多媒體通訊模組

多媒體通訊模組主要在提供多媒體視訊與音訊位元流之合適的無線傳輸環境。主要在完成 3G 無線接取多媒體高度整合晶片相關技術研發及離形系統。其中包括 11 Mbps 高速無線網路所有 IP、媒體接取控制層 [Medium Access Control] 模組。主要研究成果包括

a. 多媒體傳輸在 cdma2000 系統上的研究

- cdma2000 的 MAC 模擬平台和傳輸技術研究

- RLP 重新傳輸的效能和 RLP 造成延遲增加對 TCP 的影響的研究

- MAC 重新傳輸的效能和 RLP 和 MAC 之間的比較研究

- TCP 在無線環境下的改良技術研究

b. 無線通訊系統設計驗證技術開發

- MAC SoC 發展驗證平台之建立

- MAC 模組化之設計驗證發展流程開發

- 一個又效率的媒體控制設計和實現流程，從演算法設計、模擬、以純軟體在 Arm 平台上實現媒體接取控制，進而到軟硬體分割實現。

- 一個在超寬頻 (ultra wideband) 系統上考慮多媒體品質需求的排程演算法。

c. 低功率、雙模式 OFDM 基頻處理器

在本研究中，我們利用經過PN碼展頻或Pilot的Data欄位來消除通道中的非理想效應，例如高斯雜訊、載波頻率誤差、載波相位誤差、以及取樣頻脈誤差等等。在這些非理想效應加成下，會導致接收器的訊號會失真，所以我們提出的演算法並須可以在高斯雜訊、和多重路徑...等通道效應下，正確、有效的可以解出並補償取樣頻脈誤差。我們所提出的演算法中，接收器只需要利用PN碼展頻或Pilot的Data欄位就可以得知通道的重要參數，而不須其他的任何協助，此法也可利用於非PN碼展頻系統。為了瞭解整個系統，我們使用Matlab 建立了系統模擬平台。我們可以觀察系統中任一訊號的波形，並且可以得知通道中的非理想效應對整個系統或某些訊號有何影響。此平台更可以用來驗證我們所提出的同步演算法。以下詳列相關研究成果：

- 建立一個考量到 Front-end 效應的 Baseband 整合系統平台。

- 基頻關鍵技術演算法方面有：Estimation and Compensation for Front-End Impairments 演算法、IQ Imbalance Compensation with Carrier Frequency Offset 演算法、Frequency-Domain 通道等化器的設計、Anti-Jamming synchronization 演算法、Frequency domain based Dynamic Sampling algorithm。

- 使用單通道 OFDM 之 FFT 訊號處理的技巧，估計多路徑衰減對時域訊號所造成的失真，設計完成可檢測 150ns rms 的多路徑衰減。

- 「可適性 OFDM 等化器」：利用 Pilot 資訊改進 OFDM 等化器對通道響應發生 Null 時，所造成嚴重的系統性能衰減。並且經由實際晶片的驗證，可使單通道 OFDM 系統對抗 Null 的特殊通道響應改善系統所需 SNR 約 5dB。

- 「1x 低功率同步取樣迴路」：解決單通道 OFDM 系統對 over sampling 的依賴，以動態取樣為基礎，設計完成可對抗 150ns rms 多路徑衰減的一倍時間同步迴路並可容忍 800ppm 的時脈錯誤。

- 「全數位 I/Q 補償迴路」：利用 Pilot 資訊矯正類比電路所造成系統匹配不良，避免系統性能因此降低。並且經由實際晶片的驗證，使單通道 OFDM 系統可對抗  $20^\circ$  phase error 和 2dB gain error 的 I/Q mismatch。

- 「可容忍 I/Q 匹配不良之 CFO 補償迴路」：解決單通道 OFDM 系統對 I/Q 匹配不良時，避免系統性能因頻率追蹤誤差而降低。設計完成可在  $20^\circ$  phase error 和 2dB gain error 的 I/Q mismatch 之下，追蹤、補償 200ppm 的頻率錯誤。

- 「低取樣之雙模式封包檢測」：解決雙模式接收器封包檢測之取樣速率問題，搭配動態取樣迴路可降低待機時封包檢測所需之取樣頻率至 Baud rate 以下，並且經由實際晶片的驗證，可使單通道雙模式 OFDM/CCK 系統之待機取樣頻率降至 5MHz ~ 10MHz。

- 「全數位抗干擾 AGC」：利用低功率指標暫存匹配濾波器，直接計算接收訊號的 PAPR 與功率，以控制類比接收端的增益大小，並可容忍 interference 和 jamming 的干擾，確保接收器處於最佳的狀態。

- 「泛用型通道檢測器」：使用單通道 OFDM 之 FFT 訊號處理的技巧，估計多路徑衰減對「時域訊號」所造成的失真，設計完成可檢測 150ns rms 的多路徑衰減。

#### d. MPEG-4/21 射頻傳收器設計

- 針對 MPEG IV-21 射頻傳收系統設計所需建立之設計要項進行技術開發及環境建立，包括：元件佈局設計及特性分析，射頻積體電路元件模型庫之建立，射頻傳收系統架構評估，射頻傳收系統積體電路晶片組設計。

- 從系統架構分析著眼，考量 CMOS 特性在不同頻段的表現，依鏈結預算決定各電路模組規格，進而針對下列四種電路模組從事架構評估及設計：低雜訊放大器(Low Noise Amplifier, LNA)，混波器(Mixer)，電壓控制震盪器(Voltage Controlled Oscillator, VCO)。

- 針對 MPEG IV-21 射頻傳收系統與基頻電路之整合，針對混合訊號電路設計技術作開發研究。以所發表之 dual-band Mixer 為例，利用單一電路便可實現雙頻帶的傳接收器，可大大減少產品設計時，所需的晶片面積，進而降低產品的生產成本。而經由射頻傳收系統與基頻電路之整合系統設計，可預期整個系統連結時的特性，以其縮短產品的設計時程。

### 三、 成果效益(敬請簡要描述)

#### (一) 學術技術面

本計劃截至 95 年 7 月止共計發表了 41 篇的期刊和會議論文(33 篇國際論文、8 篇國內論文)、14 項之美國和中華民國專利(另外 13 件申請中)。次外，部份技術已發表於 IEEE 802 通訊標準會議和 MPEG/JVT 之視訊標準會議。另有兩項與 Xilinx 和瑞士 EPFL 學術機構的人員互訪與國際合作。

#### (二) 經濟面效益

本計畫針對多媒體通訊系統開發低電壓高頻寬嵌入式記憶體、發展雙核心架構多媒體通訊韌體以及 H.264 編碼加速器、結合基頻與視訊處理技術、並以 RF/MMIC 進行設計及生產無線通訊系統、與設計即時視訊轉碼之系統。開發之技術不僅實現 MPEG-21 之多媒體系統，同時也協助業界和學術界了解最新之視訊標準技術。此外，所提之技術可以有效解決行動應用上基頻傳輸的問題。同時以 RF/MMIC 進行設計及生產可將不但可以降低成本，亦減低其應用的困難度，能大幅降低應用廠商的技術阻礙。故隨著成本的降低，以及縮短產品設計週期，因而提升自身產品在市場的競爭力，繼而產生較大的經濟利潤。因產品之設計更符合消費者在使用上所要求的輕薄短小，以及省電等需求，因此更易於開拓廣大的無線通訊市場。

#### (三) 社會面效益

提升關鍵零組件和系統產品的競爭優勢以及附加價值，並積極整合產學研的研發能量，將有助於提升系統規格制定的能力及研究效力。同時，了解 MPEG-21 標準之最新發展與國外領先公司之技術，知己知彼有助於國內相關產業之成長與規畫未來之藍圖。在所發展之 MPEG-21 測試平台，有助於發展更精進的技術與評估技術能力，比如研發電子商務系統，視訊電話與開發多媒體資訊系統。完成之技術可提高本國產業在多媒體系統建立與通用存取環境的建立上有相當大的競爭力。藉由所發展之 MPEG-21 測試平台，進一步培育多媒體系統技術之相關的人才，以建立並厚實國內相關產業之實力。

### 四、 整體計畫進度

|                 |     |         |     |

|-----------------|-----|---------|-----|

| 總預定/實際執行進度差異(%) | 100 | 總支用數(%) | 100 |

|-----------------|-----|---------|-----|

## 五、績效指標

| 績效指標         | 目標值                | 初級產出                   | 效益                                | 重大突破                     |

|--------------|--------------------|------------------------|-----------------------------------|--------------------------|

| 論文           | 國內：<br>國外：         | 國內：8<br>國外：33          | 提昇 wireless Multimedia 技術         | 0.18um RFCMOS PA 及 Rx 設計 |

| 研究團隊養成       |                    |                        |                                   |                          |

| 專業人才培育       | 博碩士<br>人數：         | 博碩士<br>人數： <b>45</b>   | Wireless<br>Multimedia 專業<br>人才養成 |                          |

| 形成教材         |                    |                        |                                   |                          |

| 專利           | 已獲得專利：<br>(申請中專利：) | 已獲得專利：14<br>(申請中專利：13) |                                   |                          |

| 技術報告         | 數量：                | 數量：0                   |                                   |                          |

| 技術移轉         | 可移轉技術：件<br>先期技轉：家  | 可移轉技術：0 件<br>先期技轉：0 家  |                                   |                          |

| 規範/標準制訂      |                    | 1                      | 提昇 RF IPQ 技術<br>發展                | 提出 RF IPQ 增訂<br>規範       |

| 促成廠商投資       |                    | 0                      | NA                                | NA                       |

| 協助提升我國產業全球地位 |                    | 1                      | 提昇 RF IPQ 技術<br>發展                | 提出 RF IPQ 增訂<br>規範       |

## 六、論文與專利發表列表

### (A)期刊論文

- [1] Jin-Hwa Guo, Jui-Yuan Yu, and Terng-Yin Hsu, “Design and Analysis of Packet Synchronizer in Dual-Mode DSSS/OFDM Wireless Systems,” *WSEAS Trans. on Communication*, 2005

- [2] Terng-Ren Hsu, Terng-Yin Hsu, and Chen-Yi Lee, “Design and Analysis of Neural-based Equalization for NRZ Signal Recovery in Band-Limited Channels,” (Revised) *IEEE Trans. Neural Network*.

- [3] Jui-Yuan Yu, Jyh-Neng Yang, Hsuan-Yu Liu, Terng-Yin Hsu, and Chen-Yi Lee, “A Filterless Adaptive Technique for I/Q Mismatch Compensation in OFDM Systems” (Revised) *IEEE Trans. CAS I*

- [4] Ming-Fu Sun, Jui-Yuan Yu, and Terng-Yin Hsu, "A Novel Carrier Frequency Offset Estimation with I/Q Mismatch in OFDM Systems", submitted to *IEEE Trans. CAS I*

- [5] Chueh-An Tsai, and Terng-Yin Hsu, "Design of OFDM-based Channel Estimation with Joint Equalization for Wireless Broadband Single-Core Approaches", submitted to *IEEE Trans. CAS I*

- [6] Ming-Fu Sun, Ta-Yang Juan, Ming-Yeh Wu, and Terng-Yin Hsu, "Estimation and Compensation for Front-End Impairments in Wireless OFDM Systems", submitted to *IEEE Trans. on Wireless*

- [7] H. C. Huang, W. H. Peng, T. Chiang, and H. M. Hang, "Advances in the Scalable Extension of H.264/AVC," *IEEE Communication Magazine*, 2006. (Accepted with minor revision)

- [8] W. H. Peng, T. Chiang, H. M. Hang and C. Y. Lee, "A Context Adaptive Binary Arithmetic Codec with Maximum likelihood based Stochastic Bit Reshuffling (SBR) Technique for Scalable Video Coding," *IEEE Trans. on Multimedia*, Multimedia, vol. 8, no. 4, pp. 654-667, Aug. 2006.

- [9] S. C. Chang, W. H. Peng, S. H. Wang and T. Chiang, "A Platform based Bus-interleaved Architecture for Deblocking Filter in H.264/MPEG-4 AVC, " *IEEE Trans. on Consumer Electronics*, vol. 51, no. 1, pp. 249-255, Feb. 2005.

- [10] S. H. Wang, W. H. Peng, Y. W. He, G. Y. Lin, C. Y. Lin, S. C. Chang, C. N. Wang and T. Chiang, "A Software-Hardware Co-Implementation of MPEG-4 Advanced Video Coding (AVC) Decoder with Block Level Pipelining, " *International Journal of VLSI Signal Processing*, vol. 41, no. 1, pp.93-110, Aug. 2005

## (B)研討會論文

- [1] Lei-Fone Chen, Yuan Chen, Lu-Chung Chien, Ying-Hao Ma, Chia-Hao Lee, Yu-Wei Lin, Chien-Ching Lin, Hsuan-Yu Liu, Terng-Yin Hsu, and Chen-Yi Lee, "A 1.8 V 250 mW COFDM Baseband Receiver for DVB-T/H Applications," in *ISSCC*, Feb, 2006.

- [2] C.-H. Li, C.-H. Chang, W.-H. Peng, W. Hwang and T. Chiang, "Design of Memory Sub-System in H.264/AVC Decoder," (Accepted by ICCE 2007)

- [3] H. C. Huang, W. H. Peng, T. Chiang, and H. M. Hang, "Cross-layer System Designs for Scalable Video Streaming over Mobile WiMAX," (Submitted to IEEE WCNC 2007, Wireless Communications & Networking Conference)

- [4] T.-H. Lai, C.-N. Wang and T. Chiang, "A NMR OPTIMIZED BITRATE TRANSCODER FOR MPEG-2/4 LC-AAC, " (Submitted to ISCAS'07)

- [5] C.-H. Chang Chang, C.-H. Li, W.-H. Peng, W. Hwang and T. Chiang, "A Flexible Two-Layer External Memory Management for H.264/AVC Decoder," (Submitted to ISCAS'07).

- [6] C.-H. Li, C.-C. Chen, W.-C. Su, M.-J. Wang, W.-H. Peng, G.-G. Lee and T. Chiang, "An Unified Systolic Architecture for Combined Inter and Intra Predictions in H.264/AVC Decoder,"

ACM Wireless Networks, in *ACM Int. Conf. on Wireless Networks, Communications and Mobile Computing (IWCNC'06)*, Vancouver, July 2006

- [7] W. H. Peng, T. Chiang and H. M. Hang, "Adding Selective Enhancement in Scalable Video Coding Standard for Region-of-Interest Functionality," *IEEE Int'l Symposium on Circuits and Systems*, Greece, 2006.

- [8] W. H. Peng, C. Y. Tsai, T. Chiang and H. M. Hang, "Advances of MPEG Scalable Video Coding Standard", *IEEE Int'l Workshop on Intelligent Information Hiding and Multimedia Signal Processing*, Melbourne, Sep. 2005.

- [9] Y.-Y. Wang and C.-J. Tsai," An Efficient Dual-Interpolator Architecture for Sub-pixel Motion Estimation," Proc. IEEE Intern. Symposium on Circuit and System, 2005.

- [10]C.-N. Chiu, C.-T. Tseng, and C.-J. Tsai,, "Tightly-Coupled MPEG-4 Video Encoder Framework on Asymmetric Dual-Core Platforms, " Proc. IEEE Intern. Symposium on Circuit and System, 2005

- [11]Y.-H. Yu and C.-J. Tsai, "A Model-based Rate Allocation Mechanism for Wavelet-based Embedded Image and Video Coding," Proc. IEEE Intern. Symposium on Circuit and System, 2005

- [12]C.-H. Chen and C.-J. Tsai, "Out-of-Loop rate control for video codec hardware/software co-design," Proc. IEEE Intern. Symposium on Circuit and System, 2005

- [13]Hung Hui Juan and ChingYao Huang, "Adaptive UMTS Handover Control Algorithm in Third Generation Wireless Systems," December, 2005.

- [14]ChengTa Chang and ChingYao Huang, "Capacity-Based Compressed Mode for Inter-System Handover in UMTS," April, 2006

- [15]Chie Ming Chou, ChingYao Huang, and Chung-Ju Chang , "Dynamic Vertical Handover Control Algorithm for WLAN and UMTS," April, 2006

- [16]Yuan-Hwai Shih and ChingYao Huang, "A Buffer Time based Call Admission Control Algorithm for Real-time Traffic in IEEE 802.11e WLAN," May, 2006

- [17]Chung-Ju Chang, Frank C. M. Yen, Yih-Shen Chen, and ChingYao Huang, "A Novel Adaptive P-Persistent MAC Scheme for WLAN Providing Low Delay Variance, " June, 2006

- [18]YuLong Fan, ChingYao Huang, and YongLan Tseng,, "Multimedia Services in IEEE 802.11e WLAN Systems," July, 2006

- [19]Mei-Fen Chou, Wen-Shen Wuen, Chang-Ching Wu, Kuei-Ann Wen, and Chun-Yen Chang, „A CMOS Low-Noise Amplifier for Ultra Wideband Wireless Applications,“IEICE Trans. Fundamentals, November, 2005.

- [20]Mei-Fen Chou; Wen-An Tsou; Dunn, R.H.; Hsiang-Lin Huang; Kuei-Ann Wen; Chun-Yen Chang, „A CMOS Distributed Amplifier with Current Reuse Optimization, “ISCAS 2006

- [21]Chih-De Hung, Wen-Shen Wuen, mei\_Fen Chou, Kuei-Ann Wen, „A Unified Behavior Model of Low Noise Amplifier for System-Level Simulation, “European Microwave

- [22] Po-Tsang Huang and Wei Hwang, „2-Level FIFO Architecture Design for Switch Fabrics in Network-on-Chip, “IEEE International Symposium on Circuits and Systems, 2006

- [23] Tzu-Chiang Chao and Wei Hwan, “A 1.7mW All Digital Phase-Locked Loop with New Gain Generator and Low Power DCO, ” IEEE International Symposium on Circuits and Systems, 2006

- [24] Yu-Yuan Su, Chun-Jen Tsai, “A Dual-Core Dynamic Scheduling Paradigm For Embedded Multimedia Applications,” Proc. VLSI Design/CAD 2006

- [25] Chih-Peng Wang, Kuo-Cheng Lee, and Chun-Jen Tsai, “Design And Analysis of An Unified Asymmetric Multiprocessor Scheduler,” Proc. VLSI Design/CAD 2005

- [26] Jian-Hau Wu and Wei Hwang, “ 1024-point Energy-Aware FFT Processor Using Dynamic Frequency-Voltage Management Technique, “VLSI Design/CAD Symposium

- [27] Wei-Chih Hsieh, Chung-Hsien Hua, Wei Hwang, “ Clustered Mulit-Ported Register File With Built-In-Self-Test Circuitries in 90nm CMOS Technology, “VLSI Design/CAD Symposium

- [28] Zong-Xi Yang, Ming-Hung Chang and Wei Hwang, “ A 2.9mW ADPLL-Based Frequency Synthesizer for High Speed Clock Generation, “VLSI Design/CAD Symposium

- [29] Jen-Wei Yang, Po-Tsang Huang and Wei Hwang, “ On-Chip DC-DC Converter with Frequency Detector Design for Reconfigurable Multiplier-Accumulator Unit, “VLSI Design/CAD Symposium

- [30] Ching-Yun Cheng, Ming-Hung Chang and Wei Hwang, “ Power-Gating Sense Amplifier of Low Power PSEUDO SRAM“VLSI Design/CAD Symposium

- [31] Po-Tsang Huang, Wei-Keng Chang and Wei Hwang, “ Low Power Content Addressable Memory with Pre-Comparison Scheme and Dual-VDD Technique, “VLSI Design/CAD Symposium

### (c)專利

- [1] 黃經堯, 蔡明原, 黃作, “無線通訊動態通訊品質多重斜率通訊交遞技術演算法則”

- [2] 黃經堯, 張正達, 何玠原, “第三代 UMTS 系統於異質系統交接中基於系統容量的壓縮模式控制方法”

- [3] 蔣迪豪, 黃經堯, 莊孝強, “基於行動裝置之視訊串流可適性媒體播放控制”

- [4] 黃經堯, 范裕隆, 洪玉如, “無線區域網路支援服務品質之排程方法”

- [5] 黃經堯, 羅文嶽, 程士恆, 陳欽健, “在無線通訊系統下適應性 RTO 的預測方法”

- [6] 黃經堯, 周建銘 “針對 WLAN 與 UMTS 整合系統之新穎異質切換控制法”

- [7] 溫文燊、溫瓊岸, “低閃爍雜訊電流摺疊混波器”

- [8] 黃項群,王俊能,蔣迪豪,杭學鳴, “堆疊式影像編碼與解碼裝置”

- [9] 蔡家揚,蔡尚軒,杭學鳴,蔣迪豪,吳國瑞, “視訊影像處理方法”

- [10] 蘇子良,王俊能,蔣迪豪,李志鴻, “使用於M P E G - 4 之具有位元率-失真度最佳化畫面內更新的容錯編碼器”

- [11] 黃威、華重憲, “具有資料保存以及中間模式之電源閘結構”

- [12] 黃威、鄭東栓 “隨機存取記憶體陣列結構”

- [13] 黃威、華重憲 “Power Gating Structure Having Data Retention and Intermediate Mode”

- [14] Huang; Hsiang-Chun (Junghe, TW), Wang; Chung-Neng (Kaohsiung, TW), Chiang; Tihao (Taipei, TW), Hang; Hsueh-Ming (Hsinchu, TW) “Architecture and method for fine granularity scalable video coding”